## Verification and Simulation of Self-Adaptive Mechatronic Systems

by

Christian Heinzemann

Fakultät für Elektrotechnik, Informatik und Mathematik Heinz Nixdorf Institut und Institut für Informatik Fachgebiet Softwaretechnik Zukunftsmeile 1 33102 Paderborn

# Verification and Simulation of Self-Adaptive Mechatronic Systems

## PhD Thesis

to obtain the degree of "Doktor der Naturwissenschaften (Dr. rer. nat.)"

> by CHRISTIAN HEINZEMANN

Referee: Prof. Dr. Wilhelm Schäfer

Paderborn, September 2015

# Abstract

Self-adaptive mechatronic systems automatically adapt their behavior to a changing environment by reconfiguring their software architecture at runtime. In particular, this includes to dynamically form systems of systems at runtime, where several systems collaborate with each other using message-based communication protocols. Often, these systems are safety-critical and need to satisfy hard real-time constraints, i.e., any (timing) error in their behavior may put lives at risk. As a consequence, the software of a mechatronic system needs to meet high quality standards. In particular, it needs to be guaranteed that reconfigurations of the software architecture do not lead to an unsafe behavior or a violation of the real-time constraints. Testing alone cannot prove the correctness and thereby the safety of the mechatronic systems either provide support for analyzing real-time constraints or for analyzing reconfigurations of the software architecture, but none of the existing approaches supports both.

In this thesis, we present a combination of constructive and analytical techniques that can be used by software engineers as part of a model-driven software engineering method for assuring the correctness of the software of a self-adaptive mechatronic system. As a key novelty, our approach combines formal verification and simulation-based testing for achieving a scalable analysis of the system's software. As a basis, our component-based software architecture explicitly separates discrete event-based software components from time-continuous feedback controllers. This enables to verify the software components using a compositional model checking approach that we extended by a refinement check for message-based communication protocols. The correct integration of software components and feedback controllers is assessed by a testing-based approach based on model-in-the-loop simulation. Finally, we define an approach for specifying and verifying the reconfiguration behavior of software components that, in particular, separates the reconfiguration behavior from the functional behavior for improving scalability of the verification.

We evaluated all of our contributions based on the RailCab system. In particular, we specified a component-based software architecture including reconfigurations for a RailCab and conducted two case studies. These case studies demonstrate the viability of our techniques.

## Zusammenfassung

Selbstadaptive mechatronische Systeme passen ihr Verhalten über die Rekonfiguration ihrer Softwarearchitektur zur Laufzeit automatisch an eine sich verändernde Umwelt an. Dies ermöglicht insbesondere die Bildung von sogenannten "Systems-of-Systems" zur Laufzeit, in denen mehrere eigenständige Systeme unter Verwendung nachrichtenbasierter Kommunikationsprotokolle miteinander kollaborieren. Dabei müssen die einzelnen Systeme in der Regel harten Echtzeitanforderungen genügen und sind häufig sicherheitskritisch, d.h. jegliche Fehler im funktionalen oder zeitlichen Verhalten können Menschenleben gefährden. Nicht zuletzt deshalb muss die Software eines komplexen mechatronischen Systems hohen Qualitätsstandards genügen. Die besondere Kritikalität dieser Systeme bedingt, dass eine Rekonfiguration der Softwarearchitektur nicht zu einem undefinierten bzw. gefährdenden Verhalten oder einer Verletzung der Echtzeitanforderungen führt. Durch die Anwendung testbasierter Verfahren alleine kann die Korrektheit und damit auch die Sicherheit des mechatronischen Systems nicht garantiert werden. Existierende Ansätze für eine modellgetriebene Entwicklung und Analyse mechatronischer Systeme ermöglichen entweder die Analyse von Echtzeitanforderungen oder die Analyse von Rekonfigurationen der Softwarearchitektur zur Laufzeit. Bisher existiert jedoch kein Ansatz der beides unterstützt.

Im Rahmen dieser Arbeit wird eine Kombination aus konstruktiven und analytischen Verfahren vorgestellt. Sie kann von Softwareentwicklern im Rahmen einer modellgetriebenen Softwareentwicklungsmethode eingesetzt werden, um die Korrektheit der Software eines selbstadaptiven mechatronischen Systems zu verifizieren. Die Neuartigkeit des vorgestellten Konzepts liegt in der gezielten Kombination formaler Verifikationsverfahren mit simulationsbasierten Testverfahren mit dem Ziel, einen skalierbaren Ansatz für die Analyse der Software eines mechatronischen Systems zu erhalten. Als Grundlage für diesen Ansatz wird ein Komponentenmodell vorgestellt, das explizit zwischen ereignisdiskreten Softwarekomponenten und zeitkontinuierlichen Reglern unterscheidet. Es erlaubt die formale Verifikation der Softwarekomponenten mit einem kompositionalen Model Checking Verfahren, das um eine Verfeinerungsüberprüfung für nachrichtenbasierte Kommunikationsprotokolle erweitert wurde. Die fehlerfreie Integration von Softwarekomponenten und Reglern wird anschließend mit einem Testverfahren unter Verwendung von Model-in-the-Loop Simulationen überprüft. Ergänzend wird ein Konzept für die Spezifikation und Verifikation von Rekonfigurationen vorgestellt. Dieser Ansatz trennt explizit die Spezifikation und Analyse des funktionalen Verhaltens vom Rekonfigurationsverhalten, um die Skalierbarkeit der Verifikation zu verbessern.

Alle Beiträge dieser Arbeit wurden auf Basis des RailCab Systems evaluiert. Dazu wurde eine komponentenbasierte Softwarearchitektur für das RailCab inklusive der notwendigen Rekonfigurationen entwickelt. Weiterhin wurden zwei Fallstudien durchgeführt, die die praktische Anwendbarkeit der vorgestellten Verfahren aufzeigen.

## Acknowledgements

Writing this PhD thesis has been an intense experience. Throughout all the time that I spend for researching and writing, I was surrounded by many people that supported me in various ways. Without these people, this work would not have been possible.

First of all, I want to thank my supervisor Prof. Dr. Wilhelm Schäfer for giving me the opportunity to work in the inspiring environment of his research group and for the scientific guidance along the way. I thank Prof. Dr. Betty H.C. Cheng and Prof. Dr. Steffen Becker for writing their reports and Prof. Dr. Falko Dressler, Dr. Matthias Meyer, Prof. Dr. Ansgar Trächtler for attending my exam.

I thank Prof. Dr. Steffen Becker for the many inspiring discussions and a lot of valuable advice. This thesis would not be the same without you. Further more, I would like to thank all of my (former) colleagues at the software engineering group and the Fraunhofer project group mechatronic systems design for the scientific discussions, but also for the enjoyable social activities that made my time at Paderborn a very pleasant and valuable experience. These colleagues are Anas Anis, Christian Brenner, Christopher Brink, Nicola Danielzik, Tobias Eckardt, Markus Fockel, Jens Frieben, Christopher Gerking, Faezeh Ghassemi, Dr. Joel Greenyer, Dr. Stefan Henkler, Jörg Holtmann, Thorsten Koch, Sebastian Lehrig, Renate Löffler, Ahmet Mehic, Sven Merschjohann, Dr. Jan Meyer, Faruk Pasic, Marie Christin Platenius, Uwe Pohlmann, Dr. Jan Rieke, David Schmelter, Christian Stritzke, Julian Suck, Oliver Sudmann, Dr. Matthias Tichy, Dietrich Travkin, Dr. Markus von Detten, Benedict Wohlers, Jinying Yu.

Special thanks go to three of my colleagues. First, to Matthias Becker for being a very valuable office mate and for the many, not always scientific discussions. Second, to Dr. Claudia Priesterjahn for the excellent cooperation in many scientific topics and a lot of valuable advice along the way. Finally, to Stefan Dziwok for the many discussions and the excellent cooperation in the development of MECHATRONICUML and the MECHATRONICUML Tool Suite.

In addition I thank all of the people with whom I collaborated in the SFB 614, in the RailCab project, and in the E-Mobil project for providing me with the opportunity to work in a very interesting, interdisciplinary environment. I highly appreciate our discussions and the excellent interdisciplinary collaboration.

Special thanks go to Jutta Haupt and Jürgen Maniera of the software engineering group, Daniela Peine, Meike Steffen, and Andreas Knoke of the Fraunhofer project group as well as Astrid Canisius and Eckhard Steffen of the International Graduate School "Dynamic Intelligent Systems" for their excellent administrative and technical support. You always knew what to do.

Moreover, this work would not have been possible without the students that contributed to the ideas and their implementation as part of their Bachelor's and Master's theses as well as their jobs as student workers. In particular, I would like to thank David Schubert and Andreas Volk who have been my student workers for several years. It was always fun working with you.

I thank Matthias Becker, Stefan Dziwok, Marie Christin Platenius, Claudia Priesterjahn, and Aindrila Basak for their proof-reading.

Finally, I would like to thank my family and friends for always being there. Especially, I thank my parents for always supporting me and for giving me the opportunity of starting a scientific career. Foremost, I thank my beloved life companion Nicola Buth for her extraordinary support, for cheering up my bad moods when necessary, and for enduring all the time that I was "away" writing this thesis.

# Contents

| 1 | Introduction 1 |                                |                                                          |    |  |  |  |  |

|---|----------------|--------------------------------|----------------------------------------------------------|----|--|--|--|--|

|   | 1.1            | The Ra                         | ailCab System                                            | 2  |  |  |  |  |

|   | 1.2            | Proble                         | m Statement                                              | 3  |  |  |  |  |

|   | 1.3            | Contri                         | bution                                                   | 7  |  |  |  |  |

|   | 1.4            | Overvi                         | iew                                                      | 9  |  |  |  |  |

| 2 | Fou            | ndatio                         | ns                                                       | 11 |  |  |  |  |

|   | 2.1            | Self-A                         | daptive Mechatronic Systems                              | 11 |  |  |  |  |

|   |                | 2.1.1                          | Structuring                                              | 11 |  |  |  |  |

|   |                | 2.1.2                          | Operator-Controller-Module                               | 12 |  |  |  |  |

|   |                | 2.1.3                          | Models@Runtime                                           | 14 |  |  |  |  |

|   | 2.2            | Timed                          | Model Checking                                           | 14 |  |  |  |  |

|   |                | 2.2.1                          | Timed Automata                                           | 15 |  |  |  |  |

|   |                | 2.2.2                          | Timed Computation Tree Logic                             | 18 |  |  |  |  |

|   |                | 2.2.3                          | Model Checking Procedure                                 | 19 |  |  |  |  |

|   | 2.3            | Graph                          | -Based Specifications                                    | 19 |  |  |  |  |

|   |                | 2.3.1                          | Typed Attributed Graph Transformations Systems           | 20 |  |  |  |  |

|   |                | 2.3.2                          | Story Driven Modeling                                    | 22 |  |  |  |  |

|   | 2.4            | Mecha                          | tronicUML                                                |    |  |  |  |  |

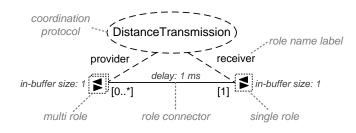

|   |                | 2.4.1                          | Real-Time Coordination Protocols                         | 26 |  |  |  |  |

|   |                | 2.4.2                          | Real-Time Statecharts                                    | 27 |  |  |  |  |

|   |                | 2.4.3                          | Assumptions on Quality-of-Service Characteristics        | 31 |  |  |  |  |

| 3 | Mec            | hatronicUML Component Model 33 |                                                          |    |  |  |  |  |

|   | 3.1            | Model                          | ing Components                                           | 34 |  |  |  |  |

|   |                | 3.1.1                          | Ports                                                    | 35 |  |  |  |  |

|   |                | 3.1.2                          | Atomic Components                                        | 38 |  |  |  |  |

|   |                | 3.1.3                          | Structured Components                                    | 41 |  |  |  |  |

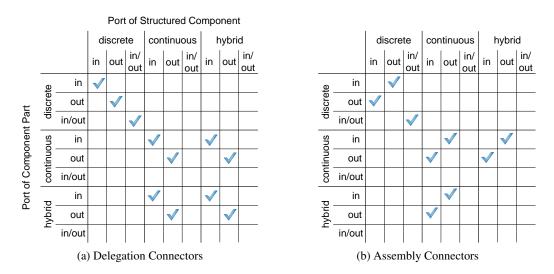

|   |                | 3.1.4                          | Connectors                                               | 45 |  |  |  |  |

|   |                | 3.1.5                          | Component Properties                                     | 46 |  |  |  |  |

|   | 3.2            |                                |                                                          |    |  |  |  |  |

|   | 3.3            | Model                          | ing Reconfiguration                                      | 49 |  |  |  |  |

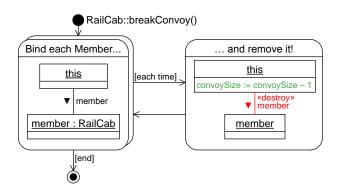

|   |                | 3.3.1                          | Component Story Diagrams                                 | 50 |  |  |  |  |

|   |                | 3.3.2                          | Controller Exchange Nodes                                |    |  |  |  |  |

|   |                | 3.3.3                          | Constraints for Multi Port Variables                     | 52 |  |  |  |  |

|   |                | 3.3.4                          | Reconfiguration of Atomic Components                     | 55 |  |  |  |  |

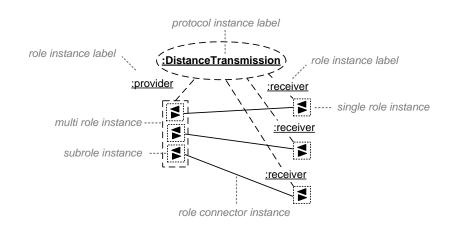

|   | 3.4            | Instant                        | tiating Real-Time Coordination Protocols on System Level |    |  |  |  |  |

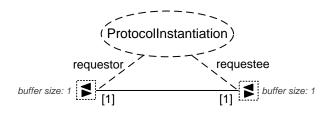

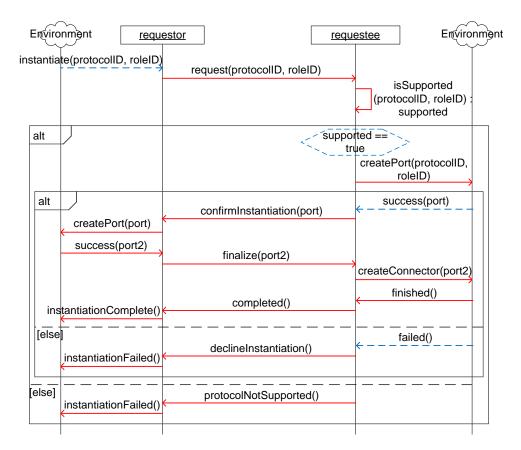

|   |                | 3.4.1                          | Instantiating the RTCP ProtocolInstantiation             |    |  |  |  |  |

|   |                |                                | -                                                        |    |  |  |  |  |

|   |      | 3.4.2 The RTCP ProtocolInstantiation                                     | 58  |  |  |  |

|---|------|--------------------------------------------------------------------------|-----|--|--|--|

|   | 3.5  |                                                                          |     |  |  |  |

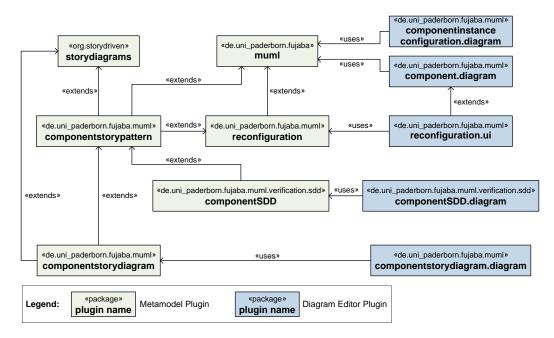

|   | 3.6  | Implementation                                                           |     |  |  |  |

|   | 3.7  | .7 Related Work                                                          |     |  |  |  |

|   |      | 3.7.1 Software Component Models                                          | 66  |  |  |  |

|   |      | 3.7.2 ADLs for Self-Adaptive Systems                                     | 68  |  |  |  |

|   |      | 3.7.3 Constraint Languages                                               | 68  |  |  |  |

|   | 3.8  | Summary                                                                  | 70  |  |  |  |

| 4 | Trar | nsactional Execution of Hierarchical Reconfigurations                    | 71  |  |  |  |

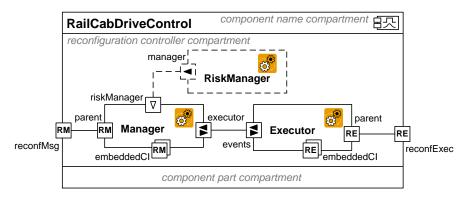

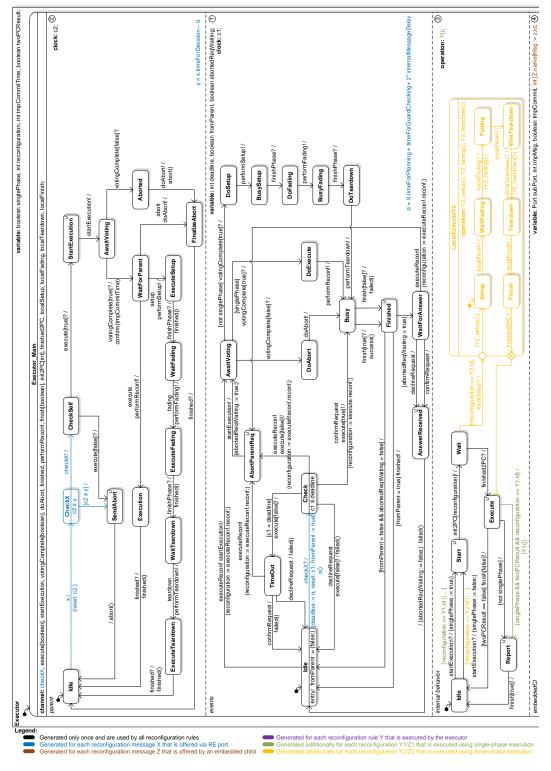

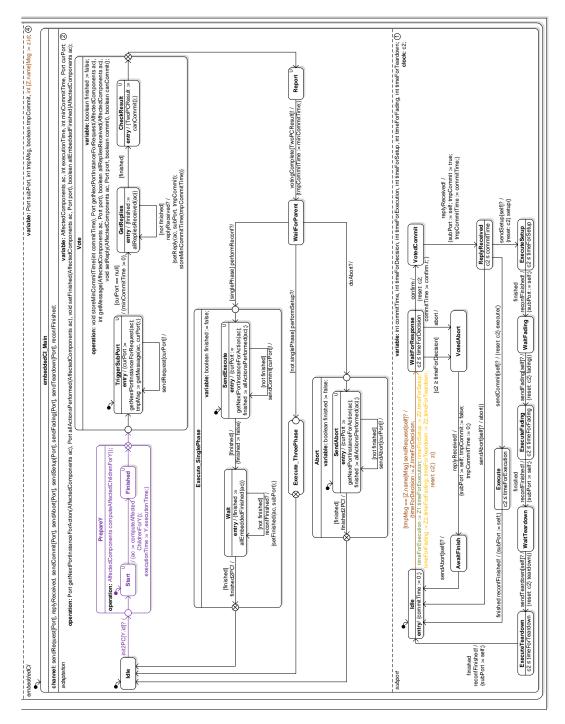

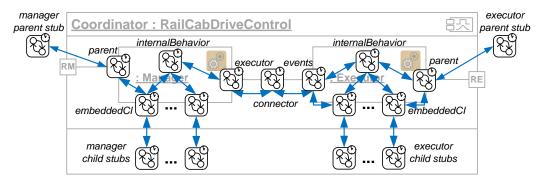

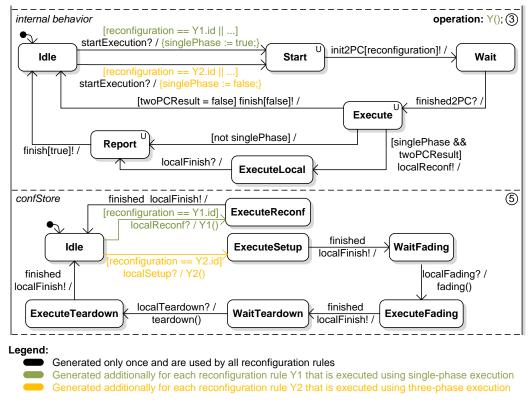

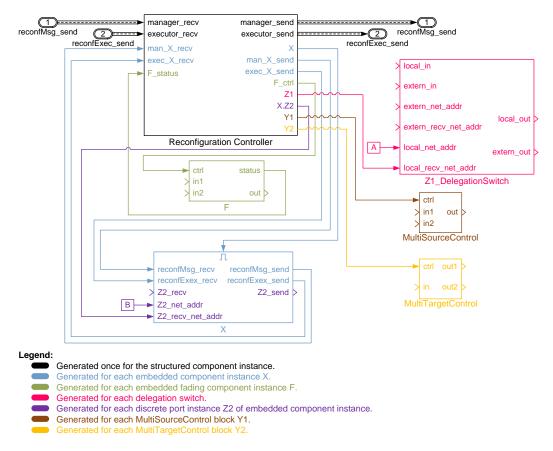

|   | 4.1  | MechatronicUML Reconfiguration Controller                                | 73  |  |  |  |

|   | 4.2  | Executing Reconfigurations                                               | 75  |  |  |  |

|   |      | 4.2.1 Single-Phase Execution                                             | 76  |  |  |  |

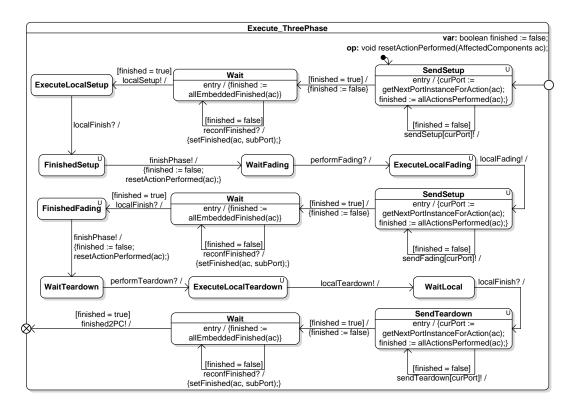

|   |      | 4.2.2 Three-Phase Execution                                              | 77  |  |  |  |

|   |      | 4.2.3 Quiescence                                                         | 81  |  |  |  |

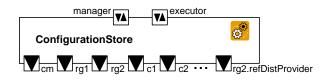

|   | 4.3  | Declarative, Table-based Specification of the Reconfiguration Controller | 84  |  |  |  |

|   |      | 4.3.1 Interface Specification of RM Ports                                | 85  |  |  |  |

|   |      | 4.3.2 Manager Specification                                              | 85  |  |  |  |

|   |      | 4.3.3 Executor Specification                                             | 87  |  |  |  |

|   |      | 4.3.4 Interface Specification of RE Ports                                | 88  |  |  |  |

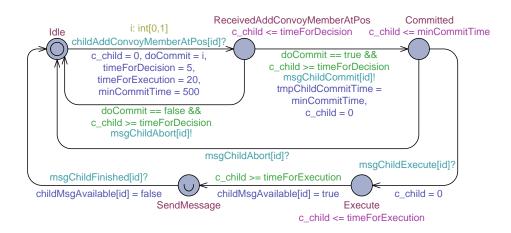

|   | 4.4  | Generating Operational Behavior Specifications                           | 89  |  |  |  |

|   |      | 4.4.1 Manager Specification                                              | 89  |  |  |  |

|   |      | 4.4.2 Executor Specification                                             | 93  |  |  |  |

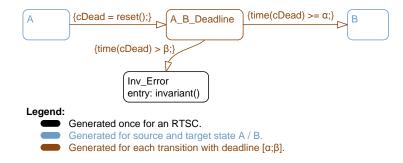

|   | 4.5  | Verifying the Reconfiguration Specification                              | 99  |  |  |  |

|   |      | 4.5.1 Consistency                                                        | 101 |  |  |  |

|   |      | 4.5.2 Timing                                                             | 102 |  |  |  |

|   | 4.6  | Implementation                                                           |     |  |  |  |

|   | 4.7  | -                                                                        |     |  |  |  |

|   | 4.8  |                                                                          |     |  |  |  |

|   |      | 4.8.1 Approaches Supporting Reconfiguration of Hierarchical Componen     |     |  |  |  |

|   |      | 4.8.2 Quiescence of Components                                           | 109 |  |  |  |

|   | 4.9  | Summary                                                                  | 110 |  |  |  |

| 5 | Veri | ifying Refinements based on Test Automata                                | 111 |  |  |  |

|   | 5.1  | Refining Real-Time Coordination Protocols to Port Implementations        | 114 |  |  |  |

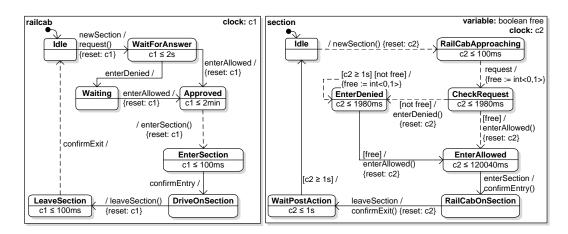

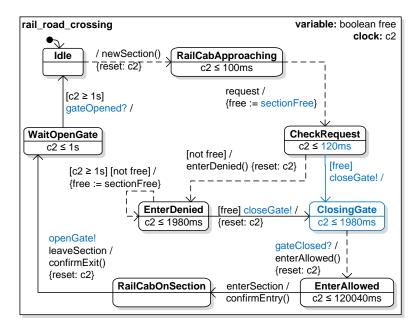

|   |      | 5.1.1 Real-Time Coordination Protocol EnterSection                       | 114 |  |  |  |

|   |      | 5.1.2 Refined Port Real-Time Statecharts                                 | 115 |  |  |  |

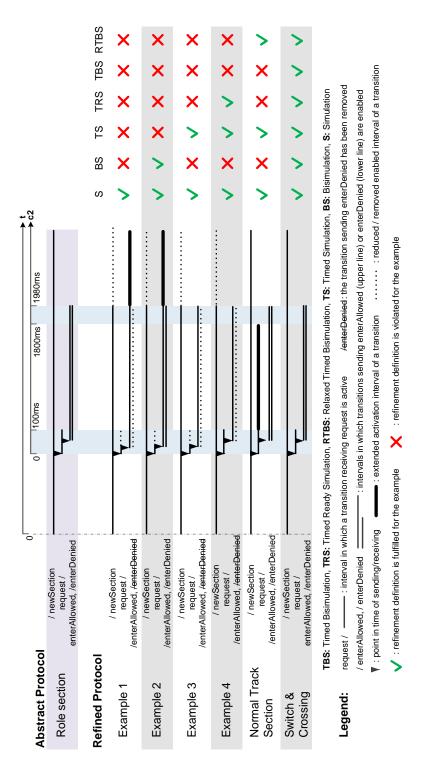

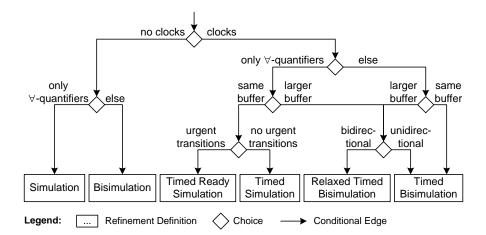

|   | 5.2  | Considered Refinement Definitions                                        | 118 |  |  |  |

|   | 5.3  | Test automata-based Refinement Checking                                  | 123 |  |  |  |

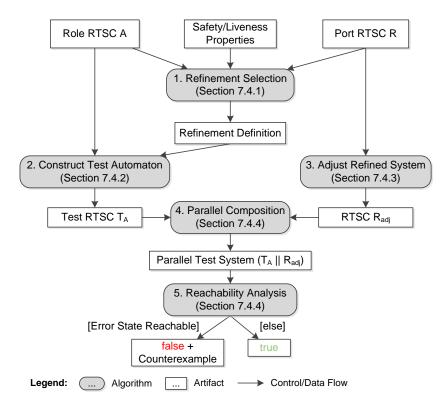

|   |      | 5.3.1 Refinement Selection                                               | 124 |  |  |  |

|   |      | 5.3.2 Construction of the Test Automaton                                 | 125 |  |  |  |

|   |      | 5.3.3 Adjusting the Port Real-Time Statechart                            | 131 |  |  |  |

|   |      | 5.3.4 Parallel Composition and Reachability Analysis                     | 132 |  |  |  |

|   | 5.4  | Implementation                                                           | 132 |  |  |  |

|   | 5.5  | Assumptions and Limitations                                              | 134 |  |  |  |

|   | 5.6                | Case S      | tudy                                                               | 134   |  |  |

|---|--------------------|-------------|--------------------------------------------------------------------|-------|--|--|

|   |                    | 5.6.1       | Case Study Context                                                 | 134   |  |  |

|   |                    | 5.6.2       | Setting the Hypothesis                                             | 134   |  |  |

|   |                    | 5.6.3       | Preparing the Input Models                                         |       |  |  |

|   |                    | 5.6.4       | Validating the Hypothesis                                          |       |  |  |

|   |                    | 5.6.5       | Analyzing the Results                                              | 137   |  |  |

|   | 5.7                | Related     | d Work                                                             |       |  |  |

|   |                    | 5.7.1       | Refinement Checking                                                |       |  |  |

|   |                    | 5.7.2       | Test automata-based Verification                                   |       |  |  |

|   | 5.8                | Summa       | ary                                                                |       |  |  |

| 6 | Cim                | ulating     | Colf Adaptiva Maghatrania Suatama in MATLAD/Simulink               | - 1 - |  |  |

| 6 | <b>5</b> im<br>6.1 | -           | Self-Adaptive Mechatronic Systems in MATLAB/Simulink               | 141   |  |  |

|   | 0.1                |             |                                                                    |       |  |  |

|   |                    | 6.1.1       | Simulink                                                           |       |  |  |

|   | $(\mathbf{a})$     | 6.1.2       | Stateflow                                                          |       |  |  |

|   | 6.2                |             | imulation of MechatronicUML Models in Simulink and Stateflow       |       |  |  |

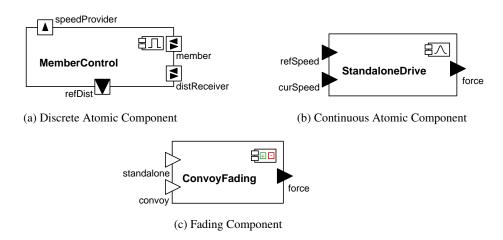

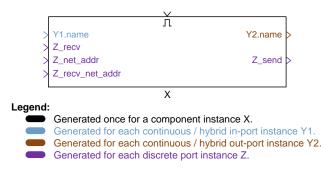

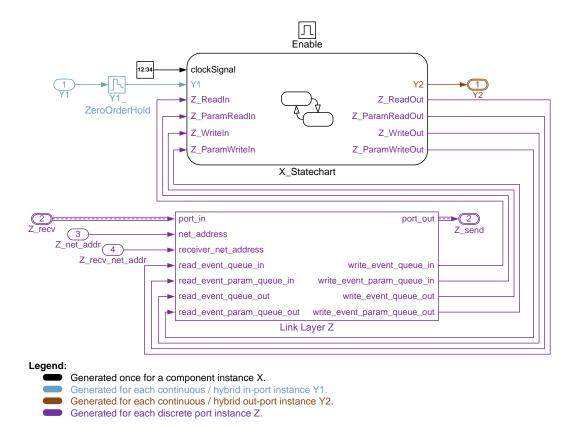

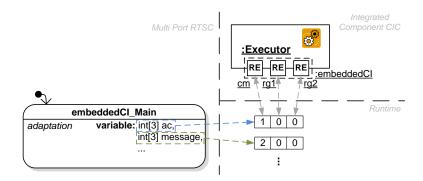

|   | 6.3                |             | ating Component Instance Configurations to Simulink Block Diagrams |       |  |  |

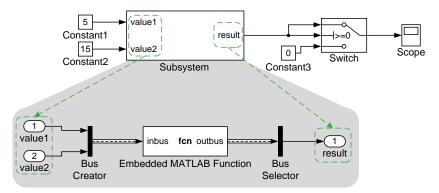

|   |                    | 6.3.1       | Translating Atomic Component Instances                             |       |  |  |

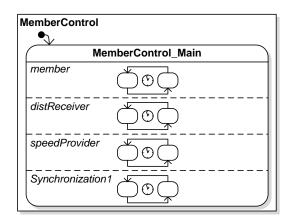

|   |                    | 6.3.2       | Translating Structured Component Instances                         |       |  |  |

|   |                    | 6.3.3       | Using Message-Based Communication                                  |       |  |  |

|   | <i>.</i> .         | 6.3.4       | Considering QoS Assumptions                                        |       |  |  |

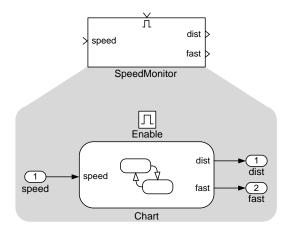

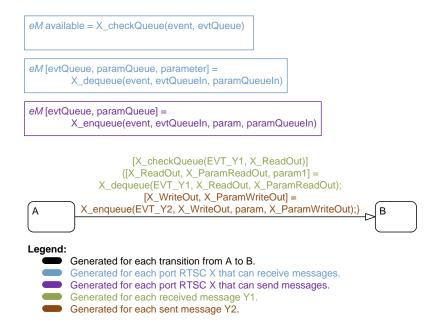

|   | 6.4                |             | ating Real-Time Statecharts to Stateflow Charts                    |       |  |  |

|   |                    | 6.4.1       | Basic Transformation Concepts                                      |       |  |  |

|   |                    | 6.4.2       | Message-Based Communication                                        |       |  |  |

|   |                    | 6.4.3       | Clock Concept                                                      |       |  |  |

|   |                    | 6.4.4       | Urgency                                                            |       |  |  |

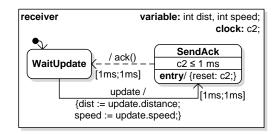

|   |                    | 6.4.5       | Real-Time Statecharts of Multi Port Instances                      |       |  |  |

|   |                    | 6.4.6       | Synchronizations                                                   |       |  |  |

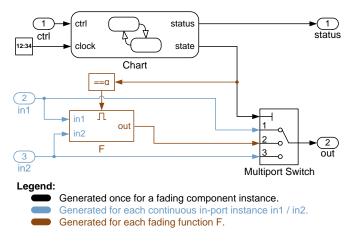

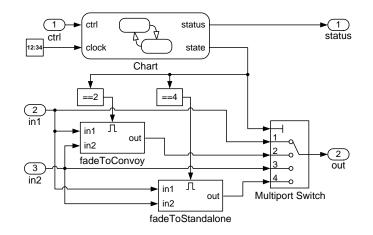

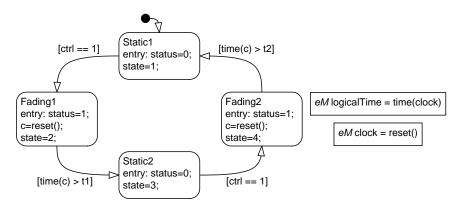

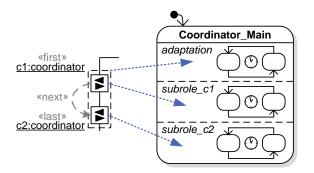

|   | 6.5                |             | ating Reconfiguration Specifications to Simulink and Stateflow     |       |  |  |

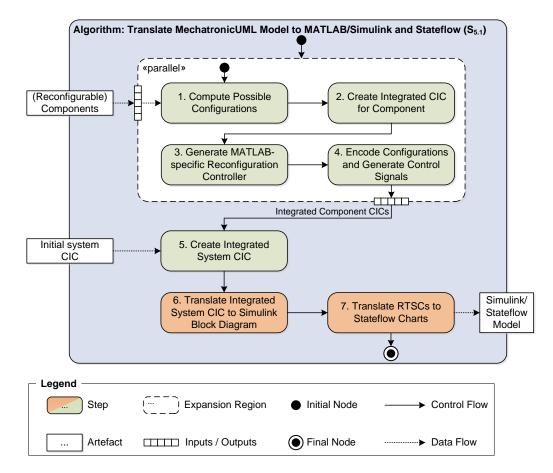

|   |                    | 6.5.1       | Step 1: Compute Possible Configurations                            |       |  |  |

|   |                    | 6.5.2       | Step 2: Create Integrated CIC for Component                        |       |  |  |

|   |                    | 6.5.3       | Step 3: Generate the MATLAB-specific Reconfiguration Controller .  |       |  |  |

|   |                    | 6.5.4       | Step 4: Encode Configurations and Generate Control Signals         |       |  |  |

|   |                    | 6.5.5       | Step 5: Create Integrated System CIC                               | 180   |  |  |

|   |                    | 6.5.6       | Integrate MATLAB-specific reconfiguration controller into the Si-  |       |  |  |

|   |                    |             | mulink Block Diagram                                               |       |  |  |

|   |                    | 6.5.7       | Realizing Port Reconfiguration in Stateflow Charts                 |       |  |  |

|   | 6.6                |             | nentation                                                          |       |  |  |

|   | 6.7                | Limitations |                                                                    |       |  |  |

|   | 6.8                |             | tudy                                                               |       |  |  |

|   |                    | 6.8.1       | Case Study Context                                                 |       |  |  |

|   |                    | 6.8.2       | Setting the Hypothesis                                             |       |  |  |

|   |                    | 6.8.3       | Preparing the Input Models                                         |       |  |  |

|   |                    | 6.8.4       | Validating the Hypothesis                                          |       |  |  |

|   |                    | 6.8.5       | Analyzing the Results                                              | 188   |  |  |

|               | 6.9  | Related | Related Work                                     |  |  |  |  |

|---------------|------|---------|--------------------------------------------------|--|--|--|--|

|               |      | 6.9.1   | Reconfiguration in MATLAB/Simulink               |  |  |  |  |

|               |      | 6.9.2   | Reconfiguration in other Simulation Environments |  |  |  |  |

|               |      | 6.9.3   | Reconfiguration in AUTOSAR 3.x                   |  |  |  |  |

|               |      | 6.9.4   | Hybrid Verification                              |  |  |  |  |

|               | 6.10 | Summ    | ary                                              |  |  |  |  |

| 7 Conclusions |      | clusio  | ns 193                                           |  |  |  |  |

|               | 7.1  | Summ    | ary                                              |  |  |  |  |

|               | 7.2  | Future  | Work                                             |  |  |  |  |

## Appendix

| Α | Con | nplete  | RailCab Example                                                 | 199   |

|---|-----|---------|-----------------------------------------------------------------|-------|

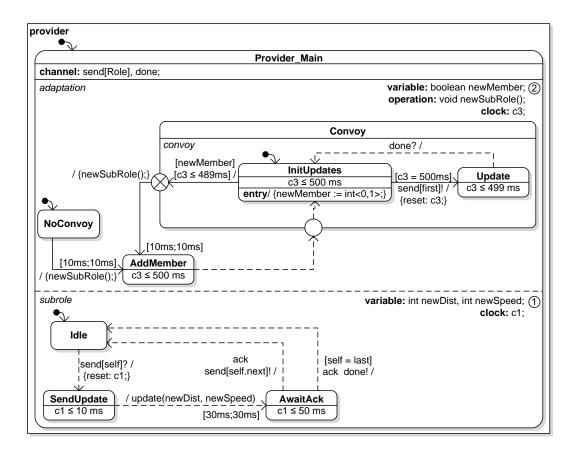

|   | A.1 | RTCPs   | · · · · · · · · · · · · · · · · · · ·                           | . 199 |

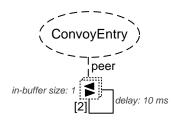

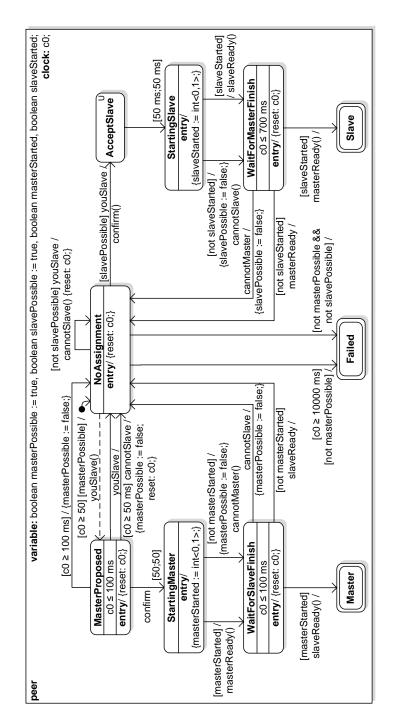

|   |     | A.1.1   | ConvoyEntry                                                     | . 200 |

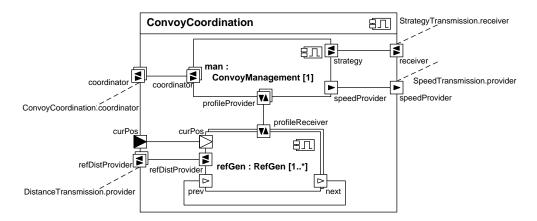

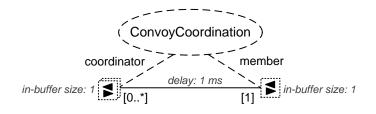

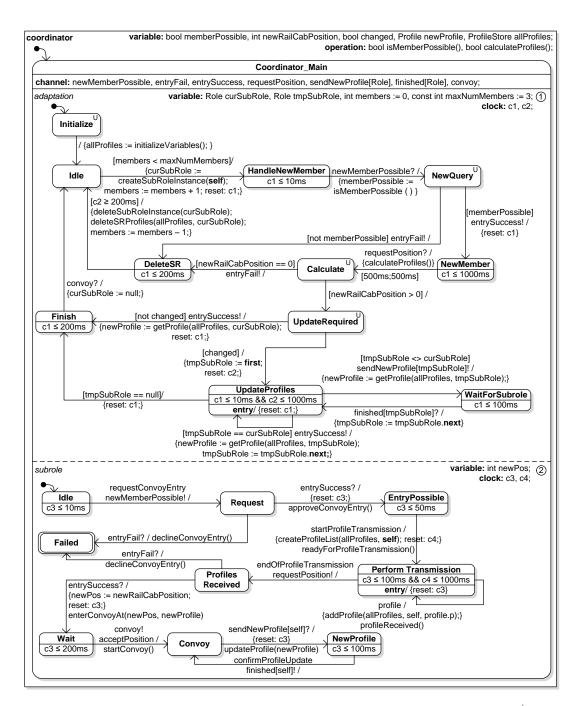

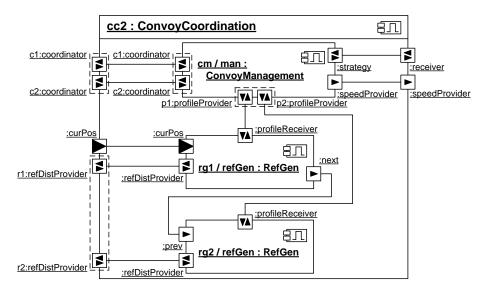

|   |     | A.1.2   | ConvoyCoordination                                              | . 202 |

|   |     | A.1.3   | ProfileDistribution                                             | . 203 |

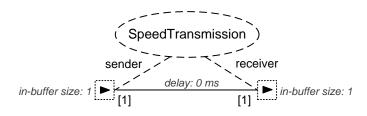

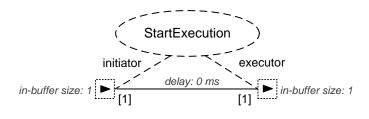

|   |     | A.1.4   | SpeedTransmission                                               | . 207 |

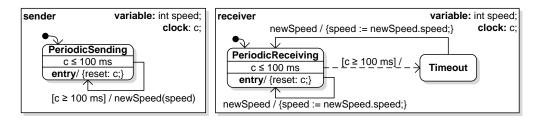

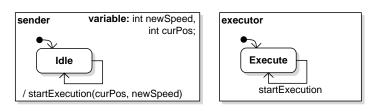

|   |     | A.1.5   | StartExecution                                                  | . 208 |

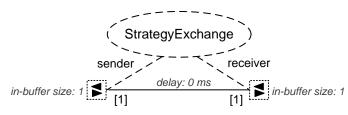

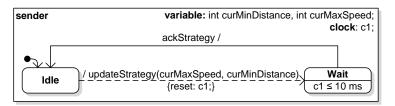

|   |     | A.1.6   | StrategyExchange                                                | . 209 |

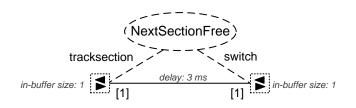

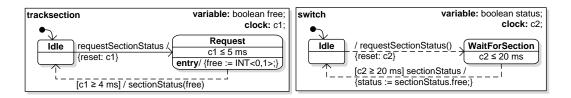

|   |     | A.1.7   | NextSectionFree                                                 | . 210 |

|   | A.2 | Instant | tiating Real-Time Coordination Protocols on System Level        | . 211 |

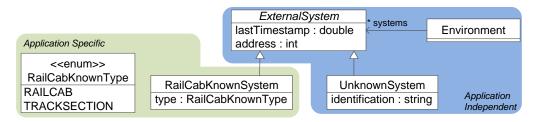

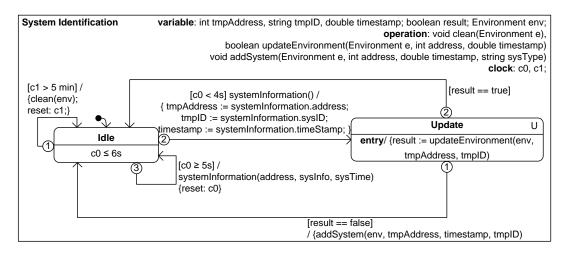

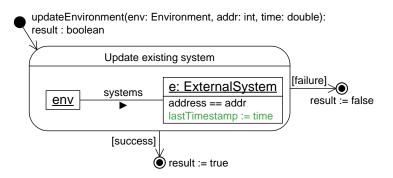

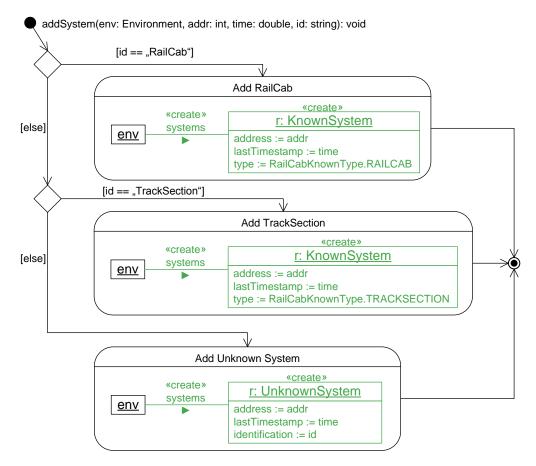

|   |     | A.2.1   | A Simple Discovery Protocol and Environment Model               | . 211 |

|   |     | A.2.2   | Instantiating the RTCP ProtocolInstantiation                    | . 215 |

|   |     | A.2.3   | The RTCP ProtocolInstantiation                                  | . 217 |

|   | A.3 | Compo   | onents                                                          | . 219 |

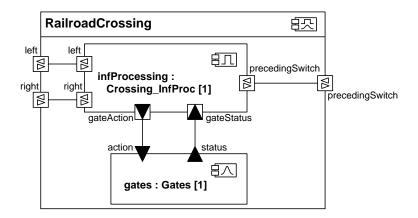

|   |     | A.3.1   | RailroadCrossing                                                | . 219 |

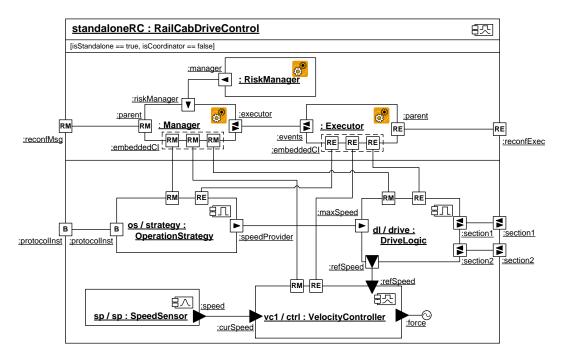

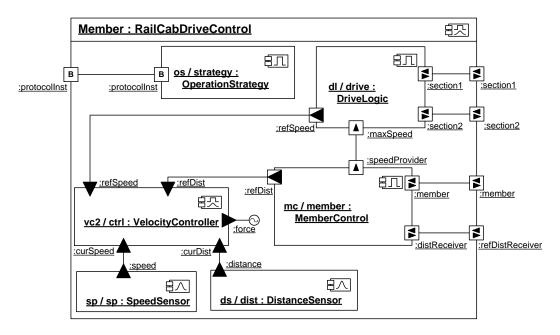

|   | A.4 | Compo   | onent Instances                                                 | . 220 |

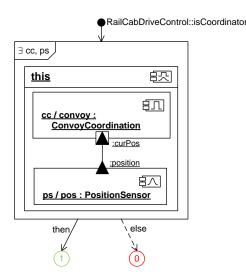

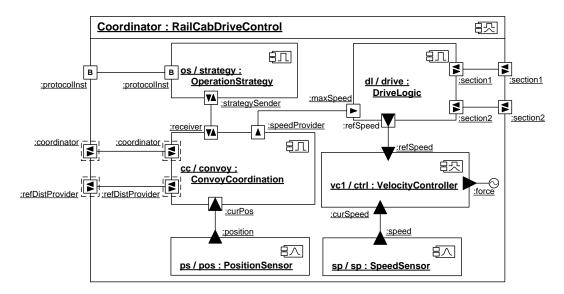

|   |     | A.4.1   | RailCab Driving as a Coordinator                                | . 220 |

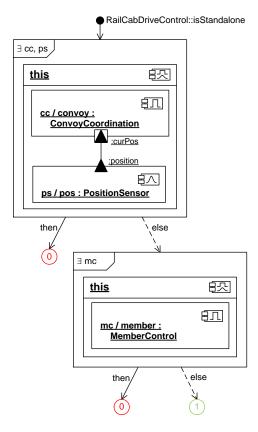

|   |     | A.4.2   | RailCab Driving as a Member                                     | . 222 |

|   | A.5 | Compo   | onent RTSCs                                                     | . 224 |

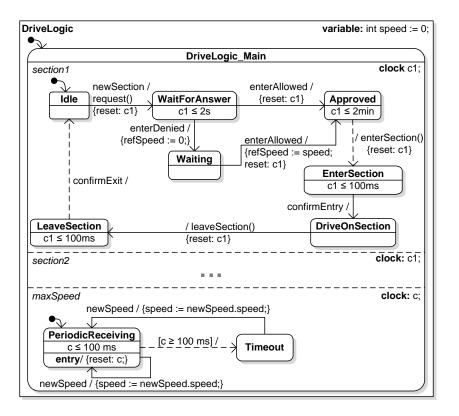

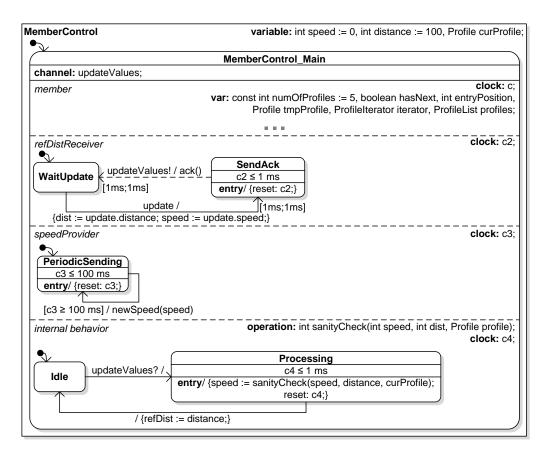

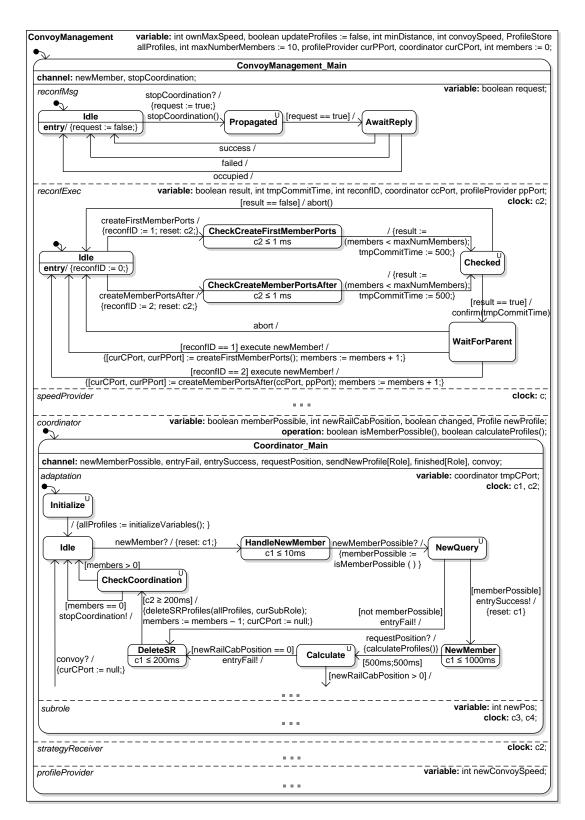

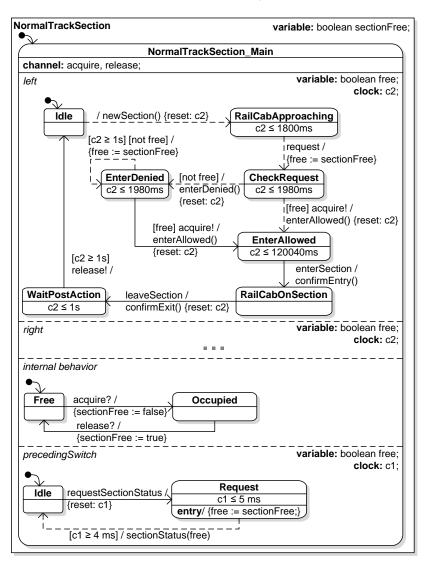

|   |     | A.5.1   | RTSCs of the RailCab Components                                 | . 224 |

|   |     | A.5.2   | RTSCs of the Section Components                                 | . 234 |

|   | A.6 | Recon   | figuration Behavior Specification of Components                 | . 238 |

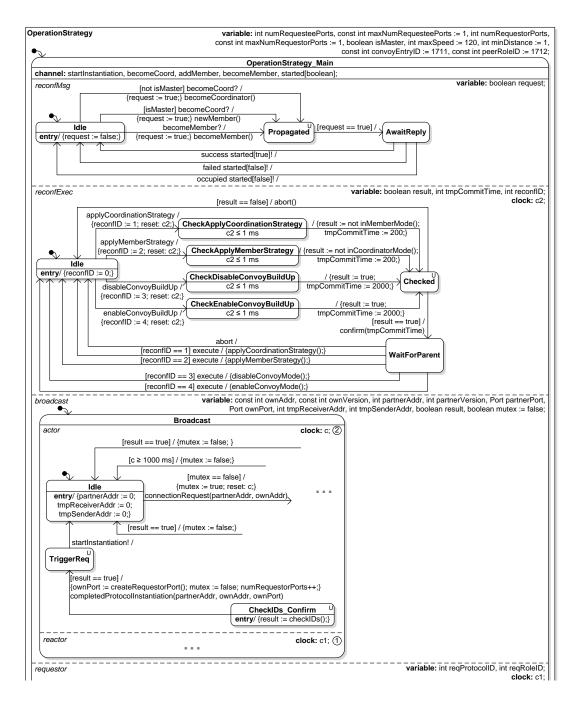

|   |     | A.6.1   | Declarative, Table-based Reconfiguration Specification          | . 238 |

|   |     | A.6.2   | Reconfiguration Rules                                           | . 242 |

|   |     | A.6.3   | Generated RTSCs for Manager and Executor of RailCabDriveControl | 252   |

|   |     | A.6.4   | Specification of the Executor Operations                        | . 258 |

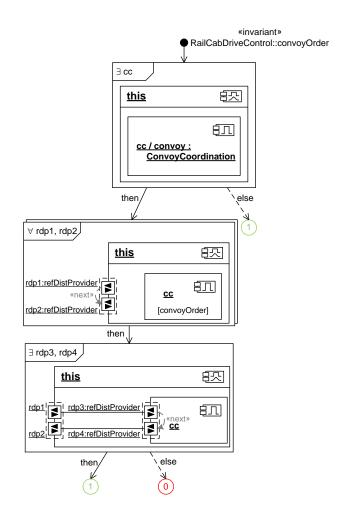

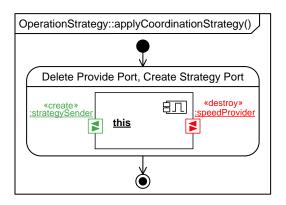

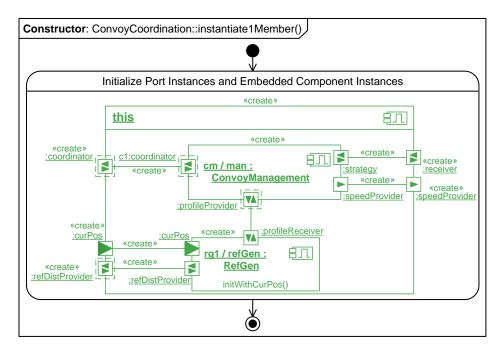

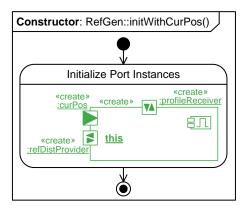

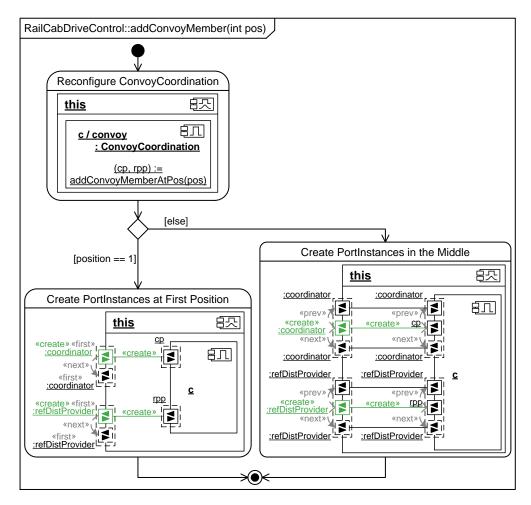

|   | A.7 | Compo   | onent SDDs                                                      | . 266 |

|   |     | A.7.1   | RailCabDriveControl                                             | . 266 |

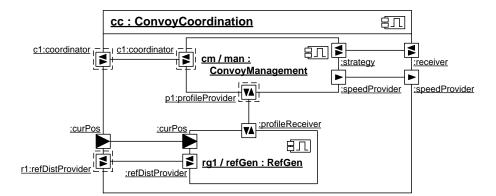

|   |     | A.7.2   | ConvoyCoordination                                              | . 267 |

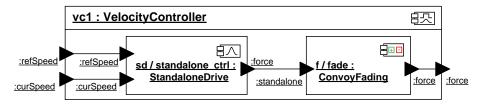

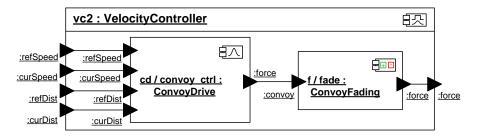

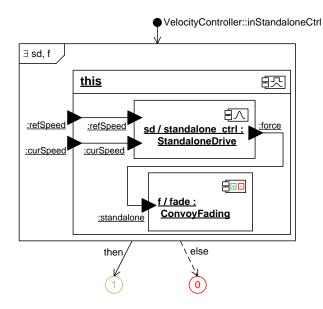

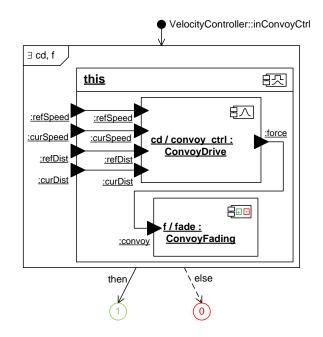

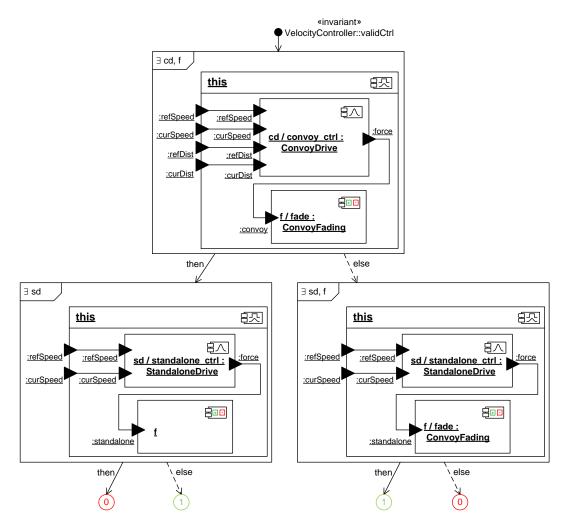

|   |     | A.7.3   | VelocityController                                              |       |

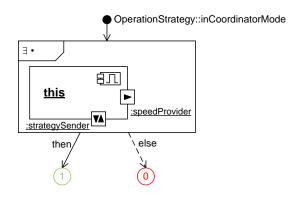

|   |     | A.7.4   | OperationStrategy                                               | . 272 |

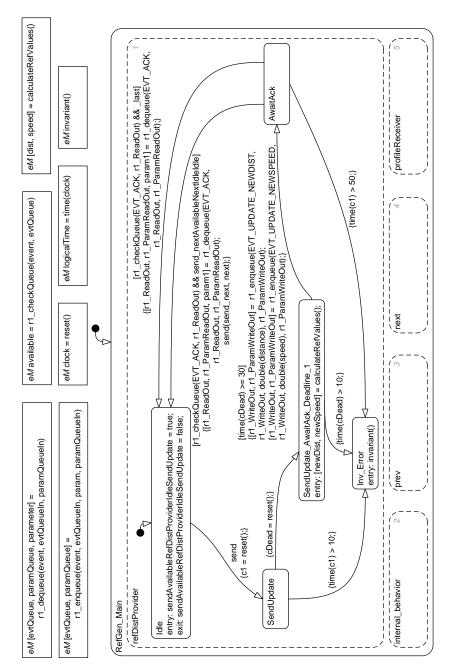

|   |     | A.7.5   | RefGen                                                          | . 272 |

|            | A.8                   | -        | ot of Generated MATLAB/Simulink Model                         |       |  |

|------------|-----------------------|----------|---------------------------------------------------------------|-------|--|

|            |                       | A.8.1    | Simulink Model for Atomic Component Instance of Type RefGen . | . 274 |  |

|            |                       | A.8.2    | Simulink Model for Structured Component Instance of Type Con- |       |  |

|            |                       |          | voyCoordination                                               | . 275 |  |

| В          | For                   | nalizat  | ion of the Real-time Statechart Semantics                     | 283   |  |

| С          | A Fi                  | ramewo   | ork for Reachability Analyses                                 | 289   |  |

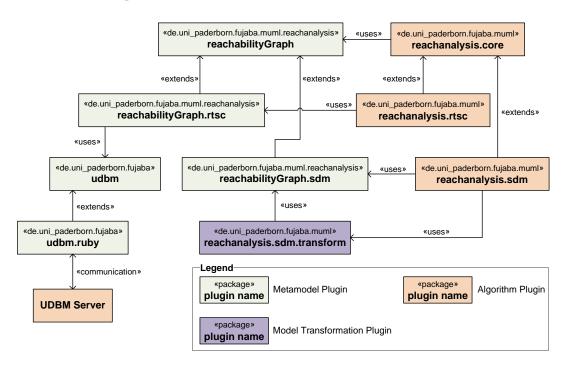

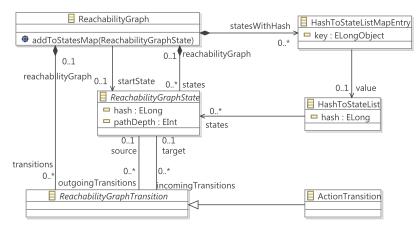

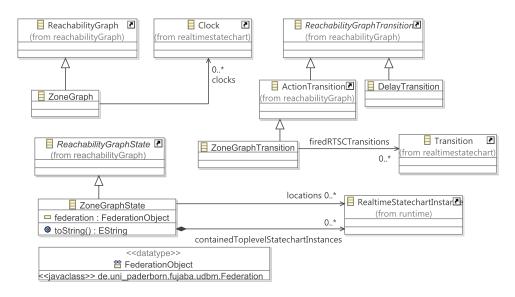

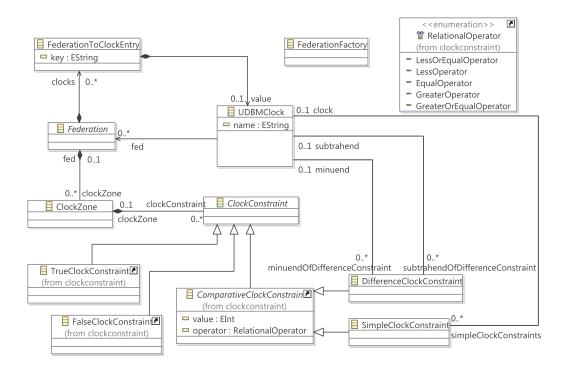

|            | C.1                   |          | ability Analysis Framework                                    | . 290 |  |

|            |                       | C.1.1    | Metamodel                                                     |       |  |

|            |                       | C.1.2    | Reachability Analysis Algorithm                               |       |  |

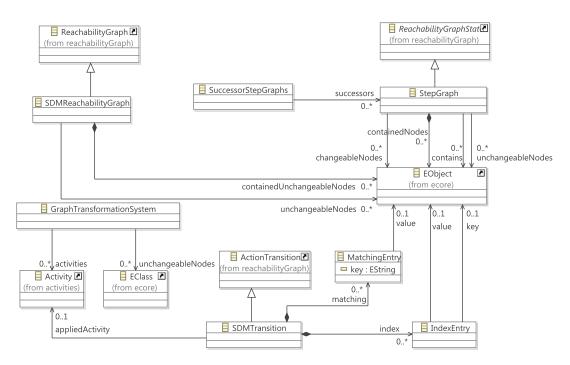

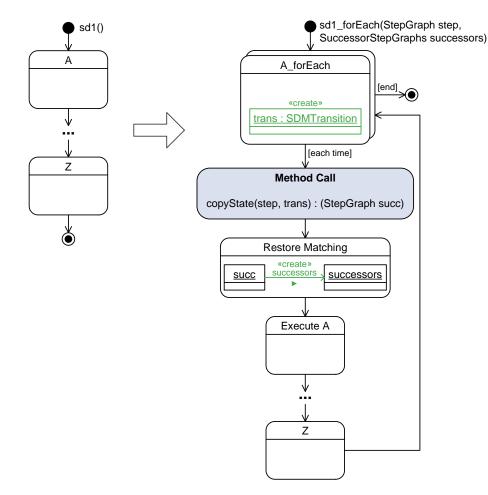

|            | C.2                   | Story I  | Diagram Reachability Analysis                                 |       |  |

|            |                       | C.2.1    | Metamodel Extension                                           |       |  |

|            |                       | C.2.2    | Functions of the Reachability Analysis                        | . 294 |  |

|            | C.3                   | RTSC     | Reachability Analysis                                         |       |  |

|            |                       | C.3.1    | Metamodel Extension                                           |       |  |

|            |                       | C.3.2    | Functions of the Reachability Analysis                        |       |  |

|            | C.4                   | UDBM     | 1 Library                                                     |       |  |

|            |                       |          |                                                               |       |  |

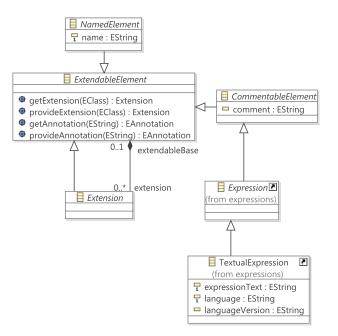

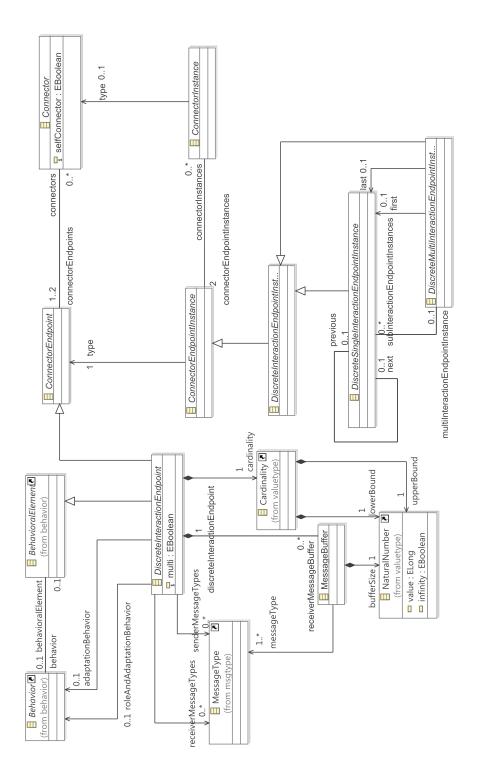

| D          |                       | amode    | -                                                             | 301   |  |

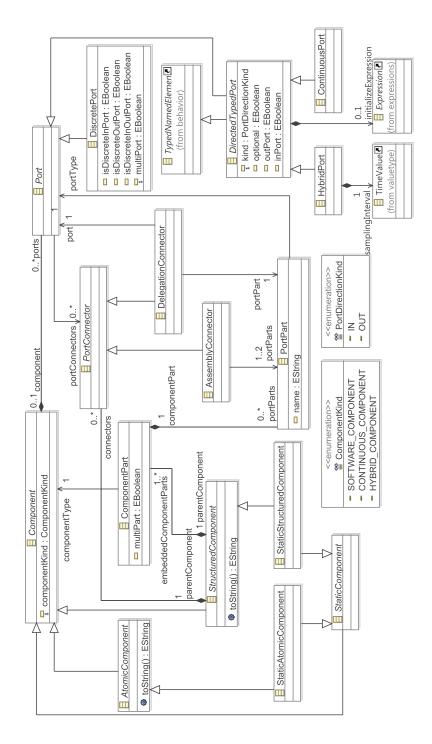

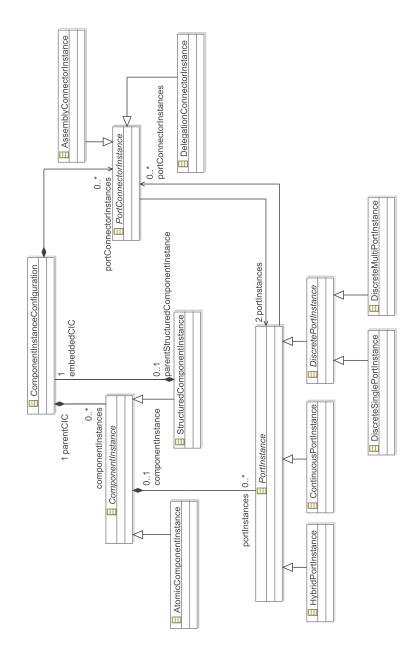

|            | D.1                   |          | tronicUML Component Model                                     |       |  |

|            |                       | D.1.1    | Core                                                          |       |  |

|            |                       | D.1.2    | Components                                                    |       |  |

|            |                       | D.1.3    | Component Instances                                           |       |  |

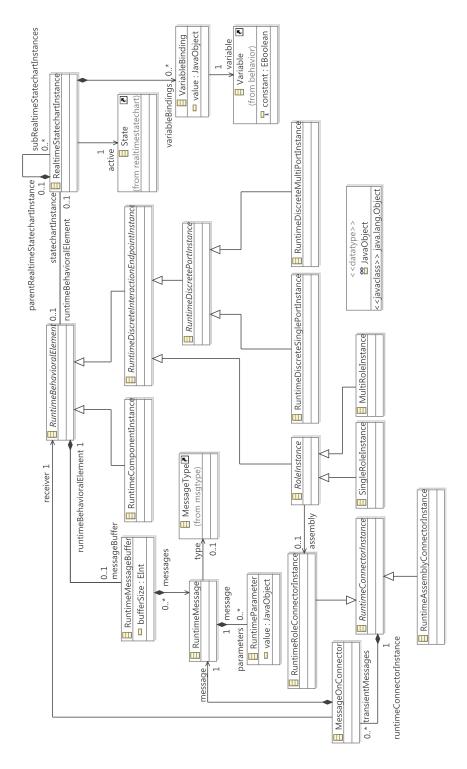

|            |                       | D.1.4    | Runtime Model                                                 |       |  |

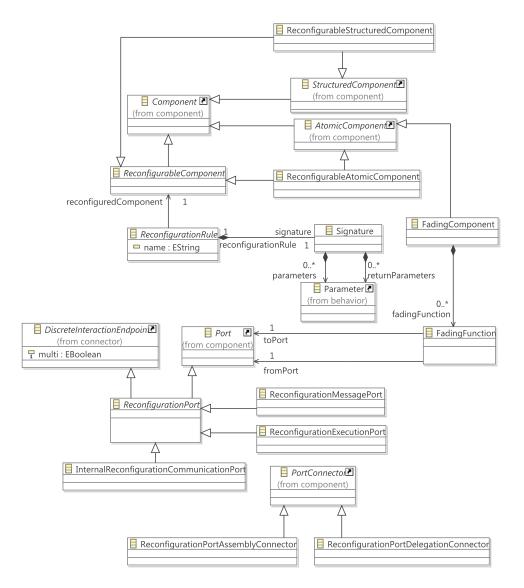

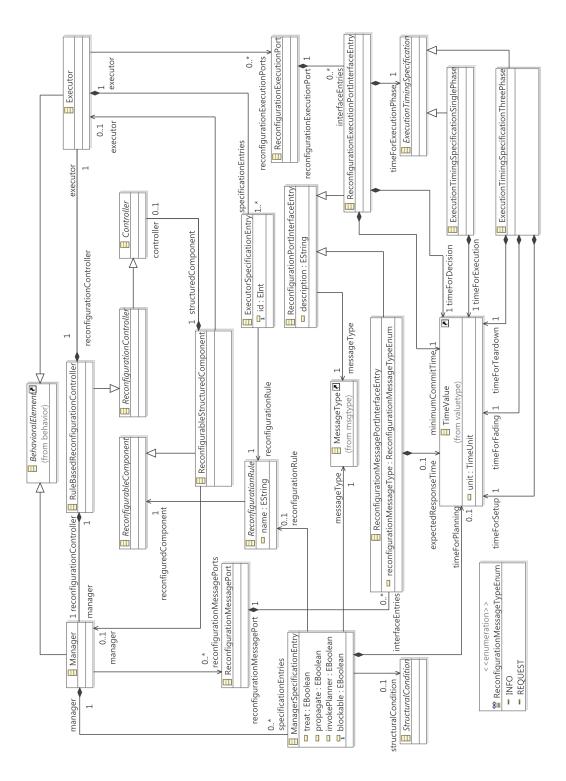

|            | D.2                   |          | tronicUML Reconfiguration                                     |       |  |

|            |                       | D.2.1    | Reconfigurable Components                                     |       |  |

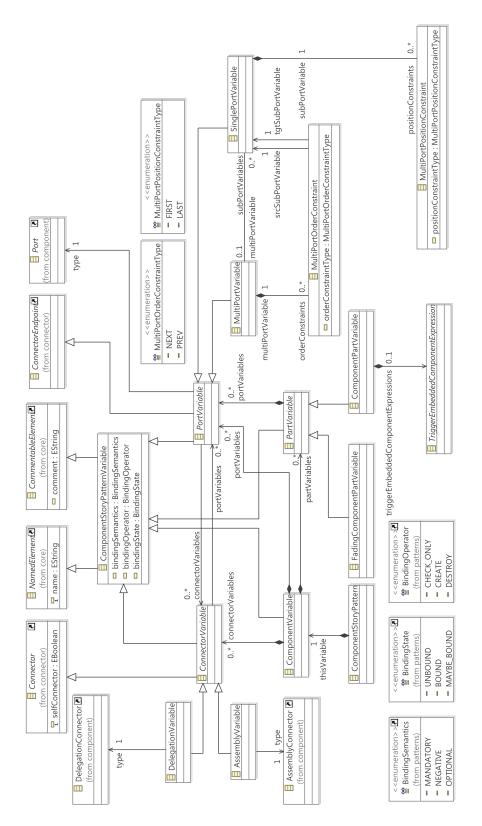

|            |                       | D.2.2    | Component Story Patterns                                      |       |  |

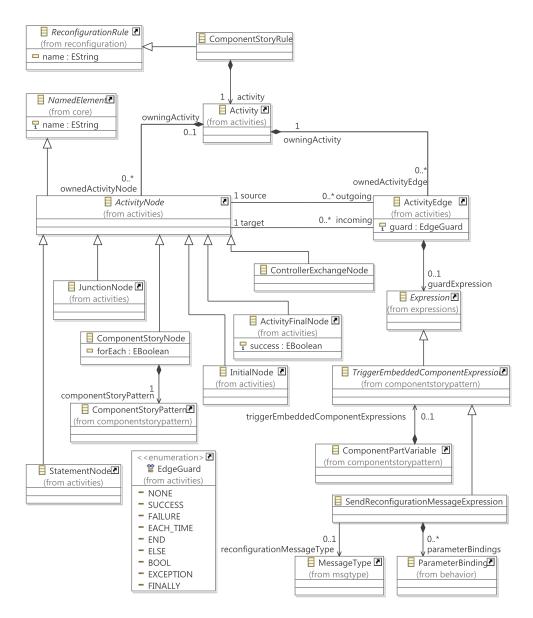

|            |                       | D.2.3    | Component Story Diagrams                                      |       |  |

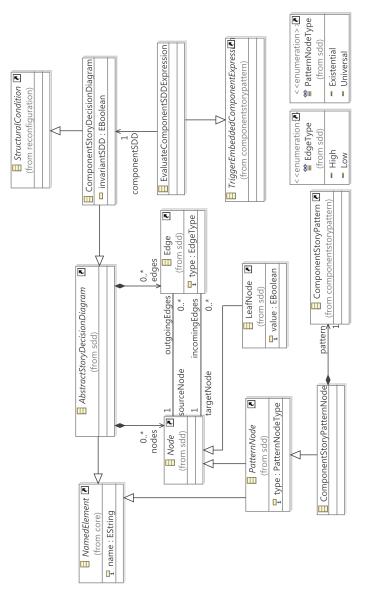

|            |                       | D.2.4    | Component Story Decision Diagrams                             |       |  |

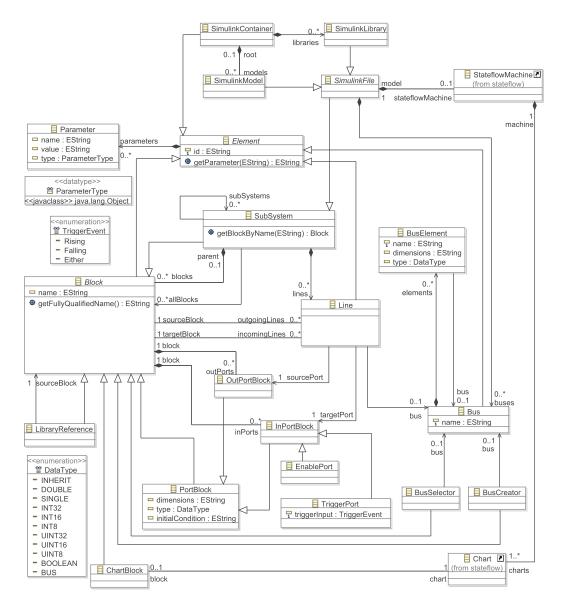

|            | D.3                   |          | AB/Simulink and Stateflow                                     |       |  |

|            |                       | D.3.1    | Simulink                                                      |       |  |

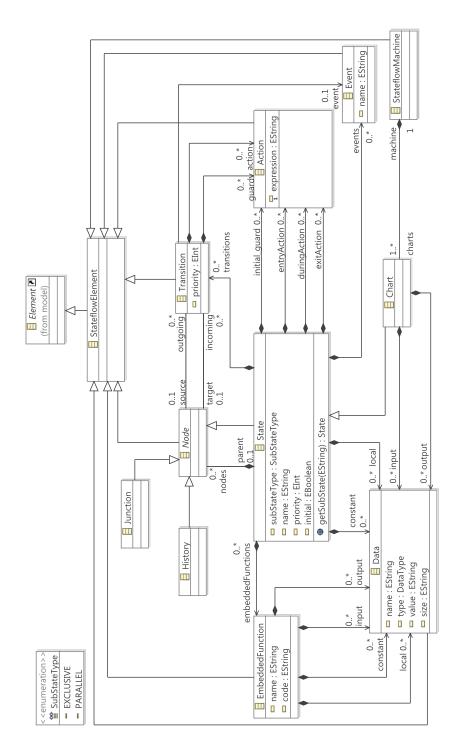

|            |                       | D.3.2    | Stateflow                                                     |       |  |

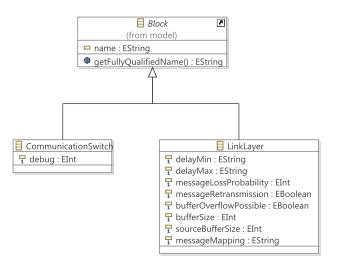

|            |                       | D.3.3    | Message-Based Communication                                   |       |  |

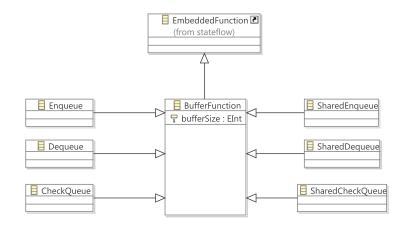

|            |                       | D.3.4    | Reconfiguration                                               | . 322 |  |

| 01         | wn Pi                 | ublicati | ions                                                          | 323   |  |

| Sι         | ıperv                 | ised T   | hesis                                                         | 331   |  |

| Literature |                       |          |                                                               | 333   |  |

| Li         | List of Abbreviations |          |                                                               |       |  |

| Li         | List of Figures 3     |          |                                                               |       |  |

## **1** Introduction

Today's technical systems mostly consist of mechanical, electrical, and software parts. Examples of such systems include modern cars, trains, or airplanes. We call those systems mechatronic systems [VDI04, GKP08]. New functionality in such systems is increasingly realized by embedded software. In particular, embedded software interconnects previously isolated software parts of a system [PBKS07, SW07]. In addition, embedded software enables to build systems of systems where several systems collaborate with each other using application-level communication protocols [WA13]. An example of such systems of systems is given by car platoons. In a car platoon, cars drive closely behind each other for reducing the energy consumption and increasing the throughput on a highway [RCC10, HESV91].

Realizing advanced functionality such as car platooning often requires an adaptation of the software architecture at runtime [CdLG<sup>+</sup>09]. Such adaptation is called structural reconfiguration [OMT98]. As an example, cars need to adapt their software architecture for driving in a platoon. Followers, for example, need to take the distance to the preceding car into account. The leading car needs to manage communication links to a varying number of followers because cars may join or leave the platoon at any time.

Despite the fact that the software architecture and communication links may change during runtime, self-adaptive mechatronic systems need to be safe [ISO10, p. 316]. Especially systems like cars or public transportation systems require high-quality software because any software failure in such a system may put lives at risk. In particular, reconfigurations can put a system into an unsafe state if they are executed incorrectly or only partially.

Ensuring high quality of the software is further complicated by hard real-time constraints that apply to such systems [But05]. That means that the correctness of the software does not only depend on the implemented functionality but also on the correct timing of the executed operations. That holds, in particular, for the interaction of systems by communication protocols. In our example, a braking maneuver of a car platoon requires that the platoon leader notifies all followers to brake at the correct point in time.

A common approach for achieving the necessary quality and mastering the inherent complexity of such software is model-driven development [Sch06, SV06]. When applying modeldriven development, the developers build models of the software instead of implementing it directly. If these models have a defined (formal) semantics, they enable to build the software correct by construction [Cha06], i.e., models may be analyzed in order to find errors already at design time. In particular, such models enable to apply analysis techniques like model checking [BK08] and simulation [ÅEM98] for guaranteeing correctness of the software. However, current approaches for the model-driven development of mechatronic systems provide no or only very limited support for adapting the software architecture of a system at runtime and for reasoning over the adaptation at design time.

Existing standards like UML [Gro11c] or SysML [Gro10] support modeling the software of a mechatronic system, but neither provide support for specifying real-time constraints and runtime reconfiguration nor define a formal semantics enabling to analyze these mod-

els. Formal models like timed automata [AD94, BY04] that are specifically dedicated to the formal analysis of real-time systems also fail with respect to specifying runtime reconfiguration. The same restriction holds for commercial tools like MATLAB/Simulink [Matg] or Dymola/Modelica [Das, Mod09] that are used in industry for developing automotive software [PBKS07, KSHL12]. In contrast, graph-based approaches like graph transformation systems [Roz97] enable the specification of runtime reconfiguration but provide no means for specifying their real-time properties. Component models for real-time systems either provide limited support for self-adaptation behavior or they support formal verification [CSVC11, HPB<sup>+</sup>10]. Architecture description languages for self-adaptive systems [BCDW04] do not consider the real-time properties that apply to mechatronic systems. Hence, none of the approaches provides the necessary modeling and analysis capabilities that are required for self-adaptive mechatronic systems.

The goal of this thesis is to extend a model-driven software engineering method by techniques for guaranteeing the correctness of the software of a self-adaptive mechatronic system. In this thesis, we will use the model-driven software engineering method MECHA-TRONICUML [GTB+03, BDG+14a] as a basis for developing and illustrating our contributions. MECHATRONICUML adapts concepts of the UML [Gro11c] for supporting the model-driven development of self-adaptive mechatronic systems. In particular, it provides a domain-specific modeling language with a formal semantics that enables formal verification of software models. Previous works on MECHATRONICUML contributed, for example, the specification of feedback controller exchange [BGO06, Hir08, OMT<sup>+</sup>08], the specification of software reconfiguration [THHO08, Tic09], and the verification of communication protocols [GTB+03, EHH+13]. As a result, MECHATRONICUML supports the specification of a software architecture including state-based real-time behavior and reconfiguration operations for self-adaptive mechatronic systems. In this thesis, we extend the support of MECHATRON-ICUML for specifying and analyzing reconfigurations and message-based communication protocols that are necessary for realizing self-adaptive mechatronic systems. As an application example, we use the RailCab system that is introduced in the next section.

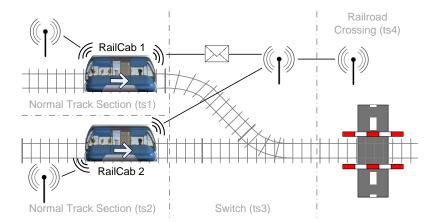

### 1.1 The RailCab System

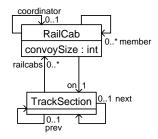

The RailCab system [HTS<sup>+</sup>08a, NBP] is one representative example of a whole class of selfadaptive mechatronic systems that applies runtime reconfiguration for adapting their software to their changing environment [HSD<sup>+</sup>15]. The vision of the RailCab system is a new kind of railway transportation system where autonomous vehicles, the *RailCabs*, transport people and goods directly to their destination without the need for changing trains. RailCabs drive autonomously, only controlled by software using the existing track systems. Figure 1.1(a) shows a RailCab prototype in scale 1:2.5 on the test track at the University of Paderborn.

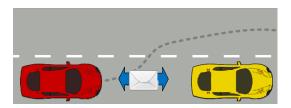

One feature of the RailCab system is the convoy mode which is similar to the aforementioned car platoons. In convoy mode, two or more RailCabs agree on driving behind one another at small distances in order to reduce the energy consumption [HTS<sup>+</sup>08a, HP14]. Figure 1.1(b) shows an illustration of the build-up of a convoy of three RailCabs. Joining a convoy requires the RailCabs to adapt their software, e.g., for handling the necessary communication inside the convoy.

(a) RailCab Prototype in Scale 1:2.5 on Test Track

(b) Build-up of a Convoy of Three RailCabs at a Switch [NBP]

Figure 1.1: The RailCab System

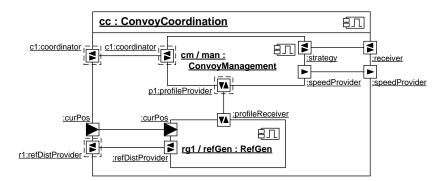

In addition, building a convoy includes electing a so-called *coordinator* [HTS<sup>+</sup>08a, HP14]. The coordinator is responsible for providing reference data and announcing acceleration and braking maneuvers to all other RailCabs in the convoy, which we call *members*. The necessary communication between the RailCabs is formally defined by a message-based communication protocol called ConvoyCoordination. This communication protocol is safety-critical because collisions are inevitable if RailCabs are not notified correctly about acceleration or braking maneuvers.

## 1.2 Problem Statement

The software of a self-adaptive mechatronic system like the RailCab is complex, i.e., it consists of a large number of concurrent, interconnected functions. A common approach for building such software is a component-based approach where the software architecture is specified by hierarchical, interconnected components [SGM02]. MECHATRONICUML follows this approach as well. Components interact via message-based communication protocols. In MECHATRONICUML, a reconfiguration of the system is specified by a modification of the software architecture, i.e., adding and removing component instances and connectors. Communication protocols and reconfigurations are formally verified for safety properties using model checking [GTB<sup>+</sup>03, GS13] and inductive analyses [BBG<sup>+</sup>06]. In this section, we outline three particular problems regarding the specification and analysis of models including runtime reconfiguration that are currently not sufficiently solved by MECHATRONICUML and other related approaches.

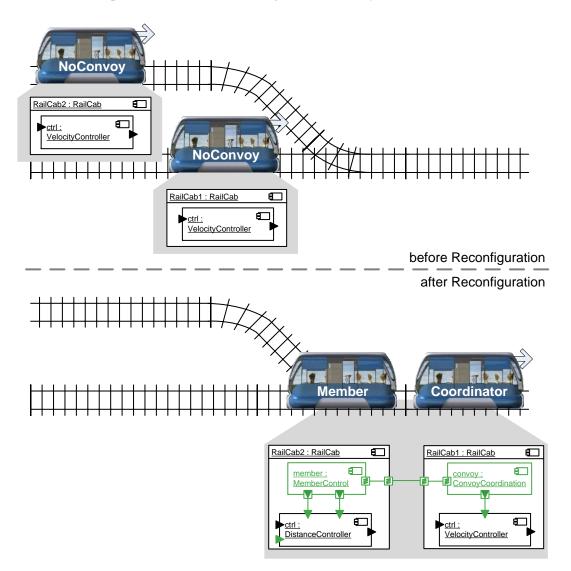

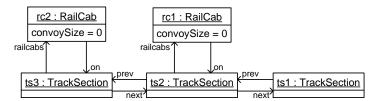

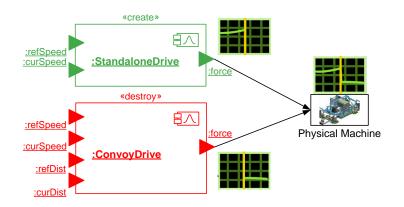

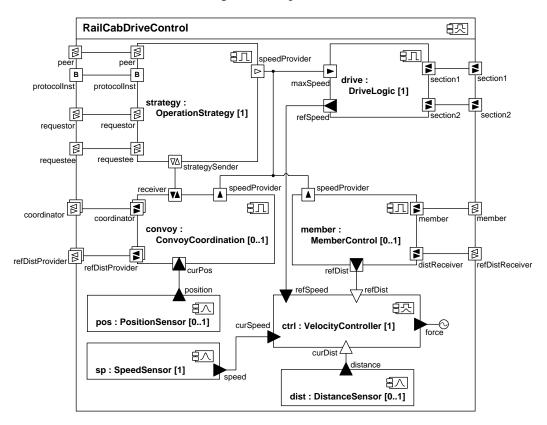

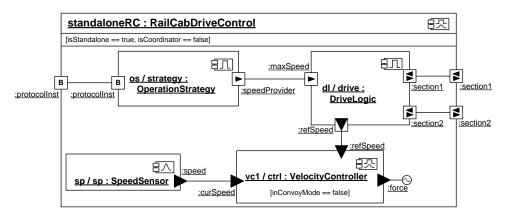

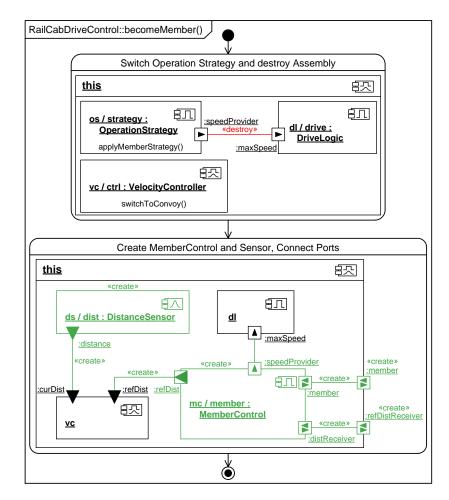

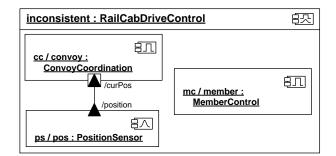

**1. Reconfiguration of Mechatronic Systems** In a component-based system, a reconfiguration often affects several components of the software architecture. As an example, consider two RailCabs that reconfigure their software architecture for building a convoy as shown in Figure 1.2. Before building the convoy, both RailCabs only execute their a VelocityController that controls their speed as shown in the upper part of Figure 1.2. For driving in the convoy, the member RailCab needs to instantiate the software component MemberControl that implements the communication protocols for driving in a convoy. In addition, this RailCab needs to replace its VelocityController by a DistanceController that takes the distance to the preceding RailCab into account as shown in the lower part of Figure 1.2. The coordinator only needs to instantiate the software component ConvoyCoordination that implements the communication protocols for communicating with the convoy members.

Figure 1.2: Illustration of the Software Reconfiguration of RailCabs for Building a Convoy

Thus, the reconfiguration for becoming a convoy member affects the RailCab software component as well as the VelocityController. In such cases, all of the affected components need to reconfigure correctly such that the intended result can be established. If reconfigurations are only executed partially, the system may become unsafe. If the RailCab only instantiates the MemberControl component but does not switch the feedback controller, the system is unsafe. In this case, the RailCab does not consider the distance to the preceding RailCab while driving in a convoy. If the RailCab only switches the feedback controller but does not instantiate the MemberControl component, the system is unsafe as well. In this case, the feedback

controller does not receive the reference speed for driving in the convoy and, as a result, the RailCab may drive too fast and cause a collision.

To be safe, a reconfiguration approach needs to ensure, on the one hand, that the reconfigurations can never produce an inconsistent software architecture as, e.g., executing the DistanceController without executing the MemberControl. On the other hand, the reconfiguration approach must ensure that a reconfiguration can be executed completely in time before actually starting it. That, in turn, requires to take the real-time constraints of the system into account while deciding whether a reconfiguration should be executed or not, and to verify that no reconfiguration violates the real-time constraints. Since the component model of a self-adaptive mechatronic system is hierarchical in most cases, the reconfiguration approach needs to support reconfiguration across different levels of hierarchy while preserving the encapsulation of components [SGM02]. At present, no existing approach for specifying reconfiguration of component-based systems considers all of the aforementioned properties.

**2. Refining Communication Protocols** In a self-adaptive mechatronic system, whose software is implemented in a component-based fashion, communication between the components is essential for realizing the functionality of the system [SW07]. This includes both, the communication between components inside a single system but also the communication between systems as part of a system of systems [WA13]. As a result, the correctness of the software of a self-adaptive mechatronic system does not only depend on the correctness of a single component but also on the correctness of the application-level communication protocols that define the interaction between components and between different system.

Due to the safety critical nature of self-adaptive mechatronic systems, it is desirable to apply formal verification methods like model checking [CGP00, BK08] to ensure correctness of their component-based software. Model checking gives a mathematical proof that safety and liveness properties, which have been specified for the system, hold. However, formal verification techniques like model checking suffer from the so-called state-explosion problem [CGP00]. It denotes the fact that the number of runtime states of a software grows exponentially in both, the number processes and the number of states of each process, if the system has concurrent executions [CKNZ12]. This makes the verification of component-based systems with concurrent components quickly infeasible. Compositional verification approaches [BCC98] tackle the state-explosion problem by verifying single components of a component-based system in isolation. Many of these approaches are based on the assume/guarantee principle [CGP00, ch. 12], i.e., they verify the correctness of a component based on assumptions that must be guaranteed by the component's environment. One of the main difficulties of assume/guarantee approaches is deriving good assumptions automatically from the software model [CAC08].

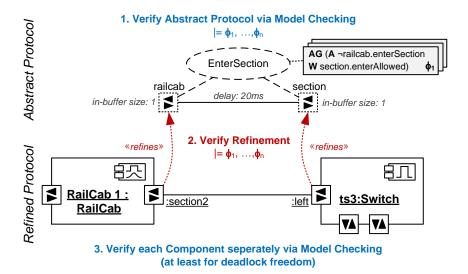

One example of a compositional verification approach based on the assume/guarantee principle is given by the compositional verification approach of MECHATRONICUML [GTB<sup>+</sup>03, GS13]. This approach prevents the computation of assumptions by providing a syntactic decomposition of the system. In particular, MECHATRONICUML separately defines components and communication protocols that define the interaction of components. Then, components may be verified under the assumption that the interaction via the communication protocol is correct. Guaranteeing this assumption requires two steps. First, we need to verify the communication protocol using model checking [EHH<sup>+</sup>13]. At this point, the assume/guarantee principle requires that the protocol is independent of the component. Second, we need to guarantee that the component correctly implements the communication protocol without invalidating the verification results obtained for the communication protocol in the first step.

However, implementing the communication protocol in the component requires to modify it. In particular, we need to integrate the protocol with the internal behavior of the component, for example, for accessing data and triggering computations. As a result, we need to verify that the component implementation of the communication protocol is a correct refinement of the verified protocol behavior according to a refinement definition. The refinement definition guarantees that the component implementation of a communication protocol does not invalidate the verification result that has been obtained for the communication protocol. In particular, a refinement definition formally defines how the component implementation (refined protocol) may deviate from the communication protocol (abstract protocol) without invalidating a particular set of verified properties. Thus, a suitable definition of refinement is essential for a compositional verification approach as the one used by MECHATRONICUML.

In literature, many different refinement definitions and according verification procedures exist [BK08, WL97, JLS00]. "Examples include timed simulation and timed bisimulation [WL97]. Depending on the particular type of protocol that is refined, all refinement definitions might be useful when building a system. A suitable refinement definition for a compositional approach needs to be as weak as possible for enabling reuse of an abstract protocol in as many different components as possible but as strong as necessary for guaranteeing that all verified properties hold for the refined protocol. If the refinement definition is too weak, it is not guaranteed that verified properties still hold for the refined protocol. If the refinement definition is too strong, the refinement check might reject the refined protocol although it fulfills all properties. This may happen, for example, if the refined protocol removes behavior that is irrelevant for the properties, but which is checked by the too strong refinement definition. The existing refinement definitions provide different compromises between reuse and preserved properties. As a consequence, there does not exist one refinement definition that is suitable for all possible protocols. Instead, a compositional verification approach should support several refinement definitions where each of which may be suitable for a particular abstract and refined protocol and a set of verified properties." [HBDS15]

As a result, we need an integrated approach that automatically selects a suitable refinement definition and, in particular, verifies it for a given pair of abstract and refined protocols.

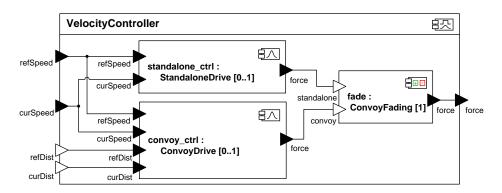

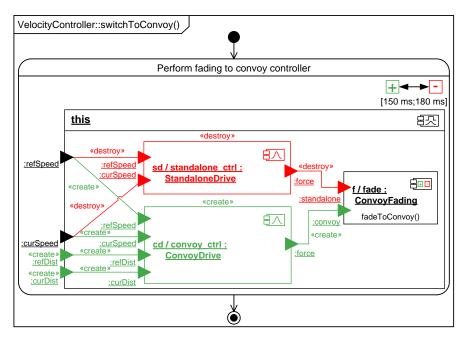

**3.** Simulation of Self-adaptive Mechatronic Systems The safe and correct operation of a mechatronic system depends on the correct integration of the time-continuous feedback controllers and the discrete software components. This includes, in particular, reconfiguration of the software architecture at runtime. As discussed before, reconfiguration of the software architecture of a mechatronic system may require to exchange feedback controllers. Exchanging feedback controllers involves the specification and execution of potentially complex fading functions [BGO06,  $OMT^+08$ ] that guarantee that safe meaningful values are applied on the physical machine at any time during the exchange. Therefore, it is absolutely mandatory to ensure correctness of the reconfigurations.

A major objective of MECHATRONICUML is to prove the correctness of such system models by applying formal verification. However, the integration of time-continuous feedback controllers whose behavior is defined by differential equations hardens formal verifi-

cation significantly. In literature, it is often referred to as the hybrid model checking problem [Hen96]. Hybrid model checking approaches either only use very simple models of timecontinuous behavior or they apply overapproximation techniques [HHMWT00]. "A primary reason for adopting overapproximation is that a precise model, or a practical engineering model at hand, incorporates elements that no verification tool can handle in combination. This is often the case for hybrid system models due to their rich vocabulary. Analysis of such models can only commence after a chain of approximation steps, some of which can be achieved automatically, others – the majority in practice – requiring manual reformulation of the model under inspection. Each of these approximations may cause a loss of precision in the model, e.g., when capturing nonlinear behavior by a linear model, making the analysis less likely to succeed with a positive certificate as outcome. At the same time, as these approximations often have to be done manually, they require extremely skilled staff, are tedious and have to be repeated when the original model changes." [ERNF12] In addition, even the most recent techniques can only handle models that are "still of academic nature in the size of problems solvable." [ERNF12]. As a result, it is not yet possible to verify correctness for large and complex reconfigurable mechatronic systems such as the RailCab.

A different approach to assess the correctness of the operations of a mechatronic system is testing by using a model-in-the-loop (MIL) simulation [Plu06]. In a MIL simulation, the developer tests a model of the mechatronic system against a model of its environment. The model of the mechatronic system always includes the feedback controllers and the discrete software components, but it may also include models of the mechanic, electric, or hydraulic parts of the system. This approach is already used in the automotive industry [BB08, SHS12].

MIL simulation of mechatronic systems is supported by commercial-of-the-shelf simulators such as MATLAB<sup>®</sup>/Simulink<sup>®</sup> [Matg] or Dymola [Das] for the specification language Modelica [Fri04, Mod09]. These tools, however, require models to be static, i.e., once specified, components and connections may not change while running a simulation. In addition, they do not provide native support for asynchronous, message-based communication with message buffers.

As a result, we need an approach that supports MIL simulation of self-adaptive mechatronic systems that communicate via asynchronous, message-based communication protocols. This approach needs to be integrated into our component-based development approach such that model checking the event-discrete software components using the compositional verification approach mentioned above remains possible.

### 1.3 Contribution

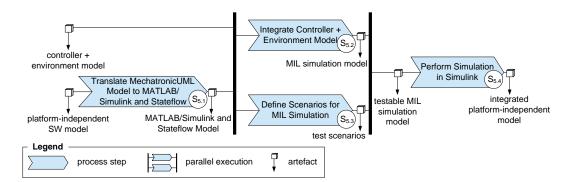

The contribution of this thesis is a combination of constructive and analytical techniques that support the component-based specification and analysis of self-adaptive mechatronic systems as part of a model-driven approach. As a key novelty compared to related approaches, we combine formal verification and simulation-based testing for achieving a scalable analysis for ensuring correctness of the software of a self-adaptive mechatronic system. In particular, we contribute a transactional execution of hierarchical reconfigurations including an approach for their verification ( $C_1$ ), a verification procedure for showing correct refinements of communication protocols ( $C_2$ ), and support for simulating self-adaptive mechatronic systems in MATLAB/Simulink ( $C_3$ ). We integrate our contributions into the MECHATRONICUML

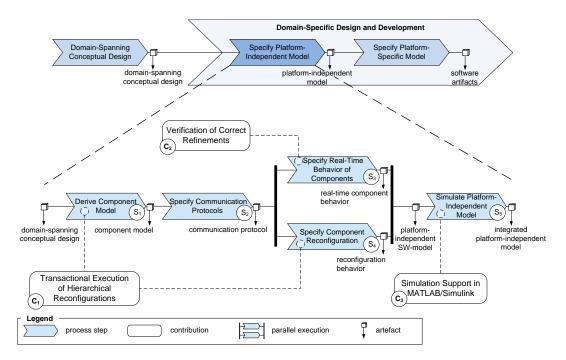

method. As a result, our contributions enhance the existing development process of MECHA-TRONICUML [HSST13, BDG<sup>+</sup>14b] as outlined in Figure 1.3. All of our contributions have been implemented as part of the MECHATRONICUML Tool Suite [DGB<sup>+</sup>14].

Figure 1.3: Excerpt of the Design Process for the Development of Self-Adaptive Mechatronic Systems (cf. [HSST13, GV14])

The starting point for the process, shown in Figure 1.3, is the domain-spanning conceptual design [GFDK09,  $GSG^+09$ ] that has been created collaboratively by experts from all disciplines involved in building the mechatronic system, e.g., mechanical engineering, control engineering, and software engineering. It includes all information about use cases, functions, and system elements that affect more than one discipline. Based on the domain-spanning conceptual design, each of the involved disciplines starts the domain-specific design and development phase. In this phase, the software engineers execute the MECHATRONICUML process [HSST13, BDG<sup>+</sup>14b], which consists of two main phases in accordance to the model-driven architecture approach [Gro14]. Thus, the process starts by creating a platform-independent model of the software. Then, the software engineers derive a platform-specific model of the software and define a deployment of the software to the hardware platform. The contributions of this thesis address the specification of the platform-independent model.

The software engineer starts specifying the platform-independent model in **Step S**<sub>1</sub> by deriving an initial component model from the domain-spanning conceptual design. In this thesis, we unify the existing component models of MECHATRONICUML and provide an extension that enables a concise, declarative specification of hierarchical reconfigurations. This specification forms the basis for a transactional execution of reconfigurations ( $C_1$ ) that respects ACI-properties of database systems [BHG87]. These are *atomicity*, i.e., either all component instances reconfigure or none does, *consistency*, i.e., each reconfiguration pro-

duces a consistent component instance configuration, and *isolation*, i.e., reconfigurations do not interfere with each other.

In Step  $S_2$ , the software engineer specifies a communication protocol for each interaction between components. This includes a formal verification of the protocol behavior using model checking [GTB<sup>+</sup>03, EHH<sup>+</sup>13, Ger13].

After specifying the communication protocols, the software engineer needs to specify the real-time behavior for each component of the component model. This real-time behavior needs to include the communication protocols that have been specified and verified in Step  $S_2$  such that the verified safety and liveness properties are not invalidated. We support the software engineer in this step by an integrated verification procedure that verifies whether the real-time behavior of a component correctly refines a communication protocol according to a formal refinement definition ( $C_2$ ). As a byproduct, our approach automatically selects a suitable refinement definition out of a set of possible refinement definitions.

In **Step S**<sub>4</sub>, the software engineer specifies the reconfiguration behavior of the components using our aforementioned extensions of the component model. In addition, we extend this step by an approach for verifying that the reconfiguration behavior fulfills the required ACI-properties and meets all hard real-time deadlines ( $C_1$ ). The result of Steps S<sub>3</sub> and S<sub>4</sub> is a platform-independent model of the software.

Finally, the software engineer needs to analyze whether event-discrete software and timecontinuous feedback controllers have been integrated correctly by using a MIL simulation in **Step S**<sub>5</sub>. We support the software engineer in this step by automatically deriving a simulation model that includes both, the real-time behavior and the reconfiguration behavior of the components. The simulation model is then extended by the implementations of the feedback controllers and the environment model. The MIL simulation may then be carried out using MATLAB/Simulink. It enables the engineers of the different disciplines to validate the whole self-adaptive mechatronic system by simulation and enables to use the code generation facilities of MATLAB/Simulink for deriving source code for the system.

### 1.4 Overview

The remainder of this thesis is structured as follows. Chapter 2 introduces the foundations that are required for understanding the contributions of this thesis. In Chapter 3, we define a new component model for MECHATRONICUML. The MECHATRONICUML component model forms the basis for the remaining contributions of this thesis. Along with the component model, we continue our RailCab example from Section 1.1. We use this example throughout the remainder of this thesis. Chapter 4 introduces our concept for transactional execution of reconfigurations. In addition, we explain our concept for verifying reconfigurable components for ACI and timing properties. Thereafter, Chapter 5 presents our approach for verifying that communication protocols have been correctly refined by the components in our component model. Next, we present our approach for MIL simulation of self-adaptive mechatronic systems in Chapter 6. In particular, we define how simulation models in MATLAB/Simulink can be derived automatically from a MECHATRONICUML model. Finally, we summarize the contributions of this thesis and give a perspective on future works in Chapter 7. We discuss the implementation and evaluation of our concepts as well as related works along with our contributions as part of the main chapters of this thesis.

The appendices provide additional, more technical information that supplement our contributions. First, Appendix A presents additional parts of the RailCab model that we use as a running example. Appendix B contains a formal definition of the semantics of Real-Time Statecharts that we use for defining state-based behavior. Finally, we describe our framework for performing reachability analyses (Appendix C) and the metamodels that have been created as part of this thesis (Appendix D).

## 2 Foundations

This chapter introduces the foundations for understanding the concepts presented in the remainder of this thesis. We start by reviewing concepts and terminology related to self-adaptive mechatronic systems in Section 2.1 that we will use in the following. Thereafter, Section 2.2 introduces timed model checking including timed automata and the timed computation tree logic. The latter two provide the formal basis for specifying and verifying state-based behavior models of a self-adaptive mechatronic system. Section 2.3 introduces graphs and corresponding graph transformations that form the basis for specifying and verifying reconfiguration operations of a self-adaptive mechatronic system. Finally, Section 2.4 introduces MECHATRONICUML, which is a domain-specific language based on timed automata and graph transformations, that enables to specify software models for a self-adaptive mechatronic system on a higher level of abstraction. We will integrate all of the contributions of this thesis into MECHATRONICUML.

## 2.1 Self-Adaptive Mechatronic Systems

Self-adaptive mechatronic systems automatically adapt their software architecture to a changing environment without human intervention. That requires to integrate and associate the software with the constituent parts of the mechatronic system such that the system may reason about itself and its behavior in its current environment. In this section, we introduce basic concepts and corresponding terminology related to self-adaptive mechatronic systems that we use throughout the remainder of this thesis. In Section 2.1.1, we describe how selfadaptive mechatronic systems may be structured hierarchically. Thereafter, we introduce the operator-controller-module as a reference architecture that enables to realize self-adaptive behavior in mechatronic systems (cf. Section 2.1.2). Finally, Section 2.1.3 describes how the concept of models@runtime may be used for executing reconfigurations.

### 2.1.1 Structuring

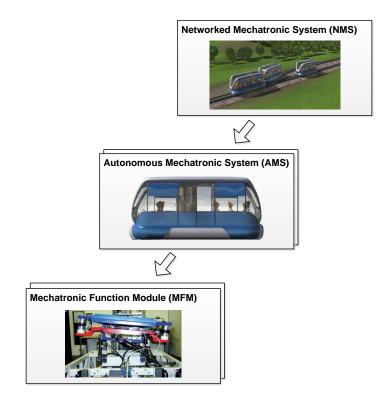

Self-adaptive mechatronic systems can be structured hierarchically as shown in Figure 2.1. In particular, they can be structured into mechatronic function modules, autonomous mechatronic systems, and networked mechatronic systems (cf. [GRS14, pp. 8-10]).

On the lowest level, a mechatronic system consists of several *mechatronic function modules* (MFM). An MFM embodies part of the mechanical system including sensors, actuators, and software for controlling the mechanical system. An example is given by the drive module [HZ14] or the active suspension module [KT14] of a RailCab. MFMs may, again, be composed of other MFMs.

The overall mechanical structure is represented by the *autonomous mechatronic system* (AMS). It consists of the MFMs of the mechatronic system and includes additional sensors

Figure 2.1: Structuring of Self-Adaptive Mechatronic Systems (cf. [GRS14, p. 9])

and software components for realizing self-adaptive behavior. An example of an AMS is a single RailCab.

Finally, AMS' may collaborate and form *networked mechatronic systems* (NMS). Networked mechatronic systems usually have no physical representation but are only virtually created by the AMS by using message-based communication protocols. Then, each AMS fulfills a particular role in the NMS. An example is given by convoys of RailCabs.

### 2.1.2 Operator-Controller-Module

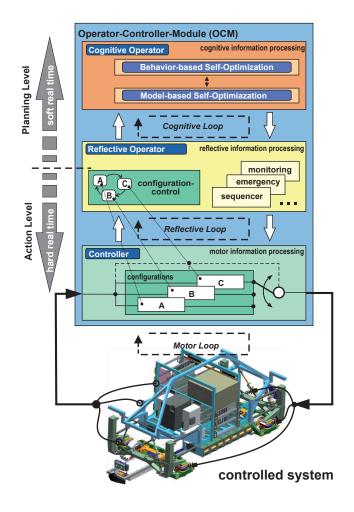

The *operator-controller-module* (OCM) is a reference architecture for self-adaptive mechatronic systems that separates the behavior specification into three conceptual levels [HOG04, GRS09, GRS14]. As part of this thesis, we relate our contributions to these three conceptual levels of the OCM. The different levels are the cognitive operator, the reflective operator, and the controller as shown in Figure 2.2.

The *controller* level is the lowest. It contains the feedback controllers that control the physical system that is also called the controlled system [Kil05]. A feedback controller continuously receives the current value of the controlled variable from the physical sensors. Based on a reference value for the controlled variable, it tries to reduce the difference between the current value and reference value to zero by computing signals for the system's actuators.

The *reflective operator* forms the middle layer of the OCM. It contains event-discrete software that is required for the operations of the mechatronic system as, for example, the behavior for operating as a coordinator or member of a convoy. As a key element of this

Figure 2.2: Overview of the Operator-Controller-Module [GRS14, p. 11]

behavior, the reflective operator executes communication protocols for interacting with other AMS.

In addition, the reflective operator provides the ability to reconfigure its own software architecture including the feedback controllers on the controller level. In accordance to Allen et al. [ADG98] and Zhang et al. [ZC06], we distinguish between *steady-state behavior* and *reconfiguration behavior*. The steady-state behavior defines the behavior that is executed by the feedback controllers on the controller level and by the reflective operator based on a particular software architecture without considering reconfigurations. The reconfiguration behavior defines possible modifications of the software architecture. Using the reflective loop, self-adaptive systems continuously monitor their own behavior for deciding whether, when, and how they need to reconfigure. During a reconfiguration, the system switches from one steady-state behavior to another steady-state behavior [ADG98, ZC06]. In the following, we refer to the different steady-behaviors of a self-adaptive mechatronic system as *functional behavior* [MSKC04].

The *cognitive operator* provides the self-optimization capabilities to the system. Therefore, it typically manages a set of weighted goals that the AMS shall achieve at runtime [vL01, GSB<sup>+</sup>08]. As a result, the cognitive operator contains functionality for reasoning about the system's behavior and the environment for optimizing the system's behavior according to the given goals.

The software on the controller level and part of the reflective operator are executed with respect to hard real-time constraints [Kop97]. This includes, in particular, the reconfiguration of the software being executed on these levels and the communication between different systems. The cognitive operator and the remainder of the reflective operator are executed in soft real-time [Kop97].

### 2.1.3 Models@Runtime

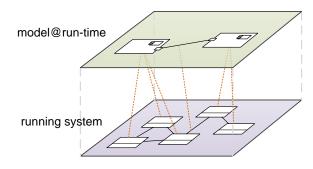

A model@runtime is a model of a system that it manages and uses by itself during runtime [BBF09]. In contrast to a reflective system model [Mae87], it is typically specified on a higher level of abstraction as denoted by Blair et al. [BBF09]. Both approaches, however, require that the model and the system are causally connected. That means that any change in the running system is reflected into the model@runtime and, what is even more important, any change of the model@runtime changes the running system in the same way. As a consequence, the system can be modified by modifying the model@runtime instead of modifying the running system directly. In this thesis, we use this approach for defining and executing reconfigurations based on a model@runtime of the software architecture [GS04].

Figure 2.3: Illustration of a Model@Runtime

Figure 2.3 illustrates the principle of a model@runtime. The running system on the lower level consists of a set of objects. The model@runtime abstracts these objects to a component representation and associates the objects and connectors of the running system to the model elements of the model@runtime. Changing the component structure in the model@runtime will also change the object structure in the running system.

## 2.2 Timed Model Checking

Model checking [CGP00, BK08] is an automated formal verification procedure that gives a mathematical proof whether a software model fulfills a given set of formal requirements. Thus, it may guarantee the absence of errors in a model, in contrast to testing, which may only show the presence of errors. Timed model checking [ACD93, HNSY94] additionally considers the real-time characteristics that apply to a model of a mechatronic system's software. In this thesis, we use (timed) model checking as an analytical method for showing the correctness of functional and reconfiguration behavior of a self-adaptive mechatronic system.

Timed model checking uses timed automata as introduced in Section 2.2.1 as a behavioral model. Therefore, timed automata provide the formal basis for specifying state-based real-time behavior in MECHATRONICUML (cf. Section 2.4). The timed computation tree logic as introduced in Section 2.2.2 enables the specification of formal requirements. These formal requirements express the safety and liveness properties that the timed automata need to fulfill. We require knowledge about such formal requirements for defining our refinement approach in Chapter 5. Finally, a timed model checking algorithm decides whether the timed automata fulfill the formal requirements given based on the timed computation tree logic (cf. Section 2.2.3).

#### 2.2.1 Timed Automata

A *timed automaton* [AD94, BY04] is a state-based model for specifying real-time behavior. Timed automata extend finite automata [Mea55] by a set of real-valued variables called *clocks* and constraints over these clocks. Clocks measure the progress of time in a system. Time progresses constantly and uniformly in all clocks. In literature, there exist many variants of timed automata (see Waez et al. [WDR11] for a recent survey). In this thesis, we will use timed safety automata [HNSY94] as they are defined for the UPPAAL model checker by Bengtsson and Wang [BY04]. For the remainder of this thesis, we will refer to timed safety automata simply as timed automata.

Like finite automata, timed automata have a set of inputs, a set of outputs, and a set of integer variables. Each transition may consume an input and produce an output. Integer variables may be used for guard conditions of the transitions and may be changed using assignments while the transition fires.

In addition, timed automata support three modeling elements based on clocks. These are invariants, time guards, and resets. An invariant is assigned to a location. The timed automaton may only rest in a location as long as the invariant is true for the current clock values. A time guard restricts the firing of a transition to a time interval. A reset sets a clock back to zero while a transition fires.

Timed automata can be composed to networks of timed automata (NTA). In an NTA, the single automata interact via their inputs and outputs using so-called *channels*. Then, they use the channels as inputs (marked with ?) and outputs (marked with !).

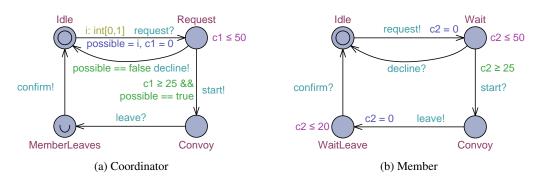

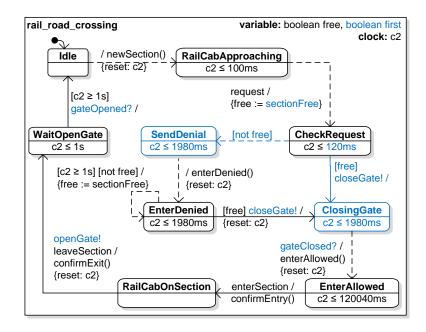

Figure 2.4 shows an NTA consisting of two timed automata that specify a simple convoy behavior. The member automaton in Figure 2.4b requests to start a convoy. The coordinator automaton in Figure 2.4a either starts the convoy or declines the request. Finally, the member automaton may choose to leave the convoy and the coordinator automaton confirms.

The two timed automata use five channels named request, start, decline, leave, and confirm for realizing the convoy behavior. Each of the timed automata has four locations and five transitions. As an example, the coordinator automaton in Figure 2.4a has locations Idle, Request, Convoy, and MemberLeaves. The transition from Idle to Request specifies a reset on clock c1, i.e., the coordinator automaton resets c1 any time it receives a request from the member automaton. The location Request has an invariant  $c1 \leq 50$ , i.e., the coordinator automator automaton while c1 is less or equal 50.

Figure 2.4: Network of Timed Automata Specifying a Simple Convoy Behavior

However, the transition from Request to Convoy may only fire if c1 is greater of equal to 25 as specified by the time guard. Thus, the coordinator automaton may only start the convoy 25 time units after receiving the request.

Timed automata may be nondeterministic. In particular, they may select a value nondeterministically from a given range using selections [BDL06a]. This value may be assigned to a variable. In our example, the coordinator automaton in Figure 2.4a uses a selection at the transition from Idle to Request. It selects the value of i from an integer range from 0 to 1. The value of i is then assigned to the variable possible that defines whether it is possible to start the convoy.

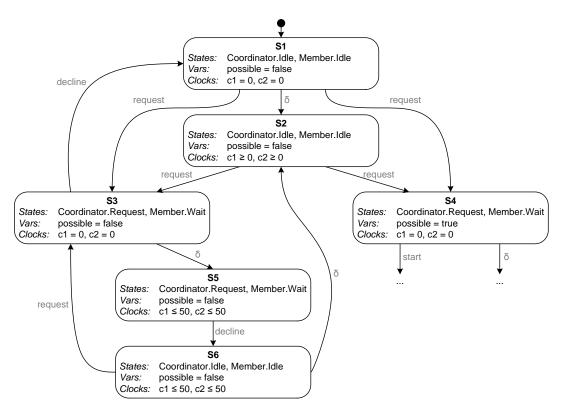

The *state* of an NTA is defined by the discrete locations of all timed automata including the values of their variables and their clocks. Since clocks are real-valued and time increases continually, timed automata always have an infinite number of states. Therefore, the semantics of an NTA is usually defined by means of *symbolic states* based on clock zones [Alu99, BY04]. Clock zones store intervals of clock values and enable to represent the state space of an NTA using a finite *zone graph*. The rules for computing the zone graph define the semantics of NTAs. We refer to paths of the zone graph as *traces*. Figure 2.5 shows the zone graph of the NTA in Figure 2.4.

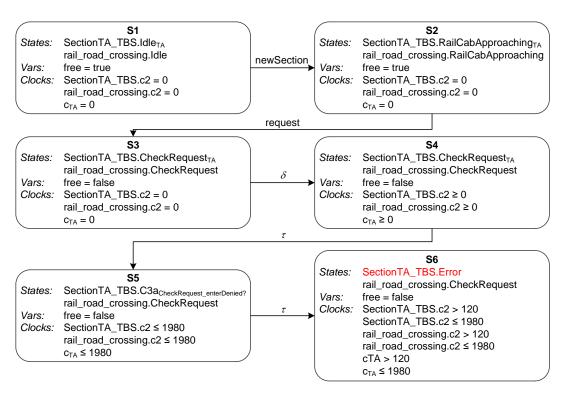

The execution of an NTA starts in the initial states of all timed automata (Idle in both automata in Figure 2.4) with all clocks being zero and all variables set to their initial values. The corresponding symbolic state S1 is the initial state of the zone graph in Figure 2.5. Further symbolic states and transitions in the zone graph are inferred by the following rules:

#### 1. Delay

An NTA may delay, i.e., the values of all clocks increase, but neither the active locations nor the values of the integer variables change. The values of the clocks may increase as long as no invariant of an active location restricts them. In the zone graph, these transitions are labeled with  $\delta$ . As an example, consider the transition from S1 to S2. In S2, all clocks have an unbounded value greater or equal to 0 because the ldle locations do not define invariants.

#### 2. Single Transition

A timed automaton in an NTA may fire a transition that does not use a channel. In this case, the active location and, potentially, the values of the integer variables change. The active locations of all other timed automata remain unchanged. Furthermore, fir-

Figure 2.5: Excerpt of a Zone Graph of the NTA in Figure 2.4

ing transitions in an NTA takes no time and, thus, the values of the clocks do not change except for resets that are performed by the transition. In the zone graph, the corresponding transitions are labeled with  $\tau$ .

### 3. Synchronized Transitions

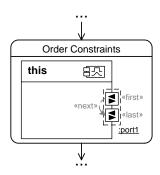

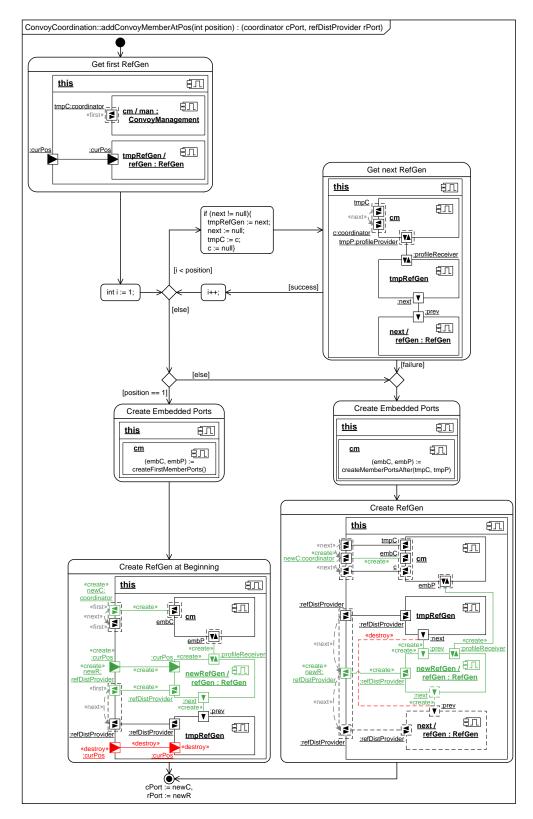

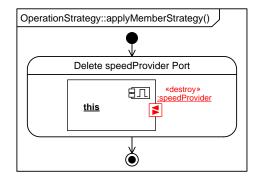

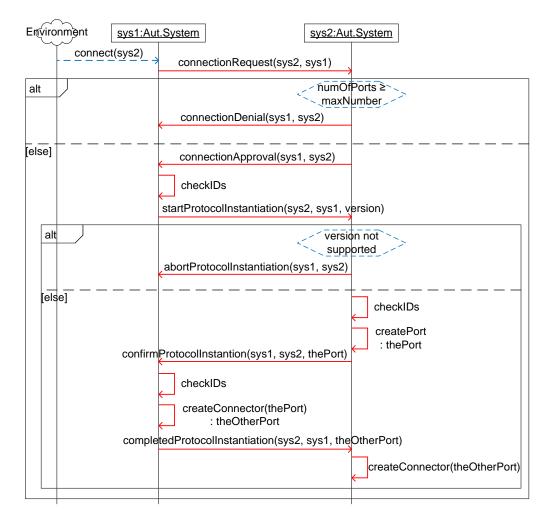

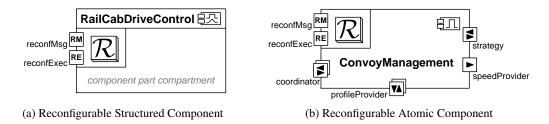

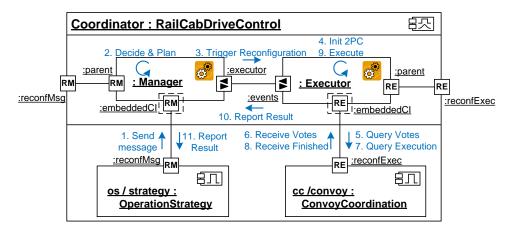

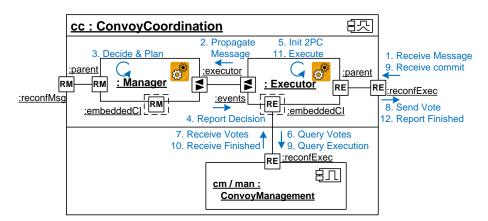

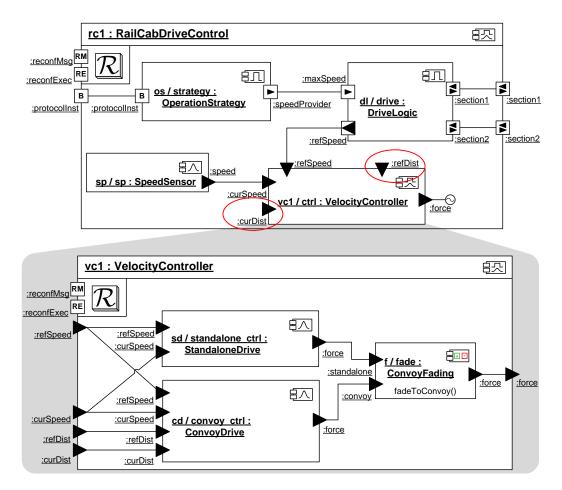

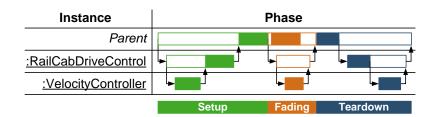

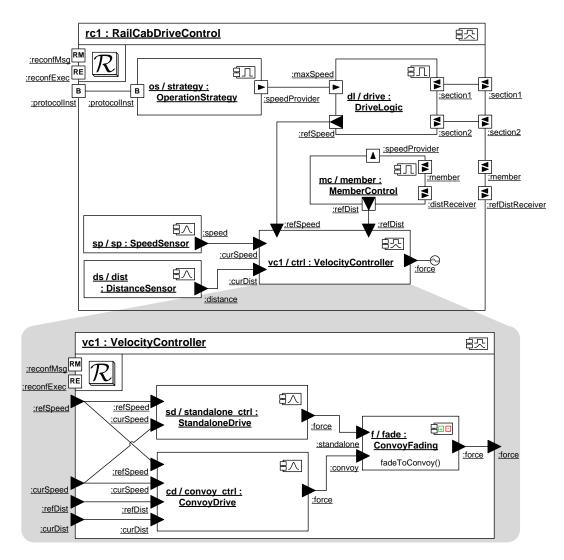

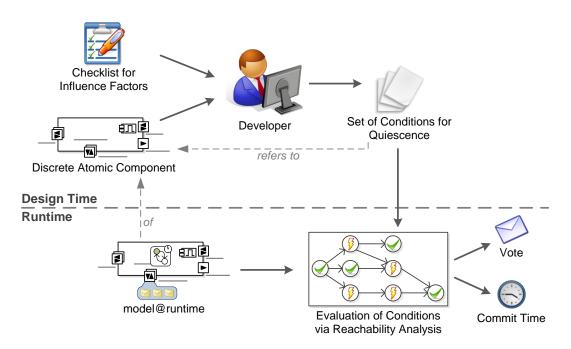

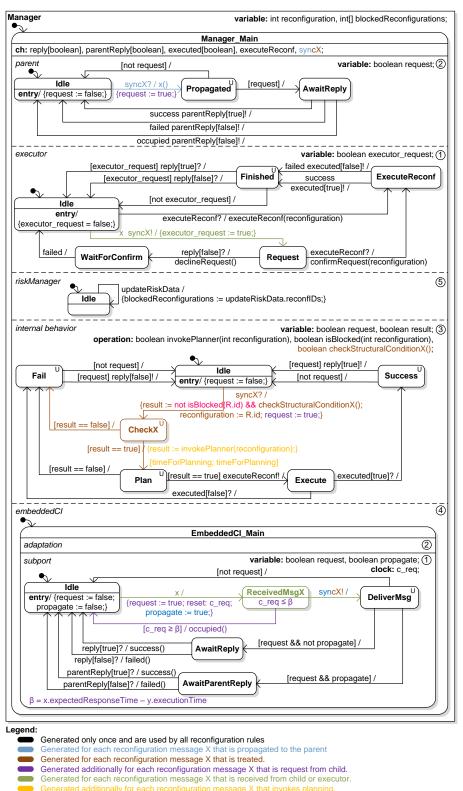

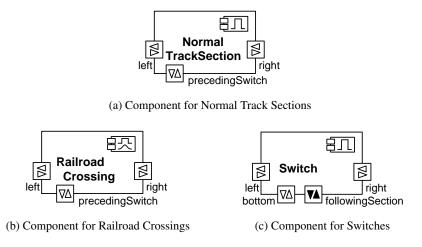

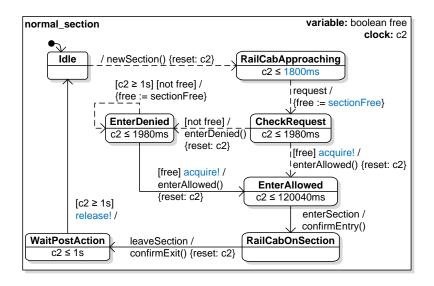

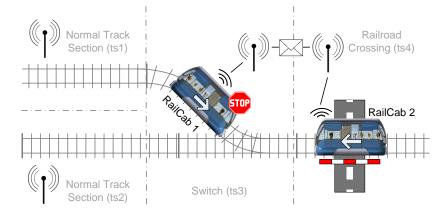

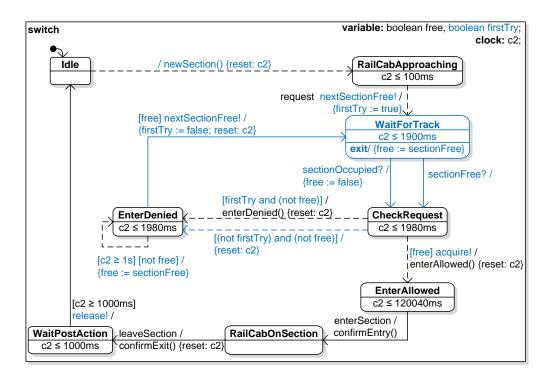

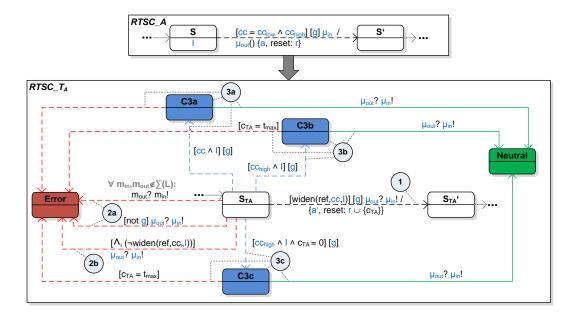

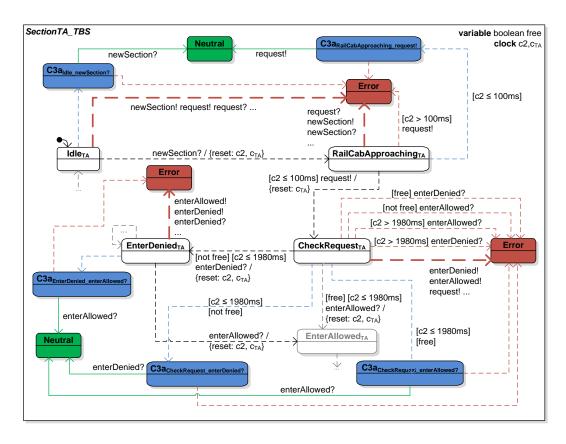

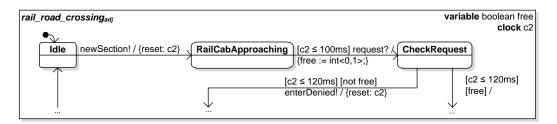

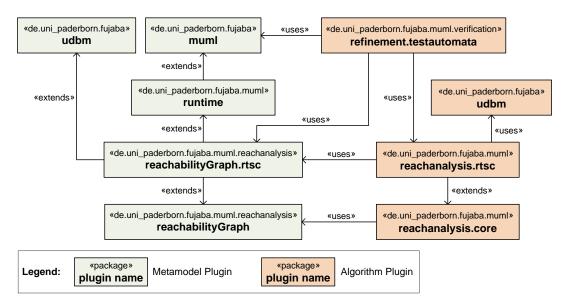

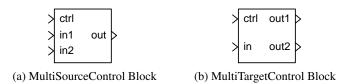

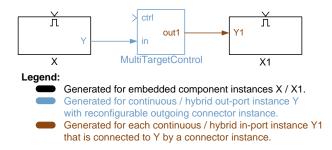

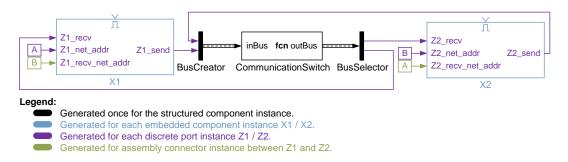

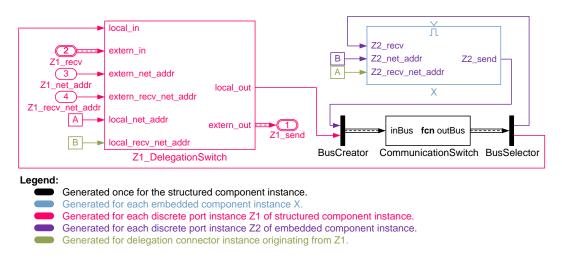

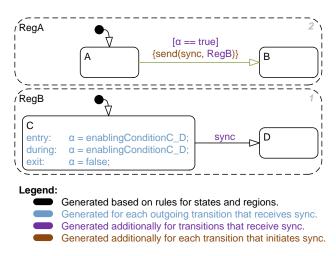

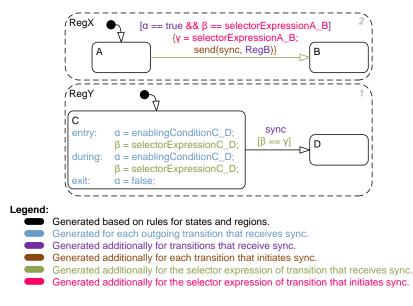

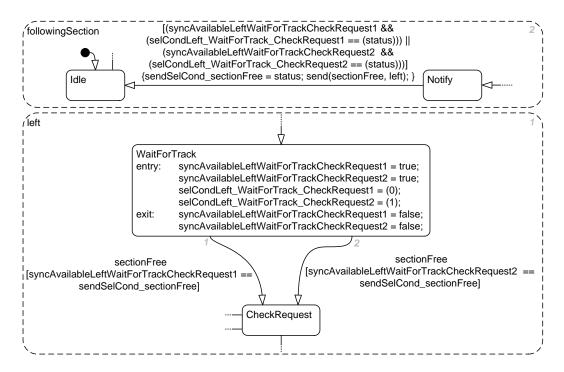

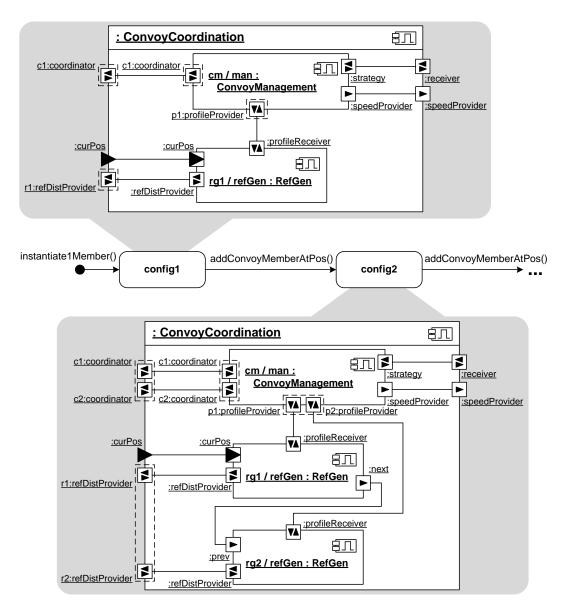

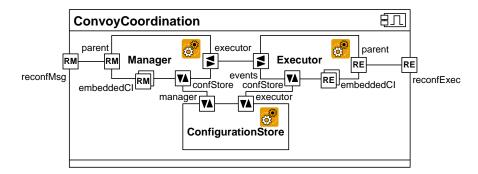

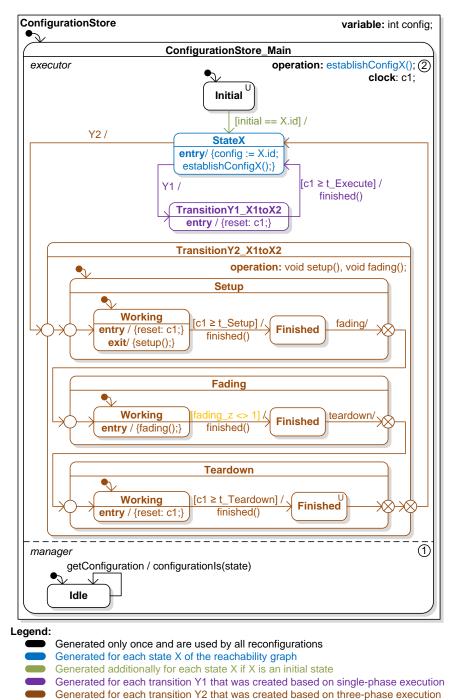

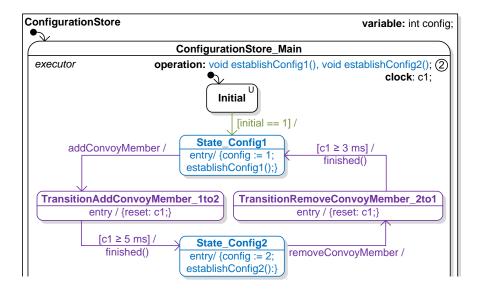

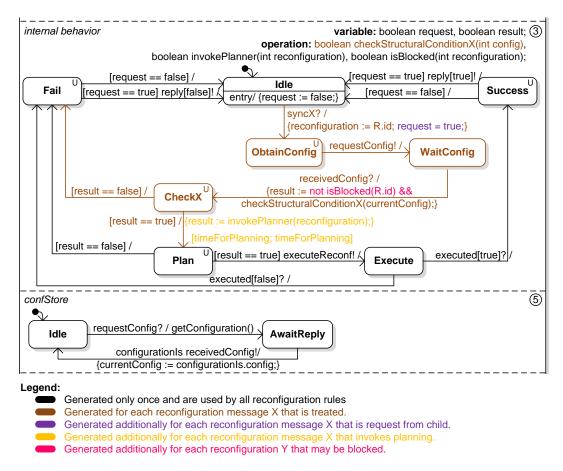

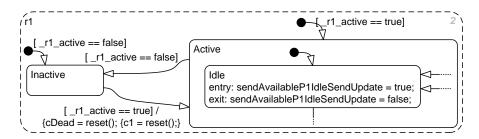

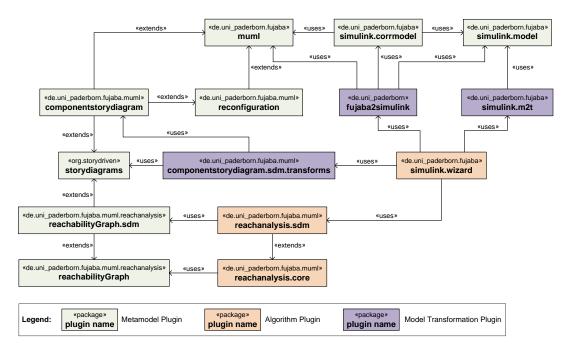

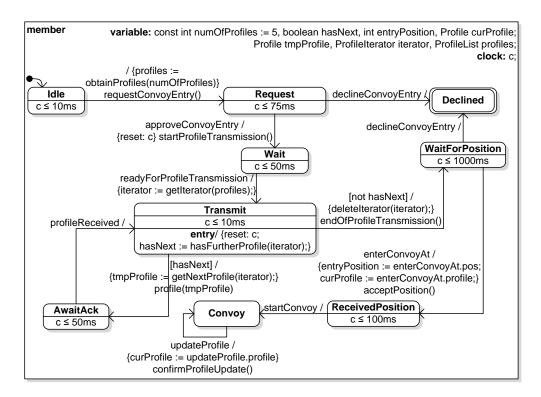

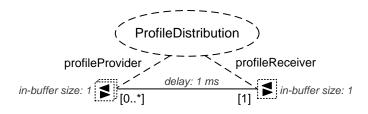

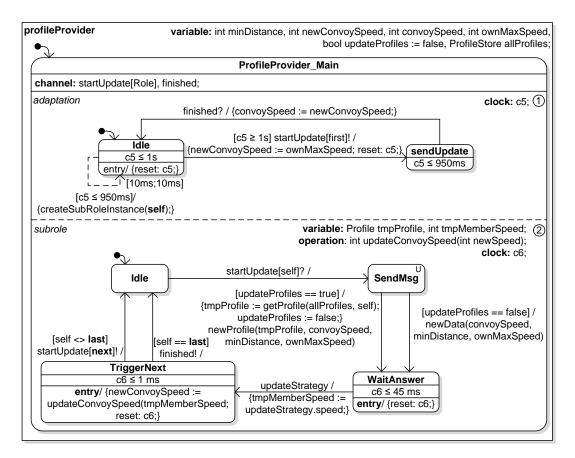

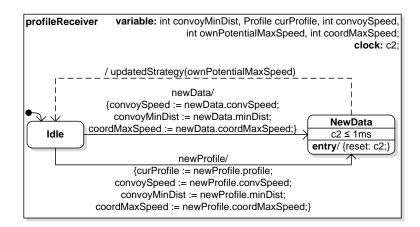

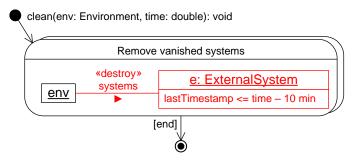

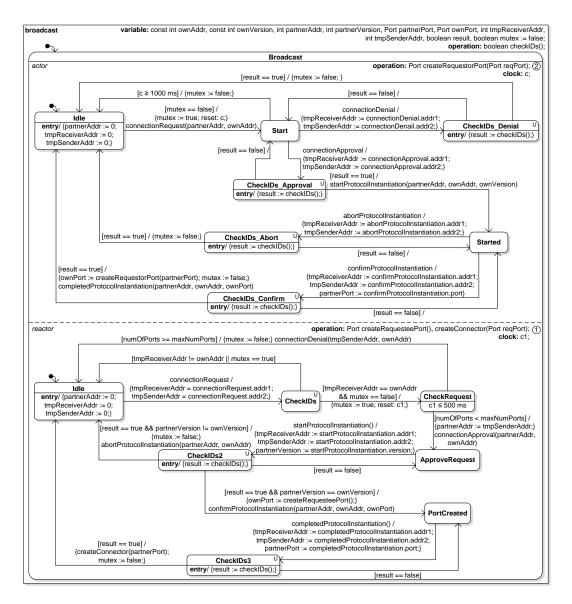

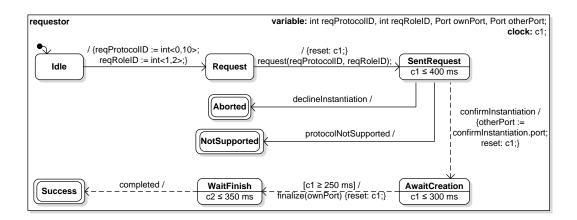

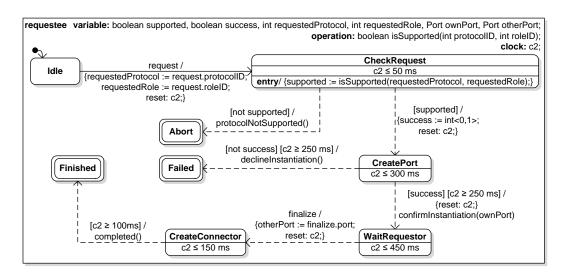

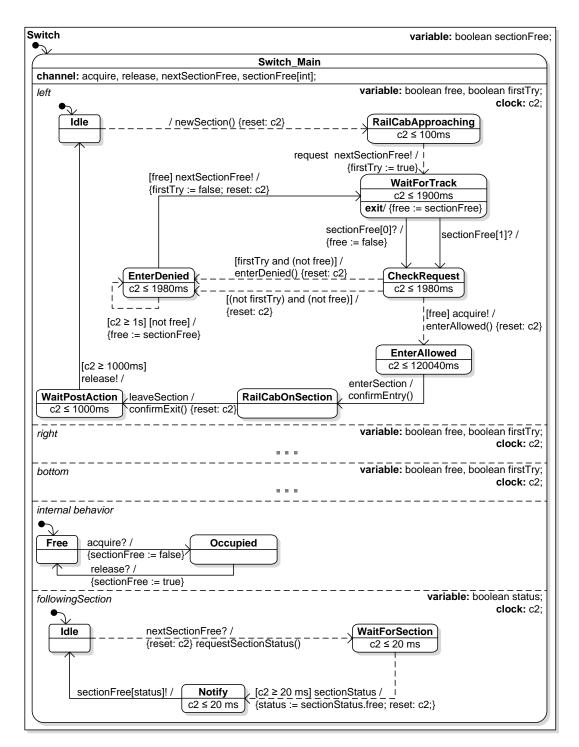

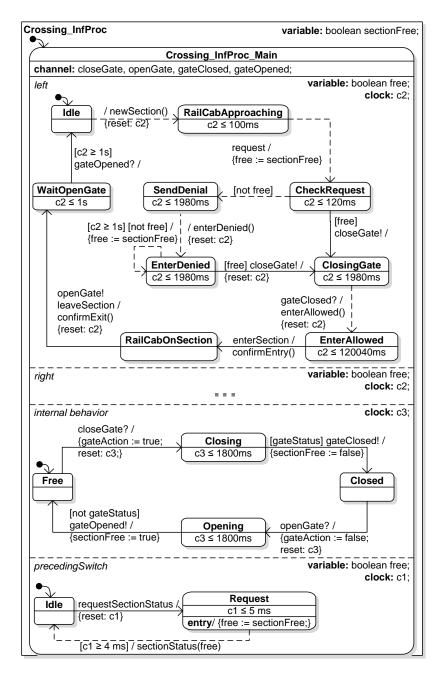

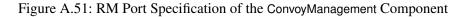

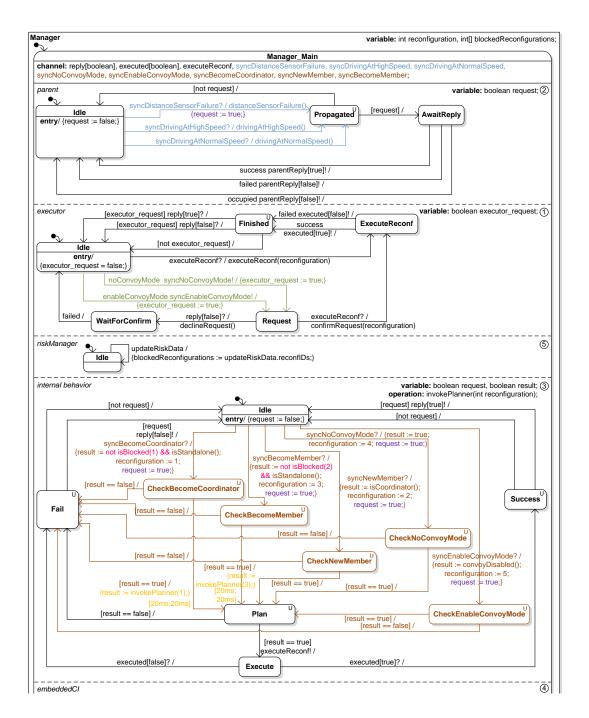

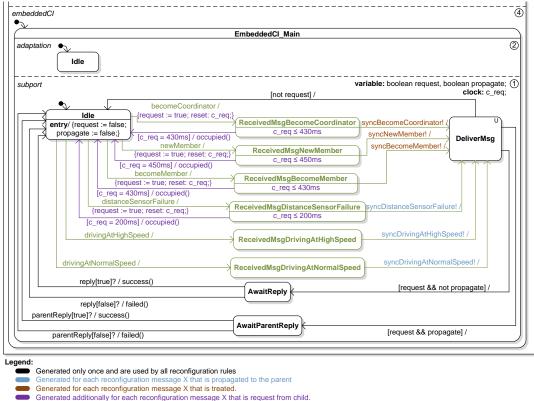

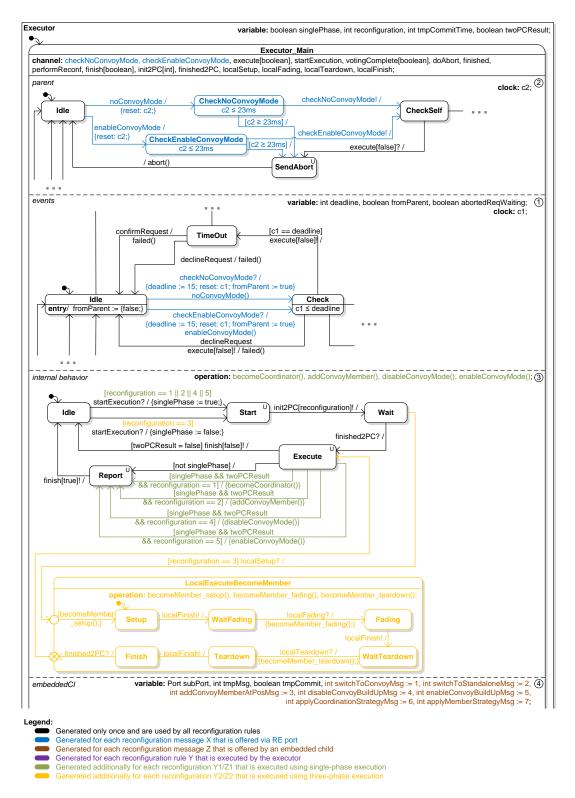

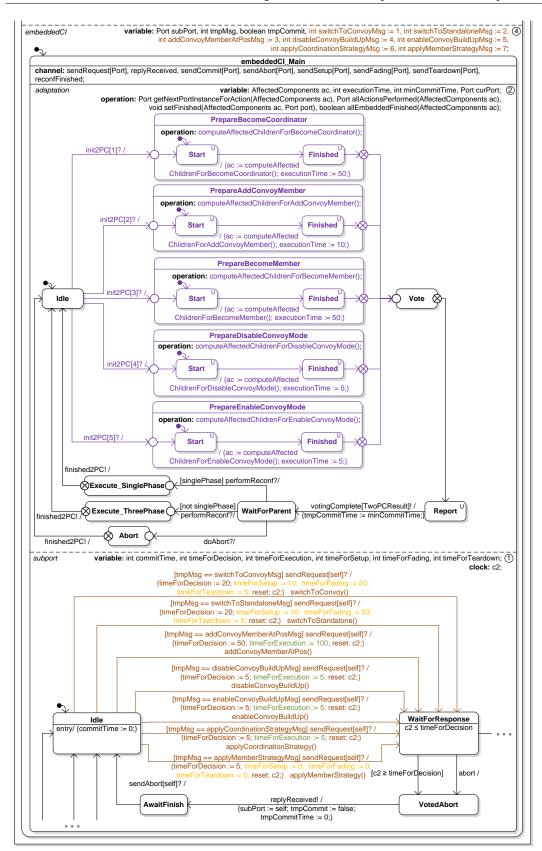

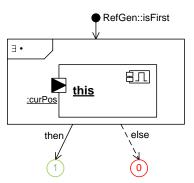

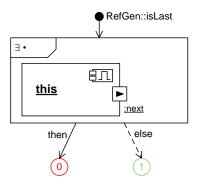

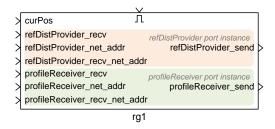

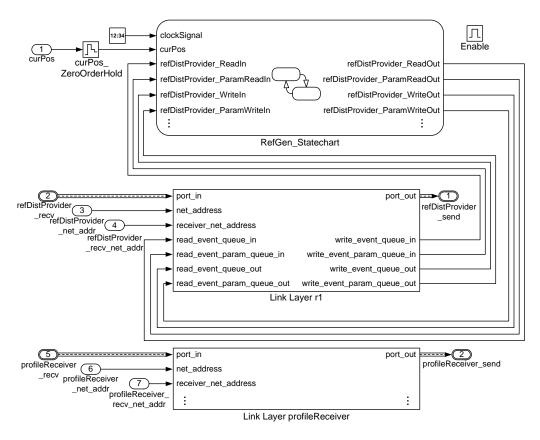

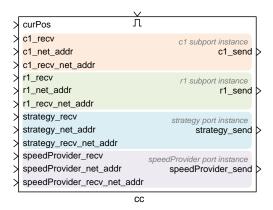

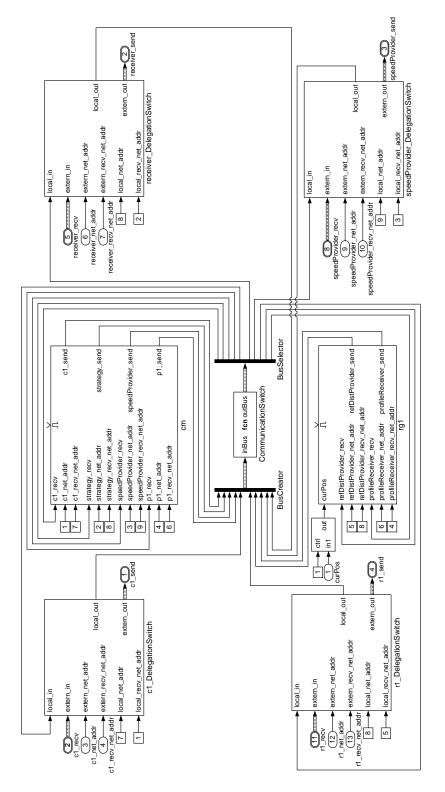

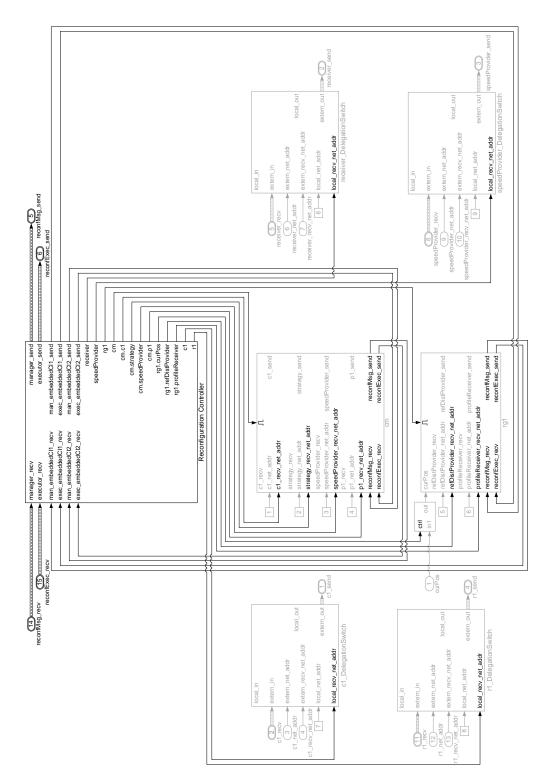

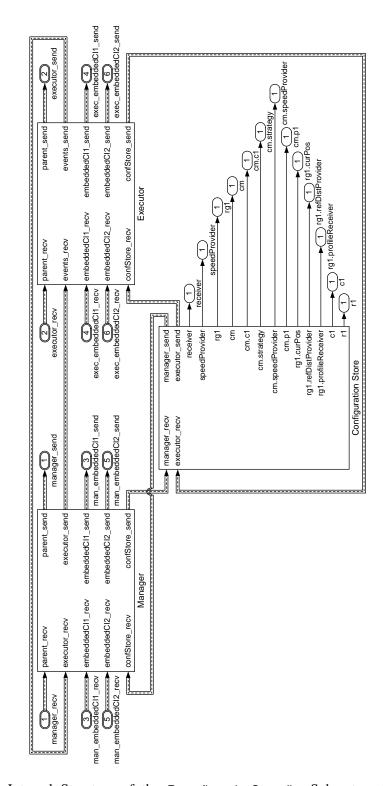

Two timed automata in an NTA may synchronize over a channel and synchronously fire one transition each. The synchronization is defined by the CCS parallel composition operator [Mil82]. As a result, synchronization is realized by hand-shake synchronization, i.e., the two timed automata move to the target locations of their transitions synchronously. For synchronizing transitions, the assignments and resets of the transition with the output (!) are executed prior to the assignments and resets of the transition with the input (?). In the zone graph, the corresponding transitions are labeled with the name of the channel. As an example, consider the transition from S2 to S3 that corresponds to a synchronization via the channel request. As a consequence, both timed automata change their active locations and, due to the resets, both clocks are set back to 0.