# Reconfigurable Accelerators in the World of General-Purpose Computing

Dissertation

A thesis submitted to the Faculty of Electrical Engineering, Computer Science and Mathematics  $_{

m of}$

Paderborn University in partial fulfillment of the requirements for the degree of *Dr. rer. nat.*

by

**Tobias Kenter**

Paderborn, Germany August 26, 2016

### Acknowledgments

First and foremost, I would like to thank Prof. Dr. Christian Plessl for the advice and support during my research. As particularly helpful, I perceived his ability to communicate suggestions depending on the situation, either through open questions that give room to explore and learn, or through concrete recommendations that help to achieve results more directly.

Special thanks go also to Prof. Dr. Marco Platzner for his advice and support. I profited especially from his experience and ability to systematically identify the essence of challenges and solutions.

Furthermore, I would like to thank:

- Prof. Dr. João M. P. Cardoso, for serving as external reviewer for my dissertation.

- Prof. Dr. Friedhelm Meyer auf der Heide and Dr. Matthias Fischer for serving on my oral examination committee.

- All colleagues with whom I had the pleasure to work at the PC<sup>2</sup> and the Computer Engineering Group, researchers, technical and administrative staff. In a variation to one of our coffee kitchen puns, I'd like to state that *research without colleagues is possible, but pointless*. However, I'm not sure about the first part.

- My long-time office mates Lars Schäfers and Alexander Boschmann for particularly extensive discussions on our research and far beyond.

- Gavin Vaz, Heinrich Riebler and Achim Lösch for intensive and productive collaboration on joint research interests.

- The Bachelor and Master students and student assistants I have supervised, for their enthusiasm and for helping me to understand potential and limitations of the different approaches in their projects. The technical contributions of Henning Schmitz have particularly contributed to my research.

- The Deutsche Forschungsgemeinschaft (DFG) and the Intel Labs Braunschweig for funding different phases of my research in the Collaborative Research Centre (CRC) 901 On-The-Fly Computing and the Project Multimodal Reconfigurable Processing Unit (MM-RPU).

- The colleagues in the CRC 901 for insightful discussions.

- Michael Kauschke and Matthias Gries for contributing an industry perspective on my research.

Finally, I would like to thank my family for their encouragement and moral support. Special thanks go to Gaby Nordendorf. If anyone was ever more convinced than me that I would eventually complete this thesis, it was her.

### Abstract

Growing and newly emerging computing workloads and markets keep pushing computer architecture forward. Power limitations and diminishing returns from wider and more parallel processors are driving the need for architectural innovations. By reducing overheads and customizing parallelism, specialized accelerators help to increase the performance of specific workloads efficiently. However, without programmability, they lack the flexibility for general-purpose computing and thus can't profit from shared costs among different workloads, users and markets. The architecture of field programmable gate arrays (FPGAs) combines programmability with a high potential for specialization for different workloads. The main obstacle for FPGA adoption in general-purpose computing is the lack of productive methods and tools for designers and maintainers of implementations running entirely or partially on FPGAs. In this work, by analyzing current approaches to tackle this productivity challenge along with their conceptual and practical trade-offs, we identify three pillars that can complement each other to jointly drive general-purpose adoption of FPGAs. These pillars combine, firstly, synthesis from parallel OpenCL designs, secondly, fast and automatic compilation targeting overlay architectures on FPGAs, and thirdly, the encapsulation of hand-optimized FPGA designs into application- or domain-specific libraries.

In this thesis, we focus on overlay architectures as one of theses paths towards productive FPGA design processes. A large variety of such architectures have been presented over the last years, but for most overlays it was poorly understood, which overheads they involve compared to custom designs implemented directly on FPGA resources. Our work quantifies such overheads with a diverse set of program loops from a state-of-the-art stereomatching application for an instruction-programmable overlay. It demonstrates that the architecture can, despite overheads, serve as a practically usable accelerator, and identifies specific differences to fully customized FPGA designs that may help to reduce overheads through overlay customization. Even though one motivating aspect for related research on overlay architectures has been their potential for fast compilation or synthesis and for quick reconfiguration, in order to demonstrate their practical usefulness to raise productivity when aiming at FPGA acceleration, we had to go one step further with regard to the design entry. To this end, we present a fast tool flow that automatically extracts suitable loops from a high-level source or binary code and offloads them to a vector coprocessor realized as an FPGA overlay. Besides the focus on productivity to foster FPGA adoption, in order to fit into established computing systems and markets, FPGAs need to architecturally coexist and cooperate with general-purpose processors. With a high-level performance estimation model that takes into account the interdependency of architectures and program designs, we explore the design space for such integrated systems. We highlight that integration of the memory hierarchy is not only helpful to reduce application design efforts, but also has considerable influence on the acceleration potential of the platform. Recent, high-profile trends in industry show interesting correspondences to our analysis. When the hardware integration of FPGA accelerators proceeds on this path, it will be foremost the interplay of design productivity and performance potential that governs the success of FPGAs in generalpurpose computing. With our analysis and technical contributions in that field, we may help to shape the outcome of this process.

## Zusammenfassung

Der Bedarf an immer höherer Rechenleistung für wachsende und neu aufkommende Rechenlasten und Märkte ist eine Herausforderung für die Rechnerarchitektur. Grenzen bei der Leistungsaufnahme und sinkende Erträge durch größere und zunehmend parallele Prozessoren machen Architekturinnovationen notwendig. Durch Effizienzsteigerungen und durch individuell angepasste Parallelität können spezialisierte Beschleuniger dazu beitragen, die Rechenleistung für bestimmte Rechenlasten zu erhöhen. Ohne Programmierbarkeit fehlt ihnen jedoch die Flexibilität für allgemeine Rechenaufgaben und sie können somit nicht davon profitieren, Kosten auf verschiedene Nutzungsszenarien und Märkte zu verteilen. Die Architektur von FPGAs, eine bestimmte Variante programmierbarer Logikbausteine, kombiniert Programmierbarkeit mit einem hohen Potenzial zur Spezialisierung für verschiedene Rechenlasten. Das größte Hindernis auf dem Weg zu einem verbreiteten Einsatz von FPGAs für allgemeine Rechenaufgaben ist der Mangel an produktiven Methoden und Werkzeugen zur Entwicklung und Wartung von Implementierungen, die ganz oder teilweise auf FPGAs ausgeführt werden. Wir analysieren in dieser Arbeit aktuelle Ansätze, die Produktivität bei der Entwicklung von FPGA-Anwendungen zu steigern, und arbeiten konzeptuelle und praktische Vor- und Nachteile heraus. Darauf aufbauend identifizieren wir drei Säulen, die einander dabei ergänzen können, die Verwendung von FPGAs für allgemeine Rechenaufgaben voranzutreiben. Diese Säulen kombinieren erstens eine Konfigurationsgenerierung ausgehend von parallelen OpenCL-Implementierungen, zweitens eine schnelle und automatisierte Übersetzung für übergelagerte Architekturen auf FPGAs, und drittens die Zusammenfassung von manuell optimierten FPGA-Konfigurationen zu anwendungs- oder bereichsspezifischen Bibliotheken.

In dieser Ausarbeitung konzentrieren wir uns auf übergelagerte Architekturen als Ansatz für produktive Entwicklungsprozesse für FPGAs. Im Laufe der letzten Jahre wurde eine Vielzahl solcher Architekturen vorgestellt, die durch eine Zwischenschicht das Abstraktionsniveau von FPGAs erhöhen. Allerdings existierte für die meisten dieser übergelagerten Architekturen nur ein unzureichendes Verständnis von Flächenmehrverbrauch oder reduzierten Rechenleistungen im Vergleich zu spezialisierten Konfigurationen die den FPGA ohne Zwischenschicht nutzen. Unsere Arbeit quantifiziert für eine instruktionsbasierte übergelagerte Architektur solche Nachteile anhand einer Auswahl unterschiedlicher Programmschleifen, die zu einer modernen Anwendung für stereoskopischen Bildabgleich gehören. Wir zeigen, dass diese Architektur trotz dieser Nachteile als praktisch nutzbarer Beschleuniger dienen kann und identifizieren verschiede Unterschiede im Vergleich zu vollständig spezialisierten Konfigurationen. Dies könnte zukünftig helfen, durch Spezialisierung der übergelagerten Architekturen, deren Nachteile weiter zu reduzieren. Das Potenzial zur schnellen Übersetzung oder Konfigurationsgenerierung für übergelagerte Architekturen, sowie die Möglichkeit schnell Konfigurationen auszutauschen, war bereits ein Anreiz für die bestehende Forschung diesem Bereich. Um allerdings zu demonstrieren, dass sie tatsächlich dazu beitragen, eine erhöhte Produktivität bei der Beschleunigung von Anwendungen mit FPGAs zu erreichen, mussten wir bezüglich der Ausgangsdarstellung einen Schritt weitergehen. Dazu stellen wir Werkzeuge vor, die automatisch geeignete Schleifen aus Hochsprachenquelltexten oder Binärcode extrahieren und auf einem Vektorprozessor zur Ausführung bringen, der als übergelagerte Architektur auf FPGAs umgesetzt ist.

Neben dem Schwerpunkt auf Produktivität zur weiteren Verbreitung von FPGAs, müssen diese auch in etablierte Rechnersysteme und Märkte integriert werden, und dazu architektonisch mit allgemeinen Prozessoren zusammenpassen und zusammenarbeiten. Mit einem abstrakten Modell zur Abschätzung von Rechenleistung, das die gegenseitige Abhängigkeit zwischen Architekturen und Programmierentscheidungen berücksichtigt, erkunden wir systematisch Alternativen für derartig integrierte Rechnersysteme. Wir arbeiten heraus, dass die Integration der Speicherhierarchie nicht nur dazu beiträgt, Anwendungsentwicklung zu erleichtern, sondern auch einen erheblichen Einfluss auf das Beschleunigungspotenzial des Rechnersystems hat. Aktuelle, viel beachtete Entwicklungen bei kommerziellen Rechnersystemen zeigen inzwischen interessante Übereinstimmungen zu unserer Analyse. Wenn die Integration von FPGA-Beschleunigern in Systeme derartig weitergeht, wird vor allem das Zusammenspiel von Produktivität und erzielbarer Rechenleistung über den Erfolg von FPGAs für allgemeine Rechenaufgaben entscheiden. Mit unserer Analyse und den technischen Beiträgen in diesem Bereich könnten wir den Ausgang dieser Entwicklung entscheidend mitgestalten.

## Contents

| AŁ  | ostrac                            | ct                      |                                                                                                                                                                                                                    | v                            |

|-----|-----------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Zu  | ısamı                             | nenfass                 | sung                                                                                                                                                                                                               | vii                          |

| Co  | onten                             | ts                      |                                                                                                                                                                                                                    | ix                           |

| Lis | st of                             | Tables                  |                                                                                                                                                                                                                    | xiii                         |

| Lis | st of                             | Listings                | 5                                                                                                                                                                                                                  | xv                           |

| Lis | st of                             | Figures                 | i de la constante de la constan                                                                                                    | xviii                        |

| 1   | <b>Intro</b><br>1.1<br>1.2<br>1.3 | Contri                  | <b>n</b><br>ation                                                                                                                                                                                                  | . 2                          |

| 2   | <b>Com</b> 2.1                    | • •                     | Concepts, Trends and Domains         ute Devices: Basic Terms and Concepts         Target Metrics         Instruction-Programmable Processors         Computing in Circuits         Field-Programmable Gate Arrays | . 6     . 8     . 17         |

|     | 2.2                               |                         | s in Technology, Architectures and Devices                                                                                                                                                                         | . 26<br>. 26<br>. 28<br>. 30 |

|     | 2.3                               | Compt<br>2.3.1<br>2.3.2 | uting domains and markets                                                                                                                                                                                          | . 35<br>. 35<br>. 37<br>. 38 |

|   |      | 2.3.3    | Markets and Workloads of General-Purpose Computing              | 40<br>41<br>42<br>45 |

|---|------|----------|-----------------------------------------------------------------|----------------------|

|   | 2.4  | Chapt    | er Conclusion                                                   | 45<br>45             |

| 3 |      |          | for general-purpose adoption of FPGAs with the help of Overlay- |                      |

|   |      | nitectur |                                                                 | 47                   |

|   | 3.1  |          | en Performance and Productivity Walls                           | 47                   |

|   |      | 3.1.1    | Productivity of General-Purpose Architectures                   | 47                   |

|   |      | 3.1.2    | Impact of System Architectures                                  | 51                   |

|   |      | 3.1.3    | FPGA Productivity                                               | 52                   |

|   |      | 3.1.4    | Three Pillars for General-Purpose FPGAs                         | 55                   |

|   | 3.2  |          | Overlays                                                        | 57                   |

|   |      | 3.2.1    | Instruction-Programmable Overlays                               | 57                   |

|   |      | 3.2.2    | Reconfigurable Hardware beyond FPGAs                            | 60                   |

|   |      | 3.2.3    | Structurally Programmable Overlays                              | 61                   |

|   | 3.3  | Chapt    | er Conclusion                                                   | 63                   |

| 4 | Ster | eo-Mat   | tching Kernels on Overlay and Custom Designs                    | 65                   |

|   | 4.1  | Introd   | uction to the Stereo-Matching Problem                           | 66                   |

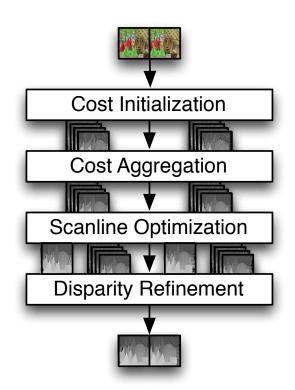

|   | 4.2  | Stereo   | -Matching Algorithm with Inherent Parallelism                   | 67                   |

|   |      | 4.2.1    | Cost Initialization                                             | 68                   |

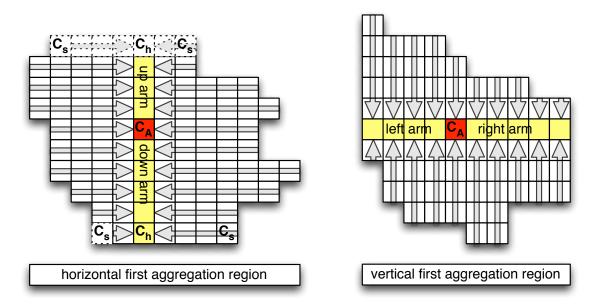

|   |      | 4.2.2    | Cost Aggregation                                                | 69                   |

|   |      | 4.2.3    | Scanline Optimization                                           | 71                   |

|   |      | 4.2.4    | Disparity Refinement                                            | 73                   |

|   |      | 4.2.5    | Software Implementation                                         | 73                   |

|   | 4.3  | Utilize  | ed FPGA Platforms and Programming Models                        | 73                   |

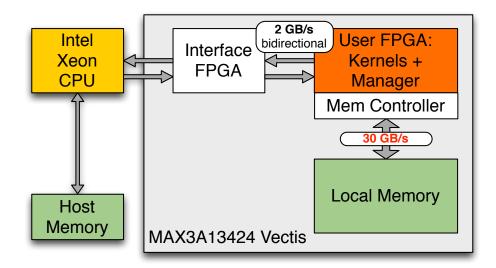

|   |      | 4.3.1    | Maxeler Platform and Programming Paradigm                       | 73                   |

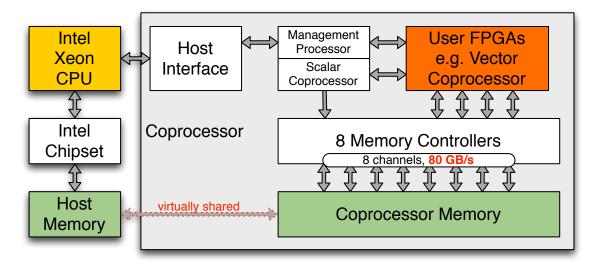

|   |      | 4.3.2    | Convey HC-1 Platform with Vector Processor Overlay              | 75                   |

|   |      | 4.3.3    | Comparison of FPGA Platforms                                    | 76                   |

|   | 4.4  |          | l-Centric Acceleration                                          | 77                   |

|   | 4.5  |          | l-Designs for two FPGA platforms                                | 81                   |

|   |      | 4.5.1    | Aggregation Kernels                                             | 82                   |

|   |      | 4.5.2    | Scanline Kernels                                                | 87                   |

|   |      | 4.5.3    | Synthesis and Integration                                       | 90                   |

|   |      | 4.5.4    | Kernel Summary                                                  | 92                   |

|   | 4.6  | Experi   | imental Setup                                                   | 93                   |

|   |      | 4.6.1    | Evaluated Systems                                               | 93                   |

|   |      | 4.6.2    | Input Data                                                      | 94                   |

|   | 4.7  |          | ation and Comparisons                                           | 96                   |

|   |      | 4.7.1    | Stereo-Matching System Performance                              | 96                   |

|   |      | 4.7.2    | Platform Overheads                                              | 99                   |

|   |              | 4.7.3 Kernel Performance                                             | . 101 |

|---|--------------|----------------------------------------------------------------------|-------|

|   |              | 4.7.4 Quantifying Overlay Overheads through Hardware-Normalization . | . 104 |

|   |              | 4.7.5 Overheads by Kernel Groups                                     |       |

|   |              | 4.7.6 Estimates on Design Efforts                                    |       |

|   |              | 4.7.7 Limitations of the Comparison                                  |       |

|   | 4.8          | Related Work                                                         |       |

|   | 4.9          | Chapter Conclusion                                                   |       |

| 5 | Con          | pilation and Runtime Techniques for FPGA Accelerators                | 113   |

| 5 | 5.1          | Motivation                                                           |       |

|   | $5.1 \\ 5.2$ | Approach                                                             |       |

|   | 0.2          | 5.2.1 Toolflow for Heterogeneous Executables                         |       |

|   |              | 5.2.2 Code Extraction                                                |       |

|   |              | 5.2.3 Vectorization                                                  |       |

|   |              | 5.2.4 Runtime Decisions                                              |       |

|   | 5.3          | Experimental Setup                                                   |       |

|   | 5.3<br>5.4   | Evaluation                                                           |       |

|   | 0.1          | 5.4.1 Comparison to Hand-Written Kernels of Chapter 4                |       |

|   |              | 5.4.2 Further Experiments                                            |       |

|   | 5.5          | Related Work                                                         |       |

|   | 5.6          | Excursion to Offloading Decisions at Runtime                         |       |

|   | 5.7          | System-Level Scheduling and Task Migration                           |       |

|   | 5.8          | Chapter Conclusion                                                   |       |

| ~ | CDI          | -<br>La se a la matema <b>C</b> onstanza di sta superiore            | 101   |

| 6 | 6.1          | J-accelerator System Integration Motivation                          | 131   |

|   | 6.1          | Proposed Architecture                                                |       |

|   | 0.2          | 6.2.1 Relation to Existing Architectures                             |       |

|   | 6.3          | Method and Framework                                                 |       |

|   | 0.5          | 6.3.1 Estimation Model                                               |       |

|   |              | 6.3.2 Partitioning Approach                                          |       |

|   | 6.4          | Design Space Exploration                                             |       |

|   | 0.4          | 6.4.1 Speedups per benchmark                                         |       |

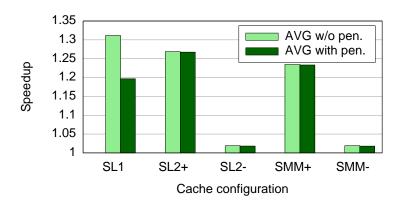

|   |              | 6.4.2 Memory integration                                             |       |

|   |              | 6.4.3 Accelerator Size                                               |       |

|   |              | 6.4.4 Execution Efficiency                                           |       |

|   |              | 6.4.5 Interface Latency                                              |       |

|   | 6.5          | Related Work                                                         |       |

|   | 6.6          | Chapter Conclusion                                                   |       |

|   |              | •                                                                    | . 143 |

| 7 |              | clusion                                                              | 151   |

|   | 7.1          | Summary                                                              |       |

|   | 7.2          | Outlook                                                              |       |

|   |              | 7.2.1 Towards a Library of Overlay Architectures and Tools           | . 152 |

#### Contents

| 7.2.2        | 2 And Beyond | 153 |

|--------------|--------------|-----|

| Acronyms     |              | 155 |

| Author's put | blications   | 159 |

| Bibliography | y            | 161 |

## List of Tables

| 2.1 | Symbols for instruction set example                              |

|-----|------------------------------------------------------------------|

| 2.2 | Selection of instructions for a RISC-like instruction set        |

| 2.3 | Execution of assembler loop in five-stage pipeline               |

| 2.4 | Truth table for 1-bit full adder                                 |

| 2.5 | Truth table for 2-input multiplexer                              |

| 2.6 | Truth table for equality check with fixed input                  |

| 2.7 | Power projections for the example loop                           |

| 2.8 | Summary of opportunities for FPGAs in general-purpose markets 45 |

| 4.1 | Hardware resources of two FPGA platforms in our experiments      |

| 4.2 | Unrolling factors of synthesized kernels                         |

| 4.3 | Resource utilization of implemented kernels                      |

| 4.4 | Dimensions of low-disparity image series                         |

| 4.5 | Dimensions of high-disparity image series                        |

| 4.6 | Speedups over CPU expressed as Kernel-ratios                     |

| 4.7 | Hardware-Normalized Kernel-Ratios between FPGA platforms 104     |

| 4.8 | Hardware-Normalized Kernel-Ratios by kernel types                |

| 5.1 | Performance evaluation of vectorized loops                       |

| 6.1 | Basic symbols of the model                                       |

| 6.2 | Data obtained by profiling and static code analysis              |

| 6.3 | Architecture parameters of the model                             |

| 6.4 | Solution-specific data depending on architecture                 |

| 6.5 | Default model parameters for design space exploration            |

| 6.6 | Alternative parameters used for three level cache hierarchy      |

| 6.7 | Investigated cache configurations                                |

# Algorithms and Listings

| 2.1 | Listing: Code snippet computing running sums of an input array 15     |

|-----|-----------------------------------------------------------------------|

| 2.2 | Listing: Assembly code program for the code snippet                   |

| 4.1 | Algorithm: Horizontal aggregation step                                |

| 4.2 | Algorithm: Scanline optimization step in left to right orientation 72 |

| 4.3 | Listing: Memory manager example                                       |

| 4.4 | Listing: Continued memory manager example for Maxeler                 |

| 4.5 | Listing: Continued memory manager example for Convey 81               |

| 4.6 | Listing: Horizontal integral sums                                     |

| 5.1 | Listing: Code example for coprocessor extraction                      |

| 5.2 | Listing: Vectorized loop nest from horizontal integral sums           |

| 5.3 | Listing: Pattern with simple loop carried dependency                  |

| 5.4 | Listing: Extended pattern with loop carried dependency                |

| 5.5 | Listing: Pattern with irregular index offsets                         |

| 6.1 | Algorithm: multi-level partitioning                                   |

| 6.2 | Function: getBestPartitionObject                                      |

# List of Figures

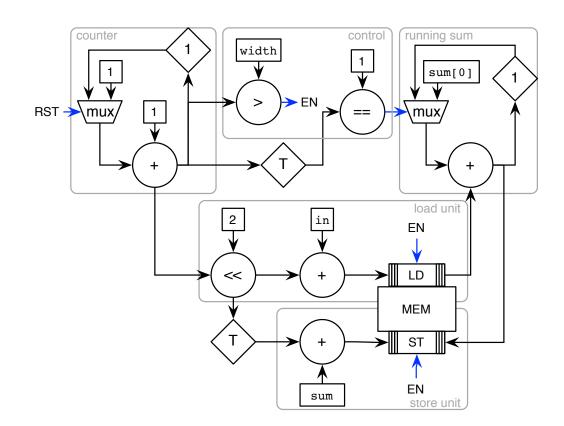

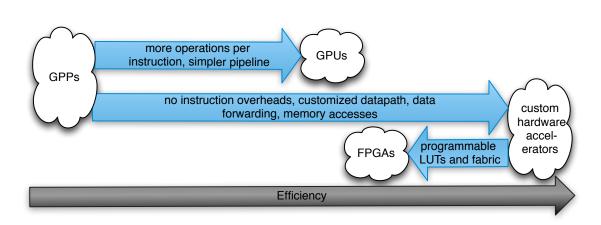

| Illustration of a circuit for previous code snippet                                                                                     | $\frac{20}{34}$                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

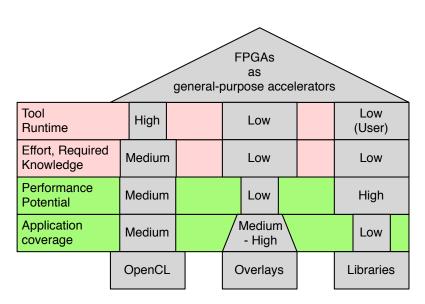

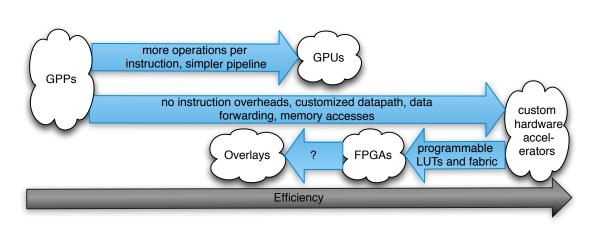

| Illustration of three pillars for FPGAs as general-purpose accelerators<br>The challenge to quantify overheads of overlay architectures | 56<br>64                                               |

| High-level overview of the stereo-matching algorithm following [182] Illustration of cross-based cost aggregation regions               | 68<br>69                                               |

| Vectis accelerator card shown                                                                                                           | 74                                                     |

| Illustration of the Convey HC-1 platform                                                                                                | 75                                                     |

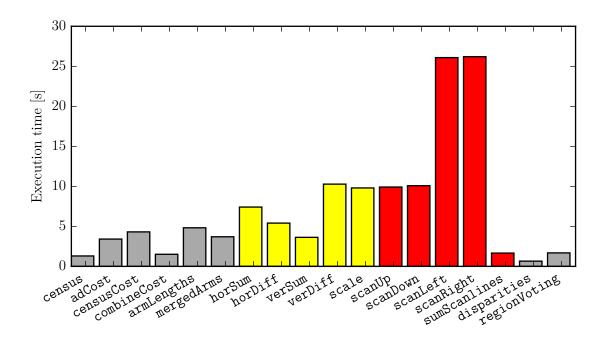

| CPU profiling on first system.                                                                                                          | 78                                                     |

| CPU profiling on second system.                                                                                                         | 79                                                     |

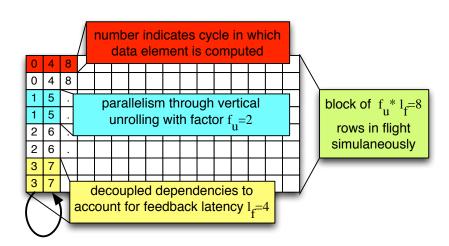

| Illustration of compute order in hardware kernel                                                                                        | 83                                                     |

|                                                                                                                                         | 84                                                     |

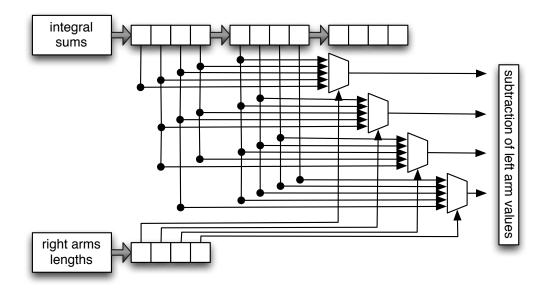

|                                                                                                                                         | 85                                                     |

|                                                                                                                                         | 86                                                     |

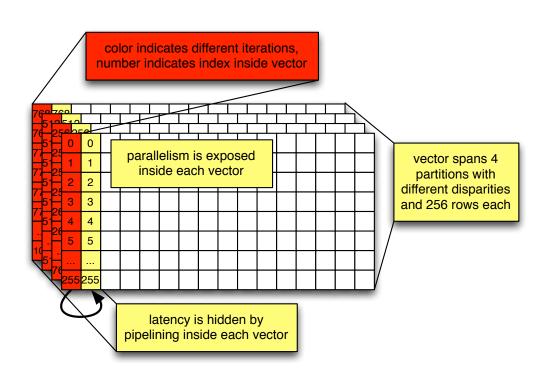

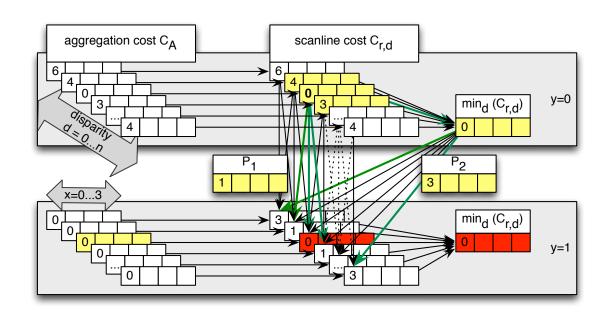

|                                                                                                                                         | 89                                                     |

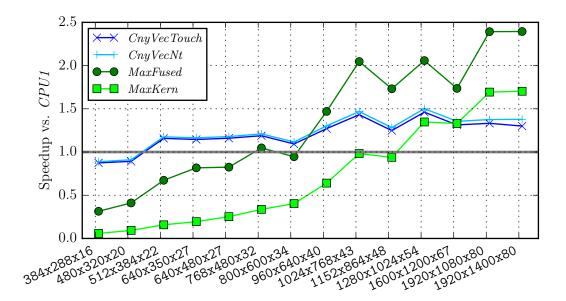

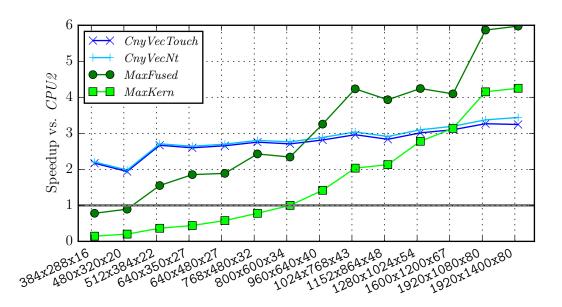

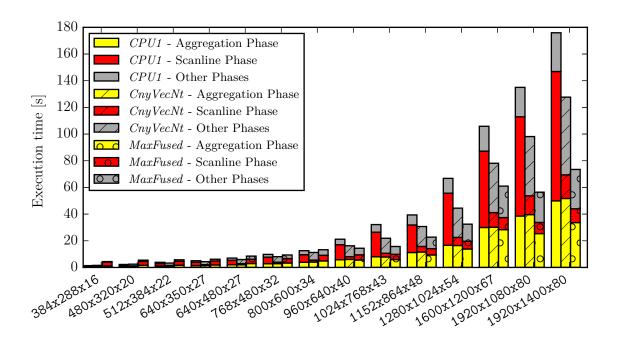

|                                                                                                                                         | 97                                                     |

|                                                                                                                                         | 97                                                     |

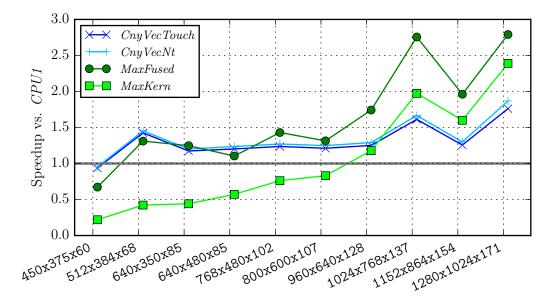

|                                                                                                                                         | 98                                                     |

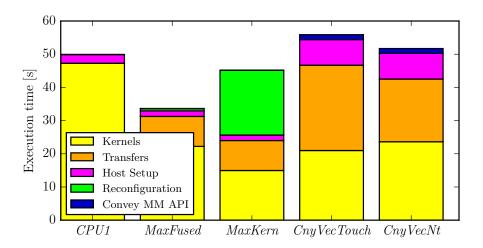

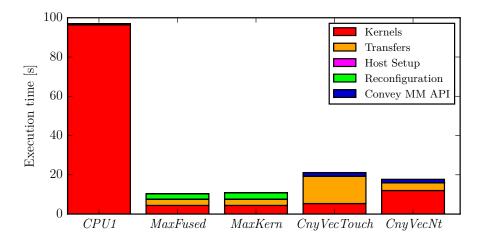

|                                                                                                                                         | 99                                                     |

|                                                                                                                                         |                                                        |

|                                                                                                                                         |                                                        |

|                                                                                                                                         |                                                        |

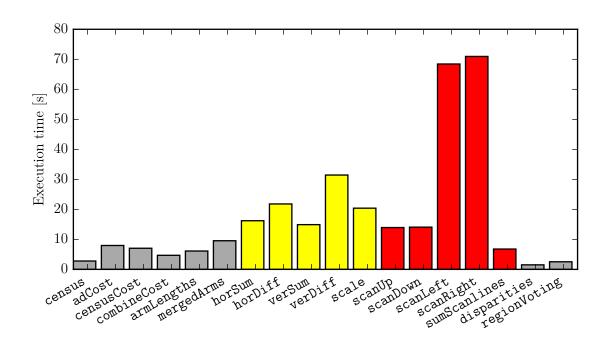

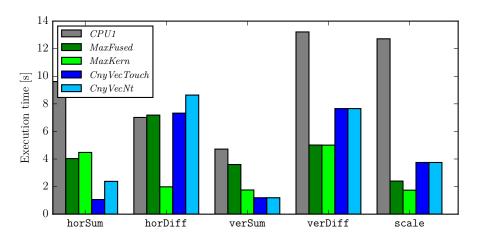

| Execution times of individual scanline kernels                                                                                          | 101                                                    |

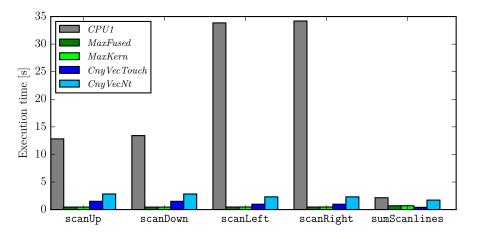

| Toolflow for generating heterogeneous binaries.                                                                                         | 116                                                    |

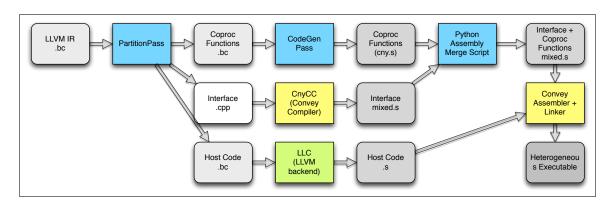

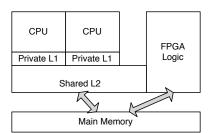

| Dual interface in an architecture with shared L2 and two private L1 caches.                                                             | 133                                                    |

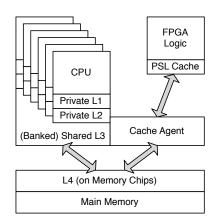

|                                                                                                                                         | 134                                                    |

| · · ·                                                                                                                                   |                                                        |

|                                                                                                                                         | Qualitative illustration of architecture efficiencies. |

| 6.4  | Illustration of POWER8 memory hierarchy with Coherent Accelerator Pro-               |

|------|--------------------------------------------------------------------------------------|

|      | cessor Interface (CAPI)                                                              |

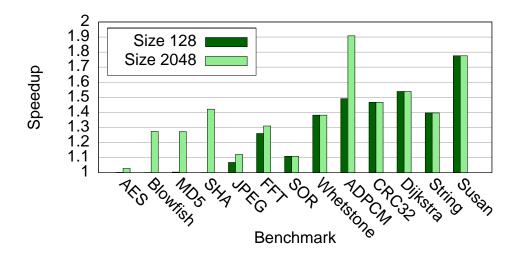

| 6.5  | Speedups for 13 benchmarks with two different accelerator sizes 143                  |

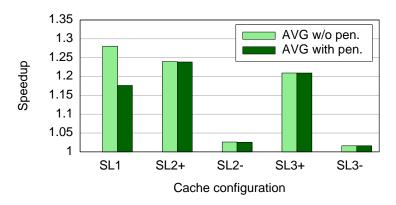

| 6.6  | Speedups for different memory integrations into a two level cache hierarchy. 145     |

| 6.7  | Speedups for different memory integrations into a three level cache hierarchy. $145$ |

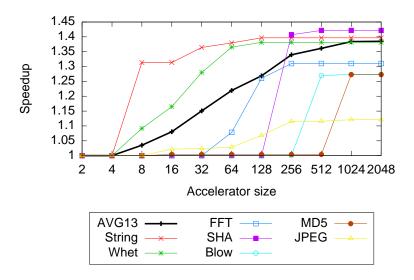

| 6.8  | Speedups for different accelerator sizes                                             |

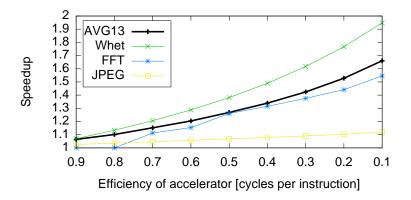

| 6.9  | Speedups for different accelerator execution efficiencies                            |

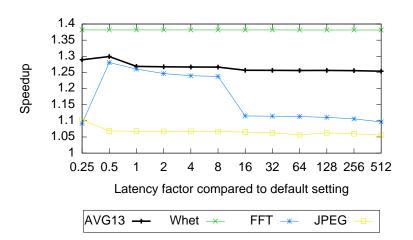

| 6.10 | Speedups for different interface latencies                                           |

## CHAPTER 1

## Introduction

In more than two decades of research on reconfigurable computing, academia and industry have shown that field programmable gate arrays (FPGAs) permit huge gains in performance and efficiency for a wide range of suitable applications through customization and exploitation of parallelism on different levels. However, current usage of FPGAs is mostly confined to individual and specific tasks, for which the FPGAs were selected as most suitable or most economic architecture. Even the first large scale deployment of FPGAs in a data center was driven by a single application scenario [213].

In this thesis, we argue that in the light of current architectural challenges in generalpurpose computing, FPGAs can play a much larger role in this domain. We identify current limitations and opportunities on this path, primarily in the area of productivity, but also with regard to system integration. We present original contributions in these two areas. In order to tackle productivity, we mainly propose and evaluate overlay architectures on FPGAs. With regard to system integration, we analyze design space options and compare our results to current trends.

In the remainder of this chapter, we first outline the motivation for this work in some more detail in Section 1.1. In Section 1.2, we lay out the contributions that this thesis makes towards general-purpose adoption of FPGAs and to specific technical challenges. In Section 1.3, we outline how the further thesis structure organizes these contributions.

### 1.1 Motivation

Computer architecture struggles to keep delivering ever more compute performance for growing and newly emerging workloads and markets. Well ahead of the eventual end of Moore's law [188], power limitations and diminishing returns from wider and more parallel processors are driving the need for architecture innovations. By reducing overheads and customizing parallelism, specialized accelerators help to efficiently increase the performance of specific workloads. However, without programmability, they lack the flexibility for general-purpose computing and thus can't profit from shared costs among different workloads, users and markets. The architecture of FPGAs combines programmability with a high potential for specialization for different workloads.

The main obstacle for FPGA adoption in general-purpose computing is the lack of productive formalisms and tools for designers and maintainers of implementations running entirely or partially on FPGAs. For specific workloads, where performance or efficiency targets could otherwise not be met, sophisticated designs for FPGAs have been developed with the corresponding effort [121]. In general-purpose computing, such effort typically cannot be spent, particularly not for a target architecture that is not yet established in a wide range of systems. FPGA manufacturers and community have invested lots of effort in improving the accessibility and productivity of programming models, languages and tools. In this thesis, we discuss three essential pillars that can trigger a break-through in FPGA adoption, focus on overlay architectures as insufficiently understood paradigm, and investigate which overheads and trade-offs they involve.

In order to fit into established computing systems and markets, FPGAs need to coexist and cooperate with general-purpose processors (GPPs). The architectural integration of central processing units (CPUs) and accelerators is not only a central factor for performance and efficiency, but also has a huge impact on the design productivity for such systems. Industry is actively pursuing the integration of specialized accelerators, graphics-processing units (GPUs) and recently also of FPGAs with GPPs. In this thesis, we analyze the potential of such integration and discuss how we can predict it, even though architectures and workload implementations closely depend on each other.

### 1.2 Contributions of this Thesis

In pursuit of the main focus of this thesis, we present the following high-level contributions to promote the adoption of reconfigurable accelerators, in particular FPGAs, in the domain of general-purpose computing.

- 1. Based on an analysis of architectures, markets and workloads, we identify opportunities for FPGAs in data center and cloud environments, in high-performance computing (HPC) and mobile computers.

- 2. We present our vision of a three-pillar approach to FPGA usage with, firstly, acceleratorfriendly Open Compute Language (OpenCL) specifications, secondly, overlay architectures to flexibly handle the trade-offs between productivity and performance of reconfigurable computing, and thirdly, libraries of reusable customized designs.

- 3. Further focusing on insufficiently understood characteristics of overlay architectures, we present the first broad quantification of the overheads of an instruction-programmable vector processor overlay architecture over fully customized kernel designs on FPGAs. For ten diverse kernels from a stereo-matching application, these overheads are on average in the range of 2.5x to 3x, which our experiments demonstrate to be small enough to still enable acceleration over GPPs.

- 4. We demonstrate that such an overlay architecture can serve as target for the desired fast and fully automated acceleration that existing tools didn't deliver.

- 5. In order to analyze the architectural integration of reconfigurable accelerators with CPUs, we present an estimation method that overcomes the interdependency of architectures and concrete implementations of workloads.

- 6. Based on this method, we give an overview of the design space of CPU-accelerator architectures that was insufficiently understood at the time of our publications.

Besides these high-level contributions, our work advances or complements the state-of-theart in several technical aspects.

- 1. By avoiding optimization-induced reductions of algorithmic quality, we present the most accurate FPGA-accelerated stereo-matching implementation published to date.

- 2. Through fully compatible scalable kernel implementations and a memory management wrapper library, it runs on two very different hardware platforms with different programming models.

- 3. With the systematic variation of kernel patterns and data layouts, we isolate the effects of outer-loop vectorization for the vector processor overlay architecture and find measurable, but small effects.

- 4. Integrating our automation methods into the LLVM<sup>1</sup> compiler infrastructure allows us not only to target different variants of compiled and source code, but also to reuse components for analysis and offloading.

- 5. For dynamic code analysis, we found an interesting opportunity space between offline profiling and deterministic offloading decisions at program runtime.

We have presented and published peer-reviewed results of this work in nine conference contributions, one workshop, and two journal articles. Tobias Kenter is main contributor and first author of six of these twelve publications, including the article in one of the two premier journals on reconfigurable computing [6]. The author's publications are summarized starting on page 160, in front of the main bibliography.

### 1.3 Thesis Structure

The remainder of this thesis broadly follows the sequence of high-level contributions summarized in the previous section. Chapter 2 starts with a general background on computing terms, concepts and architecture trends. It leads to an analysis of market opportunities of FPGAs in general-purpose computing. Chapter 3 complements its predecessor by comparing the productivity perspective of FPGAs with established general-purpose computing

<sup>&</sup>lt;sup>1</sup>http://llvm.org/

architectures. After introducing our three-pillar approach for FPGA usage in generalpurpose computing, we review existing research on overlay architectures, which is the specific pillar we focus on in this thesis. This concludes the focus on backgrounds and general analysis.

The following three chapters present original research on offloading to overlay architectures and to customized kernels and on system integration of reconfigurable accelerators. In Chapter 4, we present the overhead analysis of an instruction-programmable vector processor overlay architecture. For this purpose, we offload ten different kernels from a general-purpose stereo-matching application to the overlay architecture and alternatively to fully customized kernel-specific FPGA designs. In the following Chapter 5, we focus on the productivity aspect when targeting this overlay architecture. While existing tools required considerable developer efforts and yet had limited coverage of supported kernel patterns, we demonstrate that the specific features of the overlay architecture can be used to guide a fully automated offloading process with wide applicability.

In Chapter 6, we focus on the system integration of reconfigurable accelerators with CPUs. We present firstly an architecture model that allows reconfigurable acceleration at different granularities, secondly the method of our performance estimation that avoids mapping-specific predictions and thirdly the design space exploration results for CPU-accelerator architectures obtained with this method. Chapter 7 concludes this thesis and points at directions for future research.

## CHAPTER 2

## Computing Concepts, Trends and Domains

In this chapter, we present the required background for the vision of FPGAs as accelerators for general-purpose computing. Firstly, in Section 2.1 we introduce basic terminology of compute devices and outline basic concepts of such devices, including FPGAs, on the architectural level. So, from a high-level perspective, this section is centered around architectural foundations of how computation can be done. The deeper roots of how computation is done, that is the fundamentals of semiconductors and process technology are out of the scope of this work. However their changes over time are driving factors for past and current trends in architectures and devices, which are discussed in Section 2.2. Thirdly, Section 2.3 extends this background by discussing what kind of computation is done for different purposes and markets, along with some of their requirements. We focus on the domain of general-purpose computing, designated in the title of this thesis and in this context introduce the paradigm of On-The-Fly (OTF) Computing, which motivated large parts of this thesis. Besides data centers and cloud computing, HPC and mobile computers, we identify On-The-Fly (OTF) computing as promising, but particular challenging target for FPGA acceleration.

### 2.1 Compute Devices: Basic Terms and Concepts

In this section, we introduce basic concepts of computing and compute devices and along the way lay out the terminology used throughout this thesis.

In a general sense, a *computer* is a device that transforms information in a way that can be described in an algorithmic form. *Computation* is the direct action of transforming information performed by the computer, whereas the field of *computing* summarizes any "goal-oriented activity requiring, benefiting from, or creating computers" [252]. However, the term computer is often associated with a narrower meaning [271] that implies the presence of an instruction-programmable *processor*, also denoted as *central processing unit (CPU)* (see Subsection 2.1.2) and some *general-purpose computing* capabilities (see Subsection 2.3.1). In order to differentiate the more general computers that we discuss in this work form these narrower attributions, we denote them as *compute devices* or *compute systems*. The distinction of general-purpose devices to special-purpose or embedded systems is discussed in Subsection 2.3.1.

On the other hand, in the widest sense, computers encompass digital, analogue and even mechanical devices, whereas in this thesis, we restrict ourselves to synchronous digital compute devices implemented as integrated circuits. The basic elements of these digital circuits are transistors, which, arranged to elementary gates, implement basic logic functions on individual binary digits (bits). Inside a circuit, these bits are also denoted as signals, which after going through a sequence of combinatorial logic are stored in registers that keep their state until a clock signal triggers the register to assume the value of the input signal.

In the following Subsection 2.1.1, we continue the introduction of basic terms, here regarding target metrics of compute systems. In Subsection 2.1.2, we outline the basic concepts of computing with instruction-programmable processors and in Subsection 2.1.3 contrast them to concepts of computing in circuits. With FPGAs, a programmable architecture for computing in circuits is introduced in Subsection 2.1.4.

#### 2.1.1 Target Metrics

Compute systems execute tasks, that can be specified in the form of software or as circuits, or as a combination of both. In this subsection, we outline target metrics of such systems as used throughout this work and point to relations between these metrics. The general goal for compute systems is to achieve high performance at low costs, with low power and energy consumption and with a low design effort. Those goals often compete with each other and several of the metrics are interdependent or form combined metrics like efficiency.

There are three typical metrics to characterize *performance perf*: First, the *execution* time  $t_{exe}$  is the time to execute one specific task or benchmark. Second, the *latency*  $\lambda$  is the response time between a specific input and its resulting output. Third the *throughput*  $R = \frac{transactions}{s}$  is the rate at which similar tasks, in this context often denoted as transactions, are completed. Performance is proportional to the inverse of execution time *perf*  $\propto \frac{1}{t_{exe}}$  and proportional to the inverse of latency *perf*  $\propto \frac{1}{\lambda}$  but directly proportional to throughput *perf*  $\propto \frac{transactions}{[s]}$ . In synchronous devices, the performance depends on the clock frequency and the amount of work done per clock cycle.

When only a single task is executed at a time, the execution time is sufficient to characterize the performance a system, whereas for systems which execute more than one task in any form of concurrency, for example by pipelining, latency and throughput complement each other to characterize system performance. When comparing two different systems, a typical metric is speedup, which is the ratio of performance or execution times of the two systems. The speedup SU of a system  $S_{new}$  with regard to a reference system  $S_{old}$  is defined as  $SU = \frac{perf(S_{new})}{perf(S_{old})} = \frac{t_{exe}(S_{old})}{t_{exe}(S_{new})}$ . In the conceptual parts of this thesis, when discussing performance we will have all

In the conceptual parts of this thesis, when discussing performance we will have all of these metrics in mind unless any specific characteristic is highlighted. In our own experiments in Chapters 4 and 5, the tasks of our workload are executed sequentially and therefore we will evaluate performance solely with the means of total execution times.

The manufacturing *cost* of a compute system is a monetary metric that reflects a complex interplay of aspects like chip area, fabrication process, yield rates during fabrication, assembly costs of components into a system and all steps of the design process. For comparisons, it is often desirable to express cost as per device, but this depends a lot on the volume of devices produced, since some fraction of costs occurs per device, whereas fixed costs like for design and mask generation, often denoted as non-recurring engineering (NRE) cost, can be split among all devices produced. Additionally, the variable costs per device change through scale effects and maturity of the production process. In this thesis, we consider general cost aspects within the remainder of this chapter, but don't report upon the concrete costs of the systems we used for the experiments in the following chapters, because the costs of individual low volume systems sold for academic use hardly reflect the actual costs that such systems would have in any volume market.

The *power* of a compute system while performing a workload determines both the amount of electrical power that must be supplied to the system and the amount of thermal power that must be dissipated, in many systems through active cooling. Both cause additional costs beyond the acquisition costs of a device. Together, all of those costs are often summarized as total cost of ownership (TCO) over a specified amount of time. *Energy* is computed by the integration of power over time, in our context the time to complete a specific task or set of tasks. Thus, energy puts power in relation to performance. When comparing two systems, the system with higher power consumption may still use less energy to complete a task if it has a sufficiently higher performance. Similarly to the costs, power and energy are a concern in the conceptual parts of this thesis, but due to the different nature of our hardware platforms are not evaluated in our experiments in Chapters 4 and 5.

Although *area* contributes to the cost metric as chip surface area, it is often considered individually, frequently expressed through proxies like number of transistors in a chip or fractions of utilized FPGAs resources (see Subsection 2.1.4). In the general case, this allows to abstract away the concrete decision for a specific manufacturing process and enables cost estimations prior to actual chip production. Similarly, in the FPGA case, this allows with numbers obtained for one specific FPGA model to estimate whether a design may fit to another FPGA or how much headroom there is to add additional functionality to the same FPGA. We use such estimations in Chapter 4 of this thesis.

The term *efficiency* puts one of the presented performance metrics of a system in relation to its cost or one of the cost related metrics. Therefore, typical efficiency metrics are energy efficiency as  $\frac{perf}{energy}$ , cost efficiency as  $\frac{perf}{cost}$  and area efficiency as  $\frac{perf}{area}$ ; when discussing efficiency throughout this work, we have all of those in mind, unless specified otherwise.

When we further talk about *productivity* of a design approach or programming model for a system, we relate either some achieved performance or achieved efficiency, to the design effort, typically expressed in time spent. Since for a fair assessment of productivity the required amount of knowledge and experience needs to be taken into account, it is harder to quantify than the previous metrics. We discuss productivity issues in Section 3.1. Based on our comparison of two approaches in Chapter 4.7, we report upon the productivity we experienced during those experiments.

Finally, the *flexibility* to execute different tasks is an important characterization of a compute device. This aspect introduced in more depth in Subsection 2.3.1. Even though for each of the presented metrics a clear optimization goal exists, various trade-offs between different target metrics and different emphasis on either of the metrics are one contributing factor to the diversity of compute devices over time and now.

#### 2.1.2 Instruction-Programmable Processors

The concept of instruction-programmable computers, as the first class of compute devices presented here, goes back to the Von Neumann architecture [263], but has long evolved since the first draft from 1945. At its core, a CPU contains an arithmetic logic unit (ALU) that performs the actual computation, registers to hold operands for the ALU, and a control unit that manages the operation performed by the ALU as well as the operands to be used. The CPU is connected to a memory, where both instructions forming a program and data for the computation are stored. Additionally, an interface for external input and output is part of the concept of any computer.

Instructions can encode the operations to be performed by the ALU and specify the registers that hold the operands. Other instructions specify data movements between registers and memory. The control unit decodes an instruction and identifies the operands, triggers instruction execution for example by the ALU and determines the next instruction by updating a program counter. In the simplest and typically most common case, the program counter is just incremented, otherwise a specific control flow instruction needs to specify, how the program counter it is updated. The next instruction specified by the program counter is then fetched from memory.

The basic concept of instruction-programmable computers turned out to be extremely powerful because of the flexibility to express any kinds of computing tasks with programs made from instructions. However, it also imposes two major drawbacks: firstly, besides the actual computation performed, there is an overhead, caused for example by the instruction fetch and decode steps, by instructions that don't contribute to the actual computations, or by the repeated movement of operands from and to registers and memory. This overhead limits both performance and efficiency of computing with processors. Secondly, the sequentiality of instruction execution facilitates reasoning about program execution, but also limits performance when each instruction can only be executed after the previous one is finished. Within the remainder of this subsection, we present some mitigation strategies in the areas of instruction set architecture (ISA) design, memory hierarchies and parallelism that are employed in current processors, mostly with regard to performance bottlenecks. The alternatives presented in Subsections 2.1.3 and 2.1.4 on the conceptual level and with more concrete architectures in Subsection 2.2.3 often closely combine efficiency and performance aspects.

The area of ISA design investigates, which types of instructions a processor should be able to execute. In early times of computer architecture, there was a trend to design a high number of expressive instructions. Such expressive instructions can provide different ways to directly or indirectly encode operands in registers or memory, or designate special operations or groups of operations. With this approach, by getting more work done per instruction, the overhead of fetching and decoding each instruction can be mitigated and a compact program representation is achieved. In retrospective this strategy was denoted as complex instruction set computer (CISC), in contrast to the reduced instruction set computer (RISC) architecture, which was proposed in the 1980s [207, 208]. The latter concept proposes radically smaller and simpler instruction sets that allow memory operations only through explicit load and store instructions and have a fixed instruction size. This enables much simpler and smaller processor designs, which in turn allows to reduce the latency for executing each individual instruction. Another benefit, outside the processor itself, is that compilers can much easier generate efficient code for this type of architecture. In many contemporary GPPs, elements of both competing design approaches, CISC and RISC, have been combined.

Beyond this general distinction in ISA design approaches, a number of characteristic instruction set features have been developed to adapt processors to the needs of specific classes of tasks. For example, digital signal processors (DSPs) are optimized for signal processing applications and focus on data throughput in regular code. Microcontrollers on the other hand have very simple designs, optimized for control-dominant code and supporting only few and often slow arithmetic operations. These observations also point to the interplay of intended workloads and specialization that is an essential theme of this thesis and is more systematically approached in Section 2.3.1.

In order to supply a processor with instructions and to hold and supply most input, intermediate and output data, a word addressable memory is used. The fundamental challenge posed by such computer memory is that small amounts of memory can be made fast at the expense of area and power, whereas larger memory is slower. Therefore, a fundamental concept for memory design is that of a hierarchy, where the so-called main memory is typically designed to contain the entire program and data and two to four increasingly smaller and faster caches dynamically replicate transparently selected parts of the memory address space, so-called cache lines, for faster access. The processor registers form the fastest and smallest level of memory, but are typically not addressed like main memory and caches. At the other end of the hierarchy even larger and slower non-volatile storage like hard disks or flash are up to now not organized in data words, but in blocks and with file systems. The Von Neumann architecture's specific memory bottleneck is that both instructions and data are provided by the same memory and, which can lead to bandwidths limitations or contribute latency to the execution flow. This has been addressed by the Harvard architecture and modified Harvard architecture, which provides separate memory and interfaces for instructions and data. Most modern GPPs implement a modified Harvard architecture, where the main memory holds both instructions and data in a common address space, but separate first-level caches provide the processor with a distinct interface to each of them. Overall, modern memory hierarchies can provide good performance for many application scenarios, but contribute a significant fraction to the overall power consumption of the processors that use them.

After introducing ISA design and memory hierarchies, we now present three concepts of parallelism inside the area of instruction-programmable computers, that helped to mitigate the fundamental issue of program sequentiality over the the course of several decades, roughly following the structure and terminology of Hennesy and Patterson [118]. In the following Subsection 2.1.3 we outline how compute circuits that don't follow the basic principles of instruction-programmable processors may improve some of the aspects presented in this list.

• Instruction-level parallelism (ILP) occurs, when the correct execution of one specific instruction does not depend on the completed execution of all previous instructions from the instruction sequence of a program execution. This can be used to increase performance by executing several instructions in parallel or quasi-parallel. A compiler can increase the amount of exploitable ILP through instruction scheduling or loop unrolling. Scheduling can also be performed in hardware, then denoted as dynamic scheduling and allowing for out-of-order execution. The programmer is typically not involved in providing or exploiting ILP.

In order to execute independent instructions in parallel, which is also denoted as horizontal parallelism [216], a processor needs to contain several independent execution units, either identical or different. When the processor front-end is able to decode and issue multiple instructions per cycle, the architecture is denoted as superscalar. Superscalar architectures aim at getting more work done per cycle, expressed in terms of instructions per cycle (IPC). There are two main variants of superscalar architectures. In very long instruction word (VLIW) architectures, multiple instructions are scheduled together into a single instruction word by the compiler, whereas in dynamic superscalar architectures, the scheduling of independent instructions to parallel execution units is performed at runtime in hardware. In order to increase the usable ILP, speculation is frequently employed, that is instructions after a branch can be completely executed before the outcome of the branch is fully validated. If it turns out that the speculatively executed instructions should not have been executed, their outcomes are rolled back. Also, many dynamic superscalar architectures can reorder the sequence of instructions, delaying those instructions that need to wait for dependencies and forwarding those instructions that can already start independently of all currently executing ones. In order to maintain the correct program behavior in such out-of-order architectures, the results of all instructions go through reorder buffers in order to be committed in the correct order.

An orthogonal way to execute instructions partially in parallel is pipelining inside the processor. With pipelining, the process of executing a single instruction is split into several stages which overlap, for example while one operation is performed in the ALU, the next instruction is decoded and a third instruction can already be fetched from memory. Such pipelining is also denoted as a form of vertical parallelism. Since each stage can be completed faster than the entire sequence of stages required to execute an instruction, clock cycles are shorter, which increases throughput. However, pipelining does not increase the amount of work done per cycle, expressed as IPC. On the contrary, in order to retain the same IPC than without pipelining, firstly the sequence of instructions to be known soon enough to fetch and decode the right next instructions. In practice, branch prediction is used to make educated guesses about the outcome of control flow instructions, and can achieve prediction accuracies between 80% and more than 99% depending on its design and the benchmark characteristics. Secondly, when the pipelined instructions are not independent, the pipeline has to deal with data dependencies, which however can for example be tackled by data forwarding, from one pipeline stage, where an operand is computed to another stage where the same operand is used by a subsequent instruction. Thus, pipelining does not necessarily depend on the availability of true ILP, but is easier with it.

• Data-level parallelism (DLP) denotes a form of parallelism, where inside a program the same operation can be applied independently on different data elements. The primary source of such DLP are loops without dependencies between subsequent iterations, so that each instruction of the loop can simultaneously can be performed on the data of several different loop iterations. Parallelism between different loop iterations is also denoted as *loop-level parallelism (LLP)*. As indicated earlier, through loop unrolling LLP can also be used to generate ILP and in that case is not dependent on fully independent loop iterations.

The general concept of exploiting DLP is denoted as single instruction, multiple data (SIMD) [82]. In contrast to exploitation of ILP, SIMD concepts not only promise higher performance, but also better efficiency, because only a single instruction needs to be fetched and decoded in order to trigger several operations. Conceptually, DLP can often be automatically inferred, however efficient programs making use of DLP may still require considerable programmer interaction. This issue is also a subject of Chapter 5.

Vector computers are the classical computer architecture to exploit DLP. Vector computers hold many data elements that can be computed in parallel together in vector registers. A single vector instruction causes the same computation to be performed on all elements of those vectors, or on a subset of the elements specified through a bitmask. Computation on the different elements is performed in a pipelined manner, here employing pipelining to hide the latency of an individual operation. In addition, several vector lanes can work in parallel on different elements of the same vector. Important features of those vector computers' instruction set architectures are different methods for data transfers between memory and registers and the mentioned concept of masking operations for some vector elements. Such a vector architecture is used in Chapter 4 and targeted in Chapter 5.

A more recent way to exploit DLP is presented by SIMD instruction set extensions, sometimes marketed as multimedia instructions, that are integrated into many modern general-purpose (see Subsection 2.3.1) CPUs. In contrast to classical vector processors, their vectors registers typically contain less elements and their early incarnations contain a much less expressive instruction set. On the other hand, a typical feature of SIMD instruction set extensions is the ability to treat data in SIMD registers as differently sized types, that is either as a few elements of a large data type, e.g. 64 bit integer, or as more elements of a smaller type, e.g. 16 bit integer.

GPUs form a further group of instruction-programmable parallel architectures that makes havy use of DLP. Instead of using large vector registers, GPUs are predominantly organized into groups of processing cores, which all have a distinct register file, but execute the same instruction, thus sharing the involved fetch and decode overheads. This principle is also referred to as single instruction, multiple thread (SIMT). The roots of GPUs started as fixed function graphics accelerators, which over time first gained programmability for a more flexible graphics pipeline, and ended up being increasingly used to and designed for many other tasks with similar parallelism. In this thesis, GPUs are not investigated in the practical parts, but are considered in Sections 2.2.3, 2.3.1 and 3.1 as reference for a commercially successful accelerator architecture with a mix of programmability and specialization.

• Thread-level parallelism (TLP) is a form of parallelism, where multiple instructions from different program contexts can be executed in parallel, an execution mode denoted as multiple instruction, multiple data (MIMD) [82]. Following [118], we distinguish two different types of TLP: in *request-level parallelism*, different threads can work relatively independently on separate requests. In *parallel processing*, several threads closely collaborate on a single computational task. This is often achieved by transforming DLP into TLP and distributing parallel work items to different threads.

Considering only single-chip processors, two architectureal approaches to exploit TLP can be distinguished. In *multicore processors*, the entire structure of the CPU core, including control unit, registers and execution units like ALU, is replicated once or more times, so each core can work on a different thread independently. Often, parts of the cache hierarchy are shared among several cores in order to make collaboration between threads on different cores more efficient and in order to save some area. Systems where several identical processors or processor cores are connected through a common interface to a shared main memory are also denoted as symmetric multiprocessor (SMP) systems.

Other designs don't replicate entire CPU cores, but rather just some parts. In a widespread approach, the central register file and parts of the control unit are replicated to support the parallel or quasi-parallel execution of different threads, whereas the execution units are shared among these threads. We denote this approach as *hardware multithreading*. We choose this terminology to differentiate from the multithreading term in the operating system context, which can be realized by context switches on a single processing core. Comparing hardware multithreading to multicore processors, the shared resources are a way to save area, however they may also turn out to be a performance bottleneck, so the overall impact on area efficiency depends on architectural details and workloads.

| Symbol          | Meaning                                                           |

|-----------------|-------------------------------------------------------------------|

| Ra, Rb,         | General-purpose registers.                                        |

| RO              | Register with fixed value 0.                                      |

| <var></var>     | Location of a variable in memory.                                 |

| <imm></imm>     | Immediate operand that is encoded directly into an instruction.   |

| <label></label> | Marker in the instruction sequence that is used as branch target. |

**Table 2.1:** Symbols used by the instruction set for our example.

In hardware multithreading, the shared resources can be assigned to a different thread each clock in a round-robin way, skipping stalled threads (*fine-grained multithreading*), or only when the current thread incurs a costly stall like a cache miss (*coarsegrained multithreading*), or even dynamically within the same cycle (*simultaneous multithreading* (*SMT*)). In current processors, either fine-grained multithreading or SMT can be observed, whereas GPU architectures rely only on fine-grained multithreading. [118]

The effectiveness of all these concepts of parallelism depends on the fraction p of a task that can actually make use of this parallelism and on the remaining fraction 1 - p that for some reason remains sequential. Following Amdahl's law, when the parallel fraction pof the task achieves a parallel speedup  $SU_{max}$ , the speedup SU of the entire task can be computed as  $SU = \frac{1}{(1-p)+\frac{p}{SU_{max}}}$ . This means that in practice, both the maximal available parallelism  $SU_{max}$  in the parallel parts of the task and the fraction of sequential parts of a task put hard limits to the achievable speedups.

In this subsection, fundamental concepts of instruction-programmable processors have been introduced from a performance-centric perspective. In this spirit, current GPPs combine essentially all these concepts and more, in order to deliver good performance for any type of application. However, the means to mitigate performance issues of the Von-Neumann-based processor architecture don't necessarily improve efficiency, most of them leaving the general overhead of instruction fetch and decode unaffected and adding additional control logic that requires power and space. In this sense, the customizations of the briefly mentioned DSP and Microcontroller classes are to a large degree a reduction of features in order to improve efficiency. Microcontrollers are very simple and efficient designs, because they intentionally neglect arithmetic performance and data throughput, whereas DSPs with their focus on regular control flow can, for example, with zero-overhead loops reduce the number of executed instructions and at the same time reduce the need for sophisticated branch prediction. We illustrate computing with instruction-programmable processors with an example, before in the following subsection, discussing a computing approach that takes this customization much further.

| Instruction                 | Meaning                                                                                                    |  |  |  |  |  |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| LD <var>(Ra), Rb</var>      | Load into Rb a value from the memory location of variable <var>, modified by an offset value in Ra.</var>  |  |  |  |  |  |  |

| ST Ra, <var>(Rb)</var>      | Store the value of Ra into the memory location of variable <var>, modified by an offset value in Rb.</var> |  |  |  |  |  |  |

| ADD Ra, \$ <imm>, Rb</imm>  | Add <imm> to value from Ra and put the result into Rb.</imm>                                               |  |  |  |  |  |  |

| ADD Ra, Rb, Rc              | Add value from Rb to value from Ra and put the result into Rc.                                             |  |  |  |  |  |  |

| BLE Ra, Rb, <label></label> | Branch to label, if the value in Ra is less than or equal to the value in Rb.                              |  |  |  |  |  |  |

| BLT Ra, Rb, <label></label> | Branch to label, if the value in Ra is less than the value in Rb.                                          |  |  |  |  |  |  |

Table 2.2: Selection of instructions for a RISC-like instruction set for our example.

#### Introducing an Example

With an example, we want to illustrate some aspects of computing with instructionprogrammable processors. We focus on some simple instruction set properties and on what we call instruction overheads. We extend this example in the following subsections to alternative approaches.

To outline a processor architecture for this example, we first introduce, based on a few basic symbols (Table 2.1), some instructions for a rudimentary instruction set in Table 2.2. The separation of memory instructions (load and store) and arithmetic instructions (and logic instructions not included here) is typical for a RISC architecture. The format of the memory instructions with a variable name and an offset register follows one of the addressing modes from the simple target machine model introduced in [15] and also shows up in the base instruction set of the instruction-programmable coprocessor that we target in Chapters 4 and 5. Eventually, during machine code generation, the compiler needs to replace the variable names by actual memory addresses, either in the *static* data area or in the *stack* data area. As branch instructions, we chose a pair of instructions that allows us to write the following example in a most comprehensible way.

With this instruction set, it is possible to execute a brief code snippet that is a simplified part of the real code used later in Chapters 4 and 5. Listing 2.1 shows the code snippet that sums up an input array in and stores the running sums into an output array sum. Listing 2.2 shows an instruction sequence that can execute this code snippet with the instruction set from Table 2.2. In order to keep the example simple, we omitted to specify different data word formats and assume a single, 32-bit (4-byte) integer data type. An important optimization that is included in this instruction sequence is the reuse of sum[x] values from the previous iteration as new value sum[x-1] in R4. By transforming the loop bounds, it would also be possible to remove one of the increment instructions (Lines 7, 8) inside the loop body, but we omitted this for better readability of the example.

```

1 for(int x=1; x<width; x++)

2 sum[x] = sum[x-1] + in[x];</pre>

```

Listing 2.1: Code snippet computing and storing running sums of an input array.

```

1

ADD RO, $1, R1

##

init loop counter x to 1

2

LD

(width)(RO),

R2

##

load loop limit

BLE R2, R1, exit

3

##

branch to exit if width <= 1

4

ADD RO, $0, R3

##

init array offset to O

LD

(sum)(R3), R4

##

load sum[0] into R4

5

6

loop:

7

ADD R3, $4, R3

increment array offset (4 byte word)

##

ADD R1, $1, R1

8

##

increment loop counter x

9

LD

(in)(R3), R5

##

load in[x]

10

ADD R4, R5, R4

##

compute new sum[x]

in R4

11

ST

R4, (sum)(R3)

##

store R4 to sum[x]

12

BLT R1, R2, loop

## branch to loop entry if x < width

13

exit:

```

**Listing 2.2:** Assembly code program for the code snippet in Listing 2.2. The actual work of the code snippet is performed in Lines 9-11.

When investigating this code sequence, one can argue that the instructions in Lines 7 to 9 perform the actual work of loading a new input value, adding it to the running sum, and storing it to the result location, whereas the other instructions are a form of overhead that is required to achieve this functionality. Other instruction sets aim to reduce such overheads. For example with a typical DSP ISA, one would replace the instructions in Lines 8 and 12 by instructions before the loop body to set up a zero-overhead loop. The ISA would also support special addressing modes making the instruction in Line 7 superfluous. A typical CISC-like feature present for example in the x86 ISA are arithmetic instructions from Lines 9 and 10 by a single one. Like DSP ISAs, the x86 ISA also has addressing modes that allow to remove the instruction in Line 7. With such approaches, less instructions need to be fetched from program memory. However, inside x86 processors, such expressive instructions often get split again into several so-called micro-operations and thus internally require similar resources and time as the illustrated instruction sequence.

As platform to further illustrate the execution of the loop body from this instruction sequence on an instruction-programmable processor, we use a classic five-stage RISC pipeline like outlined in [118], with the following pipeline stages.

- **Instruction Fetch (IF)** This stage fetches the instruction that is currently indicated by the program counter from memory. It also increments the program counter.