FAKULTÄT FÜR Elektrotechnik, Informatik und Mathematik

# Digital Control for Interleaved Boost Power Factor Correction (PFC) Rectifiers

Von der Fakultät für Elektrotechnik, Informatik und Mathematik der Universität Paderborn

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften (Dr.-Ing.)

genehmigte Dissertation

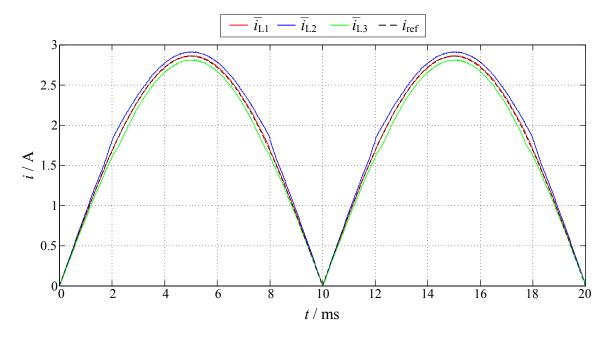

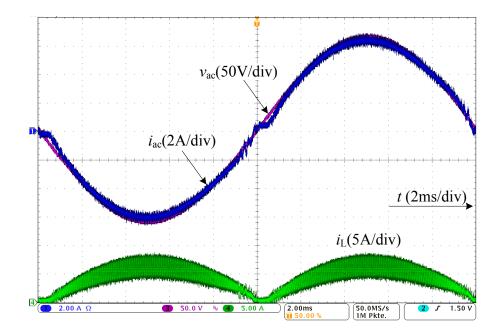

von

Dipl.-Ing. Tobias Grote

Erster Gutachter: Prof. Dr.-Ing. Joachim Böcker Zweiter Gutachter: Prof. Dr.-Ing. habil. Jürgen Petzoldt

Tag der mündlichen Prüfung: 11.04.2014

Paderborn 2014

Diss. EIM-E/304

» Flick of the switch « AC/DC

## Vorwort

Diese Arbeit entstand während meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Fachgebiet "Leistungselektronik und Elektrische Antriebstechnik (LEA)" an der Universität Paderborn, wobei große Teile in enger Zusammenarbeit mit der Delta Energy Systems (Germany) GmbH entstanden sind.

An dieser Stelle möchte ich den zahlreichen Menschen danken, die zum Gelingen dieser Arbeit beigetragen haben. Mein besonderer Dank gilt Herrn Prof. Dr.-Ing. Joachim Böcker für die Betreuung dieser Arbeit. Herrn Prof. Dr.-Ing. habil. Jürgen Petzoldt danke ich für die Übernahme des Korreferats.

Für die sehr angenehme und kollegiale Arbeitsatmosphäre am Fachgebiet LEA möchte ich mich bei allen ehemaligen Kollegen und vor allem bei Dr.-Ing. Norbert Fröhleke bedanken. Ferner bedanke ich mich bei den Kollegen der Delta Energy Systems (Germany) GmbH für die gute Zusammenarbeit und wertvolle Unterstützung. Ein besonderer Dank gilt Dr.-Ing. Frank Schafmeister für die vielen konstruktiven Anregungen und fruchtbaren Diskussionen.

Im Rahmen ihrer Studien- und Diplomarbeiten haben Dipl.-Ing. Sven Bolte und Dipl.-Ing. Dominik Schmies wertvolle Beiträge zum Gelingen der Arbeit geleistet. Ihnen gebührt mein Dank. Ein besonderer Dank gilt auch Dr.-Ing. Christian Henke für das sorgfältige Korrekturlesen meiner Arbeit.

Von ganzem Herzen bedanke ich mich bei meinen Eltern und meiner liebsten Maren für die Unterstützung und das Vertrauen in mich.

*Tobias Grote* Köterberg, im April 2014

## Abstract

Rectifiers with low power factor cause line interferences due to harmonics in the line current and reactive power and therefore reduce the power available from the grid. For this reason power factor correction (PFC) rectifiers have been established as front end stage of AC-DC converters, which should emulate a resistor on the supply side while providing a fairly regulated DC output voltage. Widely utilized topology for this purpose is a boost converter together with a diode rectifier. In order to increase the power level and to reduce the high-frequency interferences it is common to operate two or more boost converters in parallel with phase shifted switching cycles.

For those interleaved boost PFC rectifiers three different control tasks must be achieved at the same time:

- The inner current control loop needs to achieve nearly unity power factor by forcing the input current to track the shape of the sinusoidal line voltage as close as possible.

- The outer voltage control loop has to maintain a nearly constant DC output voltage.

- The current balancing control must ensure equal rail power for the paralleled converters.

Realization of these complex control tasks for interleaved boost PFC rectifiers was dominated by analog technique for many years. Due to cost-efficient digital signal processors (DSP) and microcontrollers ( $\mu$ C) with increased computational power and appropriate peripherals, digital control is widely used in PFC applications nowadays.

With applying digital control a multitude of benefits such as flexibility and programmability, decreased number of active and passive components, and as a consequence improved reliability, negligible and/or compensable offsets and thermal drifts arise. However, full digital control is not the panacea for all PFC applications. Sometimes it can be beneficial to retain some parts of the PFC control in analog technique, smartly combined with digital control parts.

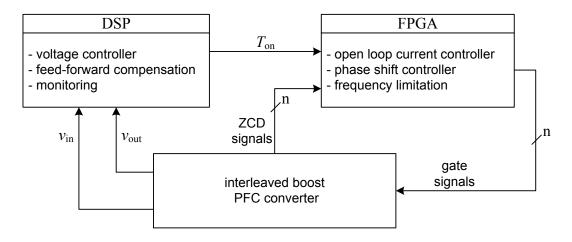

The purpose of this dissertation is the utilization of digital control for interleaved boost PFC rectifiers. After providing basic information regarding the converter topology, digital control loops and state of the art PFC control, four advanced control concepts utilizing digital control are presented:

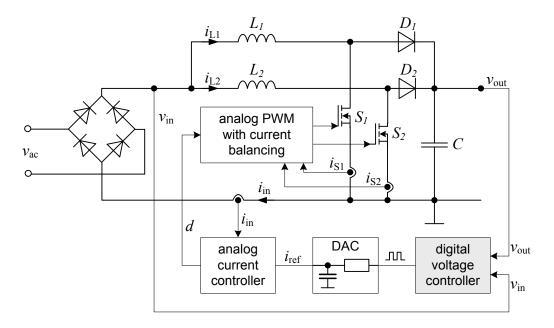

- In a semi-digital PFC control concept analog and digital control parts are smartly combined. High bandwidth control parts like the current controller as well as time-critical protection functions retain in conventional analog technique. Whereas the slow voltage compensator, load feed-forward control, multiplier and non-time-critical protection functions are implemented in the digital control part.

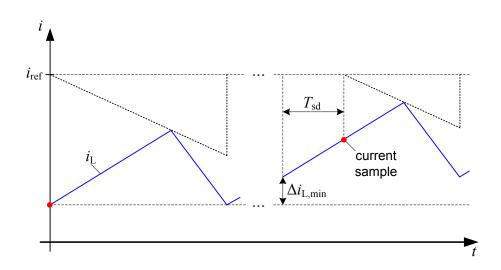

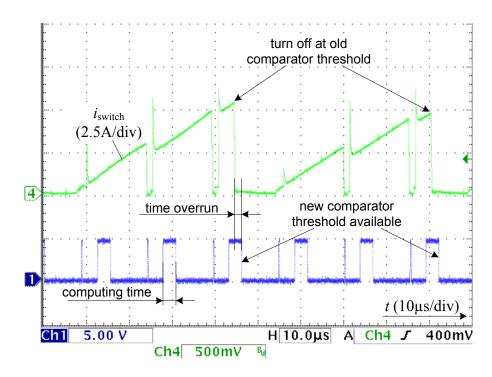

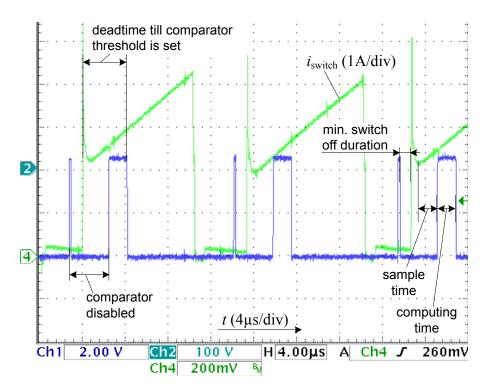

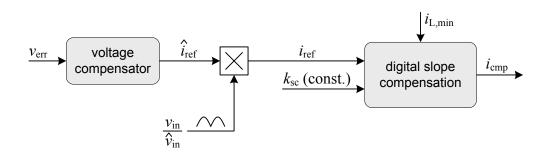

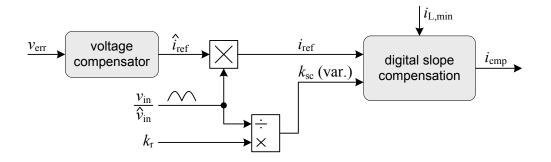

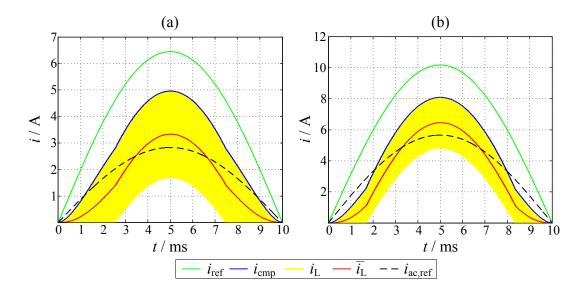

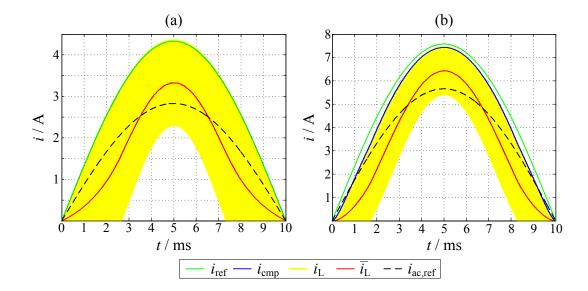

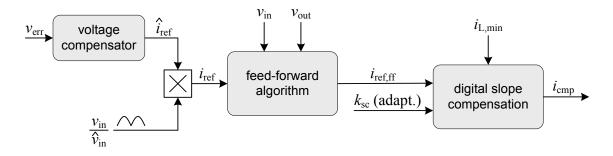

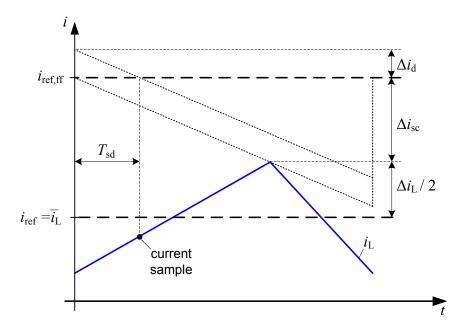

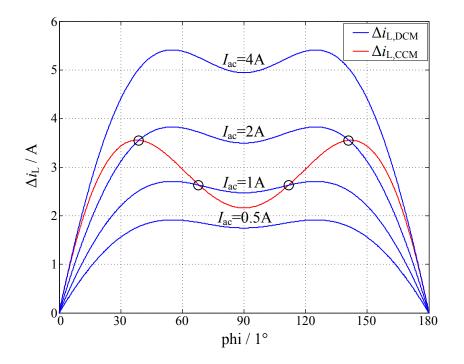

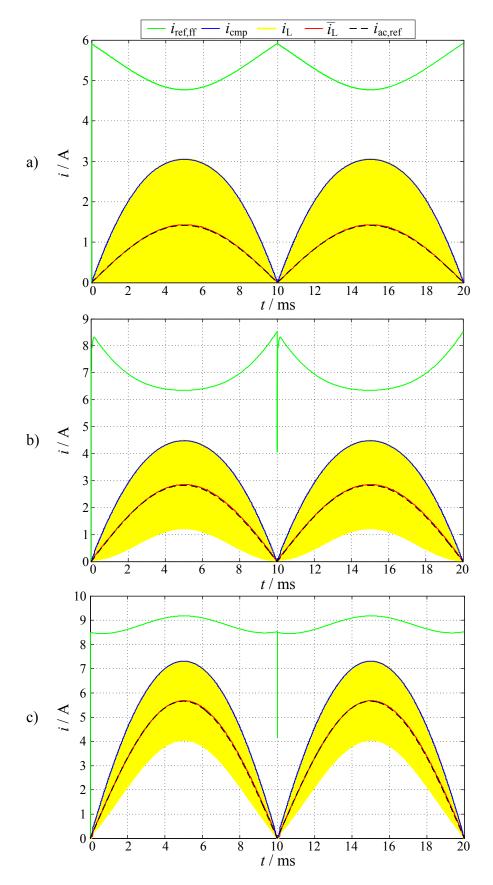

- By using DSPs or  $\mu$ Cs containing analog on-chip comparators, digital peak current control is basically feasible with little effort. In order to eliminate the drawbacks of peak current control, a digital slope compensation is introduced which does not use an analog ramp signal, but instead an algorithm to pre-calculate the desired

comparator switch-off threshold. Adaptive algorithms are employed to adjust the compensation and to ensure sinusoidal shape of the average inductor current.

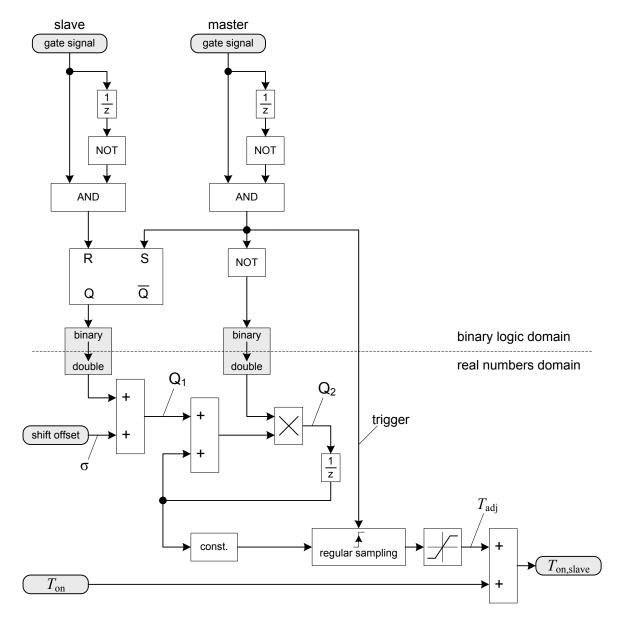

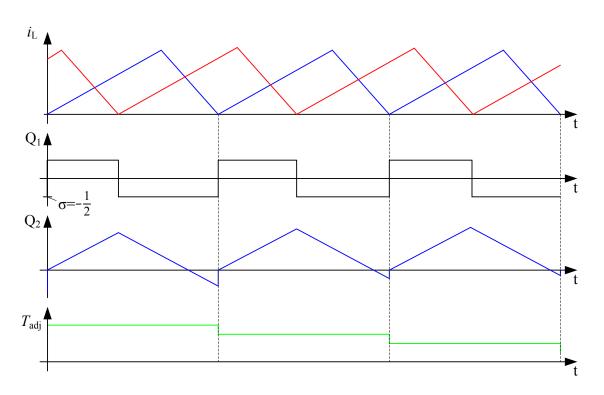

- For PFC converters operating in boundary conduction mode (BCM) interleaving of several converters is challenging, because of the variable switching frequency. The introduced digital phase shift control enables multi-rail interleaving. With the flexibility of the digital implementation it is possible to apply phase shedding and limit the switching frequency by maintaining optimal interleaving.

- Multi-rail interleaving of PFC converters operating in BCM and DCM is realized by a feed-forward control. The feed-forward algorithm can be applied alone as open-loop control without the requirement of any current measurement or together with a parallel current controller in a closed-loop version. With adjustable DCM ratio an additional degree of freedom results, which can be used to improve the performance in different ways. The switching losses can be reduced at light load and even within a line half cycle or the switching frequency can be kept within a narrow band. A promising method is introduced which tracks the DCM ratio for every operating point in order to minimize the THD in the input current.

The introduced innovations on digital control provide additional functionality for interleaved PFC rectifiers and improve the performance in different categories. The investigations have shown that digital control is not a general solution for enhanced performance. Often it is beneficial to combine digital control with suitable analog parts such as analog comparators.

# Zusammenfassung

Netzgleichrichter mit nicht-sinusförmiger Stromaufnahme verursachen Oberschwingungen im Eingangsstrom, welche die Netzqualität beeinträchtigen und die verfügbare Eingangsleistung reduzieren. Aus diesem Grund besitzen moderne elektronische Stromversorgungen eingangsseitig eine netzfreundliche Pulsgleichrichterstufe (PFC), die einen hohen Leistungsfaktor gewährleisten, so dass sich die Geräte im Idealfall wie ein ohmscher Widerstand am Netz verhalten. Zusätzlich zu der sinusförmigen Stromaufnahme muss die Eingangswechselspannung in eine möglichst konstante Gleichspannung gewandelt werden. Für diesen Zweck wird überwiegend die Topologie des Hochsetzstellers mit vorgeschaltetem Brückengleichrichter eingesetzt. Zur Erhöhung der Geräteleistung und um die schaltfrequenten Störanteile im Eingangsstrom zu reduzieren werden üblicherweise zwei oder mehr Hochsetzsteller parallel betrieben und phasenversetzt angesteuert.

An die Regelung solcher parallel betriebenen, netzfreundlichen Pulsgleichrichterstufen ergeben sich hohe Anforderungen. Gleichzeitig müssen drei verschiedene Regelungsaufgaben bewältigt werden:

- Die innere Stromregelschleife muss einen möglichst idealen Leistungsfaktor gewährleisten, indem der Eingangsstrom der sinusförmigen Netzspannung nachgeführt wird.

- Mit der äußeren Spannungsregelschleife soll am Ausgang eine möglichst konstante Gleichspannung bereit gestellt werden.

- Eine geeignete Stromsymmetrierung wird benötigt, um eine gleichmäßige Leistungsaufteilung auf alle parallel betriebenen Konverter zu erzielen.

Die Umsetzung dieser komplexen Regelung wurde seit vielen Jahren von analoger Schaltungstechnik dominiert. In den letzten Jahren sind digitale Signalprozessoren (DSP) und Mikrocontroller ( $\mu$ C) stetig leistungsstärker und kostengünstiger geworden und besitzen für die Schaltnetzteilregelung speziell ausgelegte Peripherie. Aus diesem Grund kommen heute häufig digitale Regelungen für PFC Anwendungen zum Einsatz. Dies bringt eine Reihe zusätzlicher Vorteile mit sich. Durch die Implementierung adaptiver Regelungen und komplexer Vorsteueralgorithmen erhöht sich die Flexibilität und Leistungsfähigkeit der Geräte. Die Anzahl der aktiven und passiven Bauelemente verringert sich und mögliche Offsets und Temperaturabhängigkeiten können kompensiert werden.

Allerdings ist die Implementierung einer volldigitalen Regelung nicht immer die optimale Lösung für netzfreundliche Pulsgleichrichterstufen. Für einige Anwendungen ist es vorteilhaft, nur einige Teile der Regelung digital zu realisieren und mit analogen Komponenten zu ergänzen.

Die vorliegende Arbeit beschäftigt sich mit digitalen Regelungsstrategien für parallel betriebene, netzfreundliche Pulsgleichrichterstufen. Zunächst werden die grundlegenden Eigenschaften der Konvertertopologie und digitaler Regelschleifen behandelt. Nach der Betrachtung analoger PFC Regelungen und dem Stand der Technik bei digitalen PFC Regelungen werden vier neuartige Regelungskonzepte vorgestellt, bei denen Teile oder die komplette Regelung auf einem DSP oder  $\mu$ C implementiert sind:

- Bei dem semi-digitalen Regelungskonzept sind die Regelungsaufgaben sinnvoll auf digitale und analoge Teile gesplittet. Dort wo hohe Bandbreite gefordert ist, z.B. Stromregler und zeitkritische Schutzfunktionen kommen die herkömmlichen analogen Schaltkreise zum Einsatz. Die langsame Spannungsregelung, der Multiplizierer zur Generierung des Stromsollwerts, die Eingangsleistungsvorsteuerung und nicht zeitkritische Schutzfunktionen sind auf einem kostengünstigen μC implementiert.

- Mit DSPs und µC mit auf dem Chip integrierten analogen Komparatoren lässt sich ohne großen Aufwand eine digitale Spitzenstromregelung realisieren. Um die Nachteile der Spitzenstromregelung zu eliminieren, wird eine sogenannte Slope-Kompensation benötigt. Anstelle einer analogen Sägezahn-funktion wurde für die digitale Implementierung ein Algorithmus entwickelt, der direkt die erforderliche Komparatorabschaltschwelle zu Beginn jeder Schaltperiode berechnet. Mit weiteren adaptiven Algorithmen lässt sich zum einen die Slope-Kompensation für jeden Arbeitspunkt anpassen und zum anderen der Mittelwert des Eingangsstroms der sinusförmigen Eingangsspannung nachführen.

- Beim Parallelbetrieb mehrerer Konverter an der Lückgrenze ist das Einstellen der optimalen Phasenverschiebung aufgrund der variablen Schaltfrequenz sehr schwierig. Die Implementierung einer digitalen Phasenwinkelnachführung ermöglicht das Einhalten der optimalen Phasenverschiebung mit hoher Dynamik. Durch gezieltes lastabhängiges zu- oder abschalten einzelner Konverter wird zusätzlich die maximale Schaltfrequenz begrenzt.

- Der synchrone Parallelbetrieb an der Lückgrenze oder im Lückbetrieb lässt sich auch ausschließlich mittels Vorsteuerung erreichen, der keine Strommessung benötigt. Mit optionaler Eingangsstrommessung und einem Stromregler parallel zur Vorsteuerung kann der Konverter auch mit geschlossenem Regelkreis betrieben werden. Der Vorsteueralgorithmus bietet aufgrund der einstellbaren Länge des Lückintervalls einen zusätzlichen Freiheitsgrad, mit dem sich die Betriebsweise der PFC Stufe in verschiedenen Bereichen optimieren lässt. So kann die Schaltfrequenz damit innerhalb vorgegebener Grenzen gehalten werden. Durch Absenkung der Schaltfrequenz in Abhängigkeit der Ausgangsleistung und dem Augenblickswert der Eingangsleistung können die Schaltverluste reduziert werden. In einem weiteren Anwendungsfall wird das variable Lückintervall genutzt, um in jedem Arbeitspunkt die gesamten harmonischen Verzerrungen (THD) zu minimieren.

Mit den entwickelten digitalen Regelungsstrategien ergeben sich zusätzliche Möglichkeiten für die Betriebsführung, mit denen sich die Leistungsfähigkeit von netzfreundlichen Pulsgleichrichterstufen steigern lässt. Die Untersuchungen haben aber auch gezeigt, dass eine digitale Realisierung kein Patentrezept für eine Steigerung der Leistungsfähigkeit ist. Oftmals ergibt sich erst durch die Kombination digitaler Regelung mit analogen Komponenten wie Komparatoren das optimale Regelungskonzept.

# Contents

| 1 INTRODUCTION                                        |                 |

|-------------------------------------------------------|-----------------|

| 2 BASICS OF BOOST POWER FACTOR CORR                   | ECTION          |

| RECTIFIER                                             | 5               |

| 2.1 PFC in Distributed Power Systems (DPS)            |                 |

| 2.2 Boost PFC Rectifier                               | 7               |

| 2.3 Interleaving                                      | 9               |

| 2.4 Boost Converter Basics                            |                 |

| 2.4.1 Operation Modes                                 |                 |

| 2.4.2 Control Methods                                 |                 |

| 2.4.2.1 Voltage mode control                          |                 |

| 2.4.2.2 Current mode control                          |                 |

| 2.4.3 Modeling of the Boost Converter                 |                 |

| 2.5 Current Control Design                            |                 |

| 2.6 Voltage Control Design                            |                 |

| 2.7 Multiplier and Load Feed-Forward Control          |                 |

| <b>3</b> DIGITAL CONVERTER CONTROL                    |                 |

| 3.1 Analog to Digital Conversion (ADC)                |                 |

| 3.1.1 Sampling Process                                |                 |

| 3.1.2 Quantization                                    |                 |

| 3.2 Digital Pulse Width Modulation (DPWM)             |                 |

| 3.3 Digital Controller                                |                 |

| <b>4</b> STATE OF THE ART OF INTERLEAVED PFO          | C RECTIFIER     |

| CONTROL                                               |                 |

| 4.1 Review of Analog PFC Control                      |                 |

| 4.2 Full Digital Average Current Mode PFC Control     |                 |

| 4.2.1 Sample Correction in DCM                        |                 |

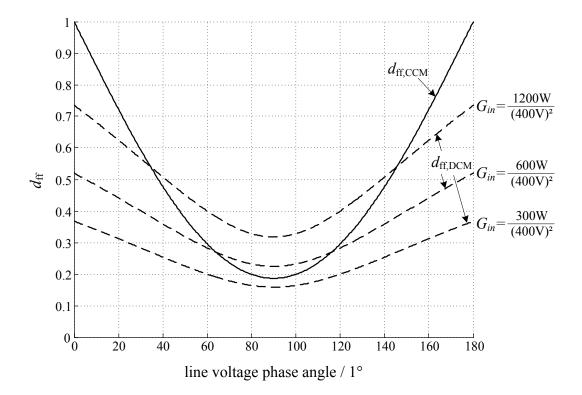

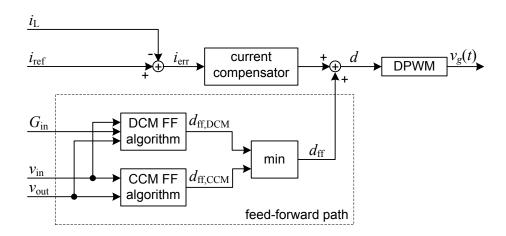

| 4.2.2 Duty-Ratio Feed-Forward Control for CCM and DCl | М 48            |

| 5 SEMI-DIGITAL PFC CONTROL (MIXED SIG                 | NAL CONTROL) 51 |

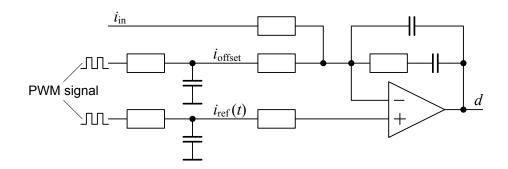

| 5.1 Control Structure                                 |                 |

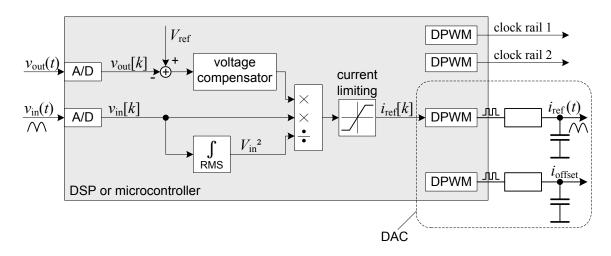

|   | 5.2   | Digital Control Implementation                       | 53  |

|---|-------|------------------------------------------------------|-----|

|   | 5.2.1 | Voltage Control, Multiplier and Feed-Forward         | 53  |

|   | 5.2.2 | PWM Clock                                            | 54  |

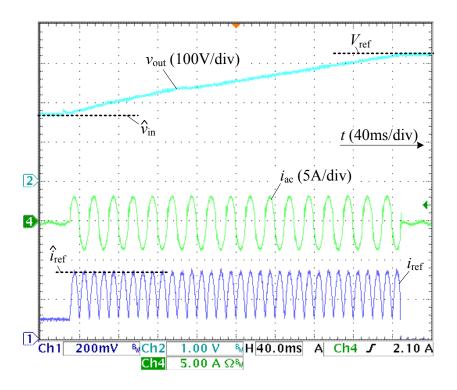

|   | 5.2.3 | 8 Soft Start-Up                                      | 56  |

|   | 5.2.4 | Power Management Features                            | 56  |

|   | 5.3   | Summary                                              | 59  |

| 6 | DIC   | GITAL PEAK-CURRENT MODE CONTROL FOR PFC              |     |

| R | ECTI  | FIERS                                                | 61  |

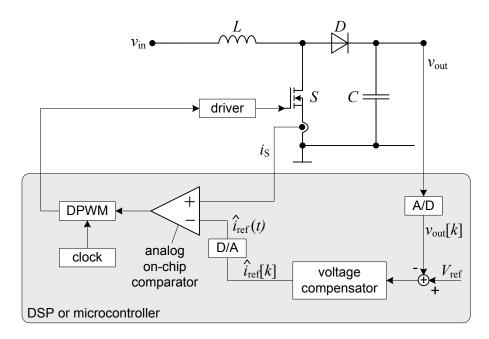

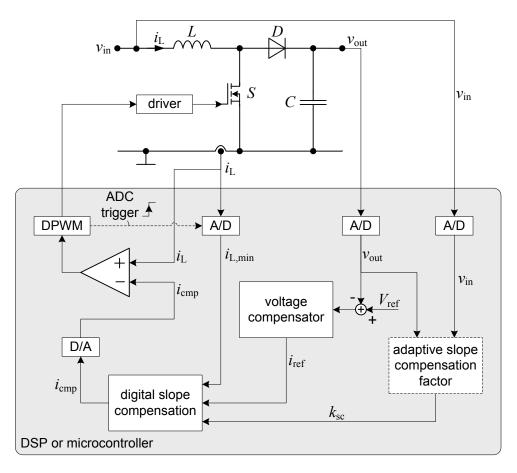

|   | 6.1   | Control Structure with On-Chip Comparators           | 61  |

|   | 6.2   | Digital Slope Compensation                           | 62  |

|   | 6.3   | Special Effects and Measures for Reliable Operation  | 68  |

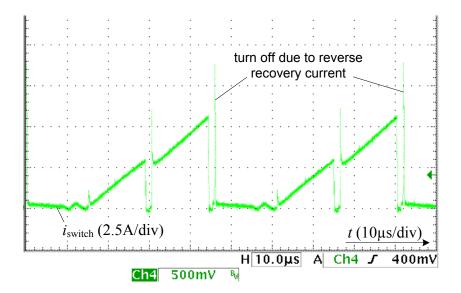

|   | 6.3.1 | How to Handle the Reverse Recovery Current           | 68  |

|   | 6.3.2 | 2 Timing                                             | 69  |

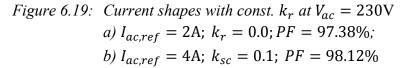

|   | 6.4   | Digital Peak Current Control for PFC Application     | 71  |

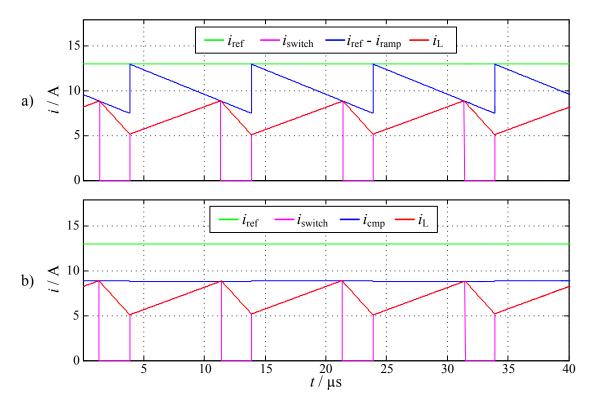

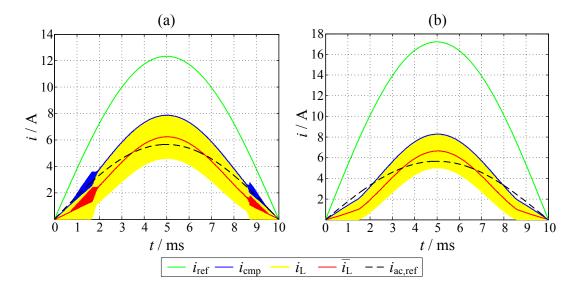

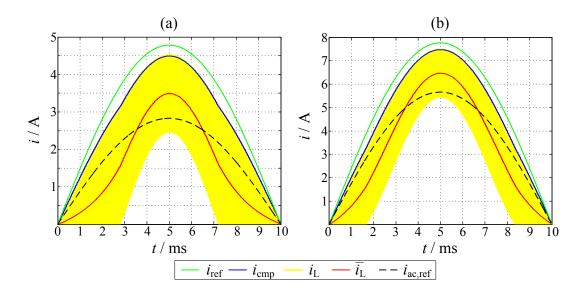

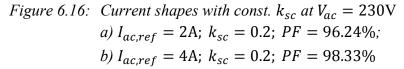

|   | 6.4.1 | Constant Compensation Factor                         | 72  |

|   | 6.4.2 | 2 Constant Compensation Ramp                         | 74  |

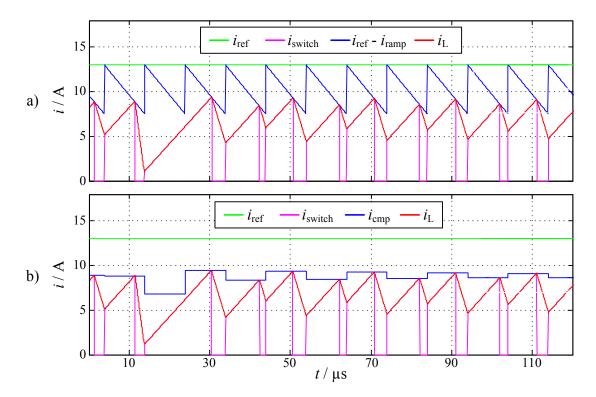

|   | 6.4.3 | B Feed-Forward Algorithm                             | 76  |

|   | 6.4.4 | Outer Average Current Controller                     | 82  |

|   | 6.4.5 | Interleaved Operation                                | 88  |

|   | 6.4.6 | Measurements                                         | 90  |

|   | 6.5   | Summary                                              | 93  |

| 7 | DIC   | GITAL BOUNDARY CONDUCTION MODE (BCM) PFC             |     |

| C | ONTI  | ROL                                                  | 95  |

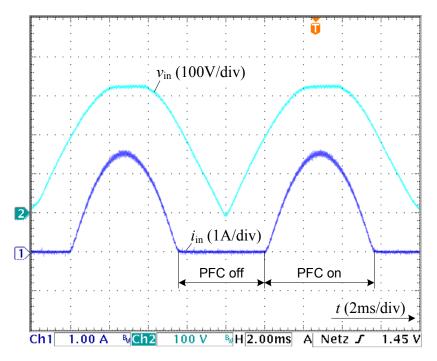

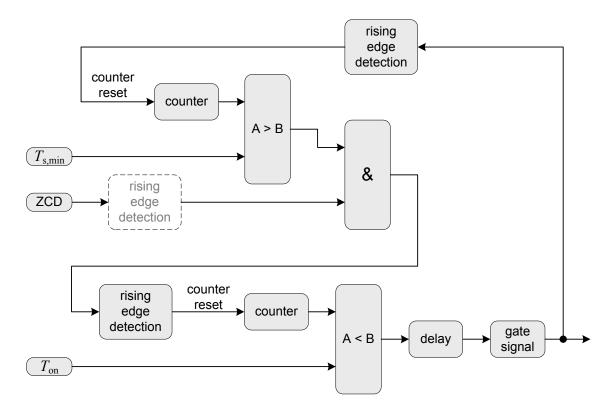

|   | 7.1   | BCM Control Concept                                  | 95  |

|   | 7.2   | Control Structure                                    | 97  |

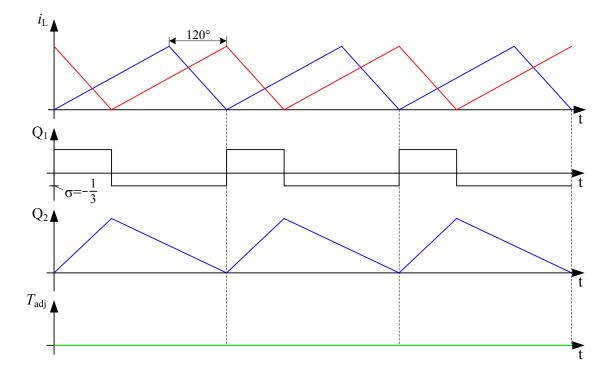

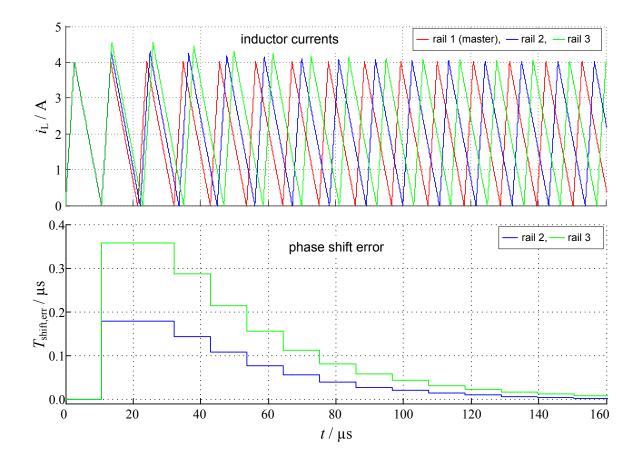

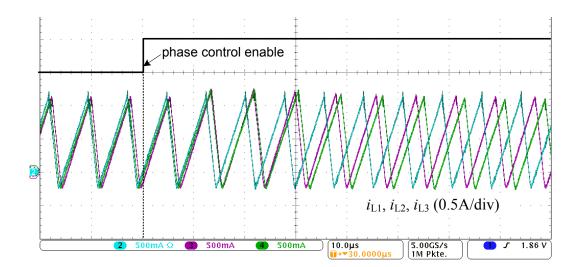

|   | 7.3   | Phase Shift Control for Interleaved BCM Rails        | 98  |

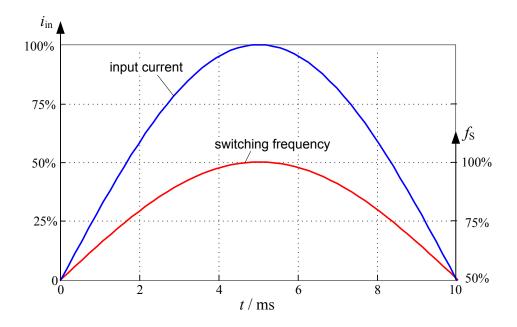

|   | 7.4   | Switching Frequency Limitation                       | 102 |

|   | 7.4.1 | Frequency Limitation due to Bounded Switching Period | 102 |

|   | 7.4.2 | 2 Frequency Limitation with Phase Shedding           | 105 |

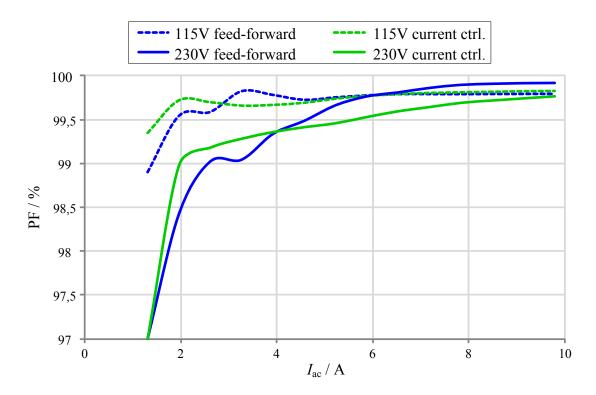

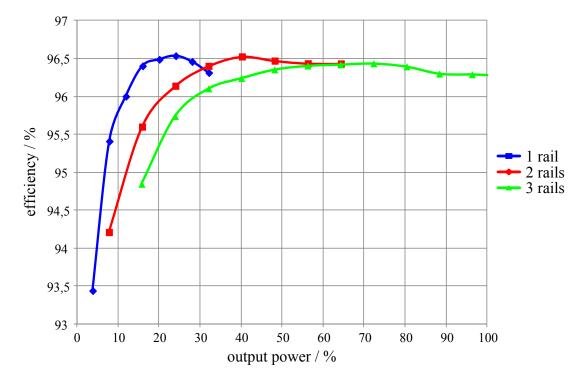

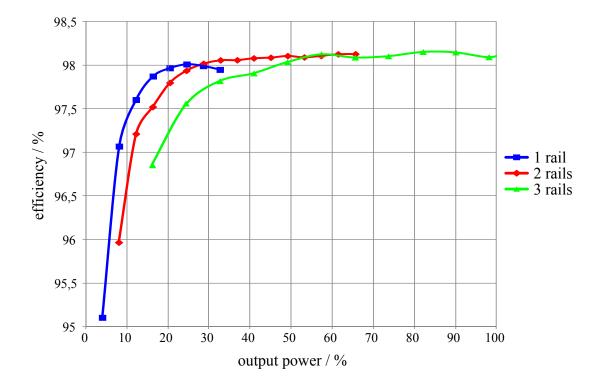

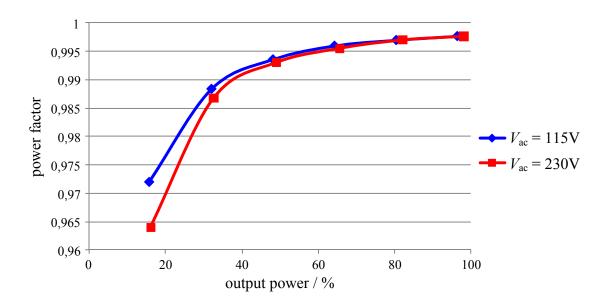

|   | 7.5   | Efficiency and Power Factor                          | 107 |

|   | 7.6   | Summary                                              | 109 |

|   |       |                                                      |     |

| 8 | FEE   | D-FORWARD CONTROL FOR BCM AND D                                  | СМ            |

|---|-------|------------------------------------------------------------------|---------------|

| 0 | PERA  | ΓΙΟΝ                                                             |               |

|   | 8.1   | eed-Forward Algorithm for BCM Operation                          |               |

|   | 8.2   | Extension into DCM operation                                     |               |

|   | 8.3   | Closed-Loop Control Strategy                                     |               |

|   | 8.3.1 | Closed-Loop Control Structure                                    |               |

|   | 8.3.2 | Transfer Function and Controller Design                          |               |

|   | 8.4   | Current Balancing                                                |               |

|   | 8.4.1 | Balancing to Identical Average or Peak Currents                  |               |

|   | 8.4.2 | Initial Calibration Sequence for Inductance Identification       | n 119         |

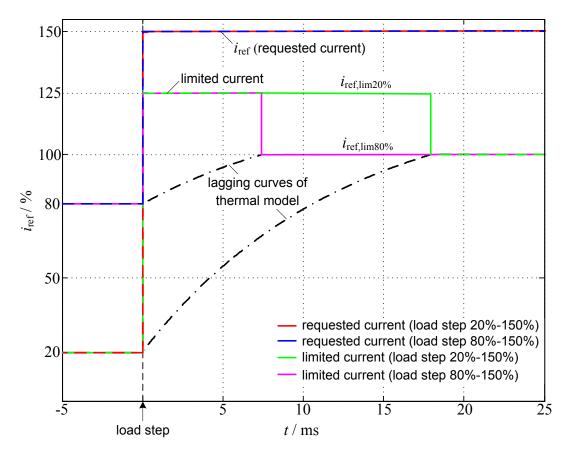

|   | 8.5   | hase Shedding                                                    |               |

|   | 8.5.1 | Common Discrete Phase Shedding                                   |               |

|   | 8.5.2 | Continuous Phase Shedding                                        |               |

|   | 8.5.3 | Switching Frequency Limitation                                   |               |

|   | 8.6   | Iarmonic Reduction in Interleaved DCM PFC Rectifiers             |               |

|   | 8.6.1 | Control law for equal inductance values                          |               |

|   | 8.6   | 1.1 Control law for discrete phase shedding                      |               |

|   | 8.6   | 1.2 Control law for continuous phase shedding                    |               |

|   | 8.6   | 1.3 Switching frequency and current limitation                   |               |

|   | 8.6   | 1.4 Verification in a PFC application                            |               |

|   | 8.6   | 1.5 Practical implementation                                     |               |

|   | 8.6.2 | Harmonic Elimination with Unequal Inductance Values              |               |

|   | 8.6   | 2.1 Harmonic elimination without balanced inductor cu            | ırrents 140   |

|   | 8.6   | 2.2 Harmonic elimination with balanced inductor curre            | nts 143       |

|   | 8.6   | 2.3 Minimization of the THD <sub>DC</sub> by applying a master I | DCM ratio 147 |

|   | 8.6   | 2.4 Practical implementation                                     |               |

|   | 8.7   | ummary                                                           |               |

| 9 | CON   | CLUSIONS                                                         |               |

| A | APP   | ENDIX                                                            |               |

|   |       | Definition of Power Factor (PF) and Total Harmonic Disto         |               |

|   | A.2   | ourier Coefficient Calculation of DCM Inductor Current.          |               |

| A.3  | Harmonic Elimination Utilizing Newton Algorithm | 159 |

|------|-------------------------------------------------|-----|

| SHOR | T FORMS                                         |     |

| DEFI | NITION OF SYMBOLS                               | 162 |

| REFE | RENCES                                          |     |

| LIST | OF PUBLICATIONS                                 |     |

# **1** Introduction

The largest part of the electrical energy is not consumed in the form that the power grid provides. Before usage the line voltage needs to be changed in amplitude and frequency. In many applications the AC line voltage must be transformed into a DC voltage. Consequently, suitable rectification is required.

Rectifiers with low power factor cause line interferences due to harmonics in the line current and reactive power and therefore reduce the power available from the grid. In order to guarantee high quality of the line voltage, norms like EN61000-3-2 have been released, which indicate limits for line interferences. Thus, power factor correction (PFC) rectifiers have been established as front end stage of AC-DC converters. An ideal PFC rectifier should emulate a resistor on the supply side, while maintaining a fairly regulated DC output voltage [Ros94]. Beyond that high efficiency and power density, low high-frequency distortions and a cost-effective realization are important design objectives.

The widely utilized topology for the PFC stage is the boost converter together with a diode rectifier. This topology is beneficial for this task because the inductor is connected to the input and allows low-distorted input currents. Furthermore, the output voltage is always higher than the amplitude of the line voltage, for which reason a worldwide usage of the same PFC rectifier at different line voltages and line frequencies is possible.

Nevertheless, it is the way of controlling the boost switch which let a simple boost converter with diode rectifier become a PFC rectifier. Generally, a cascaded control structure with outer output voltage control loop and inner current control loop is utilized. As for most converters the voltage control loop must provide a nearly constant DC output voltage. The task of the current control loop is to achieve unity power factor by forcing the average inductor current to track the shape of the sinusoidal input voltage as close as possible.

In order to increase the power level of the rectifier, it is common to operate two or more boost converters in parallel. The paralleled converter rails are typically phase shifted in order to reduce the filter size and costs and high-frequency interferences. With this interleaving technique a further task for the converter control arises. A balance control needs to ensure equal rail power.

The implementation of these complex control tasks for interleaved PFC rectifiers was dominated by analog technique for many years. Accordingly, a multitude of dedicated control ICs was developed, which provides the basic control functions for PFC applications. However, due to cost-efficient digital signal processors (DSP) and microcontrollers ( $\mu$ C) with increased computational power and appropriate peripherals digital control is widely used in PFC applications nowadays.

Digital control offers a multitude of benefits such as flexibility and programmability, decreased number of active and passive components, and as a consequence improved reliability, negligible and/or compensable offsets and thermal drifts [Mak04]. With employing digital control the demand on additional functionality of the PFC control has raised, consequently. In order to fulfill these demands it typically does not suffice to implement the traditional control structure in digital, but rather advanced control concepts needs to be invented. Furthermore, full digital control is not the panacea for all PFC applications. Sometimes it can be beneficial to retain some parts of the PFC control in analog technique combined with digital control parts.

In this thesis different control concepts for interleaved PFC rectifiers utilizing digital control are presented.

#### **Thesis Outline**

Chapter 2 of this thesis gives some basic information concerning interleaved boost PFC rectifiers. First the structure of distributed power systems (DPS) for server farms and communication networks is described with special focus on the tasks of the PFC rectifiers in those systems. The topology of the commonly used boost PFC rectifier and the basic structure of the PFC control are illustrated together with some typical shapes of voltages and currents. The interleaving technique for power converters is explained including its beneficial effect on the reduction of the total harmonic distortion (THD) in the input current. Before examining the control, the basics of the boost converter are reviewed and the differences between continuous conduction mode (CCM) and discontinuous conduction mode (DCM) are depicted. After that the three most utilized control methods voltage mode, peak current mode and average current mode control are explained. For PFC rectifiers only current mode control is suited to ensure sinusoidal input current and consequently high power factor. For this reason the control-to-inductor-current transfer functions for CCM and DCM are derived and applied for a design example for the average current control loop of a boost PFC rectifier. In order to complete the PFC control also the design of the outer voltage control loop is explained as well as the multiplier unit, which is utilized to generate the sinusoidal current reference value and to realize a load feedforward control.

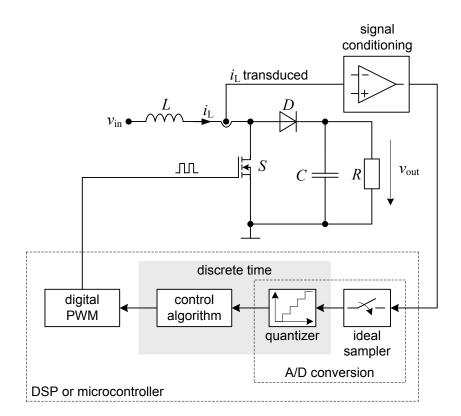

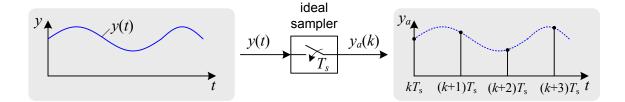

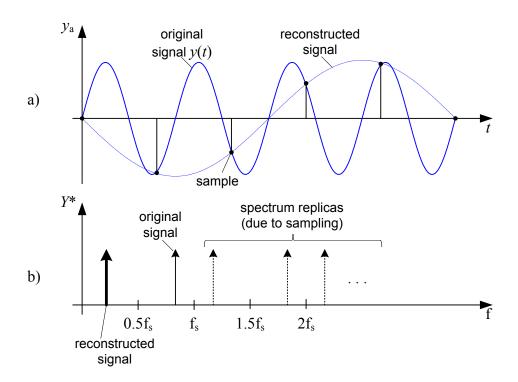

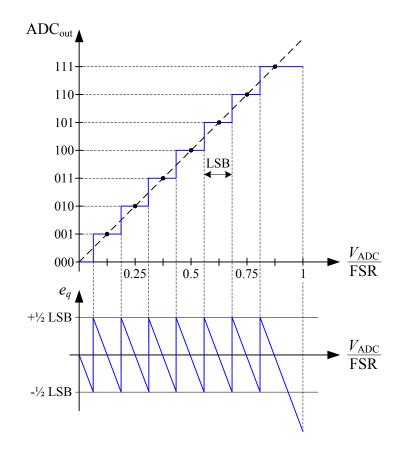

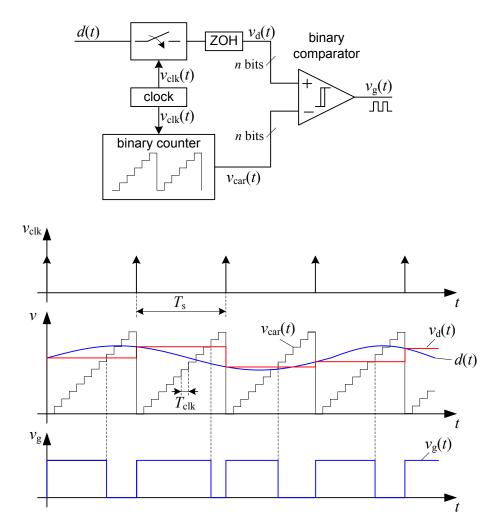

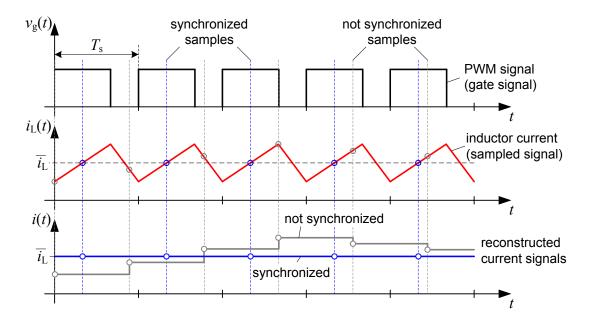

In Chapter 3 the properties of digital control and its associated parts are described in general. The sampling process and the quantization effect of the analog-to-digital conversion (ADC) are explained and their impact to the control performance is presented. Likewise the digital implementation of the pulse width modulation (PWM) is analyzed. Advantageous of digital control is the synchronization of the sampling instance and the switching cycle. On the other hand the sample-and-hold process inserts a dead-time into the control loop, which can reduce the phase margin significantly.

In Chapter 4 state of the art analog and digital PFC control is reviewed. First the traditional analog realization of PFC control is explained. Often the same control structure is retained for full digital PFC control. This is described in addition with some required or valuable

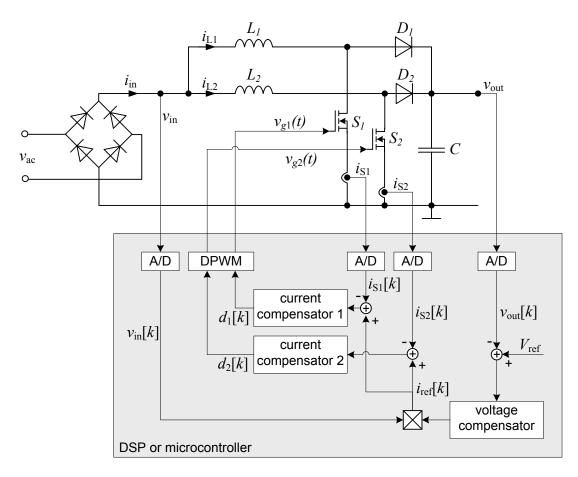

functions such as the correction of the inductor current sample in DCM and a duty-ratio feed-forward control for CCM and DCM.

In Chapter 5 - Chapter 8 advanced control concepts for interleaved boost PFC rectifiers utilizing digital control are presented.

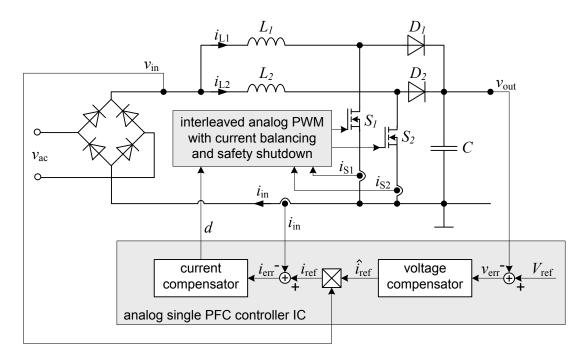

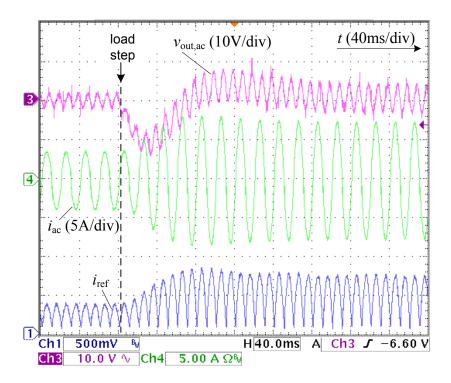

As a first mixed-signal solution a semi-digital PFC control concept with smart combination of analog and digital control parts is described in Chapter 5. High bandwidth control parts like the current controller as well as time-critical protection functions retain in conventional analog technique, whereas the slow voltage compensator, load feed-forward control, multiplier and non-time-critical protection functions are implemented in the digital control part. It is shown that already with such a partial digitalization appropriate power management features can be realized in order to improve the light load efficiency.

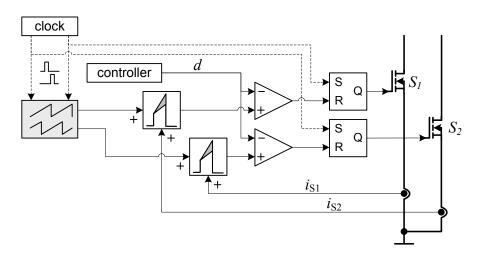

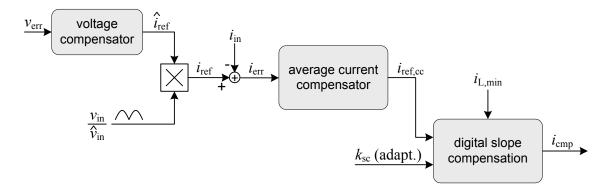

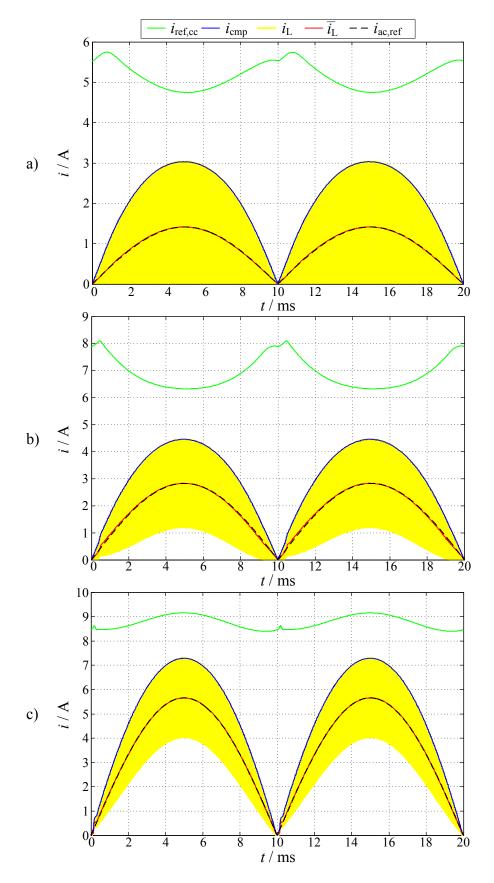

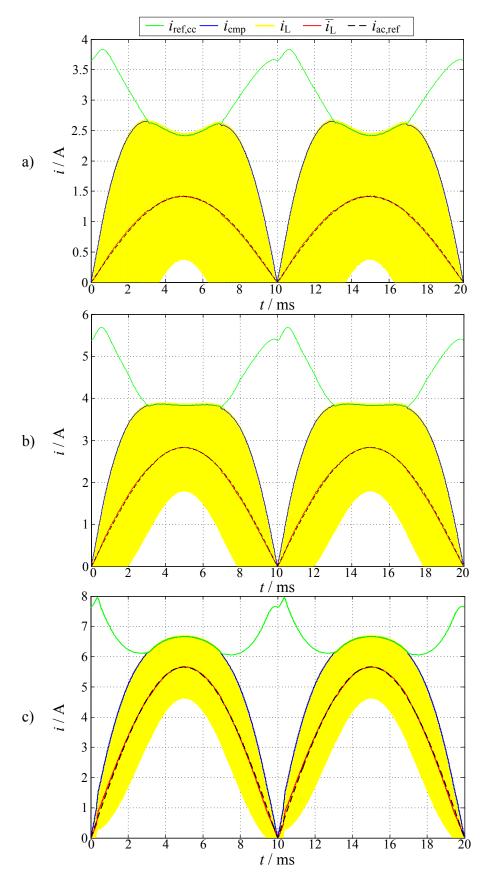

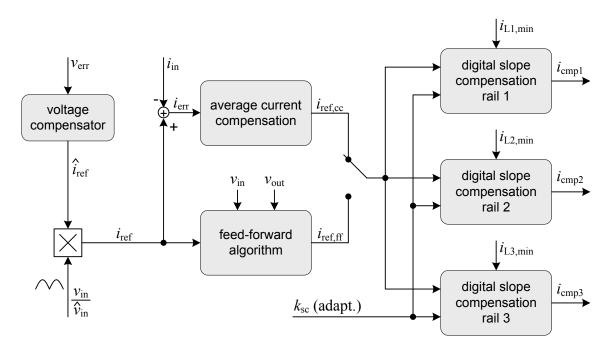

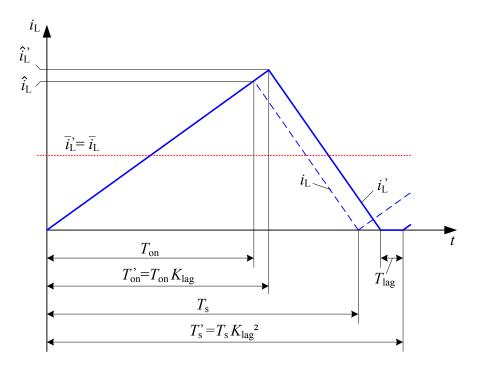

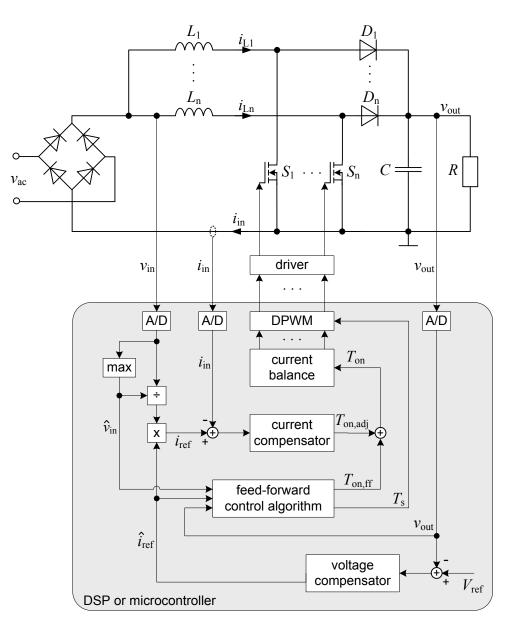

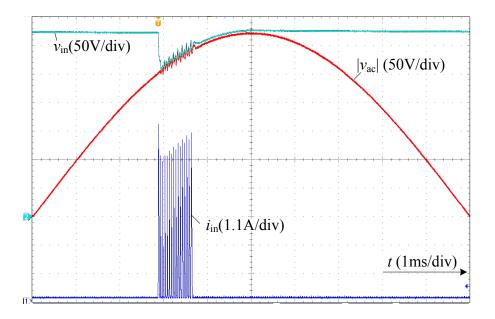

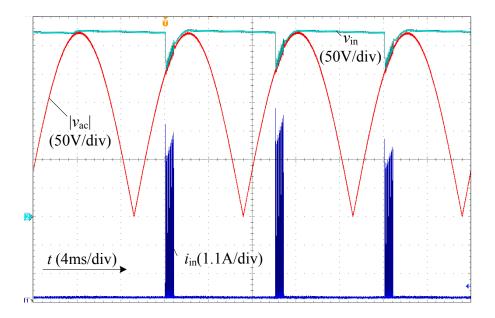

For the control concept presented in Chapter 6 digital control is combined with analog comparators in order to realize digital peak current control for interleaved PFC rectifier. With available DSPs and  $\mu$ Cs including analog on-chip comparators digital peak current control is basically feasible with little effort. In order to eliminate the drawbacks of peak current control, slope compensation is required. Thus, a digital slope compensation is introduced, which does not use an analog ramp signal, but instead an algorithm to precalculate the desired comparator switch-off threshold. This method furthermore enables adaptive slope compensation, which is beneficial for PFC applications where the operating point varies extremely. Several control structures are depicted and compared with respect to performance and computational effort.

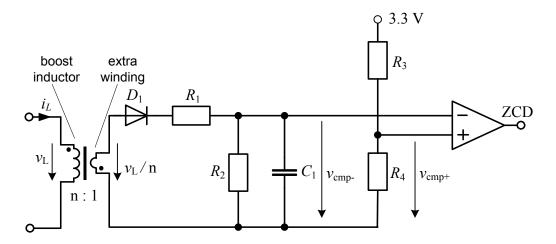

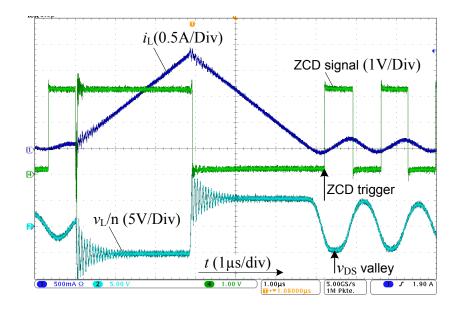

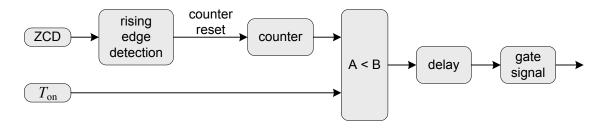

A popular control concept for PFC rectifiers is to operate the boost converter at the boundary of DCM and CCM. This boundary conduction mode (BCM) can be easily realized by utilizing a comparator to detect the instance where the inductor current becomes zero, in order to switch on the boost switch. However, due to the resulting variable switching frequency interleaving of several converters is challenging. For this reason a digital phase shift control for interleaved BCM rails is developed in Chapter 7. Because of the analog comparator in the control structure this concept strictly speaking is also a mixed-signal control concept.

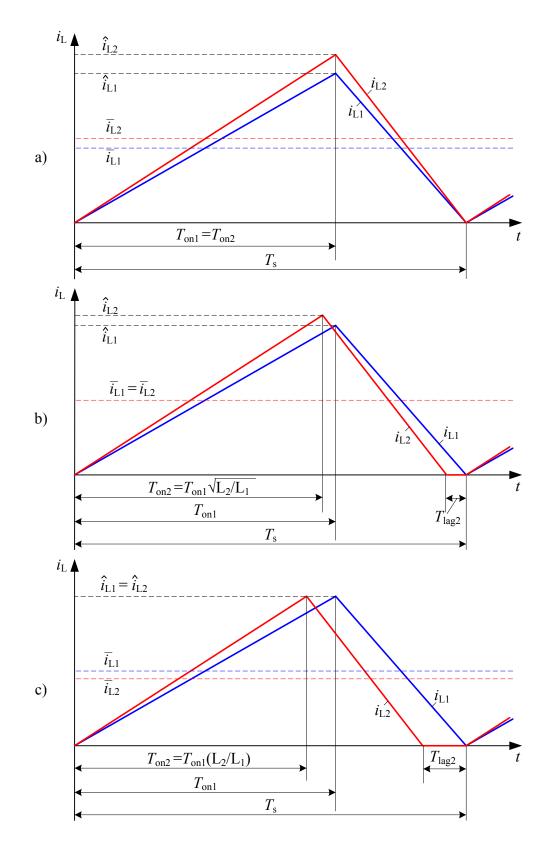

In Chapter 8 a pure digital control concept is presented, which enables multi-rail interleaving of PFC converters operating in BCM and DCM by applying a feed-forward control. The feed-forward algorithm is derived for BCM and extended to DCM operation. It can be utilized either alone without any current measurement in an open-loop control or together with a parallel current controller in a closed-loop version. The DCM ratio, e.g. the duration within the switching cycle where the inductor current is zero, can be adjusted individually for every single converter rail. This additional degree of freedom can be utilized for several features. If the inductor values of the rails differ, every rail can get its individual DCM ratio in order to balance the inductor currents. A novel continuous phase shedding method is introduced, which adjusts the DCM ratio of all rails in order to vary the effective number of energized converter rails transition-free. Further investigations show how this continuous phase shedding method can be utilized to reduce the THD in the input

current of paralleled converters in general and especially for PFC rectifiers with its continuous varying operation point.

All the presented innovations were verified in simulation and on a prototype with two or three parallel converter rails. Meaningful practical results are shown to illustrate the effectiveness of the proposed control concepts.

The conclusions are given in Chapter 9.

# 2 Basics of Boost Power Factor Correction Rectifier

The boost power factor correction (PFC) rectifier is widely used as front-end stage for AC-DC switched-mode power supplies (SMPS). The main task of PFC rectifiers is to generate a fairly regulated DC output voltage from the sinusoidal AC line voltage by providing almost unity power factor [Ros94].

For adequate performance of the PFC rectifier suitable dynamics need to be applied to the control loops by precisely designing the compensators. For this purpose the static and dynamic behavior of the controlled converter needs to be well known.

In this chapter the application of PFC rectifiers in distributed power systems (DPS) is explained. The structure of the cascaded PFC control loops is described and a short review of the boost converter functionality and its modes of operation are given. The basic control methods are described and the control-to-inductor-current transfer function is derived. Finally, the design of the current control loop, the voltage compensator and the PFC specific multiplier unit are explained.

# 2.1 PFC in Distributed Power Systems (DPS)

Since the largest part of the electrical energy is not consumed in the form that the power grid provides, the line voltage needs to be changed in amplitude and frequency before usage.

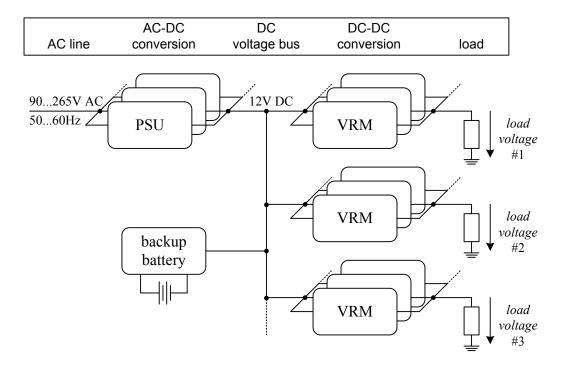

In particular the energy demand for server farms and communication networks has increased heavily in the last decades. In order to achieve higher processing speed with minimized power consumption, the supply voltages have been reduced in new logic families [Tab92]. Thus, DC voltages of only a few volts are required to supply the processors and electronic circuits. Transformation of the AC line voltage for this purpose is usually carried out by several conversion stages. This converter structures are also referred to as distributed power systems (DPS) [Tab92, Mam93, Luo05]. The structure of DPS can slightly vary depending on the application and mainframe manufacturer. A widely-used layout of a DPS with 12V bus voltage is depicted in Figure 2.1.

In the first step the AC line voltage is transformed into a DC voltage of 12V by a power supply unit (PSU). Single line phase PSUs typically have a power range up to 4kW. By paralleling of several PSUs the overall power can be scaled and the requirements for redundancy and reliability can be fulfilled. On the output side all paralleled PSUs are connected to a DC bus, which distributes the DC voltage within the system.

In many applications uninterrupted power supply also in the case of temporary power grid failure is required. For this reason battery backups are commonly utilized to supply the DC voltage bus temporarily.

In the second step the DC bus voltage is converted to the required voltage levels, for instance 3.3V, 1.8V, 1.1V. These last DC-DC converter stages are also referred to as voltage regulator modules (VRM) or point of load (POL) converter and are located close to the loads. With this method excellent dynamic and noise immunity of the supply voltages can be achieved.

*Figure 2.1: Typical structure of a distributed power system (DPS) with 12V DC bus voltage*

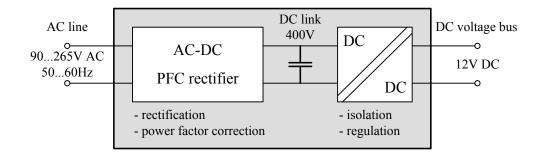

The PSUs are predominantly realized with two converter stages (cf. Figure 2.2) [Wet06]. The front-end stage is the power factor correction (PFC) rectifier, which is examined in detail in this thesis later on. The PFC rectifier transforms the AC line voltage into a DC voltage of typically 400V. In the second stage a DC-DC converter steps down this DC link voltage to the desired PSU output voltage. This converter stage needs suitable dynamic to ensure constant DC bus voltage during load steps and input voltage variations. Besides providing a stable output voltage this stage has a transformer to isolate the system from the power grid. Most utilized topologies for this purpose are the two-switch-forward converter, the phase-shift full-bridge (PSFB) converter and the LLC resonant converter.

*Figure 2.2: Classical PSU topology with two converter stages*

# 2.2 Boost PFC Rectifier

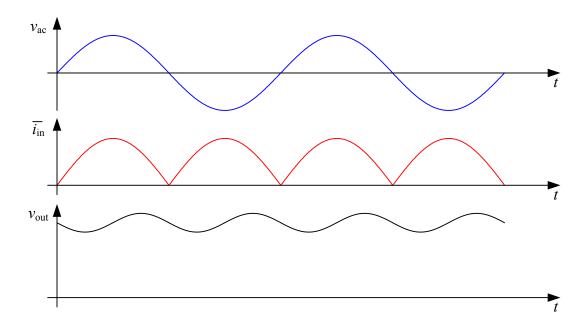

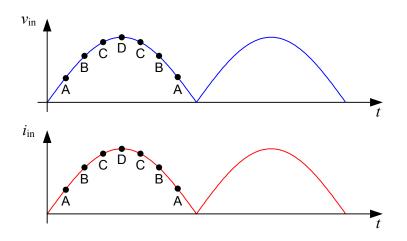

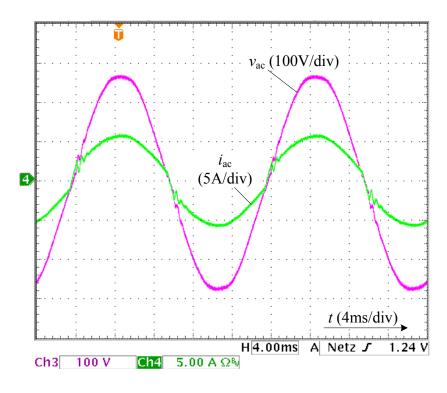

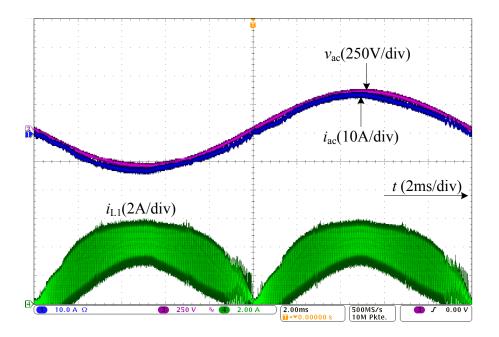

As mentioned in the previous section the PFC rectifier has to convert the AC line voltage into a DC voltage. This task could also be done with a simple passive diode bridge rectifier connected to the line voltage and feeding a bulky filter capacitor. However, this would result in a poor power factor reducing the power available from the power grid, while high harmonic distortions in the line current would cause electromagnetic interferences (EMI) problems [Ros94]. Thus, the second major task of the rectifier stage is to maintain an ideal power factor [Adr02]. This means that the input current of the PSU needs to have the same sinusoidal shape like the line voltage (cf. Figure 2.4), i.e. the PSU must act like a resistor on the supply side.

The definition of the power factor is given in Appendix A.1.

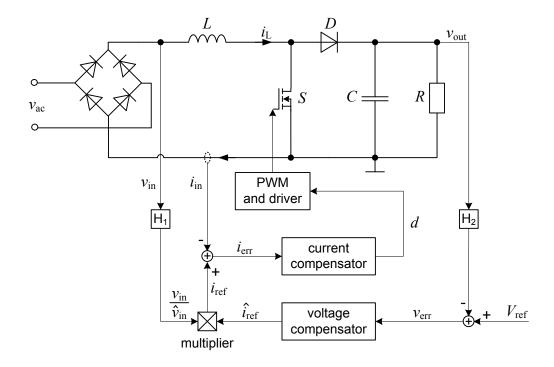

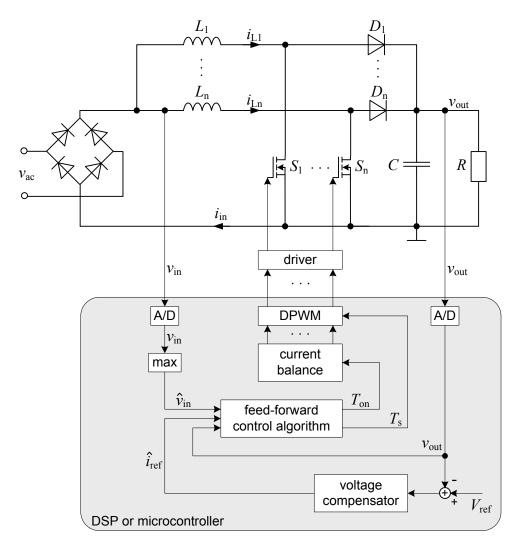

Figure 2.3: Boost PFC rectifier with cascaded control structure

Most suitable for implementing PFC and widely utilized for this purpose is the boost converter together with a diode bridge rectifier (c.f. Figure 2.3). This topology is very simple and due to the fact that the boost inductor is connected in series with the line input, smaller input current ripple is achieved and easy control of the average input current is enabled [Xie03]. An additional EMI filter is typically applied to further reduce the high-frequency ripple in the input current. Figure 2.3 shows the schematic of the boost PFC rectifier with its cascaded control structure without EMI filter. The PFC control usually consists of an outer voltage loop, controlling the DC output voltage, a multiplier unit and an inner current loop.

There are also several topologies where one diode is eliminated from the line-current path, so that the line current simultaneously flows through only two semiconductors [HJJ08]. Consequently, the efficiency of these bridgeless PFC topologies is increased. However, the control usually is the same than for the conventional topology with bridge rectifier.

Strictly speaking it is the way of controlling the boost switch which let the converter act as a PFC. The controller has to operate the boost switch in such a way to properly shape the input current  $i_{in}$  according to the shape of the rectified line voltage  $v_{in}$  [Ros94]. In order to generate the semi-sinusoidal current reference  $i_{ref}$ , the DC reference current value  $\hat{i}_{ref}$  is multiplied with the normalized input voltage signal. The DC reference current is determined by the outer voltage loop to adjust the DC output voltage  $v_{out}$ . Later in this chapter the boost converter and the corresponding control for PFC applications are described in detail.

Figure 2.4: Typical voltage and current waveforms of PFC rectifiers

Because of the boost topology the output voltage will be larger than the amplitude of the input voltage  $\hat{v}_{in}$ . In order to enable a worldwide usage of the PSUs in different power

grids the PFC rectifier normally must provide operation at wide line voltage range of 90V-265V and at line frequencies in the range of 50Hz-60Hz. A typical value for the rectified output voltage is around 400V. However, the output voltage is not a pure DC voltage, but has an AC ripple of twice the line frequency (cf. Figure 2.4). This is caused by the sinusoidal shape of the input voltage and the input current, which cause a pulsating input power. To keep the AC ripple in a certain range a large output capacitor is required. But in many applications a bulky output capacitor is applied anyway, because it is additionally utilized as an energy storage, which ensures continuing operation of the system during short term power line failures of up to one line period.

# 2.3 Interleaving

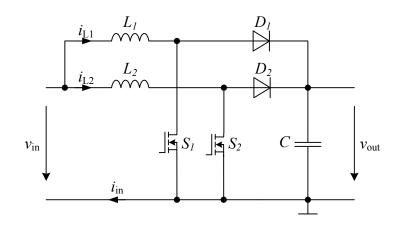

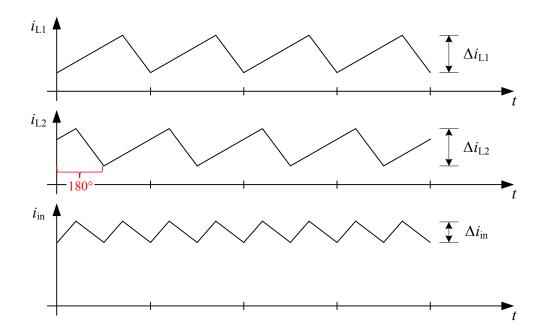

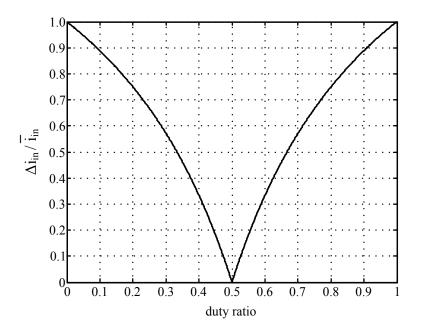

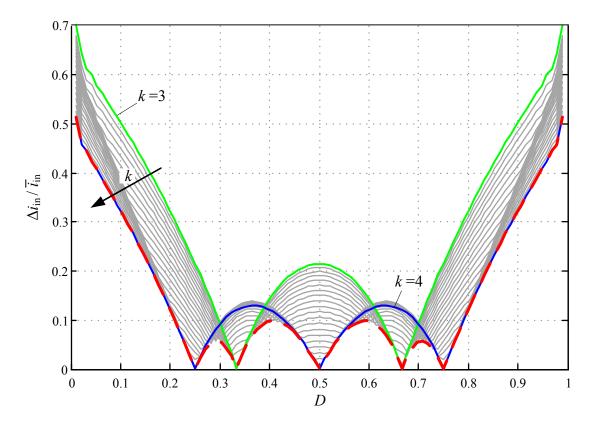

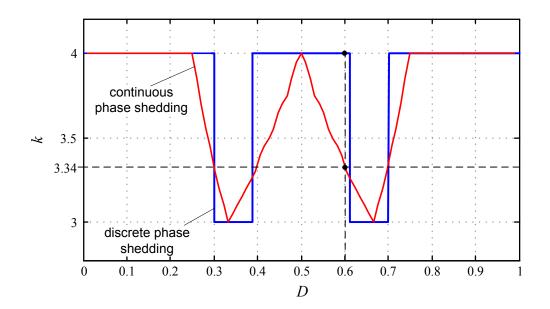

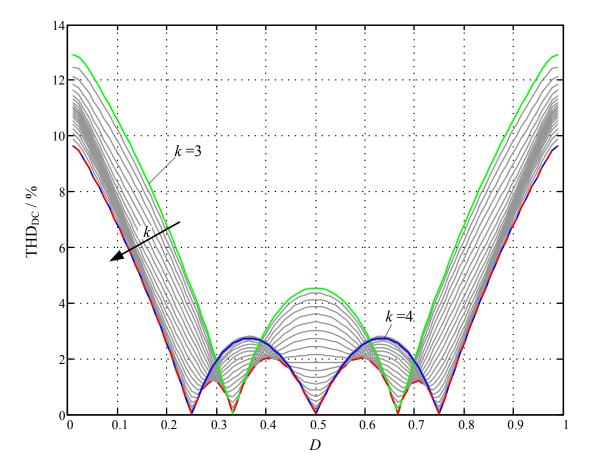

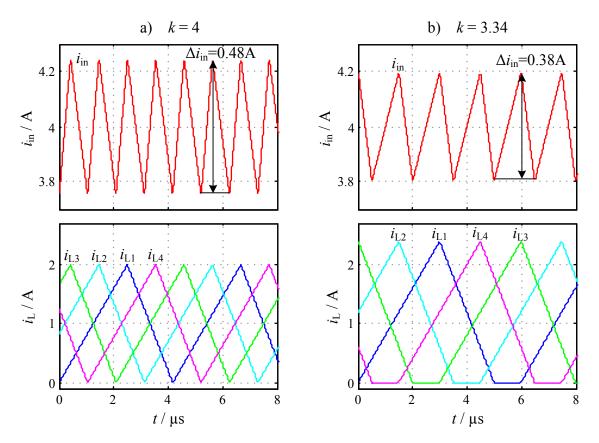

The interleaving technique is characterized by operating two or more identical converters in parallel (c.f. Figure 2.5) with phase shifted gate signals and is topic of numerous publications, e.g. [Lou06, Bal93, Miw92]. With this method the overall switching frequency of the paralleled converters is increased, while the switching frequency of every single converter cell remains at its origin value. Hence, the power level can be easily extended without increasing the device stress. Due to the overlapping inductor currents the ripple of the input current and the output voltage are reduced significantly (c.f. Figure 2.6). At certain duty-ratios the ripple  $\Delta i_{in}$  is even eliminated completely (e.g. at D = 50% for two interleaved converters). In Figure 2.7 the reduction of the ripple in the input current is illustrated versus duty-ratio for two interleaved converters. With reducing the input current ripple also the RMS current in the DC link capacitor and the EMI of boost PFC rectifiers are reduced significantly. This enables easier observance of the standards for line current harmonics and conducted EMI with less filter volume and filter components [Zum04].

*Figure 2.5: Dual interleaved boost converter*

Furthermore, interleaving offers potential to improve the light load efficiency by adjusting the number of paralleled converters at partial load [Gro09, ChMa10, QLi09]. Due to employment of several small inductances instead of a single bulky inductor faster dynamic

response can be achieved. In addition a better thermal management results by spreading of the hot spots.

*Figure 2.6:* Interleaved inductor currents and resulting input current

*Figure 2.7: Ripple reduction in the input current for dual interleaved converter*

One drawback of interleaving is the need of balancing the currents of the paralleled converters to ensure uniformed spread stress of the devices. Thus, an adequate current balancing strategy is one of the design goals for interleaved converter control.

# 2.4 Boost Converter Basics

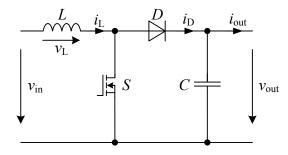

The boost converter (cf. Figure 2.8) provides a higher output voltage than the input voltage [Eri00, Kas91, Zac90a]. For this purpose one active switch (MOSFET), one passive switch (diode) and two passive energy storage elements (inductor and capacitor) are utilized.

Figure 2.8: Boost converter

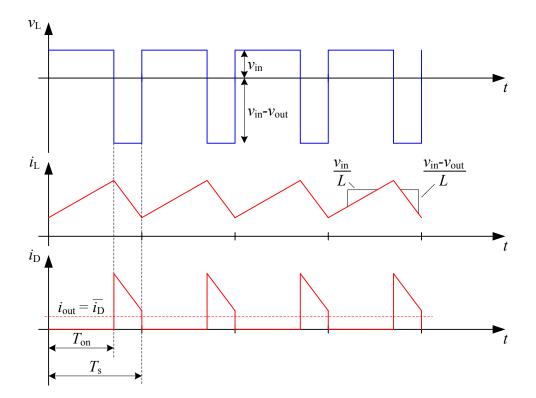

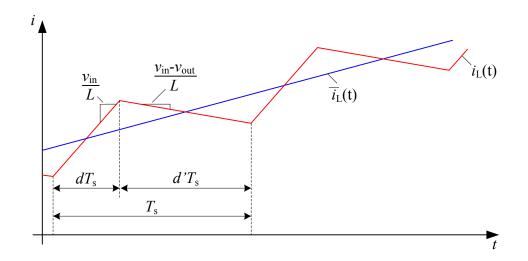

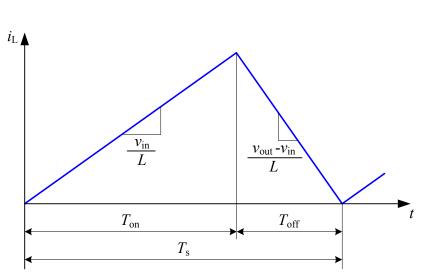

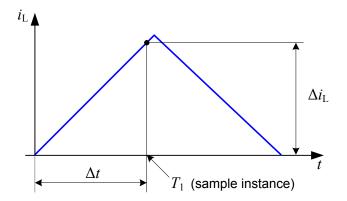

The gate of the MOSFET acts as control input port. If the switch is closed, the inductor voltage is equal to  $v_{in}$  and the current through the inductor changes with

$$\frac{di_L}{dt} = \frac{v_{in}}{L}.$$

(2.1)

During this interval the energy stored in the inductor increases. When the switch is open, the inductor voltage is  $(v_{in} - v_{out})$  and the current flows through the diode and releases the inductive energy to the converter output and decreases with

$$\frac{di_L}{dt} = \frac{v_{in} - v_{out}}{L}.$$

(2.2)

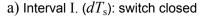

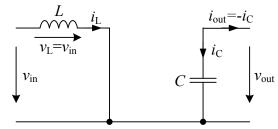

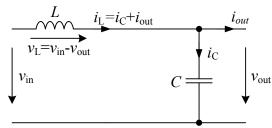

In Figure 2.9 the equivalent circuits of the different switching conditions are illustrated.

b) Interval II. ( $d'T_s$ ): switch open

c) Interval III. ( $d''T_s$ ): switch open and  $i_L=0$

Figure 2.9: Equivalent circuits of the switching intervals during one switching cycle

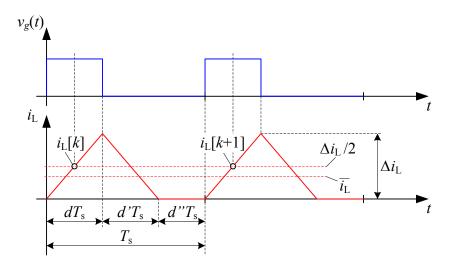

Figure 2.10 shows the waveform of the inductor voltage and current, as well as the waveform of the current which flows through the boost diode under steady state conditions. This means that the inductor current values at the beginning and at the end of the switching period  $T_s$  are equal. From this it follows, that the conversion ratio M is determined by interval:

$$M = \frac{v_{out}}{v_{in}} = \frac{T_s}{T_s - T_{on}} = \frac{1}{1 - d} = \frac{1}{d'}$$

(2.3)

The range of the duty-ratio  $d = T_{on}/T_s$  goes from zero to one.

Figure 2.10: Steady state voltage and current waveforms of an ideal boost converter

# 2.4.1 Operation Modes

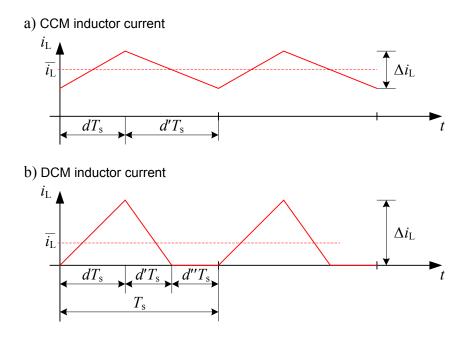

The operation modes of switching converters can be classified into two modes: firstly the continuous conduction mode (CCM), where the inductor current never comes down to zero and secondly the discontinuous conduction mode, where the inductor current resets to zero within the switching cycle.

### A. Continuous Conduction Mode (CCM)

In CCM the switching cycle portions in two intervals. First, if the switch is closed, the inductor current rises and secondly, the current falls, if the switch is open (cf. Figure 2.11 a)). In this mode the AC component of the inductor current typically is much smaller than the DC component.

#### **B.** Discontinuous Conduction Mode (DCM)

In DCM a third interval within the switching cycle appears (cf. Figure 2.9 c)). During the switch-off time the inductor current decays to zero and the converter remains in this state until the next switch-on event. This happens for example at light load operation of the converter, if the peak-to-peak inductor current ripple becomes larger than twice the average current. In some applications the converter is intentionally designed to operate only in DCM in order to avoid problems caused by the reverse recovery effect of the diode [Gro11]. Another reason to employ DCM can be avoiding the right half plane zero in the

control-to-output transfer function of the boost converter [Ara09]. Figure 2.11 b) shows the inductor current waveform in DCM.

Figure 2.11: Inductor current waveform in a) CCM and b) DCM

The converter properties in DCM are significantly different to CCM. Consequently, a rigorous change in the small and large signal transfer characteristic occurs with changing the mode of operation. In DCM the conversion ratio M becomes dependent of the load resistance R [Eri00]:

$$M_{DCM}(d,R) = \frac{v_{out}}{v_{in}} = \frac{1}{2} \sqrt{\frac{1}{2} + \frac{d^2 R T_s}{L}}$$

(2.4)

## 2.4.2 Control Methods

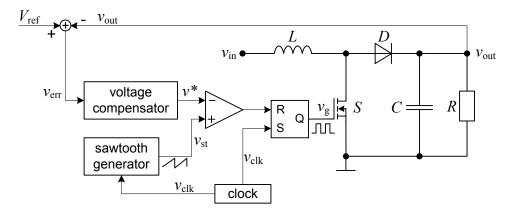

#### 2.4.2.1 Voltage mode control

Beyond the converter control methods voltage mode control is the oldest and simplest one. The control structure is illustrated in Figure 2.12 and significant signal waveforms are depicted in Figure 2.13. The output voltage is compared with the reference value and the resulting error voltage is passed to the voltage compensator. The compensator determines the comparator turn-off threshold. Together with the RS-flip-flop the comparator acts as a pulse width modulator (PWM), where the sawtooth signal on the negative comparator input is utilized as carrier signal. The RS-flip-flop turns on the boost switch at the

beginning of each switching cycle and turns off, if the sawtooth signal exceeds the error amplifier output value. Due to the fact that the duty-ratio is directly determined by the voltage error this method is also known as direct duty-cycle control (DDC) [Zac90].

Figure 2.12: Boost converter with voltage mode control

Figure 2.13: Generation of the gate signal with voltage mode control

With adequate amplitude of the sawtooth signal this control method provides a good signal-to-noise ratio. Another advantage is the simple design of the feedback loop [Zac90]. However, since the loop gain changes with the input voltage a poor control dynamic under input voltage variation results. To overcome this drawback an extension of the control method can be applied. Thereby the amplitude of the sawtooth signal is changed proportional to the input voltage. This method is also known as voltage feed-forward control (VFC) [Zac90].

For PFC applications voltage mode control is not suitable, because it is essential to control the shape of the input current which is not provided with this control method.

## 2.4.2.2 Current mode control

With current mode control the inductor current which also influences the output voltage is implicated as an additional control value. Compared to voltage mode control it exhibits a high frequency bandwidth resulting in improved control loop dynamics and leads to a better line noise rejection. With reducing the small-signal dynamics from second-order to first-order, it additionally simplifies the outer voltage loop design [Hsu79, Don96]. A cascaded control structure results where the inner current control loop operates the boost switch. The reference value for the current controller is provided by the outer voltage controller.

There is a multitude of methods of implementing the current control, which can be separated in fixed and variable switching frequency methods. Widely utilized is the peak current mode control. Thereby the switch is turned on with an external clock signal and turned off if the current reaches a certain level. Very similar but rarely used is valley current mode control, where the clock signal turns off and a comparator turns on the switch, if the current falls below the threshold level. A further fixed frequency method is average current control. As the name implies with this method the average value of the inductor current is controlled. Depending on the current error a compensator determines the duty-ratio which is passed to a PWM to generate the switching command. In particular, in boost-type PFC rectifiers, average current control ensures very low current distortions [Che03].

Examples for variable switching frequency methods are constant on-time control, constant off-time control and hysteretic control [Zac90]. At hysteretic control two comparators are utilized to determine the switching instances. The switch is turned on if the lower threshold is reached and turned off at the specified peak value. A special case for hysteretic current control is the boundary conduction mode (BCM) (often also called critical conduction mode or transition mode). With this method the lower current threshold is set to zero in order to operate the converter at the boundary of continuous and discontinuous conduction mode.

In the following peak and average current control are described in detail.

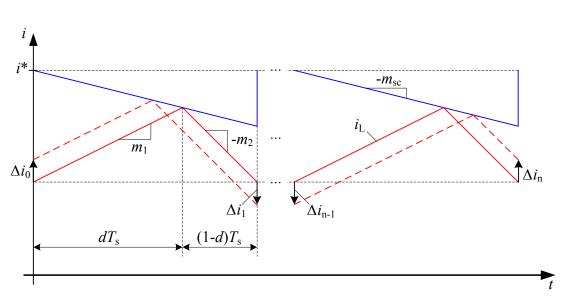

### A. Peak current mode control with slope compensation

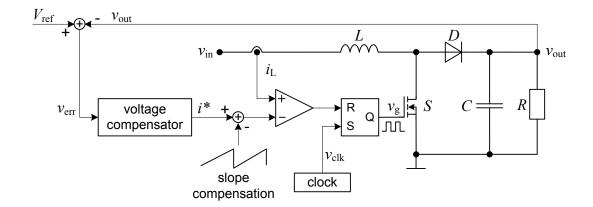

The scheme of a boost converter with outer voltage loop and inner peak current control loop is illustrated in Figure 2.14. Again the clock signal turns on the switch at the beginning of each switching cycle. The duty-ratio now is terminated when the inductor current reaches a threshold level defined by the outer voltage controller (cf. Figure 2.15).

*Figure 2.14: Peak current controlled boost converter with slope compensation*

*Figure 2.15: Generation of the gate signal with peak current mode control without slope compensation*

Additionally to the excellent control dynamics this technique features some inherent advantages such as simple cycle-by-cycle current limiting and good current sharing of paralleled converters [Hsu79, Don96]. Instead of measuring the inductor current it suffice to sense the current in the switch path for peak current control. Thus, instead of a shunt resistor, which is always a trade-off between good signal-to-noise ratio and additional losses, a simple current transformer can be utilized. However, there are several drawbacks of peak current mode control in CCM [Hol84, JLu07]. Sensing of the peak instead of the average current value causes non ideal control response. Spikes in the current signal due to noise or the reverse recovery current of the boost diode can lead to faulty switch-off, particularly at small inductor current ripple. However, the major drawback is the loss of

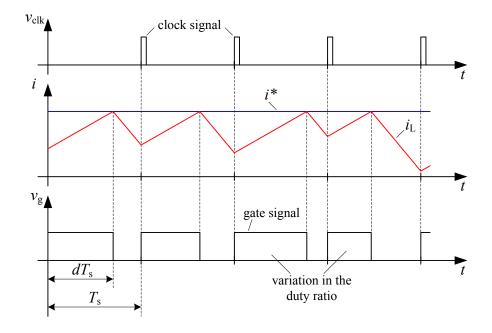

stability, if the duty-ratio exceeds 50%, resulting in subharmonic oscillations. This situation is depicted in Figure 2.15, where the peak current reference value  $i^*$  is constant but the disturbance in the inductor current increases resulting in high variation in the duty-ratio. A common approach to regain stability at duty-ratios above 50% is to apply a so called slope compensation [GrSc09, Hsu79, Don96, Hol84, JLu07, Sam08, YLi2007, Sak05]. Therefore an additional sawtooth signal with appropriate slope is either added to the current signal or subtracted from the reference value (cf. Figure 2.14). The behavior without and with slope compensation is analyzed in the following.

#### A.1 Situation without Slope Compensation

In order to derive the stability criterion of peak current mode controlled CCM converters which characterizes the transition to subharmonic oscillations, the operation without slope compensation shall be analyzed in a first step [GrSc09]. Therefore inductor currents are plotted in Figure 2.16 versus a single switching period  $T_s$  for the undisturbed (solid stroke) and a disturbed (dashed stroke) case. Both inductor current shapes have the same rising slope  $m_1$ , falling slope  $m_2$  and peak value  $\hat{\iota}_L$ . For the undisturbed case (solid line in Figure 2.16) it can be directly derived

$$\hat{\iota}_L = m_1 T_1 + I_0 \tag{2.5}$$

as well as

$$\hat{\iota}_L - m_2 T_2 = I_0 \,. \tag{2.6}$$

*Figure 2.16: Growing disturbances in the inductor current under peak current control for*  $m_1 > m_2$

Whereas for a disturbance of  $\Delta i_0$  (dashed line in Figure 2.16)

$$\hat{i}_L = \Delta i_0 + m_1 T_{1d} + I_0 \tag{2.7}$$

and

$$\hat{i}_L - m_2 T_{2d} = I_0 + \Delta i_1 \tag{2.8}$$

applies.

In both cases the duration of the switching period is identical. This is because of clock-triggered turn-on. Thus, it follows

$$T_s = T_1 + T_2 = T_{1d} + T_{2d}.$$

(2.9)

After solving Eq. (2.5) for  $T_1$ , Eq. (2.6) for  $T_2$ , Eq. (2.7) for  $T_{1d}$  and Eq. (2.8) for  $T_{2d}$ , Eq. (2.9) can be rewritten as

$$\frac{\hat{i}_L - I_0}{m_1} + \frac{\hat{i}_L - I_0}{m_2} = \frac{\hat{i}_L - \Delta i_0 - I_0}{m_1} + \frac{\hat{i}_L - \Delta i_1 - I_0}{m_2}$$

(2.10)

and directly simplified to

$$0 = -\frac{\Delta i_0}{m_1} - \frac{\Delta i_1}{m_2},$$

(2.11)

which is equivalent to

$$\Delta i_1 = -\frac{m_2}{m_1} \Delta i_0. \tag{2.12}$$

If the magnitude of the current falling slope  $m_2$  is larger than that of the rising slope  $m_1 < m_2$ , the current perturbation  $\Delta i$  obviously grows. The current error drift propagates with every switching period and after *n* cycles the perturbation will become

$$\Delta i_n = \left(-\frac{m_2}{m_1}\right)^n \Delta i_0. \tag{2.13}$$

For steady state conditions the ratio of current falling slope to rising slope can be expressed as

$$\frac{m_2}{m_1} = \frac{d}{1-d},$$

(2.14)

where d is the duty-ratio (cf. also Figure 2.17).

From Eq. (2.13) and Eq. (2.14) it follows that the instability inherently occurs as long as the duty-ratio exceeds 50% (d > 0.5).

#### A.2 Situation with Slope Compensation

The instability for d > 0.5 can be eliminated, if a compensation ramp is added to the switch-off threshold as shown in Figure 2.17 [GrSc09, Hsu79, Don96, Hol84]. When introducing the additional compensation slope  $m_{sc}$  the calculation similar to Eq. (2.5) - Eq. (2.13) directly yields as a modified formula for the current perturbation after *n* cycles

$$\Delta i_n = \left(-\frac{m_2 - m_{sc}}{m_1 + m_{sc}}\right)^n \Delta i_0. \tag{2.15}$$

From Eq. (2.15) it follows that for a stable current loop  $\left|\frac{m_2 - m_{sc}}{m_1 + m_{sc}}\right| < 1$  must be fulfilled and therefore the required slope for the compensation ramp results as

$$m_{sc} > \frac{1}{2}(m_2 - m_1).$$

(2.16)

*Figure 2.17: Inductor current under peak current control with slope compensation*

Assuming a constant inductance L, the slope is proportional to the inductor voltage. Table 2.1 contains the corresponding voltages  $m_1L$ ,  $m_2L$  and the required compensation  $m_{sc}L$  for buck, boost and buck-boost converter.

From Eq. (2.15) it can be seen that a perturbation can be compensated within only one cycle, if the slope of the compensation ramp  $m_{sc}$  is equal to the falling current slope  $m_2$ . This characteristic is called *dead-beat* control and represents the fastest possible transient response [GrSc09, Hsu79, Don96, Hol84]. If applying higher values of  $m_{sc}$  than  $m_2$ , the settling takes several cycles without overshoot.

|            | $m_1L$             | $m_2L$             | m <sub>sc</sub> L         |

|------------|--------------------|--------------------|---------------------------|

| buck       | $v_{in} - v_{out}$ | $v_{out}$          | $> v_{out} - 0.5 v_{in}$  |

| boost      | $v_{in}$           | $v_{out} - v_{in}$ | $> 0.5 v_{out} - v_{in}$  |

| buck-boost | $v_{in}$           | v <sub>out</sub>   | $> 0.5(v_{out} - v_{in})$ |

Table 2.1:Current slope generating voltages and minimum required compensation<br/>for basic converters

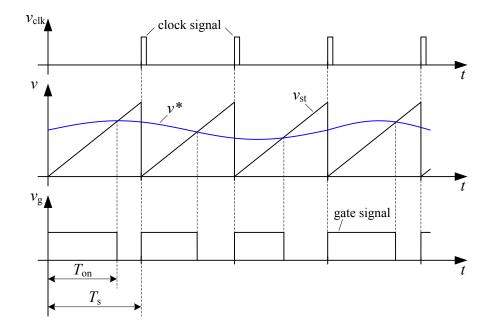

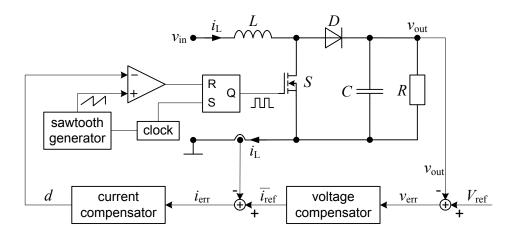

## B. Average current mode control

Most converters only need to adjust the output voltage accurately. For that purpose the outer voltage control loop requests higher current from the inner current control loop to increase or less current to decrease the output voltage. In fact it is the average value of the output current which needs to be varied, but the exact quantity of the average current is not essential. With peak current control with slope compensation there is no direct link to the average current value. But due to the fact that the output current can be varied very easily, it is well suited for those applications.

However, especially in PFC applications the situation is different. Besides controlling the output voltage also the average value of the input current must follow the reference value as good as possible to achieve unity power factor. Consequently, it is the inductor average current which needs to be controlled in boost PFC rectifiers.

Figure 2.18 shows the scheme of the boost converter with average current control. The voltage loop is similar to peak current control, but it now determines the average inductor current for the inner control loop. Based on the difference between that reference value and the actual current average value the current compensator defines the duty-ratio. Similar to voltage mode control a comparator and a RS-flip-flop form a PWM unit to generate the switching pulses. If the sawtooth signal exceeds the duty-ratio signal, the flip-flop turns off the switch and a clock signal turns on the switch at the beginning of each switching cycle. By applying an external sawtooth as carrier signal with arbitrary amplitude instead of the current slope, average current control is less noise sensitive [Zac90]. There is no need of any slope compensation and spikes in the current signal are filtered and cannot lead to faulty switch-off events.

However, to achieve the desired control dynamic and stability an accurate design of the compensation network is required. The resulting bandwidth of average current control is lower compared to peak current control, but it is quite enough for PFC applications.

Interleaving with good current sharing is possible, if every rail gets its own current control loop. But challenging is the cost effective sensing of the rail inductor currents. For single rail a shunt resistor in the ground connection path is mostly utilized, but for interleaved rails this method can only be used to sense the overall input current. By placing the shunt

resistor in the inductor path it has no direct connection to the signal ground and therefore needs resistive voltage divider at the input of a differential amplifier. The use of compensated Hall Effect current transducers in the inductor path is easy to implement, but too expensive for cost sensitive applications. By measuring in the switch path the inductor current information is not available during the switch-off interval. In some analog controller ICs a current synthesizer is applied to reconstruct the complete inductor current signal from the switch current [TI11].

Figure 2.18: Average current control for boost converter

# 2.4.3 Modeling of the Boost Converter

For the analysis and design process of power electronic circuits it is essential to have adequate converter models available. They are helpful early in the design process to choose the suitable topology, select appropriate circuit components and run simplified simulations in order to estimate the converter performance. Furthermore, converter models are indispensable for control loop design to ensure stability and meet the dynamic requirements.

There are several modeling methods which are addressed in a multitude of publications, for example [Rid90, Zac90, Eri00, Mak01, Kas91]. Elementary circuit modeling of power converters usually yields detailed continuous-time nonlinear time-varying models in state-space form [Mak01]. Those models focus only on the components which are essential to the power conversion and control processing. Dynamics occurring at frequencies higher than the switching frequency are neglected, e.g. dynamics due to snubber networks.

Additionally to the multitude of modeling methods there are several different transfer functions, which can be derived representing the dynamic behavior of a state variable (inductor current or capacitor voltage) under variation of an input variable (duty-ratio, input voltage, load, etc.).

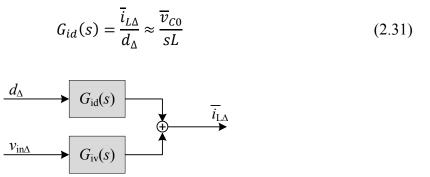

In this work the state space modeling method is utilized to derive the small signal controlto-inductor-current transfer function

$$G_{id}(s) = \frac{\overline{i}_{L\Delta}}{d_{\Delta}}$$

(2.17)

in order to design the current controller later on. Thereby the inductor current represents the control variable and the duty-ratio the actuating variable. The small signal values are indicated by ' $\Delta$ '.

Transfer functions can only be determined for linear systems. For this reason linearization around a certain operating point is required in order to analyze the small signal dynamic behavior of the non-linear system. With state space modeling only the average values of the variables within each switching cycle are considered.

In CCM the two different positions of the boost switch result in two different linear systems depicted in Figure 2.9 a) and b). Considered are the state variables inductor current  $i_L$  and capacitor voltage  $v_C$ .

Interval I.  $(dT_s)$ : switch closed

$$\frac{di_L}{dt} = \frac{1}{L}v_{in} \tag{2.18}$$

$$\frac{dv_c}{dt} = -\frac{1}{C}\frac{v_c}{R} \tag{2.19}$$

Interval II.  $(d'T_s)$ : switch open

$$\frac{di_L}{dt} = \frac{1}{L}(v_{in} - v_C)$$

(2.20)

$$\frac{dv_c}{dt} = \frac{1}{C} \left( i_L - \frac{v_c}{R} \right) \tag{2.21}$$

By averaging both intervals over one switching cycle the dynamic average values for the state-variables result (cf. Figure 2.19) [Böc09]. For the inductor current the dynamic average value is

$$\frac{d\overline{i}_L}{dt} = \frac{1}{T_s} \frac{1}{L} \left[ \int_0^{dT_s} v_{in} dt + \int_{dT_s}^{T_s} (v_{in} - \overline{v}_c) dt \right]$$

$$= \frac{1}{L} (v_{in} - d'\overline{v}_c).$$

(2.22)

With similar calculation the equation for the dynamic average value of the capacitor voltage results as

$$\frac{d\overline{\nu}_C}{dt} = \frac{1}{C} \left( d'\overline{i}_L - \frac{\overline{\nu}_C}{R} \right).$$

(2.23)

Figure 2.19: Dynamic average value of the inductor current

The required small signal dynamic model is determined by applying a small perturbation around a steady-state operating point. The operating point for this linearizing process is given by

$$\begin{aligned}

\overline{i}_{L} &= \overline{i}_{L0} + \overline{i}_{L\Delta} \\

\overline{v}_{C} &= \overline{v}_{C0} + \overline{v}_{C\Delta} \\

d' &= d'_{0} + d'_{\Delta} \\

v_{in} &= v_{in0} + v_{in\Delta}

\end{aligned}$$

(2.24)

The '0' indicates the steady state value of the observed operating point. Inserting Eq. (2.24) into Eq. (2.22) and Eq. (2.23), it follows

$$\frac{d\overline{i}_{L\Delta}}{dt} = \frac{1}{L} \left( -d'_0 \overline{v}_{C0} - d'_0 \overline{v}_{C\Delta} - d'_\Delta \overline{v}_{C0} + v_{in0} + v_{in\Delta} \right)$$

(2.25)

and

$$\frac{d\overline{\nu}_{C\Delta}}{dt} = \frac{1}{C} \left( d'_0 \overline{i}_{L0} + d'_0 \overline{i}_{L\Delta} + d'_\Delta \overline{i}_{L0} - \frac{\overline{\nu}_{C0}}{R} - \frac{\overline{\nu}_{C\Delta}}{R} \right).$$

(2.26)

Since  $d'_0 \overline{v}_{C0} = v_{in0}$  and  $d'_0 \overline{i}_{L0} = \overline{v}_{C0}/R$ , these terms eliminates each other. Both equations are transferred into Laplace domain in order to derive the required transfer function:

$$s\overline{i}_{L\Delta} = \frac{1}{L} \left( -d'_0 \overline{v}_{C\Delta} - d'_\Delta \overline{v}_{C0} + v_{in\Delta} \right)$$

(2.27)

$$s\overline{\nu}_{C\Delta} = \frac{1}{C} \left( d_0' \overline{i}_{L\Delta} + d_\Delta' \overline{i}_{L0} - \frac{\overline{\nu}_{C\Delta}}{R} \right)$$

(2.28)

With inserting Eq. (2.28) in Eq. (2.27) and solving for  $\overline{i}_{L\Delta}$ , it follows

$$\bar{i}_{L\Delta} = -d'_{\Delta} \frac{\bar{v}_{C0}(sRC+2)}{s^2 LRC + sL + {d'_0}^2 R} + v_{in\Delta} \frac{(sRC+1)}{s^2 LRC + sL + {d'_0}^2 R}.$$

(2.29)

This equation indicates that the average inductor current is not only influenced by the control variable  $d'_{\Delta}$ , but also due to variations in the input voltage  $v_{in\Delta}$ . The small signal model can be separated in the control-to-inductor-current and the line-voltage-to-inductor-current transfer function (cf. Figure 2.20). The control-to-inductor-current transfer function results from the first term on the right side of Eq. (2.29). However, typically d' is not the applied control variable but d. Therefore the substitution  $d'_{\Delta} = -d_{\Delta}$  is performed for the small signal model. Thus, the control-to-inductor-current transfer function for the boost converter in CCM results as

$$G_{id}(s) = \frac{\overline{i}_{L\Delta}}{d_{\Delta}} = \frac{\overline{v}_{C0}(sRC+2)}{s^{2}LRC+sL+{d'_{0}}^{2}R}.$$

(2.30)

In the high-frequency region the following approximation can be done to simplify the transfer function [Zac90]:

Figure 2.20: Block diagram of the small signal average inductor current model

From the second term of Eq. (2.29) the line-voltage-to-inductor-current transfer function results as

$$G_{iv}(s) = \frac{\overline{i}_{L\Delta}}{v_{in\Delta}} = \frac{(sRC+1)}{s^2 LRC + sL + {d'_0}^2 R}.$$

(2.32)

This equation describes the influences on the inductor current due to line voltage variation. The line voltage acts as a disturbance variable on the control loop and especially in PFC applications the variation in the line voltage is significant. Because the variation in the line voltage occurs periodically with line frequency the disturbances is predictable and can be partly compensated by a disturbance variable feed-forward control. Such an approach is proposed in [Keu13]. But since the switching frequency is typically in the range of several

10kHz, the change of the input voltage during a few switching cycles is small and therefore can be neglected for the design of the current compensator.

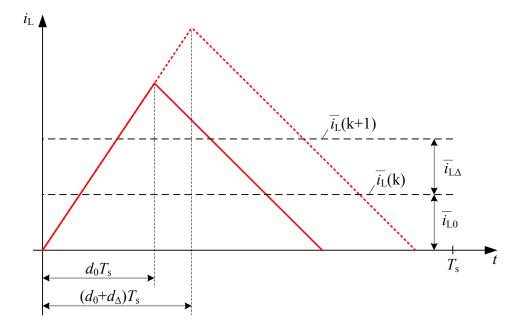

The control-to-inductor-current transfer function of Eq. (2.30) is only valid, if the boost converter operates in CCM. Consequently, a separate model for DCM operation needs to be generated. In DCM there is the third interval within each switching cycle where the switch is open and the inductor current is zero (cf. Figure 2.9 c)).

Interval III.  $(d''T_s)$ : switch open and  $i_L = 0$

$$\frac{di_L}{dt} = 0 \tag{2.33}$$

$$\frac{dv_c}{dt} = -\frac{1}{C}\frac{v_c}{R} \tag{2.34}$$

In order to change the average inductor current in CCM, the current value at the end of the switching cycle must be different to the value at the beginning of the switching cycle. In DCM the inductor current does not behave as a true state space variable anymore, since it has no free boundaries but is fixed to zero at the beginning and the end of each switching cycle. Consequently, the inductor current of each cycle is independent and does not carry any information to the following cycle [Ara09]. For the dynamic behavior of the converter average model this means that with changing from CCM to DCM the order of the system is reduced by one (from one to zero) [Böc09]. Instead of a differential equation the inductor average current in DCM is represented by the algebraic equation

$$\overline{i}_L = \frac{d^2 T_s}{2L} \frac{\overline{v}_C v_{in}}{\overline{v}_C - v_{in}}.$$

(2.35)

However, within each switching cycle, the inductor current is still a dynamic variable and does contribute to the fast dynamics of the converter [Ara09]. Figure 2.21 illustrates that the average inductor current can be influenced as usual by changing the duty-ratio. The change of the average current from cycle to cycle is given by

$$\overline{i}_{L\Delta} = \overline{i}_L(k+1) - \overline{i}_L(k).$$

(2.36)

For the small signal dynamic model the steady-state operating point for the linearizing process is defined by

$$\overline{i_L} = \overline{i_{L0}} + \overline{i_{L\Delta}} d = d_0 + d_\Delta.$$

(2.37)

Applying this operation point on Eq. (2.35) and inserting in Eq. (2.36) it follows

$$\overline{i}_{L\Delta} = \frac{(d_0 + d_\Delta)^2 T_s}{2L} \frac{\overline{v}_C v_{in}}{\overline{v}_C - v_{in}} - \frac{d_0^2 T_s}{2L} \frac{\overline{v}_C v_{in}}{\overline{v}_C - v_{in}}.$$

(2.38)

With rearranging this equation one gets

$$\overline{i}_{L\Delta} = \frac{T_s}{2L} \frac{\overline{v}_C v_{in}}{\overline{v}_C - v_{in}} (2d_0 d_\Delta + d_\Delta^2).$$

(2.39)

Figure 2.21: Dynamic inductor average current in DCM

Typically the small signal change in the duty-ratio is small compared to the large signal duty-ratio ( $d_{\Delta}^2 \ll d_{\Delta}$ ). Consequently, the second term of the equation can be neglected and the duty-ratio-to-inductor-current transfer function for DCM can be stated as

$$G_{id,DCM}(s) = \frac{\overline{i}_{L\Delta}}{d_{\Delta}} \approx \frac{\overline{v}_{C} v_{in} d_{0} T_{s}}{(\overline{v}_{C} - v_{in})L}.$$

(2.40)

## 2.5 Current Control Design

Responsible for a good power factor in PFC applications is the current control loop. The most common current control method for PFC, average current control in CCM, is described in this section. For this purpose a well designed current compensator is required, which lets the average inductor current track the sinusoidal reference value as good as

possible. In the cascaded control structure of PFC rectifiers the current control loop is the inner loop with the highest bandwidth.

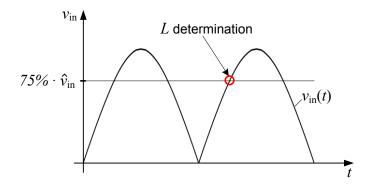

The model of the boost converter derived in the previous section depends on the operating point. Especially in PFC applications with its continuously varying input voltage and current the operation point changes extremely within each line half-cycle (cf. Figure 2.22). But, since the switching frequencies of PFC rectifiers are generally well above line frequency, input and output voltage can be considered as constant values during several switching cycles (Quasi-Static Approach) [Jov06]. Thus, the known small signal model Eq. (2.30) can be utilized for the control loop design.

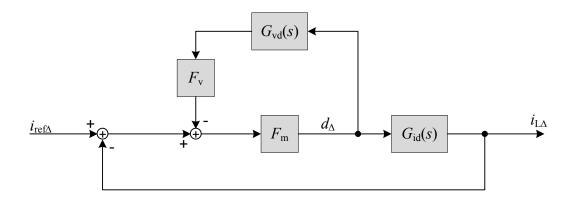

Figure 2.22: Varying operation point within line half-cycle

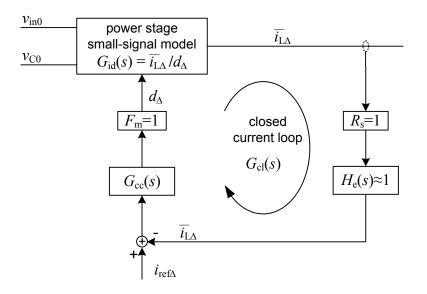

In the small signal block diagram of Figure 2.23 additionally the transfer characteristics  $F_m$  of the PWM and  $R_s$  of the current sensing are depicted and need to be considered. They typically have a constant gain and are assumed to be unity in the following design example. In [Rid90] the characteristic  $H_e(s)$  of the data-sampling nature for the boost converter current loop is derived. However, since the current loop crossover frequency  $f_{ci}$  satisfies  $f_{line} \ll f_{ci} \ll f_s/2$ , the high-frequency block diagram can be simplified by neglecting  $H_e(s)$  [Jov06].

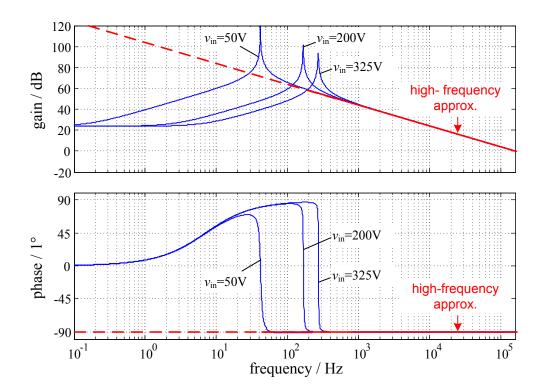

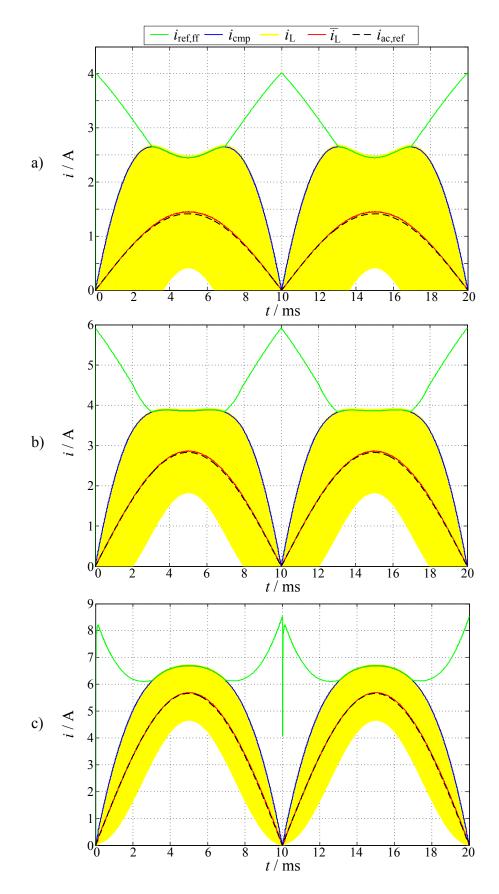

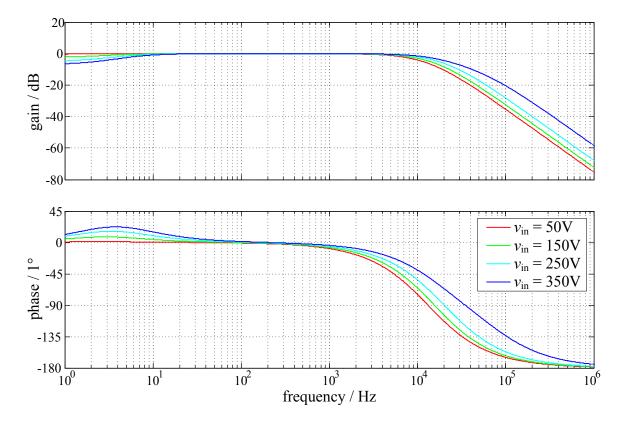

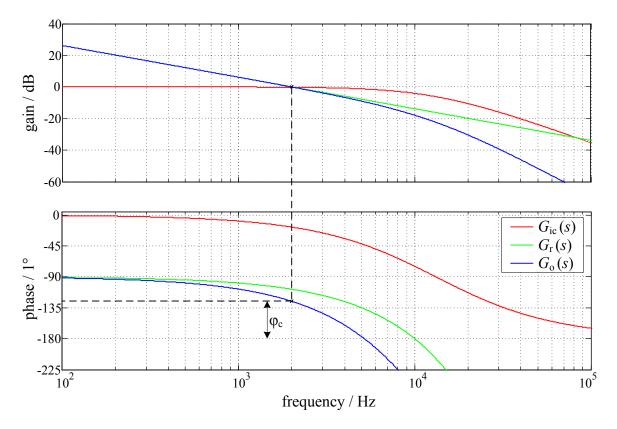

Due to the permanently varying operating point in PFC applications the complete operation range needs to be considered and the worst-case operating point must be identified for controller design. Figure 2.24 shows Bode plots of the boost converter control-to-inductorcurrent transfer function  $G_{id}(s)$  of different operating points. Note that for all Bode Plots normalized transfer functions are utilized, e.g.  $G_{id}(s) = (\overline{i}_{L\Delta}/1A)/d_{\Delta}$ . In Figure 2.24 it can be seen that the gain of  $G_{id}(s)$  is low at low frequencies and depend on the instantaneous line voltage and load current. However, at high frequencies the gain of  $G_{id}(s)$  does not depend on input voltage or load current. Since the current loop is a fast control loop the high-frequency approximation of  $G_{id}(s)$  Eq. (2.31) can be utilized for design purpose.

*Figure 2.23:* Block diagram of closed average current control loop  $G_{cl}(s) = \frac{i_{L\Delta}}{i_{ref\Delta}}$

Figure 2.24: Bode plot of the normalized boost converter control-to-inductor-current transfer function  $G_{id}(s)$  for different operating points

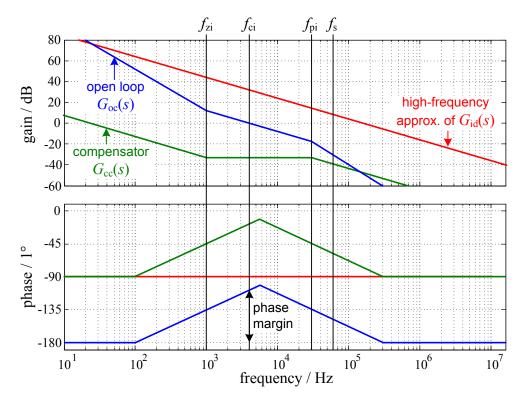

Typically a PI type compensator for the current loop is applied. Its pole at zero frequency (integrator) increases the low-frequency gain of the control loop. The zero is required to get sufficient phase margin at crossover frequency  $f_{ci}$ . For adequate stability a phase margin of at least 45° is recommended. Therefore the frequency of the zero  $f_{zi}$  should be

approximately at  $f_{zi} = f_{ci}/4$  [Jov06, Zac90b]. A good choice for the crossover frequency is  $f_{ci} = 2 - 8$  kHz. In order to attenuate switching noise in the current signal, it is advisable to add an additional pole well above crossover frequency without affecting the stability of the current loop. A good choice for this pole is at  $f_{pi} = f_s/2$  [Jov06].

In Figure 2.25 the asymptotic Bode plots of the current compensator  $G_{cc}(s)$ , the high-frequency approximation of  $G_{id}(s)$  and of the resulting open-loop transfer function  $G_{oc}(s)$  are illustrated.

*Figure 2.25: Asymptotic Bode plots of high-frequency approximation of the normalized control-to-inductor-current transfer function, compensator transfer function and open loop transfer function*

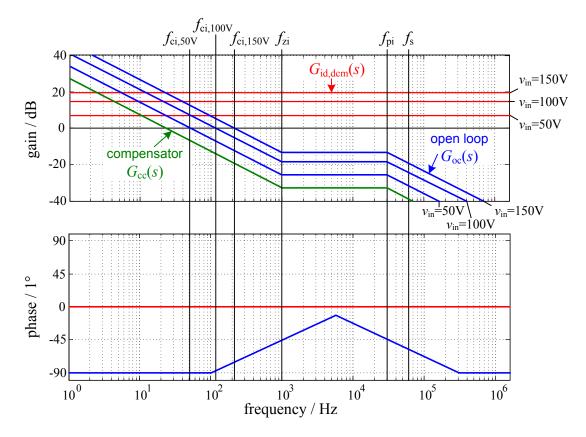

The design of the current compensator is done for CCM to achieve good power factor, but stable operation with adequate dynamic during DCM needs also be ensured. The DCM transfer function (Eq. (2.40)) has a constant gain versus frequency of only a few dB (cf. Figure 2.26). This results in a cross over frequency of the open current loop of only several 10Hz up to few 100Hz. Thus, the current loop has not suitable dynamic to track the current reference value in DCM. However, due to the fact that the loop gain and accordingly the current average value in DCM depends on the input voltage (cf. Eq. (2.35)), a reasonable tracking of the reference current is achieved. Especially at low input voltages, where DCM typically occurs, the average current follows the input voltage almost linearly.

The converter parameters which were used for the controller design are given in Table 2.2.

Figure 2.26: Asymptotic Bode plots of the normalized control-to-inductor-current transfer function in DCM for different input voltages at  $P_{out} = 500$ W, compensator transfer function and resulting open loop transfer functions

| symbol                    | denotation                   | value |

|---------------------------|------------------------------|-------|

| L                         | boost inductor               | 400µH |

| С                         | output capacitor             | 560µF |

| R <sub>100%</sub>         | load resistance at full load | 160Ω  |

| $R_{50\%}$                | load resistance at half load | 320Ω  |

| $v_{\rm out} = v_{\rm C}$ | output voltage               | 400V  |

| Pout                      | nominal output power         | 1000W |

| $f_s = 1/T_s$             | switching frequency          | 60kHz |

Table 2.2:

Converter parameters utilized for the controller design

## 2.6 Voltage Control Design

Besides tracking the input current in order to get the same shape like the input voltage and consequently unity power factor, the second task for PFC rectifiers is to provide constant output voltage. Due to the sinusoidal input voltage and input current a pulsating input power occurs, which causes an unavoidable voltage ripple with twice the line frequency at the output. The amount of this ripple mainly depends on the average input power and the value of the output capacitance. Since the ripple in the output voltage is based on physical reasons, it cannot be compensated with the voltage loop without interfering the power factor. Consequently, a good PFC requires that the output of the voltage compensator is constant during half of the line period. For the voltage loop design this means, that the bandwidth needs to be much lower than twice the line frequency in order to sufficiently attenuate second-harmonic ripple of the output voltage at compensator output [Jov06]. On the other hand a too slow voltage loop cannot respond to load changes in reasonable time. Thus, determining the bandwidth of the voltage loop is a trade-off. A good range for the crossover frequency is  $f_{cv} = 5 - 15$ Hz.

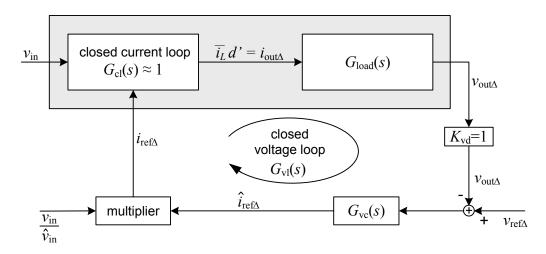

Since the voltage-loop is much slower than the current-loop, both control loops can be designed independent from each other. Furthermore, it is not essential for the voltage loop design which current control method is implemented in the inner control, i.e. it can be the same for any type of current control. The closed current loop is part of the control path in the voltage loop and can be assumed to be unity at the low crossover frequency of the voltage loop.

Figure 2.27: Block diagram of closed voltage control loop  $G_{vl}(s) = \frac{v_{out\Delta}}{v_{ref\Delta}}$

The block diagram of the output voltage control loop is depicted in Figure 2.27. For the design example the voltage divider  $K_{vd}$  for the output voltage measurement and the multiplier are assumed to have a constant gain of |G(s)| = 1. Thus, only the transfer characteristic of the output capacitor with connected load remains, which needs to be

considered for the design of the voltage compensator. Assuming a resistive load with  $R_{load} = R_{100\%}$  (cf. Table 2.2) the transfer characteristic of the load results to

$$G_{load}(s) = \frac{v_{out\Delta}}{i_{out\Delta}} = \frac{R_{100\%}}{1 + sR_{100\%}C_{out}}.$$

(2.41)

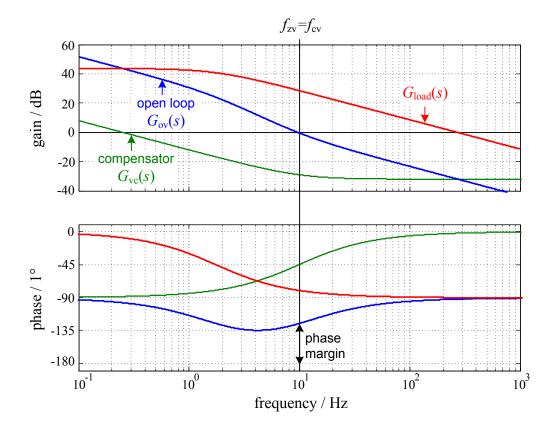

As voltage compensator a PI-type controller is applied, which has the zero at approximately  $f_{zv} = f_{cv}$  to achieve a phase margin of at least 45° (55° is achieved with the applied values). Figure 2.28 shows the Bode plots of the load, the voltage compensator and the resulting open loop transfer function.

Figure 2.28: Bode plots of the normalized voltage loop control path  $G_{load}(s)$ , compensator transfer function  $G_{vc}(s)$  and open loop transfer function  $G_{ov}(s)$

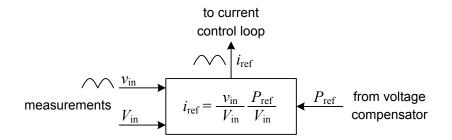

## 2.7 Multiplier and Load Feed-Forward Control

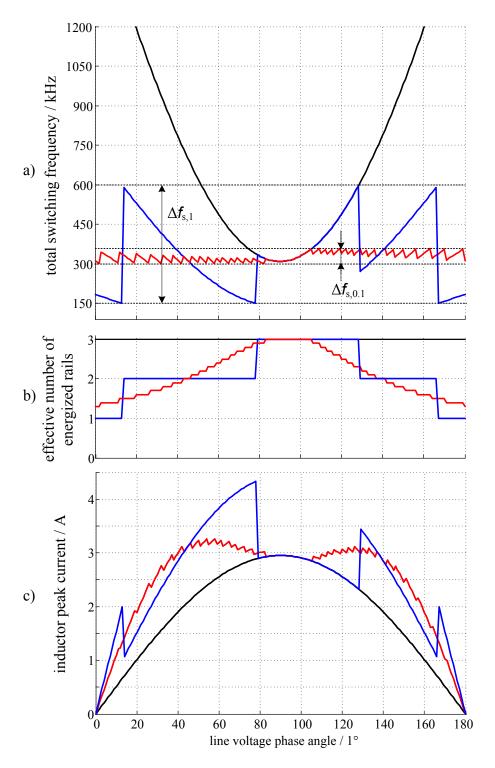

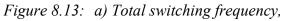

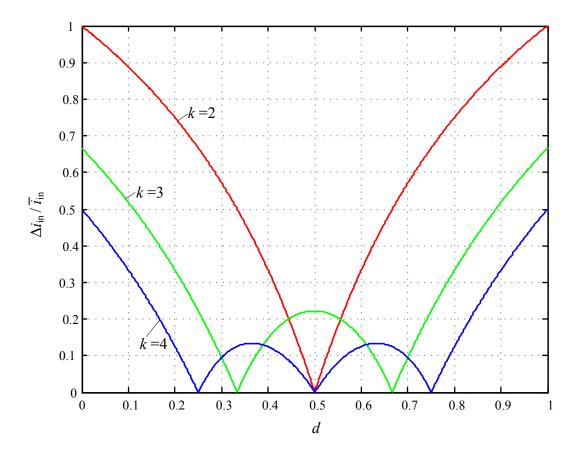

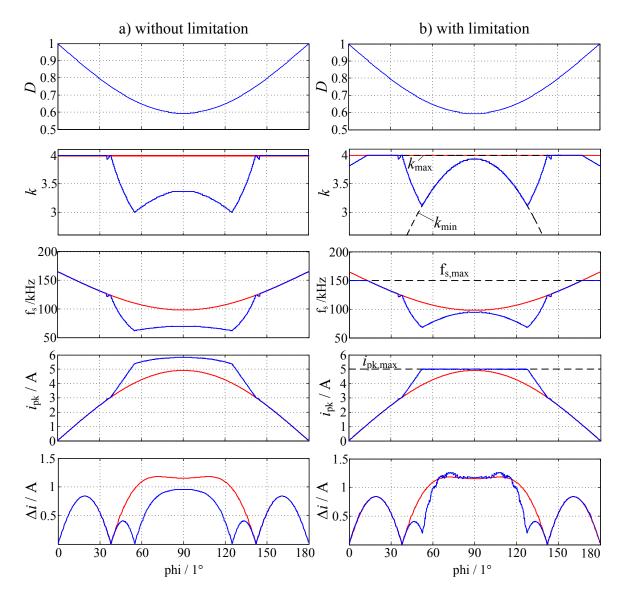

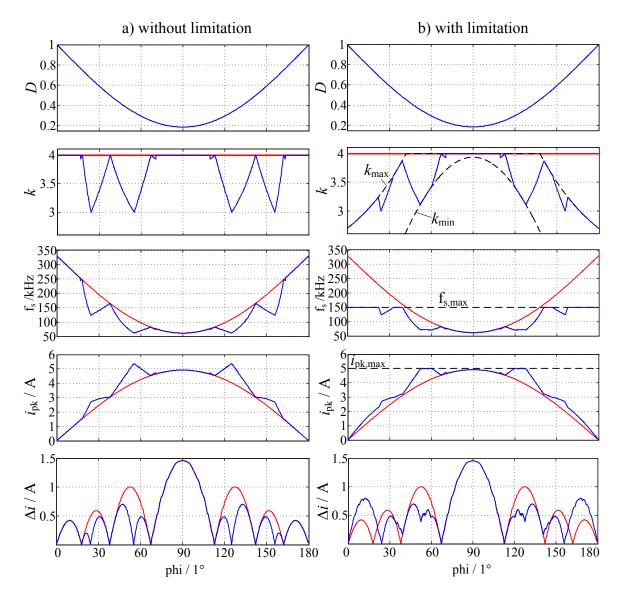

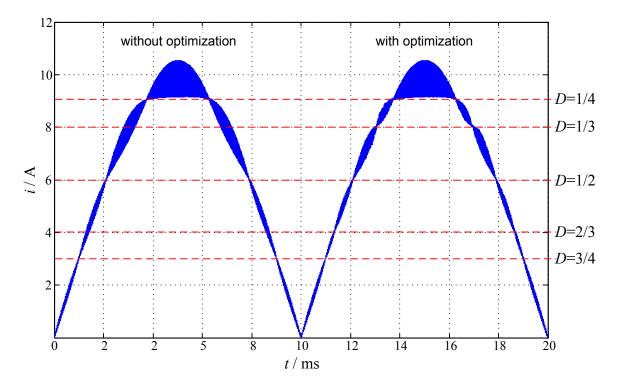

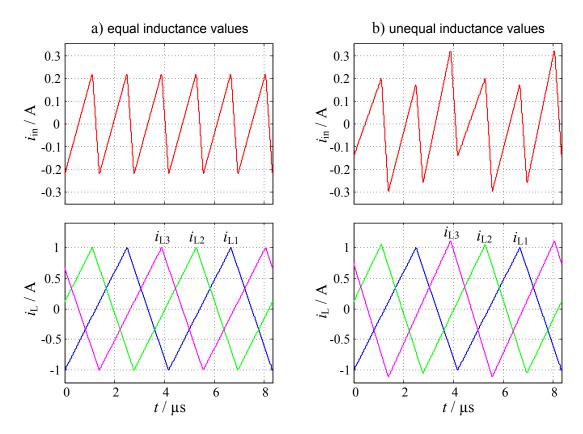

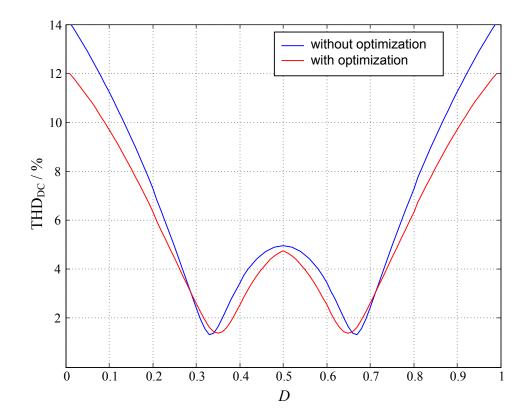

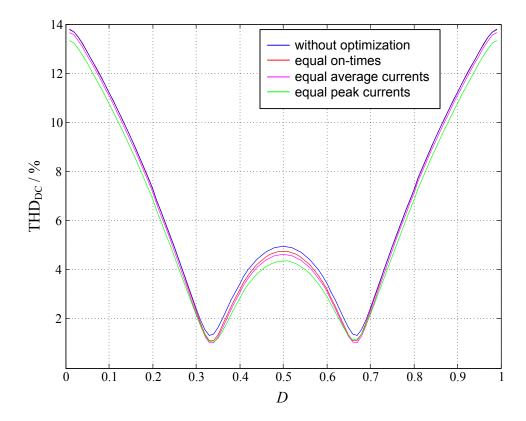

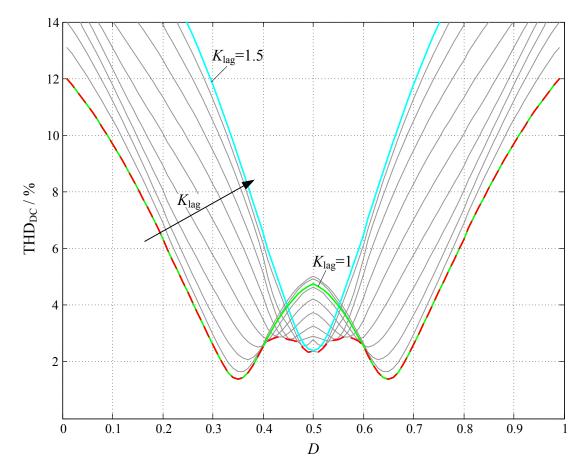

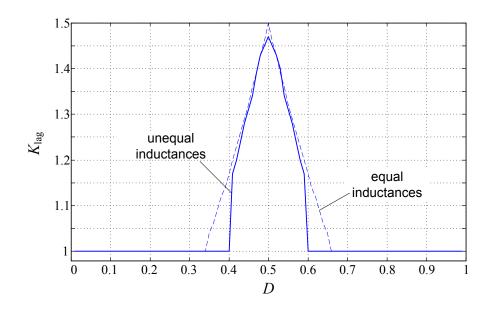

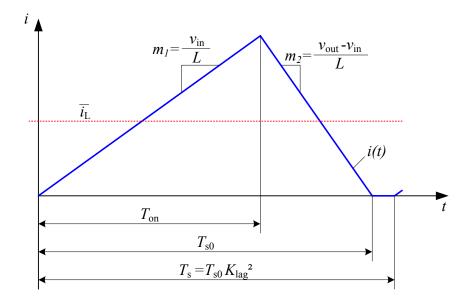

The main difference between the PFC rectifier control structure and that of conventional DC-DC converters is the multiplier and load feed-forward unit depicted in Figure 2.29. The multiplier is utilized to generate the sinusoidal reference value for the current control loop in order to achieve unity power factor. For this purpose a normalized signal of the rectified input voltage needs to be generated. This means that the instantaneous value of the rectified input voltage needs to be divided by a value which is proportional to the DC