# Adaptive Virtual Machine Scheduling and Migration for Embedded Real-Time Systems

Stefan Groesbrink, M.Sc.

A thesis submitted to the Faculty of Computer Science, Electrical Engineering and Mathematics of the University of Paderborn in partial fulfillment of the requirements for the degree of doctor rerum naturalium (Dr. rer. nat.)

2015

### Abstract

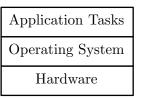

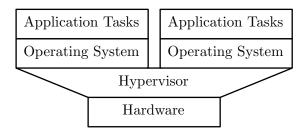

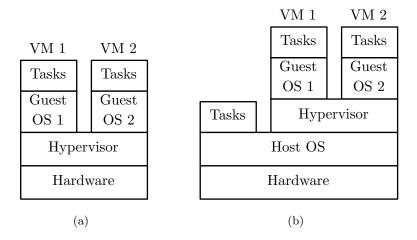

Integrated architectures consolidate multiple functions on a shared electronic control unit. They are well suited for embedded real-time systems that have to implement complex functionality under tight resource constraints. Multicore processors have the potential to provide the required computational capacity with reduced size, weight, and power consumption. The major challenges for integrated architectures are robust encapsulation (to prevent that the integrated systems corrupt each other) and resource management (to ensure that each system receives sufficient resources). Hypervisor-based virtualization is a promising integration architecture for complex embedded systems. It refers to the division of the hardware resources into multiple isolated execution environments (virtual machines), each hosting a software system of operating system and application tasks.

This thesis addresses the hypervisor's management of the resource computation time, which has to enable multiple real-time systems to share a multicore processor with all of them completing their computations as demanded. State of the art approaches realize the sharing of the processor by assigning exclusive processor cores or fixed processor shares to each virtual machine. For applications with a computation time demand that varies at run-time, such static solutions result in a low utilization, since the pessimistic worst-case demand has to be reserved at all times, but is often not needed. Therefore, adaptability is desired in order to utilize the shared processor efficiently, but without losing the real-time capability as a prerequisite for the integration.

The first contribution of this thesis is an algorithm for the partitioning of virtual machines to homogeneous cores, which produces mappings that support adaptive scheduling and the protection of safety-critical systems. The second contribution is a virtual machine scheduling architecture that combines real-time guarantees with an adaptive management of the computing power. The third contribution is a technique for real-time virtual machine migration. Together, these contributions enable the integration of independently developed and validated systems on top of a hypervisor. The processing time redistribution in case of mode changes and execution time variations follows the varying demand effectively. Adaptive measures are taken as well to protect critical systems. In case of a worst-case execution time overrun of a critical systems. In case of a hardware failure, migration is performed to continue the operation of systems on other processors. A prototype demonstrates the feasibility.

### Zusammenfassung

Integrierte Architekturen konsolidieren mehrere Funktionen auf einem gemeinsam genutzten Steuergerät. Sie sind für eingebettete Echtzeitsysteme geeignet, die komplexe Funktionalität ressourceneffizient implementieren müssen. Mehrkernprozessoren bergen das Potential die erforderliche Rechenleistung bei reduzierter Größe, Gewicht und Leistungsaufnahme zu bieten. Die größten Herausforderungen integrierter Architekturen sind eine robuste Isolation der integrierten Systeme und eine Ressourcenverwaltung, die jedem System die Erfüllung ihrer Anforderungen garantiert. Hypervisor-basierte Virtualisierung ist eine vielversprechende Integrationsarchitektur für komplexe eingebettete Systeme. Es bezeichnet die Aufteilung der Hardwareressourcen in mehrere isolierte Ausführungsumgebungen (virtuelle Maschinen), von denen jede ein Softwaresystem aus Betriebssystem und Anwendungen beinhaltet.

Diese Dissertation befasst sich mit der Verwaltung der Ressource Rechenzeit durch den Hypervisor, so dass alle Systeme die einen Prozessor gemeinsam nutzen ihre Berechnungen wie erforderlich durchführen können. Stand der Technik ist das Teilen des Prozessors durch die Zuweisung exklusiver Prozessorkerne oder festgesetzter Ausführungszeitanteile zu allen virtuellen Maschinen. Solch statische Ansätze führen jedoch bei Anwendungen deren Bedarf zur Laufzeit schwankt zu einer geringen Auslastung, da der Bedarf für den ungünstigsten Fall zu jeder Zeit reserviert werden muss, oft aber nicht benötigt wird. Aus diesem Grund ist Anpassungsfähigkeit für die effiziente Nutzung des geteilten Prozessors wünschenswert, ohne die Echtzeitfähigkeit als Voraussetzung für die Integration zu verlieren.

Der erste Beitrag dieser Dissertation ist ein Algorithmus für die Aufteilung der virtuellen Maschinen auf homogene Prozessorkerne. Er produziert Zuweisungen, die adaptive Ablaufsteuerungen und den Schutz sicherheitskritischer Systeme unterstützen. Der zweite Beitrag ist eine Technik zur Ablaufsteuerung von virtuellen Maschinen, welche Antwortzeitgarantien mit einer adaptiven Verwaltung der Prozessorleistung verbindet. Der dritte Beitrag ist eine Technik zur echtzeitfähigen Migration virtueller Maschinen. Zusammen ermöglichen es diese Beiträge unabhängig voneinander entwickelte Systeme mithilfe eines Hypervisors zu integrieren. Die Neuverteilung der Prozessorleistung im Falle von Betriebsmoduswechseln und Ausführungszeitschwankungen reagiert effektiv auf Veränderungen des Bedarfs. Adaptive Maßnahmen werden zudem zum Schutz sicherheitskritischer Systeme durchgeführt. Wenn ein solches System die reservierte Ausführungszeit überschreitet, wird versucht durch das Stehlen von Ausführungszeit von unkritischen Systemen das kritische System zu schützen. Im Falle von Hardwarefehlern wird Migration zur Fortsetzung des Betriebs auf einem anderen Prozessor angewandt. Ein Prototyp demonstriert die Machbarkeit. To my parents.

### ACKNOWLEDGEMENTS

I express my deep gratitude to my advisors Prof. Franz-Josef Rammig and Prof. Luis Almeida. Their support, ambition, dedication, tenacity, and expertise are the foundation of this work.

I would like to thank my committee Prof. Marco Platzner, Prof. Christian Plessl, and Dr. Stefan Sauer.

I am also grateful to my brilliant colleagues in Paderborn and Porto.

Foremost, I thank my family for their unwavering support, understanding, and encouragement. I am deeply thankful to Anne, for all the love, support, and patience.

# Contents

| C        | onter          | nts      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | vii |

|----------|----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|          | Abb            | reviatio | ons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | xi  |

|          | Sym            | bols .   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | xi  |

| 1        | Intr           | oducti   | ion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1   |

|          | 1.1            | Hyper    | visor-based Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1   |

|          | 1.2            | Applie   | cation Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4   |

|          | 1.3            | Adapt    | vive Scheduling of Virtualized Real-Time Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7   |

|          | 1.4            | Outlin   | ne and Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9   |

| <b>2</b> | Fun            | damer    | ntals: Hypervisor-based Multicore Virtualization for Em                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -   |

|          | $\mathbf{bed}$ | ded R    | eal-Time Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13  |

|          | 2.1            | Embe     | dded Real-Time Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14  |

|          |                | 2.1.1    | Embedded Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14  |

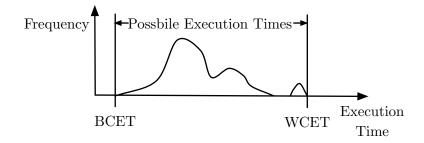

|          |                | 2.1.2    | Real-Time Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15  |

|          |                | 2.1.3    | Mixed-Criticality Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21  |

|          | 2.2            | Hyper    | visor-based Virtualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23  |

|          |                | 2.2.1    | System Virtualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23  |

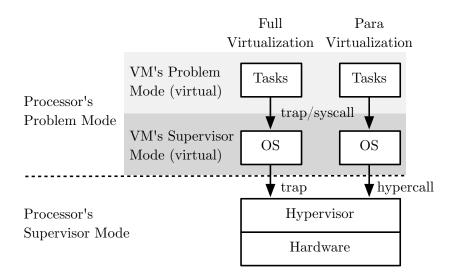

|          |                | 2.2.2    | Processor Virtualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25  |

|          |                | 2.2.3    | $\rm I/O$ Virtualization $\hfill \ldots \hfill \hfill \ldots \hfill \ldots \hfill \hfill \hfill \ldots \hfill \hfill$ | 28  |

|          |                | 2.2.4    | Virtualization for Mixed-Criticality Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29  |

|          | 2.3            | Multic   | core Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32  |

|          |                | 2.3.1    | Multicore Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34  |

|          |                | 2.3.2    | Multicore and Predictability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35  |

|          | 2.4            | Virtua   | al Machine Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37  |

|          |                | 2.4.1    | Hierarchical Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 37  |

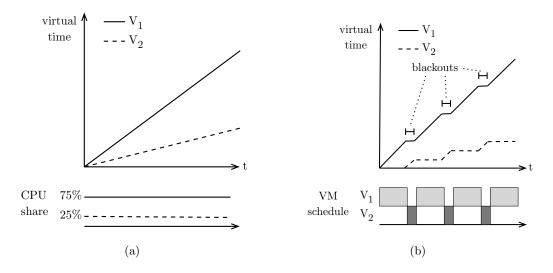

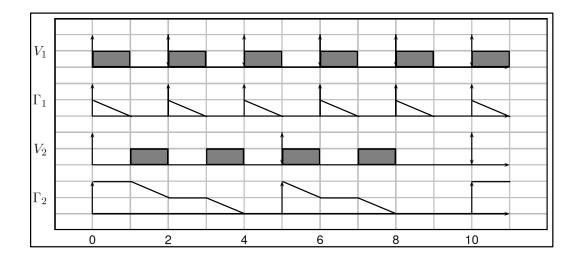

|          |                | 2.4.2    | Virtual Processor and Virtual Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38  |

|          |                | 2.4.3    | Classification and Common Solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40  |

|                                                         | 2.5                                                                                                      | Summary                                       | 43  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----|--|

| 3 A Multicore Hypervisor for Embedded Real-Time Systems |                                                                                                          |                                               | 45  |  |

|                                                         | 3.1                                                                                                      | 1 Problem Statement                           |     |  |

|                                                         | 3.2                                                                                                      | P Related Work                                |     |  |

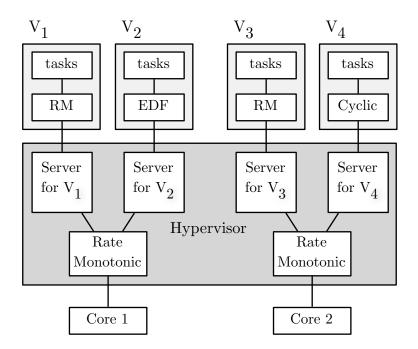

|                                                         | 3.3                                                                                                      | Proteus Multicore Hypervisor                  | 50  |  |

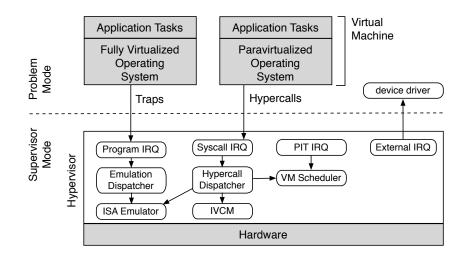

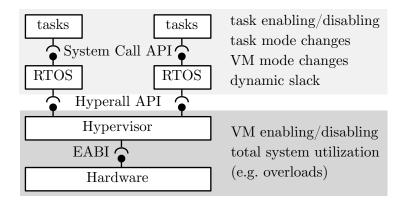

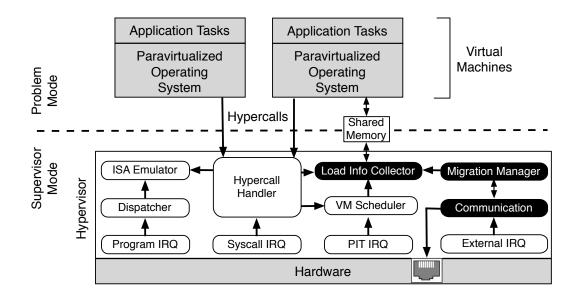

|                                                         |                                                                                                          | 3.3.1 Architecture                            | 51  |  |

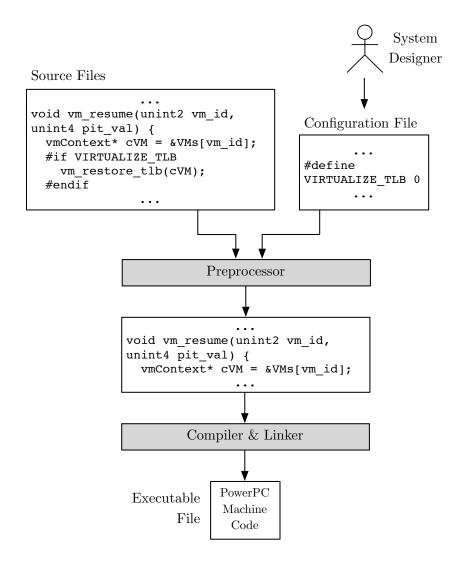

|                                                         |                                                                                                          | 3.3.2 Configurability                         | 52  |  |

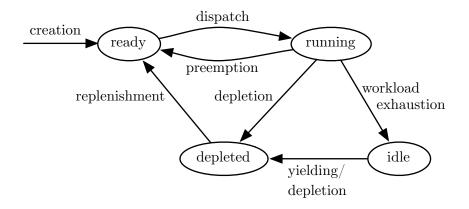

|                                                         |                                                                                                          | 3.3.3 Processor Virtualization                | 55  |  |

|                                                         |                                                                                                          | 3.3.4 Paravirtualization Interface            | 56  |  |

|                                                         |                                                                                                          | 3.3.5 Multicore                               | 57  |  |

|                                                         |                                                                                                          | 3.3.6 Memory Virtualization                   | 59  |  |

|                                                         |                                                                                                          | 3.3.7 Virtualization of Timer and I/O Devices | 59  |  |

|                                                         | 3.4                                                                                                      | Evaluation                                    | 60  |  |

|                                                         |                                                                                                          | 3.4.1 Evaluation Platform: IBM PowerPC 405    | 60  |  |

|                                                         |                                                                                                          | 3.4.2 Execution Times                         | 61  |  |

|                                                         |                                                                                                          | 3.4.3 Memory Footprint                        | 65  |  |

|                                                         | 3.5                                                                                                      | Summary                                       | 66  |  |

| <b>4</b>                                                | Mo                                                                                                       | dels                                          | 69  |  |

|                                                         | 4.1                                                                                                      | Workload Model                                | 70  |  |

|                                                         |                                                                                                          | 4.1.1 Task Model                              | 70  |  |

|                                                         |                                                                                                          | 4.1.2 Virtual Machine Model                   | 73  |  |

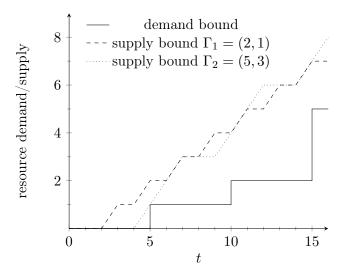

|                                                         | 4.2                                                                                                      | Resource Model                                | 76  |  |

|                                                         | 4.3                                                                                                      | Schedulability Analysis                       | 77  |  |

|                                                         | 4.4                                                                                                      | Suitability of the Model                      | 79  |  |

|                                                         | 4.5                                                                                                      | Related Work                                  | 81  |  |

|                                                         | 4.6                                                                                                      | Summary                                       | 85  |  |

| <b>5</b>                                                | Par                                                                                                      | titioning                                     | 87  |  |

|                                                         | 5.1                                                                                                      | Problem Statement                             | 89  |  |

| 5.2 Related Work                                        |                                                                                                          | Related Work                                  | 90  |  |

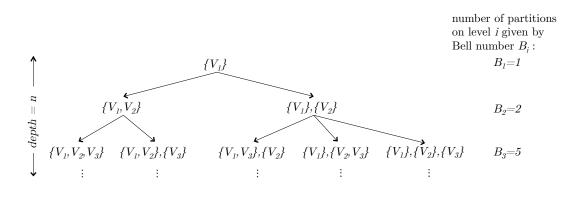

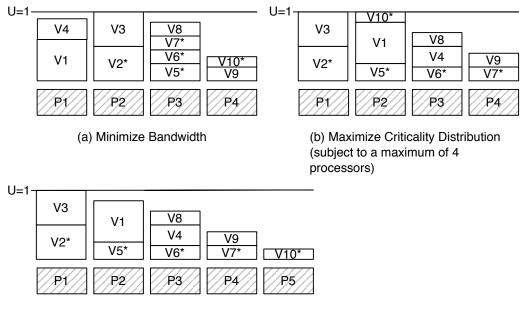

|                                                         | 5.3                                                                                                      | Branch-and-Bound Partitioning                 | 93  |  |

|                                                         |                                                                                                          | 5.3.1 Pruning & Server Transformation         | 94  |  |

|                                                         |                                                                                                          | 5.3.2 Optimization Goals                      | 99  |  |

|                                                         |                                                                                                          | 5.3.3 The Algorithm                           | 100 |  |

|                                                         |                                                                                                          | 5.3.4 Example                                 | 103 |  |

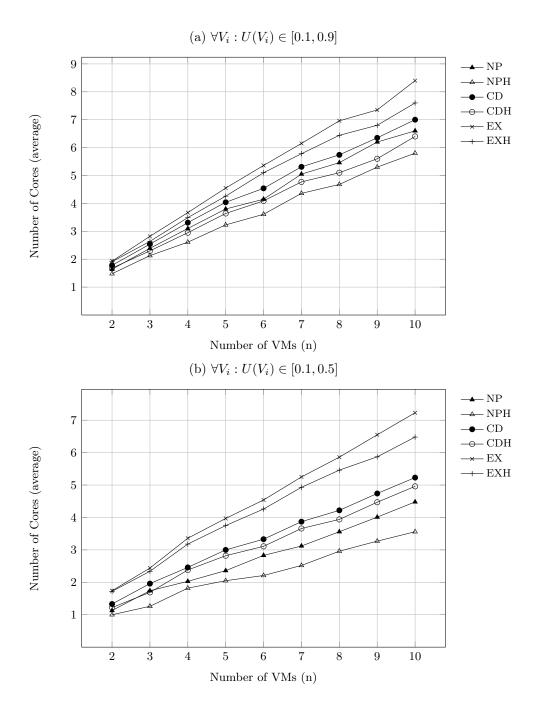

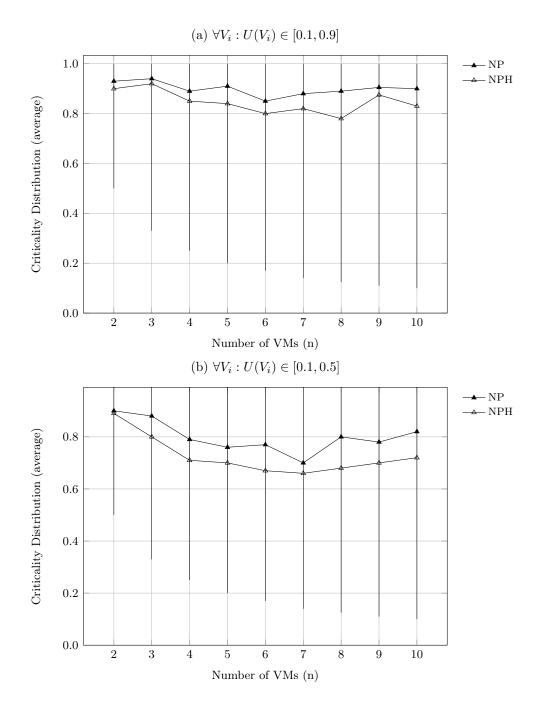

|                                                         | 5.4 Evaluation $\ldots$ |                                               | 103 |  |

|   | 5.5 | Summ   | nary                                                          | 108          |     |

|---|-----|--------|---------------------------------------------------------------|--------------|-----|

| 6 | Ada | aptive | Partitioned Hierarchical Scheduling                           | 109          |     |

|   |     | 6.1    | Proble                                                        | em Statement | 110 |

|   |     | 6.2    | Relate                                                        | ed Work      | 112 |

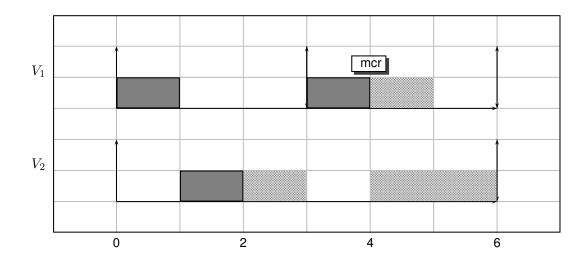

|   | 6.3 | Sched  | uling Architecture                                            | 114          |     |

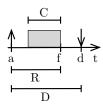

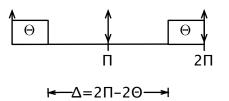

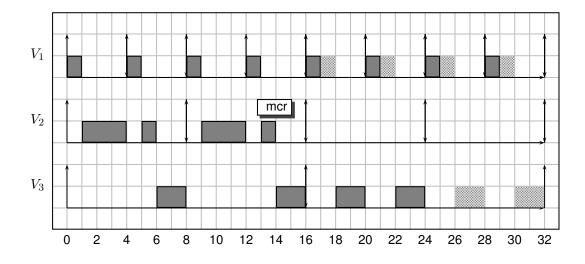

|   |     | 6.3.1  | Server-based Virtual Machine Scheduling                       | 115          |     |

|   |     | 6.3.2  | Fixed Priority Virtual Machine Scheduling                     | 117          |     |

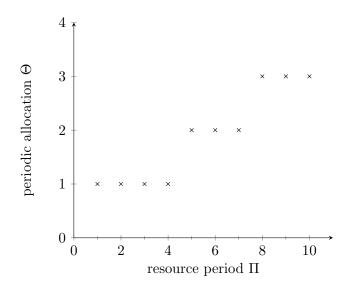

|   | 6.4 | Adapt  | tive Bandwidth Distribution                                   | 118          |     |

|   |     | 6.4.1  | Distributing Structural Slack                                 | 119          |     |

|   |     | 6.4.2  | The Algorithm and its Computational Complexity                | 121          |     |

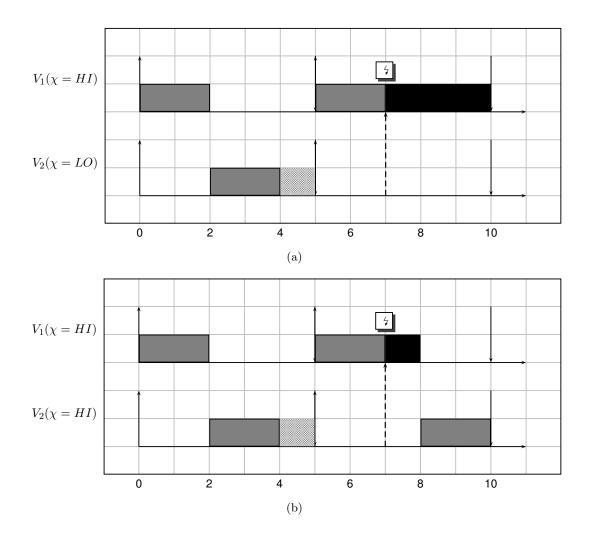

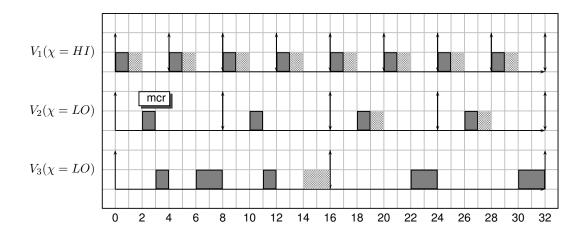

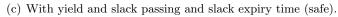

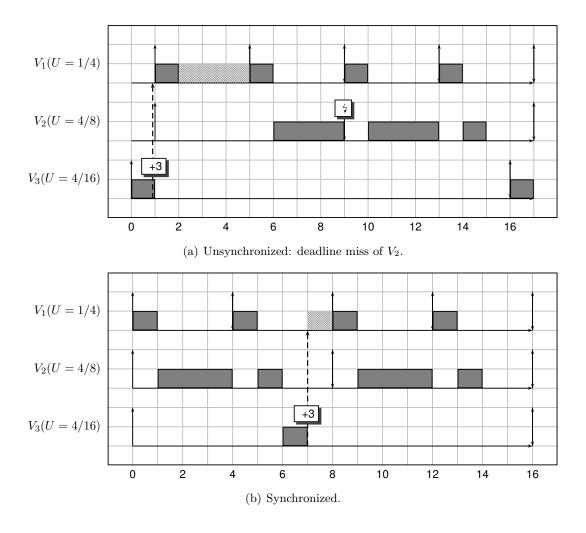

|   |     | 6.4.3  | Protection under Overload Conditions                          | 123          |     |

|   | 6.5 | Corre  | ctness of Bandwidth Distribution                              | 126          |     |

|   |     | 6.5.1  | Steady State: Temporal Isolation and Minimum Bandwidth        |              |     |

|   |     |        | Guarantee                                                     | 127          |     |

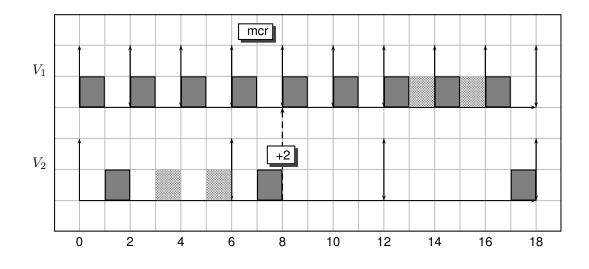

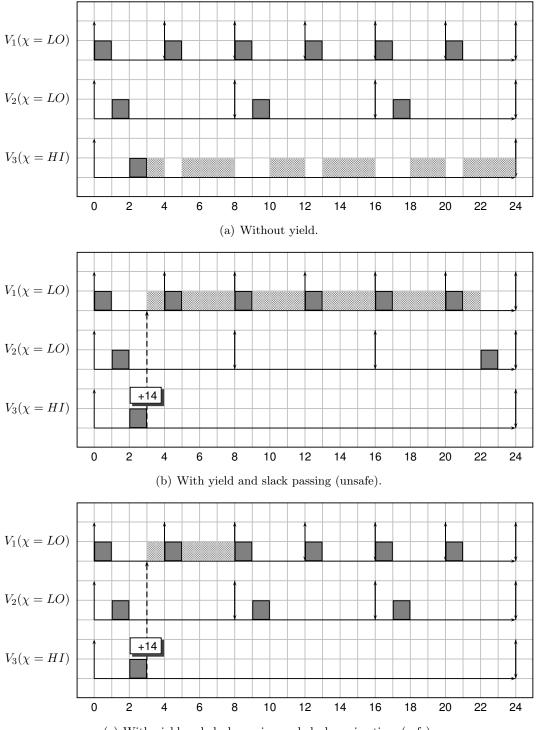

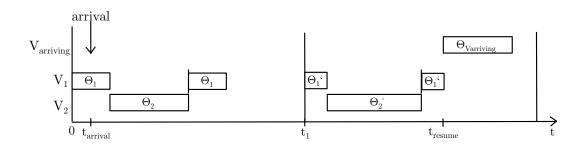

|   |     | 6.5.2  | Correctness during Mode Transitions                           | 129          |     |

|   |     | 6.5.3  | Correctness of Redistribution of Dynamic Slack                | 133          |     |

|   |     | 6.5.4  | Handling of Multiple Mode Change Requests                     | 140          |     |

|   | 6.6 | The C  | Case for Paravirtualization                                   | 140          |     |

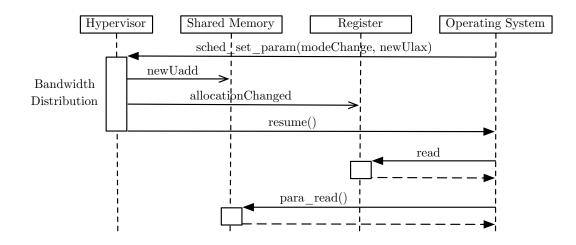

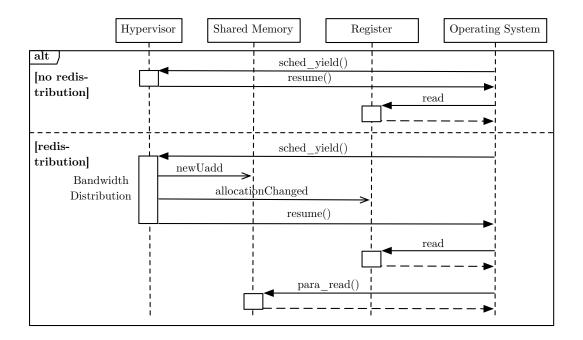

|   | 6.7 | Integr | ration into Hypervisor and Operating System                   | 143          |     |

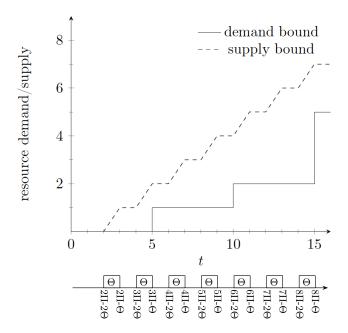

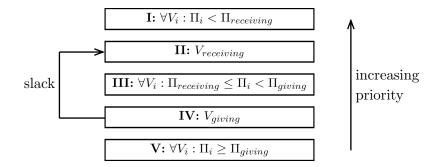

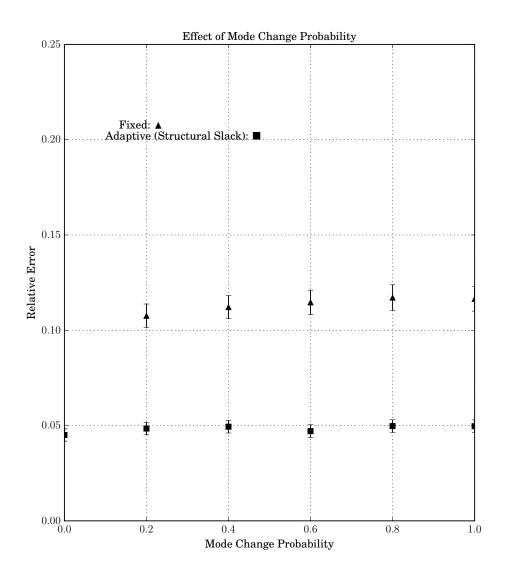

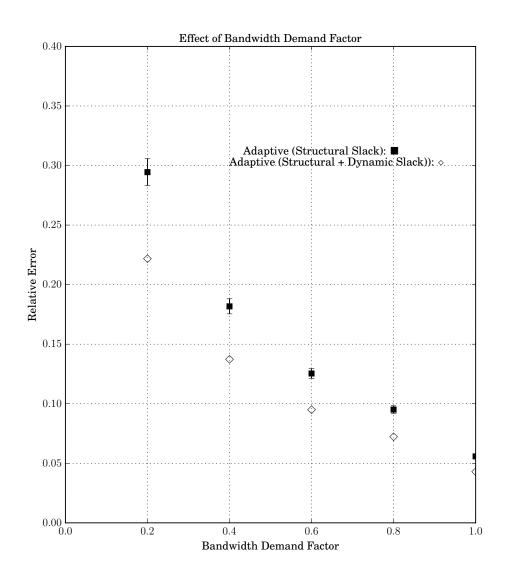

|   | 6.8 | Evalu  | ation                                                         | 144          |     |

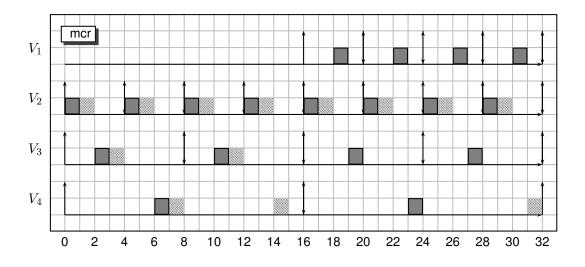

|   |     | 6.8.1  | Scheduling Simulator                                          | 144          |     |

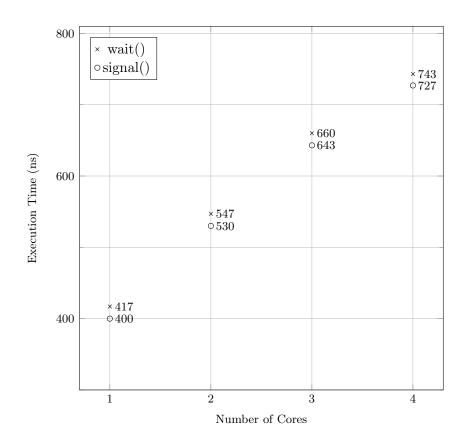

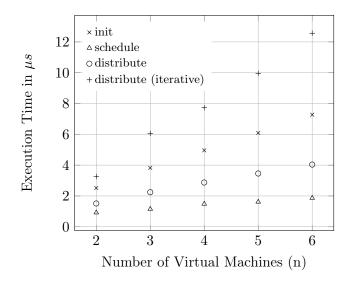

|   |     | 6.8.2  | Execution Times                                               | 146          |     |

|   |     | 6.8.3  | Overhead versus Benefit: Threshold for Slack Redistribution . | 148          |     |

|   |     | 6.8.4  | Memory Footprint                                              | 149          |     |

|   |     | 6.8.5  | Paravirtualization Effort                                     | 150          |     |

|   |     | 6.8.6  | Comparative Evaluation                                        | 150          |     |

|   | 6.9 | Summ   | nary                                                          | 158          |     |

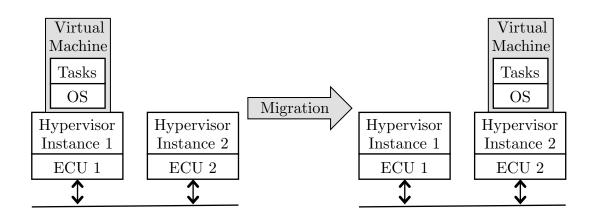

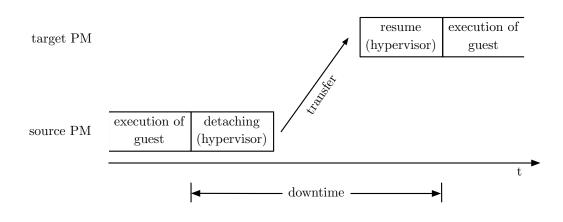

| 7 | Rea | d-Tim  | e Virtual Machine Migration                                   | 161          |     |

|   | 7.1 | Proble | em Statement                                                  | 163          |     |

|   | 7.2 | Relate | ed Work                                                       | 164          |     |

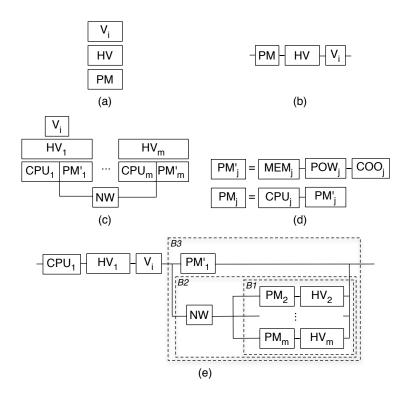

|   | 7.3 | Desig  | n                                                             | 167          |     |

|   |     | 7.3.1  | Migration Policy                                              | 167          |     |

|   |     | 7.3.2  | Integration into the Hypervisor                               | 168          |     |

|   |     | 7.3.3  | Protocol                                                      | 169          |     |

|   |     | 7.3.4  | Migration Test                                                | 171          |     |

|                 |                    | 7.3.5    | Integration into Real-Time Virtual Machine Scheduling $\ . \ .$ . | 173 |

|-----------------|--------------------|----------|-------------------------------------------------------------------|-----|

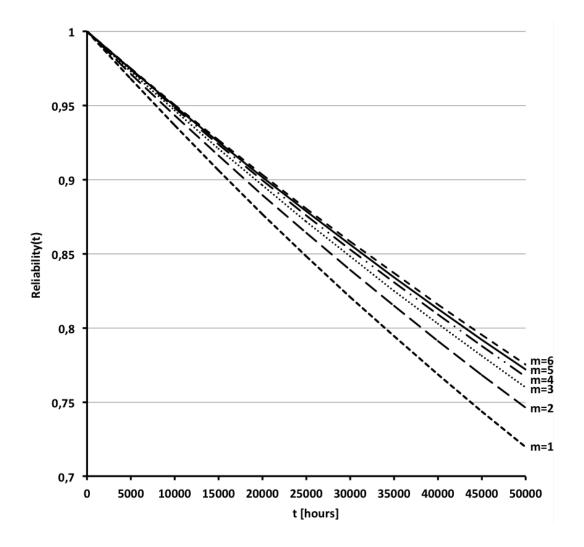

|                 | 7.4                | Evalua   | ation                                                             | 175 |

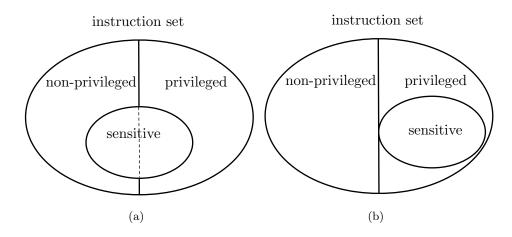

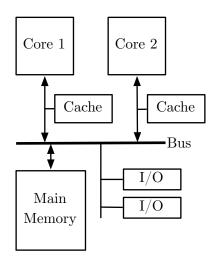

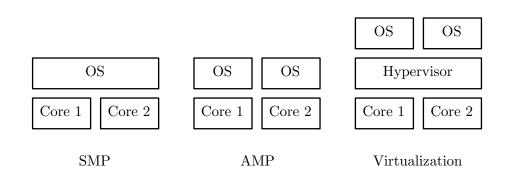

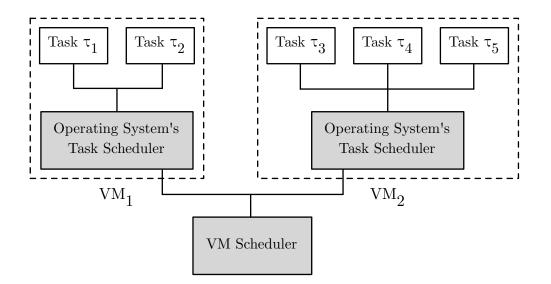

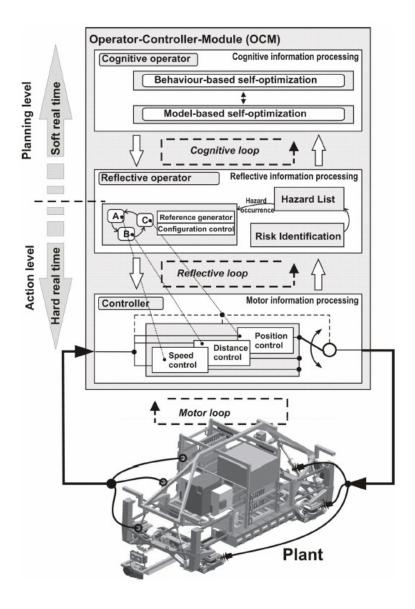

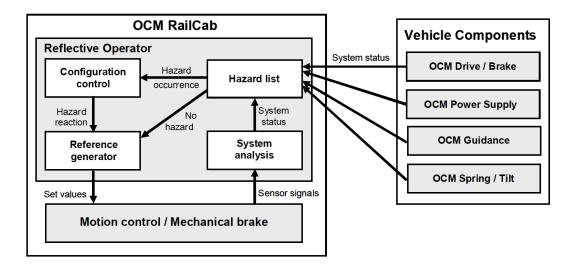

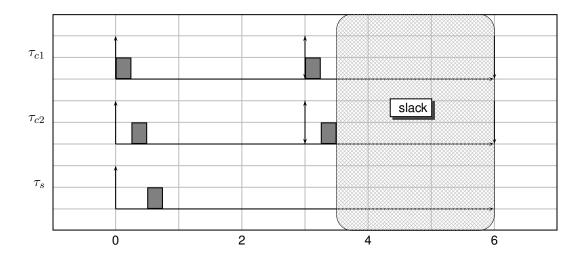

|                 |                    | 7.4.1    | Experimental Setup                                                | 175 |