# **Dynamic Reliability Management**

## **Dissertation**

A thesis submitted to the

**Faculty of Electrical Engineering, Computer Science and Mathematics**

of the

**Paderborn University**

in partial fulfillment of the requirements for the

degree of *Dr. Ing.*

by

**Jahanzeb Anwer**

Paderborn, Germany

July 2017

---

*Supervisor:*

Prof. Dr. Marco Platzner

*Reviewers:*

Prof. Dr. Marco Platzner

Prof. Dr. Sybille Hellebrand

*Additional members of the oral examination committee:*

Prof. Dr. Franz Rammig

Prof. Dr. Christian Plessl

Prof. Dr. Christoph Scheytt

*Date of submission:*

April 3, 2017

*Date of public examination:*

July 20, 2017

---

## Acknowledgements

---

First of all, I would like to thank my advisor Prof. Dr. Marco Platzner for supervising, motivating and helping me to solve each of my research problems.

Furthermore, I would like to thank:

- Prof. Dr. Sybille Hellebrand for serving as a reviewer for my dissertation.

- Prof. Dr. Franz Rammig, Prof. Dr. Christian Plessl and Prof. Dr. Christoph Scheytt for serving on my oral examination committee.

- My office-mate Sebastian Meisner for having fruitful discussions with me during numerous phases of my research.

- My colleagues Andreas Agne, Stefan Biedemann, Alexander Boschmann, Stephanie Drzevitzky, Heinrich Giebler, Heiner Giefers, Tobias Graf, Tobias Beisel, Markus Happe, Nam Ho, Server Kasap, Paul Kaufmann, Tobias Kenter, Achim Lösch, Antoniou Paraskewi, Lars Schäfers, Gavin Vaz, Tobias Wiersema and Prof. Dr. Christian Plessl for valuable discussions and making my working environment a pleasant place to conduct research.

- The Paderborn Center for Parallel Computing for providing the compute resources to run my time-consuming simulations.

- The International Graduate School of Dynamic Intelligent Systems (IGS-DIS) for providing funds to conduct this research.

Finally, I would like to thank my family. In particular, I would like to thank my parents for their continuous support and my wife Rija for her encouragement and patience.

---

## Abstract

---

Radiation-tolerant computing for FPGAs has become an important field of research due to the increased usage of FPGAs in space missions. Various device and design hardening techniques have been used in the past to mitigate errors, particularly single event upsets, that appear due to ionizing radiation particles in aerospace missions. Redundancy is the most commonly used technique to counter such errors. However, the traditional hardware design approaches use statically redundant structures and incur a fixed overhead in performance factors of area consumption, latency and power dissipation. These structures are designed to handle the worst case radiation scenarios. However, it has been shown by experiments, depicting radiation patterns of space, that the radiation strength varies a lot during the operation time span of satellite missions. Therefore, incurring a fixed overhead of static redundant structures for FPGA hardware, results in the wastage of resources as well as performance loss since lower levels of redundancy provide sufficient level of reliability in relatively calm regions of space radiation.

Since high orders of redundancy cost large overheads in performance factors, the best approach of maintaining the reliability-performance tradeoff is to dynamically reconfigure the FPGAs to required reliability levels, based on the radiation strength of the environment. Fortunately, FPGAs provide this level of flexibility since they are run-time reconfigurable. This concept of run-time reconfiguration for reliability has been named Dynamic Reliability Management (DRM) in this research. DRM is a hardware/software co-design approach consisting of design-time and run-time parts. At design-time, several redundant implementations of a hardware design are generated and rated by the performance factors of area, latency, power and achieved reliability. A Pareto-optimization method has been implemented in MATLAB that filters the non-dominated optimal implementations on the basis of three performance factors described above and the reliability magnitude. The run-time tool flow makes use of the filtered non-dominated optimal implementations while storing them as partial bitstreams in its implementation database. During the operation time span of the mission, each of these implementations can be configured on the basis of system constraints and reliability requirements. The decision when to reconfigure the selected implementation can be made on the basis of external, time, cooperative or radiation/error rate based decision mechanisms.

The construction of design-time and run-time tool flows involved using, extending and developing various tools. In particular, the redundancy-insertion tool, i.e., BANL TMR tool

---

has been extended to generate three more redundancy configurations which was limited to only triplicated voter structure in the past. The reliability computation tool has been developed based on the Boolean difference error calculus model. This model, though taken from the literature, is extended to cover the redundant structures and sequential circuit analysis before automating it as a MATLAB tool. The system-on-chip platform, developed to validate the DRM run-time tool flow consists of standard Xilinx as well as our custom IP cores. However, the DRM applications have been introduced with the concept of parallel computation engines. The parallelism of hardware applications on FPGA made us implement the DRM with an area-bounded FPGA partition while still benefiting from performance improvement in low reliability requirements.

The design-time and run-time parts of DRM have been validated with a number of benchmarks. ISCAS benchmarks having different combinational/sequential circuit architectures have been used to validate design-time tool flow. The variation of performance factors have been observed during this experimentation and various conclusions are drawn on the patterns by which the performance factors vary. To validate the run-time design tool flow, we have developed a system-on chip platform utilizing Xilinx ML605 evaluation board with Virtex 6 FPGA and embedded ReconOS operating system to run benchmark applications. The run-time applications consist of data sorting and matrix multiplication algorithms. These applications are run under a sample radiation profile and the their performance is measured under a run-time reconfigurable platform of ReconOS. Our experiments have shown that the DRM and dynamic run-time reconfiguration concept is up to seven and a half times performance efficient as compared to statically utilized redundant structures.

---

## Zusammenfassung

---

Strahlungs-tolerantes Rechnen auf FPGAs ist ein wichtiges Forschungsfeld geworden, da die Nutzung von FPGAs in Weltraummissionen stark angestiegen ist. Verschiedene Härtetechniken gegen Strahlung auf Transistor- und Entwurfsebene wurden in der Vergangenheit genutzt um Fehler, insbesondere Single-Event-Upsets welche durch ionisierende Strahlung während Weltraummissionen entstehen, abzuschwächen. Redundanz ist hierbei die am meisten benutzte Technik um solchen Fehlern entgegen zu wirken. Der traditionelle Hardwareentwurfsansatz benutzt statische Strukturen und nimmt somit zusätzliche Kosten in Form von größerer Chipfläche, Latenz und Leistungsaufnahme in Kauf. Diese Strukturen wurden entworfen um auch die ungünstigsten Strahlungsbedingungen zu überstehen. Jedoch haben Experimente zur Intensität der Strahlung im Weltraum ergeben, dass die Strahlungsintensität während einer Satellitenmission starken Schwankungen unterworfen ist. Daher resultiert die Benutzung von statisch allokierten redundanten Strukturen in einer Verschwendug von Ressourcen und Rechenleistung, da während Zeiten mit niedriger Strahlungsintensität geringere Ansprüche an die Fehlertoleranz gestellt werden können. Da mehrfach redundant ausgelegte Systeme hohe Kosten verursachen, ist der beste Ansatz um den Kompromiss aus Zuverlässigkeit und Leistungsfähigkeit zu erhalten der, den FPGA dynamisch, abhängig von der Strahlungsintensität, auf die benötigte Redundanz zu rekonfigurieren. Glücklicherweise erlauben FPGAs diese Art von Flexibilität durch ihre Fähigkeit zur Laufzeit neu konfiguriert zu werden. Dieses Konzept zur Laufzeit-Rekonfiguration von FPGAs zur Steuerung der Zuverlässigkeit wird in dieser Arbeit "Dynamic Reliability Management" (DRM) genannt. DRM ist ein Hardware/Software Co-Entwurfs Ansatz der aus Entwurfszeit- und Laufzeitteilen besteht. Zur Entwurfszeit werden mehrere redundante Implementierungen eines Hardwareentwurfes generiert und nach ihren Kosten in Fläche, Latenz, Leistungsaufnahme und erreichter Zuverlässigkeit bewertet. Eine Methode basierend auf Pareto-Optimierung wurde in MATLAB entworfen. Diese Methode filtert die nicht-dominierten, optimalen Implementierungen auf Basis der drei oben erwähnten Kostenfaktoren und der Zuverlässigkeit. Die Laufzeitumgebung nutzt nun diese gefilterten, optimalen Implementierungen, in sie sie als partielle Bitströme in der Implementierungsdatei speichert. Während der Missionslaufzeit kann nun, entsprechend der verfügbaren Systemressourcen und der benötigten Zuverlässigkeit, jede Implementierung in den FPGA geladen werden. Die Entscheidung, welche Implementierung geladen werden soll, kann auf der Grundlage von externer, zeitbasierter, cooperativer oder strah-

---

lungsbasierter Mechanismen getroffen werden.

Die Konstruktion der Entwurfs- und Laufzeitwerkzeuge beinhaltete die Benutzung, Erweiterung und Entwicklung verschiedener Werkzeuge. Im besonderen wurde das Werkzeug "BANL TMRtool", welches Redundanz in Schaltungen einfügt, erweitert um noch drei zusätzliche Redundanzkonfigurationen zu erstellen. Zuvor unterstützte es nur triplizierte Voter-Strukturen. Das Werkzeug zur Berechnung der Zuverlässigkeit wurde auf Basis des "Boolean difference error calculus" Models entwickelt. Dieses aus der Referenzliteratur entnommene Model, wurde in MATLAB implementiert und erweitert, und unterstützt nun redundante Strukturen in Schaltungen sowie die Analyse sequentieller Schaltungen. Die System-on-Chip Plattform, welche zur Validierung der DRM Laufzeitumgebung entwickelt wurde, besteht aus standard IP-Cores von Xilinx als auch aus selbst entwickelten IP-Cores. Die DRM Anwendungen wurden für Unterstützung von parallelen Recheneinheiten entworfen und entwickelt. Dank dieser Unterstützung von parallelen Recheneinheiten kann DRM trotz der statischen Größe von FPGA-Partitionen den Durchsatz der Anwendungen in Zeiten niedriger Zuverlässigkeitanforderungen erhöhen.

Die Entwurfszeitwerkzeuge und die Laufzeitumgebung wurden mit einer Reihe von Benchmarks validiert. Die ISCAS Benchmarks implementieren verschiedene kombinatorische wie auch sequentielle Architekturen und wurden benutzt um die Entwurfszeitwerkzeuge zu validieren. Die Veränderung der Kostenfaktoren wurde während der Experimente beobachtet und verschiedene Schlüsse auf die Änderungsmuster wurden gezogen. Um die Laufzeitumgebung zu validieren, wurde eine System-on-Chip Plattform entwickelt, welche das "Xilinx ML605 Evaluation Board", den darauf befindlichen Virtex6 FPGA, sowie das ReconOS Betriebssystem benutzt, um Benchmark Anwendungen ausführen zu lassen. Die Benchmark Anwendungen bestehen aus Sortier- und Matrix-Multiplikations-Algorithmen. Diese Anwendungen werden unter einem beispielhaften Strahlungsprofil ausgeführt und ihre Leistung wird auf der dank ReconOS zur Laufzeit rekonfigurierbaren Plattform ausgeführt. Unsere Experimente haben gezeigt, das DRM und das Konzept der dynamische Laufzeit-Rekonfiguration um einen bis zu siebeneinhalbmal besseren Durchsatz erlauben als statisch allozierte redundante Strukturen.

---

## Contents

---

|          |                                                                                    |          |

|----------|------------------------------------------------------------------------------------|----------|

| <b>1</b> | <b>Introduction</b>                                                                | <b>1</b> |

| 1.1      | Motivation . . . . .                                                               | 1        |

| 1.2      | Contributions of the Thesis . . . . .                                              | 2        |

| 1.3      | Thesis Outline . . . . .                                                           | 4        |

| <b>2</b> | <b>Background and Related Work</b>                                                 | <b>5</b> |

| 2.1      | Space Radiation Environment . . . . .                                              | 5        |

| 2.1.1    | Earth's Magnetosphere . . . . .                                                    | 5        |

| 2.1.2    | Ionizing Space Radiation . . . . .                                                 | 6        |

|          | Van Allen Radiation Belts . . . . .                                                | 6        |

|          | Cosmic Rays . . . . .                                                              | 7        |

|          | Solar Particle Events . . . . .                                                    | 7        |

| 2.2      | Effects of Radiation on Electronic Devices . . . . .                               | 7        |

| 2.2.1    | Cumulative Effects . . . . .                                                       | 7        |

|          | Total Ionizing Dose . . . . .                                                      | 7        |

|          | Displacement Damage . . . . .                                                      | 7        |

| 2.2.2    | Single Event Effects (SEE) . . . . .                                               | 8        |

|          | Non-destructive SEEs . . . . .                                                     | 8        |

|          | Destructive SEEs . . . . .                                                         | 9        |

| 2.3      | Radiation-induced-error Mitigation Techniques . . . . .                            | 9        |

| 2.3.1    | Radiation Hardened by Device . . . . .                                             | 9        |

| 2.3.2    | Radiation Hardened by Design . . . . .                                             | 10       |

|          | Redundancy . . . . .                                                               | 10       |

|          | Variation in Voting Structures of TMR and Cascaded TMR . . . . .                   | 11       |

| 2.4      | Field-programmable Gate Arrays in Space Computing . . . . .                        | 12       |

| 2.4.1    | Radiation-tolerance in FPGAs . . . . .                                             | 13       |

|          | Triple Modular Redundancy in FPGAs . . . . .                                       | 15       |

| 2.5      | The Need for Adaptive Fault-tolerance in FPGAs . . . . .                           | 17       |

| 2.5.1    | Correlating Adaptive Fault-tolerance with Varying-radiation Environments . . . . . | 17       |

|          | Borealis Flight . . . . .                                                          | 18       |

|                                                                            |           |

|----------------------------------------------------------------------------|-----------|

| Low-Earth-Orbit Case Study . . . . .                                       | 19        |

| Highly-Elliptical Orbit Case Study . . . . .                               | 19        |

| Anticipated Error-Rate for Different Solar Conditions . . . . .            | 20        |

| 2.6 Reliability Evaluation of FPGA Designs for Space Computing . . . . .   | 21        |

| 2.6.1 CREME96 based Reliability Computation . . . . .                      | 21        |

| Device Characterization . . . . .                                          | 21        |

| Path/Orbit Specification . . . . .                                         | 22        |

| SEU Rate Prediction . . . . .                                              | 22        |

| 2.6.2 Probabilistic Computational Reliability Models . . . . .             | 22        |

| 2.6.3 Fault-injection and Testing-based Reliability Models . . . . .       | 24        |

| 2.7 Major Research Works in Adaptive Fault-tolerance . . . . .             | 25        |

| 2.7.1 Reconfiguration for Reliability (R4R) . . . . .                      | 25        |

| 2.7.2 Reconfigurable Fault-tolerance (RFT) . . . . .                       | 25        |

| 2.7.3 Reconfiguration via Spare Resources Method . . . . .                 | 26        |

| 2.7.4 BRAM Fault-Detection based Adaptive Reconfiguration . . . . .        | 27        |

| 2.8 Chapter Conclusion . . . . .                                           | 27        |

| <b>3 Reliability Computation of Redundant Structures</b>                   | <b>31</b> |

| 3.1 Boolean Difference Error Calculator . . . . .                          | 32        |

| 3.1.1 Limitations of the BDEC Model . . . . .                              | 34        |

| BDEC v/s TMR Model of Voter . . . . .                                      | 34        |

| Reliability Computation of Sequential Circuits . . . . .                   | 35        |

| Reliability Evaluation Tool . . . . .                                      | 35        |

| 3.1.2 Extensions to the BDEC Model . . . . .                               | 36        |

| Interpretation of Redundant Behaviour . . . . .                            | 36        |

| Supporting Sequential Behaviour of Circuits . . . . .                      | 38        |

| 3.2 Automation of the BDEC Model . . . . .                                 | 38        |

| 3.2.1 Inputs to the BDEC Tool . . . . .                                    | 38        |

| FPGA Component Netlist . . . . .                                           | 39        |

| Input Error and Signal Probabilities . . . . .                             | 39        |

| 3.2.2 Programming Mathematical Model of BDEC . . . . .                     | 39        |

| 3.2.3 BDEC Reliability Computation Algorithm . . . . .                     | 41        |

| 3.3 Parameter Variability Analysis . . . . .                               | 43        |

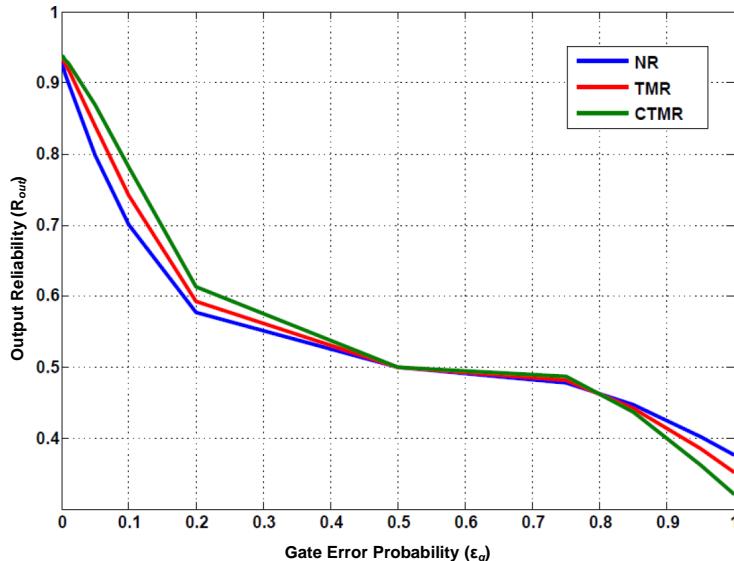

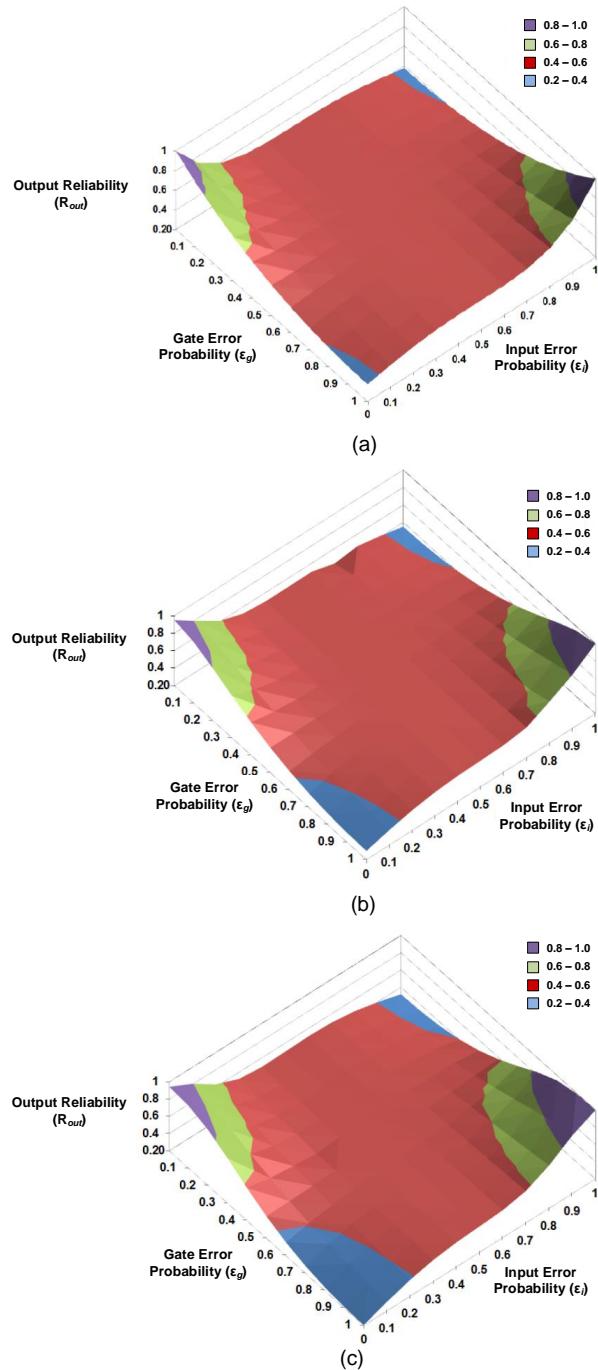

| 3.3.1 Variation of Gate-Error Probability $\varepsilon_g$ . . . . .        | 43        |

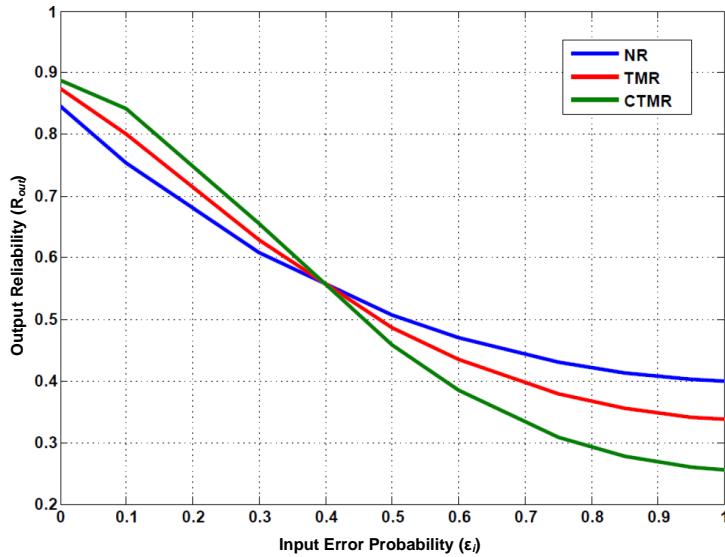

| 3.3.2 Variation of Input Error-Probability $\varepsilon_i$ . . . . .       | 44        |

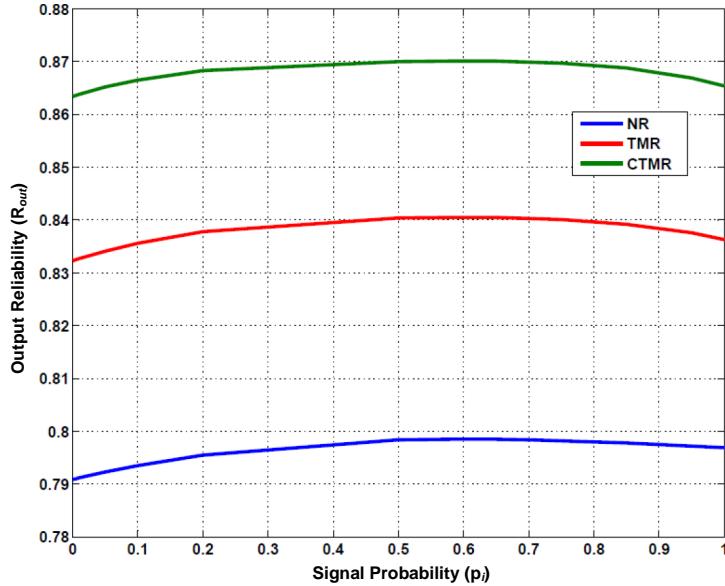

| 3.3.3 Variation of Signal Probability $p_i$ . . . . .                      | 45        |

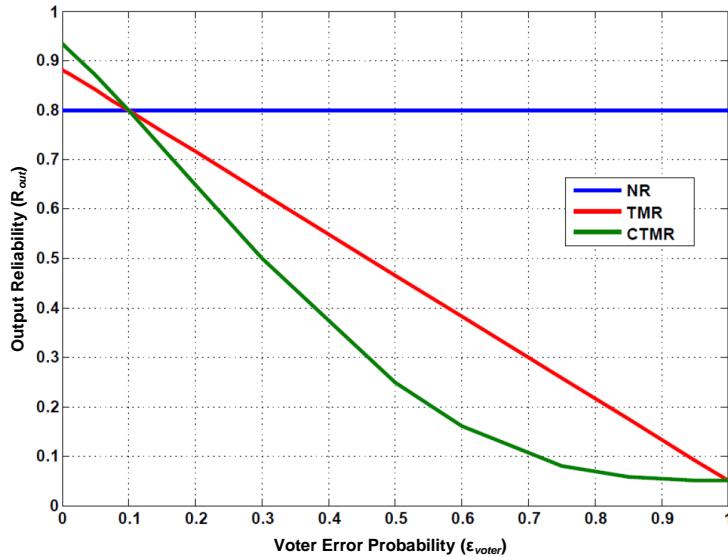

| 3.3.4 Variation of Voter Error-Probability $\varepsilon_{voter}$ . . . . . | 45        |

| 3.3.5 Joint Variation of Input and Gate Error-Probabilities . . . . .      | 46        |

| 3.4 Chapter Conclusion . . . . .                                           | 47        |

|          |                                                                        |           |

|----------|------------------------------------------------------------------------|-----------|

| <b>4</b> | <b>Dynamic Reliability Management</b>                                  | <b>49</b> |

| 4.1      | DRM Design-Time Circuit Analysis . . . . .                             | 49        |

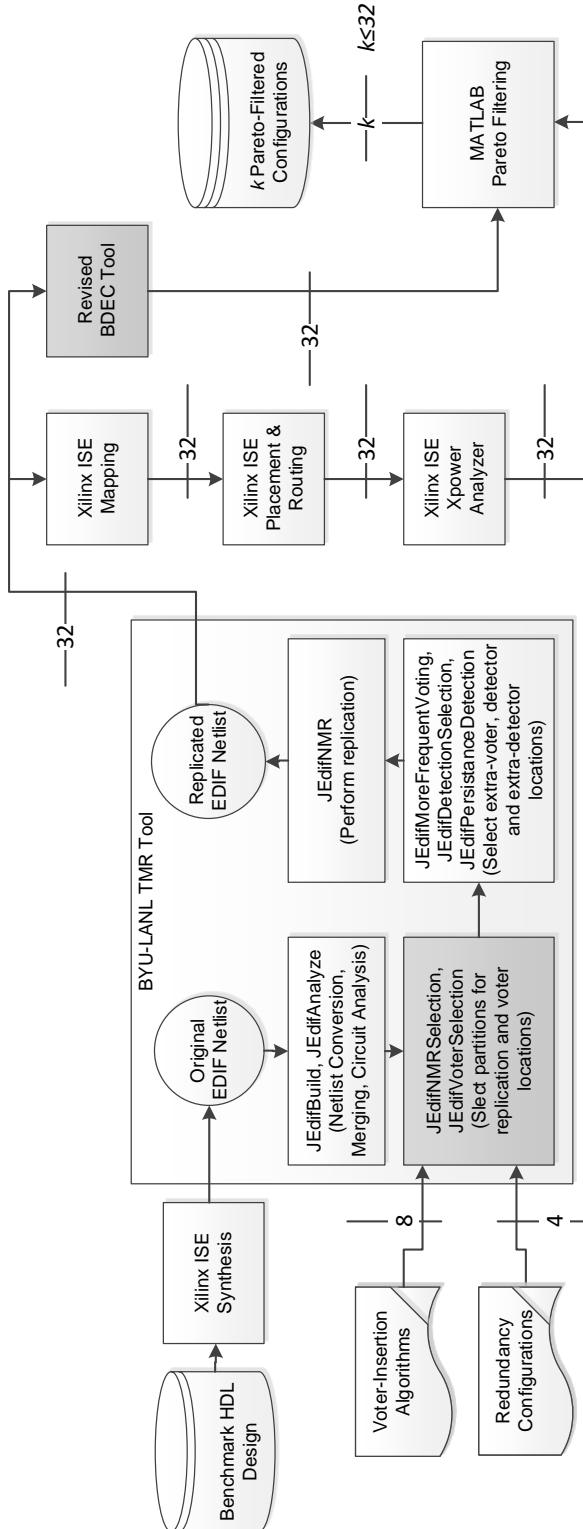

| 4.1.1    | BYU-LANL TMR Tool . . . . .                                            | 50        |

|          | JEdifBuild . . . . .                                                   | 50        |

|          | JEdifAnalyze . . . . .                                                 | 51        |

|          | JEdifNMRSelection . . . . .                                            | 51        |

|          | JEdifVoterSelection . . . . .                                          | 51        |

|          | JEdifNMR . . . . .                                                     | 51        |

|          | JEdifMoreFrequentVoting (Optional) . . . . .                           | 51        |

|          | JEdifDetectionSelection (Optional) . . . . .                           | 51        |

|          | JEdifPersistenceDetection (Optional) . . . . .                         | 51        |

| 4.1.2    | DRM Design-time Tool Flow . . . . .                                    | 52        |

|          | Xilinx ISE Synthesis . . . . .                                         | 52        |

|          | Replication via the BANL TMR Tool . . . . .                            | 52        |

|          | Performing Replication . . . . .                                       | 54        |

|          | Xilinx ISE Mapping, Placement/Routing and Power Analysis . . . . .     | 54        |

|          | Reliability Evaluation . . . . .                                       | 54        |

|          | Pareto Filtering of Implementation Points via MATLAB . . . . .         | 54        |

| 4.2      | DRM Run-Time Circuit Analysis . . . . .                                | 55        |

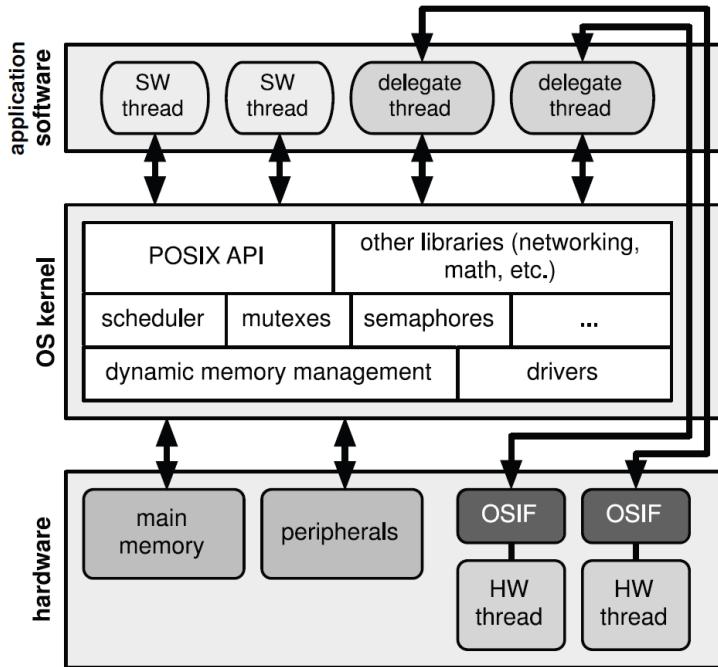

| 4.2.1    | ReconOS . . . . .                                                      | 55        |

| 4.2.2    | Decision Mechanisms for Changing Reliability Levels . . . . .          | 57        |

|          | External . . . . .                                                     | 57        |

|          | Time . . . . .                                                         | 57        |

|          | Cooperative . . . . .                                                  | 57        |

|          | Radiation/Error . . . . .                                              | 58        |

| 4.2.3    | DRM Run-time Tool Flow . . . . .                                       | 58        |

| 4.3      | Chapter Conclusion . . . . .                                           | 59        |

| <b>5</b> | <b>Validating Dynamic Reliability Management Tool Flow</b>             | <b>61</b> |

| 5.1      | Validating Design-time Tool Flow . . . . .                             | 61        |

| 5.1.1    | Experimental Setup . . . . .                                           | 61        |

| 5.1.2    | c17 and c3540 (ISCAS'85) . . . . .                                     | 62        |

| 5.1.3    | s713 and s838 (ISCAS'89) . . . . .                                     | 63        |

| 5.1.4    | b8 and b12 (ISCAS'99) . . . . .                                        | 65        |

| 5.2      | Validating Runtime Tool Flow . . . . .                                 | 67        |

| 5.2.1    | Data Sorter . . . . .                                                  | 67        |

| 5.2.2    | Matrix Multiplier . . . . .                                            | 71        |

| 5.3      | Variation of Pareto-optimal Implementations of DRM Tool Flow . . . . . | 73        |

| 5.3.1    | Using Relative versus Exact Reliability Values . . . . .               | 73        |

| 5.3.2    | Using Different Error Probability Values . . . . .                     | 73        |

| 5.4      | Conclusion . . . . .                                                   | 76        |

|                                                     |           |

|-----------------------------------------------------|-----------|

| <b>6 Summary and Conclusions</b>                    | <b>79</b> |

| 6.1 Summary . . . . .                               | 79        |

| 6.2 Conclusions and Lessons Learned . . . . .       | 81        |

| 6.3 Future Directions . . . . .                     | 82        |

| <b>Acronyms</b>                                     | <b>86</b> |

| <b>A Formulation of Error Probability Equations</b> | <b>89</b> |

| A.1 2-Input OR Gate . . . . .                       | 89        |

| A.2 2-Input XOR Gate . . . . .                      | 90        |

| A.3 3-Input LUT . . . . .                           | 91        |

| <b>List of Figures</b>                              | <b>93</b> |

| <b>List of Tables</b>                               | <b>95</b> |

| <b>Bibliography</b>                                 | <b>97</b> |

# CHAPTER 1

---

## Introduction

---

### 1.1 Motivation

The integration density of transistors on a single system-on-chip has tremendously increased in the last couple of years [1]. The packing of more transistors on a chip has been made possible due to shrinking of device dimensions and modern fabrication techniques in semiconductor technologies. However, the critical charge required to flip a logic bit, in the advent of an error, has decreased for the newer scaled technologies thereby increasing the probability of transient errors in logic devices. Therefore, the signal integrity of the electronic devices, has to be maintained nowadays, under low signal to noise ratios and power supply voltages.

There are various types of errors encountered in electronic devices, which can be mitigated using semiconductor fabrication techniques or circuit design approaches at the software or hardware level. The major sources of noise or errors are dealt with at the transistor/analog design layer, e.g., charge sharing/leakage, power supply noise or aging mechanisms like negative temperature bias instability (NBTI) or hot carrier injection (HCI), etc. Another specific category of errors is radiation-induced errors which are encountered in high radiation particularly space environments. The common error-mitigation technique for radiation-induced errors is redundancy. Redundancy, as the name implies, computes the functional output via redundant blocks and compares them before providing a reliable voted output. In this way, a possible error in either of the replicas can be mitigated. However, redundancy in a circuit can be implemented using different granularity levels and voter-insertion algorithms. However, each of the redundant implementation differs in performance factors of area consumption, latency, power dissipation and achieved reliability level.

The space computing, nowadays, is largely dominated by the field-programmable gate arrays (FPGA). FPGAs can perform various tasks during different phases of a mission without the need for holding dedicated resources for each task. This, in turn, reduces the

carry-on hardware and weight of the satellite payload, while providing the feasibility to shut-down circuit modules which are not in use to prevent excessive power dissipation. Moreover, increase in on-board processing requirements on space missions, for various image processing applications, go well with the highly parallel architecture of FPGAs [2]. Most importantly, FPGAs allow spacecraft designers to upload new configuration data (or modify the hardware) after launch in case the mission requirements change or an error is found in application/task design [3]. However, when FPGAs are exposed to space environment consisting of high solar and cosmic radiation, involving high energy electrons, alpha particles and heavy ions, errors in the form of logic reversals appear in the digital circuit elements. These errors, which mainly consist of single event upsets (SEU), could be as disastrous as causing a system level failure or as moderate as internally masked errors. In general, high levels of redundancy, with big replication factors, cost large overheads in performance factors. The traditional way of implementing redundancy in a hardware design is to utilize a fixed redundant structure and bear a constant overhead in circuit and system performance. However, the benefit of using FPGAs is that we can modify the redundant structures at run-time due to the *reconfigurability* of FPGAs. Hence, a suitable trade-off between reliability level and system performance can be maintained while the system is in operation. The idea of the run-time modification of redundant structures goes well with the FPGAs used in space computing since the radiation environment varies during the orbital time span of the space mission. In a particular case study of radiation pattern of a highly elliptical orbit, it has been shown that the redundancy requirement is high only for a very small duration of circuit operation when the satellite passes the Van Allen radiation belts [2]. Therefore, during lower levels of radiation, smaller redundancy levels could be used and vice versa so that a suitable trade off between reliability and performance can be maintained during mission time span.

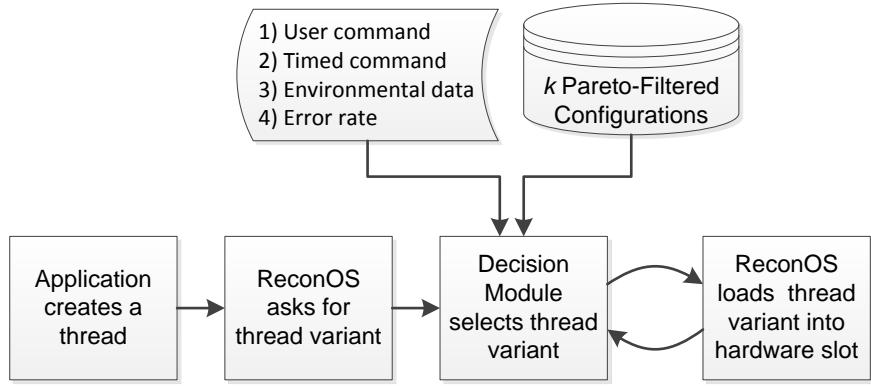

The mechanism of adaptive reconfiguration of reliability has been proposed in various research works in literature, however, the scope of these research works differ. In this thesis, we propose our technique, named Dynamic Reliability Management (DRM). DRM employs a decision mechanism which tells the system when to reconfigure for higher or lower reliability levels. DRM is composed of two parts. At the design-time, several redundant implementations of a circuit are analyzed for performance factors of area, latency, power and achieved reliability. At run-time, ReconOS, which is an operating system for reconfigurable logic cores, is utilized to switch among various redundant implementations at run-time. The circuit design has the liberty to utilize any decision mechanism for reconfiguration with ReconOS, i.e., external, time, cooperative or radiation/error rate measurements.

## 1.2 Contributions of the Thesis

This thesis contributes by presenting a novel concept of Dynamic Reliability Management (DRM). In order to realize this concept on both hardware and software, we have utilized, extended and developed various tools. The resulting tools are organized as design-time and run-time tool flows. We explain each of the contributions involving these tools as

---

follows.

- In order to generate various redundant implementations of a digital circuit design, we have utilized BYU-LANL TMR tool. The tool, by default, supports only triple modular redundancy (TMR) as the basic redundant implementation. However, we require more configurations involving higher levels of redundancy and different voter structures, to construct a larger design space for analyzing performance parameters of redundant circuits. Therefore, we have modified this tool to generate three more configurations, i.e., one-alternate-voter, two-alternate-voters and cascaded TMR, extending the design space to 32 implementations based on overall four redundancy configurations and eight voter-insertion algorithms.

- While the performance factors of area, latency and power could be evaluated by standard FPGA softwares, there exists no standard tool for calculating magnitude of reliability. Following the need for a generic tool based on FPGA based circuits, we have developed a MATLAB based tool that takes input and error probabilities of FPGA components and provides us the reliability of circuit outputs. Though the original non-automated reliability model exists in literature, we have extended it in two directions. Our tool not only helps us in evaluating redundant implementations for reliability, it makes us analyze the impact of different orders of redundancy on the circuit reliability. The most important contribution of this analysis is the definition of a threshold point. The threshold point refers to the magnitude of component error-probability after which redundancy serves no improvement in circuit reliability, in fact, it degrades it.

- After extending the BYU tool and developing MATLAB reliability tool, we have additionally used Xilinx synthesis, mapping, placement and routing and power analyzer tools to generate DRM design-time tool flow. The tool flow takes FPGA structural netlist as input and generates non-dominated redundant implementations of a circuit based on performance parameters of area, latency, power and reliability.

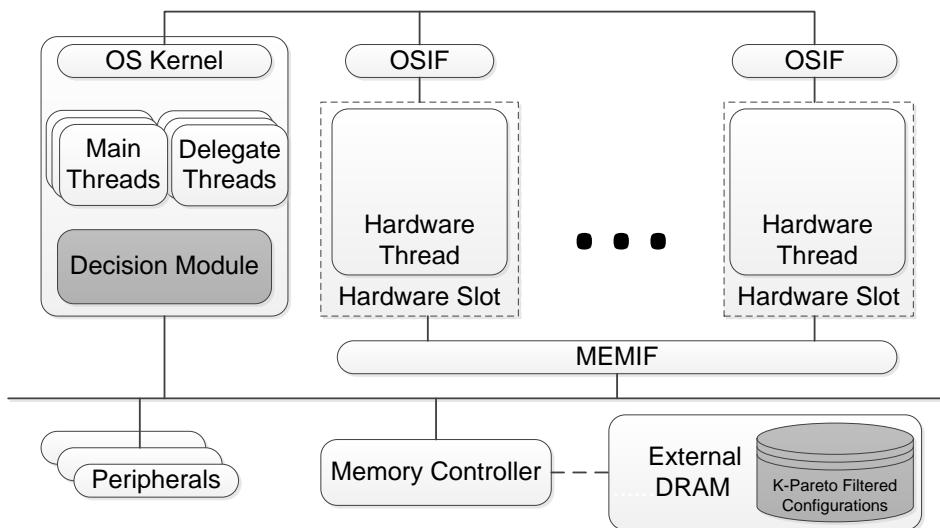

- The run-time tool flow of DRM has been constructed using ReconOS operating system involving a system-on chip platform on Xilinx ML605 evaluation board equipped with Virtex 6 FPGA. The system-on-chip (SoC) platform supports DRM by utilizing the non-dominated redundant implementations (stored in the external DRAM) and developing decision mechanism in software or hardware.

- The partial reconfiguration feature of FPGAs has been extended with the parallelism concept of hardware threads. This extended feature is required so that the maximum size of the hardware partition, which needs to be fixed to a maximum implementation size in order to exercise partial reconfiguration, can also be utilized by parallel versions of the smaller implementation sizes. In this way, we can avoid the non- or partial-utilization of large reconfigurable hardware partitions when utilized by comparatively smaller hardware threads. Additionally, the parallelism strategy provides us higher performance of hardware threads.

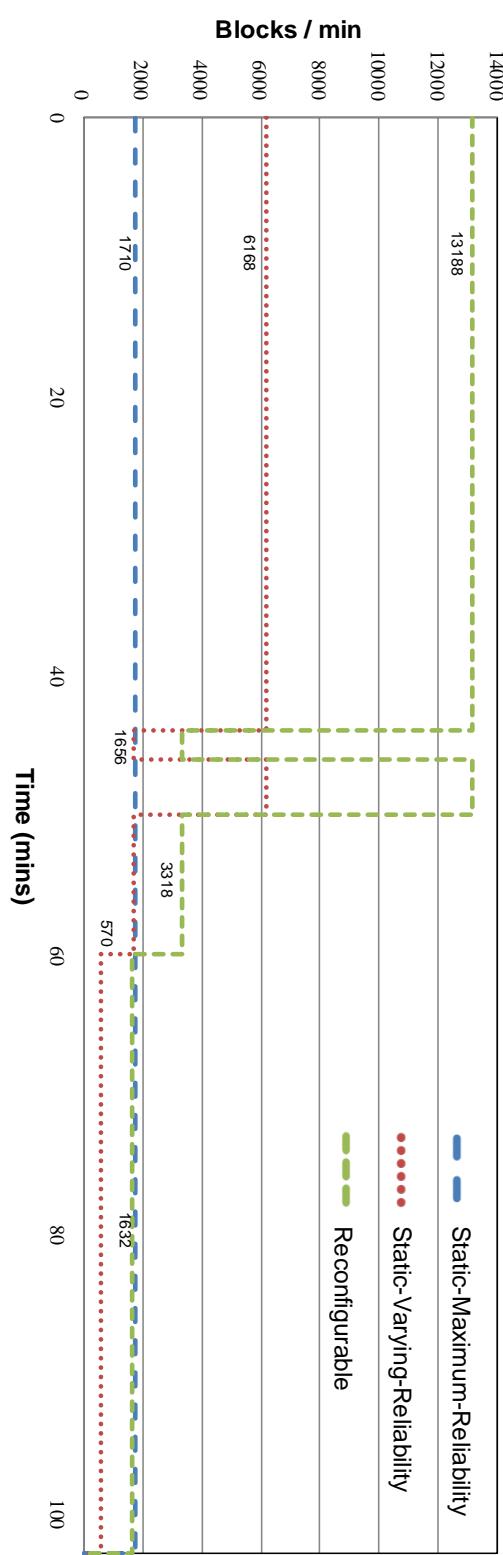

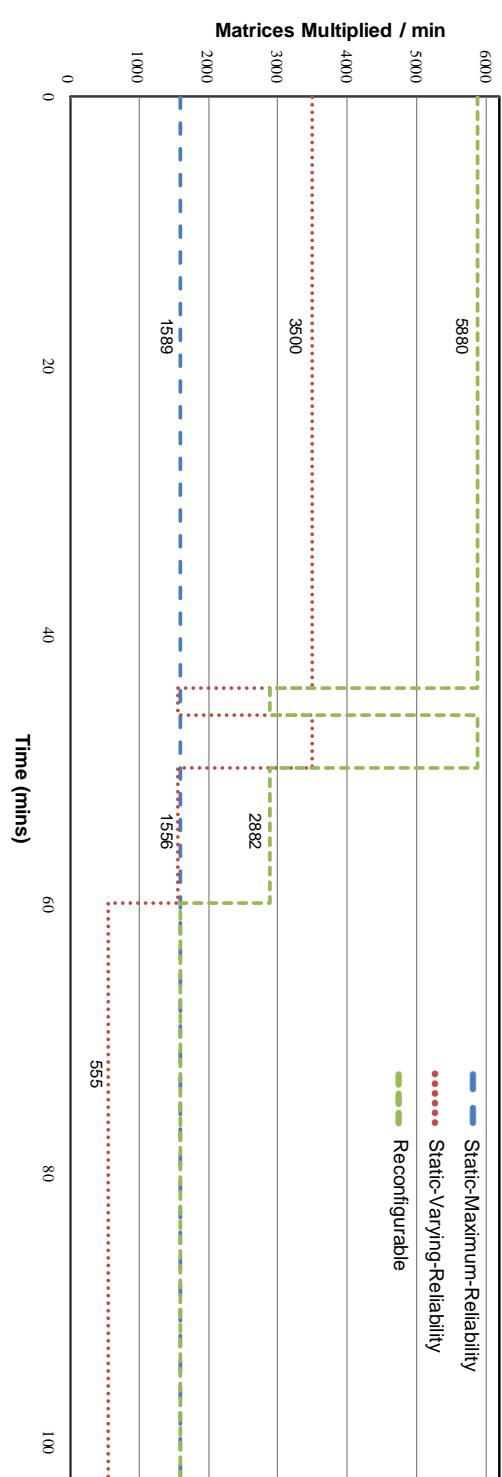

- Both of the design-time and run-time tool flows have been verified by a number of benchmark circuits. The experimentation in design-time tool flow makes us observe the pattern by which the performance factors of the redundant circuit vary in the placed and routed design. The run-time tool flow, while being verified by sorting and matrix multiplication case studies shows that our proposed DRM technique can provide up to seven and a half times higher performance when compared with static reliability management techniques with fixed redundant structures.

- This research has so far resulted in four published international conference publications [4, 5, 6, 7], one published journal publication [8] while another journal publication is under peer-review process of a respective journal.

### 1.3 Thesis Outline

The thesis is structured as follows:

**Chapter 2** provides the background of fault-tolerance in FPGA based hardware designs used in space computing. It starts by explaining the space environment and different radiation scenarios. The radiation based errors are categorized in different types along with their impacts. Afterwards, it provides the literature on approaches used in radiation tolerant computing for FPGAs. Furthermore, a short overview of adaptive reliability techniques are presented which work on the broad research line of FPGA based fault-tolerance though differing from DRM in scope and implementation.

**Chapter 3** explains the development of our reliability evaluation tool, i.e., Boolean Difference Error Calculator (BDEC) on the MATLAB software. Firstly, the conventional BDEC model is explained. Afterwards, we explain the limitations of this model and the extensions made to it in order to perform our simulations. The extended model is afterwards automated in MATLAB. This chapter presents the first experimentation of this tool, i.e., parameter variation analysis of control parameters of the BDEC model.

**Chapter 4** presents the tool flow of the design-time and run-time parts of DRM. This chapter discusses the tools that we have utilized, extended and developed for the realization of DRM on software and hardware platforms.

**Chapter 5** provides the experiments that we have conducted on various benchmarks to validate our DRM tool flow. The design-time tool flow is validated by analyzing area, latency, power and reliability of six ISCAS benchmarks of different circuit architectures. The run-time tool flow, on the other hand, has been validated by two practical case studies on system-on-chip platform for DRM, which is implemented on Xilinx ML605 evaluation board.

**Chapter 6** concludes our research as well as explains our future research directions.

# CHAPTER 2

---

## Background and Related Work

---

The signal integrity of electronic devices, reaching nanometer dimensions, has become a serious concern due to numerous device architecture issues, e.g., ground bounce, cross-coupling, charge sharing/leakage, capacitive/inductive coupling, process variations, aging mechanisms, etc [9, 10]. Additionally, ICs operating in space environment suffers from radiation induced errors, being permanent or transient in nature. The understanding of radiation environment is essential in designing reliable space electronic systems.

### 2.1 Space Radiation Environment

The radiation environment of the earth is composed of various kinds of radiation particles, with different ionizing strengths, and can lead to different effects in electronic devices. They majorly include protons, electrons, heavy ions and electromagnetic radiation (photons). It is important to understand the radiation environment of the space or orbit in which the electronic system is designed to operate, in order to take the reliability measures, e.g., shielding or device-based fault-tolerance methods.

#### 2.1.1 Earth's Magnetosphere

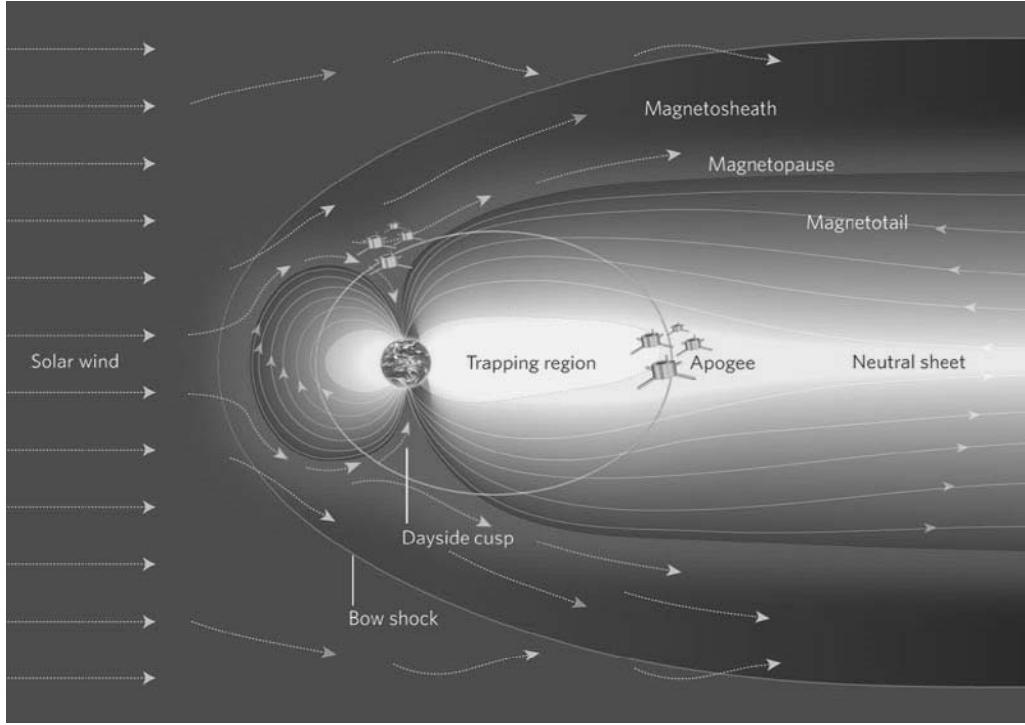

The magnetic field surrounding the Earth is called as magnetosphere, depicted in Figure 2.1 [11]. The magnetic field of the earth would have been a dipole if it were not affected by the solar wind coming from the sun. The influence of solar wind shapes the Earth's magnetic field with compressed magnetosheath (the part closer to the sun) and lengthened magnetotail (the part furthest from the sun) [12]. The path of the satellite determines which types of radiation the comprising electronic components could encounter. The orbits closer to earth might experience only few low-energy particles since the magnetosphere blocks or attenuates most of the radiation particles. The higher orbits could not only experience radiation particles from solar wind but also from deep space. Furthermore,

**Figure 2.1:** Earth's Magnetosphere [11]

the time and duration of the space mission should be considered too since the shape of the Earth's magnetosphere changes due to varying solar wind and radiation patterns.

### 2.1.2 Ionizing Space Radiation

The ionizing space radiation refers to the radiation particles having sufficient energy to remove electrons from the orbits of atoms thus resulting in charged particles. They can be classified into three domains.

#### Van Allen Radiation Belts

The earth is encircled by two radiation belts called as inner and outer Van Allen radiation belts. These belts consist of trapped radiation particles; inner belt contains mainly protons (10-100 MeV) while outer belt contains mainly electrons (up to 7 MeV) [13]. These particles are trapped due to magnetospheric force but they keep on entering or ejecting this force due to varying solar activity. In particular, the South Atlantic Anomaly (SAA) [12] is the area where the Van Allen radiation belts penetrate closer to the earth than other regions, hence poses more danger to the on-board electronics as well as a compromise on the reliability of transferred data.

---

## Cosmic Rays

These are the radiation particles which originate from the sun but exists outside our solar system (Galactic). Though these particles have low flux and are much sparser than the Van Allen belt particles, they have very high energy and are difficult to be shielded. They mainly consists of protons and heavy ions.

## Solar Particle Events

The sun has an 11 year cycle during which the solar activity greatly varies. During this period, the sun ejects protons, electrons, heavy ions, etc. The strength and number of these particles depends on the solar conditions, e.g., massive amounts of radiation during *solar maximum* period or relatively very quiet during *solar minimum* period.

## 2.2 Effects of Radiation on Electronic Devices

The radiation particles affect the functionality of electronic devices including FPGAs. Among the radiation particles encountered in space computing, protons (85% of the galactic radiation) and heavy ions (highly energetic particles, up to GeV) are the major sources of errors [12, 13]. In contrast, alpha particles (less penetrative) and gamma rays (lightly ionizing) are no longer a big concern in reliable space computing. Generally, the effects of radiation can be classified into two domains, cumulative and single event effects.

### 2.2.1 Cumulative Effects

The cumulative effects are the long-term destructive effects on a device and can be further divided into two types.

#### Total Ionizing Dose

The amount of radiation that a device can absorb before its transistors begin to degrade is called Total Ionizing Dose (TID) [14]. TID refers to the accumulation of charge in transistor's oxide region which causes an increase in current leakage and power dissipation as well as changes in threshold voltage and timing performance of the device. TID is measured in units of rad (radiation absorbed dose) where 1 rad is equal to 10nJ of energy deposited per gram of material, typically Silicon. The radiation hardened FPGAs, are rated by the total ionizing dose to show their immunity to radiation for space missions, e.g., 1 Mrad for Xilinx space grade Virtex-5QV FPGA [15].

#### Displacement Damage

This phenomenon refers to the damage done to the device when incoming radiation particles displace atoms from their original lattice positions [12]. It often leads to a chain displacement reaction, when one atom, when displaced, further displaces the neighboring

atoms unless not enough energy is left to cause further displacement. However, this is an insignificant effect in SRAM based FPGAs.

### 2.2.2 Single Event Effects (SEE)

The single event effects (SEE) are the electrical disturbances caused by the ionization of the Silicon lattice by the incident charged particle [16]. The minimum amount of charge that a particle must deposit to change the state of a logic element is called as critical charge,  $Q_{crit}$ , defined by Equation 2.1.

$$Q_{crit} = C_{node} * V_{node} \quad (2.1)$$

where  $C_{node}$  is the capacitance between transistor nodes and  $V_{node}$  is the transistor operating voltage. With every new transistor technology, the operating transistor voltage decreases as well as node capacitance due to its smaller size, thus decreasing the critical charge needed to cause a functional error in a logic device [17]. SEEs are instantaneous effects and classified into non-destructive and destructive types [9, 12, 13, 18].

#### Non-destructive SEEs

These include single event upsets (SEU), single event transients (SET), single event functional interrupts (SEFI) and multiple bit upsets (MBU).

- **Single Event Upsets (SEU):** These errors appear when a radiation particle hits a storage element, e.g., a latch and deposits sufficient charge, i.e., critical charge, to change the output state from 0 to 1 or vice versa. This is the most frequent source of errors in digital circuits, hence our further work, including error-mitigation techniques, will mainly focus on SEUs.

- **Single Event Transients (SET):** These are temporary logic level glitches in combinational elements of the circuit. They are typically non-effective unless the short surge of the transient latches with the following memory element, where it behaves like an SEU. With increasing clock speed of the logic circuits nowadays, the probability of latching up SETs is increasing too [12].

- **Single Event Functional Interrupts (SEFI):** These are errors appearing in circuit's control logic, e.g., power-on/reset circuitry. Typically, when these critical bits get upset, the FPGA must be re-configured via pulsing the PROG pin or cycling power, thus causing the outage of FPGA operation for tens or hundreds of milliseconds [19]. Typical SEFIs named during radiation testing of Xilinx Virtex-5QV FPGA include power-on-reset (POR), SelectMAP (SMAP), frame address register (FAR) and global signal SEFIs [19].

- **Multiple Bit Upsets (MBU):** A single particle can cause multiple bit SEUs when the incident path is non-orthogonal to the device. A similar scenario happens when an SET is latched into multiple registers, e.g., via select pin of a multiplexer.

---

Radiation testing of Xilinx FPGAs shows that each successive Virtex FPGA family is more susceptible to MBUs than previous models [20, 21].

### Destructive SEEs

These SEEs cause a permanent failure to the device in contrast to the temporary errors in non-destructive category. They are divided into following three types.

- **Single Event Latchup (SEL):** This condition occurs when a radiation particle causes a low-impedance path between power rails of the MOSFET, where the parasitic NPN/PNP transistors are put into positive feedback condition (PNPN). The resulting runaway current damages the device.

- **Single Event Burnout (SEB):** Primarily caused by heavy ions, SEB occurs when an ion passing through the device in its off state generates a plasma filament of electron-hole pairs in its path. The runaway current generated in this path can trigger a secondary breakdown in the parasitic transistor in the MOSFET.

- **Single Event Gate Rupture (SEGR):** This effect occurs when the path of the heavy ion breaks down the gate oxide. This happens as the electrons in the generated electron-hole pairs diffuse faster than holes, whereby the accumulated holes create a transient field which exceeds the breakdown voltage of the gate oxide. This phenomenon is more probable with thin gate oxides.

## 2.3 Radiation-induced-error Mitigation Techniques

The conventional radiation/error-tolerant technique is shielding, usually of Aluminum sheet/coating, that is good for absorbing low energy particles, up to 30 MeV. Though the heavy ions were unstoppable in previous times too, the high transistor dimensions were less vulnerable to radiation effects. Due to the shrinking of device dimensions and scaling of power supply and threshold voltages, fault-tolerance measures in addition to shielding is the requirement of time. The two major approaches to make digital circuits radiation tolerant are via device and design.

### 2.3.1 Radiation Hardened by Device

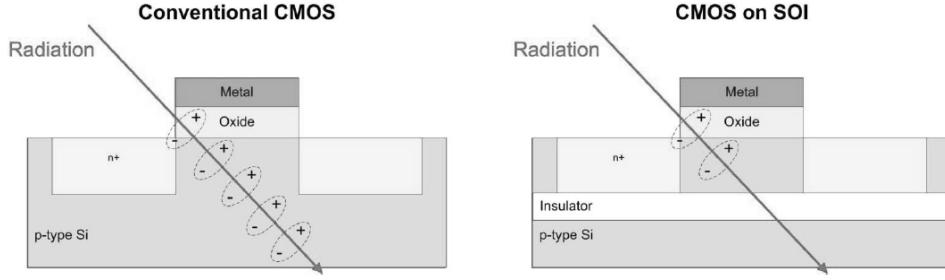

The digital circuits can be made radiation hardened by using different fabrication/process techniques for their transistors. This includes the prominent silicon-on-insulator (SOI) technology [9]. Following Figure 2.2, we can see that the conventional CMOS technology when used with silicon-on-insulator technique, i.e., an insulator on bulk silicon, the number of generated electron-hole pairs and the ion trail length reduces. Hence, the runaway current (or opposing electric fields causing dielectric breakdown) can be reduced. These techniques can particularly increase the TID and lowers SEL effects though they are expensive techniques especially for low-volume IC production. Therefore, while utilizing

**Figure 2.2:** Silicon-on-insulator technology [9]

the conventional fabrication process but utilizing architecture-based mitigation techniques makes radiation hardening *by design* an alternative.

### 2.3.2 Radiation Hardened by Design

The architecture based fault-tolerance detects and corrects single event effects, whether implemented in the software or hardware design. The conventional and popular techniques that fall into this category are redundancy and error detection and correction (EDAC). Though EDAC is mainly used for memory protection against SEEs; in this thesis, we will focus on redundancy and its various implementations in hardware design.

#### Redundancy

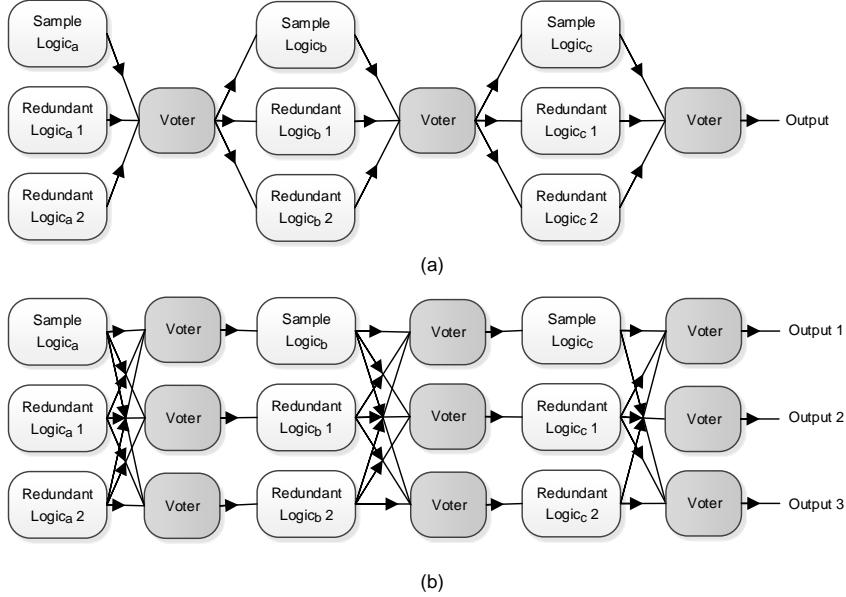

As the name implies, redundancy refers to performing a computing task more than once and compare the outputs of the redundant modules. The most popular form of redundancy is triple modular redundancy (TMR) [22, 23, 24]. In principle, TMR instantiates three copies of an identical circuit and places a voter module at the end to take a majority decision for each output. This concept is illustrated in Fig 2.3(a). The TMR equation for a single voter module is represented as Equation 2.2 where  $R_1$ ,  $R_2$  and  $R_3$  refer to reliability of the three redundant modules respectively and  $R_{voter}$  represents the reliability of the voter itself.

$$R_{out} = R_{voter}[R_1R_2 + R_1R_3 + R_2R_3 - 2R_1R_2R_3] \quad (2.2)$$

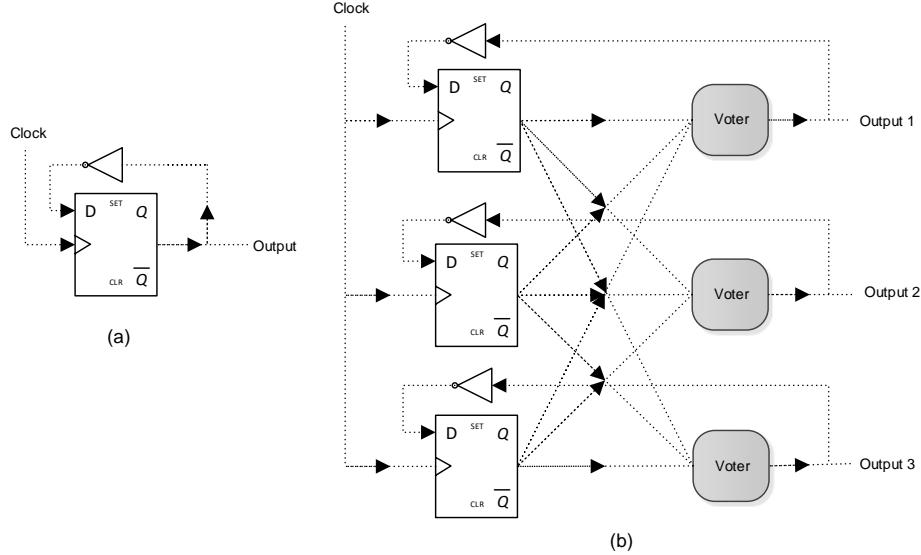

The problem with this architecture is the single point of failure, i.e., an error occurring in the voter renders the TMR technique useless. To avoid the single point of failure, the voter can also be triplicated in addition to the triplicated logic modules, as shown in Figure 2.3(b), and the three outputs for each module are run in parallel unless the output has to be merged, to communicate as a single output, via converging voters.

The optimal length of each branch after which a voter can be placed depends of the required granularity level of redundancy. A coarse grained redundancy simply requires triplication of whole circuit and places a single or triplicated voter at the end. A rather fine-grained

**Figure 2.3:** Triple modular redundancy with a) single voter b) triplicated voter

redundancy implies triplication of individual logic gates or blocks, e.g., adders or multipliers. The trade-off of TMR reliability is the degradation of circuit's performance factors, i.e., area consumption, latency and power dissipation. The scaling factor of these performance factors depend of the placement and routing of individual circuit elements/blocks in a system design.

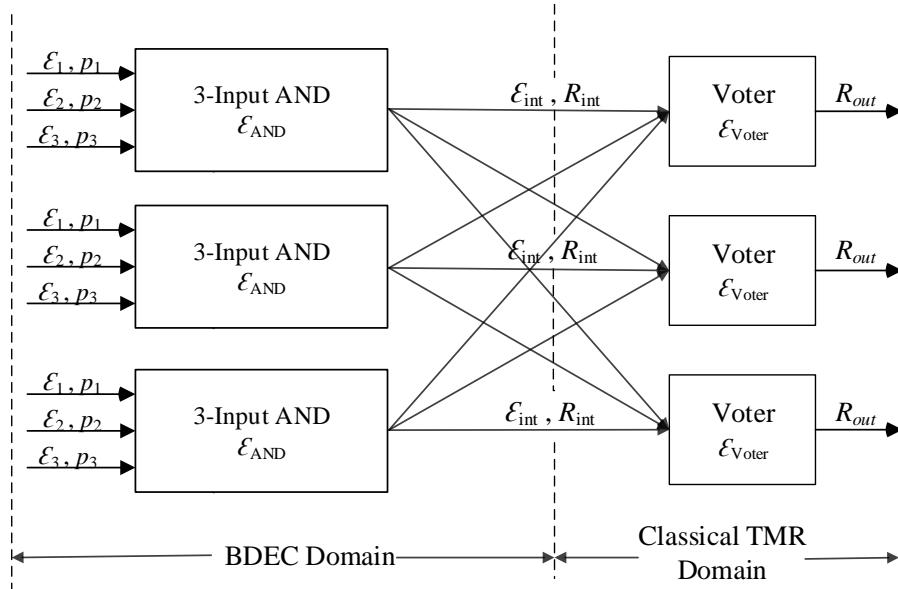

#### Variation in Voting Structures of TMR and Cascaded TMR

Besides the conventional single and triplicated voter configurations, there are configurations proposed in [25] with single/double voters in the alternate stages as shown in Figure 2.4. In contrast to the triplicated voter structure, it takes up to maximum two and one extra voter stages to correct an error for one-alternate and two-alternate voter configurations respectively. Using Monte Carlo simulations, the authors proved that these alternate configurations are slightly less reliable than triplicated voter configuration though they save the overhead of increased number of voters. Hence, in situations where the radiation environment is not very strong and area consumption is an important issue, the alternate configurations are highly useful. Additionally, there is a concept of Cascaded TMR which results in more reliable configurations than TMR, though consuming more area [26]. As an example, we illustrate level-1 CTMR as shown in Figure 2.5. It can be noted that the CTMR configuration has a single point of failure as it is the extension of TMR with a single voter. While CTMR can also be improved by using the triplicated voter strategy, we assume that CTMR is always superior to TMR for the time being. Similarly, the usage of NMR techniques or high levels of CTMR are possible though multiplying the

**Figure 2.4:** Triple modular redundancy with a) one alternate voter b) two alternate voters

cost on the performance factors of area, latency and power. Overall and based on the results presented in [24, 25, 26], we rate the reliability of the discussed configurations in the following ascending order:

- SV: Single Voter ([24])

- OAV: One alternate voter ([25])

- TAV: Two alternate voters ([25])

- TV: Triplicated voter ([24])

- CTMR: Cascaded TMR- Level 1 ([26])

In this thesis, we will use these five redundancy configurations for experimentation and comparison. However, there is no limit to the number of higher redundant configurations when one uses N-modular redundancy or higher cascaded levels of CTMR.

## 2.4 Field-programmable Gate Arrays in Space Computing

Field-programmable Gate Arrays (FPGAs) are integrated circuits, whose logic blocks and interconnects are configurable in contrast to the Application Specific Integrated Circuits (ASICs) whose functionality is fixed to a particular task. FPGAs consist of a very large number of configurable logic blocks (CLBs) containing a number of basic programmable

**Figure 2.5:** Cascaded triple modular redundancy- Level 1

components: flip-flops (FFs) and look-up tables (LUTs). These basic elements are connected by a programmable interconnect network, which allows to configure a routing network on a grid-layout and provides large flexibility in functional design modification on the FPGA. The hardware design on FPGAs is done by hardware description languages, i.e., Verilog or VHDL. Today's FPGA market is largely dominated by manufacturers Xilinx and Altera.

Due to the run-time *reconfigurable design* feature of the FPGA, it is increasingly in demand for spacecraft electronics. FPGAs can perform various tasks during different phases of a mission without the need for holding dedicated hardware for each task. This, in turn, reduces the carry-on hardware and weight of the satellite payload, while providing the feasibility to shut-down circuit modules which are not in use to prevent excessive power dissipation. Moreover, increase in on-board processing requirements on space missions for various image processing applications go well with the highly parallel architecture of FPGAs [2]. Most importantly, FPGAs allow spacecraft designers to upload new configuration data (or modify the hardware) after launch in case the mission requirements change or an error is found in application/task design [3]. As examples, SRAM FPGAs have been utilized in both earth orbits [27, 28, 29] as well as towards Mars [30].

#### 2.4.1 Radiation-tolerance in FPGAs

Since the FPGAs are manufactured by the similar state-of-the-art fabrication technologies as used in all electronics and ASICs, they are equally susceptible to radiation-induced errors. Being in demand in space-computing, their radiation-tolerant design is important as their operating environment is composed of highly energetic radiation particles. In particular, these particles could appear as errors in different resources of an FPGA, e.g., SEUs in sequential logic (registers, memory blocks, DSPs) and configuration memory and SETs in combinatorial logic (LUTs) and clock and global routing [18]. The configuration memory is the most critical part of an FPGA which stores the bitstream representing the functionality of an FPGA including LUT contents as well as routing network, and therefore needs higher protection against radiation particles than other hardware blocks. It has been

validated in radiation-tolerance studies for FPGA, for example in Rosetta experiment [31], that the FPGAs are susceptible to radiation-induced errors, particularly at high altitudes. Therefore, the FPGAs manufacturers, provide radiation-hardened solutions for FPGAs by device as well as by design.

The commonly used FPGAs are SRAM-based. Although the high performance and re-configuration flexibility are achievable only through SRAM based FPGAs, they are highly susceptible to SEUs. Therefore, the FPGA manufacturers offer space-grade FPGAs with different device technologies on the cost of lower performance compared to SRAM alternatives. They include the foremost Actel (currently known as Microsemi) RTAX Antifuse FPGAs [32]. These devices are one-time programmable and the development of permanent interconnections after configuration make them immune to SEUs. However, being non-reprogrammable, they lose their charm for utilization in multiple design modification scenarios. The second popular category consists of Flash-based FPGAs [33] which offer full reconfiguration though lacks in partial reconfiguration [2]. Moreover, these devices have typically lower TID rating than SRAM or Antifuse FPGAs [34]. Therefore, utilizing the performance of SRAM FPGAs while having built-in radiation-tolerance features leads to space-grade SRAM FPGAs, e.g., Xilinx Virtex 5QV [15], however, not all resources in these FPGAs are radiation hardened, e.g., BRAM and DSP modules [35].

In contrast to inherent radiation-tolerance capabilities of FPGAs, fault-tolerant computation approaches in hardware and software are utilized as well. TMR [9, 24] and scrubbing [36, 37] are two most popular techniques for tolerating SEUs and avoiding their accumulation in FPGA designs. TMR and its different voter implementations were discussed in Section 2.3.2. Scrubbing, on the other hand, involves refreshing the configuration memory contents by reading its golden copy at regular time intervals, to prevent accumulation of errors. Whether external or internal, scrubbing typically compares the calculated cyclic redundancy check (CRC) value of each of the configuration bitstream frames to the known CRC value of that frame [38] or rely on Hamming codes for single-error-correction-double-error-detection (SECDED) error mitigation [39]. Its worth noting that the configuration memory scrubbing do not account for errors in the user memory, i.e., BRAM, which can be made error-resilient by separate BRAM scrubbing, error-correcting codes (ECC) implementation or simply applying triple modular redundancy for each BRAM block. The combination of redundancy and scrubbing is considered a widespread optimal fault-tolerant solution in hardware. Additional approaches in literature include duplication with comparison (DWC) [40], error checking and correcting codes (ECAC) [41] and algorithm-based fault-tolerance (ABFT) [42], as examples. However, in this paper, we focus solely on redundancy and its different variations in hardware.

Hardware redundancy techniques for FPGAs are more involved than basic TMR with respect to partitioning a circuit into submodules, deciding on how many voters to insert, and where to place the voters in the FPGA design. Tools for automating redundancy-insertion in FPGA designs are available, including the TMR tool of Xilinx [43], Precision Hi-Rel software [44], and the BYU-LANL TMR tool [45]. Fault-tolerance mechanisms, particularly modular redundancy, comes with an overhead in terms of excessive area consumption as well as latency and power dissipation. Therefore, while providing fault-tolerance, the

**Figure 2.6:** TMR implementation in FPGA

design of a mission critical system also has to limit these overheads to given constraints. Generally, space-grade SRAM FPGAs have been used with redundancy and scrubbing features to obtain a combination of radiation-hardening by device as well as by design [35, 46].

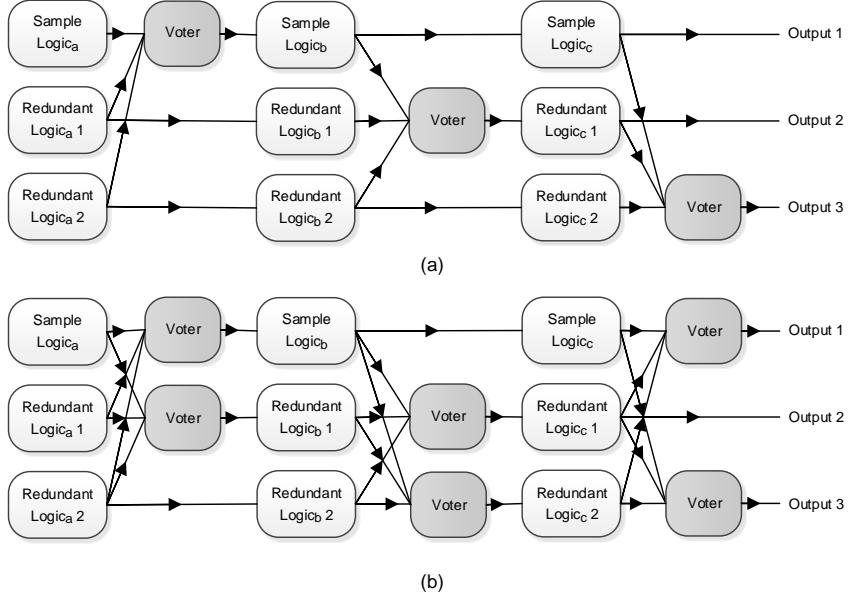

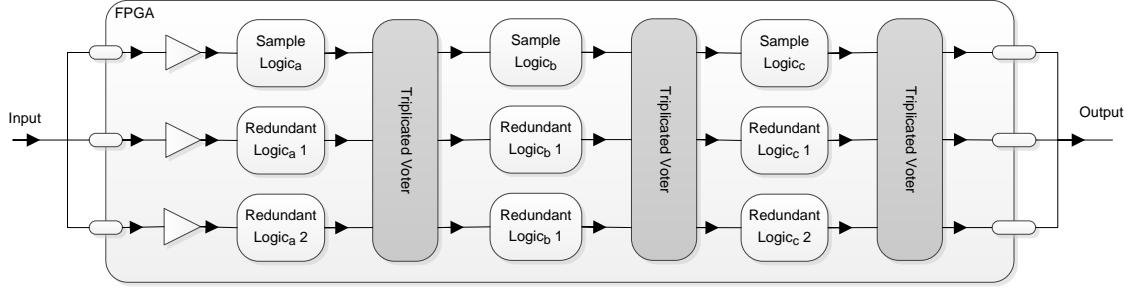

### Triple Modular Redundancy in FPGAs

The TMR technique can be used in an FPGA by simply triplicating the inputs, outputs and logic modules, inserting buffers and connecting the outputs of logic modules to the triplicated voter [24]. There are some practical considerations due to which this straightforward implementation is not suitable. Firstly, TMR is able to counter one error among the three redundant branches, and a larger length of each branch increases its probability of being erroneous more than once. To deal with this issue, there is a need to break the logic of the branch at regular intervals and place the triplicated voters in intermediate stages of the circuit as shown in Figure 2.6. Thus, an error occurring in one partition of the logic will not be forwarded to the next partition due to the error-mitigation effect of the triplicated voter. However, the minimum size of the logic partition, or granularity level, could be limited to a single component on an FPGA, e.g., a look-up table or a multiplexer. In addition, there are certain locations on an FPGA called illegal-cut locations which should not be triplicated due to the FPGA architecture, e.g., dedicated route connections in a slice [47]. Moreover, voters should not be placed on high-speed carry chains in order to not deteriorate the timing performance of the design. Most importantly, voters should always be added in the feedback paths to avoid data corruption at the outputs of sequential elements being forwarded into the feedback paths [24, 47]. These voters are commonly denoted as synchronization voters. Figure 2.7 shows a fine-grained TMR implementation than Figure 2.6 including combinational (inverter) and sequential (D-type flip-flop) elements as well as depicting a triplicated synchronization voter. Part(a) of this figure represents a state-machine of a simple 1-bit counter which is triplicated, in part(b), and the voters are inserted before the feedback path to follow the synchronization voter concept.

The process of automatic TMR insertion into a circuit design can be done by the automated redundancy-insertion tools, as mentioned previously. However, in this research, we use

**Figure 2.7:** TMR implementation of one-bit counter [24]

BYU-LANL (BANL) tool for generation of redundant circuit netlists, as it is the only open-source and modifiable tool compared to other commercial ones. The BANL tool is able to triplicate the design, insert voters and use built-in algorithms to take care of the constraints explained above. It is up to the discretion of the circuit designer to request the desired *redundancy configuration*, e.g., TMR with only single voters or with a mixture of single and triplicated voters. Moreover, there is a choice of eight algorithms that decide the placement of voters in the triplicated design. These algorithms are termed *voter-insertion* algorithms. Depending on the type of an algorithm, the sets of nets are determined where the voters should be inserted, e.g., using feedback edge set (FES) algorithms or decomposition of strongly connected components (SCCs) in the circuit graph [47]. The details of the these algorithms can be found in [48]. The algorithms used in the BANL tool and used in our experimentation are abbreviated as follows:

- CC: Connectivity cutset

- AFC: After flipflop cutset

- BFC: Before flipflop cutset

- BD: Basic decomposition

- HFC: Highest fanout cutset

- HFFC: Highest flipflop fanout cutset

- HFFIC: Highest flipflop fanin cutset

---

- HFFOC: Highest flipflop fanin output cutset

Originally, the BANL tool supported only SV and TV configurations while we extended the tool to support the rest of the three configurations, i.e., OAV, TAV and CTMR, as explained in Section 2.3.2. It has to be noted that all configurations have to resort to single voters for illegal-cut locations. This happens as the three redundant branches have to converge to one where the single voter provides the required convergence at the redundancy-forbidden locations. Therefore, the configuration TV which is the default configuration of the BANL tool as well as OAV, TAV and CTMR combines their respective configurations with single voter structures. However, we are not using sole SV configuration for experimentation due to its single point of failure limitation.

## 2.5 The Need for Adaptive Fault-tolerance in FPGAs

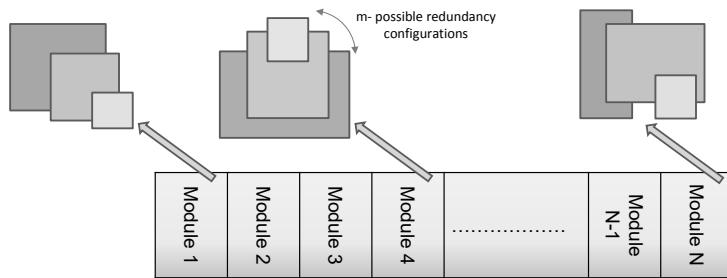

Following different redundancy structures in Section 2.3.2, we learned that by going towards higher levels of redundancy, the hardware usage increases. This in turn increases the area consumption, latency and power dissipation. Moreover, as briefly discussed in Section 2.1, the radiation strength of the space environment is fluctuating, and depends on the path of the space mission. Therefore, there is a need to develop an adaptive system that monitors the radiation strength and varies the redundancy levels accordingly at run-time thereby optimizing the trade-off between reliability and performance in a best possible way. An extended design approach to this idea is to vary the reliability/redundancy levels of individual hardware modules in a system according to their criticality or available resources on the FPGA. This concept is illustrated in Figure 2.8, where each of the  $n$  hardware modules have  $m$  possible redundancy configurations rated by different performance factors.

### 2.5.1 Correlating Adaptive Fault-tolerance with Varying-radiation Environments

In this section, based on the literature, we provide 4 distinct radiation scenarios to explain how the radiation strength varies along the path of a space mission, and hence discuss how

**Figure 2.8:** The Concept of Adaptive Redundancy

**Figure 2.9:** Borealis radiation strike-rate profile

varying reliability/redundancy levels fit into such radiation patterns. The first scenario is referenced with height, second and third with respect to time and fourth with solar conditions. The radiation strikes per minute and the soft error-rate are considered proportional measures of radiation strength, however, not all the radiation particles appear as errors in the hardware due to the their low ionizing energy or masking effects.

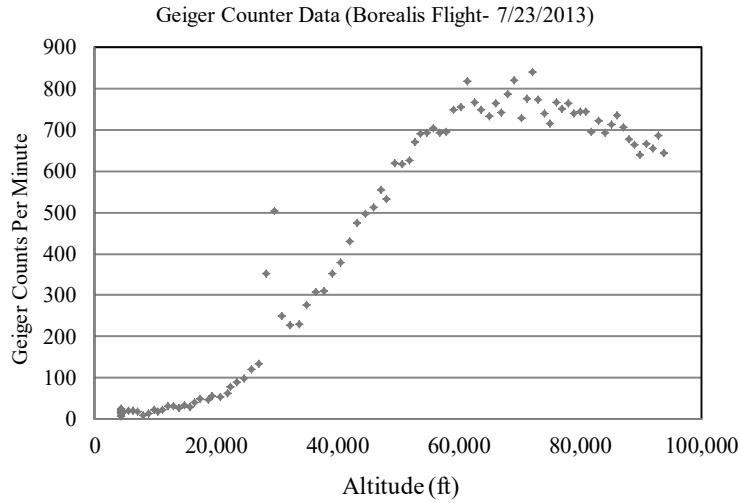

### Borealis Flight

In a hot air balloon testing conducted at University of Montana [49], a custom radiation sensor was built and sent to a high altitude of around 100,000 feet with the time duration of 103 minutes (one-way). The experiment was aimed at observing the total number of particles hitting the sensor in a high energy flux environment, up to 10 MeV. The sensor logged the radiation strikes per minute, detected by a Geiger counter that captures most of the low and high energy particles. Figure 2.9 shows the variation of the recorded radiation strike rate with altitude. This figure reports on an extended experimentation of [49] called as Borealis flight<sup>1</sup>. It is evident from this experiment that the radiation strikes increase sharply with altitude. To implement adaptive fault-tolerance in this scenario, one can divide the radiation data into number of regions equal to the redundancy levels/configurations at hand while utilizing higher redundant structures for high radiation regions. In this case, the more redundancy levels we have at hand, the better a system would be able to exploit the trade-off between reliability and performance. It is also worth noting that the sensor captured two radiation data points at approximately 30,000 feet which are uncorrelated to the trend. This emphasizes the need for a system which is able to adapt the reliability level in order to respond to unexpected deviations from an observed trend.

---

<sup>1</sup>The data has been obtained via private communication with the authors in [49].

**Figure 2.10:** Expected fault-rate of LEO [2]

### Low-Earth-Orbit Case Study

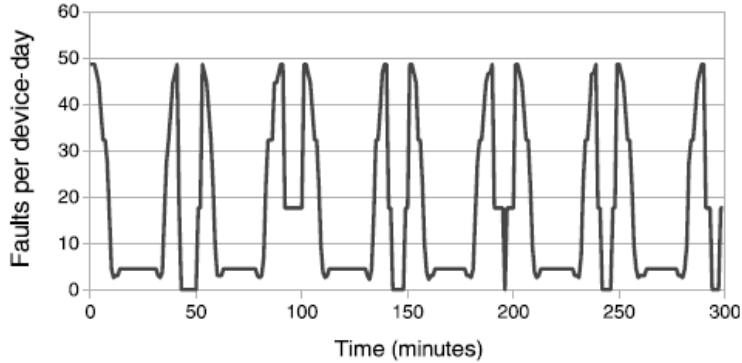

In the research work presented in [2], a fault-rate model is presented and used to simulate the expected error-rate for a path in low-earth orbit (LEO) with the two-line element (TLE) of EO-1 satellite. This orbit is typically used for Earth-observing science applications. The error-rate is presented in the unit of faults per device day which is useful to represent the cumulative error-rate when a number of devices/FPGAs are monitored in parallel. The orbital track of LEO case study has a mean travel time of 98 minutes due to which we see the repetition of fault pattern, in Figure 2.10, with maximum fault-rates estimated at the Earth's magnetic poles. The fault rate in this orbit is not excessive as the orbit has an altitude of 700 km which is below the Van Allen radiation belts and completely within the Earth's magnetosphere. It can be observed from the figure that there are approximately three discrete radiation/fault-rate levels, hence three reconfigurable reliability levels would be sufficient.

### Highly-Elliptical Orbit Case Study

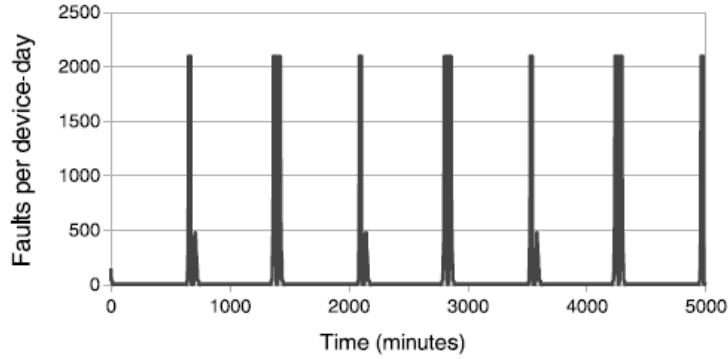

Referring to the research work in [2], an additional case study for expected fault-rate was conducted for an elliptical orbit of perigee 1100 km and apogee 39000 km with a mean travel time of 12 hours. The path is called Molniya orbit and used for the communication satellites in particular. Compared to the LEO case study, the fault-rate is very high especially when the satellite passes the Van Allen radiation belts. As can be seen in the radiation plot of Figure 2.11, the fault rate gets high at the end of the time period when it passes the Van Allen radiation belts. Most of the orbit duration has negligible fault-rate as compared to a short duration of excessive fault-rate at the end of the time period. For such a fault-rate profile, we can expect two reliability levels to be sufficient where the higher reliability level is required only for a very short duration.

**Figure 2.11:** Expected fault-rate of HEO [2]

#### Anticipated Error-Rate for Different Solar Conditions

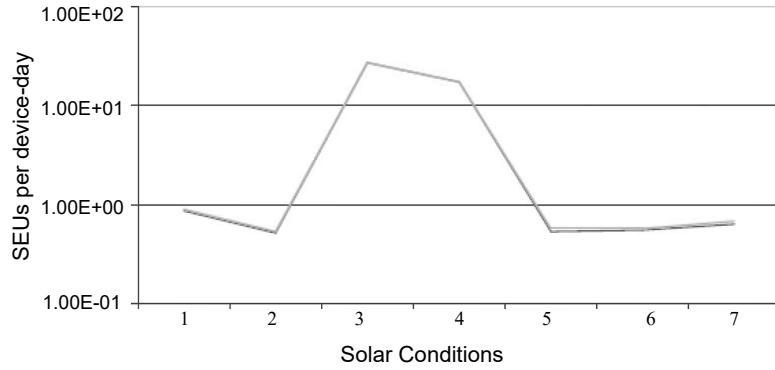

In the research work conducted in [28], an expected error-rate for another LEO was anticipated for seven different solar conditions as shown in Figure 2.12. While the names of the solar conditions are replaced with numeric numbers in the figure for simplicity; their details can be found in [28]. The graph shows the minimum fault-rate of 0.5 SEUs per device day in solar condition No. 2 and maximum fault-rate of 26 SEUs per device day for solar condition No. 3. The graph can be divided into two regions according to SEU-rate. The first region (solar conditions No. 1, 2, 5, 6 and 7) can be used with low redundancy while second region (solar conditions No. 3 and 4) can be used with high redundancy structures.

**Figure 2.12:** Expected fault-rate of LEO orbit under different solar conditions [28]

---

## 2.6 Reliability Evaluation of FPGA Designs for Space Computing

The reliability of the FPGA based hardware designs for space applications can be computed by developing methods following the knowledge of space environment and device vulnerability. The different resources of an FPGA, e.g., configuration memory, BRAM, DSP components, etc should be modeled for reliability separately since each of these resources respond differently to radiation. Additionally, the redundant structures can be evaluated for reliability-enhancement by developing fault-rate models. The traditional way of modeling reliability of electronic systems is to describe the time until the system fails by a random variable. Using an exponential distribution for the time between failures, assuming independent failures, and a constant fault-rate  $\lambda$  we can determine a system's time-dependent reliability  $R(t)$  as defined by Equation 2.3.

$$R(t) = e^{-\lambda t} \quad (2.3)$$

Assuming a constant fault-rate is reasonable if we exclude the burn-in and wear-out phases of systems. Thus, based on an estimated or measured fault-rate,  $R(t)$  can be calculated and expresses the probability that a system survives, i.e., is without fault, from its start at time 0 until time  $t$ . The reciprocal of  $\lambda$  is denoted as mean-time to failure (MTTF) or mean-time between failures (MTBF) in case of systems that can be repaired. MTTF and MTBF are widely used as reliability metrics. Though many research works follow this generic reliability equation, they differ in how they determine the fault-rate  $\lambda$ . In literature, two methods of reliability/fault-rate computation for FPGAs are used in addition to error-injection based simulations and radiation testing methods.

### 2.6.1 CREME96 based Reliability Computation

Vanderbilt University's online tool CREME96 [50] is specifically used to compute fault-rate of devices used in aerospace missions. The tool takes as input parameters defining a space orbit, weather conditions and fault cross-section of a device and hence computes the fault-rate/SEU-rate of the device in units faults per device-day [12].

#### Device Characterization

The initial step is to characterize the device that is to be used in space orbit. For this purpose, the device's upset rate is calculated via experimental testing in particle accelerator. Afterwards, the FPGA's static cross-section is determined by calculating the upsets caused in the device for a given fluence of radiation, as shown in Equation 2.4.

$$\sigma = \frac{\text{Number of errors}}{\text{fluence (particles/cm}^2\text{)}} \quad (2.4)$$

The static cross-section refers to the FPGA's vulnerable area to radiation particles at a specific energy. Therefore, the experimental testing is repeated for a range of energy levels including both proton and heavy ions to compute the overall static SEU cross-section.

### Path/Orbit Specification

CREME96 uses data from previous satellite orbits to predict an average flux of particles in certain orbits under different solar conditions. Therefore, while choosing orbit conditions and parameters, the specific solar condition has to be selected as well. *Solar Minimum* and *Solar Maximum* refers to the lowest and highest averaged flux during the solar activity of 11 year solar cycle, respectively. The *worst week*, *worst day* and *worst 5 minute peak* solar conditions refers to the specific solar event of October 1989, and used for worst case estimates. Additionally, *peak trapped proton* solar condition refers to the worst proton flux for all proton energies for both solar minimum and maximum portions of solar cycle.

### SEU Rate Prediction

Therefore, utilizing the device SEU cross-section, choosing a solar condition and by providing specific parameters of space orbit, the SEU rate due to heavy ions and protons are computed separately and hence averaged. The basic fault-rate model of this tool whether used in its original form or modified for specific system designs can be found in research works of [2, 3, 46]. However, the impact of redundancy can be modeled by Markov fault model [2] or classical TMR equation [46].

### 2.6.2 Probabilistic Computational Reliability Models

Another category of reliability computation is via probabilistic computational models that take as input error probabilities of individual components and compute the output error probability  $\varepsilon_{out}$  of the overall system by propagating error probabilities from inputs to outputs. A number of publications relate the output error probability to the system's reliability according to  $R = (1 - \varepsilon_{out})$ , the most popular works being [51, 52, 53, 54]. It is important to note that this notion of reliability and the underlying notion of a system's output error probability are instantaneous and hence timeless. The related work, however, does not detail how to determine the exact component error probabilities and uses arbitrarily set values. Hence, the probabilistic computational models are in contrast to the time-dependent reliability measure of Equation 2.3, and the fault-rate method in CREME96 that simulates real device and orbit features and targets mainly radiation induced errors. A brief overview of the major probabilistic computational models along with their complexity is provided as follows.

An accurate and powerful model in error probability calculation is the probabilistic transfer matrices model (PTM) [51], though it is an extremely complex and time-intensive method when used for large circuits. For large circuits, the number and size of matrices become huge which needs a lot of storage memory and computation time for calculating regular and tensor matrix products. The major concern is the modelling of a wire swap as a single PTM stage. In FPGAs where wire swaps are based on the placed and routed design by FPGA design softwares, e.g., Xilinx ISE, the reliability differs from one routed design to another. Moreover, the numerous wire swaps in large circuits drastically increase the number of matrix calculations, which is why this approach is unfeasible for modelling large

circuits. Algebraic decision diagrams (ADD) have been used to improve the storage and timing performance of PTM method though it is still a non-promising solution for large circuits. An error-analysis for sequential circuits based on PTM is proposed in [55] though the application is considered for a simple adder only.

A major research work in error-modelling has been proposed with the probabilistic gate model (PGM) [52] and the Bayesian networks error modelling [53]. The basic algorithm of PGM is easy to model though the accurate model has a high complexity particularly to evaluate reliability of large circuits. Therefore, a midway solution called modular approach is proposed for large circuits though no details of a toolbox implementation or assumptions considered are presented. Moreover, sequential circuits are not supported. Similarly, Bayesian networks are used efficiently for analyzing small circuits; however approximate techniques are proposed for large circuits due to complexity of the model. Additionally, the results of Bayesian model are highly incomparable to PTM and other popular error probabilistic schemes [56].

Probabilistic decision diagrams (PDD) [57] provide a model scalable for analysis of large circuits by decomposing the circuit based node graph and thus achieving timing efficiency. However, its worst-case complexity is still exponential in the number of inputs of the circuit. Probabilistic model checking [58] is another approach measuring circuit reliability but on the cost of excessive memory requirement and timing complexity. The memory requirement problem was addressed successfully in [26] though high runtimes are still a problem. A hybrid approach combining exact and probabilistic models to evaluate reliability is proposed in [59]. This scheme lowers the complexity of the analysis, however the timing results are not reported. The analysis is performed on small circuits excluding sequential elements though it is a good approach to harden error-sensitive gates in the circuit by upsizing them. Observability-based and single-pass reliability analysis [60] claims to be an extremely fast and scalable approach particularly compared to PTM and Bayesian techniques though the work lacks detailed results and comparisons. A strong focus is given on using observability analysis to improve reliability by manipulating reconvergent fanout while avoiding redundancy-insertion.

A simple and fast approach known as Boolean difference error calculator (BDEC) is proposed in [54, 61]. This technique is independent of the wire swapping, involves simple Boolean calculus and is perfectly analytic which makes it accurate for calculating reliabilities for circuits of any size. Moreover, its complexity is linear in the number of inputs of the circuit. Since the model is applicable to any logic element represented in a form of Boolean equation, it is perfect to use with FPGA based netlists. The authenticity of this approach has been proved by the comparison of results of this scheme with Monte Carlo simulations performed in [54]. A close insight into BDEC can be found in the next chapter where we utilized and modified this technique to calculate reliability values of non-redundant and redundant versions of utilized benchmarks.

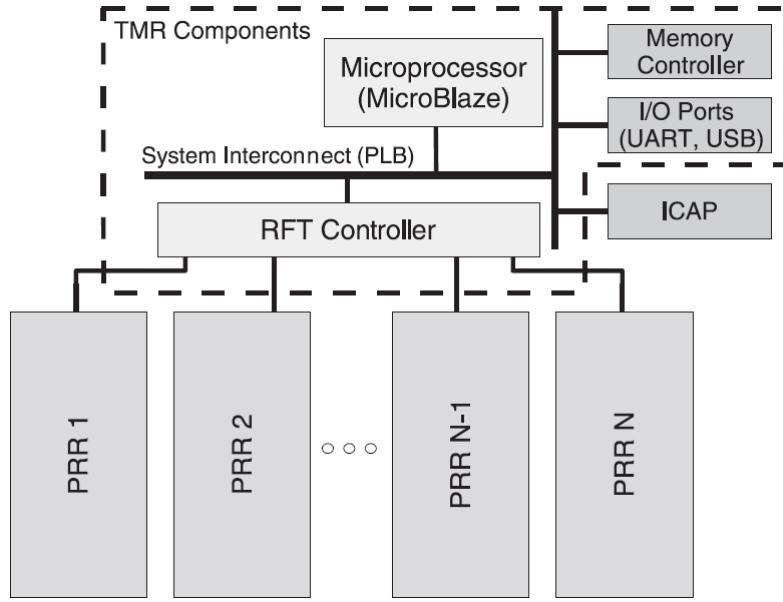

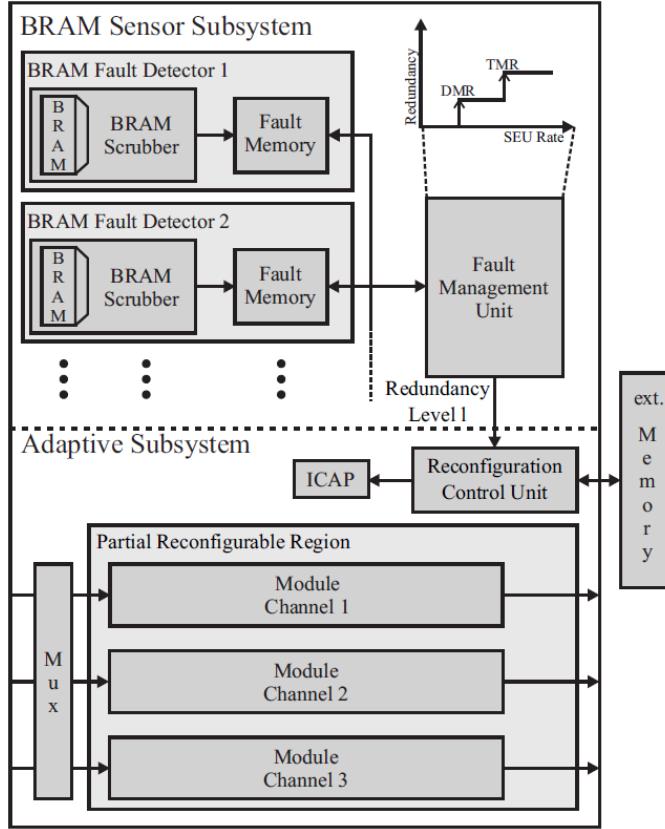

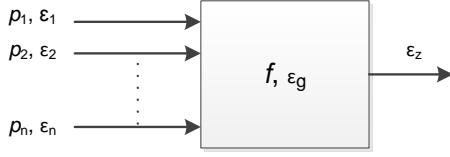

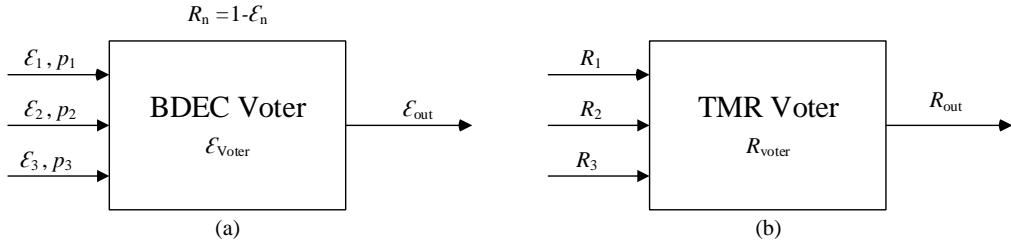

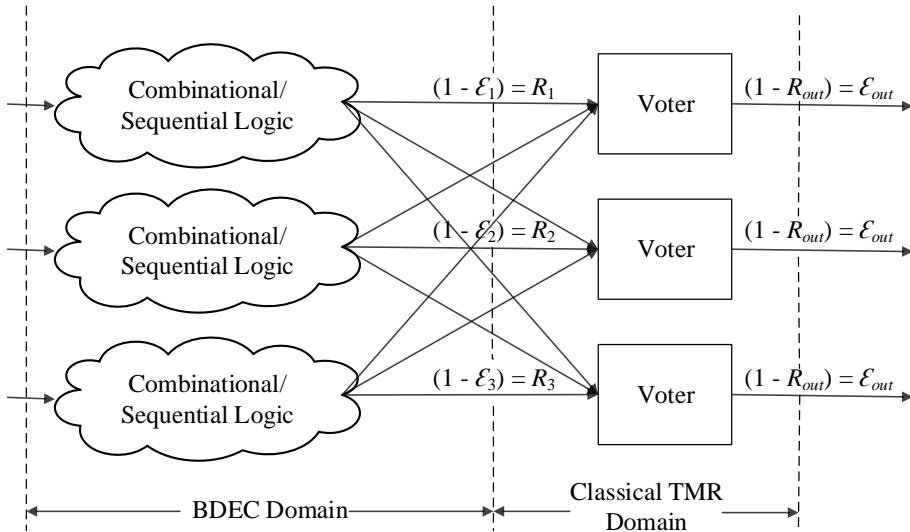

The drawback of using these probabilistic methods is that they do not take into account the impact of redundancy. While redundant configurations of a circuit are known to be more reliable than non-redundant version, these methods provide us even lesser reliability of redundant circuits since they take each component as erroneous and bigger