INTERFACING DETECTORS AND

COLLECTING DATA FOR

LARGE-SCALE EXPERIMENTS IN

HIGH ENERGY PHYSICS

USING COTS TECHNOLOGY

*Jörn Schumacher*

**PADERBORN UNIVERSITY**

*The University for the Information Society*

*Dissertation*

Department of Computer Science

Paderborn University

INTERFACING DETECTORS AND

COLLECTING DATA FOR LARGE-SCALE

EXPERIMENTS IN HIGH ENERGY

PHYSICS USING COTS TECHNOLOGY

Jörn Schumacher

*Author*

Prof. Dr. Christian Plessl

*Academic Supervisor*

# Contents

|                 |                                                                                       |           |

|-----------------|---------------------------------------------------------------------------------------|-----------|

| <b>Contents</b> | <b>i</b>                                                                              |           |

| <b>1</b>        | <b>Introduction</b>                                                                   | <b>1</b>  |

| 1.1             | Motivation . . . . .                                                                  | 1         |

| 1.2             | High Energy Physics and Accelerator Experiments . . . . .                             | 2         |

| 1.3             | Trigger and Data Acquisition Systems . . . . .                                        | 5         |

| 1.4             | Contribution . . . . .                                                                | 7         |

| 1.5             | Outline . . . . .                                                                     | 10        |

| <b>2</b>        | <b>From Custom to COTS Components: Evolution of the ATLAS Data-Acquisition System</b> | <b>11</b> |

| 2.1             | LHC Upgrade Program . . . . .                                                         | 11        |

| 2.2             | LHC Run 1 (2009 – 2013) . . . . .                                                     | 12        |

| 2.3             | Run 1 Performance Data . . . . .                                                      | 18        |

| 2.4             | LHC Run 2 (2015 – 2018) . . . . .                                                     | 20        |

| 2.5             | LHC Run 3 and beyond . . . . .                                                        | 24        |

| 2.6             | Centralized Data Distribution with FELIX . . . . .                                    | 25        |

| 2.7             | Related Work . . . . .                                                                | 27        |

| <b>3</b>        | <b>Architecture of a COTS-based Read-Out Switch</b>                                   | <b>29</b> |

| 3.1             | Overview . . . . .                                                                    | 29        |

| 3.2             | Detector Connectivity . . . . .                                                       | 29        |

| 3.3             | The Detector Link Interface Card . . . . .                                            | 31        |

| 3.4             | The FELIX Software Stack . . . . .                                                    | 34        |

| 3.5             | Related Work . . . . .                                                                | 39        |

| <b>4</b>        | <b>Efficient Decoding of Detector Link Data Streams</b>                               | <b>41</b> |

| 4.1             | Overview . . . . .                                                                    | 41        |

| 4.2             | The PCIe Packet Format . . . . .                                                      | 41        |

| 4.3             | The Packet Decoding Algorithm . . . . .                                               | 42        |

| 4.4             | Profiling . . . . .                                                                   | 43        |

| 4.5             | Optimizations . . . . .                                                               | 43        |

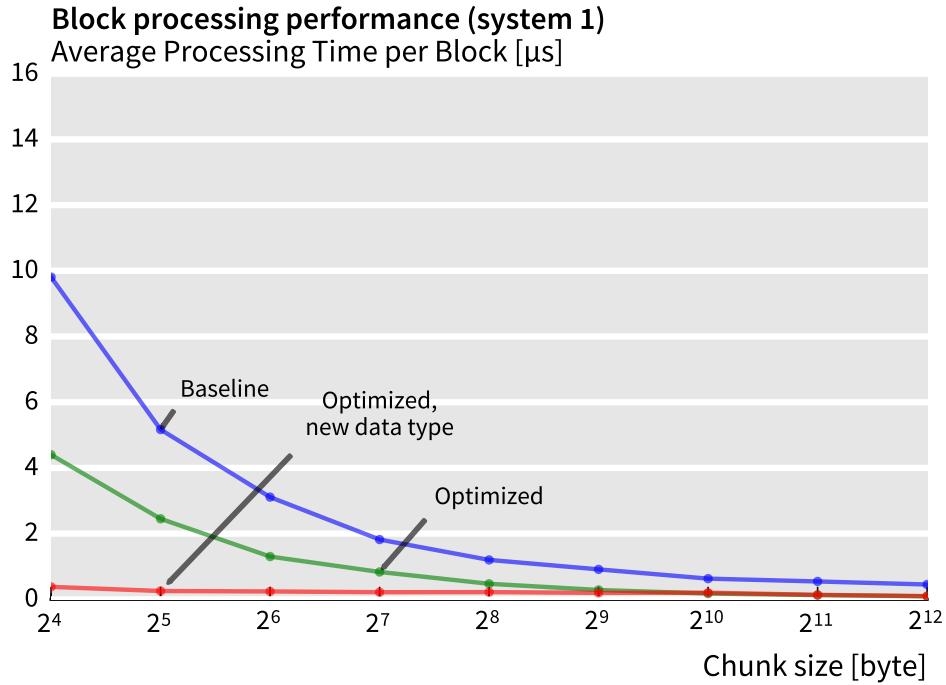

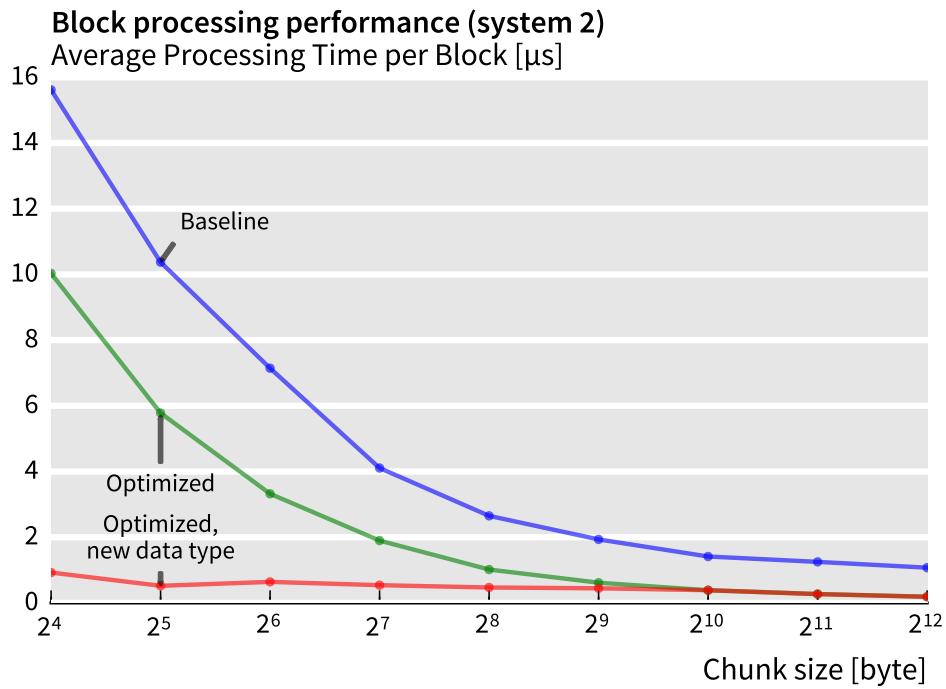

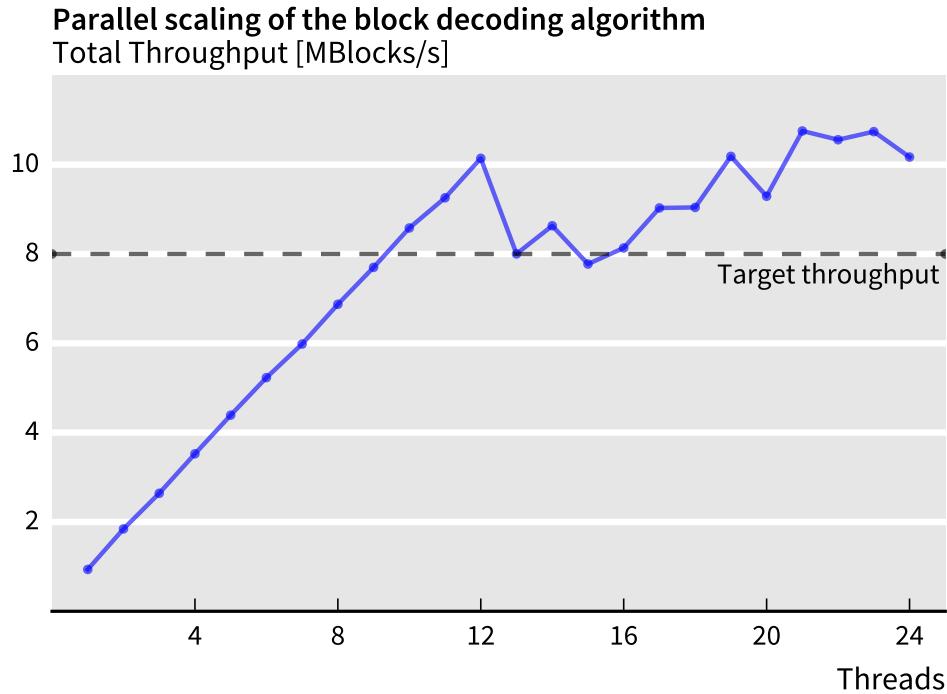

| 4.6             | Benchmark Results . . . . .                                                           | 46        |

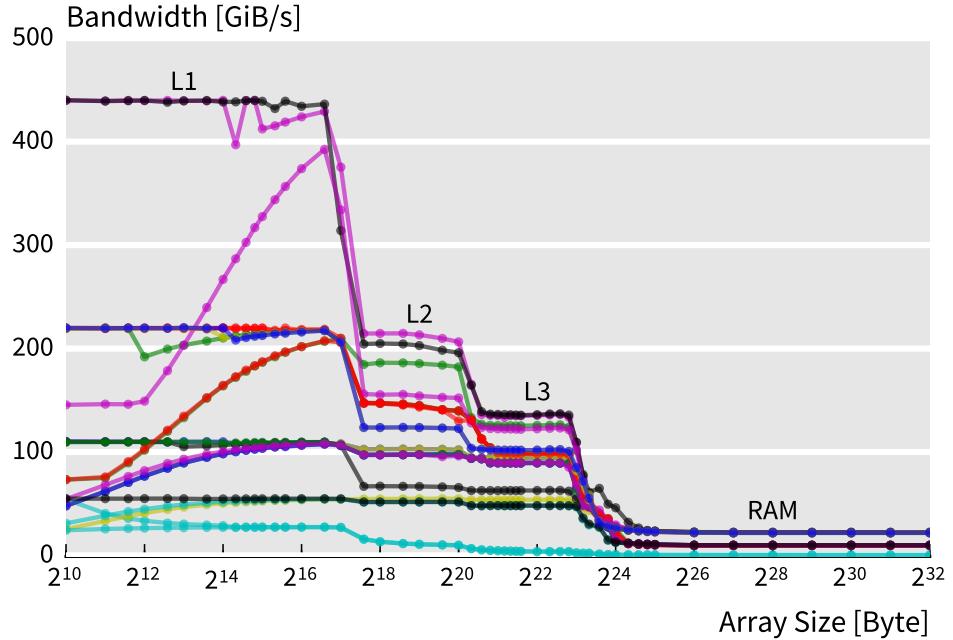

| 4.7             | Memory Bandwidth Analysis . . . . .                                                   | 48        |

|                                                      |            |

|------------------------------------------------------|------------|

| 4.8 Conclusion . . . . .                             | 52         |

| 4.9 Related Work . . . . .                           | 53         |

| <b>5 Fast Networking for DAQ Systems</b>             | <b>55</b>  |

| 5.1 Overview . . . . .                               | 55         |

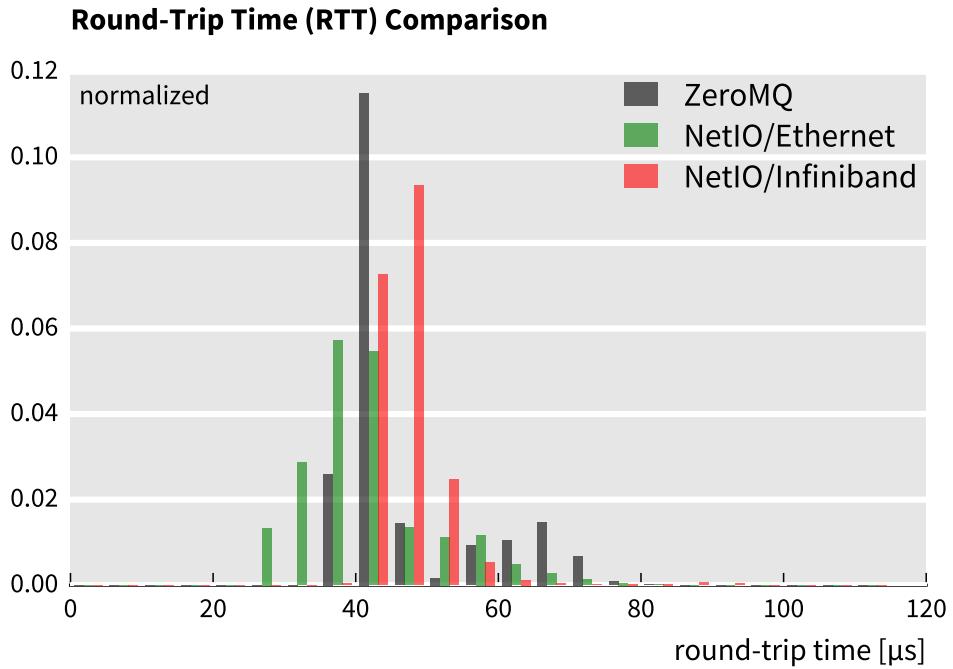

| 5.2 Networking in FELIX . . . . .                    | 56         |

| 5.3 The NetIO Message Service . . . . .              | 58         |

| 5.4 User-level sockets . . . . .                     | 60         |

| 5.5 Low-Level Sockets . . . . .                      | 62         |

| 5.6 The POSIX Back-end . . . . .                     | 63         |

| 5.7 The FI/Verbs Back-end . . . . .                  | 64         |

| 5.8 The Intel OmniPath Back-end . . . . .            | 65         |

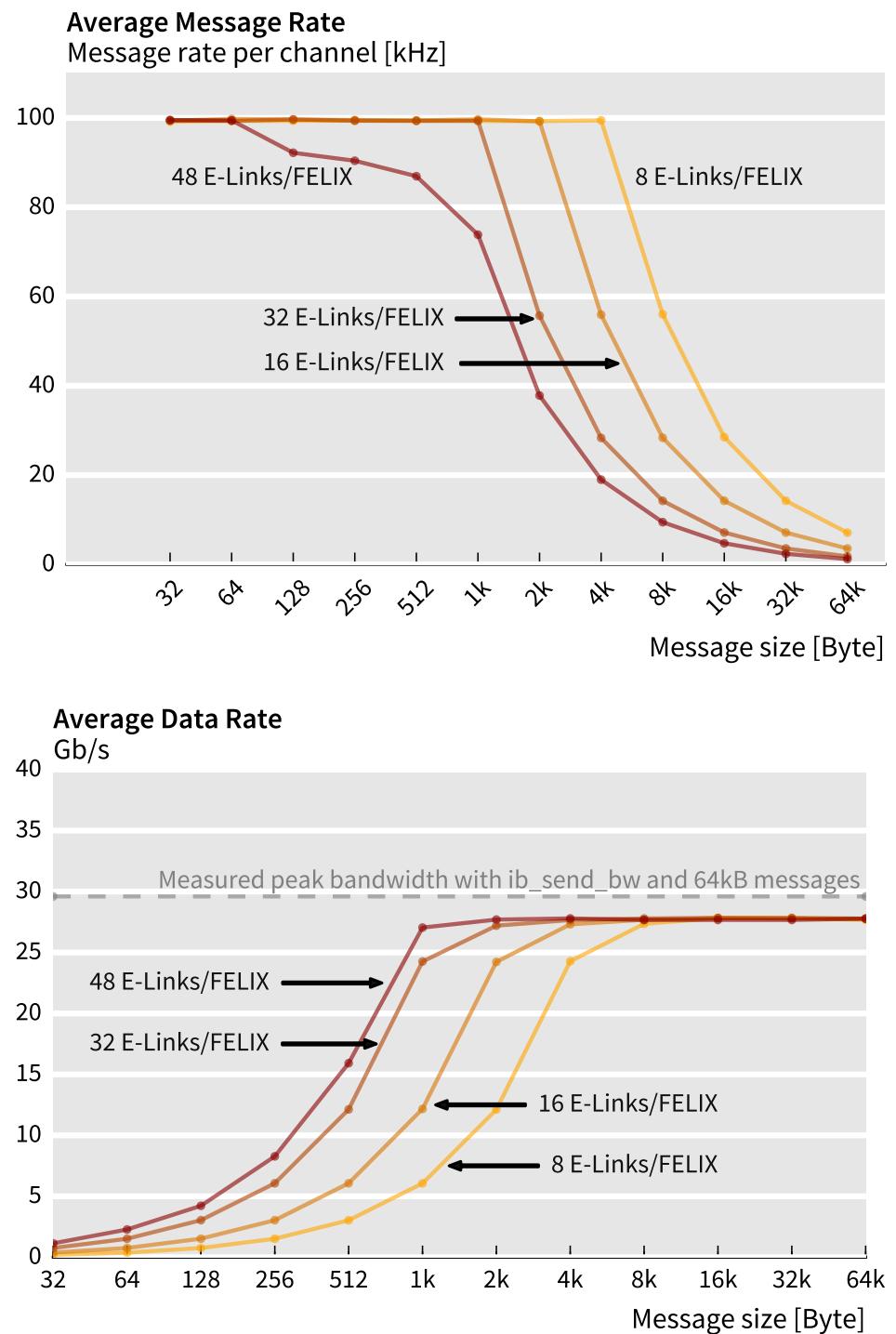

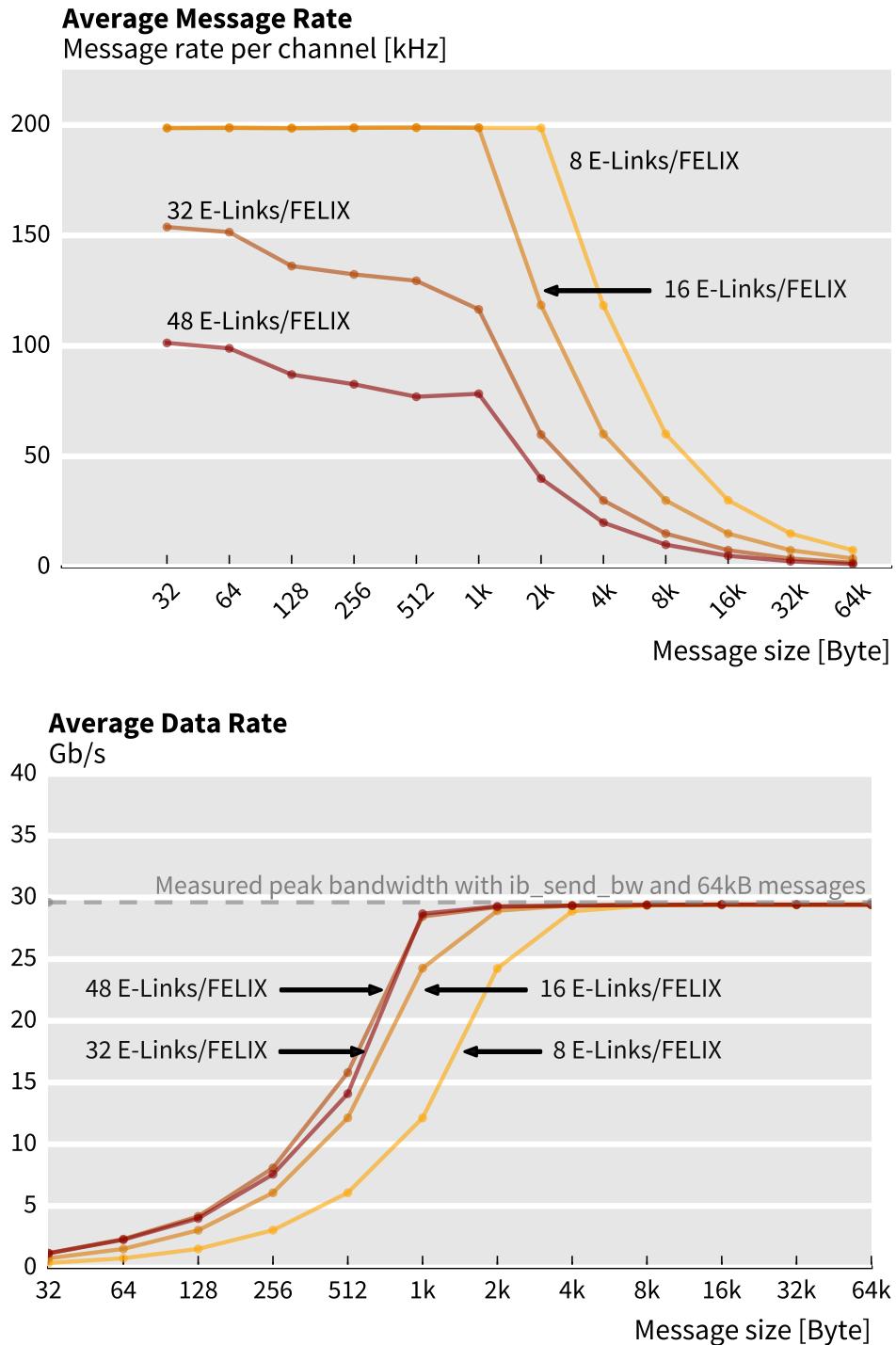

| 5.9 Benchmarks and Tests with NetIO . . . . .        | 65         |

| 5.10 Related Work . . . . .                          | 68         |

| <b>6 System Evaluation of a COTS-based Read-Out</b>  | <b>71</b>  |

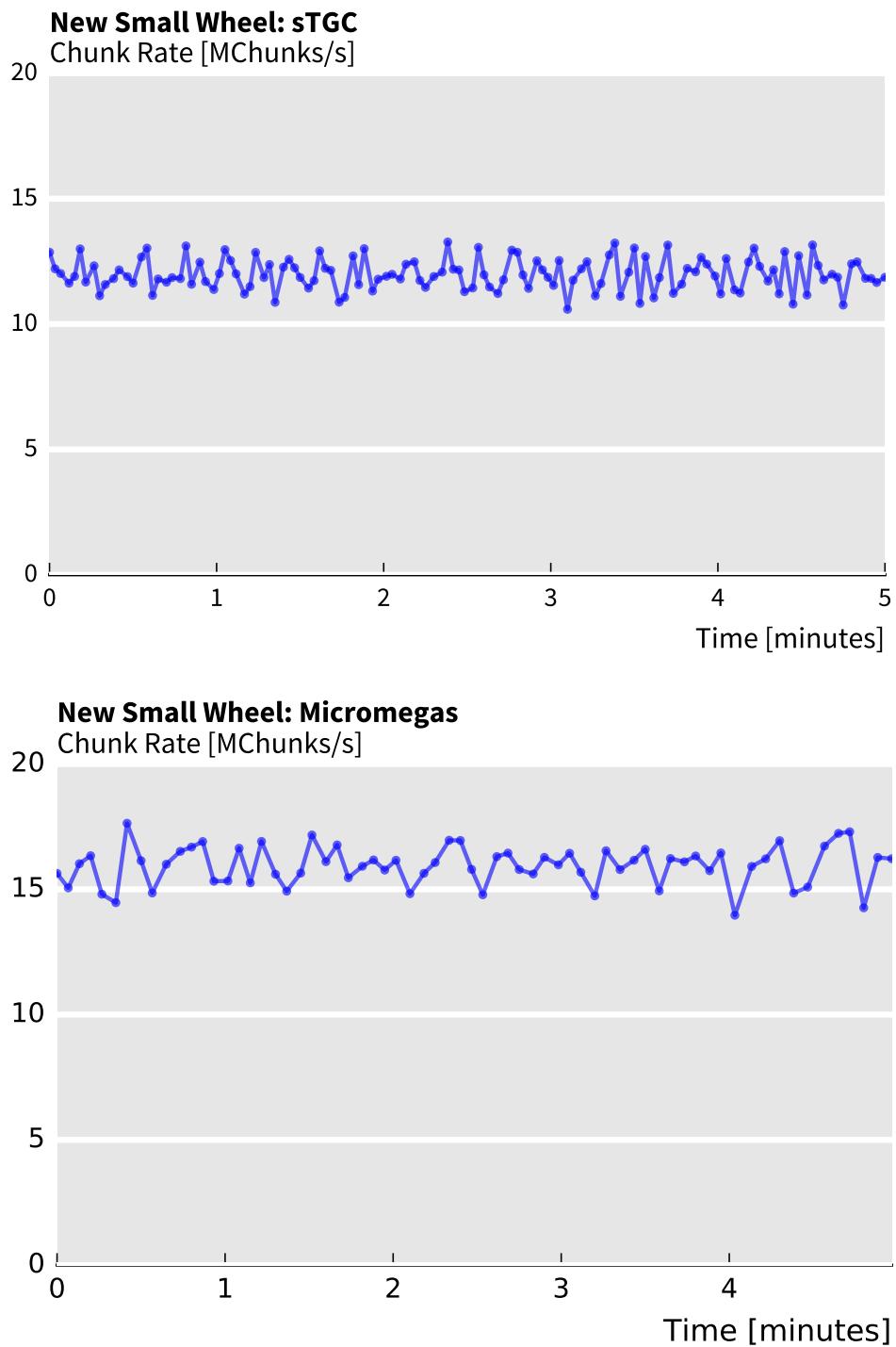

| 6.1 Methodology . . . . .                            | 71         |

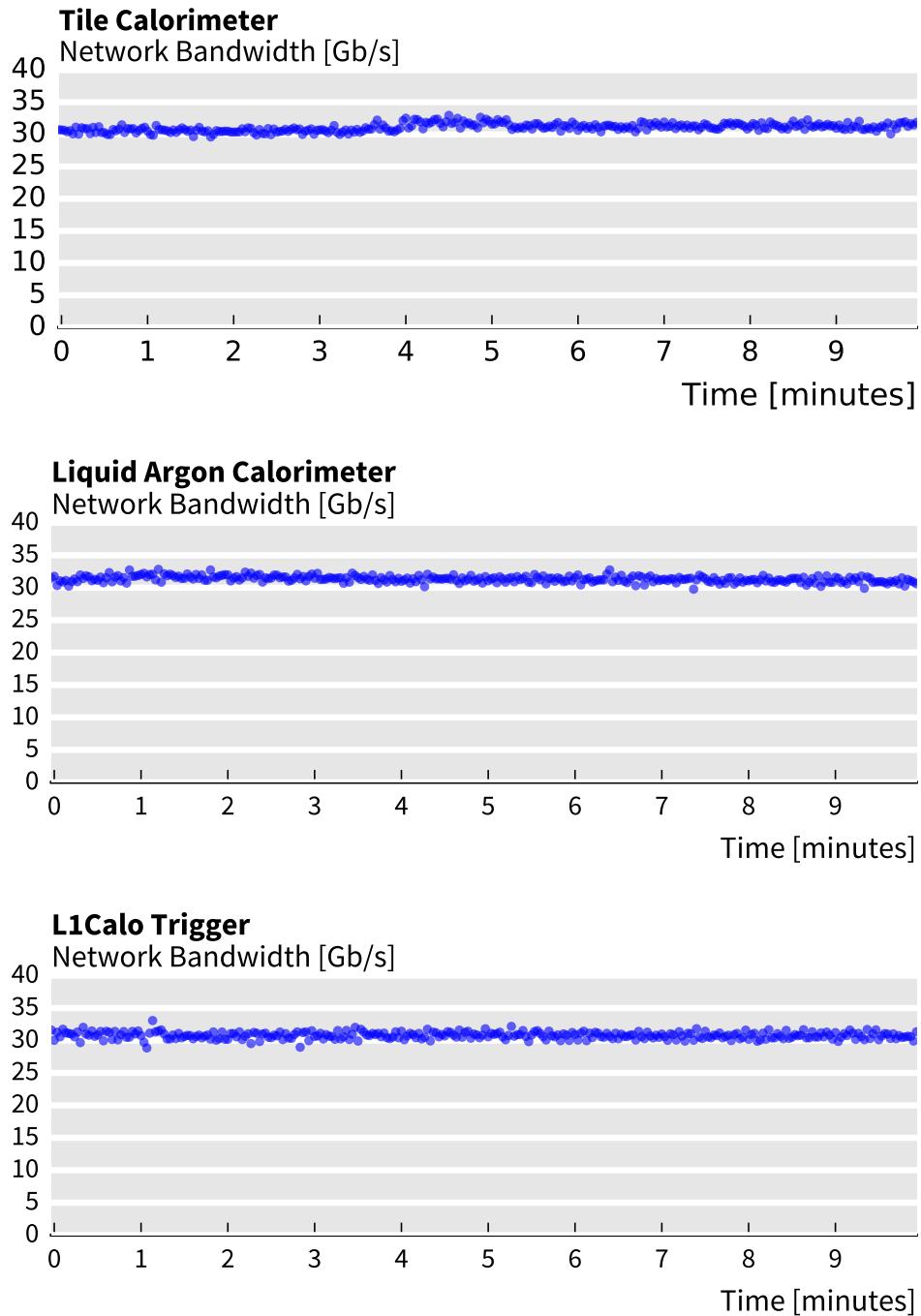

| 6.2 Case Study: The New Small Wheel . . . . .        | 72         |

| 6.3 Case Study: Full Mode . . . . .                  | 74         |

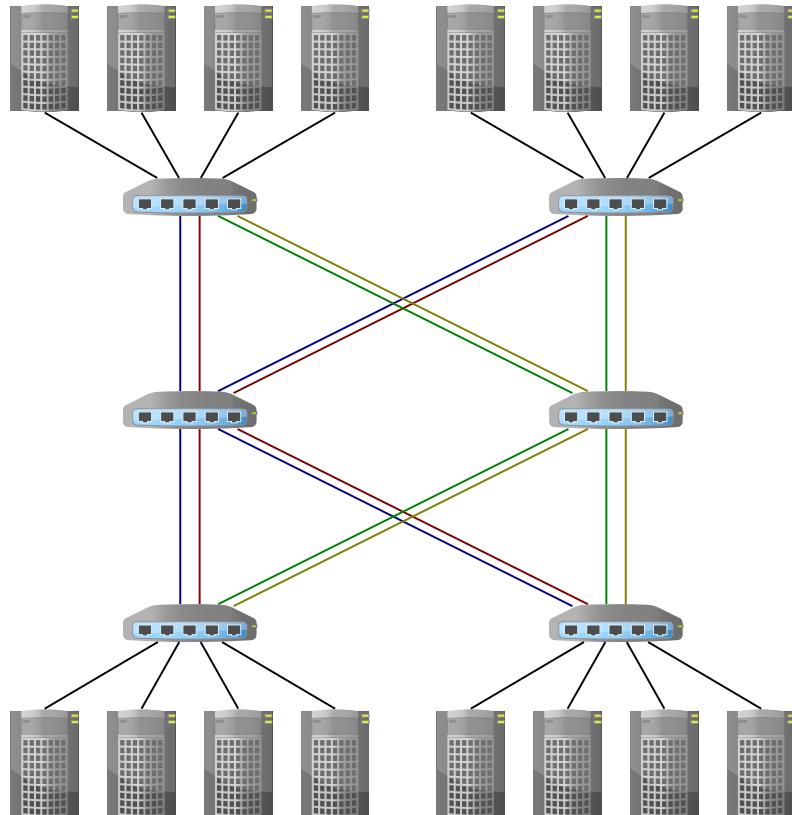

| 6.4 Scalability . . . . .                            | 78         |

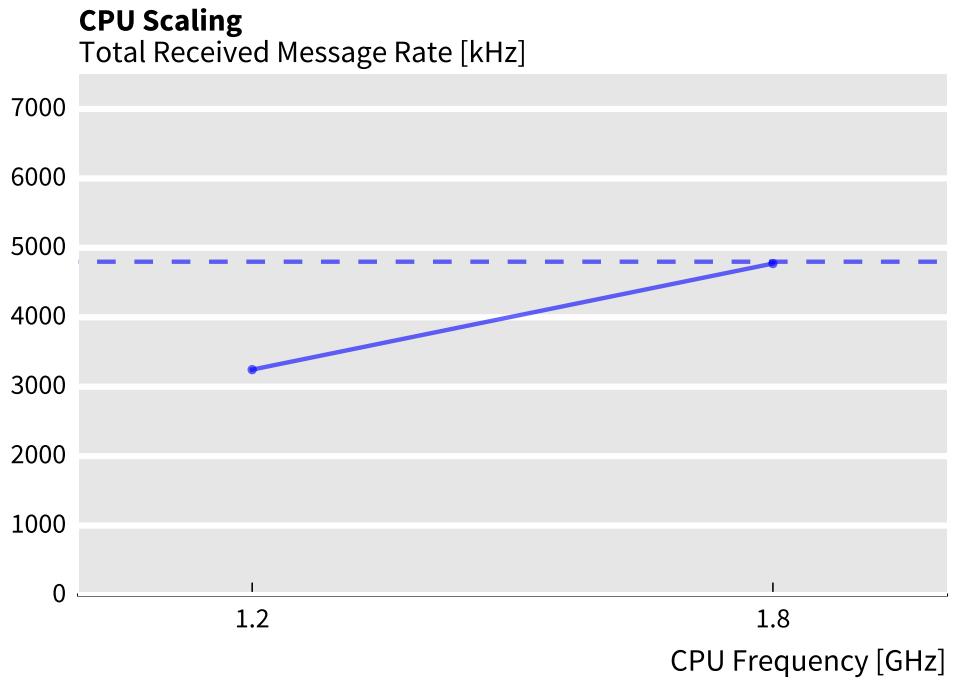

| 6.5 CPU Scaling . . . . .                            | 82         |

| <b>7 Conclusion</b>                                  | <b>85</b>  |

| 7.1 Summary . . . . .                                | 85         |

| 7.2 COTS-based Readout for HEP experiments . . . . . | 85         |

| 7.3 FELIX . . . . .                                  | 86         |

| 7.4 Outlook . . . . .                                | 87         |

| 7.5 Final Words . . . . .                            | 88         |

| <b>Publications of the Author</b>                    | <b>89</b>  |

| <b>Bibliography</b>                                  | <b>91</b>  |

| <b>List of Figures</b>                               | <b>97</b>  |

| <b>List of Tables</b>                                | <b>99</b>  |

| <b>Acronyms</b>                                      | <b>101</b> |

## Abstract

Data-acquisition systems for high-energy physics experiments like the ATLAS experiment at the European particle-physics research institute CERN are used to record experimental physics data and are essential for the effective operation of an experiment. Located in underground facilities with limited space, power, cooling, and exposed to ionizing radiation and strong magnetic fields, data-acquisition systems have unique requirements and are challenging to design and build.

Traditionally, these systems have been composed of custom-designed electronic components to be able to cope with the large data volumes that high-energy physics experiments generate and at the same time meet technological and environmental requirements. Custom-designed electronics is costly to develop, effortful to maintain and typically not very flexible.

This thesis explores an alternative architecture for data-acquisition systems based on commercial off-the-shelf (COTS) components. A COTS-based data distribution device called FELIX that will be integrated in ATLAS is presented. The hardware and software implementation of this device is discussed, with a specific focus on performance, heterogeneity of systems and traffic patterns. The COTS-based readout approach is evaluated in the context of the future requirements of the ATLAS experiment.

The main contributions of the thesis are an analysis of the ATLAS data-acquisition system with a focus on the readout system, a software architecture for the main application on FELIX hosts, a performance analysis and tuning based on computer science methods for central FELIX software components with respect to the requirements of the ATLAS experiment, a network communication library with a high-level software interface to utilize high-performance computing network technology for the purpose of data-acquisition systems, and an evaluation and discussion of ATLAS data-acquisition using FELIX systems as a case study for COTS-based data-acquisition in high-energy physics.

## Zusammenfassung

Datenerfassungssysteme für Experimente in der Hochenergiephysik wie das ATLAS Experiment am europäischen Forschungsinstitut für Teilchenphysik CERN werden eingesetzt, um experimentalphysikalische Daten aufzuzeichnen und sind essenziell für den effektiven Betrieb eines Experiments. Solche Systeme sind oft in unterirdischen Einrichtungen untergebracht und haben begrenzten Zugang zu Strom, weniger Möglichkeiten zur Kühlung und sind zudem ionisierender Strahlung sowie magnetischen Feldern ausgesetzt. An ihre Entwicklung werden einzigartige Anforderungen gestellt und stellen eine Herausforderung dar.

Um mit den hohen Datenmengen, die ein Hochenergiephysikexperiment erzeugt, umgehen zu können und gleichzeitig den technologischen und umweltbedingten Anforderungen zu genügen bestehen diese Systeme traditionell aus individuell gefertigten elektronischen Komponenten. Solche eigenentwickelten Komponenten sind allerdings teuer zu entwickeln, schwer zu warten und in der Regel nicht sehr flexibel.

Diese Arbeit untersucht eine alternative Architektur für Datenerfassungssysteme die auf kommerziellen Standardkomponenten (commercial off-the-shelf, COTS) basiert. Eine in das ATLAS Experiment zu integrierende COTS-basierte Datenverteilungskomponente "FELIX" wird vorgestellt. Die Hardware- und Software-Implementierung dieses Geräts wird diskutiert, mit einem Schwerpunkt auf Leistungsfähigkeit, Heterogenität der Systeme und Kommunikationsmuster. Der COTS-basierte Ansatz wird im Rahmen der zukünftigen Anforderungen des ATLAS-Experiments bewertet.

Die Hauptbeiträge dieser Dissertation sind eine Analyse des ATLAS Datenerfassungssystems mit Schwerpunkt auf dem Datenauslesesystem, eine Software Architektur für die Hauptsoftwarekomponente von FELIX Systemen, eine Performanzanalyse und Geschwindigkeitsverbesserungen von zentralen FELIX Softwarekomponenten basierend auf Prinzipien und Methoden der Informatik unter Beachtung der Anforderungen des ATLAS Experiments, eine Softwarebibliothek für Netzwerkkommunikation die es erlaubt Netzwerktechnologie aus dem Bereich des Hochleistungsrechnen für die Zwecke von Datenerfassungssystemen zu nutzen, und letztlich eine Evaluation des neuen ATLAS Datenerfassungssystems mit FELIX als Fallstudie für COTS-basierte Datenerfassungssysteme in der Hochenergiephysik.

## Acknowledgements

This dissertation is the product of more than three years of research. During this time, many people contributed with advice and support in one way or the other. I would like to express my sincere gratitude to all the individuals who helped me along the way. Without their help this dissertation would not have been possible.

First and foremost, I thank my academic advisor Professor Christian Plessl and my CERN supervisor Dr Wainer Vandelli. During my placement at CERN both of them provided me with guidance and advice as much as freedom to explore new ideas.

A large portion of the research presented in this thesis is based on the ATLAS FELIX project. I thank the FELIX development team for the productive and fun collaboration. It has always been a great joy to work as a member of this team.

I thank Emily, Noel, Sean, Tobias, and Will for their time and effort that they put into proofreading this dissertation, and Volker for his advice on graphics. Their comments were a tremendous help in improving my writing.

Finally, I thank my family, my wife Natalia and our daughter Stella, my parents Anton and Maria-Luise, and my brothers Volker and Tobias, for their endless support during the past years. They have been an enormous source of motivation.

# Chapter 1

## Introduction

### 1.1 Motivation

Data acquisition (DAQ) systems for high energy physics experiments are often implemented as complex distributed applications. The DAQ system of the ATLAS experiment [1] at the Large Hadron Collider [2] at CERN in Geneva, Switzerland consists of tens of thousands of applications running on thousands of nodes, in addition to a large amount of custom-designed electronic components. The DAQ system has to interface the ATLAS detector front-end electronics via dedicated custom optical links. The cost of building and maintaining an experiment like ATLAS is high, and thus a DAQ system needs to operate efficiently and record data at a high rate and high quality.

The high data rates in DAQ systems pose a challenge for computing and networking components, so traditionally many custom-designed electronic components, FPGAs, DSPs and so forth have been used to build early components of a DAQ chain close to the detectors. In the past years a trend has emerged in the high energy physics community to push the use of commercial off-the-shelf (COTS) components ever closer to the detectors and reduce the amount of custom electronics. The motivation this approach is the reduction of development time and cost as well as facilitating maintenance and operation of DAQ systems.

The ATLAS experiment is following this trend as well, and in this thesis I present the approach that the experiment is taking. The ATLAS approach is based on FELIX, a new central data distribution system that sits between the ATLAS detectors and data filters and processors and forwards data in both directions. A project like FELIX has to meet the various computational requirements of DAQ systems, e.g., to handle a high data throughput, low or fixed latencies for low-level data communication, high availability and so forth. The thesis shows the specifications of the FELIX system and explores how such a system can be implemented to meet the aforementioned requirements.

## 1.2 High Energy Physics and Accelerator Experiments

High energy physics (HEP), or particle physics, is the study of elementary particles [3]. Particle colliders are an important tool in HEP. A particle collider works by accelerating two beams of charged particles by the means of electromagnetic fields. The two beams cross in defined interaction points, where particles from the two crossing beams collide at high energies. The outcome of these collisions can be new particles which can be detected and analyzed by instruments in the interaction points. Particle colliders can be used to observe rare physics phenomena or unstable particles that decay quickly.

### CERN

*CERN* (for *Conseil Européen pour la Recherche Nucléaire*, or *European Council for Nuclear Research*) is a European High Energy Physics research facility founded in 1964. The organization is located in the French/Swiss border region near Geneva, Switzerland. Currently CERN has 21 member states and more international collaborators.

The research at CERN concentrates on subatomic particles and includes topics such as testing predictions of the Standard Model of particle physics, supersymmetry, dark matter and others.

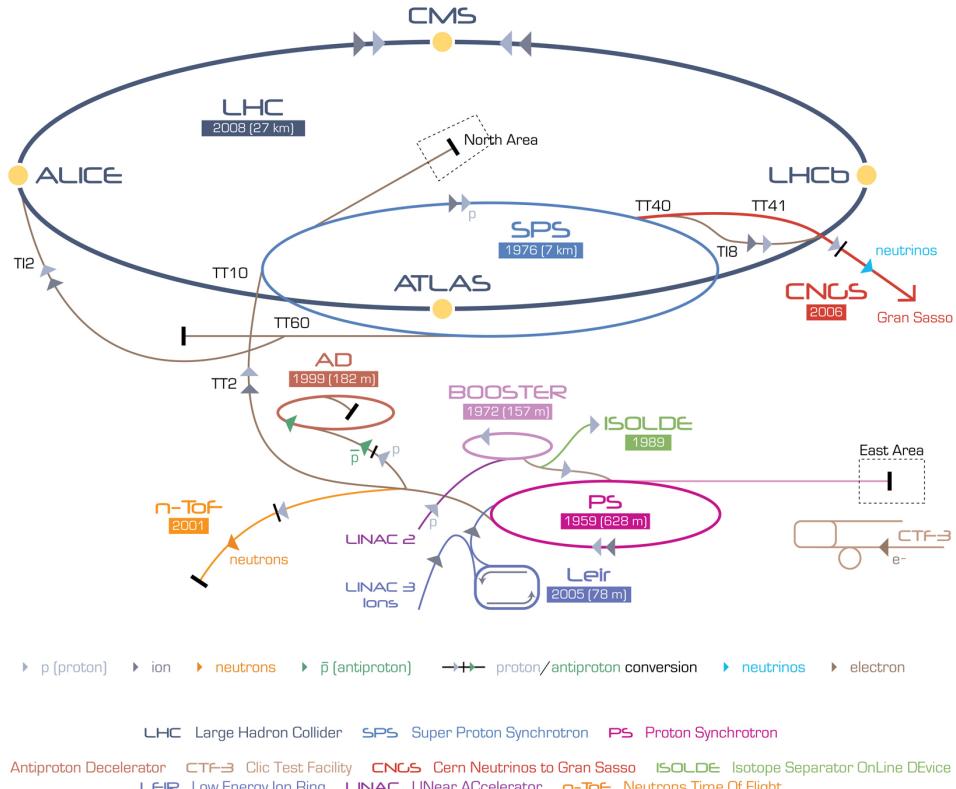

CERN is the home of many different experiments in High Energy Physics, many of which are based on various particle colliders. There are several linear accelerators (LINAC2, LINAC3, LINAC4), an antiproton decelerator to study antimatter, LEIR (Low Energy Ion Ring), the Proton Synchrotron and others. Most well known is the Large Hadron Collider (LHC), the world's biggest particle collider.

### The Large Hadron Collider

The *Large Hadron Collider* (LHC) is a circular collider with a circumference of 27 km. It was constructed in the tunnel of the Large Electron-Positron Collider (LEP), an older collider that was the predecessor of the LHC. The tunnel is below ground, at an average depth of ca. 100 m. Two particle beams consisting of protons or lead ions are circulated in opposite directions in two vacuum tubes. The beams are bent using strong superconducting magnets. The LHC consists of 1232 dipole magnets, each 15 m in length, and 392 quadrupole magnets, each 5-7 m in length. To achieve superconductivity, the magnets are cooled down to -273.1 °C using liquid helium. The beams cross at four points along the LHC circumference. The four LHC experiments ALICE, ATLAS, CMS, and LHCb are the collision points, where beam particles collide at high energies. The experiments use various detector technologies to measure the outcome of these collisions.

Figure 1.1: The accelerator complex at CERN. Particle beams pass through several accelerators before entering the LHC ring where they are accelerated to their final velocity. The LHC experiments ALICE, ATLAS, CMS, and LHCb are situated at four collision points along the circumference of the LHC. Image source: CERN.

Particles are accelerated to velocities close to the speed of light in several smaller accelerators before entering the LHC ring, see Figure 1.1. In the final beam, particles circulate the vacuum tubes in *bunches* of  $1.15 \times 10^{11}$  particles. An interaction of bunches in the counter-rotating beams in the collision points is called a *bunch crossing*. An important metric is the *bunch crossing rate* (*BCR*), the amount of bunch crossings in each collision point per unit of time. The LHC operates at a bunch crossing rate of 40 MHz. Although the number of particles in a bunch is high, only around 20 particles will collide in a bunch crossing at the nominal mode of operation as of 2016.

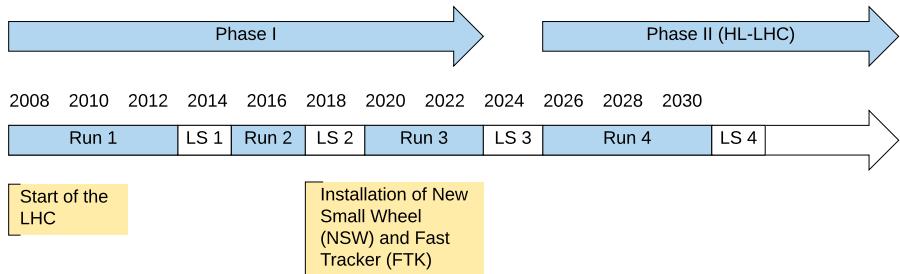

The LHC and the four experiments are upgraded at irregular intervals, typically around every 3 years. The first upgrade took place in the so-called Long Shutdown 1 from 2013 to 2015; the next upgrade phase (Long Shutdown 2) is a planned 18-month period beginning in 2018. The upgrade projects aim to improve performance and reliability.

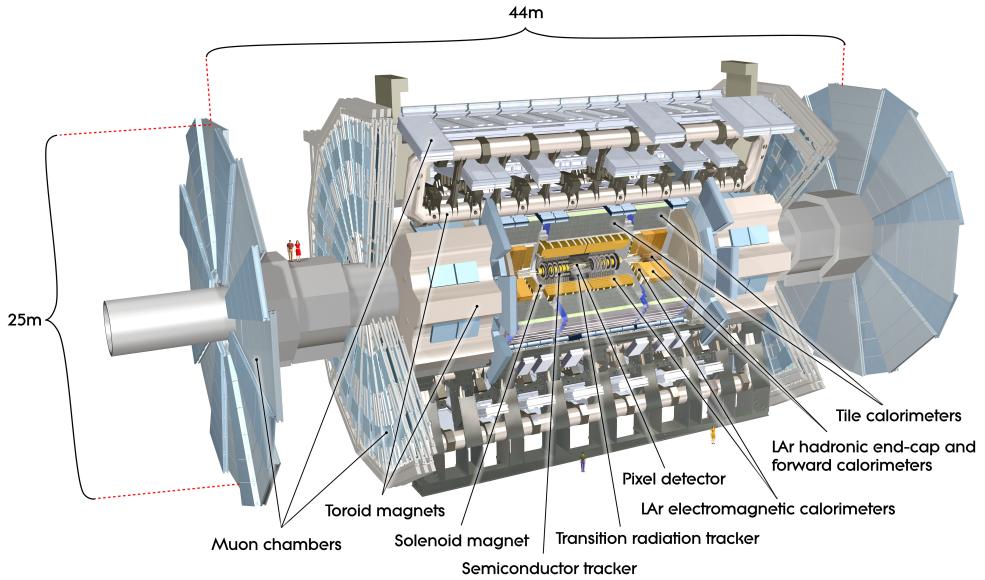

Figure 1.2: The ATLAS experiment. The two magnet systems are used to bend the trajectories of charged particles. The other systems are detectors that measure various properties of passing particles. Image source: ATLAS experiment.

### The ATLAS Experiment

ATLAS [1] is, together with CMS, one of the two general-purpose particle physics experiments at the LHC. ATLAS is an international collaboration of more than 5000 scientists from institutions all around the world. As a general-purpose experiment, ATLAS has the goal to explore a wide range of particle physics phenomena. Specific goals include the test of predictions of the Standard Model of particle physics, the exploration of matter/antimatter asymmetry, or the exploration theories beyond the Standard Model.

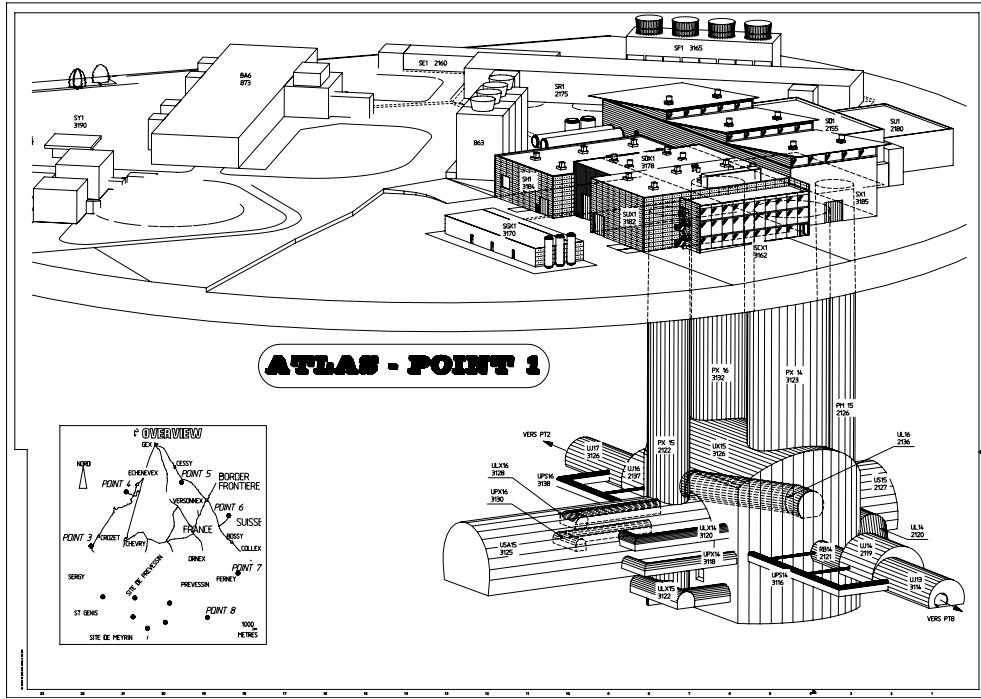

The ATLAS experiment has a cylindrical design, see Figure 1.2. It is 44 m long, 25 m in diameter and weighs about 7000 t. The experiment is situated in a cavern approximately 100 m below ground. Next to the experiment cavern is a service cavern used for cooling systems, detector control and readout or maintenance purposes. An above-surface datacenter processes data generated by the experiment. A schematic of the experiment layout is shown in Figure 1.3. There are many environmental factors posing a challenge for data taking. Electronics in the detector and service cavern are exposed to radiation and magnetic fields and space is limited.

Different detectors measure properties of the particles that are created by the collision in the center of ATLAS. The properties that are measured are

Figure 1.3: The ATLAS experiment cavern is situated approximately 100 m below ground level. A neighboring service cavern (USA15) contains detector readout components and parts of the ATLAS data-acquisition system, but also systems for cooling and machine control. The rest of the data acquisition system is situated in a datacenter above surface (SDX). Image source: [4].

the particle's trajectory, momentum, and total energy. A magnet system generates two overlapping magnetic fields that bend the trajectory of charged particles. Energy is measured by different Calorimeter systems. Charge and mass of the particles can be reconstructed from the other properties. Muons, which barely interact with matter, are detected by a special Muon spectrometer.

### 1.3 Trigger and Data Acquisition Systems

An experiment like ATLAS generates a large amount of data. In each bunch crossing, particles from the counter-rotating beams interact and might produce new particles or radiation as outcome of the collisions. The sum of all interactions in a bunch crossing and their outcomes is referred to as an *event*.

**Definition 1.1** (Event). *The sum of all outcomes of all interactions between particles in a bunch crossing as measured and recorded by detector electronics is called an event.*

In ATLAS, an event typically contains an average of 1.5–2 MB of data from all detectors. At a bunch crossing rate of 40 MHz the ATLAS experiment therefore generates more than 60 TB of data each second, a data rate that is challenging to record with modern storage systems. The vast majority of events represent well-known physical processes, so by filtering only interesting events the data rate can be reduced significantly. Such an event filtering system is called *trigger*.

**Definition 1.2** (Trigger). *A system that receives a stream of events as input and generates an ACCEPT or REJECT decision for each event is called a trigger.*

Triggers can be implemented in hardware, software, or a mixture of both. Multiple levels of triggers can be used with different implementations or strategies. A trigger can accept or reject an event based on the number of particles, type of particles, energy or momentum of particles, or other characteristics of an event.

The system that receives data from the detector sources and records an event stream on permanent storage is called *data acquisition system*.

**Definition 1.3** (Data Acquisition System). *A data acquisition system (DAQ) collects event data from detectors, receives trigger decisions from a trigger, and records accepted events on permanent storage.*

The systems in the detectors that interface with the DAQ are called *detector front-ends*. The main task of a DAQ system is to collect and relate data from different sources to events and finally write the event stream to a permanent storage. Often DAQ system also include entities to monitor the quality of measured data, data compression, or other relevant tasks.

## Computer Engineering Challenges of DAQ systems

DAQ systems need to meet the requirements of the respective experiment. These can include, among others, the following:

**High Data Rates** In order to maximize the efficiency of the experiment and the number of recorded events, events are generated at a high rate. The front-end electronics, trigger, and DAQ system need to be able to handle an event stream at a high rate. The trigger is used to reduce the output event rate to a manageable value.

**High Availability** Due to the cost of operation and maintenance, many experiments are run for long periods of time without a pause in data-taking. Stops in data-taking due to faulty components in a DAQ system can be costly, and maintenance can be complicated due to environmental factors like high radiation in the vicinity of the experiment. DAQ systems have to be designed for high availability.

**High Throughput** High resolution readout of experiments at a large event rate requires the DAQ system to handle a large data throughput. This can pose a challenge to communication links and interconnects that require a high bandwidth.

**Low Latency or Fixed Latency** A new event in the ATLAS experiment is generated every 25 ns. Low-level readout electronics in a DAQ system need to operate at a low or even fixed latency in order to process information at this rate. Cable lengths and processing times of components need to be considered, and part of the components will typically need to have real-time capabilities.

**Heterogeneity of Systems, Workloads and Requirements** A DAQ system involves many different components with different purposes and characteristics. Some detectors might generate more data than others so that work is unevenly distributed. A calibration run will have different requirements than a data-taking run. Some systems like detector control are critical for operation while other systems are redundant or can be deactivated temporarily.

**Radiation and Magnetic Fields** The environment has a big impact on the design of a DAQ system. Experiments like ATLAS produce radiation and strong magnetic fields and are cooled down to extreme temperatures. Electronics placed directly in the experimental cavern need to be designed to withstand these conditions.

**Underground Access** The placement below ground level complicates maintenance and restricts space, cooling, and power. This is challenging for any substantial installation of computing hardware.

**Long Distances** In ATLAS, cables connecting the service cavern that contains most of the readout components and the surface-level datacenter have to be about 150 m long. This distance is longer than typical distances in datacenters. Links that connect the various computing elements need to be able to cover such long distances.

**Storage** The filtered event stream has to be recorded and archived to a permanent storage for later analysis. The storage subsystem has to support a write speed to handle the incoming event stream and provide large enough space to store experiment data.

## 1.4 Contribution

Traditional DAQ systems are often built using many custom electronic components. The development and production of custom electronics requires

careful planning and takes great cost and effort, but the challenges like high data-rates and throughput and latency requirements could render custom electronics the only viable option for the early stages of a DAQ system.

The unique challenges of DAQ systems for high energy physics experiments and the workloads, data access patterns, and performance requirements that differ in many aspects from classical high-performance computing scenarios, present an interesting area of study for computer science. In this thesis I explore the use of COTS components and computer science methods and principles for DAQ systems. Specifically, I contribute the following developments:

- An analysis of the current ATLAS DAQ system and outline points where a new DAQ system based on COTS components can improve data taking.

- As part of the ATLAS/TDAQ FELIX developer team I introduce a new DAQ system for the ATLAS experiment based on the FELIX project that maximizes the use of PC components and software over custom electronics. The new system in the DAQ chain based on computer engineering principles enables a more scalable, fault-tolerant and uniform system design. My personal contribution to the project is the development of many software components of the FELIX project.

- I show computer science methods and techniques to develop software components that meet the performance requirements of a DAQ system like ATLAS.

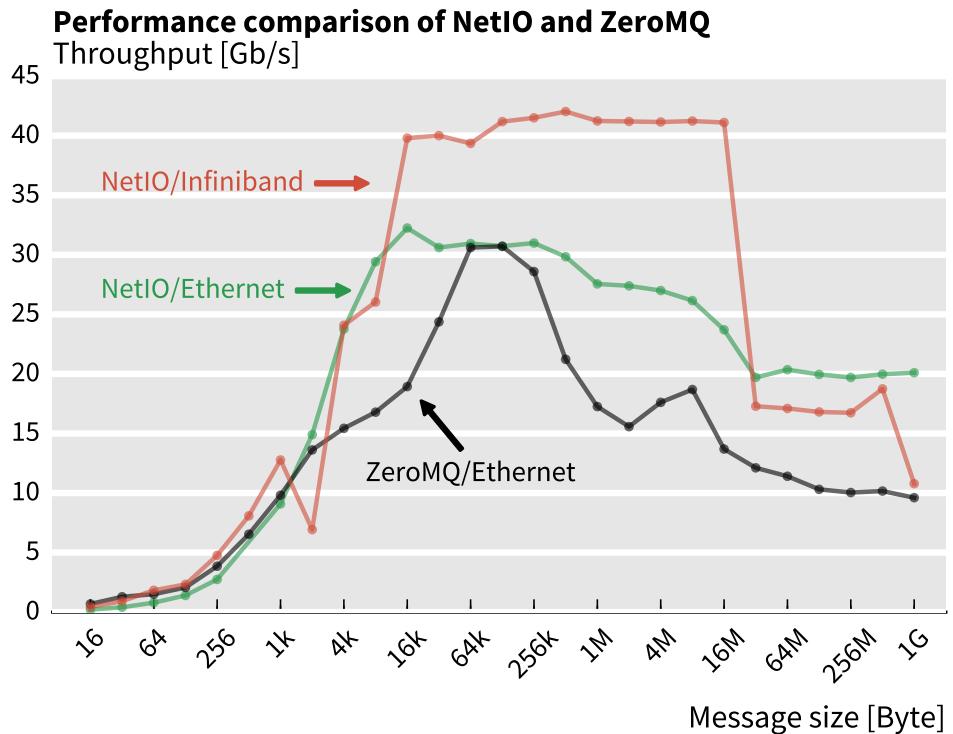

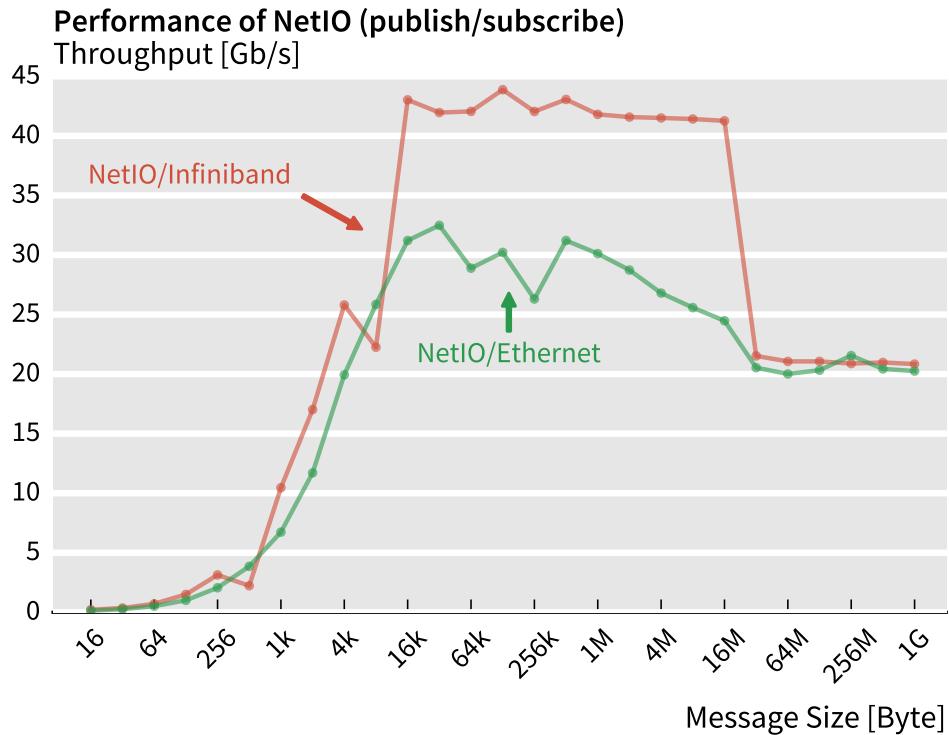

- I present NetIO, a general purpose network communication service that provides users with implementations for high-level communication patterns on top of high-performance fabrics. NetIO supports different HPC interconnects like Infiniband natively. It is used in FELIX and tuned for the foreseen workloads of the project, but the library is designed to be of general purpose and can be used outside the scope of ATLAS.

- Using a prototype of the FELIX system I evaluate and discuss the future ATLAS DAQ system with respect to the computational challenges presented in Section 1.3.

The FELIX project is a joint development effort that involves tens of developers from various institutes. I contributed the initial software stack for the FELIX project. Among other things I implemented the low-level tools to operate the FELIX PCIe I/O card, the main FELIX data processing application, code for processing data packets at a high rate with minimal latency and the FELIX network I/O stack (the NetIO library). Furthermore I contributed to

the hardware selection of the FELIX PC platform. The FELIX project also delivers a custom PCIe board to connect to the ATLAS detector electronics and firmware for the FPGA on this board that manages low-level communication with detectors and the host PC. I did not participate in the development of the PCIe card and its firmware.

I published several results of my research as scientific papers and also contributed as co-author to other papers in the context of the ATLAS DAQ system:

- Jörn Schumacher et al., “*FELIX: a High-Throughput Network Approach for Interfacing to Front End Electronics for ATLAS Upgrades*” [Schumacher et al., 2015a]. Presented in April 2015 at the 21st International Conference for Computing in High-Energy Physics (CHEP 2015) in Okinawa, Japan.

- Jörn Schumacher et al., “*Improving packet processing performance in the ATLAS FELIX project*” [Schumacher et al., 2015b]. Presented in June 2015 at the 9th ACM International Conference on Distributed Event-Based Systems (DEBS 2015) in Oslo, Norway.

- Jörn Schumacher et al., “*High-Throughput Network Communication with NetIO*” [Schumacher et al., 2016]. Presented in October 2016 at the 22nd International Conference for Computing in High-Energy Physics (CHEP 2016) in San Francisco, USA.

- Andrea Borga et al., “*Evolution of the ReadOut System of the ATLAS experiment*” [Borga et al., 2014]. Presented in June 2014 at the 3rd International Conference on Technology and Instrumentation in Particle Physics (TIPP 2014) in Amsterdam, The Netherlands.

- Andrea Borga et al., “*A new approach to front-end electronics interfacing in the ATLAS experiment*” [Borga et al., 2016]. Presented in September 2015 at the Topical Workshop for Electronics in Particle Physics (TWEPP 2015) in Lisbon, Portugal.

- Julia Narevicius et al., “*FELIX: The New Approach for Interfacing to Front-end Electronics for the ATLAS Experiment*” [Narevicius et al., 2016]. Presented in June 2016 at the 20th Real Time Conference (RT 2016) in Lisbon, Portugal.

- Kai Chen et al., “*FELIX: a PCIe based high-throughput approach for interfacing front-end and trigger electronics in the ATLAS Upgrade framework*” [Chen et al., 2016]. Presented in September 2016 at the Topical Workshop for Electronics in Particle Physics (TWEPP 2015) in Karlsruhe, Germany.

## 1.5 Outline

The rest of this thesis is organized as follows. Chapter 2 gives an overview of the evolution of the ATLAS DAQ system and introduces a new DAQ architecture based on the FELIX project for the upcoming ATLAS upgrades. The implementation of the FELIX system and its hardware, firmware and software components is discussed in Chapter 3. Chapter 4 describes how data in FELIX are encoded and transmitted over the PCIe bus and how the data can be efficiently decoded software. In Chapter 5 the network communication service NetIO is introduced and its implementation is discussed. Comparative performance measurements are given. Chapter 6 presents system benchmarks of a FELIX prototype in realistic scenarios. Concluding remarks are given in Chapter 7.

## Chapter 2

# From Custom to COTS Components: Evolution of the ATLAS Data-Acquisition System

### 2.1 LHC Upgrade Program

The LHC and its experiments consist of many different subsystems that are constantly maintained and upgraded. The upgrades have the aim of improving the LHC performance, for example collision energy and intensity. As a consequence, experiments have to be upgraded to cope with the new conditions. This includes not only the detectors themselves, but also the data acquisition systems, which are presented with an increased and more challenging workload in terms both of event processing rate and complexity. Upgrades are therefore computer engineering challenges with new requirements for computing, networking and storage. The upgrade periods also present an opportunity for redesigning DAQ architectures or deploying new components, and can be seen as a convenient break from data taking for research and development of computing and processing infrastructures.

The LHC is planned to be operated for decades and thus the upgrades are planned a long time in advance. 3- to 4-year run phases are typically followed by 1- to 2-year shutdown phases during which systems can be upgraded or replaced.

The LHC schedule is shown in Figure 2.1. LHC Run 2 is scheduled to continue until the end of 2018, followed by a second long shutdown phase (LS2) of two years. In 2021 the LHC is scheduled to restart and run continuously until 2023. The period from 2015 to 2023 (Run 2 and 3) are referred to as LHC Phase I. With these upgrades the LHC is planned to exceed its peak design luminosity, an operational parameter indicating the intensity of

Figure 2.1: A timeline for operation and maintenance periods of the LHC. The beginning of Phase II marks a major upgrade to the collider.

the collisions, in Run 3. ATLAS will be upgraded during the long shutdown phases. Major upgrades in LS2 are the installation of a new muon detector, the New Small Wheel (NSW) [5], and a new low-level trigger component, the Fast Tracker (FTK) [6].

Phase I is followed by a third long shutdown phase (LS3) which marks the beginning of Phase II. The LHC will be subject of a major overhaul with the goal of increasing its design luminosity by a factor of 10. LHC Run 4 is scheduled from 2026 to 2030, followed by a one-year long shutdown phase (LS4) in 2031. Run 5 is planned to start in 2032.

## 2.2 LHC Run 1 (2009 – 2013)

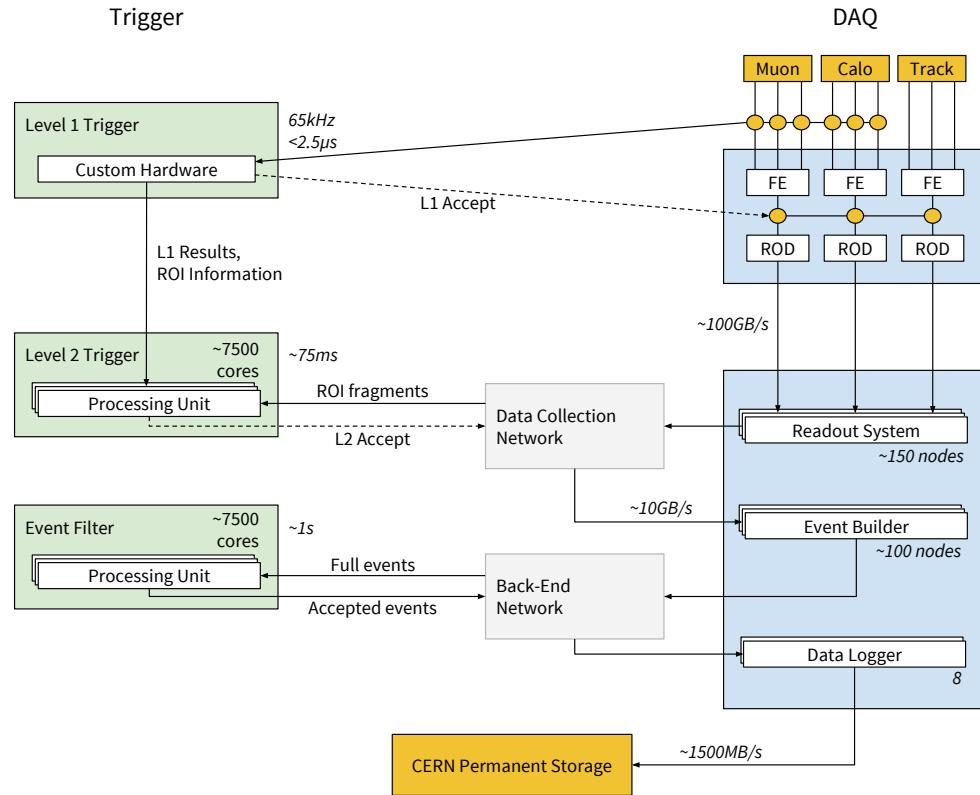

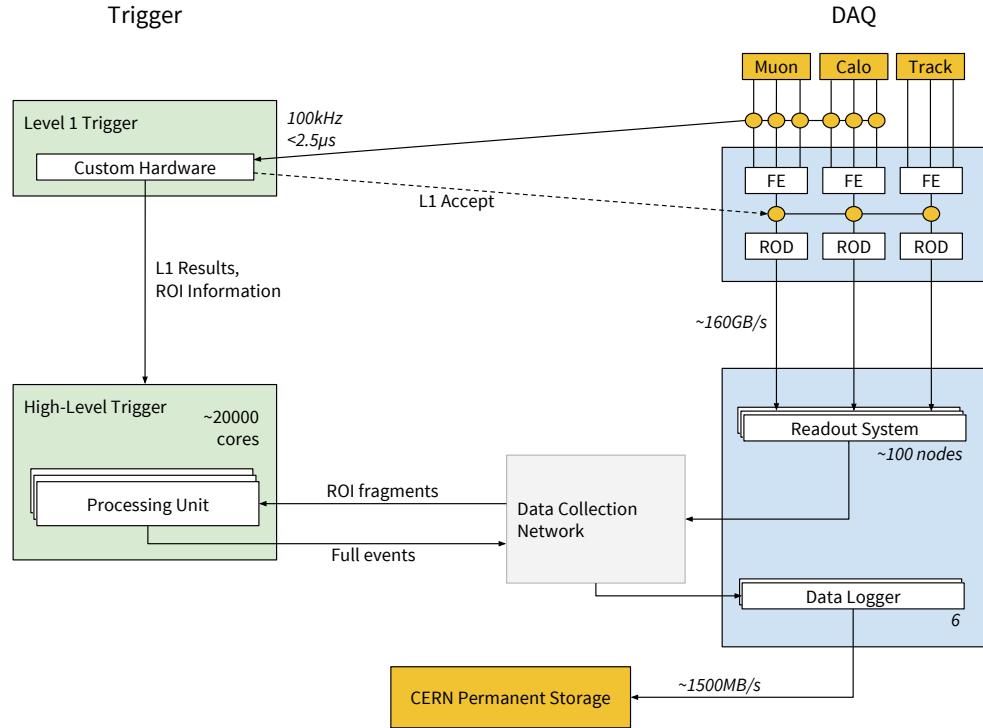

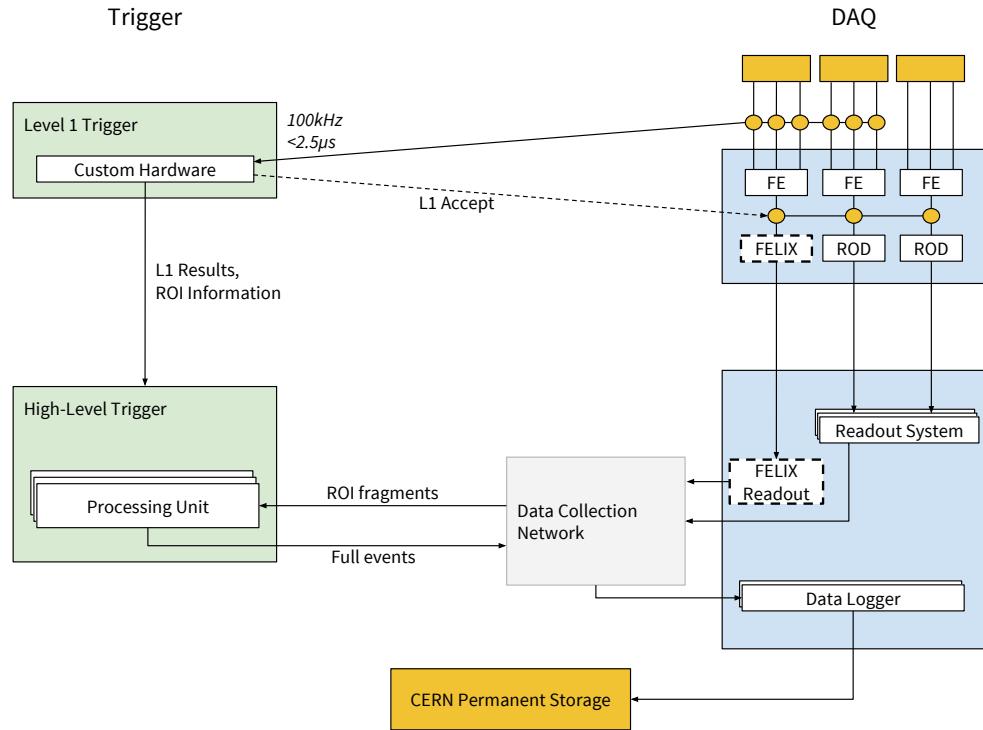

In this section I present an overview of the ATLAS trigger and data-acquisition system during the first LHC run from 2009 to 2013. The descriptions are based on the publication [7]. The ATLAS trigger and data-acquisition system consisted and still consists of many individual hardware and software components which are operated full-time during data taking. A schematic overview of the system is depicted in Figure 2.2. The peak collision energy reached during run 1 was 8 TeV.

The overall architecture of the system involves three layers of triggers: the L1 trigger, the L2 trigger and the event filter. While the L1 trigger is built purely from custom-designed electronic components, the L2 trigger and event filter are based on server PCs. Data fragments of events accepted by the L1 trigger are buffered in a layer of server PCs called the Read-Out System (ROS) until the L2 trigger and event filter decisions are made. Finally, accepted events are sent to a set of storage servers where they are recorded on disk. The individual components will be discussed in more detail in the sections below.

Figure 2.2: The ATLAS TDAQ system during LHC Run 1. The trigger part is on the left, data acquisition on the right.

## Detector Readout

The first layer of the ATLAS data acquisition system consisted of the Read-Out Drivers (RODs). These are detector-specific systems receiving data from the various ATLAS detectors. They performed data manipulation tasks like compression, reformatting as well as data aggregation. The ATLAS front-end electronics and RODs communicated over custom, non-uniform and detector-specific optical links. The RODs were typically implemented as rack-mounted VMEbus [8] modules. VMEbus is a widespread bus used in high energy physics.

The RODs also received ACCEPT signals for accepted events from the first ATLAS trigger level via the TTC system (see below for descriptions of the trigger and TTC). Accepted events were forwarded to the 151 ROS PCs. The ROS system buffered event fragments and forwarded them on request to the higher-level data processors. RODs and ROS PCs were connected via optical point-to-point links running the S-Link [10] protocol, the so-called ReadOut Links (ROL). Each ROL was operated at a data rate of either 160 or 200 MB/s.

Figure 2.3: The ROBIN card. Image source: [9]

The ROS PCs were equipped with custom PCI cards called Read-Out Buffer Input (ROBIN) [11] to interface with the ROLs (Figure 2.3). Each ROBIN connected to up to three ROLs. The majority of the ROS PCs housed four ROBIN cards and thus connected up to 12 ROLs. An onboard chip for simple data processing tasks was also mounted on the ROBIN. The ROS PCs were mapped to the detectors and subdetectors of the ATLAS experiment. A ROS PC for example might have received event fragments from a few neighboring cells of the Liquid Argon calorimeter. The mapping was organized in a way that particles traversing through neighboring cells in a detector would lead to event fragments being sent to the same ROS. This minimized the number of ROS PCs storing information and therefore the number of messages being sent in the DAQ system.

### TTC

The Timing, Trigger and Control (TTC) [12] system fulfilled multiple functions. First, the system delivered an accurate clock signal synchronous to the LHC bunch crossing rate to the readout electronics of the ATLAS DAQ system (timing). Second, the system delivered the ACCEPT information of the L1 trigger to the RODs, which forwarded accepted events to the ROS system (trigger). Third, control information, like a BUSY signal that temporarily pauses the trigger, was forwarded to all trigger components using the TTC system (control).

The TTC system was implemented with optical fibres, custom electronics,

and a simple protocol where small data packets were transmitted at a 40 MHz clock rate. The TTC system had a required timing accuracy in the order of nanoseconds.

### Event Building and Data Flow

An event building system collected the event fragments from the ROS PCs and assembled the full event data structure. The application that built the full events is called SubFarm Input (SFI). The DataFlow Manager (DFM) application orchestrated the assignments to the SFIs and acted as a load balancer. The DFM also communicated *clear* commands from the High Level Trigger (see below) to the ROS system, which in turn could free old event data fragments.

### Trigger

Three trigger levels were used for ATLAS in LHC Run 1. The *Level-1 trigger* (*L1*) was a low-level trigger that had events at the bunch crossing rate of 20 MHz as input. During operation the accept rate could reach 65 kHz (but the DAQ system was designed for an L1 accept rate of up to 75 kHz). Due to limited buffering capabilities in the front-end electronics a trigger decision had to be made within a few microseconds to decide whether the acquired event needs to be preserved or discarded. The ATLAS L1 trigger had a maximum latency of  $2.5\ \mu\text{s}$ , including the delay introduced by signal transit times in cables. The system was implemented in dedicated electronic components that were situated in the service cavern close to the ATLAS experiment to minimize latency. Trigger decisions were made using information from the calorimeters and muon detectors. Track reconstruction was not possible at this stage due to the strong latency requirements. Upon an L1 accept signal data were pushed from the front-ends to the ROS systems and were buffered there.

A second low-level system, the *Region-of-Interest-Builder* (*RoIB*), computed region-of-interest information, i.e., location information about interesting features of detected signals. Together with the L1 accept signal this information was distributed to the *Level-2 trigger* (*L2*).

L2 trigger decisions were based on partial event data. The L2 trigger received the information from the RoIB and requested data from the ROS PCs corresponding to the geographical information in the region-of-interest. The L2 trigger was composed of three different types of nodes: L2 supervisor nodes (L2SV), L2 processing units (L2PU) and L2 result handlers (L2RH). The L2 supervisor nodes were equipped with PCI cards called FILAR [13] to receive the RoIB data. Events were assigned by the L2SV nodes to one of the L2PU nodes, which ran algorithms to decide on the acceptance of the event. The L2 trigger in LHC Run 1 was operated at a maximum accept rate of circa

6 kHz. The L2 decision was sent to the L2SV nodes. The L2 trigger consisted of 768 servers in the end of 2011. Events that were accepted by the L2 trigger were then built and passed to the *event filter (EF)*.

The event filter was the last trigger level in ATLAS. Its algorithms were based on full event data. The accept rate of the event filter was up to 300 Hz. The event filter consisted of two types of applications. The event filter data-flow components (EFD) buffered the full event data. The event filter processing units (EFPUs) ran the actual trigger algorithms on the event data. Each event filter node ran one EFD and multiple EFPUs. EFD and EFPUs communicated via shared memory. In total the event filter consisted of 630 servers in 2011 by the end of LHC Run 1.

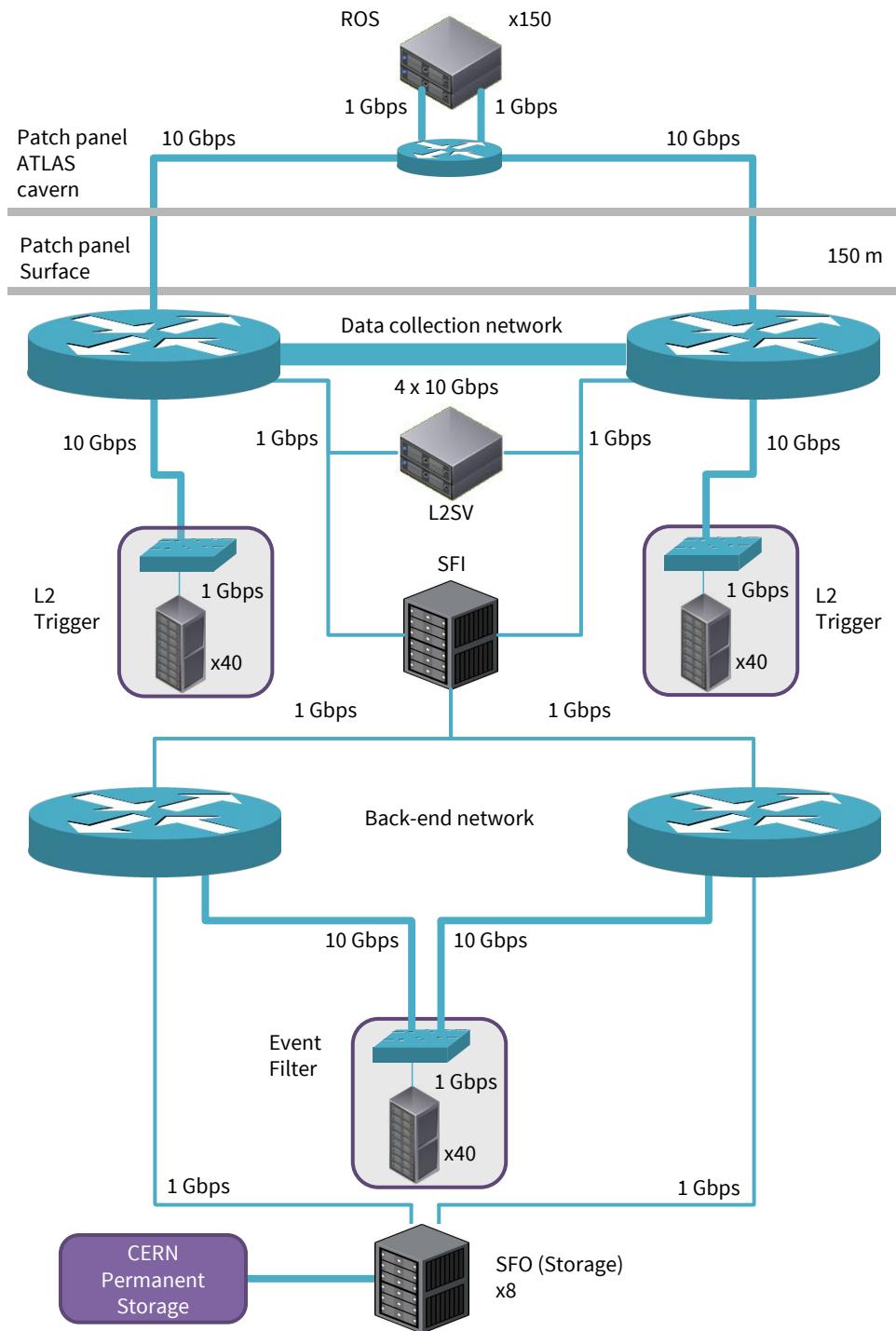

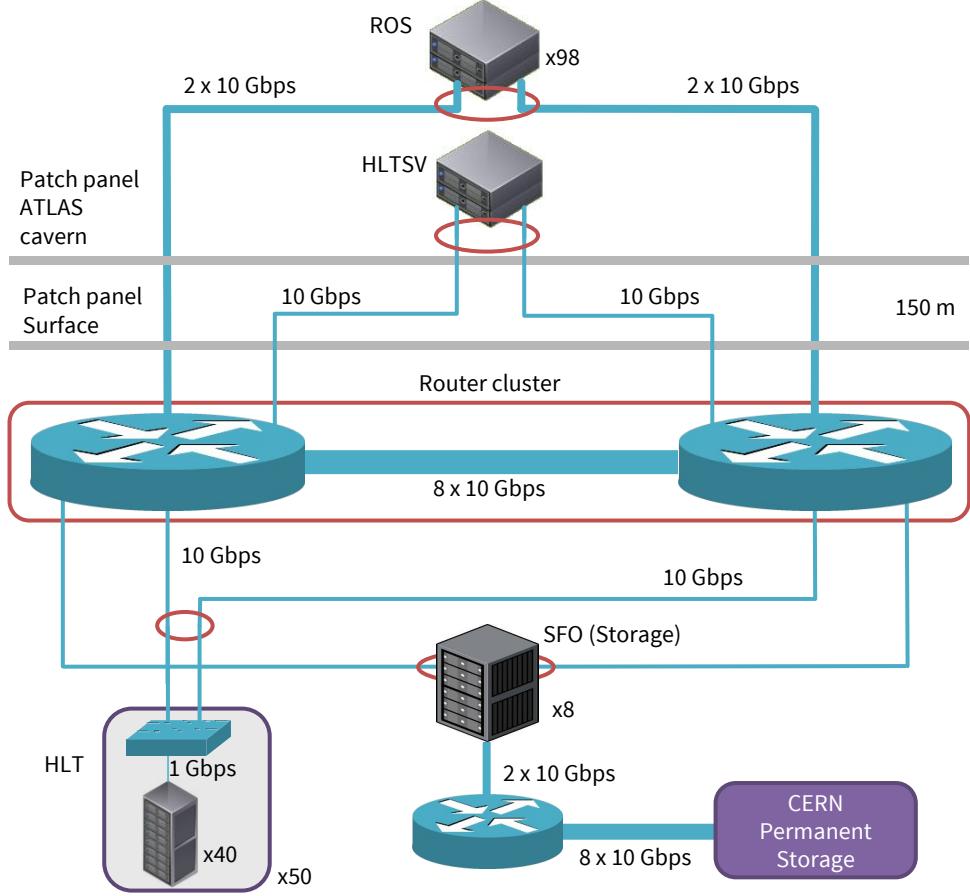

## Networks

In the ATLAS TDAQ system there were three separate networks: a control network, a data collection network, and a back-end network. The main purpose of the control network was run control and monitoring while the data collection and back-end networks were used for high-volume event data traffic. The networks are shown in Figure 2.4.

The control network was, for redundancy reasons, backed by two core routers. Each server was connected to both routers via 1GbE links, either directly or via concentrator switches. All servers in the ATLAS DAQ system were connected to the control network.

The data collection network connected the ROS PCs with the L2 trigger and event builder. It had a similar topology as the control network and was backed by two core routers. The aggregated bandwidth was however much higher. ROS PCs and L2 trigger nodes were connected to each core router via aggregator switches. Event builder nodes and L2SV nodes were connected to each core router via direct 1GbE links. The two core routers were interconnected via four 10GbE links.

The back-end network was also built using two core routers to distribute data between the event builder, event filter and storage nodes. Event builder nodes were connected using 1GbE links to each router. Storage servers and event filter processing nodes used aggration switches and 1GbE links to each core router.

## Storage

Accepted events were written to hard disk drives in a data logging farm consisting of six nodes. The application that received data from the event filter and wrote it to disk was called SubFarm Output (SFO). One SFO was running per data logging node. The event streams were only temporarily stored in the SFO nodes. A script moved the recorded data to CASTOR [14], a centralized

Figure 2.4: The ATLAS DAQ networks in Run 1. Not shown is the control network that each server is connected to.

Figure 2.5: The run control state machine.

storage facility at CERN that was designed for archiving large amounts of data.

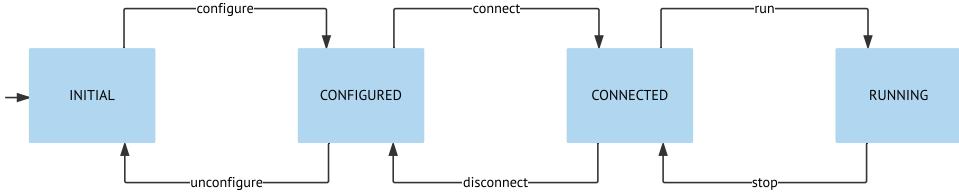

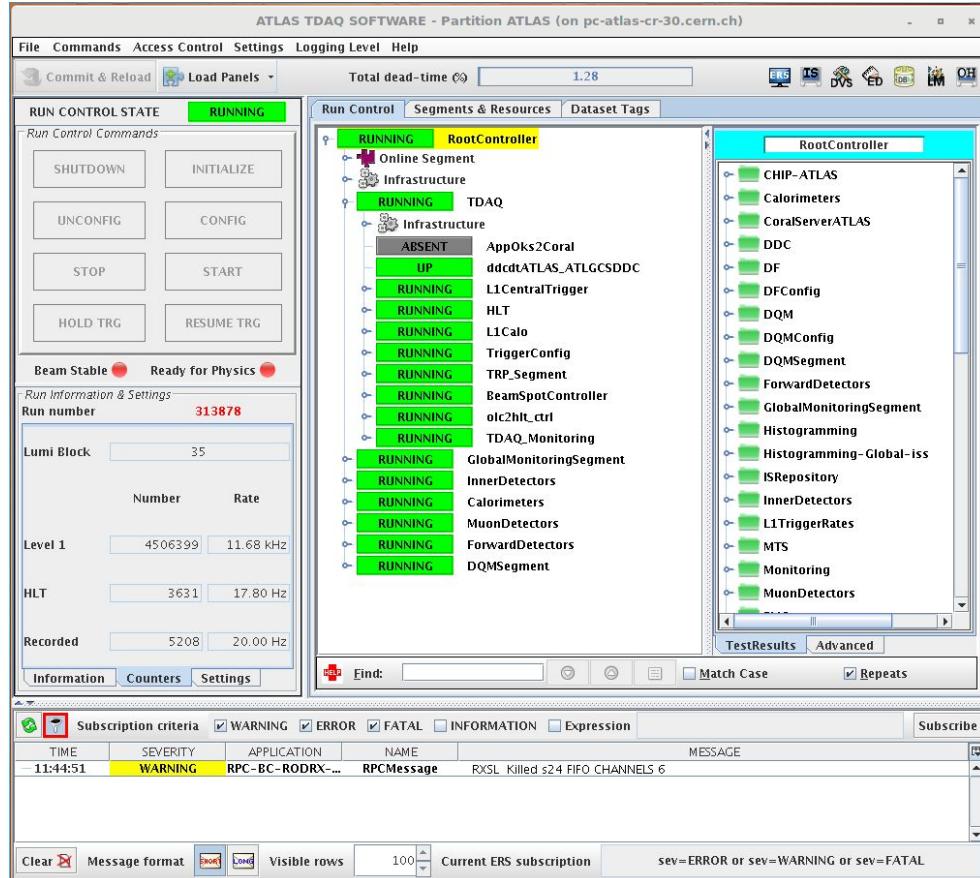

### Run Control

The complete ATLAS online computing system including data acquisition, trigger, detector control, monitoring, calibration etc. consisted of many applications operating on thousands of nodes. Together they formed a large distributed computing system that needed to be operated, configured and monitored. To manage the state of each single component, each application implemented a state machine interface. Each application could be in one of the states INITIAL, CONFIGURED, CONNECTED, or RUNNING (plus several sub-states), see Figure 2.5. Similar applications were grouped together, and each group was assigned to a controller application, which itself implemented the state machine interface. A state transition in the controller was passed to the applications that were managed by the controller. Controllers themselves could be grouped and managed by other controllers, and so a hierarchy of state machines could be formed. On the top of this hierarchy was a single controller, the root controller. By bringing the root controller to the state RUNNING the entire distributed system was brought to data taking mode. Figure 2.6 shows a screenshot of the graphical user interface that is used to operate the state of all run control applications.

To communicate state changes and other information among the applications, an interprocess communication framework was needed. In ATLAS, CORBA [15] was used for this purpose. Services and frameworks for logging, error reporting and configuration were provided to the applications and allow centralized control of the computing farm to the operator in the control room.

### 2.3 Run 1 Performance Data

During the operation of the ATLAS experiment in the first LHC run from 2009 to 2013 many operational data were gathered. These give an insight

Figure 2.6: The graphical user interface that is used by operators in the ATLAS control room.

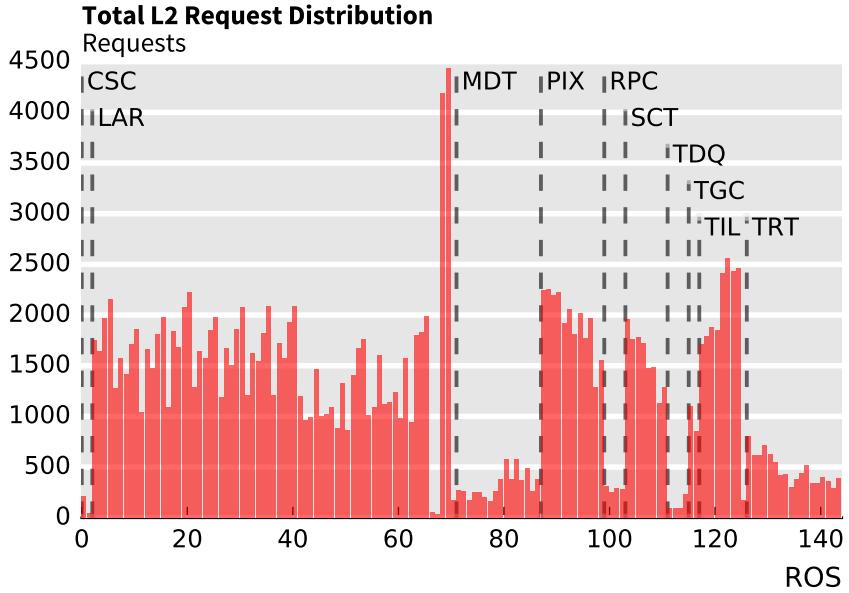

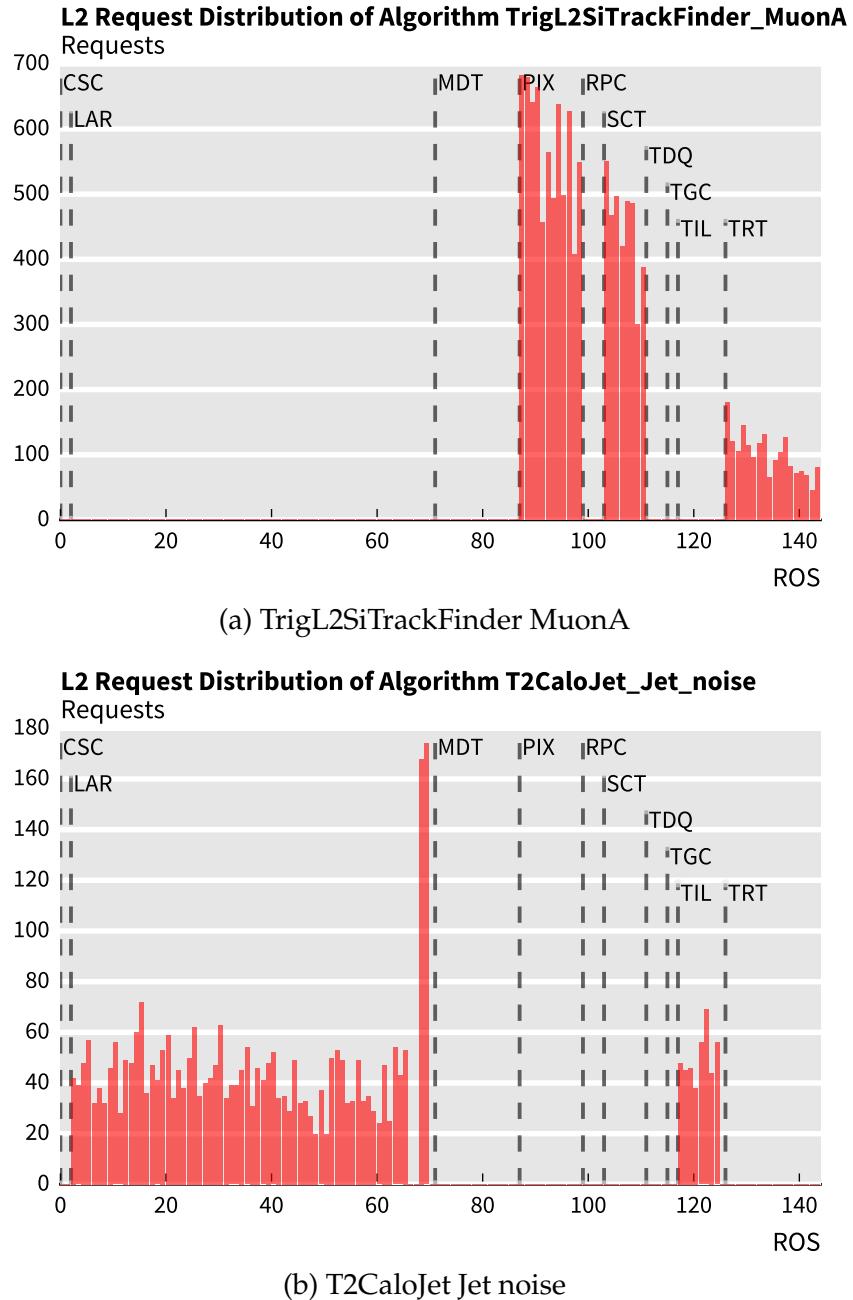

into the performance characteristics of the trigger and data acquisition system. Of particular interest here is a dataset that describes the load on the different ROS PCs generated by the L2 trigger. The distribution of requests in one specific time-interval<sup>1</sup> is shown in Figure 2.7.<sup>2</sup> Clearly the load on the ROS PCs was distributed unevenly. The reason for this becomes clear when looking at the request rate per L2 trigger algorithm. The L2 trigger system made accept or reject decision based on a few tens of algorithms. These algorithms were based on different properties of the recorded data. Figure 2.8 shows the number of requests on the ROS PCs for two L2 algorithms. The algorithm in Figure 2.8a was based on particle trajectory reconstruction and thus requested data from the Pixel, SCT and TRT ROS PCs. The algorithm in Figure 2.8b, however, was based on information from the calorimeters and

<sup>1</sup>The time-interval in which the operating conditions of a particle collider are constant is called *lumi-block*, because the collider delivers a constant luminosity in this time-interval.

<sup>2</sup>Data were recorded during run number 0209025 and lumiblock 176.

Figure 2.7: Distribution of L2 requests on the 151 ROS PCs. Data were recorded under typical run conditions.

therefore requested data from the respective calorimeter ROS PCs. Which algorithms were used and how much weight was given to their output were configuration parameters of the ATLAS trigger system.

The ROS request distribution shows not only significant differences between ROS PCs of different detectors, but also between ROS PCs of a single detector (e.g. Liquid Argon (LAr)). As a consequence the assignment of ROLs to ROS PCs had to be balanced when the operational parameters of the LHC changed and more data were transmitted on the ROLs. Since the ROS PCs were connected to the RODs via point-to-point S-Links, the Run 1 architecture did not allow dynamic load balancing. The only possibility to balance the system load was to statically reassign ROLs to ROS PCs. This required a physical intervention on the ROS PCs. This had to be done during Run 1 for example for the Pixel detector. On the other hand systems with a low load had spare resources that are not used, which decreased the efficiency of the system. It is thus desirable to strive for an even load distribution.

## 2.4 LHC Run 2 (2015 – 2018)

During the long shutdown phase in 2013/14 (Long Shutdown 1, LS1) the LHC was halted for maintenance operations. The bunch crossing rate was increased to the nominal LHC rate of 40 MHz.

Due to various factors also the average size of an event increased. This in-

Figure 2.8: Distribution of L2 requests per L2 algorithm. Shown are the request patterns of two different L2 algorithms. The algorithm in (a) uses information from the trackers, the algorithm in (b) is based on information from the calorimeters.

Figure 2.9: The ATLAS TDAQ system during LHC Run 2. L2 trigger and event filter have been merged to a single high-level trigger.

inevitably increases the performance requirements on the ATLAS DAQ system, which makes an update necessary.

At the same time also the operational requirements of the DAQ were adjusted: the L1 target rate was increased from 75 kHz to 100 kHz, the target output rate/disk storage was increased to 1 kHz. Due to installation of new detector and trigger systems the number of Read-Out Links was increased from 1600 to 1800.

Three major components of the ATLAS DAQ system were upgraded in preparation for Run 2: the ROS PCs, the L2 trigger and event filter which were merged to a single high-level trigger, and the data collection network (Figure 2.9). Minor upgrades included a replacement of the RoIB and the SFOs. The upgrades described in this section are based on [16].

## Detector Readout

Because of new performance requirements due to the increased incoming data rate as well as concerns for hardware obsolescence<sup>3</sup> the ROS system experienced a major upgrade during LS1. A new S-Link interface, the RobinNP [16], was developed. The RobinNP is a PCIe Gen-1 x8 card. Via three QSFP modules it interfaces with up to 12 S-Links. The firmware of the card was redesigned and rewritten. Major processing tasks are now performed on the host system’s CPU as opposed to the onboard chip on the ROBIN. This decision was taken with the future possibility of future CPU upgrades in mind, which would allow a cheap and easy way of increasing ROS performance should the need arise. Up to two RobinNP cards are mounted in upgraded server PCs. The new servers have a 2U height profile, as opposed to 4U in the old ROS, allowing for a much denser system.

## Trigger

One of the most significant changes in the LS1 upgrade was the redesign of the high-level trigger. In the first LHC run the high-level trigger was split into the L2 trigger and the event filter, with the event builder in between. In run 2 the L2 trigger and event filter are merged into a single high-level trigger. The new, unified trigger is executed on a single computer farm. The new design is much simpler, and also more efficient due to the removal of the communication step between the two trigger levels.

At the same time the HLT farm’s compute capabilities were also expanded by the installation of new hardware. The number of available cores was increased from about 15,000 to more than 20,000 in Run 2.<sup>4</sup>

Another trigger-specific upgrade was the already mentioned increase of the L1 rate from 75 kHz to 100 kHz.

## Networks

During LS1 the links connecting the ROS with the core routers of the data collection network were updated to from 1 GbE links to 10 GbE links. The overall architecture with two interconnected core routers as network backbone persisted. However, the routers were changed to operate in a bonding mode to form a router cluster for increased reliability and capacity. If one router fails data acquisition can continue at the same rate. Each ROS is equipped with four 10 GbE links and connected to both core routers. Each HLT rack is connected via two bonded 10 GbE links, while individual HLT servers are connected via 1 GbE links (see Figure 2.10).

---

<sup>3</sup>The ROBIN card was based on the PCI standard (predecessor to PCIe), which at the same time was slowly phased out of commercially available server hardware.

<sup>4</sup>During the course of Run 2 the farm size was further increased to a total number of 37,000 cores in 2017.

Figure 2.10: The ATLAS data collection network in Run 2. Two redundant core routers are the back-end of the network.

The back-end network became obsolete due to the merge of L2 trigger and event filter and was removed.

## 2.5 LHC Run 3 and beyond

The analysis of operational data presented in Section 2.3 made clear that the system architecture of Run 1 and Run 2 inherently leads to an unbalanced load distribution on the ROS PCs due to the static mapping of ROS PCs to detectors and sub-detectors. Moreover, a system based on static point-to-point links does not scale well. To reduce the load on a specific ROS machine and rebalance the load to a new node the ReadOut Links have to be reassigned. In case of a system failure of ROS or ROD the corresponding ReadOut Links become unavailable for recording. RODs and ROSs are therefore single points

of failure.

Quality-of-service control where one traffic type is prioritized over another can be important. For example, a detector control data stream like a critical temperature sensor has a high priority since it is essential for a safe operation of the experiment. With the point-to-point S-Links of Run 1 and Run 2, a quality-of-service control is only possible on a per-link basis. A network with multi-path switching is more flexible in this regard and can also tolerate link failure to some extent.

Many of the low-level DAQ components from the Run 1 and Run 2 architecture like the RODs are custom, purpose-built electronic devices. Development and maintenance of these components are significant cost factors in the operation of the ATLAS experiment. Shifting requirements due to the LHC upgrade programs create the need for an ongoing development effort. Since the LHC experiments are planned to be operated for many decades, the continued supply of spare parts can also pose a problem for maintenance of these systems. Software, on the other hand, is relatively cheap and easy to develop and maintain. Computer technology has thus far undergone a constant, steady evolution, as can be seen by the continued validity of Moore's Law.

In this thesis I explore the potential of DAQ systems that make use of commercial off-the-shelf (COTS) components and computers early in the DAQ chain for ATLAS and similar HEP experiments from a computer science point of view. From the above mentioned points one could derive the following key ideas for such DAQ systems, and the ATLAS DAQ system in particular:

1. Scalability, load-balancing, failure-tolerance and quality-of-service can be improved by using dynamic switched networks over static point-to-point links early in the DAQ chain

2. Development and maintenance cost and effort can be reduced by pushing the usage of COTS technology and computer engineering methodologies closer to the detector.

3. Software solutions are preferred over hardware solutions where reasonably possible.

These key concepts enable the application of insights, techniques and knowledge from computer science to aid the development of DAQ systems for high-energy physics applications.

## 2.6 Centralized Data Distribution with FELIX

FELIX, for FrontEnd LInk eXchange, is an ATLAS project that incorporates the above points with the aim to provide a central, commodity data distri-

Figure 2.11: The architecture of the ATLAS trigger and data-acquisition system as planned for LHC Run 3. The FELIX Readout components implement the functionality of both the ROD and ROS in the old system.

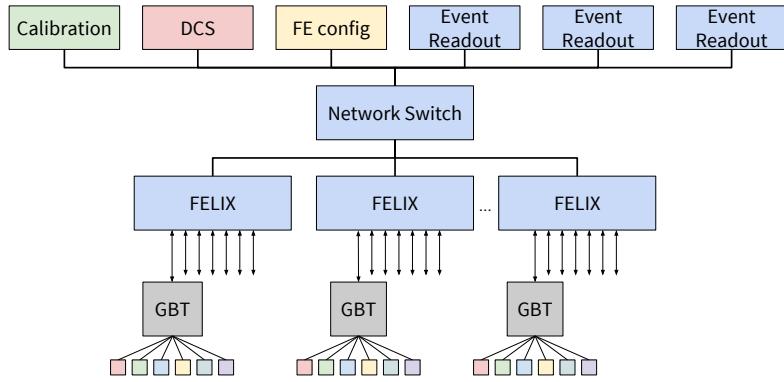

bution layer early in the DAQ chain. FELIX consists of PC-based nodes that sit between the ATLAS detector front-end electronics and the network peers implementing, most likely in software, functions previously performed in detector-specific RODs. The new FELIX-based ATLAS trigger and DAQ system is shown in Figure 2.11. The project is a joint development effort of several institutes.<sup>5</sup>

The front-ends are connected to FELIX nodes via radiation-hardened optical links (called the Versatile Link [17]), on top of which the GigaBit Transceiver (GBT) [18, 19] protocol is employed. The Versatile Link and the GBT protocol are CERN projects providing a uniform, reliable, radiation-hardened link for high-energy physics experiments. The ATLAS experiment as well as other LHC experiments are phasing out custom link protocols in favour of

<sup>5</sup>At the time of this writing the FELIX development team consists of members from Argonne National Laboratory (USA), Brookhaven National Laboratory (USA), CERN (Switzerland), NIKHEF (Netherlands), Paderborn University (Germany), Radboud University Nijmegen (Netherlands), Royal Holloway University of London (UK), University of California, Irvine (USA), and the Weizmann Institute of Science (Israel).

the Versatile Link and GBT. In the following the combination of the Versatile Link and the GBT protocol will be simply referred to as *GBT link*.

On the back-end side, FELIX nodes connect via a switched high-performance network to the ATLAS DAQ system, detector control system, as well as detector specific calibration and monitoring systems. All these systems are implemented as software application running on servers connected to the FELIX network. The RODs, which were previously implemented as dedicated electronic components, can be implemented in software and the functionality can be merged into the ROS functionality. With all traffic flowing via FELIX systems there is now one single way for DAQ and auxiliary systems to communicate with detector front-end electronics.

FELIX will also interface with the existing TTC system as described earlier. FELIX receives TTC streams and can distribute the information downstream to detector front-end electronics, as well as upstream to the DAQ and other systems. TTC data that are sent downstream via the GBT links are forwarded with a fixed, low-latency delay to ensure accurate timing.

## 2.7 Related Work

The original ATLAS trigger and data acquisition system that was in use during the first LHC run from 2009 until 2013 is described in [7], its evolution to the system that is currently used in the second LHC run (from 2015 until 2018) is described in [20]. The Data Collection software framework used in ATLAS TDAQ is presented in [21], which is one of the first examples of common communication and message passing frameworks in ATLAS.

The LHCb project currently uses a combination of a low-level trigger and a high level trigger, similar to the ATLAS DAQ architecture in Run 2. The plan for the 2018 upgrade is to completely remove the low-level trigger and therefore read out the detector at the bunch crossing rate of 40 MHz. The foreseen detector readout system is based on GBT links and custom electronic component using the ATCA standard. As an alternative, a proposal for PCIe-based readout is also being investigated [22,23]. The system uses the PCIe40, an FPGA PCIe board developed by the LHCb collaboration. In this scenario the PCIe40 boards would be housed directly in the event builder PCs.

ALICE plans to deploy GBT links in their detectors and is developing a common interface between detector electronics, trigger and DAQ, called the CRU (Central Readout Unit) [24]. The implementation of the CRU is based on PCIe and the PCIe40 board from LHCb.

The CMS experiment upgraded their DAQ system for the current LHC Run 2. In the CMS architecture, low-level custom electronics connect to the PC-based DAQ system using a subset of the TCP/IP protocol over Ethernet links that is implemented in FPGAs [25,26].

## Chapter 3

# Architecture of a COTS-based Read-Out Switch

### 3.1 Overview

One of the core concepts that form the basis of the work presented in this thesis is the use of commercially available components for the purpose of detector readout. The FELIX project applies this principle at least in two distinct aspects.

First, the FELIX devices, based on commercial PC technology, minimize the need for custom components. Some custom hardware is unavoidable, for example detector links and TTC connections are very specific to high-energy physics and require custom developed hardware and firmware components. In FELIX connections to detectors and TTC system are implemented on a PCIe card with an on-board FPGA.

Second, FELIX functions like a switch that connects multiple endpoints (detectors and DAQ systems) and routes data between them (Figure 3.1). This characteristic of FELIX makes it easy to implement DAQ functions in software running on COTS servers as opposed to dedicated electronics, because the connection to detector front-ends that might require custom devices is already handled by FELIX. An example are the the RODs, which were typically implemented as VME modules in LHC run 1 and 2. With FELIX, the ROD functionality in Run 3 can be provided by software components running on server PC.

### 3.2 Detector Connectivity

The Versatile Link [17] is an optical link technology developed at CERN targeted at high-energy physics experiments. The nature of these experiments requires the link and electronics to be radiation-resistant. The Versatile Link is a full duplex link.

Figure 3.1: FELIX devices connect to multiple DAQ system endpoints.

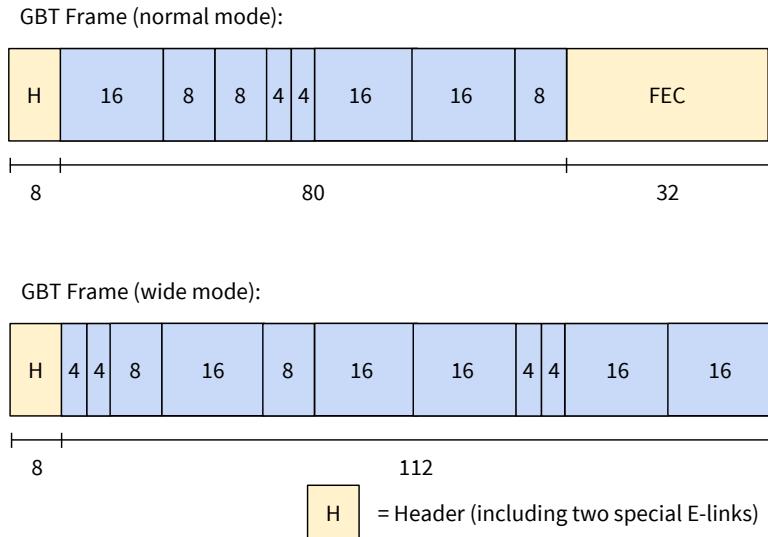

The Gigabit Transceiver (GBT) protocol [18,19] is used on top of the Versatile Link. A widely available chip, the GBTx, allows the serialization of data streams according to the GBT protocol. The GBT protocol supports a standard mode which includes forward error correction using a Reed-Solomon code, and a wide mode with increased bandwidth but without forward error correction. The protocol uses virtual lanes, so-called e-links, to handle multiple parallel streams on a single, physical link. At the bunch crossing rate of 40 MHz the GBT protocol transmits packets called GBT frames of 120 bits, of which 80 bits (standard mode) or 112 bits (wide mode) are usable for user data. An e-link can be 2, 4, 8, or 16 bit wide, meaning that 2, 4, 8, or 16 bits of a GBT frame are utilized. A single GBT link can contain between 5 and 40 e-links in standard mode, or between 7 and 56 e-links in wide mode. In addition two special 2 bit e-links are part of the GBT frame headers. These are used as channels for the detector control system and for configuration of the GBTx chip itself. E-links have a net bandwidth of 80, 160, 320, or 640 Mbps. An illustration of the GBT protocol is shown in Figure 3.2.

The FELIX project decided to make two additions to the pure GBT protocol. The first addition is the definition of a packet encoding protocol on top of the standard e-link information. E-links are stream-based as opposed to packet-oriented protocols and therefore packet boundaries would be lost without an additional encoding. FELIX supports an 8B/10B encoding as well as an High-Level Data Link Control (HDLC) encoding. Packet boundaries are transmitted as out-of-band characters in the respective encodings.

The second addition is a third operation mode next to the standard and wide GBT modes. The third mode does not support e-links, but instead uses an 8B/10B encoding to carry a single packet stream on the link. This mode provides more bandwidth and is thus more efficient than the other modes, but sacrifices forward error correction and e-links. This third mode is referred to as full mode, and is intended for applications not requiring radiation-hard

Figure 3.2: Illustration of the GBT Frames in normal and wide mode. The 80 bit or 112 bit payload field is divided in 2, 4, 8, or 16 bit E-links.

links. An example of this would be trigger electronics that are hosted in the ATLAS service cavern, and thus not in a radiation area.

### 3.3 The Detector Link Interface Card: Hardware, Firmware and Low-Level Software Tools

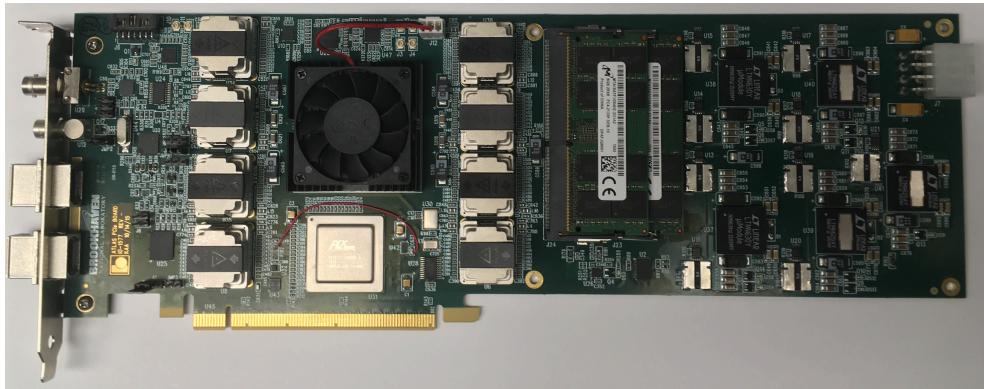

The PCIe card in the FELIX PC that connects to the detector links is simply called the FLX card. It is currently available in three versions (also see Table 3.1):

**FLX-709** This card is based on the Xilinx VC-709 [27] development kit. The card hosts a Xilinx Virtex-7 VX690T FPGA and has four cages for SFP+ transceivers. It connects the host PC via a PCIe Gen-3 x8 interface. The FLX-709 only supports up to four GBT links, but the hardware is commercially available and relatively inexpensive, which makes it a good board for development and test setups.

**FLX-710** The FLX-710 is based on the HiTech Global HTG-710 [28] PCIe board with the Xilinx Virtex-7 X690T FPGA. The card has two CXP sockets to connect two 12-channel full-duplex CXP transceivers. It can therefore support up to 24 GBT links. The board also has a PCIe Gen-3 x8 interface. The FLX-710 was the initial development board used by the FELIX project.

|                | FLX-709                | FLX-710               | FLX-711                   |

|----------------|------------------------|-----------------------|---------------------------|

| Board          | Xilinx VC-709          | HiTech Global HTG-710 | Custom                    |

| FPGA           | Xilinx Virtex-7 XV690T | Xilinx Virtex-7 X690T | Xilinx Ultrascale XCKU115 |

| PCIe Interface | Gen-3 x8               | Gen-3 x8              | Gen-3 x16                 |

| Links          | 4                      | 24                    | 48                        |

| TTC            | via TTCfx FMC          | via TTCfx FMC         | onboard connector         |

Table 3.1: Specifications of the three generations of FLX cards.

Figure 3.3: Hardware prototype of the FLX-711 card.

**FLX-711** The FLX-711 (Figure 3.3) is based on a custom PCIe board that was originally designed for use in the LAr detector community.<sup>1</sup> The FLX-711 has a Xilinx Kintex Ultrascale XCKU115 FPGA, a PCIe Gen-3 x16 interface and supports up to 48 optical links in full-duplex. The FLX-711 is a candidate for the final card that will be used in the Run 3 FELIX installation.

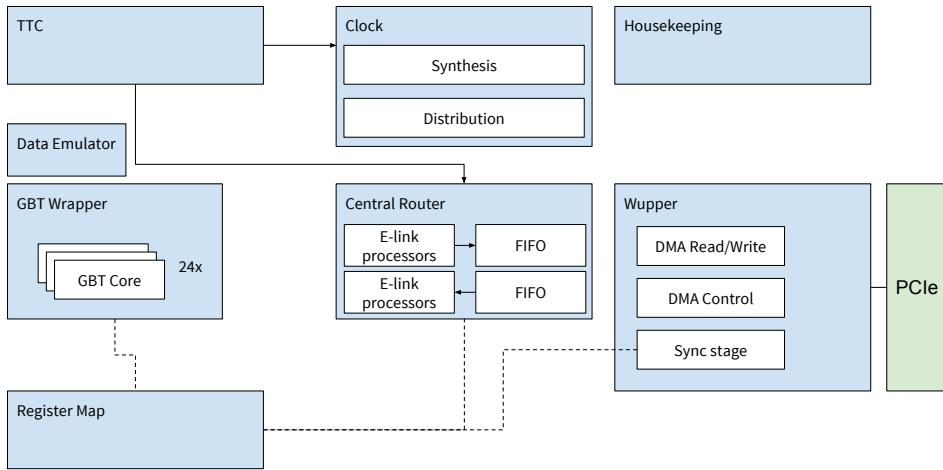

Multiple FLX cards can be installed in a FELIX PC to increase link density. The firmware in the FLX card's FPGA contains the logic to interface between detector links and the host PC. The firmware can be divided into six major components (see Figure 3.4): a) the GBT interface, b) the Central Router, which handles data forwarding from and to e-links, c) a DMA engine and interface to the PCIe bus called *Wupper*, d) configuration and register map, e) TTC interface and f) a housekeeping module to configure and control clock resources and other peripherals on the FLX card.

<sup>1</sup>The original use of the card is for testing the Liquid Argon Trigger Digitizer Board (LTDB) which is a sub-system of the ATLAS L1 trigger.

Figure 3.4: Block diagram of the FLX card firmware.

### The GBT Interface

The GBT interface is a wrapper around an HDL softcore provided from the CERN GBT team. It manages the encoding and decoding of GBT frames (in the case of standard and wide mode) and the operation of the optical transceivers.

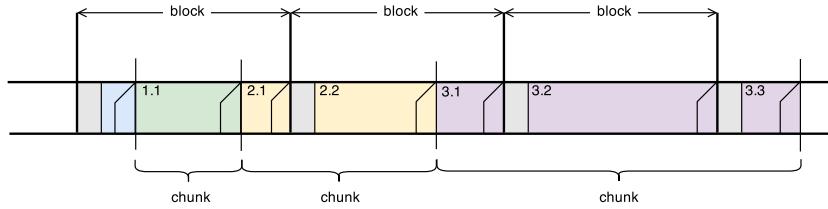

### The Central Router

The Central Router encodes and decodes the packet stream on top of the GBT streams, and encodes and decodes blocks that are transmitted over the PCIe bus (see chapter 4 for a description of the encoding format). Per e-link two FIFOs are maintained for transmission of data in both directions, from the GBT links and to the GBT links. For performance reasons the Central Router will encode the variable-length packets coming from the detector links into one or multiple fixed-size 1 kB blocks. These blocks are then transferred via the PCIe bus. The Central Router also forwards TTC information to the GBT links.

### DMA Engine and Interface to the PCIe Bus

As part of the development of the FLX card firmware a DMA engine called Wupper [29] for the PCIe Gen-3 hard block of the Xilinx Virtex-7 FPGA was developed. Wupper allows eight DMA transfers in parallel and a maximum transfer rate of 64 Gb/s. MSI-X is supported for the handling of interrupts.

Wupper supports two modes of operation: a single-transfer mode, and a continuous-transfer mode. In single-transfer mode a software application

will request the DMA engine to perform a single transfer of data into a buffer in the host system memory. Once the transfer is complete, the DMA engine channel is free to be programmed with further DMA operations.

In the continuous mode on the other hand the Wupper engine treats the destination memory region of the transfer as a circular buffer and maintains a read- and write-pointer. Data can be fed continuously to the DMA engine by the FPGA logic. Wupper will write the incoming data to the destination buffer and update the write-pointer. User software can read the data from the buffer and will subsequently update the read-pointer. When the write-pointer reaches the read-pointer, Wupper will pause the transfer until the read-pointer is advanced. When the end of the buffer is reached, a wrap-around occurs and reading or writing continues at the beginning of the buffer. The continuous mode is useful to continuously transfer data to the host system without the need of reprogramming the DMA engine for every block of data, thus making the usage of the PCIe bus more efficient.

### Configuration and Register Map

The FLX card parameters are controlled via a central register map. The register map has to be synchronized with software tools. To ease development a Python script is used to generate a VHDL register map as well as C source-code from a central register description file.

### The TTC System: Trigger, Timing and Control

A connection to the TTC system is physically established via a FPGA mezzanine card (FLX-709, FLX-710) or via a dedicated on-board optical connector (FLX-711). The 40 MHz TTC clock is cleaned and extracted in the FPGA and is used to operate the optical transceivers for the detector links at a synchronized clock. Furthermore the TTC information is forwarded to the detector front-ends and host system via the Central Router.

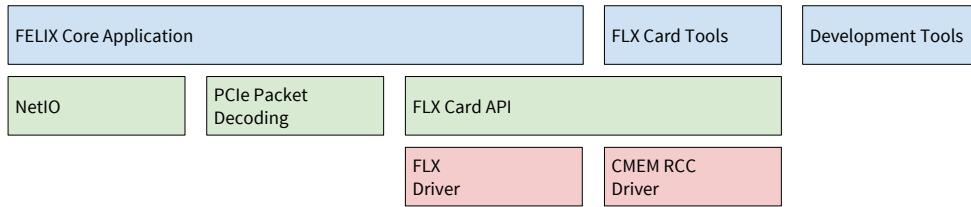

## 3.4 The FELIX Software Stack

The FELIX software stack (Figure 3.5) runs on top of a RedHat-based Linux operating system (Scientific Linux). The software reads and writes data from and to the detector links, manages network connections to DAQ nodes, and encodes and decodes data packets. The software stack consists of a main server component to route data traffic between detectors and DAQ, various support libraries, and command-line tools for operation, monitoring and diagnostics. FELIX connects to a high performance network via a standard PCIe network interface card on the same host PC.

Figure 3.5: The FELIX software stack.

## Drivers

Two kernel device driver modules are used to operate an FLX card. The first driver, which is simply called *flx*, maps memory regions assigned by the Linux kernel to the FLX card to the user address space. The memory regions are PCIe memory spaces that contain the FLX card's register map. Via ioctl operations a user application can request the driver to map the configuration register space of the FLX card to its own address space. Via direct manipulation of the mapped memory region the user application can configure and operate the card, start or stop DMA operations, or read status information. Furthermore, slow data transfer operations between the host system and the FLX card can be implemented by software writing to specific memory addresses which are read out by the FPGA firmware on the card. Giving user space applications direct access to the PCIe address space of the FLX card is more light-weight than encapsulating the accesses in the driver. The direct access method avoids context switches each time a register of the FLX card is accessed. However, this approach is only suitable for slow data transfers. Use cases requiring a higher throughput should use DMA transfers instead.

The *flx* driver is also responsible for handling MSI-X interrupts issued by the FLX card. Interrupts can be used to signal DMA transfer completions, full or empty FIFOs or other important events such as error conditions. The *flx* driver manages the handling of interrupts and notifies user space programs of the events. For debugging and diagnostic purposes the *flx* driver outputs basic operational data to the `/proc/flx` file in the proc file system.

The second driver in the FELIX software is *cmem\_rcc*, which stands for contiguous memory (the appendix *rcc* is for historic reasons). To use the continuous mode of the Wupper DMA engine efficiently it is necessary to provide a large, contiguous block of system memory as a destination. On modern PC architectures memory is virtualized for user space applications, but devices on the PCIe bus typically operate with physical memory addresses.<sup>2</sup>

<sup>2</sup>There are architectures which use a IOMMU (input-output memory management unit) to provide virtual addresses also for peripheral devices. An example is Intel VT-d. However, not all modern CPUs include an IOMMU, and in order to maximize freedom in the choice of hardware for FELIX it is beneficial to opt for contiguous physical memory allocations over an IOMMU.

Thus, the normal memory allocation functionalities provided by the Linux kernel are not sufficient. The cmem driver closes this gap and allows the allocation of large regions of contiguous physical memory via ioctl system calls.<sup>3</sup>

## Low-Level Tools

Several low-level tools with a command-line interface are available to configure and operate the FLX cards. The tools are listed in Table 3.2. The toolset is used by developers, testers and end users to test and debug the FLX card. The functionality of the tools is mostly implemented in a shared library `libflxcard`, which is also used by the FELIX core application (see below).

## Core Application

The FELIX core application is the central process of a FELIX system. The application has the following functions:

1. Packet forwarding from the front-ends to the DAQ system: read and decode data packets from the FLX card and forward the packets to network endpoints based on dynamic routing rules.

2. Packet forwarding from the DAQ system to the front-ends: receive messages from network endpoints and write the contained packets to the e-links that are supplied in the message header.

3. Configure the FLX card, e-link configuration and operational parameters based on input from a configuration file.

4. Recover from a network endpoint failure. This could mean that data are temporarily routed to another endpoint, or that data transfers are resumed seamlessly after recovery of the network endpoint.

5. Gather statistics and performance metrics.

6. Report operational status information like the status of the detector links and warn in case of a hardware failure.

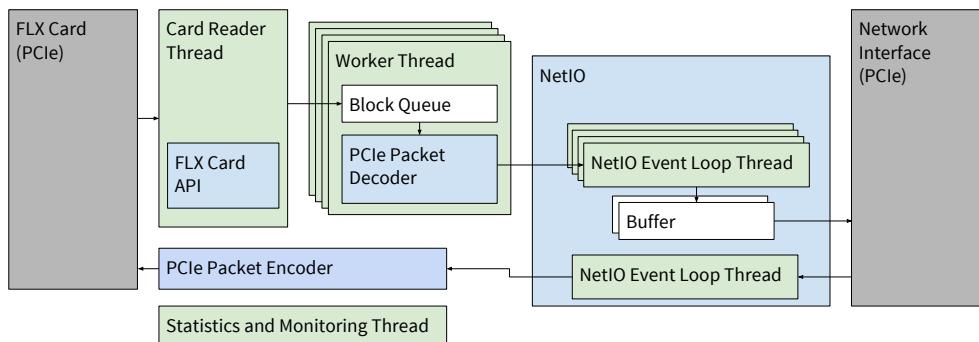

Figure 3.6 shows a diagram of the architecture of the FELIX core application. In the case of a system with multiple FLX cards, one application is run per card.

---

<sup>3</sup>In Linux kernel v3.5 the Contiguous Memory Allocator (CMA) was added, which provides similar functionality as the cmem driver. Since the Linux distribution Scientific Linux 6, which is very commonly used in high-energy physics, is still based on kernel series 2.6, the FELIX project uses cmem over CMA.

| Name            | Description                                                                                                                                                |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FlxCard_scope   | An interactive debugging tool.                                                                                                                             |

| flx-config      | Access to configuration options of the FLX card and the raw register map.                                                                                  |

| flx-dma-stat    | Displays the status of the Wupper DMA engine.                                                                                                              |

| flx-dma-test    | Tests the functionality of the Wupper DMA engine.                                                                                                          |

| flx-dump-blocks | Reads raw data from the card via DMA transfers and dumps the data into a file. Data come from GBT links or the internal FLX data generator.                |

| flx-i2c         | Reads from or writes to I <sup>2</sup> C-connected devices on the FLX board.                                                                               |

| flx-info        | Displays generic information about the FLX cards, connected transceivers, link status or connected sensors.                                                |

| flx-init        | Initial configuration and clock setup. This program has to be executed once before data can be read from the card.                                         |

| flx-irq-test    | Tests the functionality of the MSI-X interrupts.                                                                                                           |

| flx-reset       | Resets the card or specific parts of the firmware to the initial state.                                                                                    |

| flx-spi         | Similar to flx-i2c, this tool is used to communicate with devices connected via the SPI bus.                                                               |

| flx-throughput  | A throughput benchmark to measure the transfer speed of the Wupper DMA engine.                                                                             |

| fdaq            | Read and decode GBT data from an FLX card and record the decoded data stream to a file. This application can be used as a standalone DAQ system for tests. |

| fupload         | Transmit user-supplied data via GBT links.                                                                                                                 |

Table 3.2: The low-level command line tools for the FLX card.

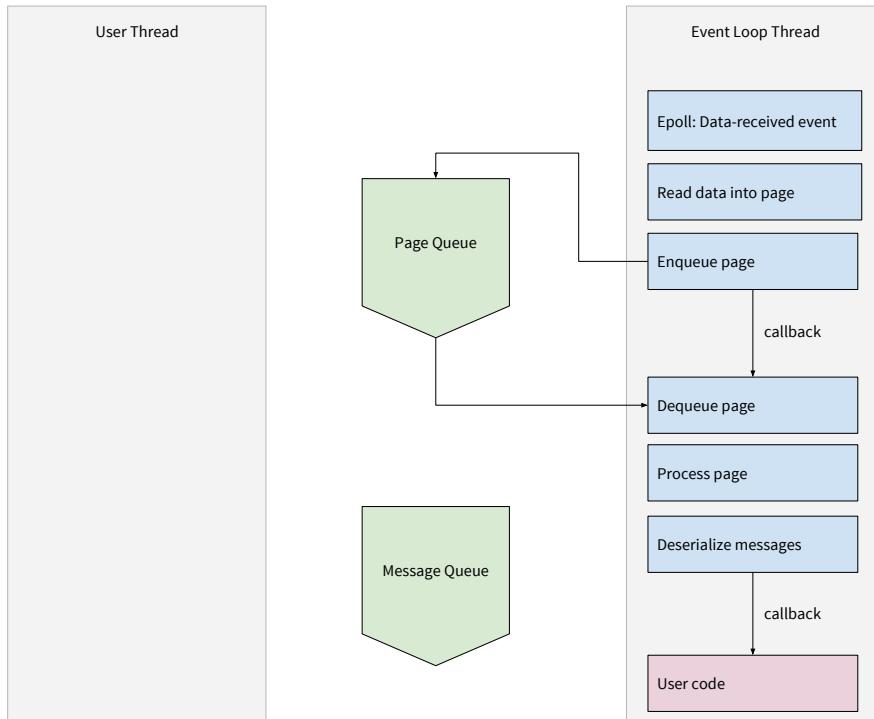

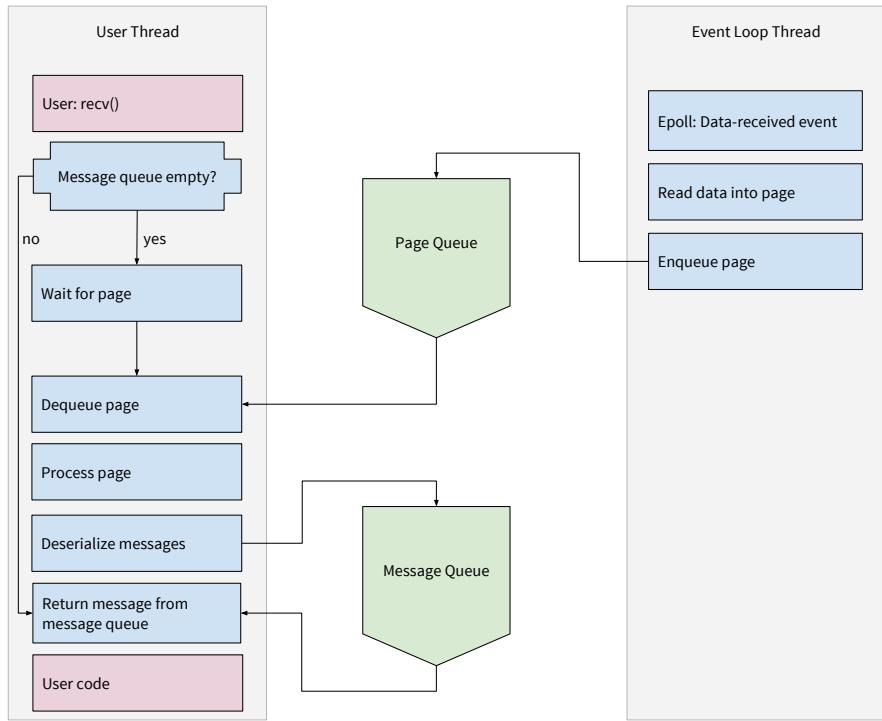

### Front-End to DAQ Path

A single thread is responsible for reading data from the FLX card. As mentioned before, data that are transferred from the FLX card are encoded in fixed-size 1 kB blocks. The thread reading from the FLX card assigns these blocks in a round-robin fashion to one of multiple block queues. For each block queue a worker thread is started which reads the blocks from the assigned block queue and processes the blocks. Within the worker thread the

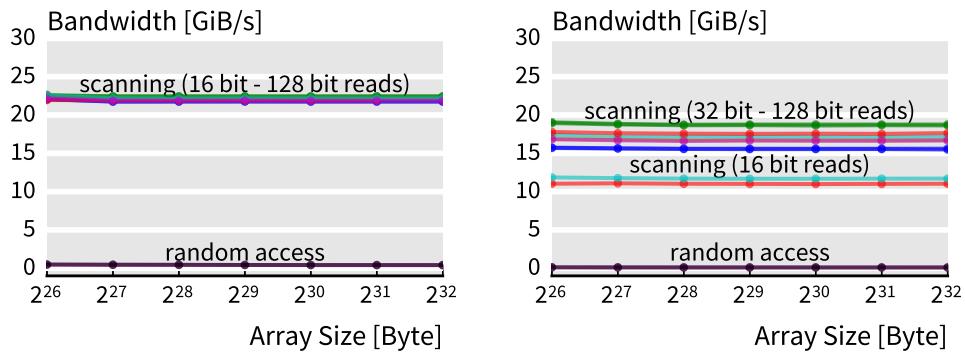

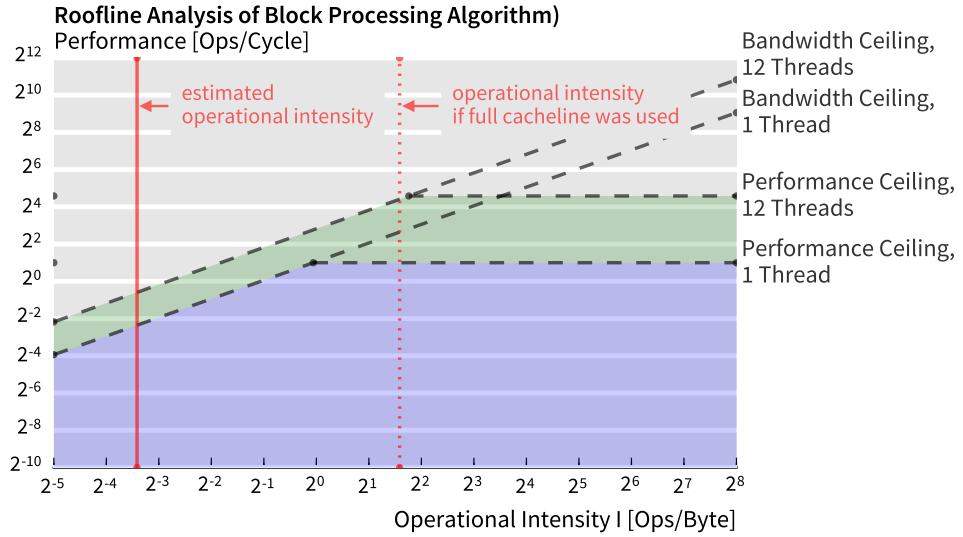

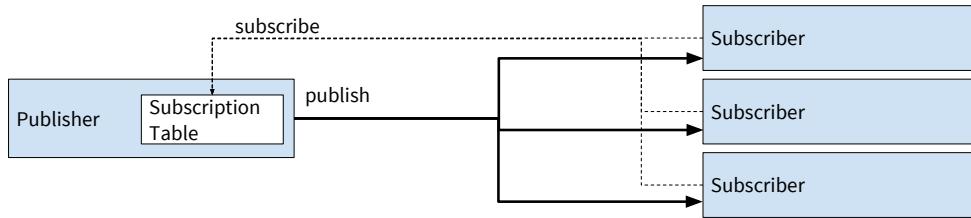

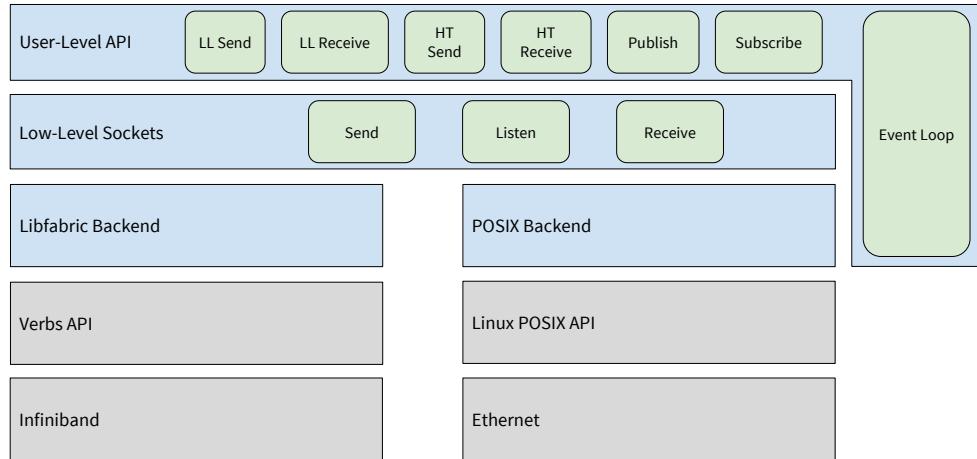

blocks will run through a pipeline with the following steps: