# **Half-Cycle-Sampled Discrete Model of Series-Parallel Resonant Converter with Optimized Modulation and its Control Design**

Von der Fakultät für Elektrotechnik, Informatik und Mathematik

der Universität Paderborn

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften (Dr.-Ing.)

genehmigte Dissertation

von

Junbing Tao

Erster Gutachter: Prof.Dr.-Ing. Joachim Böcker

Zweiter Gutachter: Prof.Dr.-Ing. Andreas Steimel

Tag der mündlichen Prüfung: 21.04.2015

Paderborn 2015

Diss. EIM-E/315

# Abstract

In the development of isolated DC-DC converters, series-parallel-resonant converter (SPRC) demonstrates its advantages with regard to wide operation range, high efficiency and highly dynamic performance. Compared to phase-shifted full bridge converter (PSFB), SPRC topology presents a limited utilization, because of its nonlinear gain and dynamic characteristics. The complexity of its model and further difficulties of its control design are the bottle-necks of this problem.

Due to the nonlinear characteristics of the SPRC, the primary objective of this work is to find a balanced modelling method for the SPRC between its complexity and accuracy. In the research of optimized modulation strategy (OM), it is interesting to find out the control signals in the OM modulator are sampled every half cycle of resonant oscillation with varying the switching frequency. From this point, this varying-step sampling can be applied in the modelling approach and also in the control design. This discrete system, with synchronized sampling steps in converter, modulator and controller, is called “half-cycle-sampled discrete (HSD) system”. It is proved to be the best balanced modelling approach for describing the SPRC. It efficiently utilizes the calculation resources and has sufficient accuracy for the SPRC. This HSD modelling approach takes the dynamic behaviour of the modulator into consideration.

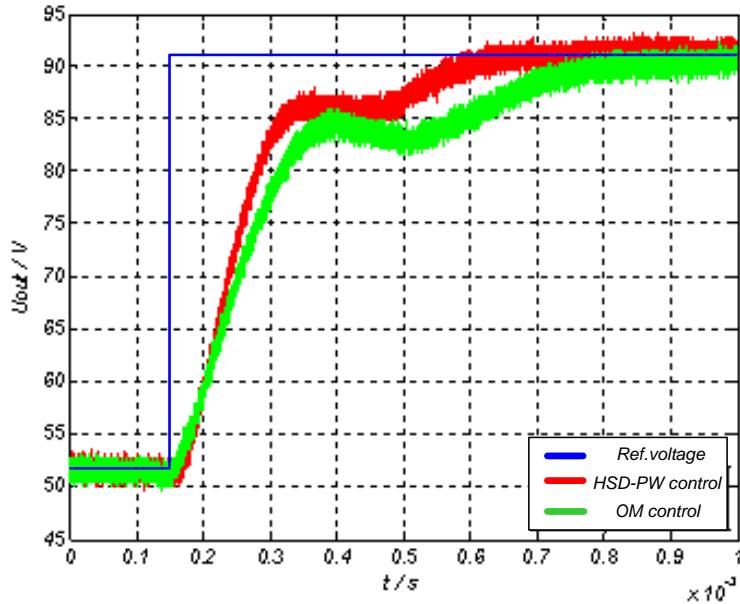

The second objective of this work is to design the appropriate controller in order to improve the dynamic performance of the SPRC. With the accurate dynamic model of the SPRC, the discrete controller with the varying sampling step is considered an optional improvement. The other improvement is to utilize the width of pulses as the control signal instead of the duty ratio. A novel control algorithm, HSD-PW control, is proposed combining these two improvements. It demonstrates that HSD-PW control clearly reduces the control settling time of output voltage in the experiment.

Subsequently, the calculation system of the entire controlled SPRC is implemented in the computer, in order to simulate the dynamic behaviour of SPRC. All the design options are added to the calculation system as the modules. The calculation system has a simple algorithm and can be performed rapidly. It is a helpful tool for computer-aided design in the future.

# Zusammenfassung

Bei der Entwicklung von isolierten DC-DC-Wandlern zeichnet sich die Topologie des Serien-Parallel-Resonanzkonverters (SPRC) durch einen breiten Betriebsbereich, einen hohen Wirkungsgrad sowie durch eine hohe Dynamik aus. Im Gegensatz zur phasenverschobenen Vollbrücke (PSFB) weist die Topologie des SPRC eine nichtlineare Charakteristik auf, weshalb diese auf dem Anwendungsfeld von Gleichstromwandlern bislang nur in eingeschränkter Weise zum Einsatz kommt. Eine aufwändige Modellierung sowie der Entwurf einer geeigneten Regelung sind die wesentlichen Herausforderungen, die der Einsatz eines Serien-Parallel-Resonanzkonverters aufgrund seiner Komplexität mit sich bringt.

Das primäre Ziel dieser Arbeit war es, eine ausgewogene Modellierungsmethode für den SPRC zu finden, die einen Kompromiss zwischen Komplexität und Genauigkeit bezüglich der nichtlinearen Charakteristik erlaubt. Bei der Erforschung von optimierten Modulationsstrategien wurde festgestellt, dass der Modulator in jeder Halbperiode der Resonanzschwingung abgetastet und die Schaltfrequenz zu diesen Zeitpunkten angepasst werden kann. Aus dieser Erkenntnis heraus erscheint es sinnvoll, das Verfahren der Abtastung mit variabler Schrittweite in die Modellierung und den Reglerentwurf mit einzubeziehen. Das zeitdiskretisierte System mit synchronisierten Abtastschritten für Konverter, Modulator und Regelung wird „Halbperioden-abgetastetes diskretes (HSD) System“ genannt. Es hat sich als ausgewogenster Modellansatz zur Beschreibung des SPRC herausgestellt. Dieser nutzt die zur Verfügung stehenden Rechenressourcen in effizienter Weise und garantiert dabei gleichzeitig eine ausreichende Genauigkeit für den SPRC.

Ein weiteres Ziel dieser Arbeit war es, den entsprechenden Regler auszulegen, um die Dynamik des SPRC zu verbessern. Mit dem akkurate, dynamischen Modell des SPRC kann auch der diskrete Regler mit variabler Abtastzeit als eine zusätzliche Verbesserung angesehen werden. Zu einer weiteren Verbesserung führte die Verwendung der Pulsbreite anstatt des Tastverhältnisses als Stellsignal. Mit einem neuartigen Regelalgorithmus, der HSD-PW-Regelung, können diese beiden Verbesserungen erzielt werden. Die HSD-PW-Regelung führte in praktischen Versuchsdurchführungen zu einer reduzierten Ausregelzeit der Ausgangsspannung.

Anschließend wurde das Modell des geregelten SPRC auf einem Rechner implementiert, um das dynamische Verhalten der SPRC zu simulieren. Zusätzliche Module, die in das Berechnungsverfahren integriert wurden, erlauben die Ausführung aller relevanten Entwurfsoptionen. Das Berechnungsverfahren selbst besteht aus einem einfachen Algorithmus, der nur relativ kurze Ausführungszeiten erfordert. Dieses Verfahren leistet in Form eines hilfreichen Werkzeugs einen wertvollen Beitrag im Bereich des Computer-aided Design.

# Notation

## Symbols

| Symbol                            | Explanation                                                           | Unity    |

|-----------------------------------|-----------------------------------------------------------------------|----------|

| $\alpha, \beta, \theta$           | Auxiliary angle values describing the waveform                        | rad      |

| $A, B, C, D$                      | Transfer system matrix of small-signal model                          |          |

| $A_d, B_d$                        | System matrix of discrete linear model                                |          |

| $A_{pw}, B_{pw}$                  | System matrixes of continuous model for pulse-width-regulated SPRC    |          |

| $A_{d,pw}, B_{d,pw}$              | System matrixes of discrete model for pulse-width-regulated SPRC      |          |

| $A, A_n$                          | The amplitude of saw-tooth signal in modulator                        |          |

| $C_f$                             | Capacitor in output filter                                            | F        |

| $C_p$                             | Parallel capacitor                                                    | F        |

| $C_s$                             | Series capacitor                                                      | F        |

| $D, D_p$                          | Duty ratio, extra duty ratio for time compensation                    |          |

| $D_{nom}$                         | Normalized duty ratio                                                 |          |

| $D_{real}$                        | Real effective duty ratio in the modulation                           |          |

| $D_1, D_2, D_3, D_4$              | Reverse parallel diodes of full bridge circuit of SPRC-LC             |          |

| $D_5, D_6, D_7, D_8$              | Rectifier diodes in secondary side of SPRC-LC                         |          |

| $E$                               | Identity matrix                                                       |          |

| $F_{uCp,a}$                       | Average coefficient of parallel-capacitor voltage                     |          |

| $F_{uCp,s}$                       | Sine coefficient of parallel-capacitor voltage                        |          |

| $F_{uCp,c}$                       | Cosine coefficient of parallel-capacitor voltage                      |          |

| $f_s$                             | Switching frequency                                                   | Hz       |

| $i_{Lf}, I_{Lf}$                  | Current through output filter inductor                                | A        |

| $i_{Ls}, I_{Ls}$                  | Current through series inductor, amplitude of series inductor current | A        |

| $\Delta i_{Ls}$                   | Unbalanced part of resonant current                                   | A        |

| $i_{out}$                         | Output current                                                        | A        |

| $i_R$                             | Rectifier current                                                     | A        |

| $K_{p,d}, K_{i,d}$                | Discrete control parameters                                           |          |

| $L_s$                             | Series inductor in resonant tank                                      | H        |

| $L_f$                             | Inductor in output filter                                             | H        |

| $P_w$                             | Pulse-width signal                                                    | s        |

| $r$                               | Current ratio, $I_{Lf}/I_{Ls}$                                        |          |

| $R_L$                             | Load resistance                                                       | $\Omega$ |

| $s, s_n$                          | Slope of saw-tooth signal in the modulator                            | 1/s      |

| $t_h, t_{h,n}$                    | length of half cycle                                                  | s        |

| $T_1, T_2, T_3, T_4$<br>( $T_n$ ) | Gate signals of transistors or the transistors                        |          |

| $U_{out}, u_{out}$                | Output voltage                                                        | V        |

| $U_{dc}, u_{dc}$                  | Input voltage, direct current (DC) voltage                            | V        |

## Notation

---

|                                      |                                                                    |          |

|--------------------------------------|--------------------------------------------------------------------|----------|

| $u_{Cs}, U_{Cs}$                     | Voltage on series capacitor, amplitude of series capacitor voltage | V        |

| $u_{Cp}$                             | Voltage on parallel capacitor                                      | V        |

| $u_{Cf}, U_{Cf}$                     | Voltage on output filter capacitor                                 | V        |

| $u_{ref}$                            | Reference of output voltage                                        | V        |

| $\omega$                             | Angular switching frequency                                        | rad/s    |

| $\mathbf{x}, \mathbf{y}, \mathbf{u}$ | State variables of linear models                                   |          |

| $Z_{ac}, Z_{equ}$                    | AC equivalent impedance of secondary side                          | $\Omega$ |

# Contents

|                                                                                       |    |

|---------------------------------------------------------------------------------------|----|

| Abstract .....                                                                        | 2  |

| Zusammenfassung.....                                                                  | 3  |

| Notation.....                                                                         | 4  |

| Symbols.....                                                                          | 4  |

| Contents .....                                                                        | 6  |

| 1     Introduction.....                                                               | 10 |

| 2     The principal idea of half-cycle sampled system.....                            | 14 |

| 2.1    Designing choices of series-parallel-resonant converter .....                  | 15 |

| 2.2    Introduction of three different modulation strategies .....                    | 17 |

| 2.3    General thoughts about half-cycle sampled discrete system .....                | 19 |

| 2.4    General method of half-cycle sampled discrete model.....                       | 23 |

| 2.5    Summary .....                                                                  | 25 |

| 3     Improved steady-state model of SPRC-LC considering the voltage distortion ..... | 27 |

| 3.1    State-of-the-art modelling techniques of SPRC-LC .....                         | 27 |

| 3.2    Major assumptions and simplification of SPRC-LC topology .....                 | 31 |

| 3.3    Extended fundamental AC analysis .....                                         | 32 |

| 3.3.1    Circuit analysis of rectifier.....                                           | 34 |

| 3.3.2    Steady-state analysis of extended fundamental AC model.....                  | 36 |

## Contents

---

|       |                                                                                |    |

|-------|--------------------------------------------------------------------------------|----|

| 3.4   | Improved steady-state analysis for SPRC-LC .....                               | 40 |

| 3.4.1 | Equivalent circuit of SPRC-LC .....                                            | 40 |

| 3.4.2 | Description of parallel capacitor voltage .....                                | 42 |

| 3.4.3 | Three coefficients and expression of improved steady state model .....         | 45 |

| 3.4.4 | Advantages of improved steady-state analysis .....                             | 48 |

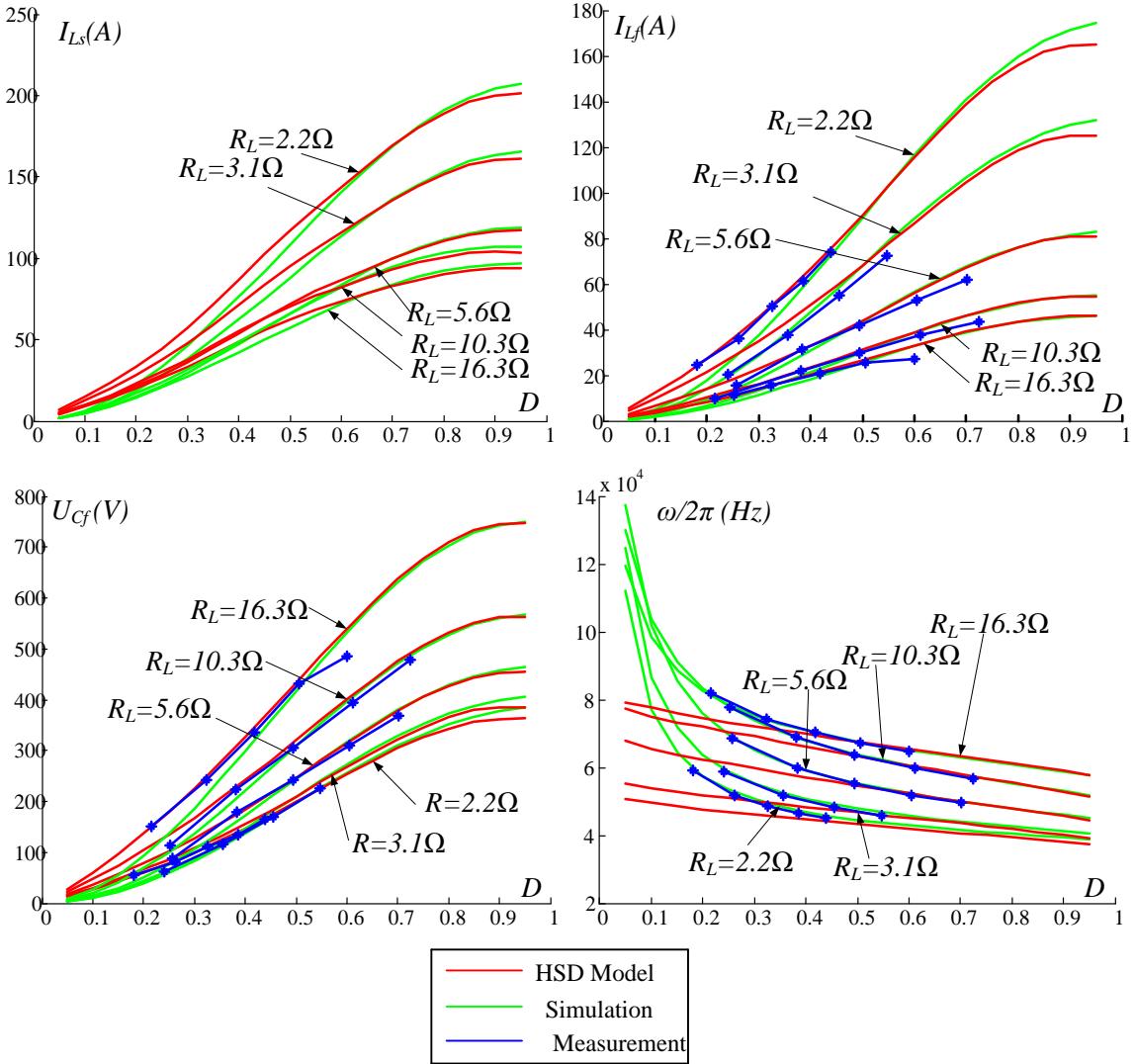

| 3.5   | Simulation and experimental verification .....                                 | 49 |

| 3.6   | Summary .....                                                                  | 50 |

| 4     | Continuous models and half-cycle-sampled discrete models of SPRC with OM ..... | 52 |

| 4.1   | Large-signal and nonlinear model .....                                         | 53 |

| 4.1.1 | Original continuous model.....                                                 | 54 |

| 4.1.2 | Major assumptions of HSD model.....                                            | 55 |

| 4.1.3 | Slowly-changing continuous model.....                                          | 58 |

| 4.2   | Small-signal and linear model .....                                            | 61 |

| 4.3   | Half-cycle-sampled discrete model.....                                         | 64 |

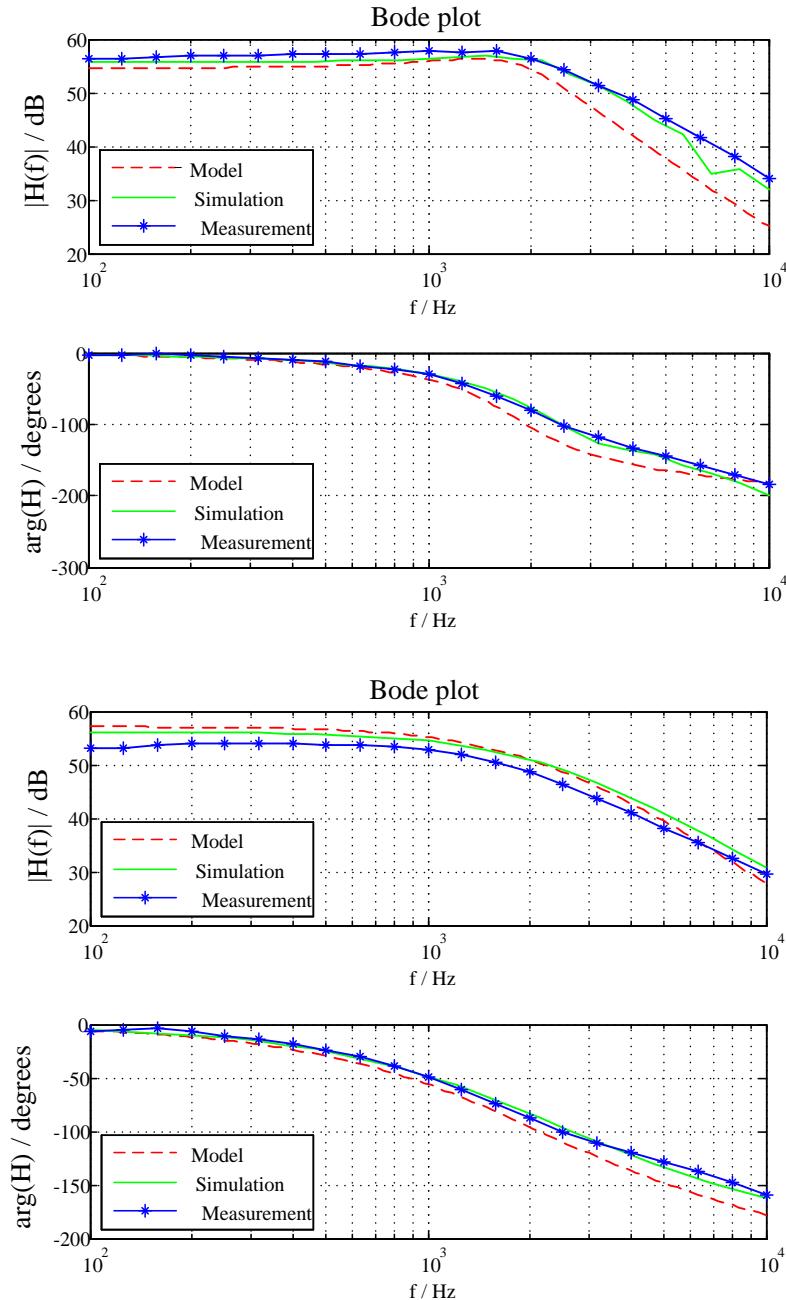

| 4.4   | Simulation and experimental verification .....                                 | 67 |

| 4.5   | Summary .....                                                                  | 72 |

| 5     | Modelling and implementations of optimized modulation strategy .....           | 74 |

| 5.1   | Optimized modulation strategies of SPRC .....                                  | 75 |

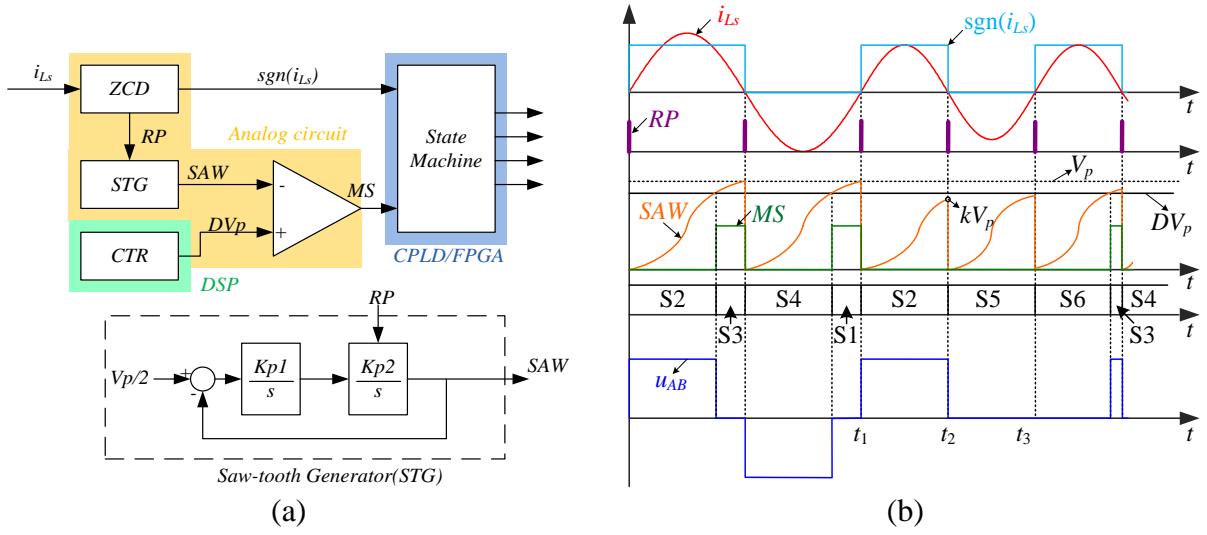

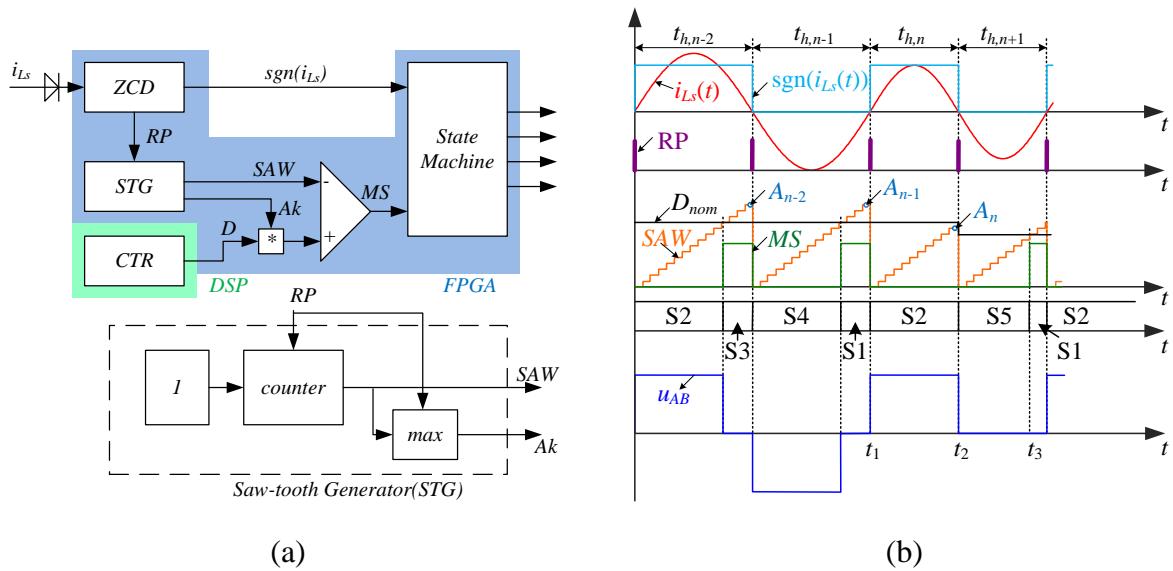

| 5.1.1 | Ideal modulator and the operation principle of optimized modulation.....       | 76 |

| 5.1.2 | Hybrid implementation of optimized modulator .....                             | 77 |

| 5.1.3 | Digital implementation of optimized modulator.....                             | 79 |

| 5.1.4 | Time compensation in digital implementation .....                              | 80 |

---

## Contents

---

|                                                                                   |     |

|-----------------------------------------------------------------------------------|-----|

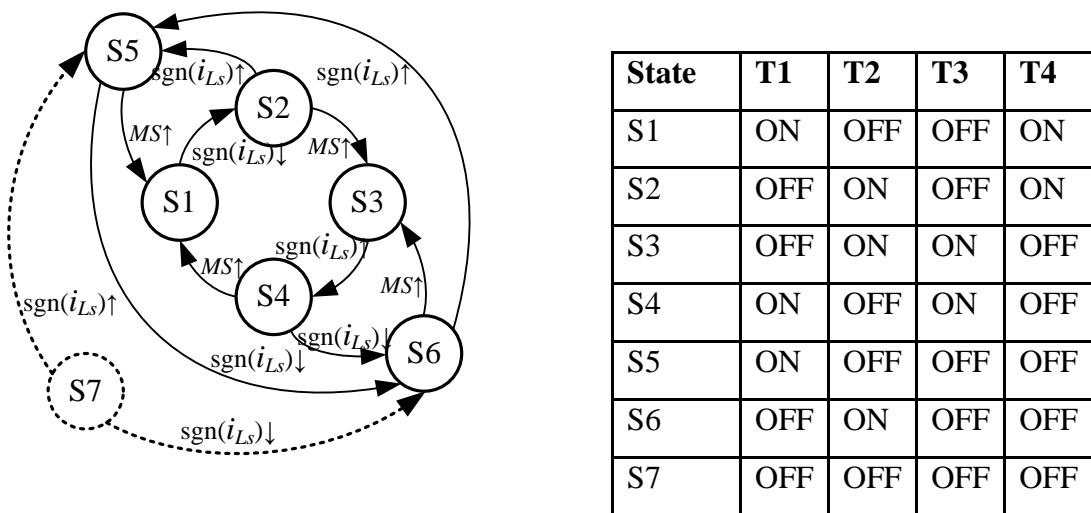

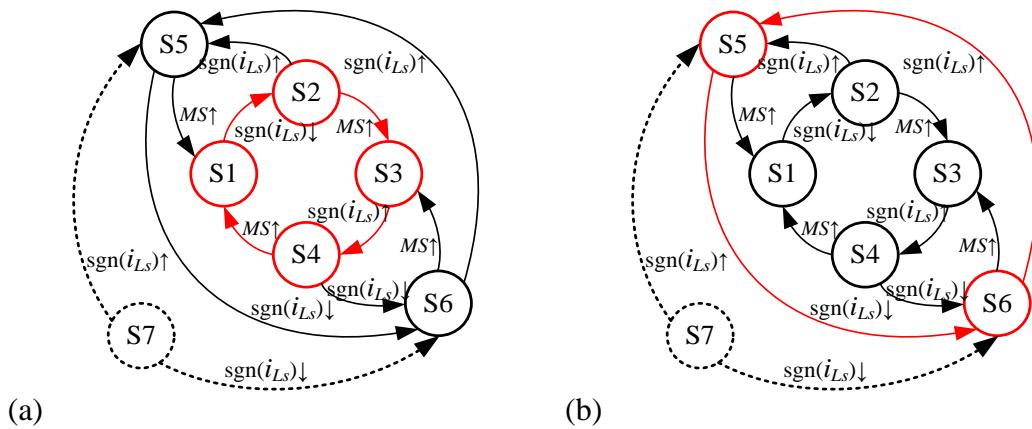

| 5.2 State machine .....                                                           | 81  |

| 5.2.1 Design of state machine .....                                               | 81  |

| 5.2.2 Special operation mode for start-up phase.....                              | 83  |

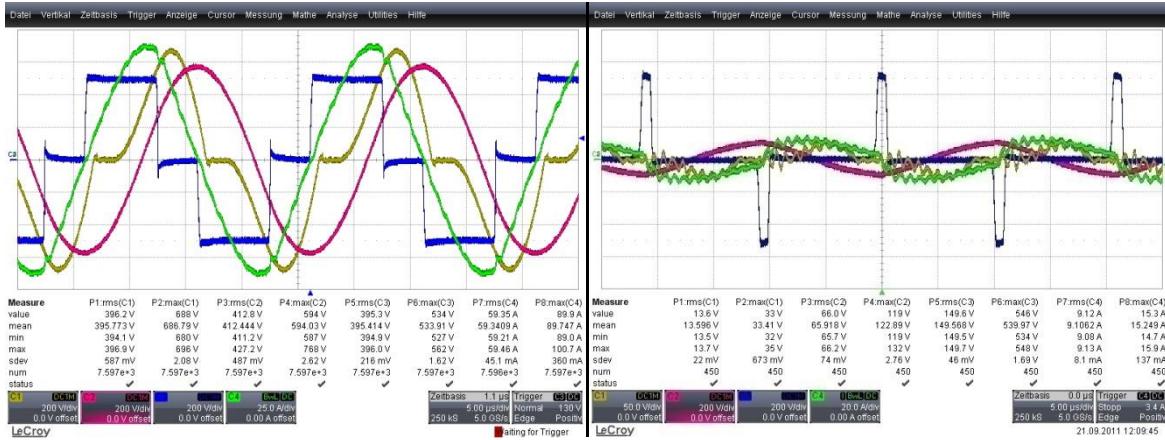

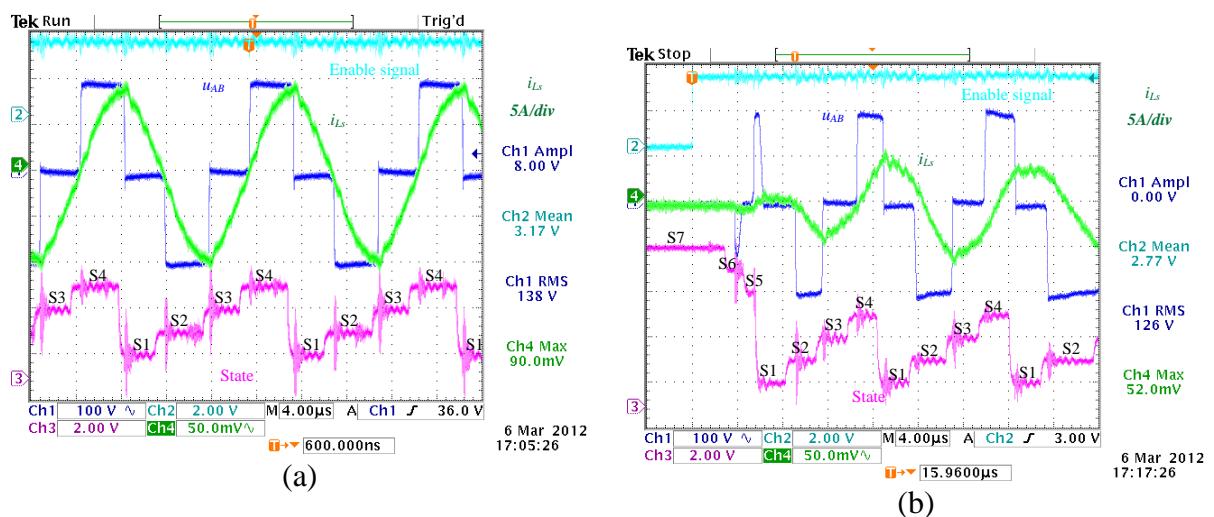

| 5.2.3 Experimental results of digital OM modulation .....                         | 85  |

| 5.3 Modelling of modulators' dynamic behaviour .....                              | 86  |

| 5.4 Summary .....                                                                 | 87  |

| 6 Pulse-width regulation and half-cycle-sampled discrete control .....            | 89  |

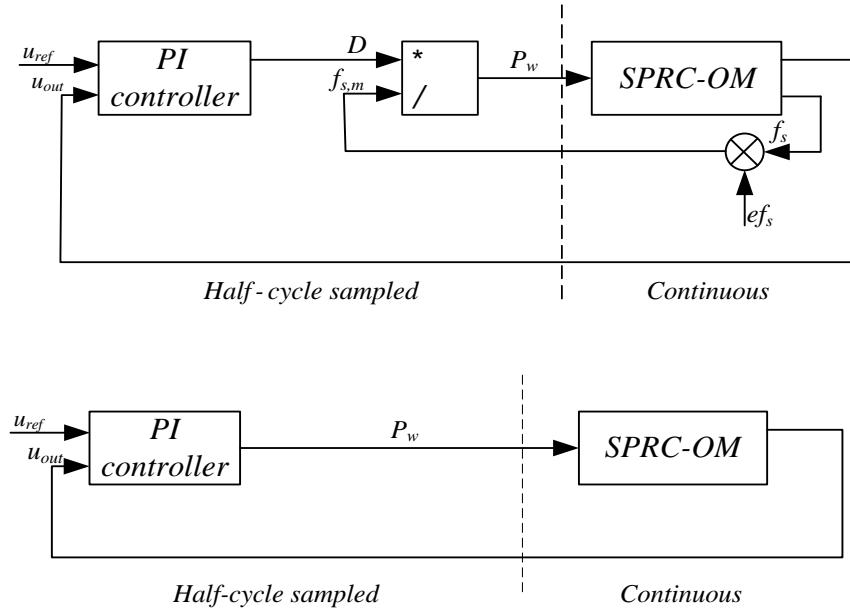

| 6.1 Drawbacks of digital OM control .....                                         | 89  |

| 6.2 Half-cycle-sampled discrete control (HSD control) .....                       | 91  |

| 6.3 Pulse-width regulation .....                                                  | 93  |

| 6.4 HSD pulse-width control (HSD-PW) .....                                        | 95  |

| 6.5 Modelling of pulse-width regulation .....                                     | 98  |

| 6.6 Closed-loop design of duty-ratio regulation and pulse-width regulation .....  | 99  |

| 6.7 Simulation and experimental validation .....                                  | 102 |

| 6.8 Summary .....                                                                 | 104 |

| 7 Half-cycle-sampled calculation system and hardware implementation of SPRC ..... | 106 |

| 7.1 Calculation system for SPRC-LC-OM .....                                       | 106 |

| 7.2 Experimental setup of SPRC in hardware .....                                  | 111 |

| 8 Conclusion and outlook .....                                                    | 114 |

| 8.1 Conclusion .....                                                              | 114 |

| 8.2 Outlook .....                                                                 | 116 |

| List of figures .....                                                             | 117 |

## Contents

---

|                     |     |

|---------------------|-----|

| List of table ..... | 120 |

| References.....     | 121 |

# 1 Introduction

DC-DC converters with isolation are becoming more and more popular due to the rapid development of their present applications in electric power applications. At the same time, new fields of DC-DC applications appear in renewable energy harvesting, fuel-cell application and power management. In isolated DC-DC converter topologies, the phase-shifted full bridge (PSFB) is still the first choice in medium and high power application. Because of the potentially smaller switching losses, resonant converters are becoming more and more attractive beside the PSFB. Because resonant converters enable soft-switching conditions for the transistors, the switching frequencies are normally higher than the PSFB with the same efficiency requirements. Due to their higher switching frequencies, resonant converters achieve advantages in output filter volume and dynamic performance. Thus, resonant converters show the potential to replace the PSFB in medium and high power DC-DC isolated applications, for their smaller switching losses, higher power density and faster dynamics. [Cao14]

Series-resonant converters (SRC), parallel-resonant converters (PRC) and series-parallel-resonant converters (SPRC) are the most common circuits among the resonant converter topologies. The SPRC unites advantages of SRC and PRC, and abolishes their main disadvantages. The SPRC is allowed to be operated in a wide load range from full load to no load, whereas PRC regulation is lost at full load and SRC regulation is lost at light load. When wide operating ranges are required, the SPRC offers the best efficiency performance in the medium and high power range. Compared to the PSFB under the same efficiency and operation range requirement, higher power density and better dynamic performance can be achieved in SPRC [Bha90][Cao14][Fro91].

Until now, the SPRC has not yet been widely utilized in real isolated DC-DC applications. The major reason is its nonlinear gain and dynamic characteristics and its modelling complexity. The PSFB performs a linear characteristic in its continuous current mode, which is easy to understand and predict. Because of this linear characteristic, the control algorithm of the PSFB is simple and robust. Even in spite of its relative high switching losses, PSFB is still the preferred choice for many industry applications.

Compared to PSFB, the modelling techniques and controller design for the SPRC pose a series of challenges. The state-of-the-art modelling techniques of the SPRC can be divided into two categories. One category of modelling techniques, including fundamental AC analysis [Ste88] and extended describing function model [YLJ92], is simple but has a poor accuracy, especially at heavy load condition. The other category, including sampled-data analysis and time-domain analysis [VEK86], is accurate but complex to derive and calculate. The SPRC is suitable for being operated in a wide load range, but modelling techniques do not show sufficient accuracy at heavy load condition [FWM03]. If high accuracy in wide load range and output-voltage range is required, the modelling techniques for the SPRC normally become too complicated to calculate and implement. These modelling approaches involve groups of numerical solutions and consume a lot of computation resources. The complexity of SPRC modelling approaches also impedes the development of its controller algorithm. The major state-of-the-art control algorithm is gain-scheduling proportional-integral control. The application of an advanced control structure depends on further development of simple and accurate modelling techniques.

Due to the development of digital devices, e.g. field programmable gate array (FPGA) and complex programmable logic device (CPLD), appropriately designed algorithms with certain complexity can be implemented in these devices, calculating the model in real-time. This technique is mainly used in hardware-in-the-loop (HIL) simulation, as an objective for

verifying the controller. The development of these real-time algorithms also spurs some complex control ideas, like model-predictive controls. State-of-the-art modelling techniques with sufficient accuracy in wide range (sampled-data or time-domain method) are too complex to be implemented in these digital devices. This is mainly because several transcendental differential equations are substance of these SPRC models. Until now, these modelling approaches are used for computer-aided analysis and computer-aided design in practice, which are calculated by numerical solution methods in high-end computers with practically infinite calculation capabilities. The calculation requirements of these modelling approaches are clearly beyond the capability of present digital devices. This is another motivation for developing novel modelling and control algorithms for the SPRC. By reducing the complexity of algorithms, the SPRC model can be transplanted to FPGAs for real-time simulation.

Due to these problems, this dissertation focuses on the discussion of modelling and control algorithms for the SPRC. Finding an appropriate algorithm with relatively low computation complexity and sufficient accuracy for the SPRC is the main objective of this dissertation.

Main questions about modelling and control algorithm for SPRC are listed below:

- Is it possible to model the SPRC without involving numerical solutions?

- What is the best compromise between model complexity and accuracy?

- How does the novel modelling algorithm support the control design?

- How can the dynamic performance of SPRC be improved with the advanced control design?

In order to answer these questions, a new idea about modelling techniques for resonant converter is proposed, called the half-cycle-sampled discrete (HSD) system. In Chapter 2, the principle idea of the HSD system is introduced. Improved steady-state analysis of the SPRC

considering the voltage distortion is proposed in Chapter 3. The modelling algorithm cleverly avoids numerical solutions in the calculation process and simplifies the calculation procedure. By combining Forsyth's steady-state model [FWM03] and HSD model, a novel discrete dynamic model for the SPRC with optimized modulation is presented in Chapter 4. The modulation and control strategies of SPRC are discussed utilizing the novel HSD idea to answer the third question. These modulation strategies are introduced and implemented in Chapter 5. These strategies are also modelled in the discrete system to describe their dynamic behaviour. The HSD principle is also applied in the controller design, using synchronized varying-step controller instead of the fixed-step controller. In Chapter 6, these novel controllers are introduced and implemented to improve the dynamic performance of the system. In Chapter 7, a calculation system of the SPRC is introduced based on the HSD system. The novel calculation system simulates the dynamic process of SPRC system. The experimental setup of SPRC hardware is also presented in Chapter 7. Finally, a conclusion and outlook are given in Chapter 8.

## 2 The principal idea of half-cycle sampled system

In order to find a low-calculation-cost modelling algorithm for the SPRC, a novel modelling technique for the SPRC is proposed in this chapter. Due to the sampling characteristic of the modulation strategy, the general idea of novel system, called half-cycle sampling, is generated. As the SPRC has a similar waveform in each half period of the switching cycle, the sampling step is selected as the same as the length of each half cycle. Utilizing this varying-step sampling, the entire system of the SPRC is converted to a half-cycle-sampled discrete system (HSD system). This novel sampling leads to a novel varying-step sampled model of SPRC, called HSD model. This discrete model will be briefly introduced in this chapter and introduced in detail in chapter 4.

This chapter includes 5 sections. First, the entire system of the SPRC is designed and introduced, including SPRC topology and its control circuit. The circuit design and operation modes of the SPRC are presented in Section 2.1. SPRC has a number of options in its design process, including the selection of switching frequency, filter topology and modulation strategies. There are three major modulation strategies for the SPRC, which are introduced and selected in Section 2.2. The principal idea of HSD method is proposed and introduced in Section 2.3. As a varying-step sampled system, the general modelling procedures from electrical circuits to the HSD models are introduced in Section 2.4. Finally, a short summary of the novel HSD idea is given in Section 2.5.

## 2.1 Designing choices of series-parallel-resonant converter

As the growth of series-parallel-resonant converters (SPRC) utilization, the design of SPRC system becomes mature during time. The SPRC has three major options in its design process, including the selection of switching frequency, filter topology and modulation strategies. Compared to PSFB and other resonant converters, SPRC shows its advantage in efficiency and operation range. Thus, the SPRC is mainly designed for two specifications in this dissertation: wide operation range and fast dynamic performance. Following this specifications, SPRC is designed with two options below.

First, the category of SPRC topologies can be separated by the type of its output filter, as with capacitive filter (SPRC-C) and with inductor-capacitive filter (SPRC-LC). SPRC-C has better output performance when high quality of output voltage is required [Cav06]. In order to achieve high control dynamics while retaining small output voltage and current ripples, inductor-capacitive filter as a higher-order filter performs better than single capacitive filter.

[Cao14]

Second, SPRC can also be operated at sub-resonant mode or super-resonant mode, with the switching frequency below or above the resonant point. A super-resonant converter is selected because of its elimination of the reverse-recovery losses on the freewheeling diodes [Cao14].

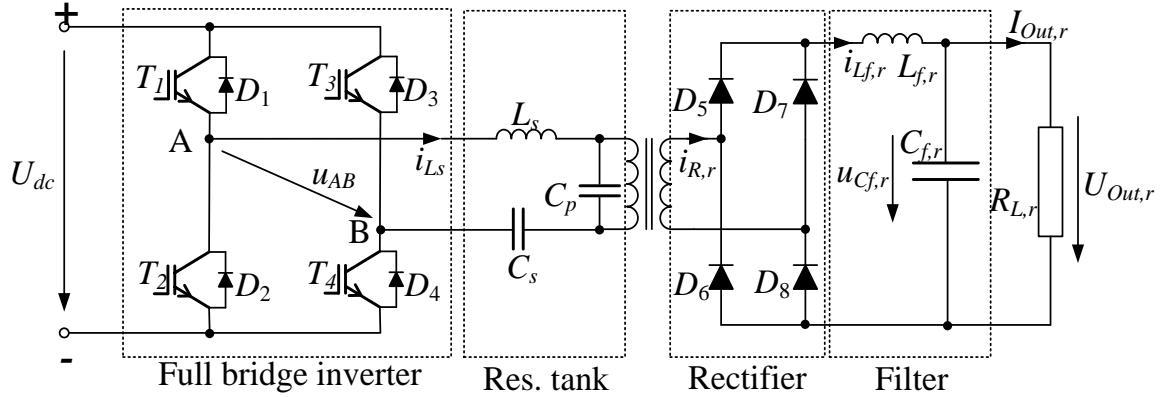

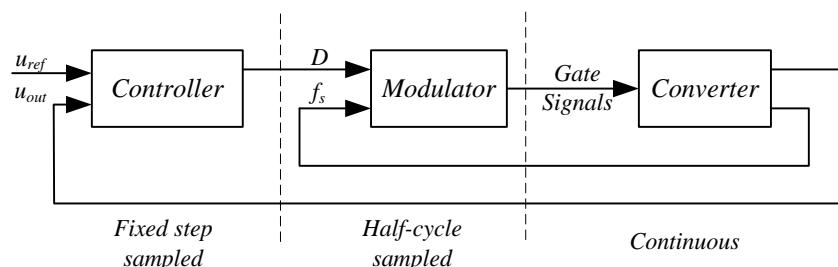

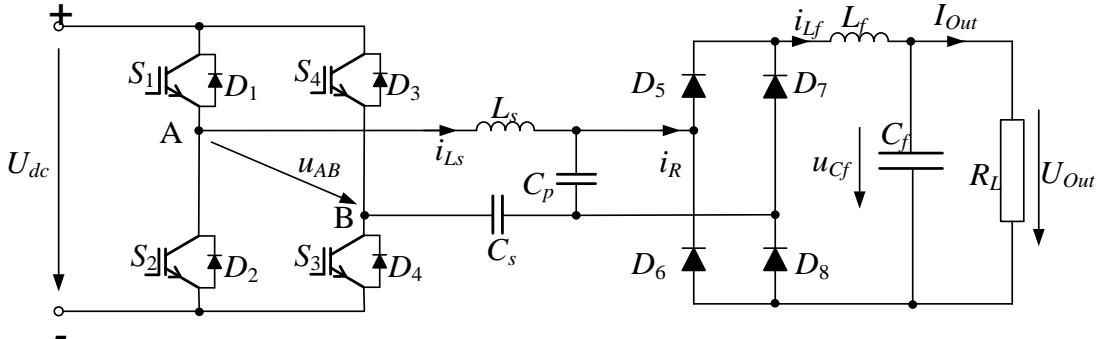

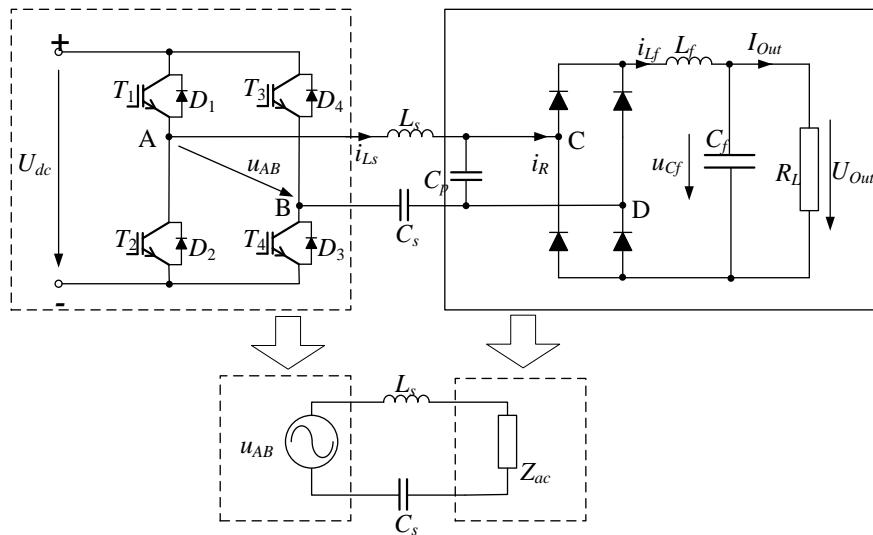

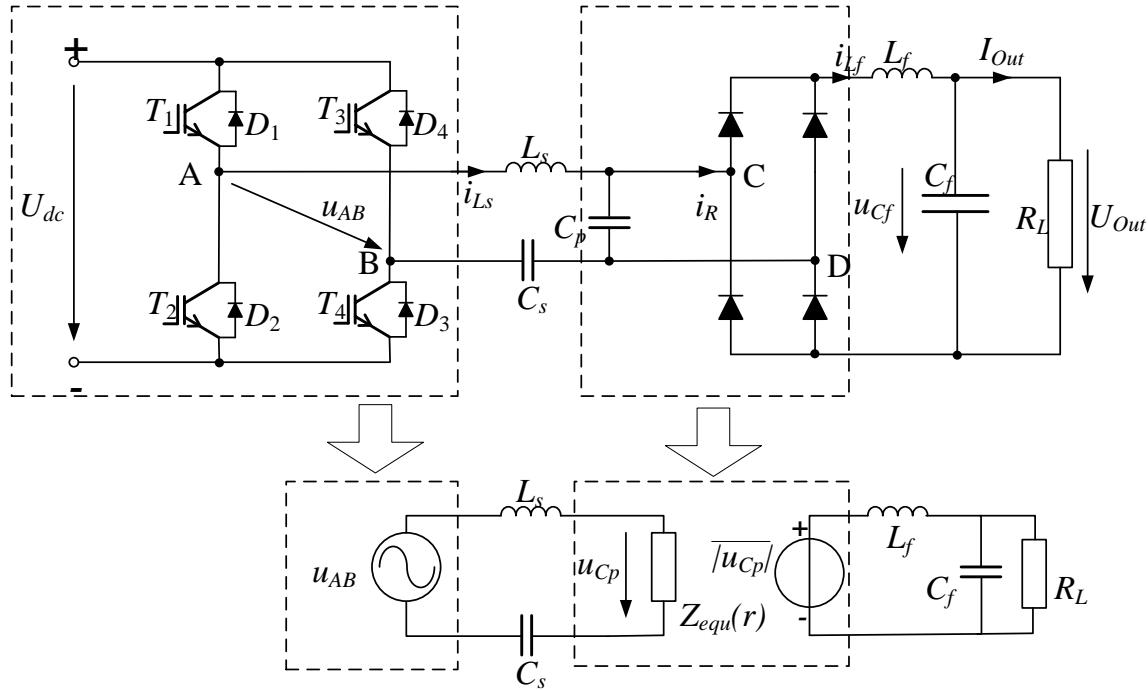

Therefore, a super-resonant SPRC-LC is selected in this dissertation because it performs the better efficiency (no reverse-recovery losses) and potential high dynamics (LC filter) [Cao14]. The circuit diagram of the super-resonant SPRC-LC is illustrated in Figure 2.1. The SPRC circuit is composed of full-bridge inverter, resonant components, transformer, rectifier and output filter. Considering it as a black box in the control system, the four gate signals for the

transistors are the input Boolean signals ( $T_n$ ,  $n = 1, 2, 3, 4$ ) while the output voltage ( $U_{out,r}$ ) is the output signal of this converter.

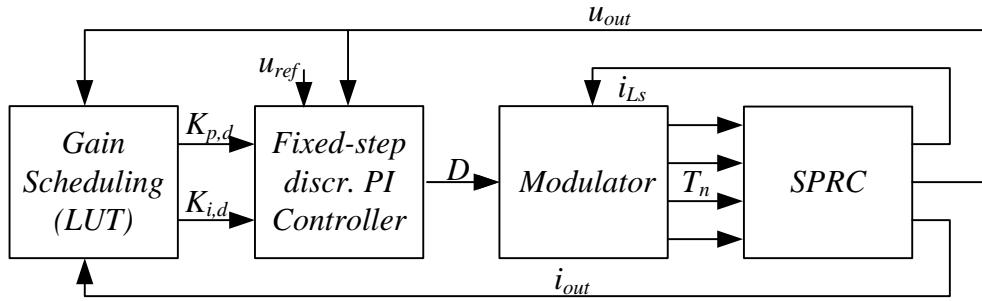

Figure 2.1: Schematics and major components of a series-parallel-resonant converter

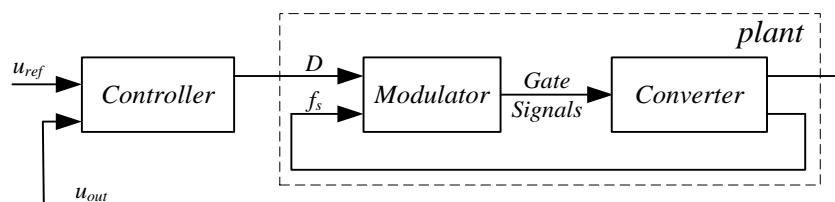

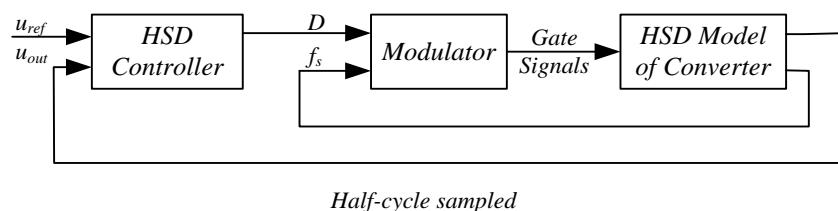

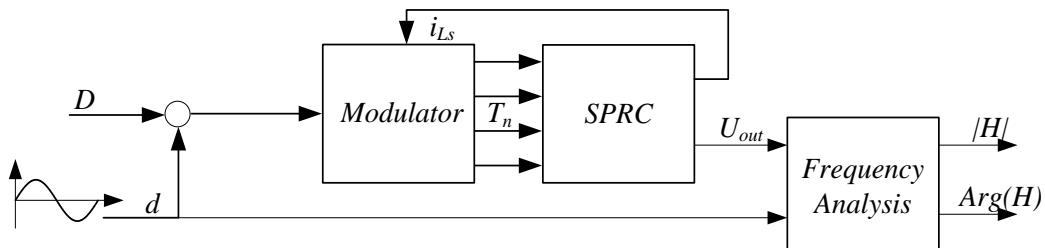

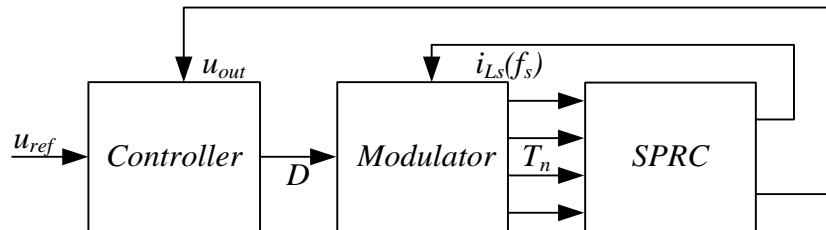

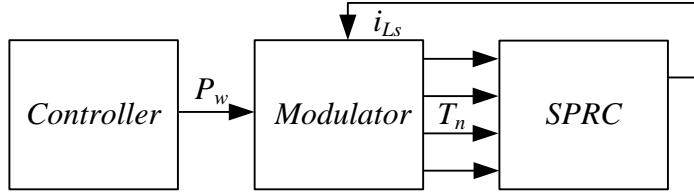

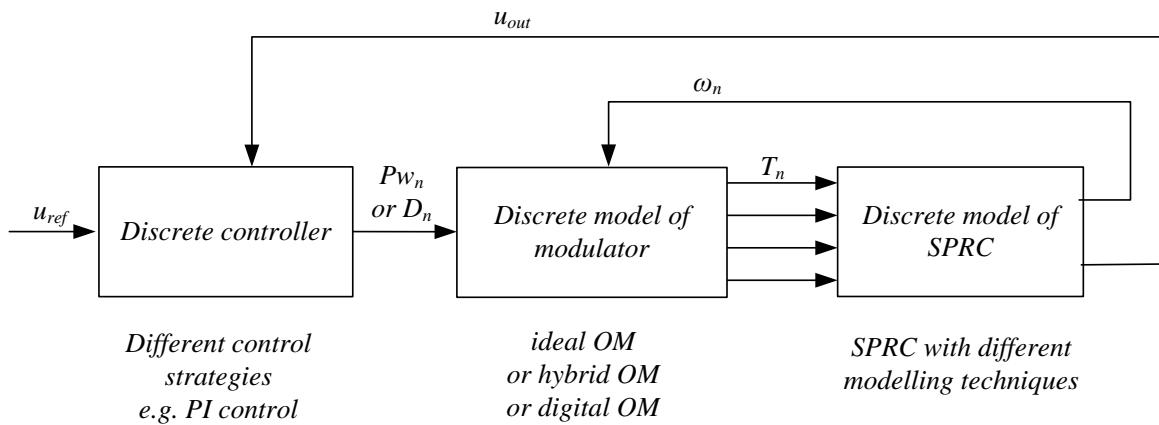

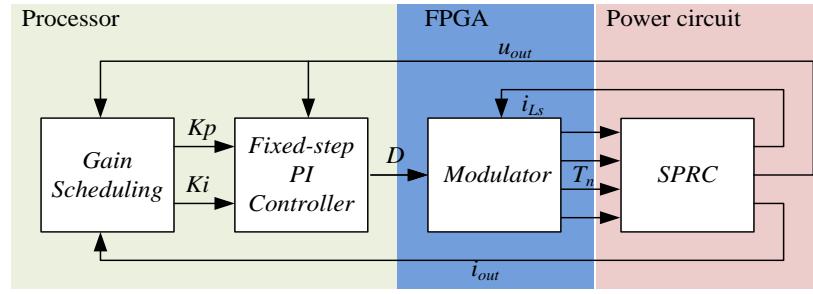

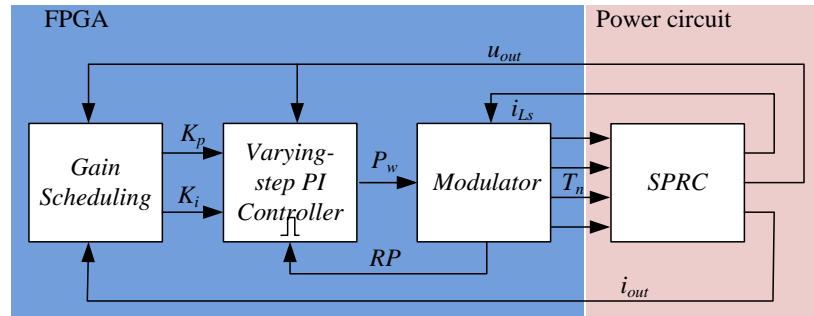

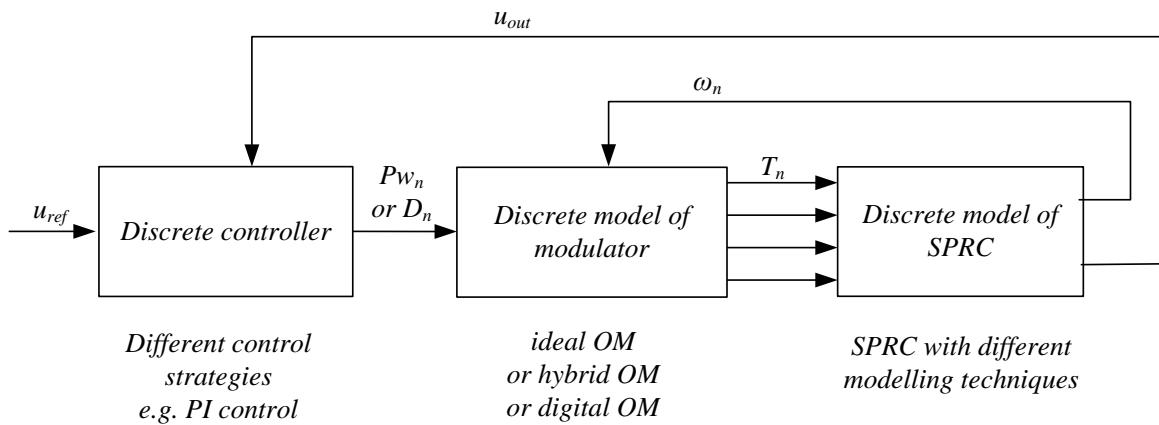

To regulate the output voltage, the control structure of SPRC is normally divided into the controller, the modulator and the converter. An example of SPRC control structure is illustrated in Figure 2.2. In this dissertation, the output voltage is the only control objective for the different control algorithms. The reference value  $u_{ref}$  is given, while the output voltage  $u_{out}$  is the feedback signal from the converter. The controller determines the control signals with its control algorithm, as duty ratio  $D$  in the figure. The modulator converts the control signals into corresponding gate signals ( $T_n$ ,  $n = 1, 2, 3, 4$ ) and sends them to the transistors.

Figure 2.2: Basic block structure of SPRC system

## 2.2 Introduction of three different modulation strategies

According to previously published works [YP04+], there are several optional modulation and control strategies for the SPRC-LC topology. Because of the conduction condition of full-bridge inverter, the modulation behaviour can be simplified as generating a square waveform ( $u_{AB}$ ) with positive, negative and zero values of input DC voltage ( $U_{dc}$ ).

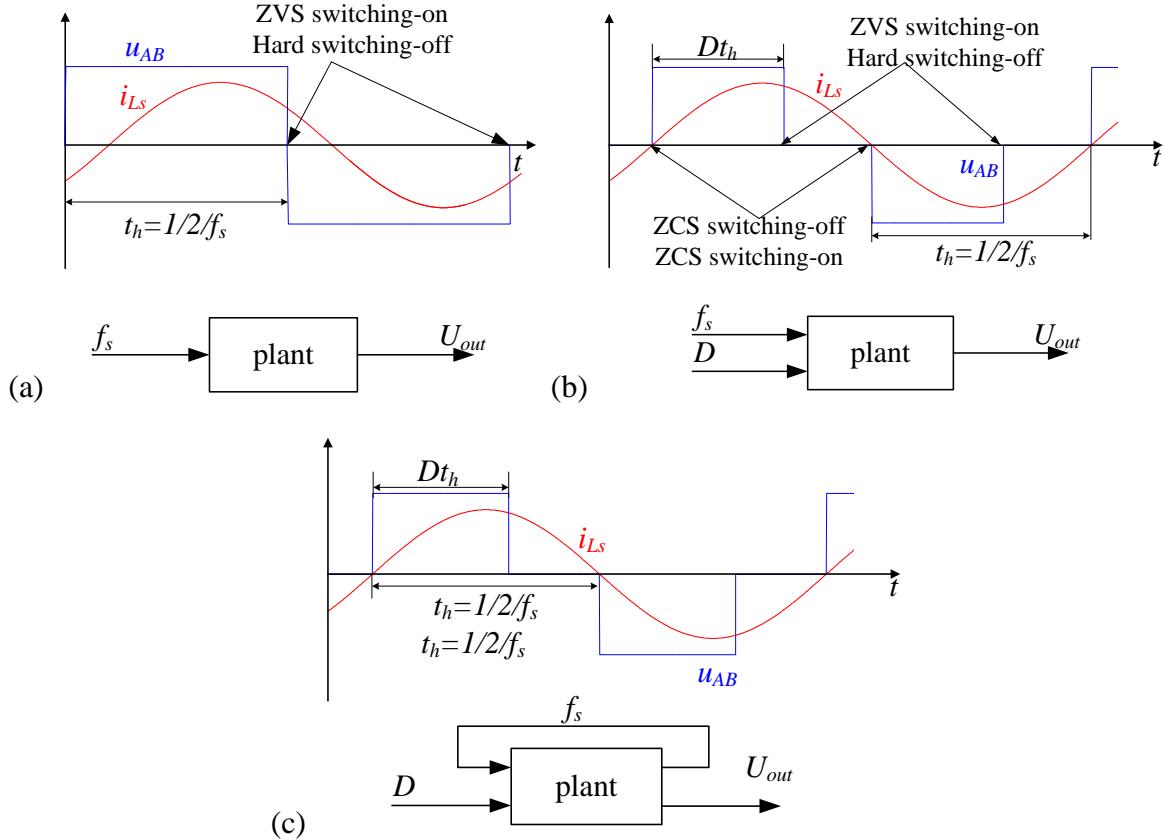

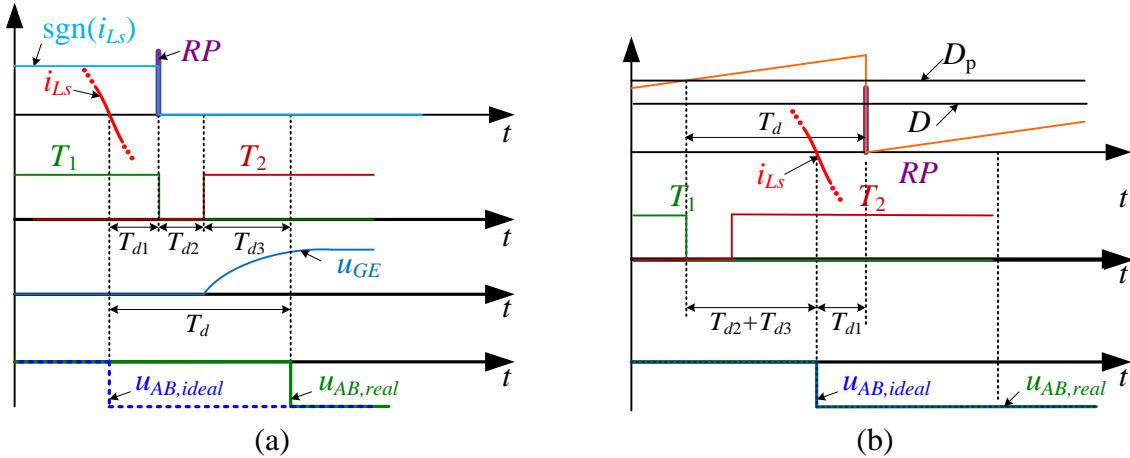

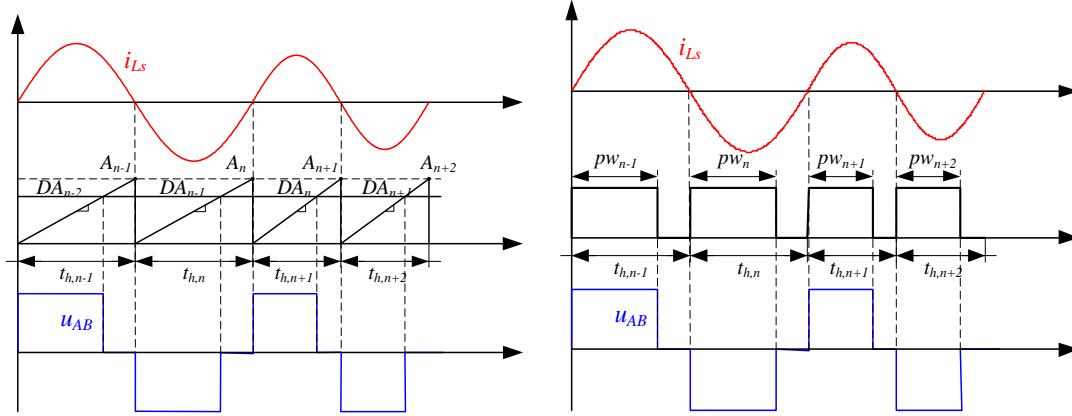

Normally, the switching frequency is the only controlled variable in the system, while the duty ratio is constant to unity. This modulation strategy is called pulse frequency modulation (PFM), as illustrated in Figure 2.3(a). At different switching frequencies, the phase difference between  $i_{LS}$  and  $u_{AB}$  varies. It is the most widely applied modulation strategy for resonant converters. However, the converter operated with PFM has two hard switching-off transients in every switching cycle. If a wide operation range is required, the switching frequency also varies in a wide range. Because the design of transistors and magnetic cores are depending on the highest frequency, it introduces some additional challenges in design process. Thus, PFM is not suitable for wide operation range application.

Figure 2.3: Comparison of modulation strategies, (a) PFM (b) PFWM (c) OM

In order to avoid this problem, the duty ratio can also be controlled in the system [Aig05]. As illustrated in Figure 2.3(b), the modulation strategy acting on both switching frequency and duty ratio is called pulse frequency and width modulation (PFWM). PFWM reduces the switching frequency variation in a wide operating range due to the additional duty-ratio regulation. It can achieve zero-voltage switching (ZVS) in one leg and zero current switching-off and switching-on (ZCS) in the other, if the load condition is appropriate. PFWM is suitable for wide operation range because of the relatively small frequency variation.

If the ZCS condition needs to be guaranteed in PFWM, the switching frequency has a nonlinear relationship with the duty ratio. Each switching frequency has a corresponding duty ratio at certain operating point. This relationship mainly depends on the circuit parameters of

the resonant tank and is sensitive to the parasitic components. In practice, the controller does not have the capability to predict the relationship because complicated calculation is required.

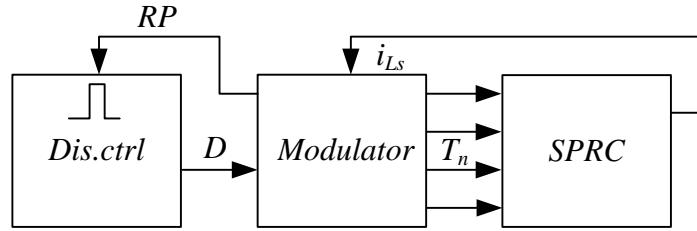

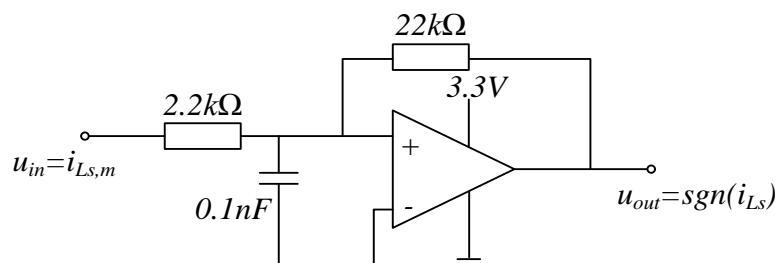

In order to avoid these complex calculations in the control algorithm, Pinheiro proposed a novel modulation strategy in 1999, called self-sustained oscillating control (SSOC) [PJJ99]. Instead of directly controlling switching frequency, SSOC measures and utilizes the resonant current as the synchronizing signal in modulation. The modulator is operated and reset synchronously by the resonant current, which contains the information of switching frequency. The control structure of this modulation can be approximately considered as an internal feedback of switching frequency.

Although in [PJJ99] SSOC modulation is mainly designed for PFM, it can also be applied to the PFWM strategy. In this dissertation, the modulation strategy combined with PFWM and SSOC is called optimized modulation (OM). Once the duty ratio is adjusted in OM, the switching frequency is automatically adapted by the feedback loop, as illustrated in Figure 2.3(c). ZVS and ZCS conditions are automatically guaranteed even in a wide operation range. OM inherits the high efficiency and narrow frequency variation from PFWM and the modulation is more convenient to implement. It is obviously the best modulation strategy for the SPRC with wide operation range requirement

### 2.3 General thoughts about half-cycle sampled discrete system

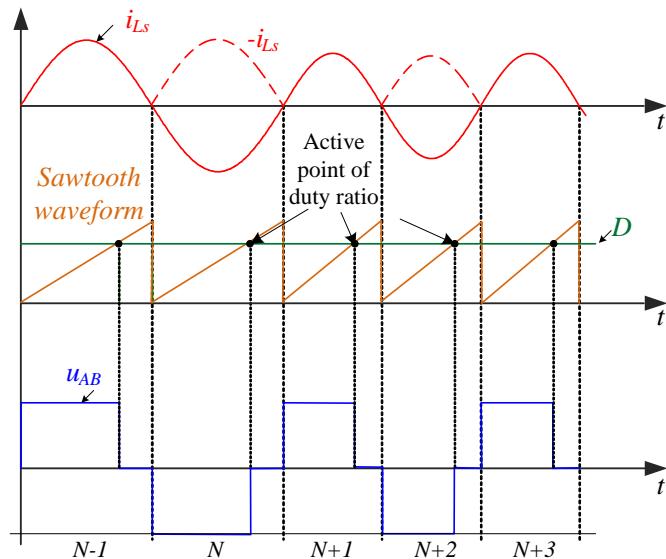

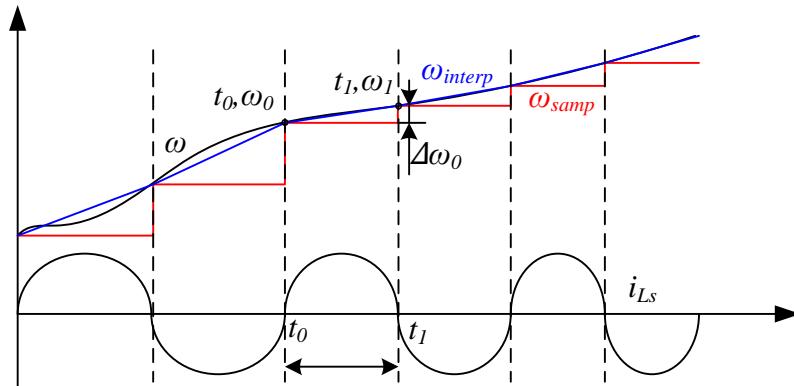

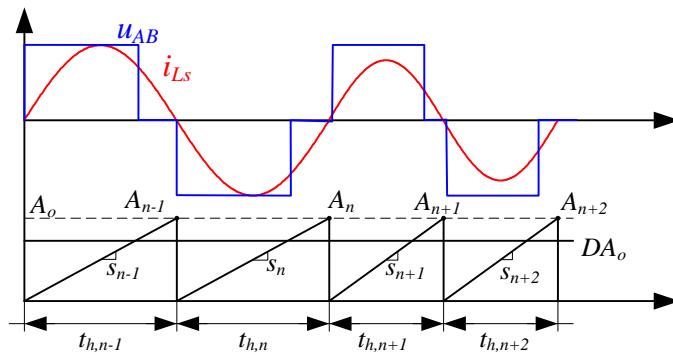

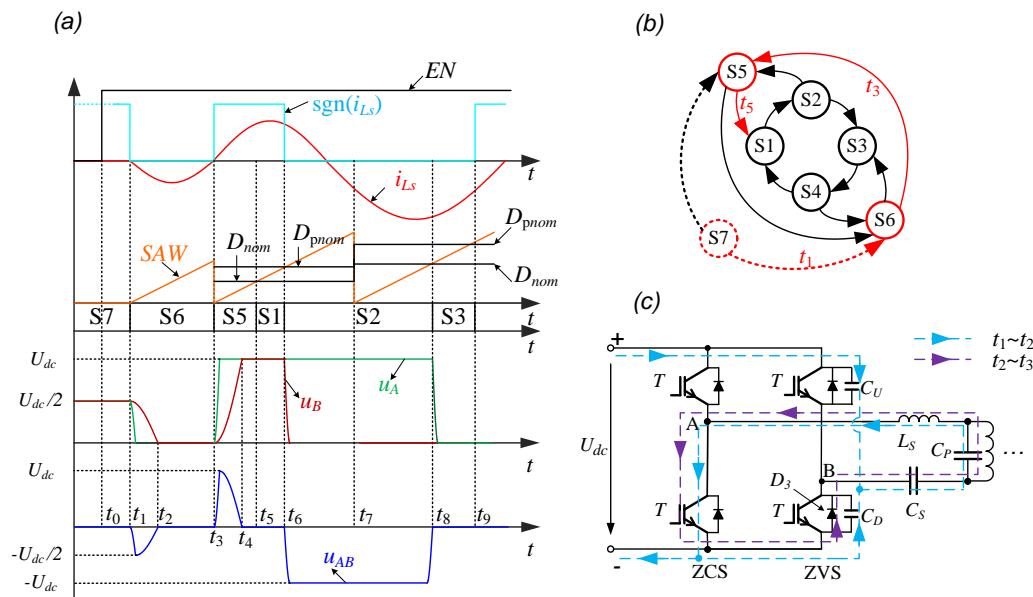

The details and the implementations of a real OM strategy will be introduced in Chapter 4. In order to explain the half-cycle sampled thoughts in this section, Figure 2.4 gives the major waveforms of SPRC-LC operated by OM (SPRC-LC-OM).

From top to bottom, the waveforms depict resonant current  $i_{Ls}$ , saw-tooth signal with duty ratio and output voltage of full-bridge inverter  $u_{AB}$ . The modulation strategy can simply be expressed by three steps. First, the modulator generates the synchronized saw-tooth

waveform. The saw-tooth signals are reset at the zero-crossing point of resonant current  $i_{Ls}$ . Second, the duty-ratio signal is compared to the saw-tooth waveform to decide the pulse width of  $u_{AB}$ . Third, voltage  $u_{AB}$  is generated with the desired pulse width and the direction of  $i_{Ls}$ .

In Figure 2.4, the switching frequency is increasing. It is observed that the waveforms  $i_{Ls}$ ,  $u_{AB}$  and saw-tooth signals have similar shapes in different half cycles, even with different switching frequencies. The waveforms  $i_{Ls}$  and  $u_{AB}$  in odd half cycles are inversely symmetrical to the waveforms in the even half cycles. Considering this symmetric characteristic, the waveforms  $|i_{Ls}|$ ,  $|u_{AB}|$  and saw-tooth signals are periodic waveforms in the half cycle. Half-cycle periods can be considered as the minimum analysis unit in the time-domain. It is also interesting to point out that only one value of duty ratio is active in every time unit, as shown in the figure. It can be considered as sampling with varying step in every half cycle.

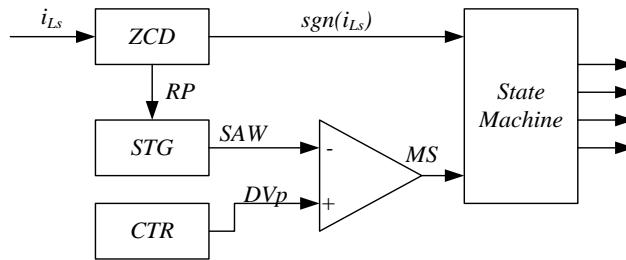

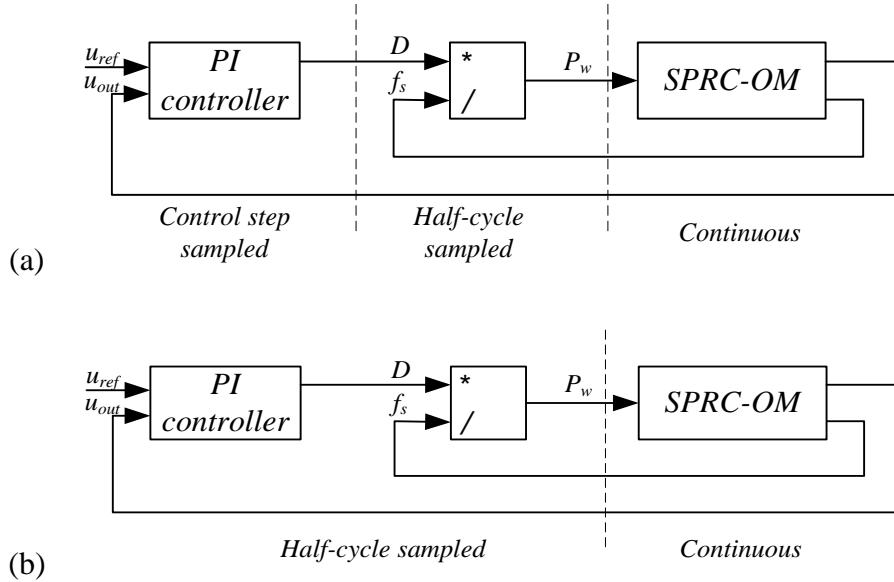

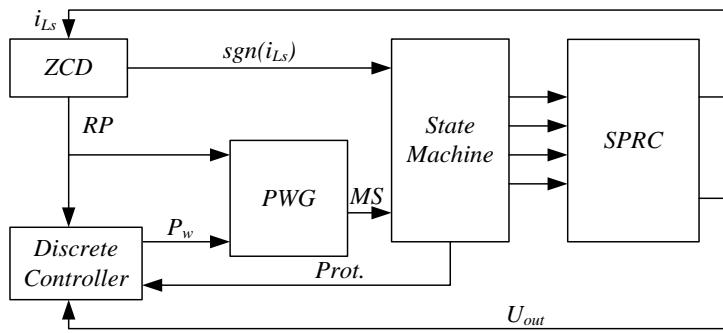

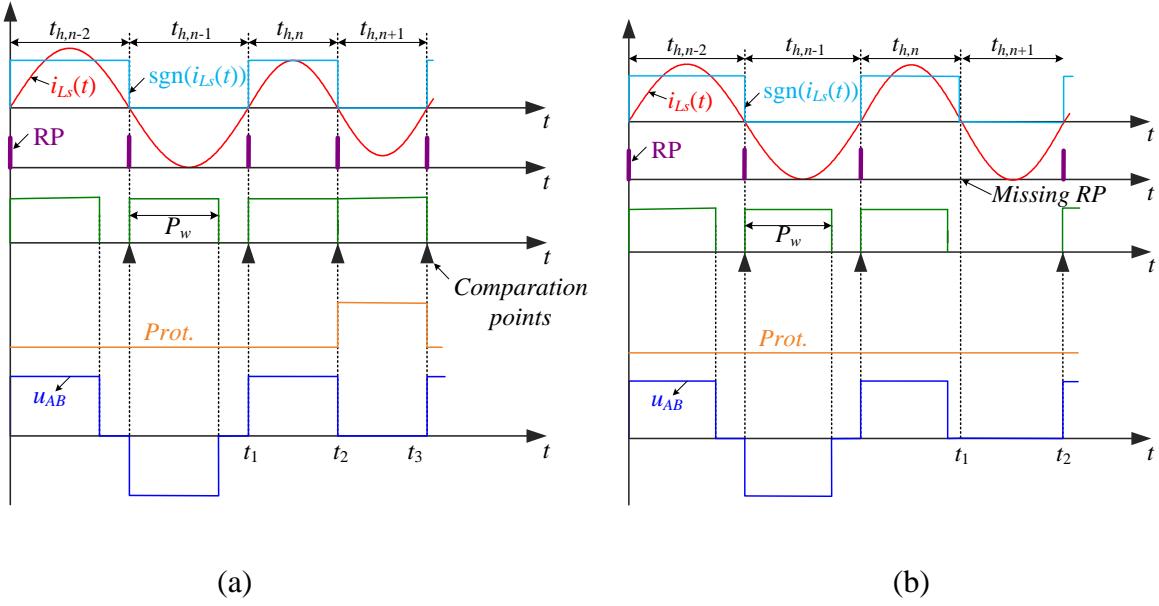

Figure 2.4: Synchronicity of major waveforms and half cycle sampling characteristic in optimized modulation

In state-of-the-art control systems of SPRC, there are normally three different sampling times. Although some of these modelling techniques [YLJ92] [CNT+12] analyse the model with half-cycle sampling period in derivation, almost all the published works [Ste88] [PJJ99] [YLJ92] [CNT+12] [YPJ04] of modelling techniques assume that the SPRC converter is a continuous system. Second, the modulator samples the control signals synchronously with the resonant current  $i_{Ls}$  as the analysis mentioned above. The control signal in OM and SSOC is sampled with half cycle. Third, the controller, normally digital and discrete, has another fixed sampling step, e.g. 20 kHz in the control system. Figure 2.5(a) illustrates the different sampling steps in the SPRC-LC-OM system.

The characteristic of the modulator leads to a novel thought for modelling technique and control algorithm. Instead of the system with different sampling steps, the whole system should be created based on the same sampling step. The sampling step of SPRC system depends on the length of half-cycle. The entire system can be called “half-cycle-sampled discrete system” (HSD system). The structure of HSD system is illustrated in Figure 2.5 (b).

(a)

Half-cycle sampled

(b)

Figure 2.5: Three different sampling steps in original control system (a) and half-cycle sampled control system (b)

As illustrated in Figure 2.5, the HSD system comprises of the novel half-cycle-sampling discrete controller (HSD controller), the modulator and the novel half-cycle-sampling discrete model of SPRC-LC (HSD model). This dissertation will be organized with these three blocks. The HSD model will be introduced in Chapter 3 and Chapter 4. The modulator will be introduced and implemented in Chapter 5. The HSD controller will be designed and implemented in Chapter 6.

Generally speaking, HSD model with half-cycle sampling eliminates the frequency higher than switching frequency. This is a conclusion of Nyquist–Shannon sampling theorem. In real converter, the output filter is designed as a low-pass filter for eliminating the voltage and current ripples. High-frequency signals are blocked in the output filter and have almost no effect at the output side in real converter. Therefore, a HSD model of SPRC can perform an accurate average result and an inaccurate ripple result in theory.

Beside the accuracy of average result, there are some obvious advantages of the HSD system. First, the HSD system makes the controller, modulator and converter to be operated synchronously. It brings some convenience in control and protection, as well as the exception handling. The control structure of the SPRC system will be simplified because of its synchronicity. Second, in the aspect of variable expression, the HSD system gives the most compact expression of the SPRC system. It constricts the deduction process, simplifies the algorithm and reduces the cost of computation resources. Obviously, the HSD system gives a potential modelling technique with a good compromise between complexity and accuracy.

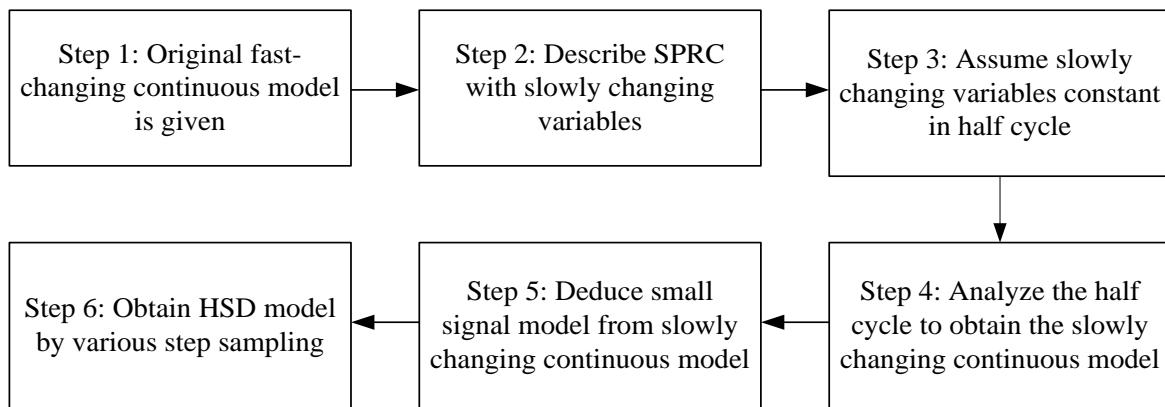

## 2.4 General method of half-cycle sampled discrete model

Among the three blocks of SPRC structure, the HSD modelling approach of SPRC is the most significant part in the HSD system. The converters comprise of electrical components in real hardware. The modelling approach from these components to a mathematical model is one of the emphases of this dissertation. The design of synchronized controller and modulator are dependent on this HSD model. A general method of HSD model is proposed in this section.

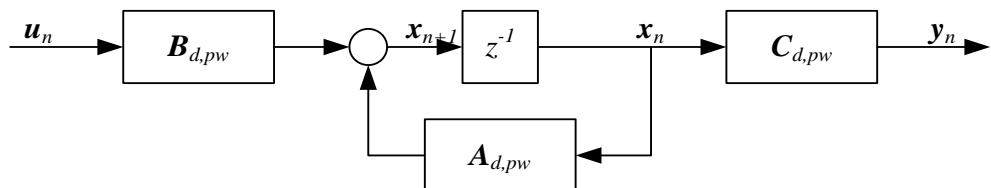

In control theory, the HSD model can be considered as a discrete system with varying sampling steps. There is complete knowledge and research about the analysis of a discrete system. The discrete domain control is also fully developed. Thus, the focus will be on the generation of HSD model with varying sampling steps. A general method for creating a HSD model is introduced in the following.

Figure 2.6: The modelling process of general HSD model method

There are six steps to derive the HSD model from the electrical circuit. First, the original fast-changing continuous model is given based on the characteristics of the passive components in the converter. The second step is describing the resonant state variables with slowly changing variables. Using the resonant current as an instance, it rapidly changes during the half cycle, from positive to negative. In order to assume this variable is constant in the third step, the

amplitude of resonant current  $I_{Ls}$  is taken as the modelling variable instead. The amplitude of resonant current  $I_{Ls}$  is relatively steady and changes slowly during several half cycles.

Third, assume these slowly changing variables as being constant in every half cycle. AC analysis can now be applied with this assumption. The slowly changing continuous model, also the large-signal model, can be derived in the fourth step, based on the analysis of the model. In the fifth step, the small-signal, or linear model is deduced from the slowly changing large-signal model by perturbation and linearization. In the sixth step, varying step sampling is applied in the large- and small-signal model, generating the linear and nonlinear HSD model.

An example of the sixth step is illustrated in the following. For a certain operating point, the linear or small-signal model of the SPRC-LC can be expressed by its system matrixes as

$$\frac{dx}{dt} = Ax + Bu \quad (2.1)$$

$$y = Cx + Du \quad (2.2)$$

The varying step sampling is applied on this model. The sampling step can be expressed as

$$t_s = t_h = \frac{1}{2f_s} = \frac{\pi}{\omega}$$

where  $t_s$  and  $t_h$  represent the sampling step and the time length of half cycle.  $f_s$  represents the switching frequency and  $\omega$  the angular switching frequency. If the Forward Euler Method is applied, the discrete model can be expressed by the discrete system matrixes as

$$x_{n+1} = (E + \frac{A}{2f_{s,n}})x_n + \frac{B}{2f_{s,n}}u_n \quad (2.3)$$

$$y_n = Cx_n + Du_n \quad (2.4)$$

where  $f_{s,n}$  is the varying switching frequency in the dynamic process and  $E$  represents the identity matrix. In state-of-the-art modelling techniques, the switching frequency  $f_{s,n}$  is

considered as an input variable or a state variable in matrixes already. The HSD model does not introduce extra intermediate parameters into the system.

For the nonlinear model, the process of HSD modelling is similar. With different operation points, the nonlinear model can be linearized and can be described by an approximate linear model. Thus, the corresponding nonlinear discrete model can also be generated from the continuous large-signal model.

The HSD model is a general method for any modelling approach or any discretization methods. Different modelling techniques have different assumptions and calculation procedures in the fourth step. Different discretization methods lead to different expressions in the sixth step. Many published modelling approaches, e.g. [Ste88] [PJJ99] [YLJ92] [CNT+12] [YPJ04] have their corresponding discrete modelling approaches for the SPRC-LC topology. In these discrete approaches, the best compromise in regards of simplicity and accuracy will be discussed in the following two chapters.

## 2.5 Summary

In this chapter, the principal idea of the HSD system is introduced. The basic thoughts of HSD systems come from the investigation of modulation strategies. For a modulator applying SSOC and OM strategies, the sampling step of control signal is synchronized with the resonant current. In order to achieve synchronicity in the entire SPRC system, the same sampling step is applied for the converter model and the controller. Therefore, the whole SPRC system is expressed using the HSD system, including HSD model and HSD control. In this chapter, the advantages of this HSD system are analysed briefly. HSD system describes the dynamic behaviour of the SPRC and is relatively concise in the mathematical expression. HSD modelling method is considered as a potential balanced method between complexity and accuracy.

The general method of the HSD model is also introduced in this chapter. It involves the varying-step sampling of a continuous model. The stability of this discrete model is also addressed. The general method of the HSD model can be applied for any modelling approach for the SPRC with any discretization method. As there are many developed modelling approaches for SPRC topology, those offering the best compromise are discussed in the next two chapters.

### 3 Improved steady-state model of SPRC-LC considering the voltage distortion

The model of the resonant converter, as a nonlinear gain system, normally contains transcendental equations. The attempt to solve these equations costs many computation resources. These complex models have limited benefits because only high-performance computers can offer sufficient calculation capability and can thus be employed in analysis. In order to reduce the calculation complexity of the SPRC model to the digital devices level, a novel steady-state modelling technique will be proposed in this chapter.

In this chapter, the state-of-the-art modelling techniques for the SPRC-LC are first investigated in Section 3.1. Within the four state-of-the-art modelling categories, extended fundamental AC analysis, proposed by Forsyth, give a good balance between complexity and accuracy. It is selected as the basis for further development. To highlight the derivation, SPRC-LC circuit is simplified based on some assumptions, which will be presented in Section 3.2. Extended fundamental AC analysis will be introduced step by step in Section 3.3. Because of its drawbacks, improved steady-state analysis considering the voltage distortion is introduced in Section 3.4. Simulation and experimental validation of the novel steady-state analysis with PFWM are performed in Section 3.5. Finally, a short summary is given in section 3.6.

#### 3.1 State-of-the-art modelling techniques of SPRC-LC

Resonant converters are characterized in general nonlinear gain and dynamic systems. The nonlinear gain characteristics cause the major difficulties when starting the design of its operation points. Treating this nonlinear gain characteristic, many contributions have been

published on the steady-state modelling techniques for the SPRC-LC, from the 1980s until now.

There are mainly four major categories of the modelling techniques: fundamental AC analysis, extended describing function model, extended fundamental AC analysis and sampled-data or time-domain analysis.

The fundamental AC analysis method was proposed in 1988 [Ste88]. It is widely utilized for operation range decision and first-step circuit design of resonant converters. The analysis method assumes all the voltage and current waveforms in the resonant tank to be ideally sinusoidal, including resonant current  $i_{LS}$ , series-capacitor voltage  $u_{Cs}$ , and parallel-capacitor voltage  $u_{Cp}$ . The rectifier diodes ( $D_n, n = 5, 6, 7, 8$ ) are considered as ideal switches, which transform the sinusoidal waveform of the parallel-capacitor voltage  $u_{Cp}$  into its absolute value  $|u_{Cp}|$ . The output filter is considered sufficiently large, such that the average value of  $|u_{Cp}|$  equals the output voltage  $u_{out}$  in steady state. Hence, the load DC resistance is converted to an equivalent AC resistance, so that AC circuit analysis can be applied in the resonant tank. The DC voltage transfer ratio and the steady-state model are derived in [Ste88]. The small-signal model of fundamental AC analysis method is derived in [PJJ99].

Fundamental AC analysis is an approximate but simple method. It does not involve complicated mathematical calculations. One of the major problems of fundamental AC analysis is its accuracy at heavy-load condition. The parallel-capacitor voltage  $u_{Cp}$  is distorted from sinusoidal waveform, which brings the deviation into the model.

Another modelling approach for resonant converters was proposed by Yang in [YLJ92] and [YLJ92+], called extended describing function model. The major method is to describe the resonant behaviour with slowly time-varying values. Again, it assumes that all the voltage and current waveforms of the resonant tank are ideally sinusoidal. Instead of the real state

variables, fundamental Fourier coefficients of resonant current  $i_{LS}$  and resonant voltages ( $u_{CS}$  and  $u_{CP}$ ), are utilized to describe the waveforms of the resonant-tank components. This approach yields an accurate small-signal model in the high-frequency range. At heavy load, this approach also leads to large deviations due to the distorted waveforms.

In order to solve the insufficiency at heavy load, Forsyth proposed another steady-state model for the SPRC-LC topology in [FWM03], called extended fundamental AC analysis. This analysis considers the distorted parallel-capacitor voltage  $u_{CP}$  as the integration result of its current. The resonant current  $i_{LS}$  and the series-capacitor voltage  $u_{CS}$  are still assumed as ideally sinusoidal waveforms. Due to the accurate description of parallel capacitor voltage  $u_{CP}$ , extended fundamental AC analysis performs much better at heavy load. The corresponding small-signal model of extended fundamental AC analysis is first mentioned in [CNT+12]. The approach is easy to understand but mathematically relatively complex to be solved. It involves a series of transcendental equations each half cycle, for which numerical solutions are required and high calculation costs have to be paid.

Another modelling approach of SPRC-LC is sampled-data or time-domain analysis. Though with different expressions, the essence of time-domain analysis is the same as sampled-data analysis. Many impressive works have been published in this category, such as [VEK86], [YPJ04], [CTF+13], etc. Sampled-data analysis considers the resonant converter as a “switched control system”. This comprises of several subsystems and switches between them depending on the switching strategies. The mathematical research in this field towards investigation of stability is still developing nowadays [DK01], [Mic06]. In practice, this method requires an explicit solution of differential equations, because the deviation will be cumulative during the calculation procedure. Due to the third-order resonant tank of the SPRC, sampled-data analysis needs 14 switching transients in SPRC-LC-OM [CTF+13].

Sampled-data analysis is calculated iteratively in dynamic processes, so large calculation resources are required.

The basic ideas of modelling techniques with their steady-state model and small-signal model are summarized in the following table. From top to bottom, model complexity is increasing, while accuracy of approach is also improved.

Table 3.1: The major modelling methods of SPRC

| Name                             | Major assumptions                                                          | Steady-state model  | Small-signal model | Drawbacks                                                         |

|----------------------------------|----------------------------------------------------------------------------|---------------------|--------------------|-------------------------------------------------------------------|

| Fundamental AC analysis method   | Ideally sinusoidal waveform in resonant tank                               | [Ste88]             | [PJJ99]            | Inaccuracy under heavy load                                       |

| Extended describing model        | Ideally sinusoidal waveform in resonant tank described by their amplitudes | [YLJ92]<br>[YLJ92+] |                    | Inaccuracy under heavy load                                       |

| Extended fundamental AC analysis | Distorted parallel capacitor voltage                                       | [FWM03]             | [CNT+12]           | Transcendental equations in the model                             |

| Sampled-data analysis            | Switched control system                                                    | [VEK86]<br>[YPJ04]  |                    | Requires an explicit numerical solution of differential equations |

There are also some other intuitive approaches to derive SPRC steady-state and small-signal model. The approximate method of Vorperian [Vor89] assumes that the dynamic behaviour of the SPRC is dominated by a single-pole transfer function in the middle frequency range. It is a good combination of accuracy and simplicity. However, this approach is an intuitive idea rather than a formal approximation.

The modelling techniques for different modulation strategies have also been developed during the progress of modulation strategies. Modelling approaches for PFM and PFWM have already been widely analysed in published works, e.g. [YLJ92+] and [FWM03]. For OM, however, only a time-domain modelling approach is presented in [CTF+13]. The major

difficulty encountered in SPRC-LC-OM modelling is the variation of switching frequency.

Without constant switching frequency, AC analysis is not allowed to be applied in resonant-tank. Thus, the time-domain analysis is the only method available for SPRC-LC-OM.

Because of the complexity of time-domain analysis, simpler modelling approaches with sufficient accuracy are required for further development of OM.

Among all these modelling techniques, the sampled-data or time-domain method is the most complex and the most accurate method, but extended fundamental AC analysis is relatively balanced between its complexity and accuracy. Considering the possibility of implementation in digital devices, extended fundamental AC analysis is selected as the basic analysis method in this chapter. In Section 3.3, the modelling details of extended fundamental AC analysis are introduced.

### **3.2 Major assumptions and simplification of SPRC-LC topology**

Before establishment of the SPRC model, some major assumptions are made in order to simplify the modelling process. First, all components, including the transistors, diodes, capacitors and inductors, are assumed ideal without any losses. The input DC voltage  $u_{dc}$  is considered constant without voltage ripples. The internal resistance is neglected. The transformer is regarded as ideal and the windings are perfectly coupled.

The topology of converter is simplified as Figure 3.1. All quantities in the secondary side of transformer are referred to the primary side. In this dissertation, the primary side equivalent quantities are dominantly mentioned. In order to make the expression clear, the real parameters of the secondary side components are expressed with the subscript 'r'. The

parameters of the primary side equivalent component are expressed directly.

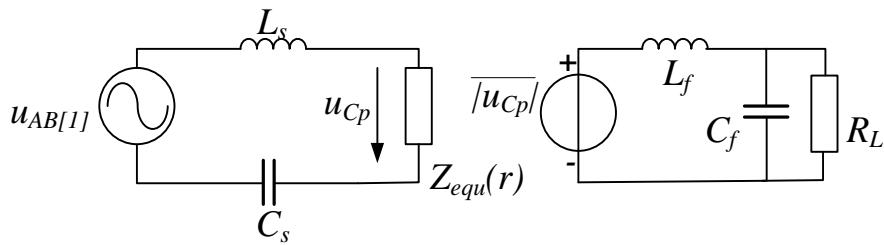

Figure 3.1: Simplified topology of SPRC-LC

In order to clarify the modelling method and its features, several small-value components in the power circuit are ignored. The parasitic resistance and inductance of the filter capacitor, the series resistance of filter inductor and resonant inductor and the equivalent conduction resistance of transistors and diodes are examples in the SPRC circuit. Part of these small-value components are the source of power losses in the circuit. Though they have certain effects on the output voltage, small-value and parasitic components are ignored in order to pursue the most simplified system in the analytical study. For further development of practical modelling techniques, these components can be taken into consideration in the future.

### 3.3 Extended fundamental AC analysis

As the basic method of novel modelling technique, Forsyth's extended fundamental AC analysis [FWM03] is introduced first. Extended fundamental AC analysis is suitable for the SPRC with constant switching frequency, taking the distorted parallel capacitor voltage into consideration.

The basic principle of extended fundamental AC analysis is converting the SPRC-LC topology into a simplified equivalent AC circuit, as illustrated in Figure 3.2. There are two

steps in the circuit conversion. The first step converts the full-bridge inverter circuit and the DC voltage source into an equivalent AC voltage source. Due to the band-pass characteristic of the resonant tank, the fundamental-frequency harmonic  $u_{AB[1]}$  approximates the output voltage of the full-bridge inverter  $u_{AB}$ . The second step converts parallel capacitor, rectifier, filter and the load into an equivalent impedance  $Z_{ac}(R_L)$ , which is dependent on the load resistance.

Figure 3.2: Circuit conversion of SPRC in extended fundamental AC analysis

In the equivalent circuit, AC circuit analysis can be applied. Series capacitor and series inductor are considered as a corresponding impedance. The resonant current  $i_{LS}$  can be expressed as

$$I_{LS} = \frac{U_{AB[1]}}{\left| j\omega L_s + \frac{1}{j\omega C_s} + Z_{ac} \right|} \quad (3.1)$$

With the explicit value of the resonant current  $i_{LS}$ , all the related voltage values ( $u_{LS}$ ,  $u_{CS}$  and  $u_{Zac}$ ) in the resonant tank can be calculated. Therefore, the significant point of this model lies in the estimation of equivalent impedance  $Z_{ac}$ . In order to derive a correct equivalent impedance  $Z_{ac}$ , circuit analysis is applied to the rectifier and the parallel capacitor.

### 3.3.1 Circuit analysis of rectifier

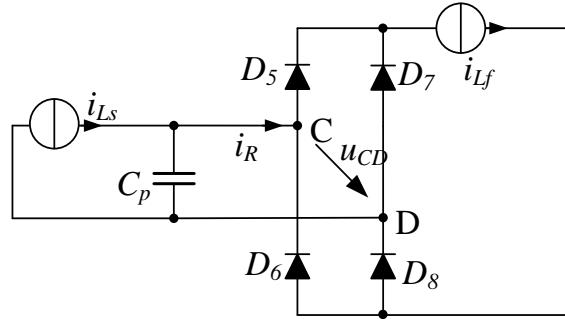

Figure 3.3: Equivalent circuit of rectifier in SPRC

Figure 3.3 illustrates the equivalent circuit of rectifier and parallel capacitor in the SPRC. In steady state, the resonant current and the filter-inductor current are modelled as a corresponding current source. Assuming the resonant current is sinusoidal,  $i_{Ls}(t) = I_{Ls} \sin(\omega t)$ , and output inductor current has no ripple  $i_{Lf}(t) = I_{Lf}$ , the conduction states of diodes are decided by the value of both currents. In order to avoid the series connection of two unequal current sources, the DC current source is sometimes considered as an inductor. Because of the symmetry of the resonant waveform, the circuit analysis in half switching cycle is sufficient. The half cycle with positive resonant current ( $i_{Ls} > 0$ ) is analysed for the instance. The conduction conditions of the rectifier are listed in the table below and are illustrated in Figure 3.4.

Table 3.2: Conduction conditions of rectifier ( $i_{Ls} > 0$ )

| Condition No. | $u_{Cp}$ | $ i_{Ls}  - i_{Lf}$ | Diode action                                                            | $i_R$     |

|---------------|----------|---------------------|-------------------------------------------------------------------------|-----------|

| 1             | >0       | >0                  | D <sub>5</sub> , D <sub>8</sub> ON, D <sub>6</sub> , D <sub>7</sub> OFF | $i_{Lf}$  |

| 2             | <0       | >0                  | D <sub>6</sub> , D <sub>7</sub> ON, D <sub>5</sub> , D <sub>8</sub> OFF | $-i_{Lf}$ |

| 3             | >0       | <0                  | D <sub>5</sub> , D <sub>6</sub> , D <sub>7</sub> , D <sub>8</sub> ON    | $i_{Ls}$  |

| 4             | <0       | <0                  | D <sub>6</sub> , D <sub>7</sub> ON D <sub>5</sub> , D <sub>8</sub> OFF  | $-i_{Lf}$ |

Figure 3.4: Rectifier in different conduction conditions, (a) condition 1 (b) condition 2 (c) condition 3 (d) condition 4

Three conduction conditions of the rectifier, condition 1, 2 and 4, are common with two conducting diodes and the other two blocking diodes. Only in condition 3, the currents are distributed over all four diodes. Because the resonant current is smaller than the filter inductor current  $|i_{Ls}| - i_{Lf} < 0$ , part of the diode current comes from the resonant current ( $|i_{Ls}|$ ), and part is straight free-wheeling through the rectifier ( $i_{Lf} - |i_{Ls}|$ ). The current in each diode is expressed as,

$$i_{D5} = i_{D8} = \frac{(|i_{Ls}| + i_{Lf})}{2} \quad (3.2)$$

$$i_{D6} = i_{D7} = \frac{(-|i_{Ls}| + i_{Lf})}{2} \quad (3.3)$$

The rectifier sink current  $i_R$  equals the resonant current  $|i_{Ls}|$  in condition 3.

### 3.3.2 Steady-state analysis of extended fundamental AC model

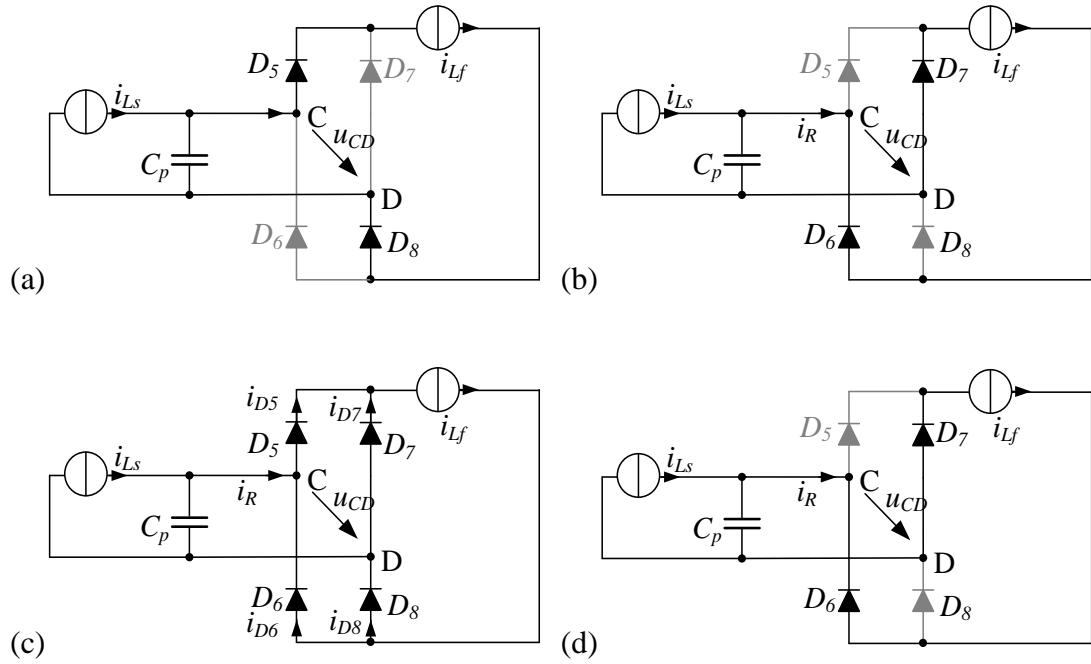

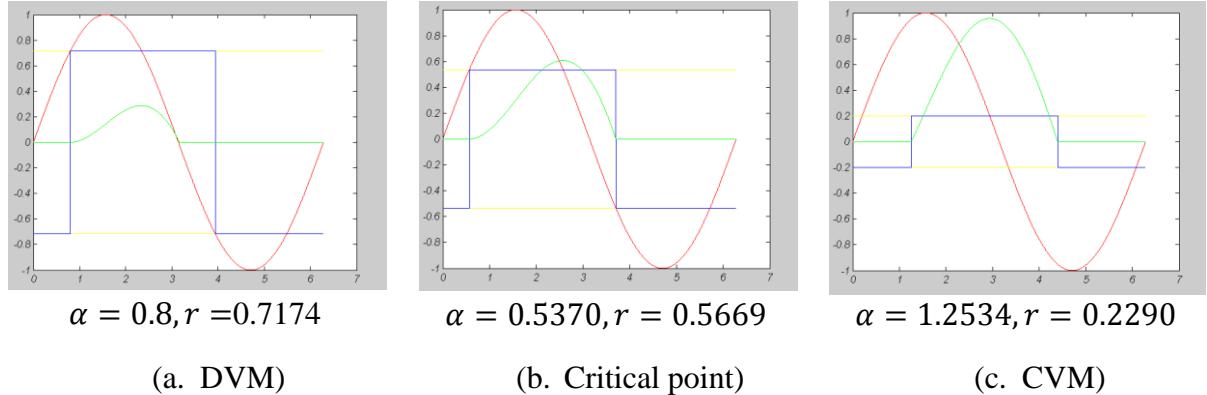

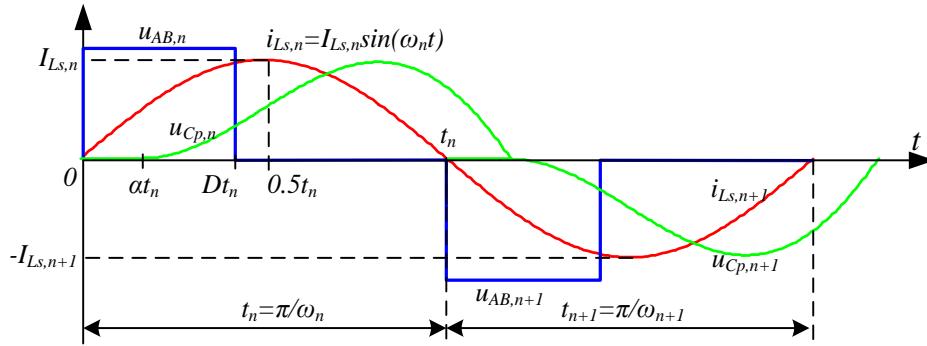

Figure 3.5: Typical waveform of  $u_{AB}$ ,  $u_{Cp}$ ,  $i_R$  and  $i_{Ls}$  in SPRC-OM

Based on the circuit analysis, the steady-state waveform of the SPRC converter can be drawn, as illustrated in Figure 3.5. There are two important instants in the SPRC waveforms: the instant when  $|i_{Ls}(t)|$  equals  $i_{Lf}(t)$  and the instant when  $u_{Cp}(t)$  equals 0. If  $u_{Cp}(t) = 0$  occurs after  $|i_{Ls}(t)| = i_{Lf}(t)$ , the waveform is illustrated as Figure 3.5 (a). If  $u_{Cp}(t) = 0$  occurs before  $|i_{Ls}(t)| = i_{Lf}(t)$ , the waveform is illustrated as Figure 3.5 (b). In these waveforms, the four different rectifier conditions appear as mentioned in the previous section. Based on the continuity of the  $u_{Cp}$  waveform or the appearance of condition 3 or condition 2, the operation mode can be divided into continuous voltage mode (CVM) and discontinuous voltage mode (DVM). In DVM, condition 3 appears in circuit analysis, which changes the shape of rectifier current  $i_R$ . In Figure 3.5 (b), the changed waveform of rectifier current  $i_R$  is clearly illustrated.

Both CVM and DVM waveforms can be described by mathematical functions depending on time in a half cycle. Assuming sinusoidal waveform, the resonant current is expressed as

$$i_{Ls}(t) = I_{Ls} \sin(\omega t) \quad (3.4)$$

The parallel-capacitor voltage  $u_{Cp}$  in half cycle is the result of the integration of the current difference, which can be expressed as

$$u_{Cp}(t) = u_{Cp}(0) + \int_0^t (I_{Ls} \sin(\omega \tau) - i_R) d\tau \quad (3.5)$$

Because of the waveform symmetry, the description of waveform in a half cycle is sufficient.

In the phase range  $0 < \omega t < \pi$ , the diode current  $i_R$  can be described in CVM as

$$i_R(t) = \begin{cases} -I_{Lf}, & 0 < \omega t < \alpha \\ I_{Lf}, & \alpha < \omega t < \pi \end{cases} \quad (3.6)$$

and in DVM as

$$i_R(t) = \begin{cases} -I_{Lf}, & 0 < \omega t < \beta \\ I_{Ls}, & \beta < \omega t < \alpha \\ I_{Lf}, & \alpha < \omega t < \pi \end{cases} \quad (3.7)$$

In this dissertation, the definition of  $\alpha$  and  $\beta$  is different from the original paper [FWM03], because there is some further development of large-signal model in Chapter 4. The angle  $\alpha$  is defined as the angle when the voltage  $u_{Cp}(t)$  leaves the zero point and becomes positive in the first half cycle. Due to the symmetric characteristic of the waveform, the voltage  $u_{Cp}(t)$  becomes negative at the angle  $\pi + \alpha$  in second half cycle in steady state. The angle is given the name “leaving angle”, marking the instant when  $u_{Cp}(t)$  leaves the x-axis. The angle  $\beta$  is defined as the angle when the voltage  $u_{Cp}(t)$  returns to zero, called “returning angle”. In CVM mode,  $\beta = \alpha$ . In order to simplify the expression, the calculation phase window is moved from time range  $0 < \omega t < \pi$  to  $\alpha < \omega t < \pi + \alpha$ . In the novel phase windows, the expressions of rectifier current  $i_R$  are expressed as

$$i_R(t) = I_{Lf} = I_{out}, \quad \alpha < \omega t < \pi + \alpha \quad (3.8)$$

in CVM and

$$i_R(t) = \begin{cases} I_{Lf}, & \alpha < \omega t < \pi + \beta \\ -I_{Ls}, & \pi + \beta < \omega t < \pi + \alpha \end{cases} \quad (3.9)$$

in DVM. Inserting (3.8) and (3.9) into (3.5) gives

$$u_{Cp}(t) = \frac{I_{Ls}}{\omega C_p} (-\cos(\omega t) - \omega t r + \alpha r + \cos(\alpha)), \quad CVM \quad (3.10)$$

$$u_{Cp}(t) = \begin{cases} \frac{I_{Ls}}{\omega C_p} (-\cos(\omega t) - \omega t r + \alpha r + \cos(\alpha)), & \alpha < \omega t < \pi + \beta \\ 0, & \pi + \beta < \omega t < \pi + \alpha \end{cases}, \quad DVM \quad (3.11)$$

The ratio  $r$  is defined as the quotient of the filter-inductor current divided by the amplitude of the resonant current.

$$r = \frac{I_{Lf}}{I_{Ls}} \quad (3.12)$$

### Continuous voltage mode (CVM)

For the continuous voltage mode,  $u_{Cp}$  falls to zero at the end of every half cycle  $t = \pi + \alpha$ .

The expression for  $\alpha$  is obtained by setting  $u_{Cp}\left(\frac{\alpha+\pi}{\omega}\right) = 0$  and  $u_{Cp}\left(\frac{\alpha}{\omega}\right) = 0$ .

$$\alpha = \arccos\left(\frac{\pi r}{2}\right) \quad (3.13)$$

Although even with the correct expression in their text, the figures in [FWM03] and [Cao14] are somehow misleading. In CVM, the angle  $\alpha$  does not equal to the value  $\arcsin(r)$ . This means the waveform of  $i_R(t)$  and  $i_{Ls}(t)$  is not affected in the figure. As illustrated in Figure 3.5(a), there is a short period of rectifier conduction condition 2 in CVM mode.

An expression for the converter output voltage may be obtained by calculating the average value of the rectified parallel capacitor voltage  $\overline{|u_{Cp}|}$ . Integrating the equation (3.10) over half cycle gives the following

$$u_{out} = \overline{|u_{Cp}|} = \frac{1}{\pi} \int_{\alpha}^{\pi+\alpha} u_{Cp}(t) d\omega t = \frac{2I_{Ls} \sin(\alpha)}{\pi \omega C_p} \quad (3.14)$$

Set  $u_{out} = i_{out} R_L$  in (3.14) where  $R_L$  is the load resistance. It gives the fundamental frequency impedance  $Z_{ac}$  in CVM. The expression gives,

$$Z_{ac} = \frac{1 - \frac{4}{\pi^2}(1 + \cos 2\alpha) + j \frac{4}{\pi^2} \sin 2\alpha}{j\omega C_p} \quad (3.15)$$

### Discontinuous voltage mode (DVM)

For the discontinuous voltage mode, the first setting is  $u_{Cp} \left( \frac{\pi+\beta}{\omega} \right) = 0$ , giving

$$-\cos(\pi + \beta) - \pi r - \beta r + \alpha r + \cos(\alpha) = 0 \quad (3.16)$$

Second, the average rectified voltage  $\overline{|u_{Cp}|}$  is expressed as

$$\overline{|u_{Cp}|} = u_{out} = \frac{1}{\pi} \int_{\alpha}^{\pi+\alpha} u_{Cp}(t) d\omega t = \frac{1}{\pi} \int_{\alpha}^{\pi+\beta} u_{Cp}(t) d\omega t \quad (3.17)$$

Rearranging this equation, it gives

$$u_{out} = \frac{I_{Ls}}{\pi \omega C_p} \left( \sin \alpha + \sin \beta + \frac{\alpha^2}{2} - \frac{(\pi + \beta)^2}{2} + (\alpha r + \cos(\alpha))(\pi + \beta - \alpha) \right) \quad (3.18)$$

Inserting  $u_{out} = i_{out} R_L$  and  $\sin \alpha = r$  into the equation yields

$$\sin \alpha + \sin \beta + \frac{\alpha^2}{2} - \frac{(\pi + \beta)^2}{2} + (\alpha r + \cos(\alpha))(\pi + \beta - \alpha) = \pi R_L r \omega C_p \quad (3.19)$$

The fundamental-frequency impedance  $Z_{ac}$  is expressed as

$$Z_{ac} = \frac{1 - \frac{1}{2\pi} [2(\alpha - \beta) + j e^{-2j\beta} - j e^{-2j\alpha}] - \frac{2r}{\pi} (1 + e^{-j\alpha})}{j\omega C_p} \quad (3.20)$$

The solving procedure of extended fundamental AC analysis can be divided into four steps.

The first step is to solve angles  $\alpha$  and  $\beta$  from the equations (3.13) in CVM, or (3.16) and (3.19) in DVM. With the explicit angle values, the fundamental-frequency impedance  $Z_{ac}$  is calculated by (3.15) in CVM or (3.20) in DVM. Then, an AC analysis is applied to the

resonant tank to estimate the resonant current by (3.1). Finally, the output voltage is calculated with impedance  $Z_{ac}$ , resonant current, current ratio  $r$  and load  $R_L$  by (3.17).

Extended fundamental AC analysis is an accurate approach because of considering the distorted parallel-capacitor voltage. In CVM, the modelling calculation is simple. A major drawback of this approach is its dependence on the explicit numerical solution in DCM. Because equations (3.16) and (3.19) are transcendental functions, the only way to solve these equations is to calculate their numerical solutions. As the output voltage is sensitive to the angles  $\alpha$  and  $\beta$ , explicit numerical solutions are required and thus large calculation resources are needed.

Because the load  $R_L$  is also contained in the function of the equivalent AC impedance  $Z_{ac}$ , the output filter has to be ignored in the extended fundamental AC analysis. It is not a big problem for the steady-state analysis, but it brings some difficulty to extend the steady-state model towards a corresponding large-signal model.

## 3.4 Improved steady-state analysis for SPRC-LC

### 3.4.1 Equivalent circuit of SPRC-LC

Forsyth's analysis takes frequency analysis of the distorted parallel-capacitor voltage into consideration in SPRC-LC models firstly. However, the major problem of Forsyth's modelling technique is that numerical solutions are required and the output filter is eliminated. In order to deduce a more flexible and feasible steady-state model, an improved steady-state analysis is proposed.

Improved steady-state analysis does not focus on the equivalent fundamental-frequency impedance  $Z_{ac}$  depending on the load resistance. Instead, the parallel-capacitor voltage  $u_{Cp}$  is the most significant waveform in the converter. The distorted voltage  $u_{Cp}$  performs as AC

voltage in the resonant tank, while its absolute value  $|u_{Cp}|$  is considered as the DC voltage source for the filter circuit. The equivalent circuit of the SPRC is considered as two separated circuits, an AC circuit and a DC filter circuit, as illustrated in Figure 3.6.

Figure 3.6: Circuit conversion of SPRC in improved steady-state analysis

The DC input source and full bridge are considered as an equivalent AC source  $u_{AB}$ . The parallel capacitor and diodes are replaced by an equivalent impedance  $Z_{equ}(r)$  and corresponding DC source  $\overline{|u_{Cp}|}$ . These two equivalent components depend on the current ratio  $r$ . In the output filter and load circuit, the steady-state equation is described as

$$\overline{|u_{Cp}|} = u_{out} \quad (3.21)$$

Because of the band-pass characteristic of the resonant tank, the fundamental frequency waveform plays the significant role in the circuit. Similar to Extended Fundamental AC analysis, an AC analysis can be applied as,

$$I_{Ls} = \frac{U_{AB[1]}}{\left| j\omega L_s + \frac{1}{j\omega C_s} + Z_{equ} \right|} \quad (3.22)$$

The analysis of the distorted  $u_{Cp}$  waveform, including its average value, is the most significant point for the improved steady-state model. In the mathematical expression, it is described by these two components, equivalent impedance  $Z_{equ}(r)$  and corresponding DC source  $\overline{|u_{Cp}|}$ .

### 3.4.2 Description of parallel capacitor voltage

As illustrated in equation (3.10) and (3.11), the time-domain waveform of  $u_{Cp}$  is expressed in the phase range  $\alpha < \omega t < \pi + \alpha$  as following,

$$u_{Cp}(t) = \frac{I_{Ls}}{\omega C_p} (-\cos(\omega t) - \omega t r + \alpha r + \cos(\alpha)), \quad CVM \quad (3.23)$$

$$u_{Cp}(t) = \begin{cases} \frac{I_{Ls}}{\omega C_p} (-\cos(\omega t) - \omega t r + \alpha r + \cos(\alpha)), & \alpha < \omega t < \pi + \beta \\ 0, & \pi + \beta < \omega t < \pi + \alpha \end{cases}, \quad DVM \quad (3.24)$$

In order to analyse the shape of the waveform, the novel function  $f(\theta, \alpha, r)$  is defined as the expression in the bracket in (3.23) and (3.24). The normalized function  $f(\theta, \alpha, r)$  depends on only three independent parameters,  $\theta$ ,  $\alpha$  and  $r$ .

$$f(\theta, \alpha, r) = -\cos(\theta) - \theta r + \alpha r + \cos(\alpha), \quad \alpha < \omega t < \pi + \alpha, \quad CVM$$

$$f(\theta, \alpha, r) = \begin{cases} -\cos(\omega t) - \omega t r + \alpha r + \cos(\alpha), & \alpha < \omega t < \pi + \beta \\ 0, & \pi + \beta < \omega t < \pi + \alpha \end{cases}, \quad DVM \quad (3.25)$$

where  $\theta$  is the variable representing the time  $\omega t$ . The waveform of the parallel-capacitor voltage  $u_{Cp}$  can be considered as a horizontally and vertically stretched figure from this newly defined function  $f(\theta, \alpha, r)$ . Parallel-capacitor voltage  $u_{Cp}$  can be decided by three describing factors: the shape of the waveform described by  $f(\theta, \alpha, r)$ , the amplitude and the switching frequency. In other words, the shape of parallel-capacitor voltage  $u_{Cp}$  in SPRC is the same as the function  $f(\theta, \alpha, r)$ , expressed as

$$u_{Cp}(t) = \frac{I_{Ls}}{\omega C_s} f(\omega t, \alpha, r) \quad (3.26)$$

Afterwards, this newly defined function can be analysed independently. As the angle  $\theta$  represents  $\omega t$ , the shape of the waveform  $f(\theta, \alpha, r)$  actually depends on the other two inner

parameters, angle  $\alpha$  and current ratio  $r$ . In Figure 3.6, three examples of waveform with different  $\alpha$  and  $r$  are illustrated.

Figure 3.7: Waveform examples of  $f(\theta, \alpha, r)$  depending on  $\alpha$  and  $r$

The operation mode can be divided into CVM and DVM. The definition of these two operation modes are the same as extended fundamental AC analysis.

If  $(\theta, \pi + \alpha, r) = 0$ , the waveform returns to zero exactly at the end of the half cycle  $\omega t = \pi + \alpha$ , as the third figure in Figure 3.7 (c) illustrates. It is operated in CVM. The expression of the angle  $\alpha$  is obtained by two equations.

$$f(\theta, \alpha, r) = 0, \quad f(\theta, \pi + \alpha, r) = 0 \quad (3.27)$$

If  $f(\theta - \Delta\theta, \pi + \alpha, r) = 0$ , the dependent variable returns to zero before the end of the half cycle, as illustrated in Figure 3.7 (a), it is operated in DVM. Here,  $\Delta\theta$  represents a small positive angle difference. The expression of the angle  $\alpha$  is obtained from time point  $\theta = \alpha$ ,

$$f(\theta, \alpha, r) = 0 \quad (3.28)$$

The transition between CVM and DVM mentioned in [FWM03] and [Cao14] is also correct, but the transition condition can be given more strictly as

$$r_c = \frac{2}{\sqrt{\pi^2 + 4}} \approx 0.5370, \quad \alpha_c = \arcsin\left(\frac{2}{\sqrt{\pi^2 + 4}}\right) \approx 0.5669 \quad (3.29)$$

Combining these two modes, the relationship of angle  $\alpha$  and current ratio  $r$  is given in formula (3.30) and illustrated in Figure 3.8(a). With this relationship of  $\alpha$  and  $r$ , the shape of function waveform has only one freedom degree. It can be described by one parameter, e.g. by the current ratio  $r$ .

$$\alpha(r) = \begin{cases} \arcsin(r), & \text{if } r \geq r_c, \text{DVM} \\ \arccos\left(\frac{\pi r}{2}\right), & \text{if } r < r_c, \text{CVM} \end{cases} \quad (3.30)$$

Figure 3.8: (a) Relationship between angle  $\alpha$  and current ratio  $r$  and (b) series of curves depending on current ratio  $r$

Figure 3.8(b) gives a series of curves with different current ratio  $r$ . In Figure 3.8(a), the trajectory of the angle  $\alpha$  decreases from  $\pi/2$  to  $\arcsin(r_c)$  in CVM, in the range  $0 < r < r_c$ . Then it increases from  $\arcsin(r_c)$  to  $\pi/2$  in DVM in the range  $r_c < r < 1$ , which can also be observed in Figure 3.8(b). Those shapes of curves vary from an approximate sinusoidal waveform ( $r = 0.1$ ) to a severely distorted waveform ( $r = 0.9$ ) when current ratio  $r$  varies.

After all analysis above, the shape of parallel-capacitor voltage  $u_{Cp}$  can be described by the function  $f(\theta, r) = f(\theta, \alpha(r), r)$ . There is only one parameter deciding the shape, which makes the following AC analysis possible.

### 3.4.3 Three coefficients and expression of improved steady state model

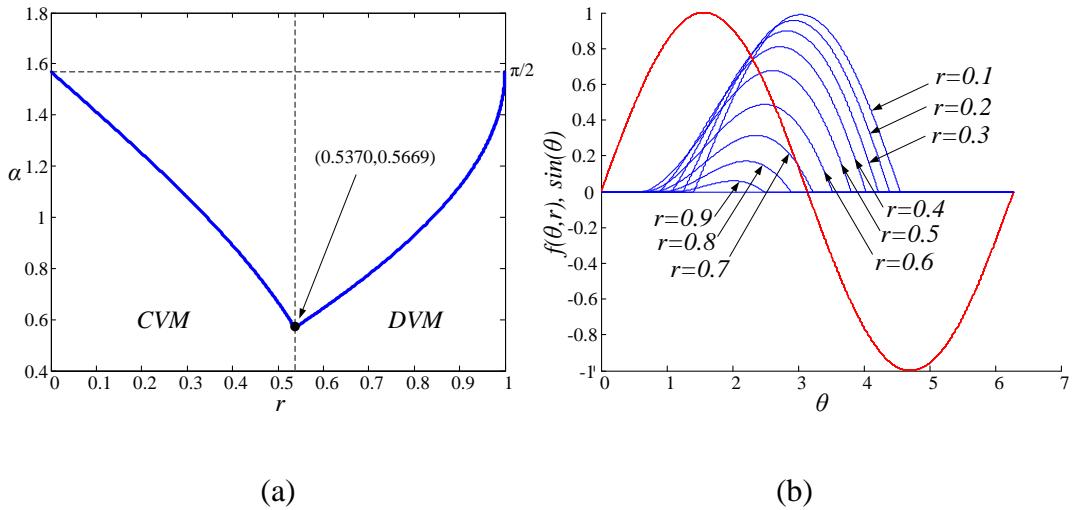

Because the parallel-capacitor voltage  $u_{Cp}$  shares the same shape as these series of curves, the application of frequency analysis and Fourier transforms are possible. With a group of curves depending on different current ratios  $r$ , the Fourier transforms give a series of coefficients for describing the curves. Considering simplicity of the steady-state model, only the fundamental-frequency Fourier coefficients are used in improved steady state model.

The fundamental frequency Fourier coefficients,  $F_{uCp,s}(r)$  and  $F_{uCp,c}(r)$ , and average coefficient  $F_{uCp,a}(r)$  are given by the following equations. The subscript, ‘s’ denotes the sine part of the fundamental-frequency coefficients, ‘c’ denotes the cosine part of the fundamental-frequency coefficients and ‘a’ denotes the average coefficients. These three coefficients are the zero-order and first-order coefficients in a Fourier series.

$$F_{uCp,a}(r) = \frac{1}{\pi} \int_{\alpha}^{\pi+\alpha} f(\theta, \alpha, r) d\theta \quad (3.31)$$

$$F_{uCp,s}(r) = \frac{2}{\pi} \int_{\alpha}^{\pi+\alpha} f(\theta, \alpha, r) \sin(\theta) d\theta \quad (3.32)$$

$$F_{uCp,c}(r) = \frac{2}{\pi} \int_{\alpha}^{\pi+\alpha} f(\theta, \alpha, r) \cos(\theta) d\theta \quad (3.33)$$

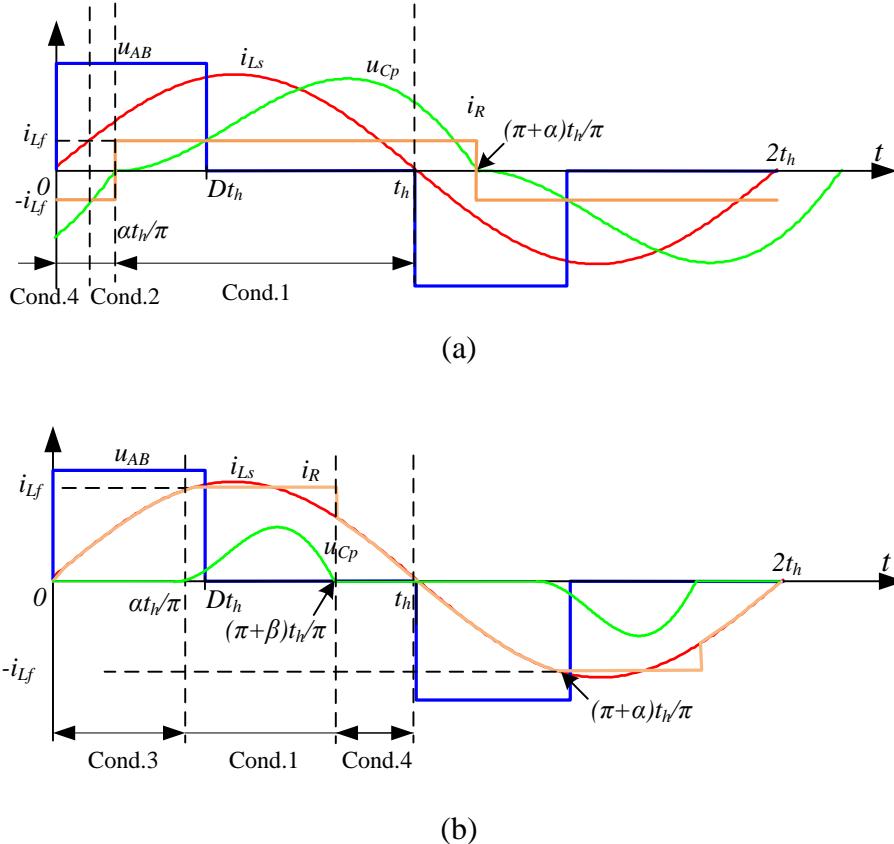

Figure 3.9: Three coefficients depending on current ratio  $r$

As the curves is decided by the only parameter  $r$ , these coefficients are depending on this parameter, current ratio  $r$ . The coefficients can be considered as three functions of the current ratio  $r$ , as illustrated in Figure 3.9. With three coefficients, the formulas (3.34) and (3.35) approximately describe the parallel-capacitor voltage  $u_{Cp}$  and its rectified value  $|u_{Cp}|$ .

$$u_{Cp} = \frac{I_{Ls}}{\omega C_p} (F_{uCp,s}(r) \sin(\omega t) + F_{uCp,c}(r) \cos(\omega t)) \quad (3.34)$$

$$|u_{Cp}| = \frac{I_{Ls}}{\omega C_p} F_{uCp,a}(r) \quad (3.35)$$

Here, the coefficients  $F_{uCp,s}(r)$  and  $F_{uCp,c}(r)$  describe the fundamental harmonic of the parallel-capacitor voltage  $u_{Cp}$ . The coefficient  $F_{uCp,a}(r)$  describes the equivalent DC voltage of the distorted voltage  $u_{Cp}$ . Because  $F_{uCp,s}(r)$  is always positive and  $F_{uCp,c}(r)$  is always negative, the equivalent impedance  $Z_{equ}(r)$  can be considered as a connection of resistor and capacitor in the real circuit.

Therefore, the AC equivalent impedance  $Z_{equ}(r)$  is a complex function depending on the real value  $r$ . It can be expressed as

$$Z_{equ}(r) = \frac{1}{\omega C_p} (F_{uCp,s}(r) + jF_{uCp,c}(r)) \quad (3.36)$$

These coefficients are functions depending on only one variable, the current ratio. They are not directly related to the components' parameters of the electrical circuit. These coefficients are common method for the SPRC-LC topology with different parameters and operation points.

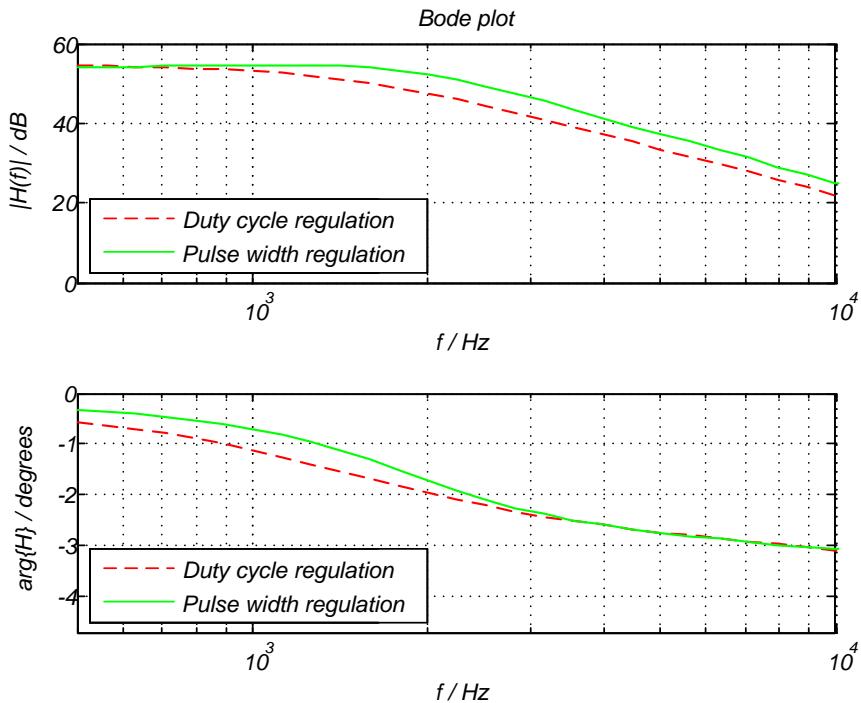

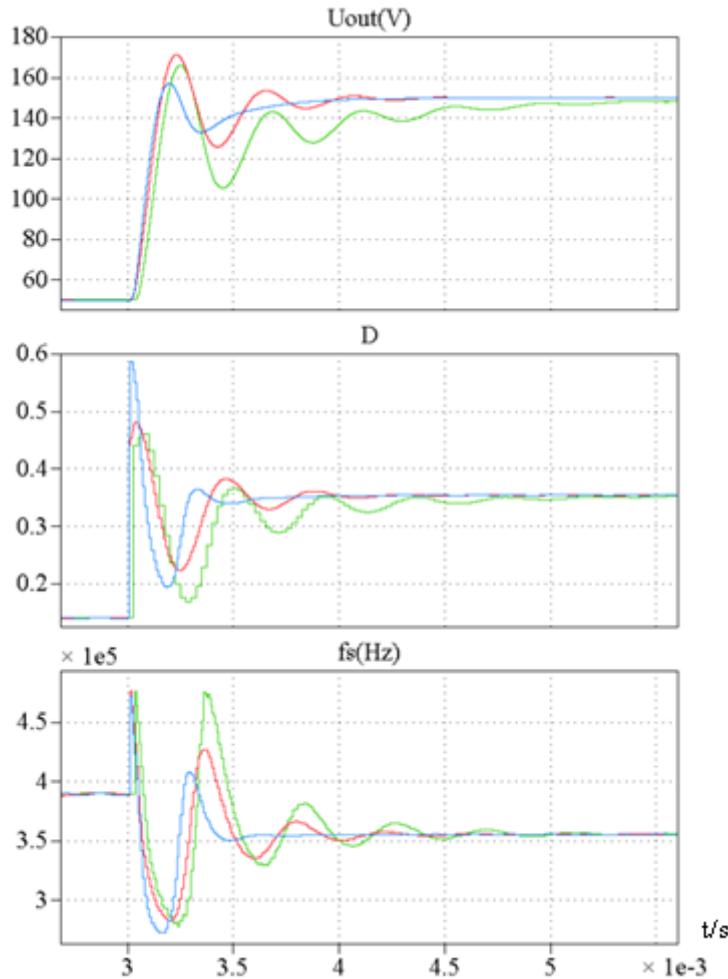

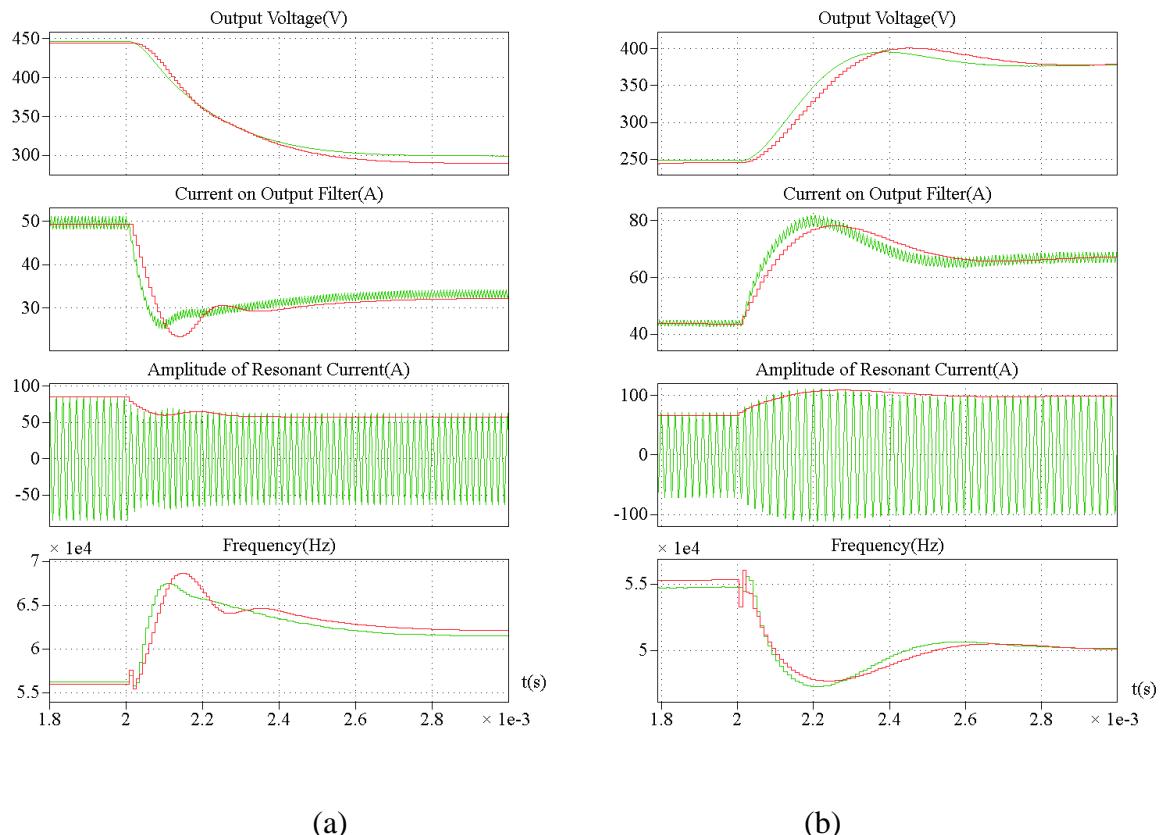

By inserting (3.35) and (3.36) to the model of SPRC, the improved steady state analysis of SPRC-LC is proposed. The equivalent circuit of the SPRC is illustrated in Figure 3.10. As the functions of current ratio  $r$ , the impedance  $Z_{equ}$  and DC voltage  $|u_{Cp}|$  is the mathematical approach for distorted voltage  $u_{Cp}$ .