GUARANTEEING PROPERTIES OF

RECONFIGURABLE HARDWARE CIRCUITS WITH

PROOF-CARRYING HARDWARE

DISSERTATION

A thesis submitted to the

FACULTY FOR COMPUTER SCIENCE, ELECTRICAL ENGINEERING AND

MATHEMATICS

of

PADERBORN UNIVERSITY

in partial fulfillment of the requirements

for the degree of *Dr. rer. nat.*

by

TOBIAS WIERSEMA

Paderborn, Germany

Date of submission: May 2021

**SUPERVISOR:**

Prof. Dr. Marco Platzner

**REVIEWERS:**

Prof. Dr. Marco Platzner

Prof. Dr. Heike Wehrheim

Prof. Dr. David Andrews

**ORAL EXAMINATION COMMITTEE:**

Prof. Dr. Marco Platzner

Prof. Dr. Heike Wehrheim

Prof. Dr. David Andrews

Prof. Dr. Friedhelm Meyer auf der Heide

Prof. Dr. Juraj Somorovsky

**DATE OF SUBMISSION:**

May 2021

## ABSTRACT

---

Previous research in proof-carrying hardware has established the feasibility and utility of the approach, and provided a concrete solution for employing it for the certification of functional equivalence checking against a specification, but fell short in connecting it to state-of-the-art formal verification insights, methods and tools. Due to the immense complexity of modern circuits, and verification challenges such as the state explosion problem for sequential circuits, this restriction of readily-available verification solutions severely limited the applicability of the approach in wider contexts.

This thesis closes the gap between the PCH approach and current advances in formal hardware verification, provides methods and tools to express and certify a wide range of circuit properties, both functional and non-functional, and presents for the first time prototypes in which circuits that are implemented on actual reconfigurable hardware are verified with PCH methods. Using these results, designers can now apply PCH to establish trust in more complex circuits, by using more diverse properties which they can express using modern, efficient property specification techniques.

## ZUSAMMENFASSUNG

---

Die bisherige Forschung zu Proof-Carrying Hardware (PCH) hat dessen Machbarkeit und Nützlichkeit gezeigt und einen Ansatz zur Zertifizierung der funktionalen Äquivalenz zu einer Spezifikation geliefert, jedoch ohne PCH mit aktuellen Erkenntnissen, Methoden oder Werkzeugen formaler Hardwareverifikation zu verknüpfen. Aufgrund der Komplexität moderner Schaltungen und Verifikationsherausforderungen wie der Zustandsexplosion bei sequentiellen Schaltungen, limitiert diese Einschränkung sofort verfügbarer Verifikationslösungen die Anwendbarkeit des Ansatzes in einem größeren Kontext signifikant.

Diese Dissertation schließt die Lücke zwischen PCH und modernen Entwicklungen in der Schaltungsverifikation und stellt Methoden und Werkzeuge zur Verfügung, welche die Zertifizierung einer großen Bandbreite von Schaltungseigenschaften ermöglicht; sowohl funktionale, als auch nicht-funktionale. Überdies werden erstmals Prototypen vorgestellt in welchen Schaltungen mittels PCH verifiziert werden, die auf tatsächlicher rekonfigurierbarer Hardware realisiert sind. Dank dieser Ergebnisse können Entwickler PCH zur Herstellung von Vertrauen in weit komplexere Schaltungen verwenden, unter Zuhilfenahme einer größeren Vielfalt von Eigenschaften, welche durch moderne, effiziente Spezifikationstechniken ausgedrückt werden können.

## PUBLICATIONS

---

Some ideas and figures have appeared previously in the following publications:

- [1] Tobias Wiersema. "Schedulding Support for Heterogeneous Hardware Accelerators under Linux." English. Master's Thesis. Paderborn University, Nov. 2010. 60 pp.

- [2] Tobias Beisel, Tobias Wiersema, Christian Plessl, and André Brinkmann. "Cooperative Multitasking for Heterogeneous Accelerators in the Linux Completely Fair Scheduler." In: *22nd International Conference on Application-specific Systems, Architectures and Processors*. ASAP 2011 (Santa Monica, CA, USA, Sept. 11–14, 2011). Ed. by Joseph R. Cavallaro, Milos D. Ercegovac, Frank Hannig, Paolo Ienne, Earl E. Swartzlander Jr., and Alexandre F. Tenca. IEEE, 2011, pp. 223–226. DOI: [10.1109/ASAP.2011.6043273](https://doi.org/10.1109/ASAP.2011.6043273).

- [3] Tobias Beisel, Tobias Wiersema, Christian Plessl, and André Brinkmann. "Programming and Scheduling Model for Supporting Heterogeneous Accelerators in Linux." In: *Proceedings of the Third Workshop on Computer Architecture and Operating System Co-design*. CAOS 2012 (Paris, France, Jan. 23–25, 2012). Jan. 2012, pp. 28–36. URL: [http://projects.csail.mit.edu/caos/caos\\_2012.pdf](http://projects.csail.mit.edu/caos/caos_2012.pdf).

- [4] Marie-Christine Jakobs, Marco Platzner, Tobias Wiersema, and Heike Wehrheim. "Integrating Software and Hardware Verification." In: *11th International Conference on Integrated Formal Methods*. iFM 2014 (Bertinoro, Italy, Sept. 9–11, 2014). Ed. by Elvira Albert and Emil Sekerinski. Vol. 8739. Lecture Notes in Computer Science. Springer, 2014, pp. 307–322. DOI: [10.1007/978-3-319-10181-1\\_19](https://doi.org/10.1007/978-3-319-10181-1_19).

- [5] Tobias Wiersema, Arne Bockhorn, and Marco Platzner. "Embedding FPGA Overlays into Configurable Systems-on-Chip: ReconOS meets ZUMA." In: *2014 International Conference on ReConfigurable Computing and FPGAs*. ReConFig'14 (Cancun, Mexico, Dec. 8–10, 2014). IEEE, Dec. 2014, pp. 1–6. DOI: [10.1109/ReConfig.2014.7032514](https://doi.org/10.1109/ReConfig.2014.7032514).

- [6] Tobias Wiersema, Stephanie Drzevitzky, and Marco Platzner. "Memory Security in Reconfigurable Computers: Combining Formal Verification with Monitoring." In: *2014 International Conference on Field-Programmable Technology*. FPT 2014 (Shanghai, China, Dec. 10–12, 2014). IEEE, Dec. 2014, pp. 167–174. DOI: [10.1109/FPT.2014.7082771](https://doi.org/10.1109/FPT.2014.7082771).

- [7] Tobias Wiersema, Sen Wu, and Marco Platzner. "On-The-Fly Verification of Reconfigurable Image Processing Modules Based on a Proof-Carrying Hardware Approach." In: *Applied Reconfigurable Computing*. 11th International Symposium, ARC 2015 (Bochum, Germany, Apr. 15–17, 2015). Ed. by Kentaro Sano, Dimitrios Soudris, Michael Hübner, and Pedro C. Diniz. Vol. 9040. Lecture Notes in Computing Science. Springer, 2015, pp. 377–384. DOI: [10.1007/978-3-319-16214-0\\_32](https://doi.org/10.1007/978-3-319-16214-0_32).

- [8] Tobias Wiersema, Arne Bockhorn, and Marco Platzner. "An Architecture and Design Tool Flow for Embedding a Virtual FPGA into a Reconfigurable System-on-Chip." In: *Computers and Electrical Engineering* 55 (2016). Ed. by Manu Malek, pp. 112–122. DOI: [10.1016/j.compeleceng.2016.04.005](https://doi.org/10.1016/j.compeleceng.2016.04.005).

- [9] Tobias Wiersema and Marco Platzner. "Verifying worst-case completion times for reconfigurable hardware modules using proof-carrying hardware." In: *11th International Symposium on Reconfigurable Communication-centric Systems-on-Chip*. ReCoSoC 2016 (Tallinn, Estonia, June 27–29, 2016). IEEE, 2016, pp. 1–8. DOI: [10.1109/ReCoSoC.2016.7533910](https://doi.org/10.1109/ReCoSoC.2016.7533910).

- [10] Tobias Isenberg, Marco Platzner, Heike Wehrheim, and Tobias Wiersema. "Proof-Carrying Hardware via Inductive Invariants." In: *Transactions on Design Automation of Electronic Systems*. TODAES 22.4 (July 2017), 61:1–61:23. DOI: [10.1145/3054743](https://doi.org/10.1145/3054743).

- [11] Qazi Arbab Ahmed, Tobias Wiersema, and Marco Platzner. "Proof-Carrying Hardware versus the Stealthy Malicious LUT Hardware Trojan." In: *Applied Reconfigurable Computing*. 15th International Symposium, ARC 2019 (Darmstadt, Germany, Apr. 9–11, 2019). Ed. by Christian Hochberger, Brent Nelson, Andreas Koch, Roger Woods, and Pedro Diniz. Vol. 11444. Lecture Notes in Computer Science. Springer, 2019, pp. 127–136. DOI: [10.1007/978-3-030-17227-5\\_10](https://doi.org/10.1007/978-3-030-17227-5_10).

- [12] Linus Witschen, Tobias Wiersema, and Marco Platzner. "Making the Case for Proof-carrying Approximate Circuits." 4th Workshop on Approximate Computing. WAPCO 2018 (Manchester, England, Jan. 22, 2018). Workshop without proceedings. 2018. URL: <https://api.semanticscholar.org/CorpusID:52228901>.

- [13] Linus Witschen, Tobias Wiersema, Hassan Ghasemzadeh Mohammadi, Muhammad Awais, and Marco Platzner. "CIRCA: Towards a Modular and Extensible Framework for Approximate Circuit Generation." Third Workshop on Approximate Computing. AxC 2018 (Bremen, Germany, May 31–June 1, 2018). Workshop without proceedings. 2018.

- [14] Linus Witschen, Muhammad Awais, Hassan Ghasemzadeh Mohammadi, Tobias Wiersema, and Marco Platzner. "CIRCA: Towards a Modular and Extensible Framework for Approximate Circuit Generation." In: *Microelectronics Reliability. MER* 99 (2019), pp. 277–290. doi: [10.1016/j.microrel.2019.04.003](https://doi.org/10.1016/j.microrel.2019.04.003).

- [15] Linus Witschen, Tobias Wiersema, and Marco Platzner. "Proof-carrying Approximate Circuits." In: *Transactions on Very Large Scale Integration (VLSI) Systems. TVLSI* 28 (9 2020), pp. 2084–2088. doi: [10.1109/TVLSI.2020.3008061](https://doi.org/10.1109/TVLSI.2020.3008061).

- [16] Qazi Arbab Ahmed, Tobias Wiersema, and Marco Platzner. "Malicious Routing: Circumventing Bitstream-level Verification for FPGAs." In: *Proceedings of the Design, Automation & Test in Europe Conference & Exhibition. DATE 2021* (Virtual Conference, Feb. 1–5, 2021). IEEE, Feb. 2021, pp. 1490–1495.

- [17] Linus Witschen, Tobias Wiersema, Masood Raeisi Nafchi, Arne Bockhorn, and Marco Platzner. "Timing Optimization for Virtual FPGA Configurations." In: *Applied Reconfigurable Computing. Architectures, Tools, and Applications. 17th International Symposium, ARC 2021* (Virtual Conference, June 29–30, 2021). Lecture Notes in Computing Science. Springer, 2021.

*Not by might,

nor by power,

but by my Spirit,

says the Lord of hosts.*

— Zechariah 4:6

## ACKNOWLEDGMENTS

---

Like any sizable project, the realization of this thesis has only been possible thanks to the help and support of many incredible people that I have been blessed with on this journey. I thus want to humbly express my thanks to some of these people in particular in the next lines, and to assure all of my colleagues, friends and family that remain unmentioned that I feel very grateful for their support nonetheless.

First I would like to thank Marco Platzner for his guidance and invaluable support throughout the entire process, for always being considerate, fair, and practical in everyday matters as well as the grand strategic choices. Drawing from your experience and example has allowed me not only to finish this project, but also to learn important lessons about leadership that values the human in the process. I would furthermore like to thank him, Heike Wehrheim, and David Andrews for the time and effort they spent to review this thesis, as well as all members of the committee for evaluating my work.

I am very grateful for the people that I got to work with over the duration of the process in the CEG, who made working there a lighthearted experience. A special thanks to my office buddies, Tobias Beisel, Server Kasap, Andreas Agne, and Muhammad Awais, that they endured my ramblings and taught me Urdu. I would also like to thank the ones I got to work with closely, Christian Plessl, Alexander Boschmann, Achim Lösch, Marie-Christine Jakobs, Linus Witschen, and Qazi Ahmed, for their professionalism and support. A special thanks also to Paraskewi Antoniou-Dahmann and Jennifer Lohse for their patience and huge support in the plentiful administrative issues that arose. My thanks also goes to all the unmentioned colleagues, cake bakers, the PC2 and its staff for the compute cluster access and support, and the students whose theses or work supported mine, with Arne Bockhorn in particular, since his dedication and commitment surpassed his contractual obligations by far, which has helped me tremendously. I am also grateful for the support of the staff of the CRC 901 "On-the-Fly-Computing", especially Ulf Schröder, Marion Hucke, and the K-Team that I was part of, as well as the DFG for their financial support in the form of the grant of said project, and also to the university for facilitating the realization of the CRC and providing the infrastructure.

Last but foremost I would like to thank my families for their unwavering support, both, the one I was born into and that raised me and the one that I married into. Special thanks to my wife Iris and children Eliane and Simeon for their enduring patience of my absent periods of plentiful work, as well as their abundant love and the warm home and joy they have provided me with to counterbalance said efforts. Not even a year of continuous homeoffice could lessen our love for each other and I pray that it will remain this way for a long time.

## CONTENTS

---

|          |                                                    |            |

|----------|----------------------------------------------------|------------|

| <b>1</b> | <b>INTRODUCTION</b>                                | <b>1</b>   |

| 1.1      | Motivation . . . . .                               | 1          |

| 1.2      | Thesis Contributions . . . . .                     | 5          |

| 1.3      | Thesis Organization . . . . .                      | 5          |

| <b>2</b> | <b>BACKGROUND</b>                                  | <b>7</b>   |

| 2.1      | Reconfigurable Hardware . . . . .                  | 7          |

| 2.2      | Hardware verification . . . . .                    | 16         |

| 2.3      | Proof-carrying Hardware . . . . .                  | 38         |

| 2.4      | Tools and Platforms . . . . .                      | 45         |

| <b>3</b> | <b>REALIZING BITSTREAM-LEVEL PCH</b>               | <b>53</b>  |

| 3.1      | Proof-carrying Reconfigurable Hardware . . . . .   | 53         |

| 3.2      | Generalized Bitstream-level PCH Flow . . . . .     | 61         |

| 3.3      | Conclusion . . . . .                               | 65         |

| <b>4</b> | <b>VIRTUAL FIELD-PROGRAMMABLE GATE ARRAYS</b>      | <b>67</b>  |

| 4.1      | Virtualizing FPGAs . . . . .                       | 68         |

| 4.2      | Related work . . . . .                             | 71         |

| 4.3      | Extending ZUMA . . . . .                           | 76         |

| 4.4      | ZUMA-based PCH Evaluation Platform . . . . .       | 95         |

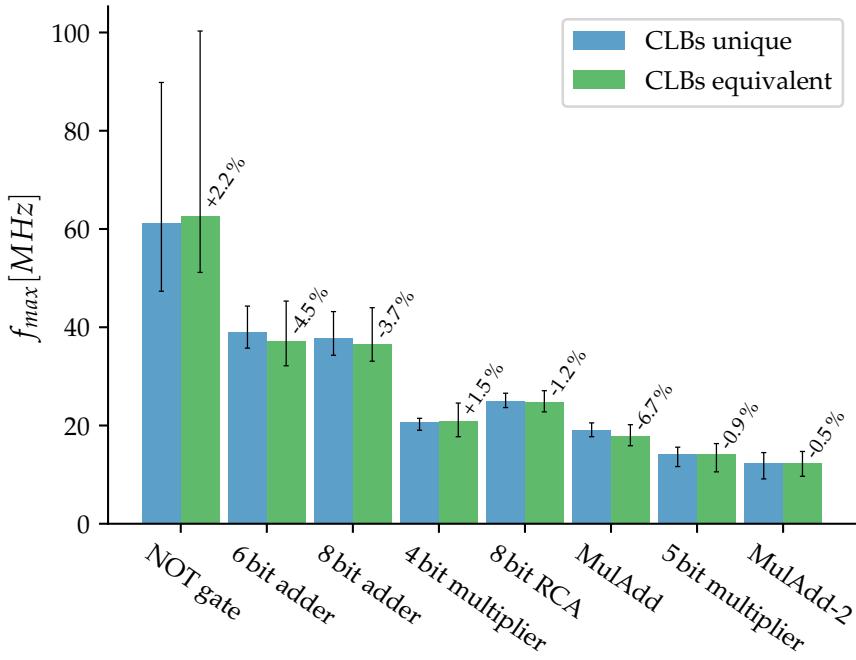

| 4.5      | Timing Analysis and Optimization . . . . .         | 104        |

| 4.6      | Conclusion . . . . .                               | 120        |

| <b>5</b> | <b>PROVING PROPERTIES WITH PCH</b>                 | <b>121</b> |

| 5.1      | Related Work . . . . .                             | 121        |

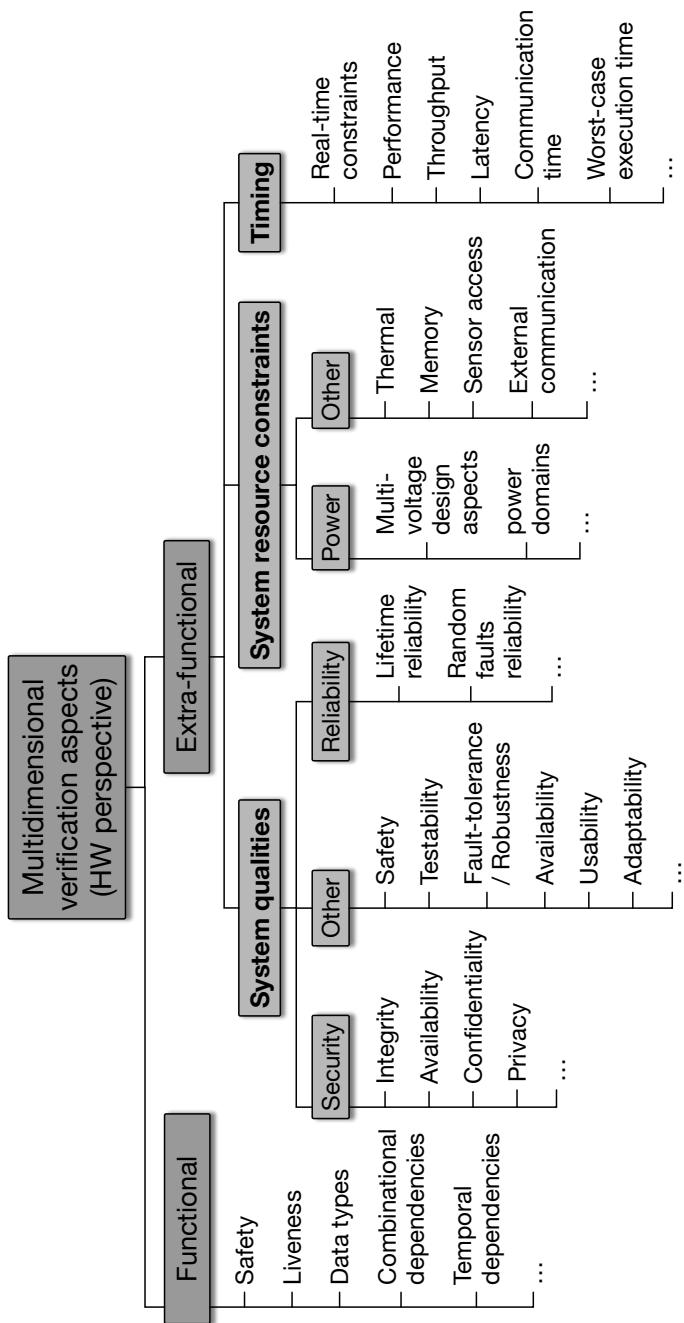

| 5.2      | Property classification . . . . .                  | 123        |

| 5.3      | Sequential Property Checking . . . . .             | 128        |

| 5.4      | Monitor-based Property Checking . . . . .          | 150        |

| 5.5      | Scalability . . . . .                              | 163        |

| 5.6      | Conclusion . . . . .                               | 168        |

| <b>6</b> | <b>NON-FUNCTIONAL PROPERTY CHECKING</b>            | <b>171</b> |

| 6.1      | Worst-case Completion Time . . . . .               | 172        |

| 6.2      | Information Flow Security . . . . .                | 185        |

| 6.3      | Approximation Quality . . . . .                    | 207        |

| 6.4      | General Self-Composition Miters . . . . .          | 222        |

| 6.5      | Conclusion . . . . .                               | 225        |

| <b>7</b> | <b>PCH DEMONSTRATORS</b>                           | <b>227</b> |

| 7.1      | Demonstrator 1: Certified Image Filters . . . . .  | 227        |

| 7.2      | Demonstrator 2: Certified PSL Guard Dogs . . . . . | 234        |

| <b>8</b> | <b>CONCLUSION</b>                                  | <b>243</b> |

| <b>9</b> | <b>OUTLOOK</b>                                     | <b>245</b> |

| <b>A</b> | <b>TABLES</b>                                      | <b>247</b> |

|          | <b>BIBLIOGRAPHY</b>                                | <b>271</b> |

## LIST OF FIGURES

---

|             |                                                  |     |

|-------------|--------------------------------------------------|-----|

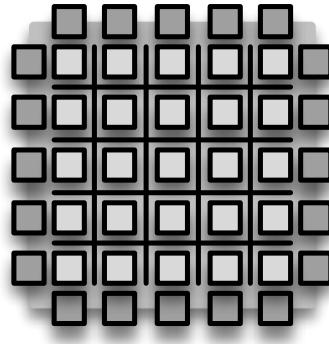

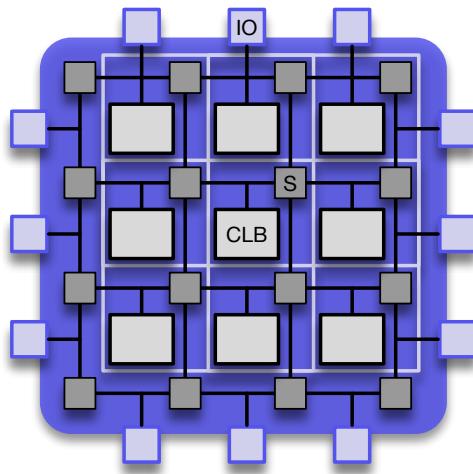

| Figure 2.1  | Abstract FPGA overview. . . . .                  | 11  |

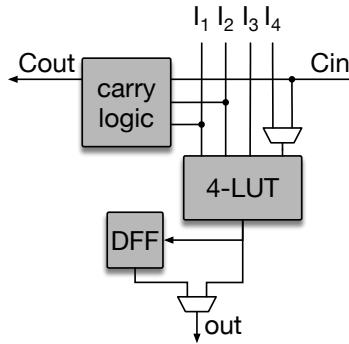

| Figure 2.2  | BLE layout. . . . .                              | 12  |

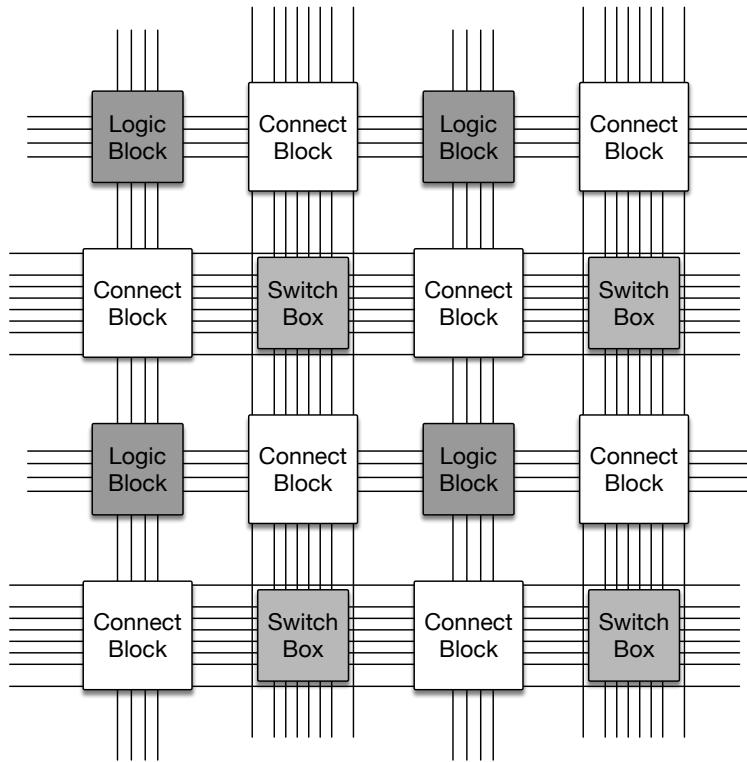

| Figure 2.3  | Island-style FPGA structure details. . . . .     | 13  |

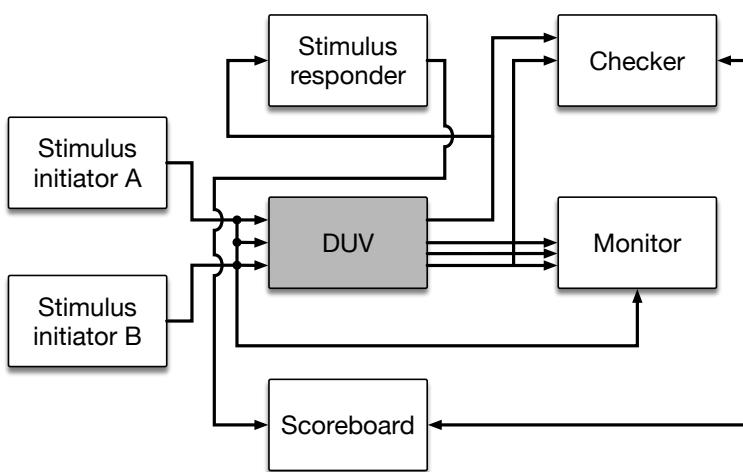

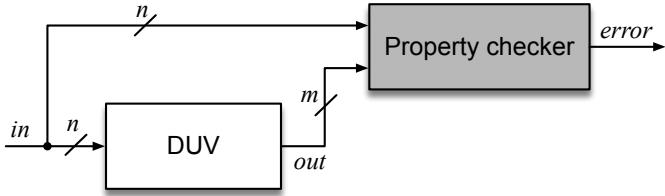

| Figure 2.4  | Hardware verification environment. . . . .       | 22  |

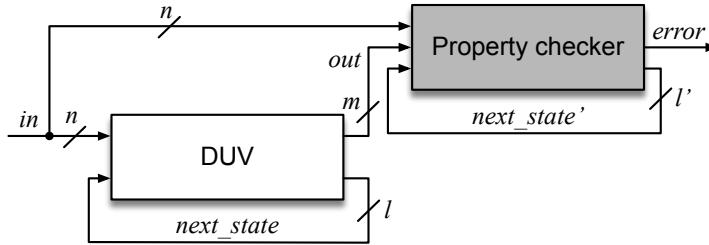

| Figure 2.5  | Formal Hardware verification environment. . .    | 25  |

| Figure 2.6  | Formal Hardware verification flow. . . . .       | 26  |

| Figure 2.7  | Boolean Equivalence Miter. . . . .               | 27  |

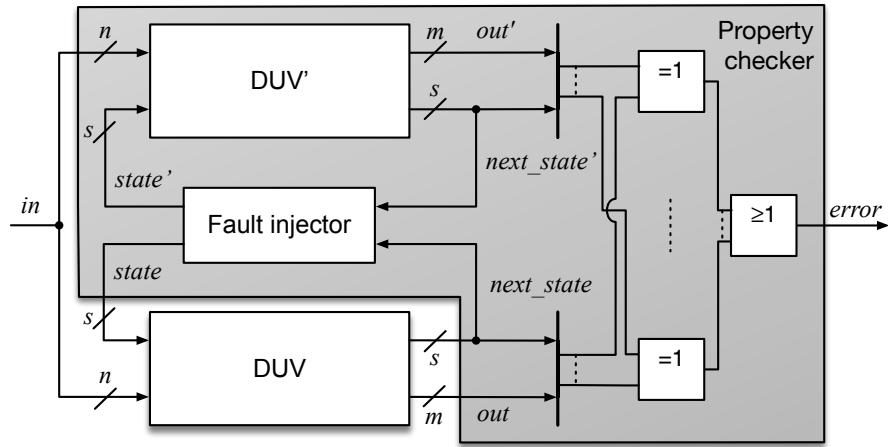

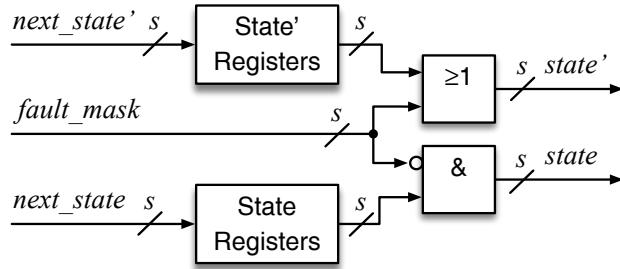

| Figure 2.8  | Property verification circuits. . . . .          | 28  |

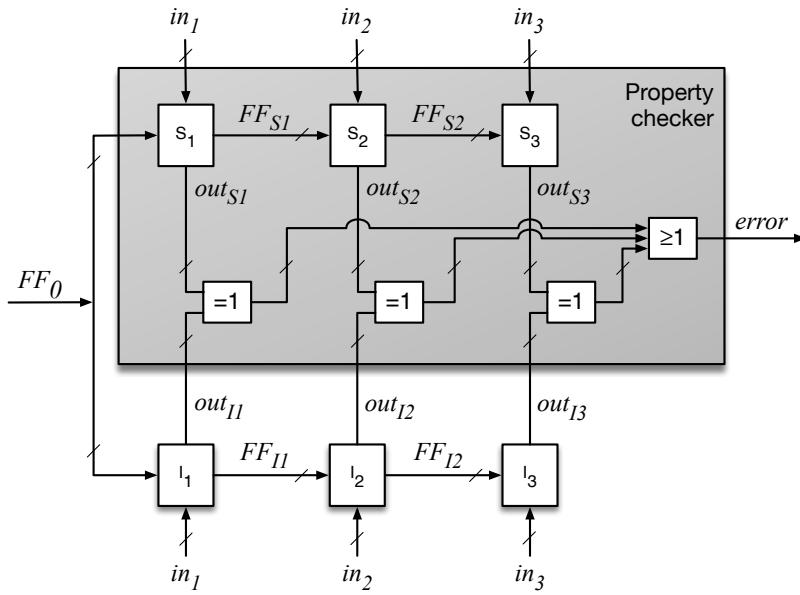

| Figure 2.9  | Unrolled sequential PVC. . . . .                 | 31  |

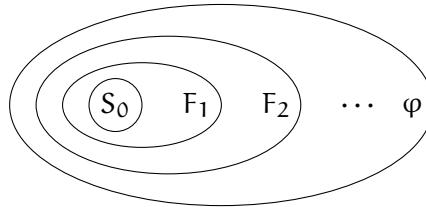

| Figure 2.10 | PDR frames. . . . .                              | 33  |

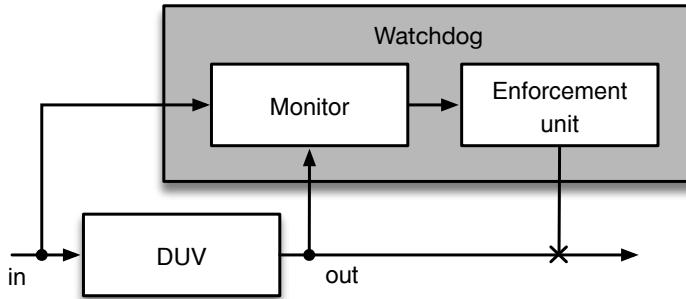

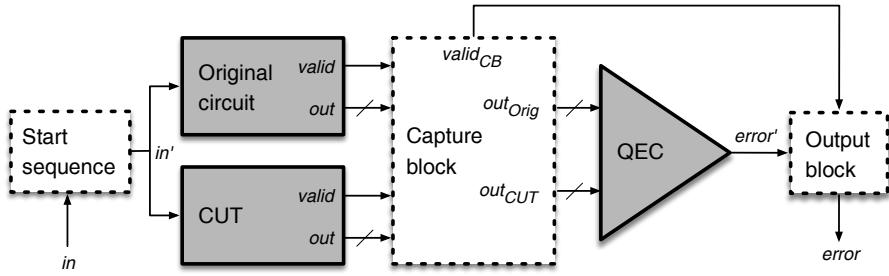

| Figure 2.11 | Runtime verification PVC. . . . .                | 35  |

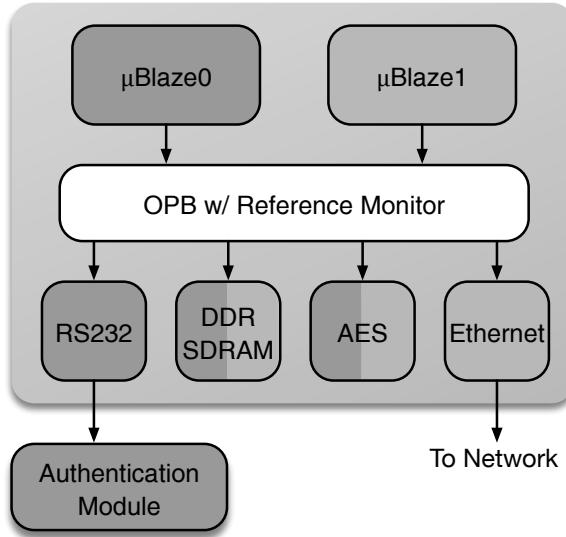

| Figure 2.12 | Memory reference monitor example. . . . .        | 36  |

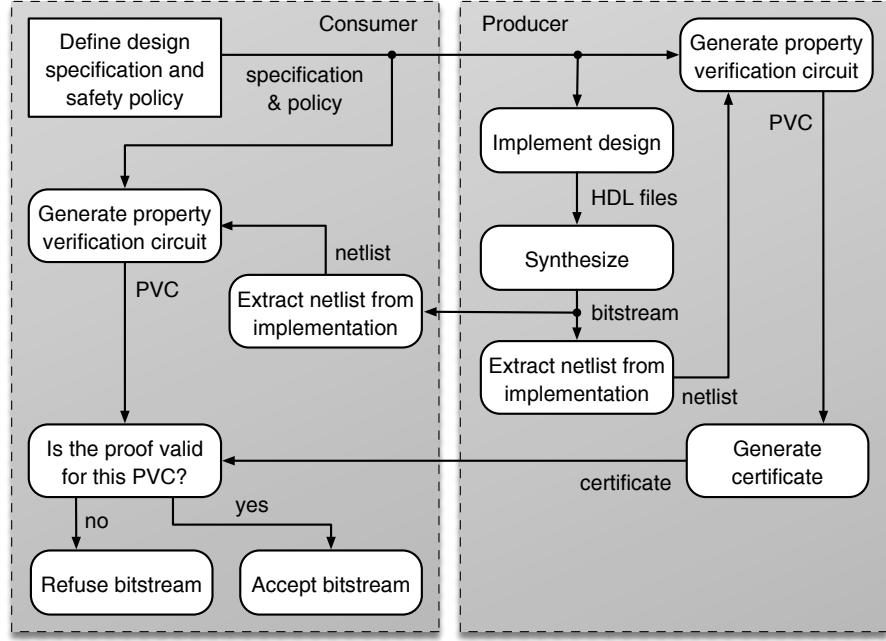

| Figure 2.13 | Abstract PCH flow. . . . .                       | 40  |

| Figure 2.14 | Combinational miter PVC. . . . .                 | 42  |

| Figure 2.15 | Sequential miter PVC. . . . .                    | 43  |

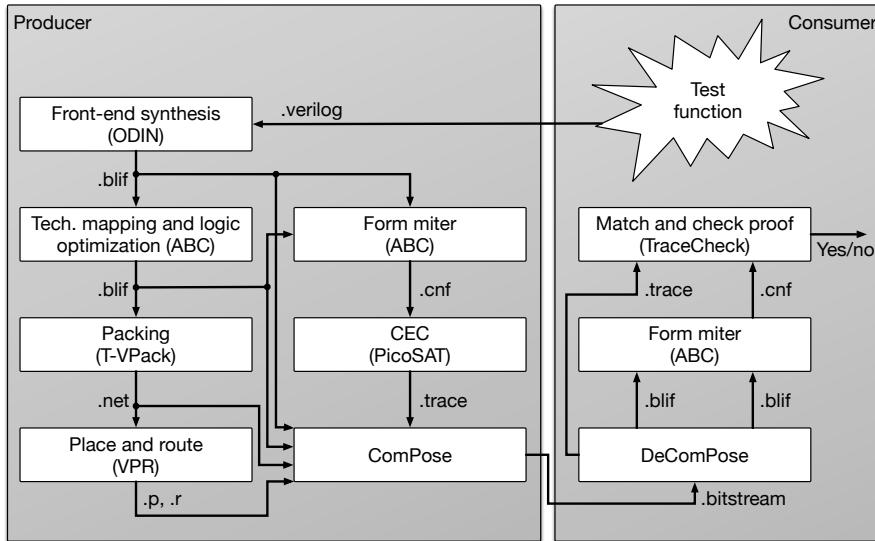

| Figure 2.16 | First prototypical PCH flow. . . . .             | 43  |

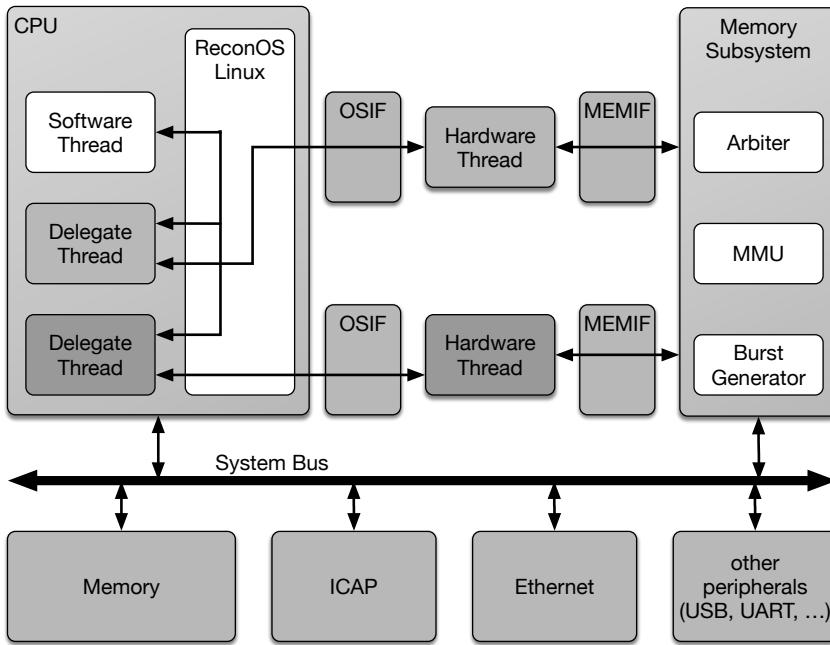

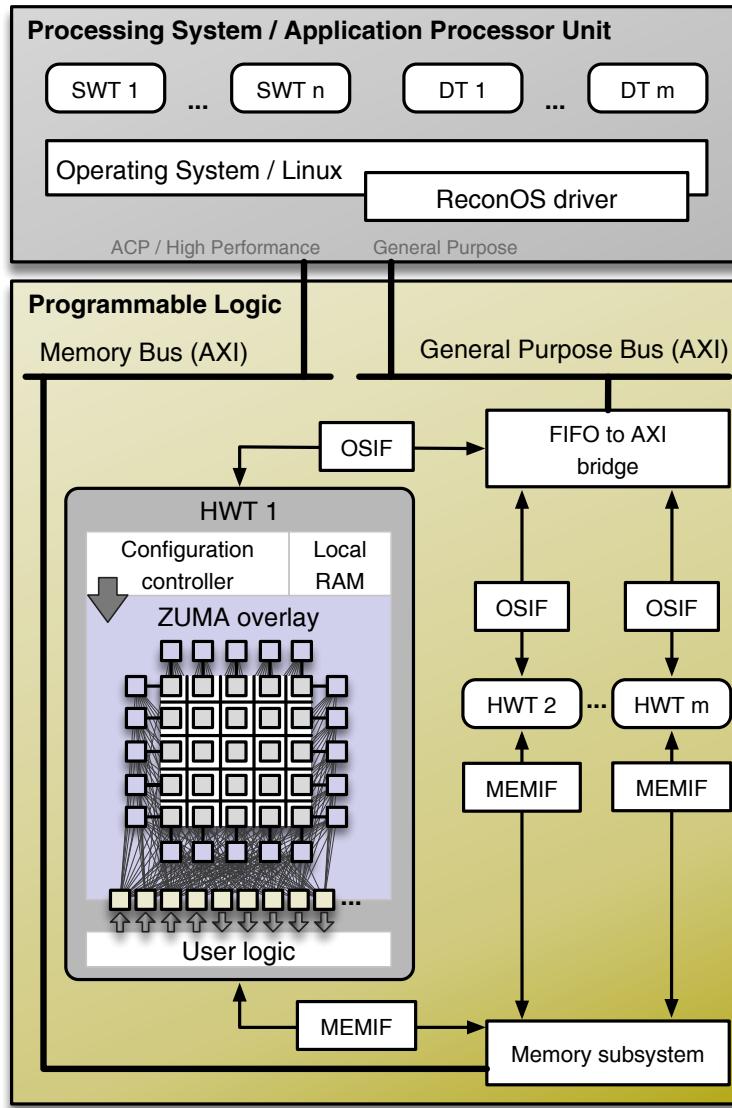

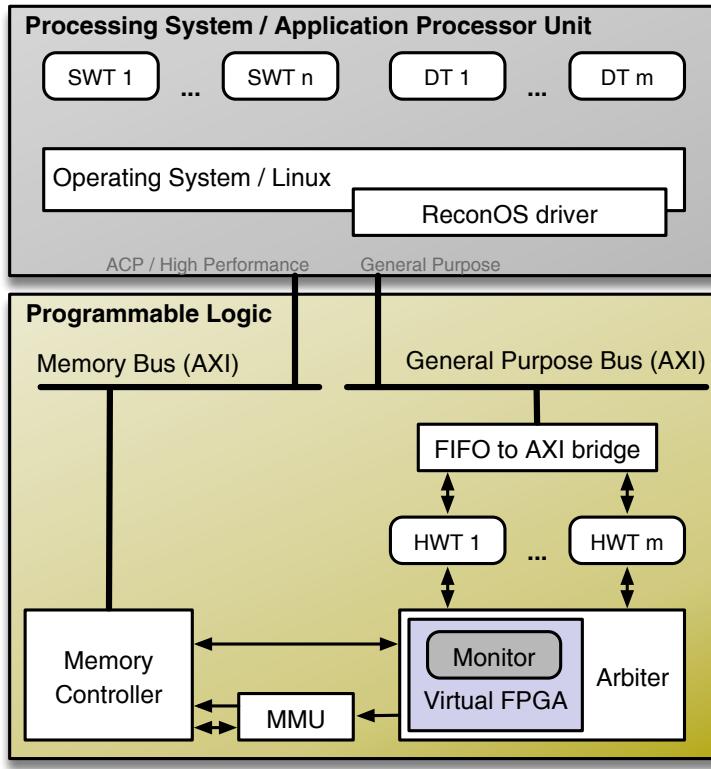

| Figure 2.17 | The ReconOS architecture. . . . .                | 51  |

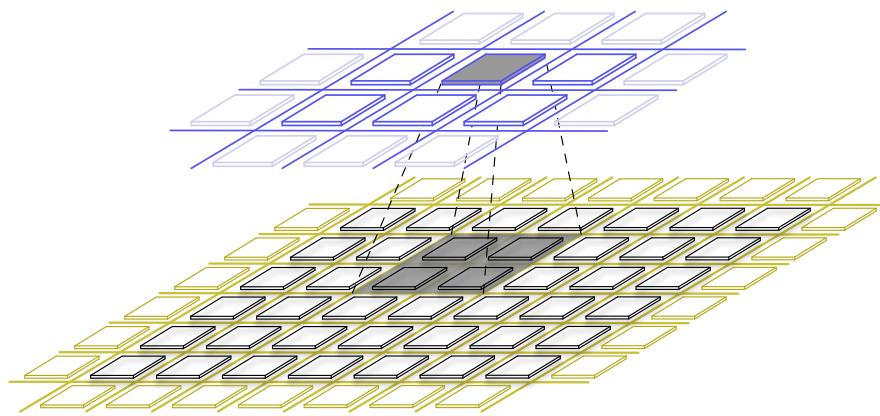

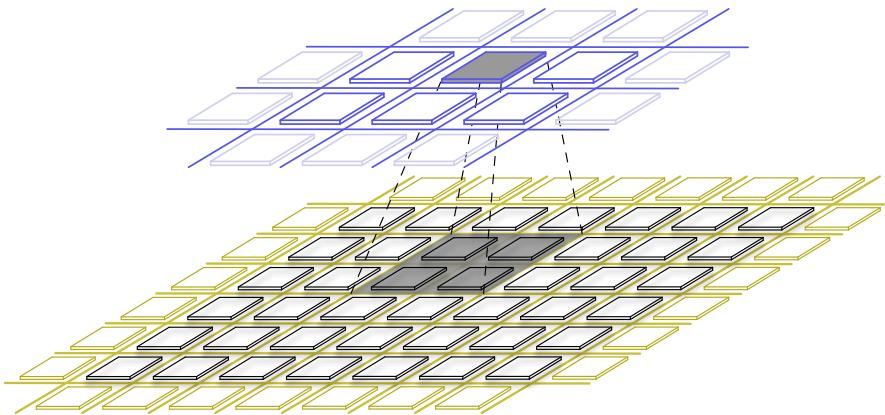

| Figure 3.1  | Virtual and physical FPGA layers. . . . .        | 58  |

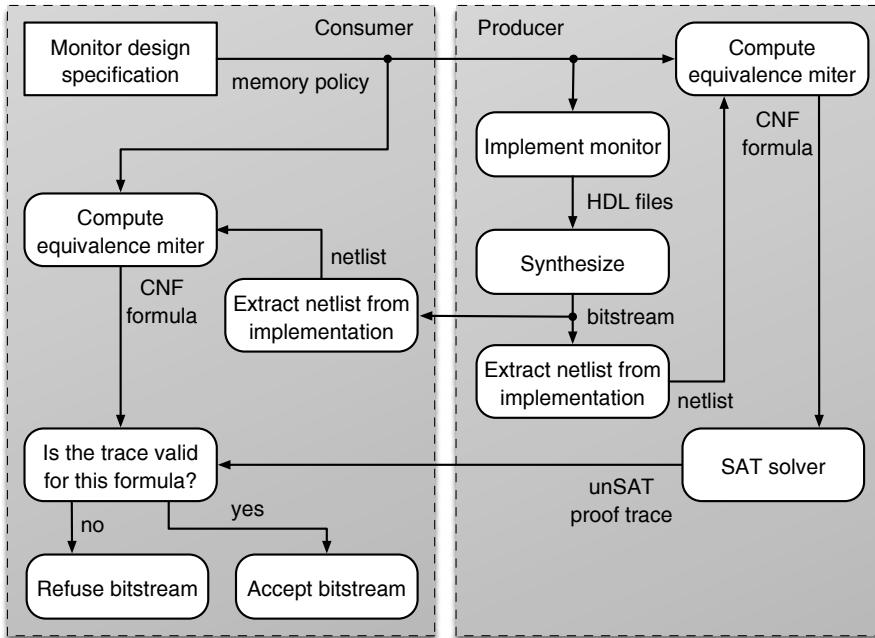

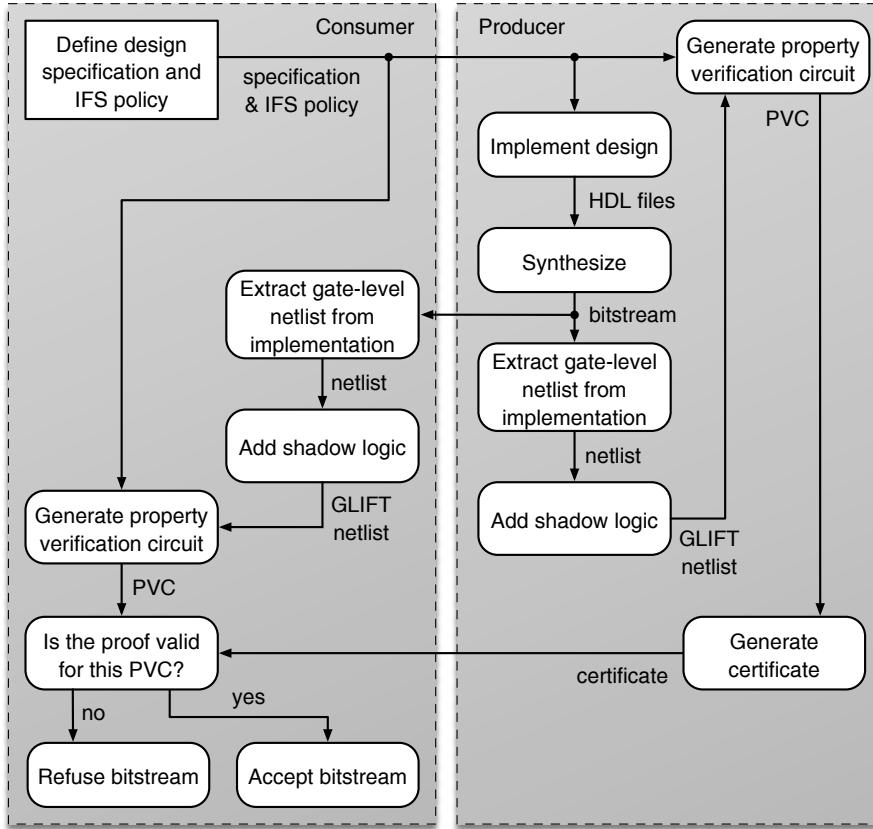

| Figure 3.2  | General bitstream-level PCH flow. . . . .        | 62  |

| Figure 4.1  | VFPGA as overlay of an FPGA. . . . .             | 69  |

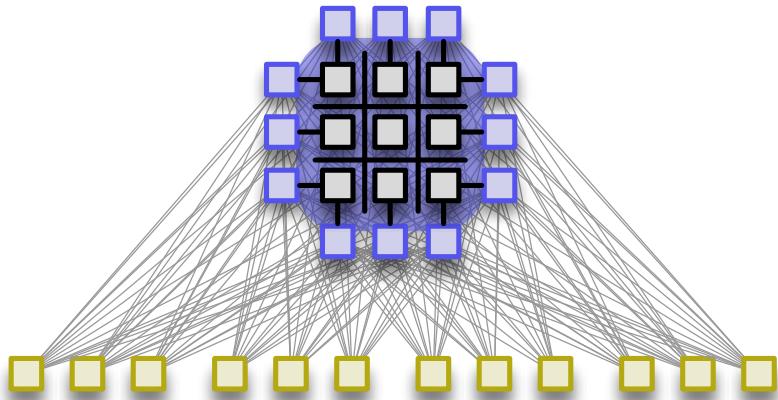

| Figure 4.2  | Basic ZUMA overlay layout. . . . .               | 77  |

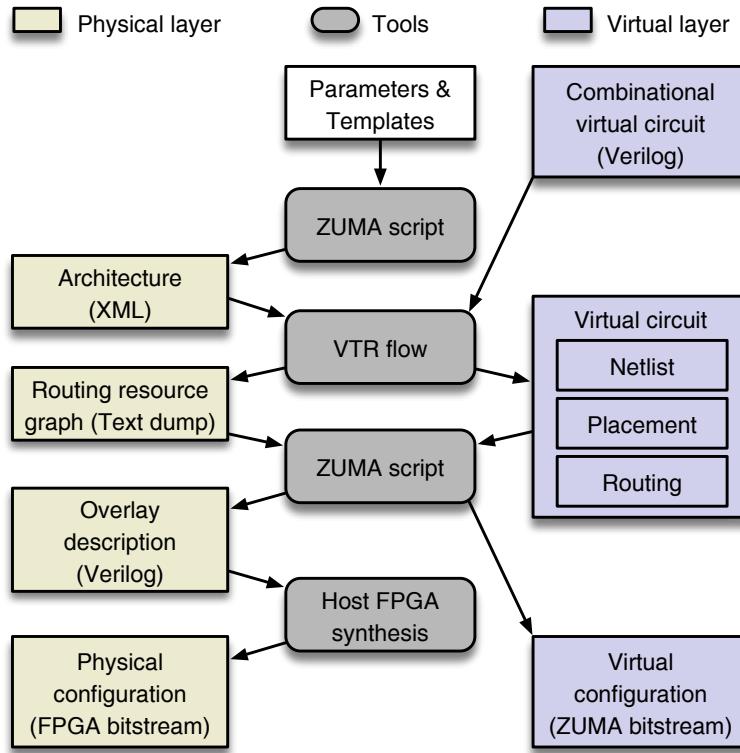

| Figure 4.3  | Original ZUMA tool flow. . . . .                 | 79  |

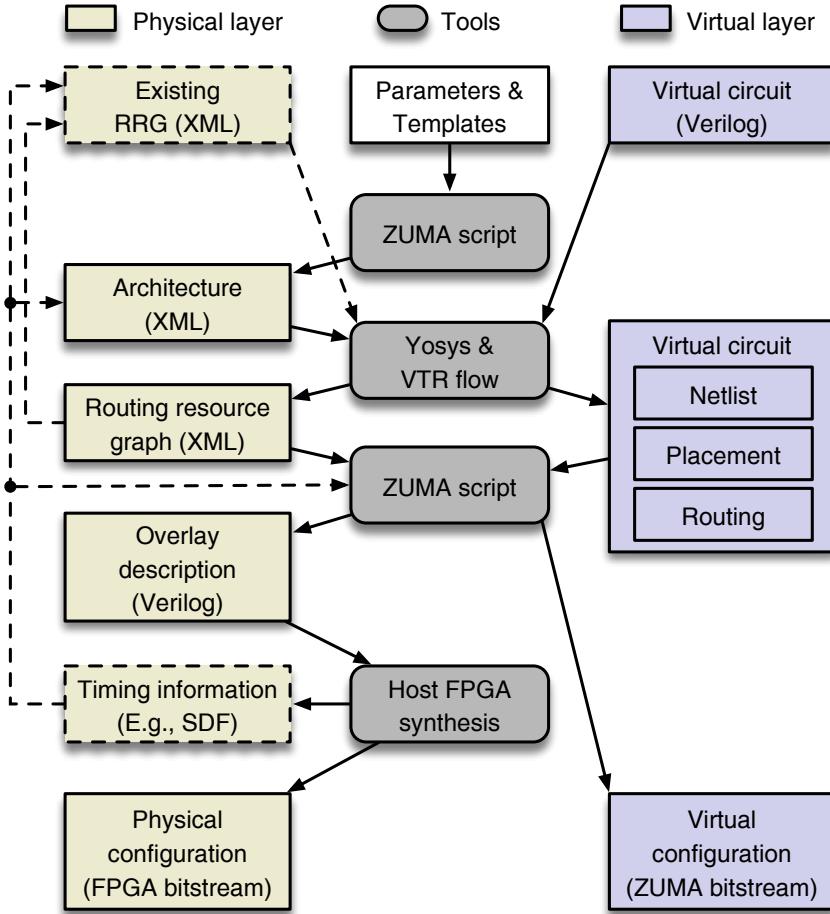

| Figure 4.4  | Current ZUMA tool flow. . . . .                  | 81  |

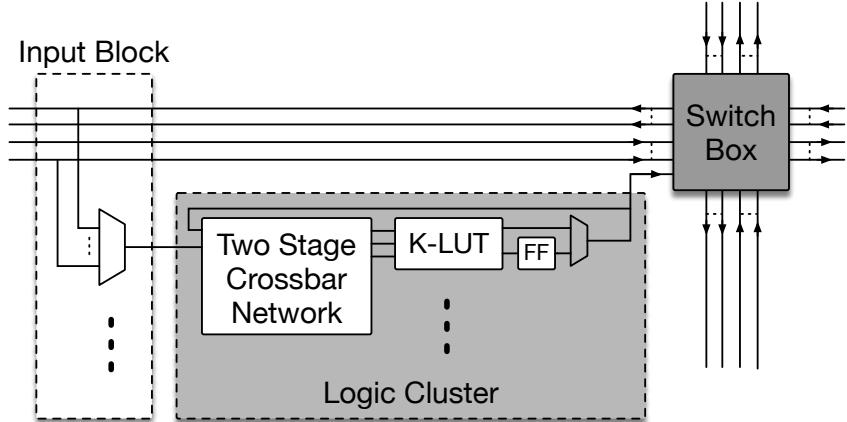

| Figure 4.5  | ZUMA configurable logic block. . . . .           | 82  |

| Figure 4.6  | Distributed memory block diagram. . . . .        | 83  |

| Figure 4.7  | ZUMA ordering layer overview. . . . .            | 86  |

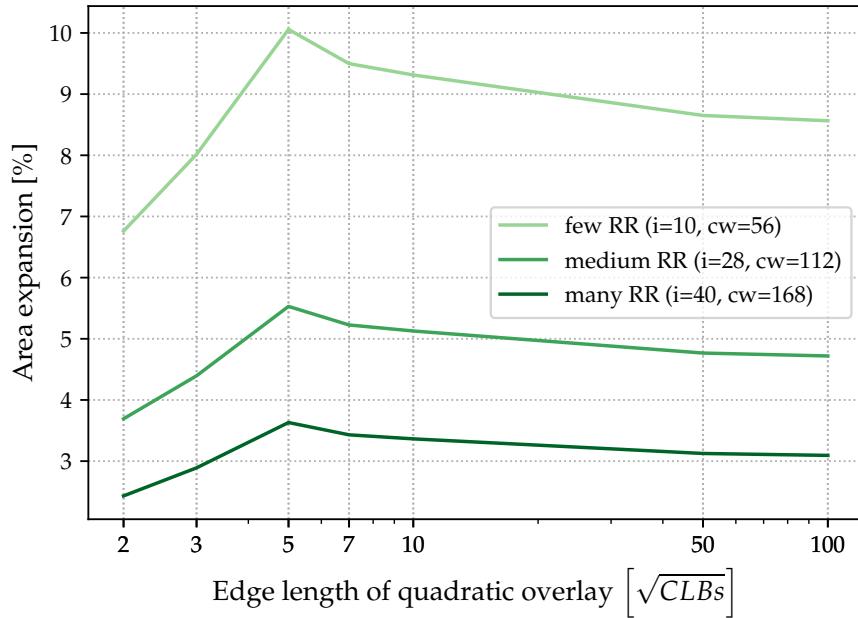

| Figure 4.8  | Area cost of the ordering layer. . . . .         | 88  |

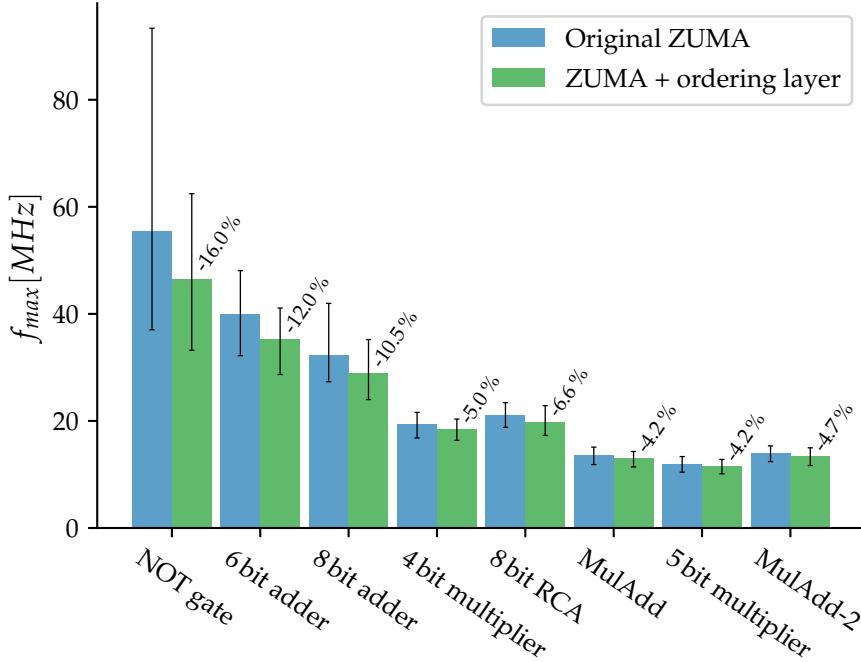

| Figure 4.9  | Delay penalty of the ordering layer. . . . .     | 89  |

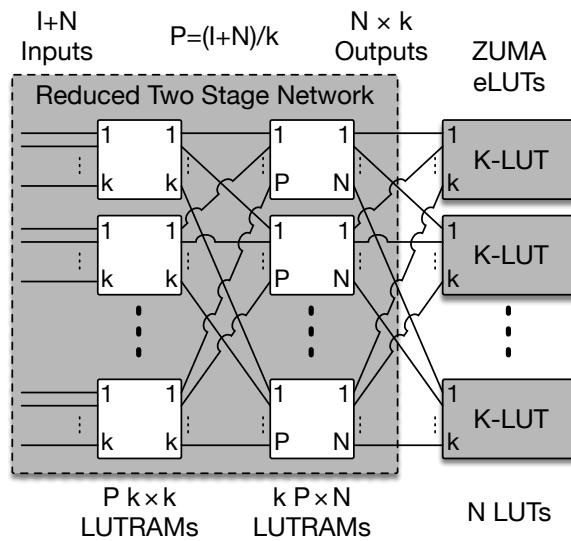

| Figure 4.10 | Clos network-based intra-cluster routing. . .    | 91  |

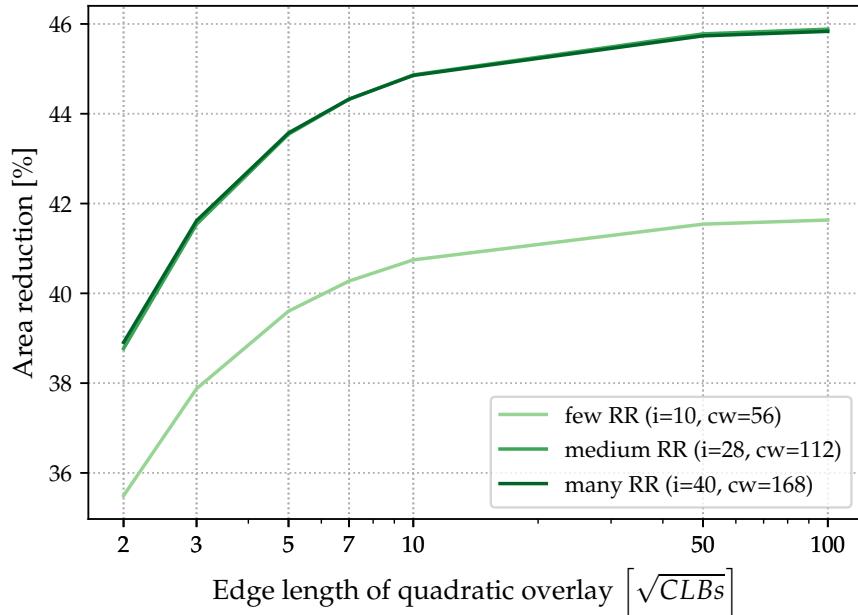

| Figure 4.11 | Area benefit of the Clos network-based IIBs. .   | 92  |

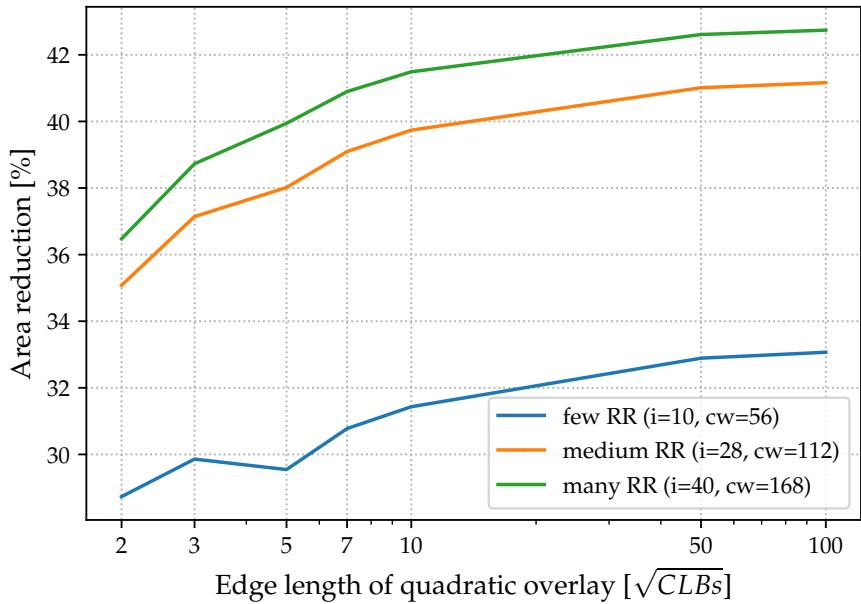

| Figure 4.12 | Area benefit of using all ZUMA extensions. .     | 94  |

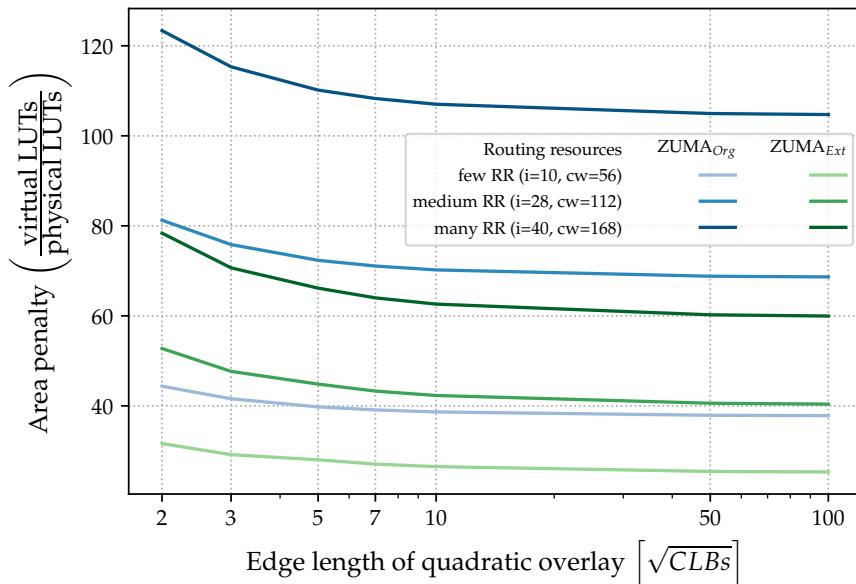

| Figure 4.13 | Area penalty of virtualizing with ZUMA. . .      | 95  |

| Figure 4.14 | ZUMA overlay embedded in a ReconOS HWT.          | 97  |

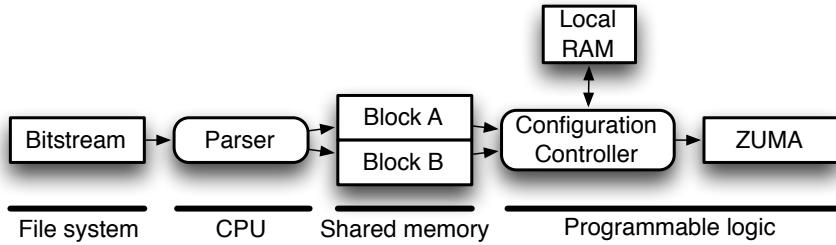

| Figure 4.15 | ZUMA configuration process. . . . .              | 98  |

| Figure 4.16 | SDF I/O path delays. . . . .                     | 110 |

| Figure 4.17 | Timing change with swappable CLBs. . . . .       | 115 |

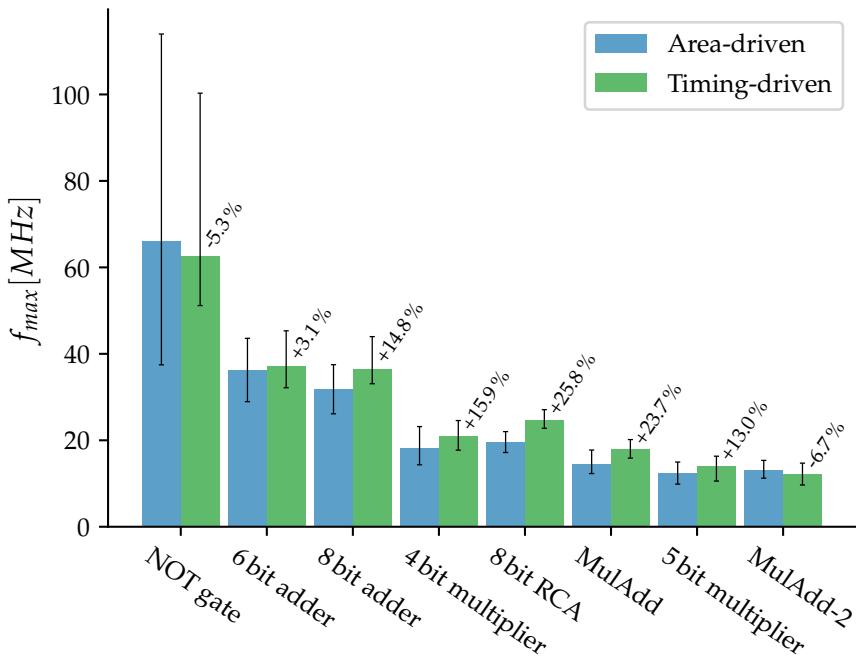

| Figure 4.18 | Timing change with timing-driven P&R. . . .      | 117 |

| Figure 5.1  | Combinational property verification circuits. .  | 122 |

| Figure 5.2  | Taxonomy of hardware properties. . . . .         | 125 |

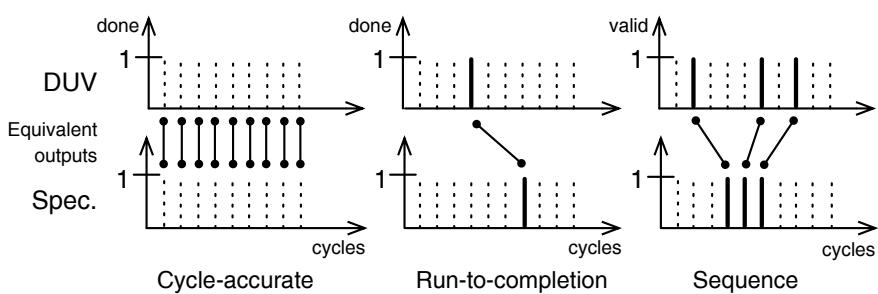

| Figure 5.3  | Sequential property verification circuits. . . . | 129 |

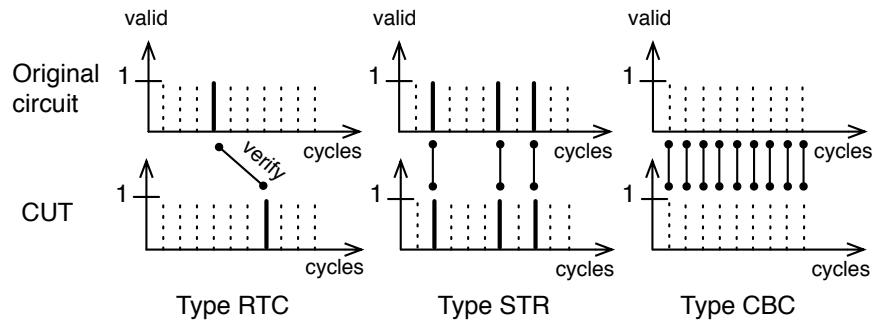

| Figure 5.4  | Sequential equivalence types. . . . .            | 129 |

|             |                                                 |     |

|-------------|-------------------------------------------------|-----|

| Figure 5.5  | Unrolled sequential PVC. . . . .                | 131 |

| Figure 5.6  | Runtime verification PVC example for BMC. .     | 132 |

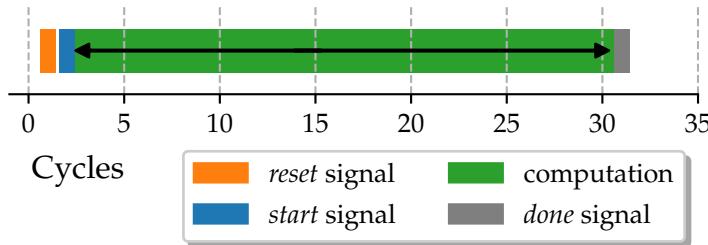

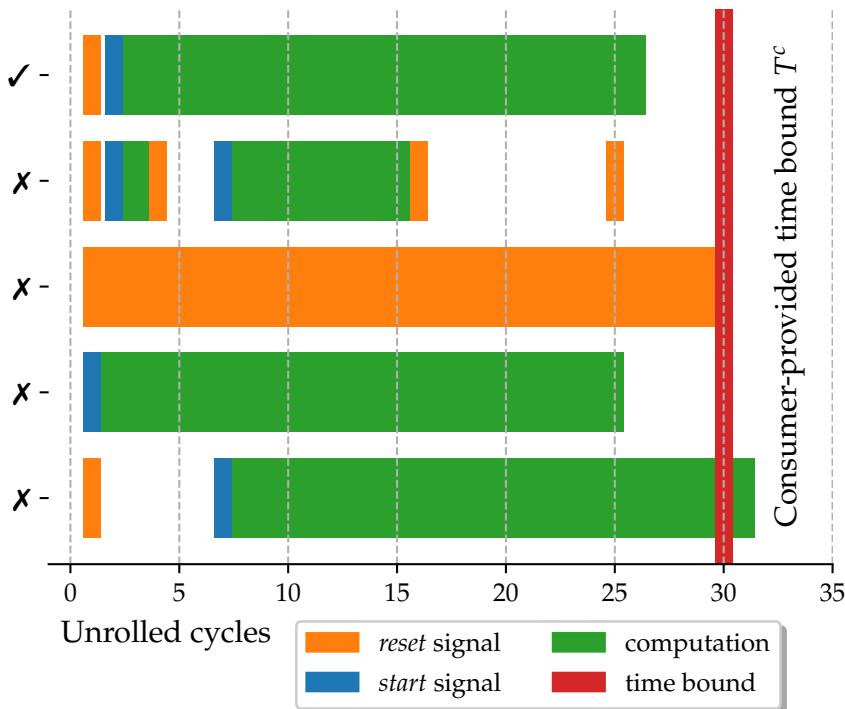

| Figure 5.7  | WCCT protocol example. . . . .                  | 133 |

| Figure 5.8  | Synchronous sequential circuits C. . . . .      | 135 |

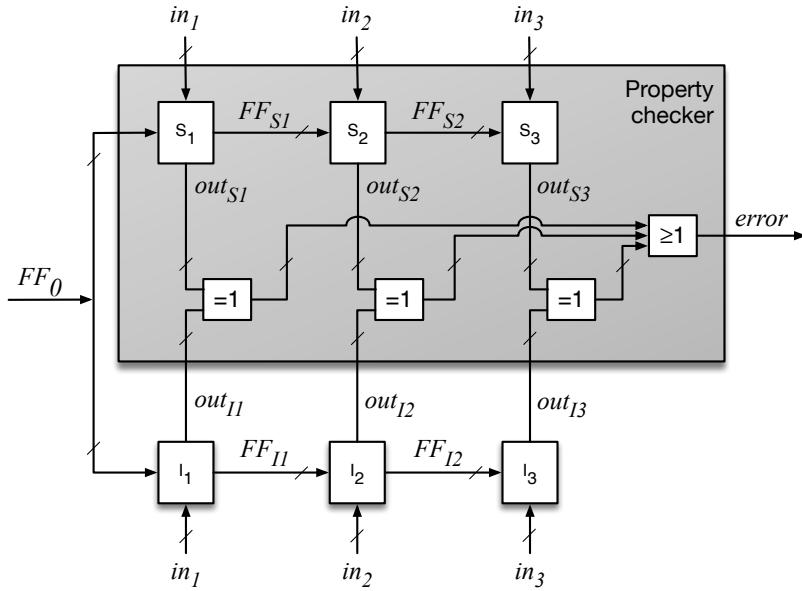

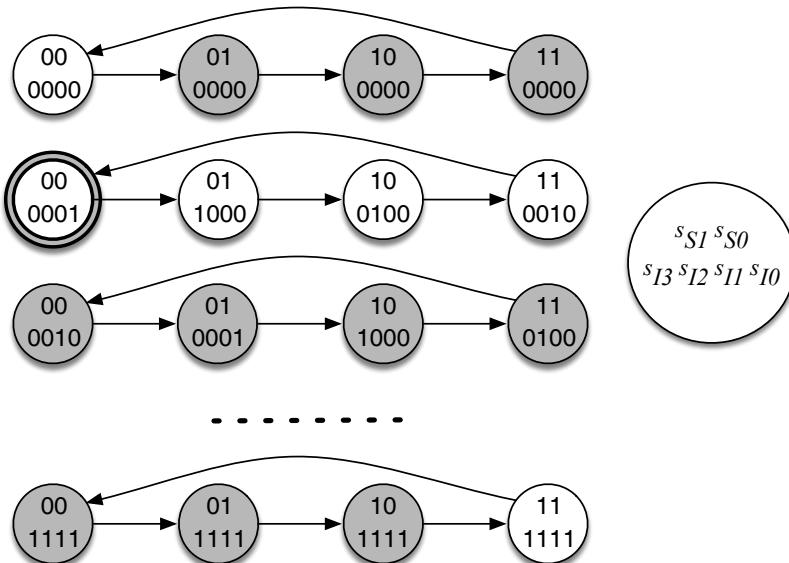

| Figure 5.9  | Example of a sequential PVC. . . . .            | 138 |

| Figure 5.10 | Example of a circuit's state space. . . . .     | 139 |

| Figure 5.11 | Generic PCH flow. . . . .                       | 143 |

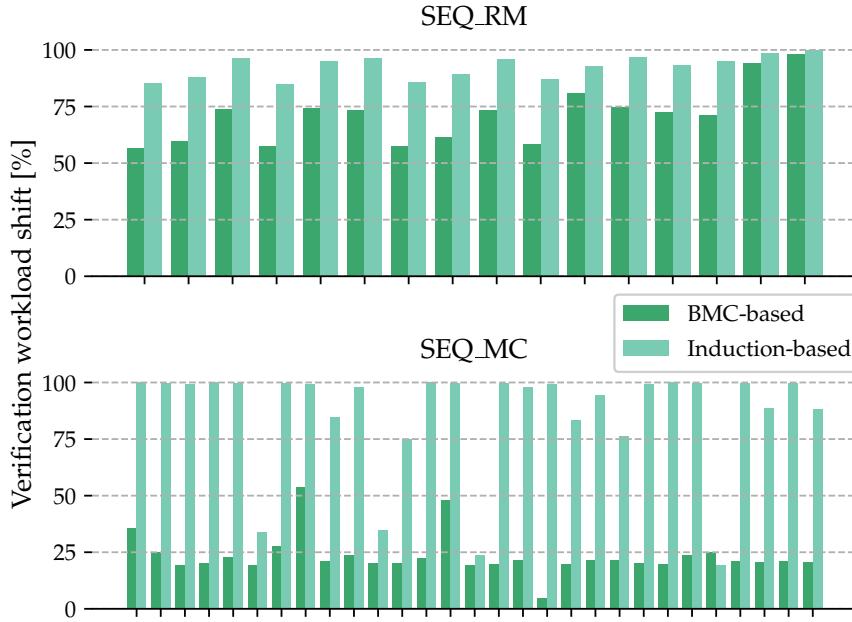

| Figure 5.12 | Workload shift in SPC. . . . .                  | 149 |

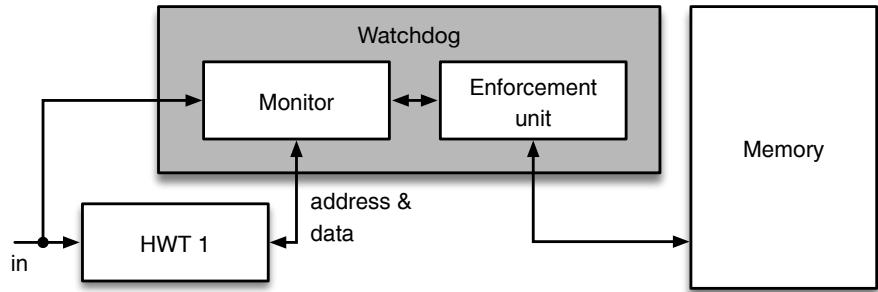

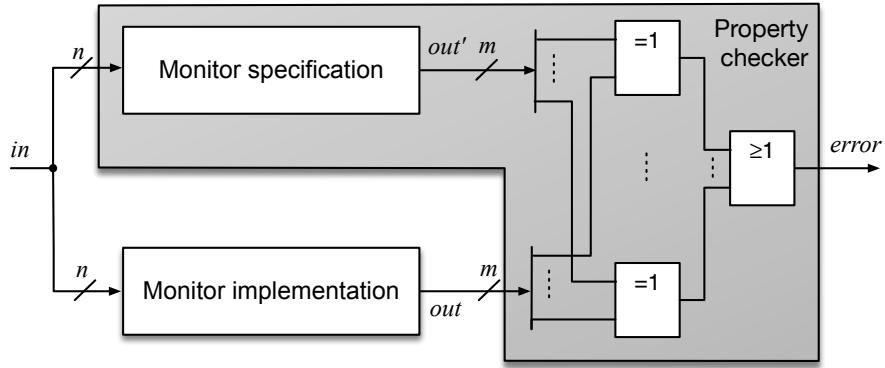

| Figure 5.13 | Memory monitor miter. . . . .                   | 152 |

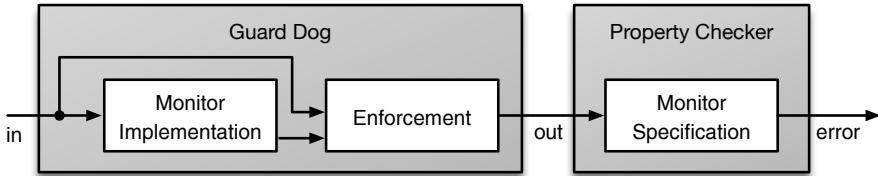

| Figure 5.14 | Guard dog miter. . . . .                        | 153 |

| Figure 5.15 | Runtime verification PCH flow. . . . .          | 155 |

| Figure 5.16 | Memory access monitor in ReconOS arbiter. .     | 158 |

| Figure 6.1  | Abstract PCH flow for WCCT proofs. . . . .      | 173 |

| Figure 6.2  | Circuit model for WCCT analysis. . . . .        | 175 |

| Figure 6.3  | WCCT and HW module interaction. . . . .         | 178 |

| Figure 6.4  | WCCT protocol filtering examples. . . . .       | 179 |

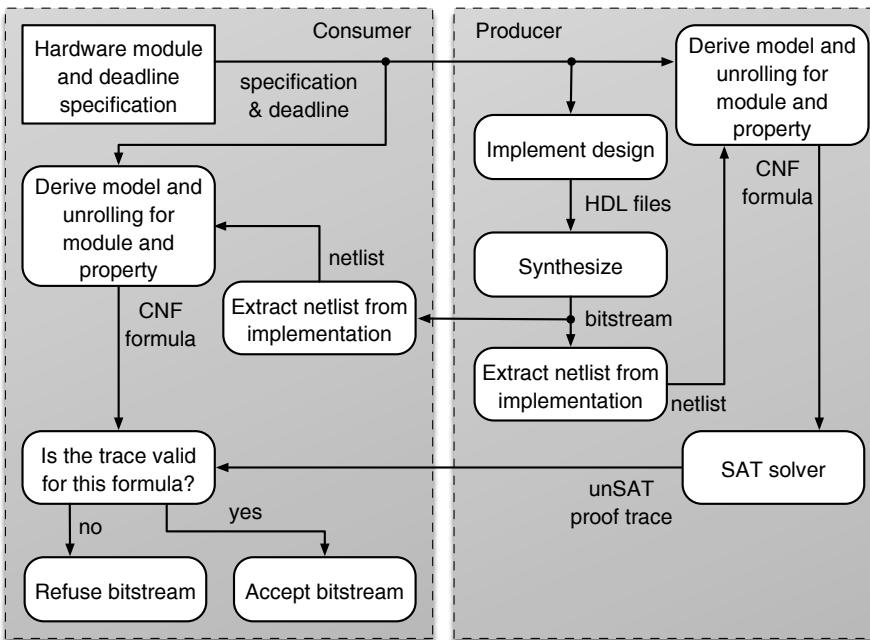

| Figure 6.5  | PCH flow for WCCT proofs. . . . .               | 181 |

| Figure 6.6  | A multihead weigher. . . . .                    | 183 |

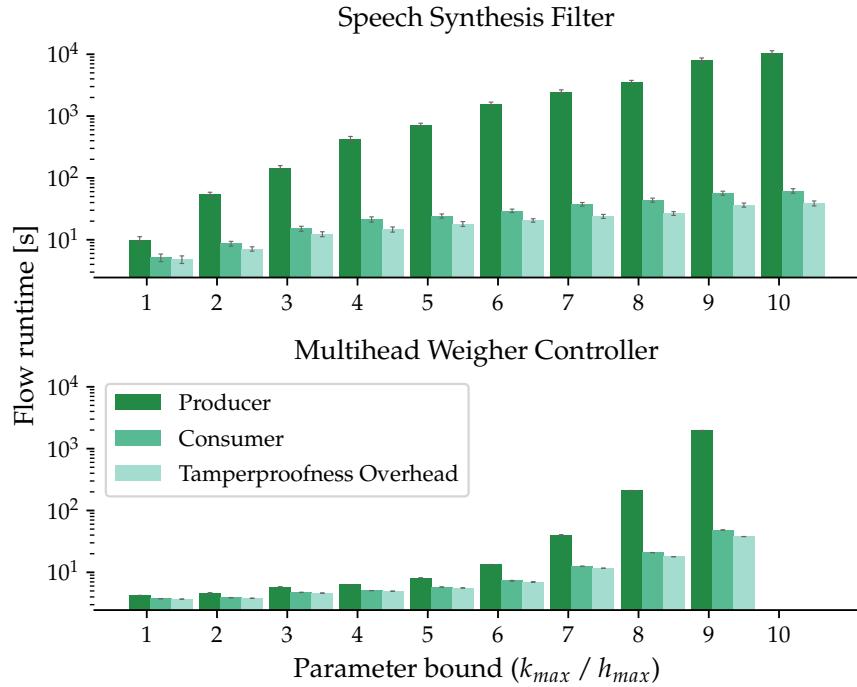

| Figure 6.7  | Flow runtimes for both WCCT case studies. .     | 184 |

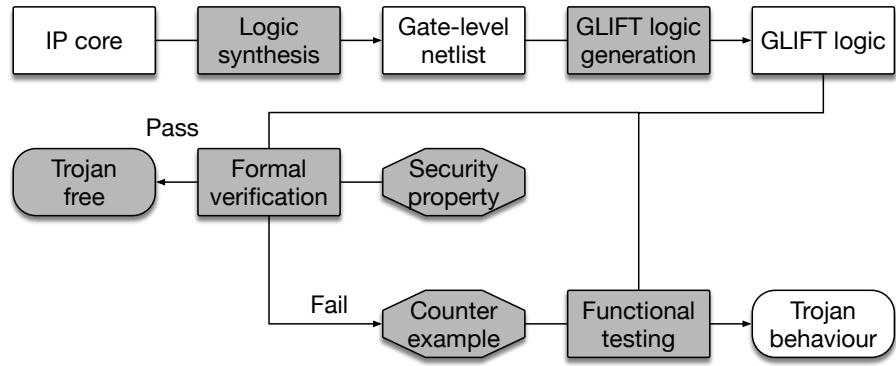

| Figure 6.8  | GLIFT HW Trojan detection flow. . . . .         | 190 |

| Figure 6.9  | Two-sided PCH GLIFT flow. . . . .               | 191 |

| Figure 6.10 | Non-interference miter. . . . .                 | 193 |

| Figure 6.11 | Port boundary shift for PCHIFT. . . . .         | 198 |

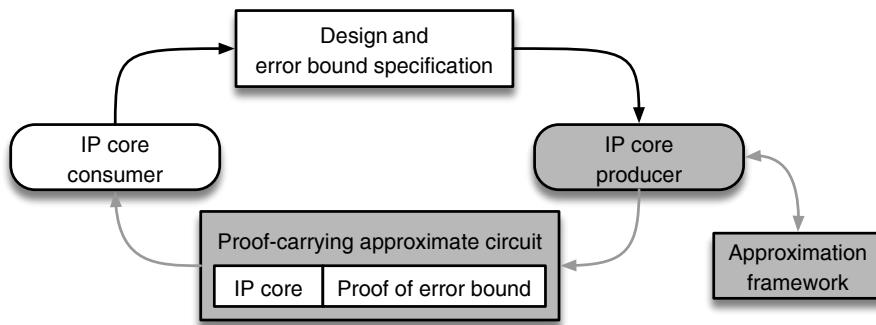

| Figure 6.12 | The PCAC flow. . . . .                          | 211 |

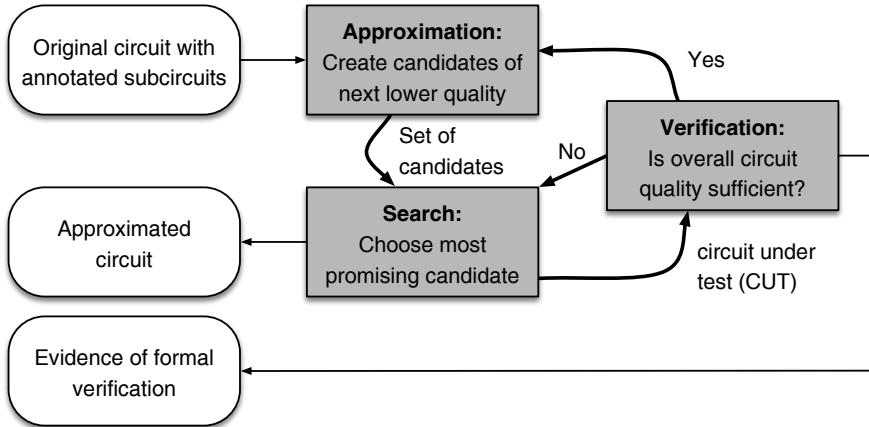

| Figure 6.13 | CIRCA approximation flow overview. . . . .      | 213 |

| Figure 6.14 | Sequential quality constraint circuit. . . . .  | 215 |

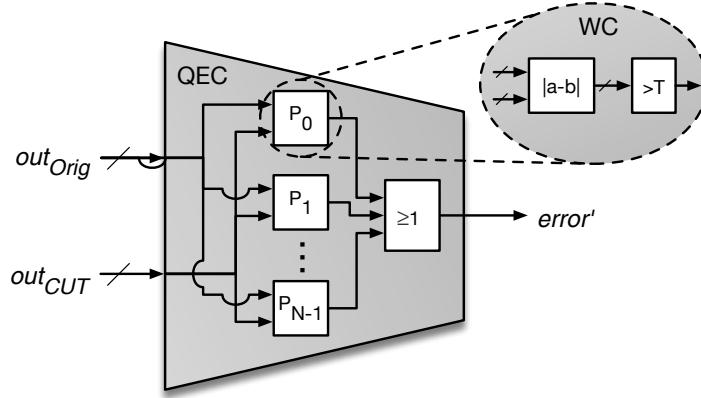

| Figure 6.15 | Quality evaluation circuit. . . . .             | 215 |

| Figure 6.16 | PCAC sequential circuit types. . . . .          | 216 |

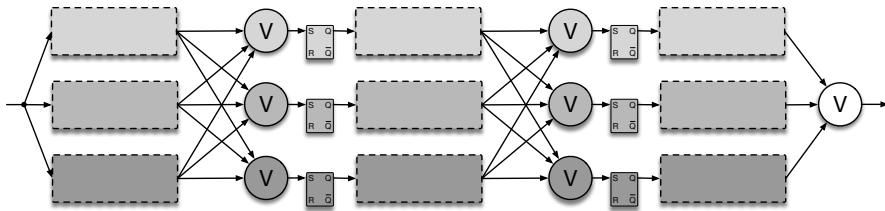

| Figure 6.17 | General structure of distributed TMR. . . . .   | 223 |

| Figure 6.18 | SCM for redundancy. . . . .                     | 224 |

| Figure 6.19 | Fault injection. . . . .                        | 224 |

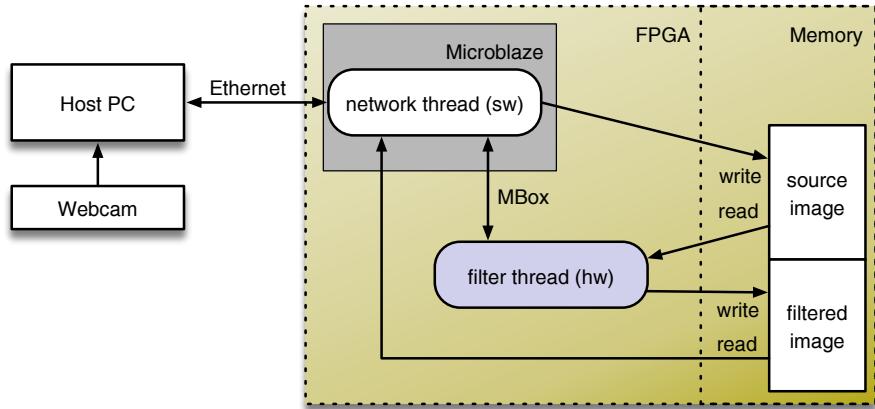

| Figure 7.1  | Image processing application overview. . . . .  | 228 |

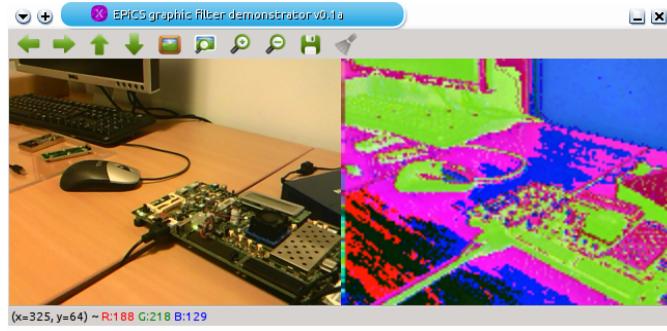

| Figure 7.2  | Screenshot of Demonstrator 1. . . . .           | 228 |

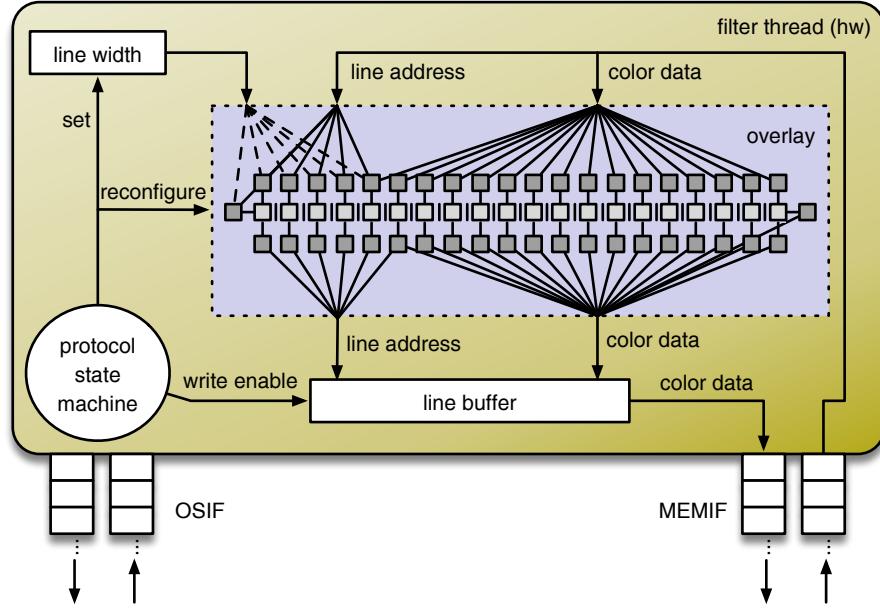

| Figure 7.3  | ZUMA-augmented filtering HWT. . . . .           | 230 |

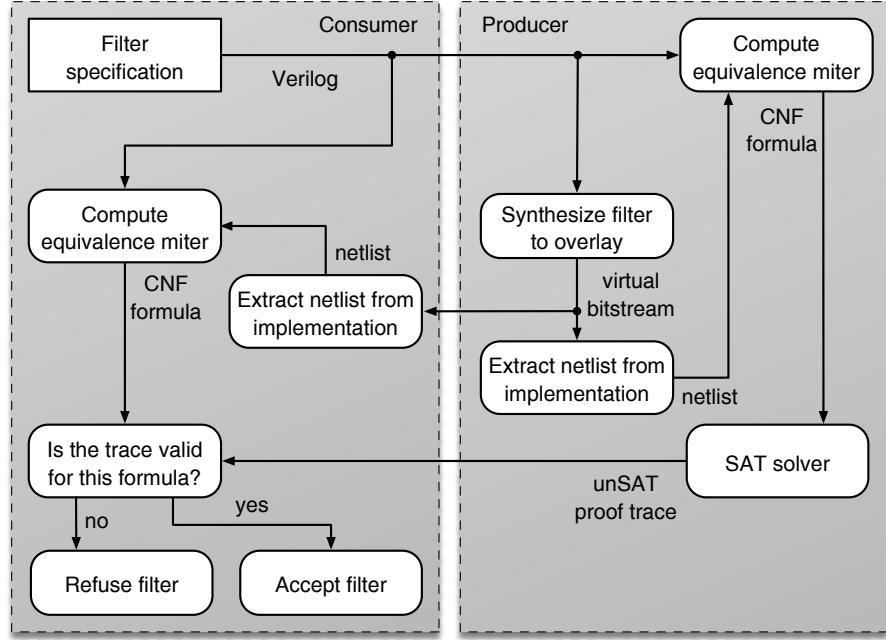

| Figure 7.4  | PCH flow for the first demonstrator. . . . .    | 232 |

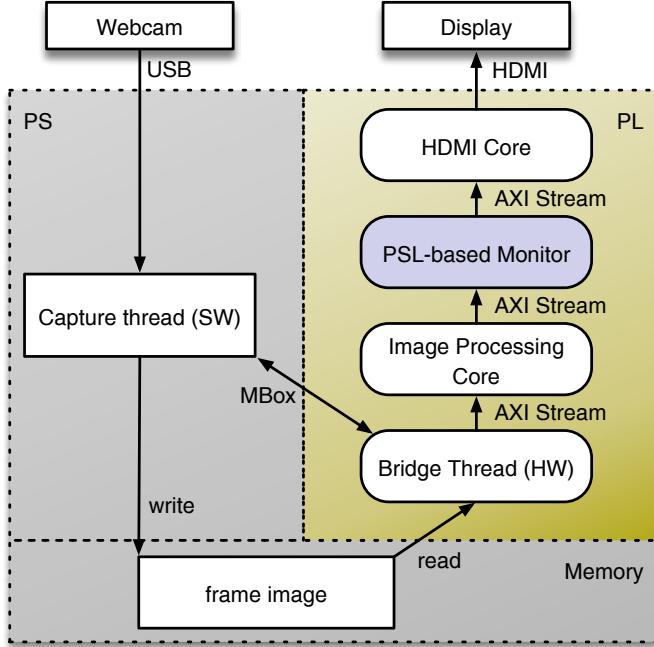

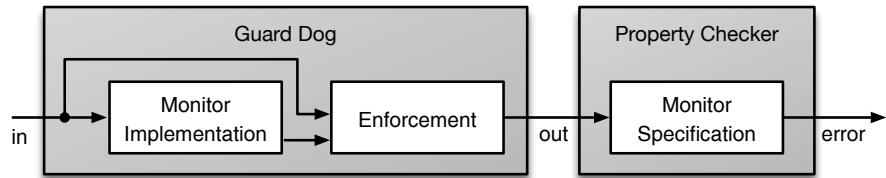

| Figure 7.5  | PSL-based monitoring in video pipeline. . . . . | 236 |

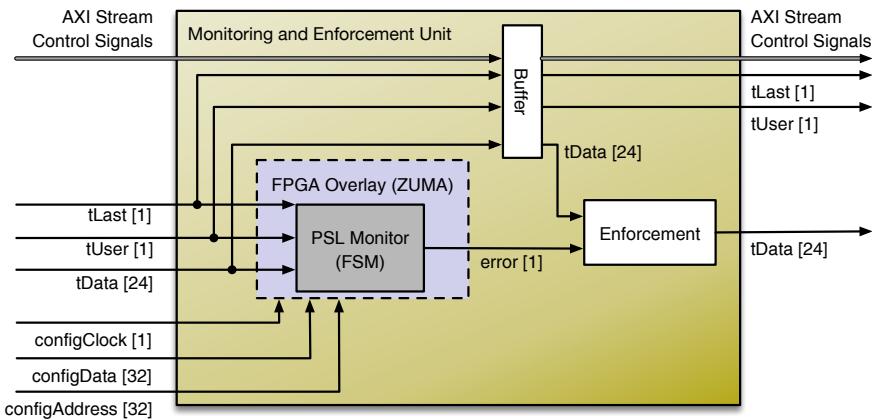

| Figure 7.6  | ZUMA-augmented filtering pipeline stage. .      | 237 |

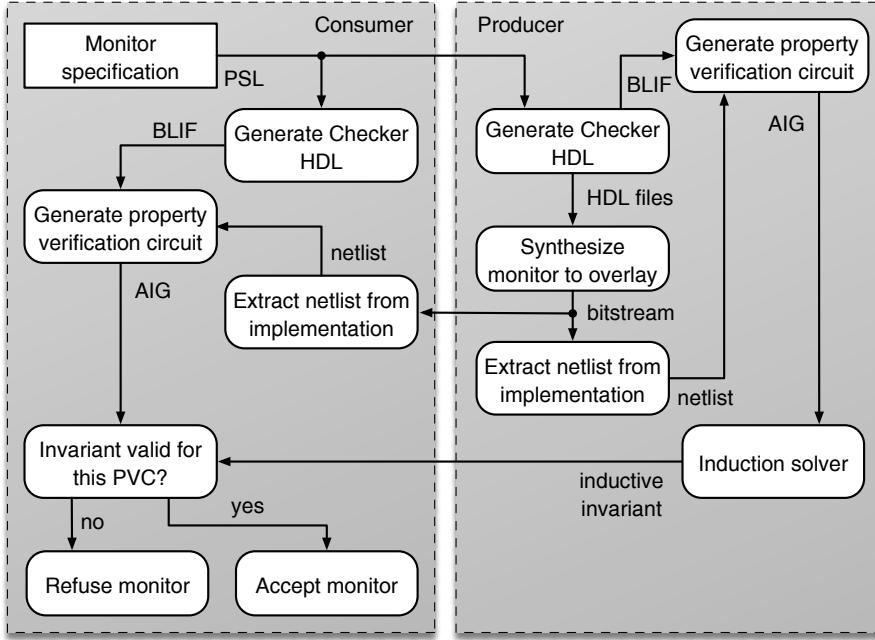

| Figure 7.7  | PCH flow for the second demonstrator. . . . .   | 239 |

| Figure 7.8  | Miter function for Demonstrator 2. . . . .      | 240 |

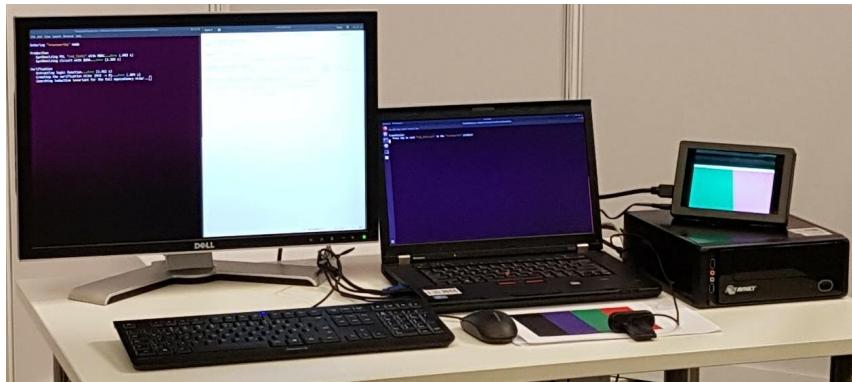

| Figure 7.9  | Booth setup of Demonstrator 2. . . . .          | 240 |

## LIST OF LISTINGS

---

|                 |                                           |     |

|-----------------|-------------------------------------------|-----|

| SDF Excerpt 4.1 | Xilinx file header. . . . .               | 109 |

| SDF Excerpt 4.2 | I/O path delays. . . . .                  | 109 |

| SDF Excerpt 4.3 | Interconnect delays. . . . .              | 110 |

| Listing 6.1     | Protocol filtering example. . . . .       | 180 |

| Listing 7.1     | Image processing filter example. . . . .  | 230 |

| Listing 7.2     | Combinational PSL filter example. . . . . | 237 |

| Listing 7.3     | Sequential PSL filter example. . . . .    | 238 |

| Listing 7.4     | Producer output example. . . . .          | 241 |

| Listing 7.5     | Consumer output example. . . . .          | 242 |

| Listing 9.1     | PRNG verification example. . . . .        | 246 |

## LIST OF TABLES

---

|            |                                                              |     |

|------------|--------------------------------------------------------------|-----|

| Table 4.1  | Area and speed of ReconOS with $3 \times 3$ overlay. . . . . | 100 |

| Table 4.2  | Area breakdown of a HWT with overlay. . . . .                | 102 |

| Table 4.3  | ZUMA on ReconOS synthesis measurements. . . . .              | 103 |

| Table 4.4  | ZUMA bitstream sizes. . . . .                                | 103 |

| Table 4.5  | Timing extraction method comparison. . . . .                 | 111 |

| Table 5.1  | Benchmark circuits for SPC. . . . .                          | 145 |

| Table 5.2  | Comparison of BMC and IND for SEQ-RM. . . . .                | 146 |

| Table 5.3  | Comparison of BMC and IND for SEQ-MC. . . . .                | 147 |

| Table 5.4  | Peak memory comparison (BMC, IND). . . . .                   | 148 |

| Table 5.5  | Runtime comparison for guard dog PCH. . . . .                | 159 |

| Table 5.6  | Guard dog prototype versions. . . . .                        | 160 |

| Table 5.7  | Prototype overheads. . . . .                                 | 161 |

| Table 5.8  | CEC for Multipliers. . . . .                                 | 164 |

| Table 5.9  | Benchmarks for scalability evaluation. . . . .               | 166 |

| Table 5.10 | Runtime and workload shift for SCAL. . . . .                 | 167 |

| Table 5.11 | PCH flow comparison 2017–2020. . . . .                       | 168 |

| Table 6.1  | PCH runtimes for GLIFT. . . . .                              | 201 |

| Table 6.2  | Trojan detection using GLIFT. . . . .                        | 203 |

| Table 6.3  | PCH runtimes for non-interference miters. . . . .            | 204 |

| Table 6.4  | Trojan detection using non-interference miters. . . . .      | 206 |

| Table 6.6  | CIRCA runtimes for PCAC. . . . .                             | 220 |

| Table 6.7  | PCAC PCH flow runtimes. . . . .                              | 221 |

| Table 7.1  | Area and timing of Demonstrator 1. . . . .                   | 233 |

| Table 7.2  | PCH times for Demonstrator 1. . . . .                        | 234 |

| Table 7.3  | Area and synthesis times of Demonstrator 2. . . . .          | 241 |

| Table 7.4  | PCH times for Demonstrator 2. . . . .                        | 242 |

## ACRONYMS

---

- #SAT** Counting Boolean Satisfiability. Pages: [126](#), [127](#), [215](#)

- AC** Approximate Circuit. Pages: [208–217](#)

- AES** Advanced Encryption Standard. Pages: [36–38](#), [199](#), [202](#), [203](#)

- AIG** And-inverter-graph. Pages: [xix](#), [45](#), [144](#), [165](#), [210](#), [214](#), [218](#), [219](#)

- ALU** Arithmetic Logic Unit. Page: [12](#)

- ASCII** American Standard Code For Information Interchange. Page: [79](#)

- ASIC** Application-specific Integrated Circuit. Pages: [1](#), [2](#), [15](#), [16](#), [59](#), [71](#), [173](#), [223](#)

- AxC** Approximate Computing. Pages: [207–209](#), [214](#), [215](#), *Glossary: Approximate computing*

- AXI** Advanced Extensible Interface. Pages: [96](#), [162](#), [235–237](#), [241](#)

- BDD** Binary Decision Diagram. Pages: [24](#), [26](#)

- BLE** Basic Logic Element. Pages: [11](#), [77](#), [99](#), [160](#), [162](#), [236](#)

- BLIF** Berkeley Logic Interchange Format. Pages: [46](#), [47](#), [86](#), [87](#)

- BMC** Bounded Model Checking. Pages: [27](#), [30](#), [31](#), [42](#), [46](#), [55](#), [122](#), [128](#), [130–134](#), [142–144](#), [146–149](#), [155](#), [168](#), [169](#), [179](#), [182](#), [210](#), [217](#), [223](#), [225](#)

- CAD** Computer-aided Design. Pages: [9](#), [14](#), [15](#), [45](#), [46](#), [58](#), [60](#), [69](#), [118](#)

- CDMA** Code Division Multiple Access. Page: [199](#)

- CEC** Combinational Equivalence Checking. Pages: [xx](#), [xxii](#), [5](#), [26](#), [27](#), [30](#), [41](#), [44](#), [62](#), [65](#), [152](#), [163](#)

- CEX** Counterexample. Pages: [26](#), [27](#), [32](#), [189](#), [195](#)

- CLB** Configurable Logic Block. Pages: [xvi](#), [9](#), [11–14](#), [69](#), [77](#), [78](#), [80](#), [87](#), [89–91](#), [99](#), [100](#), [106](#), [112–114](#), [116](#), [118](#), [119](#), [160](#), [231](#), [232](#), [236](#), [245](#)

- CNF** Conjunctive Normal Form. Pages: [26](#), [27](#), [32](#), [42](#), [47–50](#), [130](#), [143](#), [155](#), [156](#), [181](#), [205](#), [231](#)

- COI** Conflict-of-interest. Pages: [37](#), [38](#), [158](#)

- COTS** Commercial Off-the-shelf. Pages: [1](#), [2](#), [104](#), [165](#), [225](#)

- CPC** Combinational Property Checking. Pages: [31](#), [128](#), [142](#)

- CPU** Central Processing Unit. Pages: [xvi](#), [xxiii](#), [12](#), [16](#), [36](#), [51](#), [96](#), [99](#), [144](#), [182](#), [228](#), [232](#)

- CTI** Counterexample To Induction. Pages: [33](#), [139–141](#)

- CUT** Circuit Under Test. Pages: [213](#), [214](#), [216](#), [217](#)

- DES** Data Encryption Standard. Page: [188](#)

- DMA** Direct Memory Access. Page: [35](#)

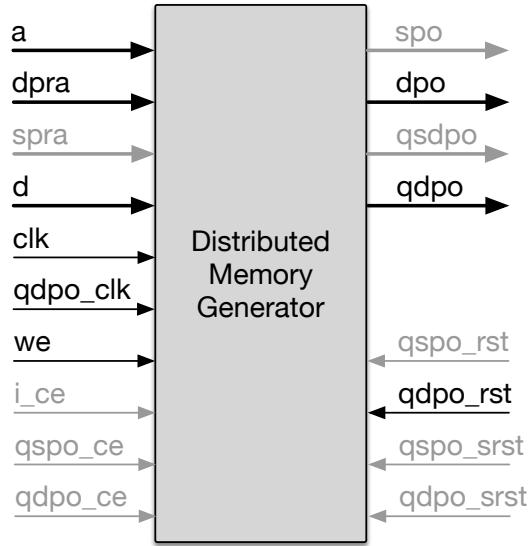

- DMG** Distributed Memory Generator. Pages: [78](#), [101](#), [118](#)

- DNF** Disjunctive Normal Form. Page: [26](#)

- DSL** Domain Specific Language. Pages: [27](#), [28](#)

- DSP** Digital Signal Processing. Page: [74](#)

- DT** Delegate Thread. Pages: [50](#), [96](#), [97](#), *Glossary: Delegate thread*

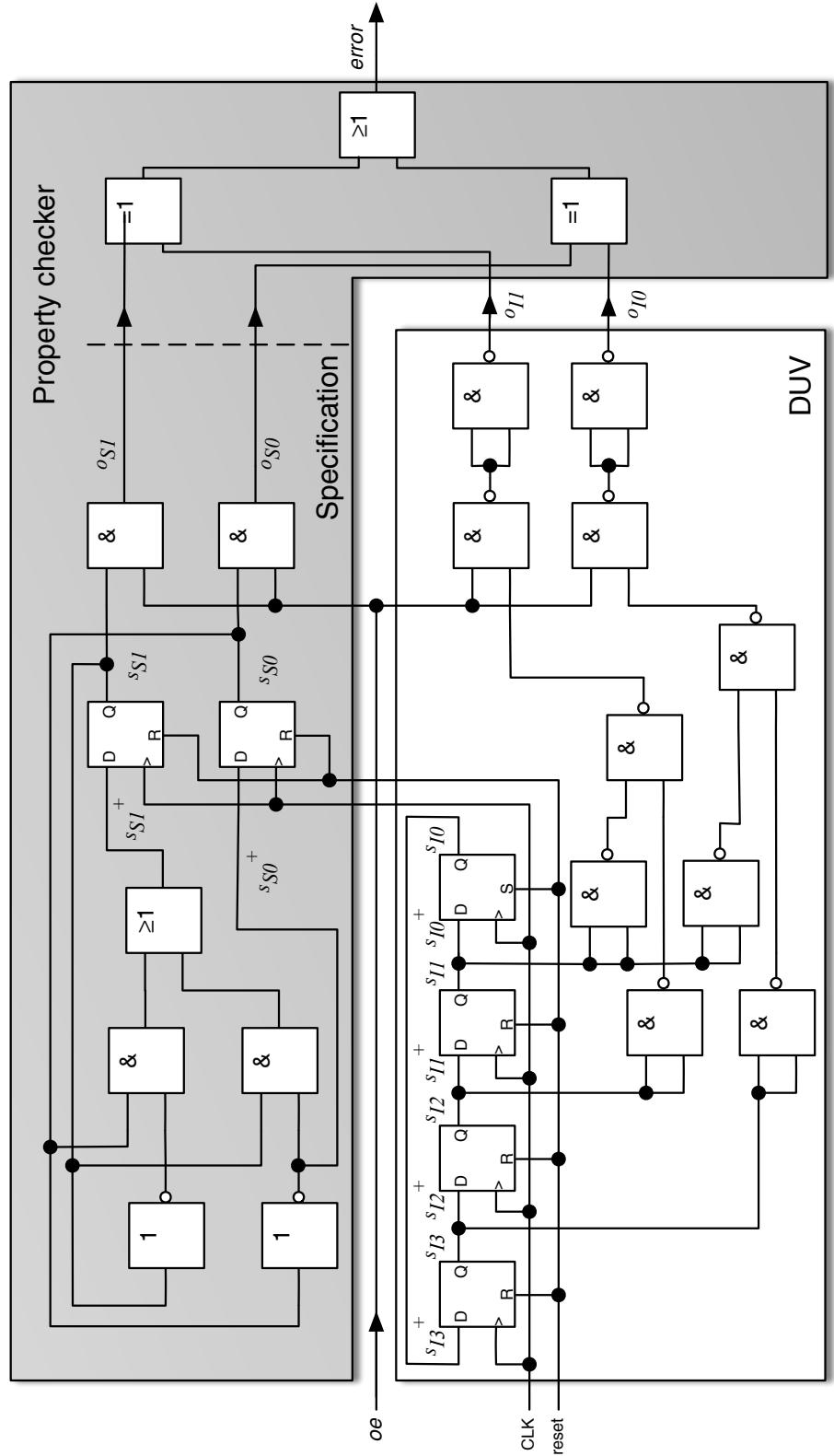

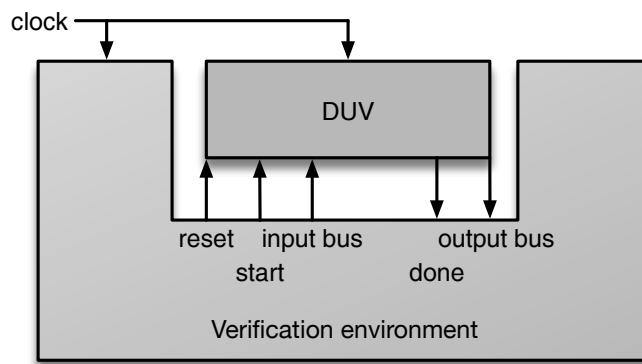

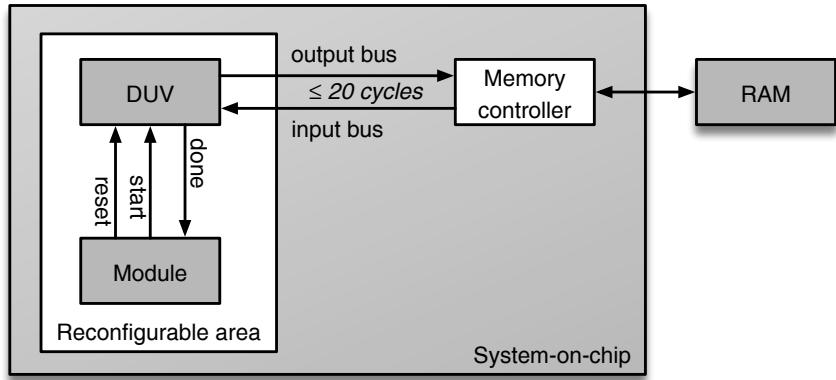

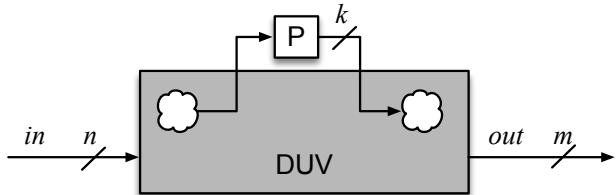

- DUV** Design Under Verification. Pages: [xxii](#), [18–26](#), [28–35](#), [47](#), [63](#), [122](#), [128](#), [150](#), [151](#), [153](#), [154](#), [163](#), [175](#), [177](#), [188](#), [189](#), [192–201](#), [203](#), [205–207](#), [217](#), [243](#)

- EDA** Electronic Design Automation. Pages: [2](#), [3](#), [14](#), [15](#), [17](#), [24](#), [44](#), [45](#), [59](#), [60](#), [70](#), [73](#), [75](#), [80](#), [81](#), [93](#), [100](#), [101](#), [104](#), [105](#), [118](#), [123](#), [244](#), [245](#)

- EDM** Elmore Delay Model. Page: [107](#)

- eLUT** Embedded Lookup Table. Pages: [76](#), [78](#), [80–84](#), [90](#), [91](#), [94](#), [101](#), *Glossary: Embedded lookup table*

- FEC** Functional Equivalence Checking. Pages: [25](#), [46](#), [121–124](#), [126–128](#), [133](#), [137](#), [144](#), [152](#), [153](#), [155](#), [194](#), [195](#), [197](#), [198](#), [208](#), [231](#), [244](#), *Glossary: Functional equivalence checking*

- FF** Flip-flop. Pages: [xxiii](#), [9](#), [11](#), [17](#), [31](#), [42](#), [77](#), [78](#), [82–84](#), [99](#), [106](#), [130](#), [134](#), [135](#), [137](#), [141](#), [160](#), [164](#), [200](#), [236](#), *Glossary: Flip-flop*

- FIFO** First In, First Out. Pages: [50](#), [96](#), [229](#)

- FPGA** Field-programmable Gate Array. Pages: [xx–xxiii](#), [1–3](#), [5](#), [6](#), [9–16](#), [35](#), [36](#), [42–44](#), [46](#), [47](#), [54–60](#), [65](#), [67–80](#), [83–85](#), [87](#), [88](#), [92](#), [93](#), [95](#), [101](#), [104–106](#), [109](#), [112](#), [113](#), [116](#), [119](#), [120](#), [153](#), [155](#), [162](#), [163](#), [171](#), [199](#), [218](#), [225](#), [229](#), [230](#), [232–234](#), [243–245](#)

- FSM** Finite State Machine. Pages: [20](#), [23](#), [24](#), [27](#), [32](#), [37](#), [38](#), [101](#), [132](#), [135](#), [155](#), [156](#), [173](#), [200](#), [205](#), [229](#)

- FV** Formal Verification. Pages: [xix](#), [xxi](#), [xxii](#), [4](#), [10](#), [17–20](#), [23–26](#), [28–30](#), [34](#), [39](#), [40](#), [44](#), [45](#), [49](#), [57](#), [62–64](#), [123](#), [124](#), [150](#), [151](#), [159](#), [163](#), [169](#), [177](#), [188–190](#), [202](#), [207](#), [243](#), [244](#)

- GLIFT** Gate-level Information Flow Tracking. Pages: [186–192](#), [198–203](#), [205–207](#)

- GSM** Global System For Mobile Communications. Page: [182](#)

- HDL** Hardware Description Language. Pages: [16](#), [18](#), [21](#), [23](#), [27–29](#), [38](#), [41](#), [42](#), [44–47](#), [58](#), [68](#), [78](#), [102](#), [108](#), [118](#), [121](#), [122](#), [154](#), [189](#), [238](#)

- HLS** High-level Synthesis. Page: [209](#)

- HPC** High-performance Computing. Pages: [154](#), [162](#)

- HVL** Hardware Verification Language. Pages: [6](#), [23](#), [29](#), [124](#), [243](#), [245](#)

- HW Trojan** Hardware Trojan. Pages: [4](#), [44](#), [66](#), [188–190](#), [195](#), [196](#), [199–206](#)

- HWMCC** Hardware Model Checking Competition. Pages: [30](#), [32](#), [46](#), [63](#), [144](#), [163–165](#), [167](#), [219](#), [243](#)

- HWT** Hardware Thread. Pages: [xx](#), [50](#), [96–99](#), [101–103](#), [131](#), [132](#), [157](#), [160–163](#), [228](#), [229](#)

- I/O** Input / output. Pages: [xxii](#), [9](#), [12](#), [13](#), [15](#), [20](#), [22](#), [27](#), [31](#), [77](#), [84–87](#), [89](#), [92](#), [96](#), [98–101](#), [112](#), [114](#), [115](#), [153](#), [185](#), [189](#), [192](#), [194](#), [205](#), [230–232](#), [235](#), [236](#)

- IC** Integrated Circuit. Pages: [1–3](#), [8](#), [9](#), [84](#), [85](#)

- IC<sub>3</sub>** Incremental Construction Of Inductive Clauses For Indubitable Correctness. Pages: [30](#), [32](#), [33](#), [46](#), [66](#), [128](#), [134](#), [141](#), [142](#), [146](#)

- IFS** Information Flow Security. Pages: [127](#), [172](#), [185–187](#), [189–195](#), [198](#), [200](#), [203–205](#), [207](#), [223](#), [225](#)

- IFT** Information Flow Tracking. Pages: [185](#), [188](#), [191](#), [199](#), [202](#), [207](#)

- IIB** Input Interconnect Block. Pages: [77](#), [90–92](#), [94](#), [99–101](#), *Glossary: Input interconnect block*

- IP-core** Intellectual Property Core. Pages: [1–3](#), [15](#), [16](#), [19](#), [20](#), [23](#), [33](#), [36](#), [39](#), [41](#), [44](#), [58](#), [60](#), [78](#), [80](#), [96](#), [188](#), [189](#), [199](#), [200](#), [202](#), [205](#), [211](#), [217](#), [225](#), [235](#), [236](#), *Glossary: Intellectual property core*

- IS** Inductive Strengthening. Pages: [128](#), [140–143](#), [148](#), [190](#), [202](#), [205](#), [217](#), *Glossary: Inductive strengthening*

- ISA** Instruction Set Architecture. Page: [22](#)

- LDM** Linear Delay Model. Page: [107](#)

- LUT** Lookup Table. Pages: [xx](#), [xxi](#), [9](#), [11](#), [13–15](#), [46](#), [72](#), [76–78](#), [80–84](#), [87](#), [90](#), [92](#), [93](#), [99](#), [101](#), [160](#), [162](#), [218](#), [230](#), [232](#), [236](#), [240](#)

- LUTRAM** Lookup Table Random Access Memory. Pages: [72](#), [78–83](#), [87](#), [92–94](#), [98–102](#), [110](#), [115](#), [118](#), [119](#), [162](#), [232](#), [240](#), *Glossary: Lookup table random access memory*

- MC** Model Checking. Pages: [23–26](#), [30](#), [44](#)

- MEMIF** Memory Interface. Pages: [50](#), [96](#), [97](#), [229](#), [235](#)

- MMU** Memory Management Unit. Pages: [50](#), [51](#), [161](#), [235](#)

- MUX** Multiplexer. Pages: [11](#), [15](#), [87](#), [88](#), [90–93](#), [99](#), [101](#), [106](#), [109](#), [113](#)

- NFS** Network File System. Page: [98](#)

- NIM** Non-interference Miter. Pages: [192–194](#), [198](#), [204](#), [205](#), [207](#), [222](#), [223](#)

- ODG** Overlay Description Graph. Pages: [78](#), [79](#), [83](#), [106–110](#), [112–115](#)

- OS** Operating System. Pages: [xx](#), [7](#), [50](#), [51](#), [96](#), [98](#), [120](#)

- OSIF** Operating System Interface. Pages: [50](#), [96](#), [229](#)

- PCAC** Proof-carrying Approximate Circuit. Pages: [208](#), [211](#), [212](#), [218](#), [219](#), [222](#)

- PCB** Proof-carrying Bitstream. Pages: [39](#), [41](#), [42](#), [155](#), [156](#), [160](#), [181](#), [193](#), [239](#)

- PCC** Proof-carrying Code . Pages: [3](#), [38](#), [39](#), [44](#), [53](#), [57](#), [58](#), [61](#), [62](#), [64](#), [66](#), [121](#), [244](#)

- PCH** Proof-carrying Hardware. Pages: [3–7](#), [10](#), [17](#), [20](#), [25](#), [27](#), [30](#), [33](#), [36](#), [38–41](#), [44](#), [45](#), [47–50](#), [53–55](#), [57–67](#), [69](#), [71](#), [73](#), [75](#), [76](#), [82](#), [95](#), [104](#), [120–124](#), [126–128](#), [130](#), [132](#), [133](#), [136](#), [137](#), [140–142](#), [144](#), [146](#), [147](#), [149–154](#), [157–160](#), [163–165](#), [167](#), [168](#), [171](#), [172](#), [175](#), [180–182](#), [184–188](#), [190](#), [191](#), [194–198](#), [200–205](#), [207–209](#), [211](#), [213](#), [214](#), [217](#), [218](#), [220–222](#), [225](#), [227](#), [229–235](#), [238](#), [241–246](#), *Glossary: Proof-carrying hardware*

- PCHIP** Proof-carrying Hardware Intellectual Property. Pages: [44](#), [45](#), [55](#), [61](#), [122](#), [123](#), [188](#), [199](#), [205](#)

- PDR** Property-directed Reachability. Pages: [30](#), [32](#), [33](#), [46](#), [128](#), [134](#), [142](#), [165](#), [217](#)–[221](#), [239](#), [243](#)

- PIP** Programmable Interconnect Point. Pages: [xxii](#), [11](#)–[13](#), [81](#), [82](#), [86](#), [90](#), [92](#), [104](#), [108](#)

- PL** Programmable Logic. Pages: [96](#), [99](#), [102](#), [162](#), [235](#)

- POSIX** Portable Operating System Interface. Pages: [50](#), [96](#)

- PrC** Property Checker. Pages: [xxii](#), [6](#), [26](#), [28](#), [32](#), [39](#), [42](#), [62](#), [63](#), [122](#), [123](#), [126](#)–[130](#), [133](#), [136](#), [137](#), [142](#), [144](#), [152](#), [172](#), [175](#)–[180](#), [184](#), [188](#), [189](#), [192](#), [196](#), [214](#), [242](#), [243](#), *Glossary: Property checker*

- PRNG** Pseudo Random-number Generator. Pages: [245](#), [246](#)

- PS** Processing System. Pages: [96](#), [97](#), [99](#), [235](#), [240](#)

- PSL** Property Specification Language. Pages: [28](#), [29](#), [154](#), [163](#), [227](#), [234](#), [237](#), [238](#), [241](#)–[243](#)

- PVC** Property Verification Circuit. Pages: [28](#), [31](#), [32](#), [41](#), [62](#), [63](#), [66](#), [121](#), [122](#), [126](#), [128](#), [130](#), [132](#)–[137](#), [139](#)–[144](#), [150](#), [155](#), [165](#), [172](#), [176](#)–[179](#), [181](#), [182](#), [184](#), [190](#)–[194](#), [198](#), [200](#)–[202](#), [204](#)–[207](#), [210](#), [214](#), [217](#), [222](#)–[225](#), [239](#), [243](#), *Glossary: Property verification circuit*

- QBF** Quantified Boolean Formula. Pages: [194](#)–[196](#)

- QBFV** Quantified Bit-vector Formula. Page: [196](#)

- QEC** Quality Evaluation Circuit. Page: [214](#)

- RAM** Random Access Memory. Pages: [xxi](#), [12](#), [17](#), [72](#), [78](#), [82](#), [93](#), [98](#), [99](#), [109](#), [157](#), [165](#), [167](#), [182](#), [200](#), [232](#)

- RFEC** Relaxed Functional Equivalence Checking. Pages: [208](#), [209](#), [214](#), [217](#), [222](#), [225](#), *Glossary: Relaxed functional equivalence checking*

- RR-graph** Routing Resource Graph. Pages: [74](#), [78](#), [80](#), [93](#), [106](#), [107](#), [112](#)–[114](#)

- rSoC** Reconfigurable System-on-chip. Pages: [5](#), [6](#), [69](#), [70](#), [74](#), [76](#), [81](#), [96](#), [97](#), [99](#), [120](#), [131](#), [132](#), [172](#), [228](#), [231](#)–[235](#), [240](#), [243](#)

- RTL** Register-transfer Level. Pages: [14](#), [44](#), [47](#), [55](#), [60](#), [122](#), [124](#), [188](#), [189](#)

- SAT** Boolean Satisfiability. Pages: [27](#), [31](#), [32](#), [41](#), [42](#), [44](#), [45](#), [48](#), [49](#), [65](#), [121](#), [122](#), [126](#)–[128](#), [130](#), [133](#), [142](#), [143](#), [155](#), [158](#), [163](#), [179](#)–[182](#), [189](#), [190](#), [195](#), [210](#), [215](#), [217](#), [231](#), [239](#)

- SCM** Self-composition Miter. Pages: [172](#), [192](#), [196](#), [222](#), [225](#), [245](#), [246](#)

- SDF** Standard Delay Format. Pages: [88](#), [106](#), [108](#)–[113](#), [115](#)

- SEC** Sequential Equivalence Checking. Pages: [xx](#), [xxii](#), [27](#), [128](#), [133](#), [152](#)

- SERE** Sequential Extended Regular Expression. Page: [29](#)

- SMT** Satisfiability Modulo Theories. Pages: [196](#), [245](#)

- SoC** System-on-chip. Pages: [12](#), [35](#), [67](#), [71](#), [73](#), [74](#), [84](#), [101](#), [157](#), [233](#), [235](#), [239](#), [241](#)

- SPC** Sequential Property Checking. Pages: [31](#), [128](#)–[130](#), [134](#), [142](#), [144](#), [146](#), [148](#), [150](#), [171](#), [172](#), [176](#), [177](#), [179](#), [182](#), [190](#), [210](#), [222](#)

**SQCC** Sequential Quality Constraint Circuit. Pages: [210](#), [214–219](#)

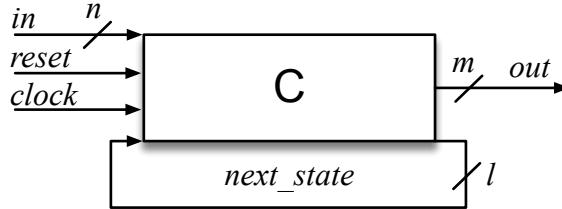

**SSC** Synchronous Sequential Circuit. Pages: [65](#), [84](#), [120–122](#), [127–132](#), [134](#), [135](#), [142](#), [149](#), [150](#), [168](#), [173](#), [175](#), [176](#), [185](#), [193](#), [198](#), [209](#), [225](#), [243](#), *Glossary: Synchronous sequential circuit*

**STA** Static Timing Analysis. Pages: [80](#), [88](#), [105](#), [176](#)

**SWT** Software Thread. Pages: [xx](#), [50](#), [96](#), [98](#), [228](#)

**TCB** Trusted Computing Base. Pages: [41](#), [45](#), [53–60](#), [65](#), [66](#), [73](#), [123](#), [128](#), [131](#), [157](#), [175](#), [177](#), [191](#), [192](#), [207](#), [238](#), [242](#), *Glossary: Trusted computing base*

**TCL** Tool Command Language. Page: [119](#)

**TLB** Translation Lookaside Buffer. Pages: [51](#), [161](#)

**TMR** Triple Modular Redundancy. Page: [223](#)

**TRNG** True Random-number Generator. Page: [246](#)

**UCF** User Constraint File. Page: [108](#)

**vFPGA** Virtual Field-programmable Gate Array. Pages: [xx](#), [xxi](#), [5](#), [45](#), [55](#), [58–61](#), [65](#), [67–77](#), [79](#), [80](#), [84–91](#), [95–98](#), [100](#), [101](#), [103–105](#), [110](#), [115–121](#), [157](#), [158](#), [160](#), [163](#), [225](#), [227](#), [229](#), [231](#), [233](#), [235](#), [240](#), [243](#), [245](#), *Glossary: Virtual field-programmable gate array*

**VPR** Versatile Place And Route. Pages: [46](#), [47](#), [71](#), [73](#), [78–80](#), [85](#), [86](#), [89](#), [90](#), [93](#), [105–107](#), [112–118](#)

**VTPR** Virtual Time Propagation Register. Pages: [74](#), [104](#), [117](#), [118](#)

**VTR** Verilog-to-routing. Pages: [7](#), [42](#), [43](#), [46](#), [47](#), [60](#), [69](#), [71–74](#), [76–78](#), [80](#), [84–86](#), [88](#), [90](#), [93](#), [113](#), [114](#), [155](#), [230](#), [238](#)

**WCCT** Worst-case Completion Time. Pages: [127](#), [133](#), [172](#), [174–177](#), [179](#), [180](#), [182–185](#), [208](#), [225](#)

**WCET** Worst-case Execution Time. Pages: [173](#), [174](#)

**XML** Extensible Markup Language. Pages: [46](#), [78](#), [93](#), [113](#)

## GLOSSARY

---

**AIGER** is a file format for [and-inverter-graphs \(AIGs\)](#) defined by Armin Biere. Pages: [47](#), [144](#), [190](#), [239](#)

**Approximate computing** denotes any form of computing that is performed deliberately at less than full precision, which is usually done to reduce some metric like energy consumption while exploiting some inherent error-resiliency in the target domain. Pages: [xv](#), [207](#)

**Checkable proof** is the result of a [formal verification](#) in form of a transcript or certificate, which can be checked for correctness

afterwards in order to verify the verification. Pages: [xxi](#), [38](#), [39](#), [48](#), [54](#), [63](#), [65](#), [130](#), [141](#), [148](#), [165](#), [167](#), [168](#), [190](#), [197](#), [210](#), [213](#), [225](#)

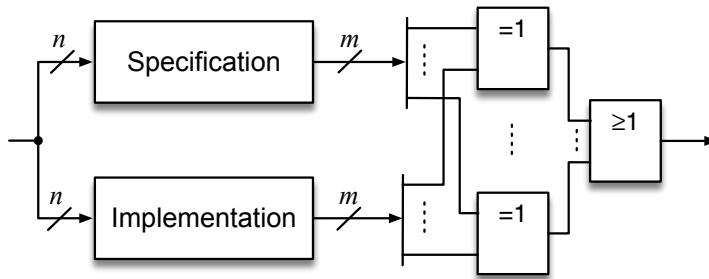

**Combinational circuit** is a circuit whose outputs solely depend on the current inputs, i. e., it saves no internal state that would affect the observable behavior. Pages: [26](#), [27](#), [31](#), [33](#), [41](#), [42](#), [55](#), [78](#), [82](#), [101](#), [121](#), [122](#), [126](#), [129](#), [130](#), [142](#), [143](#), [152](#), [155](#), [175](#), [179](#), [195](#), [210–212](#), [216](#), [231](#), *Compare: Sequential circuit*

**Covert channel** denotes an unintended flow of information between two circuit elements through existing ports, i. e., a hidden new information channel within existing ones. Pages: [185](#), [192](#), [195](#), [198](#), [199](#), [204](#), [206](#), [207](#)

**Delegate thread** is a special kind of **software thread (SWT)** in ReconOS that is acting on behalf of a **hardware thread (HWT)**, thus constituting the gateway by which the HW can have access to, e. g., **operating system (OS)** services, virtual memory, and shared memory. Pages: [xvi](#), [50](#), [51](#), [96](#), [97](#), [158](#)

**Embedded lookup table** is the term used by ZUMA to denote the virtual **lookup tables (LUTs)**, i.e., the LUTs of the ZUMA **virtual field-programmable gate array (vFPGA)**, in contrast to the physical lookup tables of the physical host **FPGA**. Pages: [xvi](#), [76](#)

**Extra-functional property** Pages: [124](#), [127](#), *see Non-functional property*

**Flip-flop** is a volatile sequential circuit element which can stably store a single bit as long as it is supplied with power. Pages: [xvi](#), [xxiii](#), [9](#), [11](#), [17](#), [31](#), [77](#), [78](#), [82](#), [130](#), [131](#), [135](#), [200](#), [236](#)

**Functional equivalence checking** is a formal HW verification technique that, depending on the circuit types, employs either **combinational equivalence checking (CEC)** or **sequential equivalence checking (SEC)** to verify that a given circuit exhibits the same observable behavior as another one, which usually is a so-called **golden model** of the circuit. Pages: [iii](#), [xvi](#), [25](#), [46](#), [121](#), [128](#), [152](#), [194](#), [197](#), [208](#)

**Functional property** is a property of a circuit that concerns its functionality, i.e., the observable behavior at the primary outputs. Pages: [40](#), [55](#), [56](#), [123](#), [124](#), [127](#), [171](#)

**Golden model** is a model or instance of a circuit which has been defined by someone as the correct reference design that implements the original design intent. Pages: [xx](#), [19](#), [55](#), [123](#), [124](#), [151](#), [152](#), [244](#)

**Hard-core** describes a hardware circuit which is implemented in actual, physical hardware (e. g., silicon) and that usually forms

a functional block, e. g., a **CPU**. Pages: [16](#), [50](#), [96](#), [99](#), *Compare: Soft-core*

**Inductive strengthening** is a circuit property which has the following three characteristics: *initiation*, i. e., it holds for all initial states, *consecution*, i. e., if it holds in one state then also in all of its immediate successors, and *strengthen*, i. e., compared to a base property, this one holds for the same or fewer states. Pages: [xvii](#), [128](#), [140](#), [142](#), [190](#), [202](#), [266](#), [267](#)

**Input interconnect block** is the ZUMA notation for the configurable routing network that connects the inputs of a **configurable logic block (CLB)** to the inputs of its **lookup tables (LUTs)**, as well as all outputs of the LUTs as feedback to the LUT inputs, such that any CLB input or LUT output can be used as input for any LUT. Pages: [xvii](#), [77](#), [90–92](#)

**Intellectual property core** is a tradable hardware module, usually containing the encoded netlist of a (potentially quite sizable) circuit that can be included as a building block in other hardware designs. Pages: [xvii](#), [1](#), [15](#), [19](#), [33](#), [39](#), [58](#), [78](#), [188](#), [235](#)

**Island-style** describes a regular layout style for reconfigurable hardware devices (such as **FPGAs**), where the actual configurable logic blocks (CLBs) are “islands” in the regular lattice of horizontal and vertical routing channels. Pages: [12](#), [14](#), [77](#), [78](#)

**Lookup table random access memory** is **RAM** made of lookup tables (LUTs), that can also be used as regular LUTs in data paths at the same time, which immediately lends itself to their use in **virtual field-programmable gate arrays (vFPGAs)**. Typically only a fraction of all LUTs on an FPGA are usable as RAM (e. g., half of them). Pages: [xvii](#), [72](#), [78](#)

**Non-functional property** is a property of a circuit that is not part of its observable behavior, i.e., two circuits which are functionally equivalent could still differ in these properties (e.g., area, latency). Pages: [6](#), [40](#), [56](#), [59](#), [124](#), [127](#), [133](#), [171–173](#), [175](#), [176](#), [182](#), [185](#), [208](#), [222](#), [225](#), [244](#), *Synonym: Extra-functional property*

**Overlay** is a circuit that is implemented on field-programmable gate arrays (FPGAs), which itself is implementing a configurable circuit that can be used to implement simpler circuits. Pages: [xxiii](#), [5](#), [6](#), [55](#), [58–60](#), [67–108](#), [110–120](#), [157](#), [158](#), [160](#), [162](#), [163](#), [182](#), [229–233](#), [235](#), [238](#), [240](#), [241](#), [245](#)

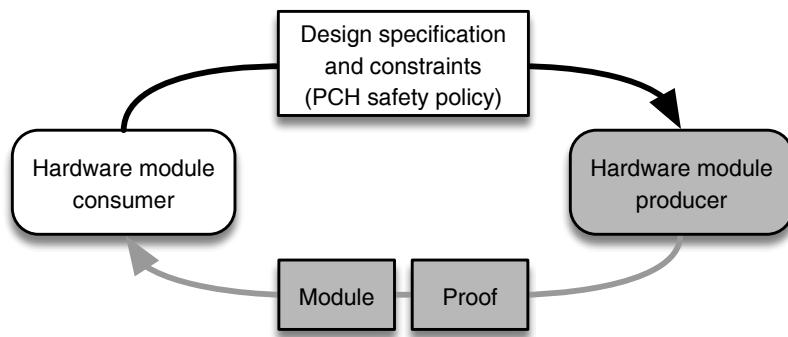

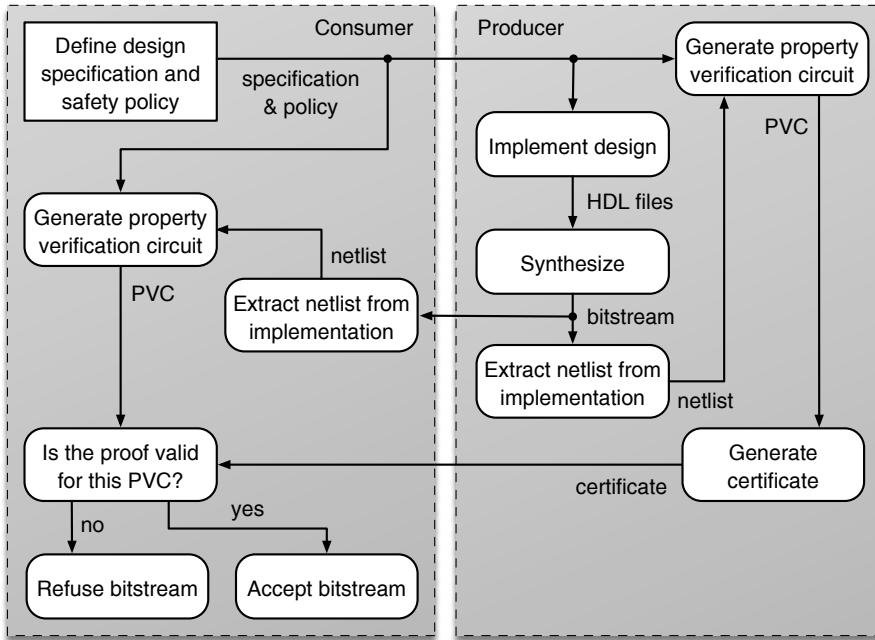

**Proof-carrying hardware** denotes a distributed just-in-time verification technique between two parties who exchange a hardware module in trade and leverage a **checkable proof**, i. e., an artifact of a **formal verification**, to establish a guarantee for the trustworthiness of the consigned representation in terms of

some a priori agreed-upon properties at a much lower computational cost than performing the formal verification. Pages: [iii](#), [xvii](#), [3–7](#), [10](#), [17](#), [38–40](#), [43](#), [48](#), [53](#), [55](#), [61](#), [62](#), [64](#), [67](#), [69](#), [73](#), [104](#), [120](#), [121](#), [127](#), [128](#), [142](#), [143](#), [150](#), [151](#), [154](#), [155](#), [159](#), [163](#), [165](#), [171](#), [181](#), [186](#), [191](#), [200](#), [214](#), [222](#), [225](#), [227](#), [229](#), [232–234](#), [239](#), [242–245](#), [261](#), [270](#),

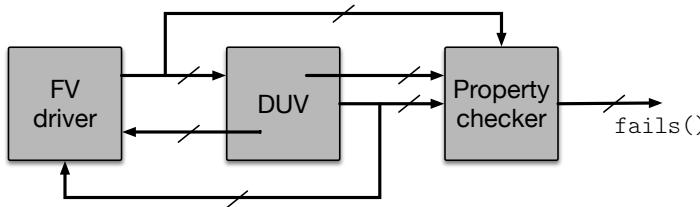

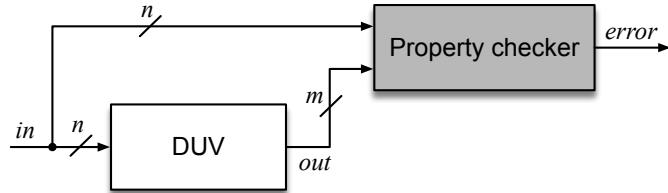

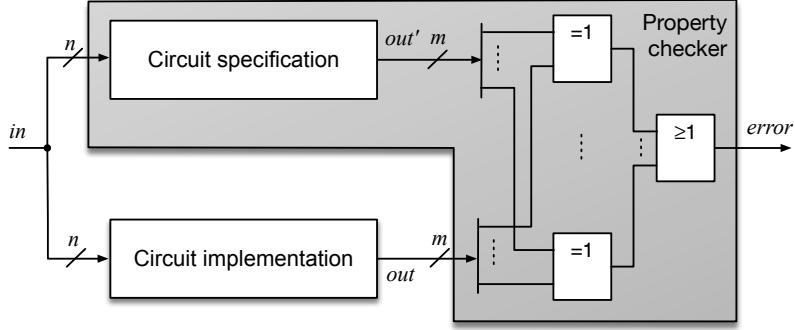

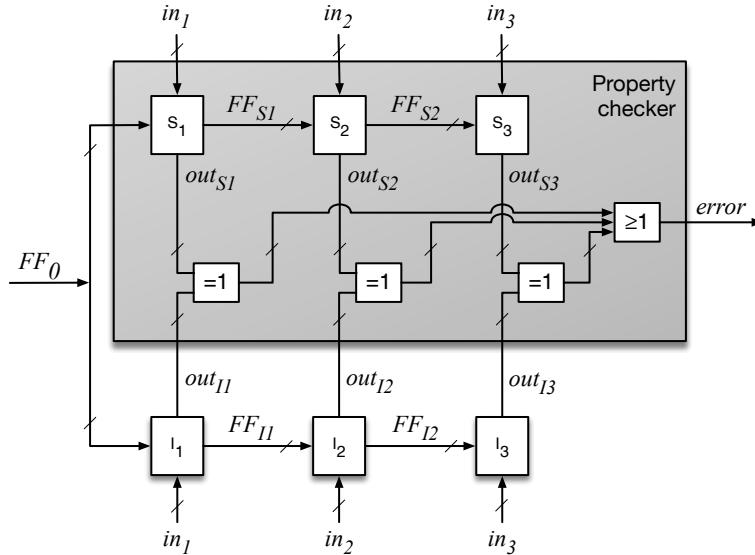

**Property checker** is a piece of circuitry that has only one output and can evaluate whether or not another circuit has the encoded property, by observing the other circuit's primary I/Os (black-box verifications) or even its internal signals (white-box verifications); the checker's output *error* evaluates to *true* whenever the **design under verification (DUV)** violates the property. Pages: [xviii](#), [xxii](#), [28](#), [31](#), [32](#), [42](#), [43](#), [63](#), [122](#), [128](#), [129](#), [133](#), [136](#), [142](#), [144](#), [172](#), [176](#), [177](#)

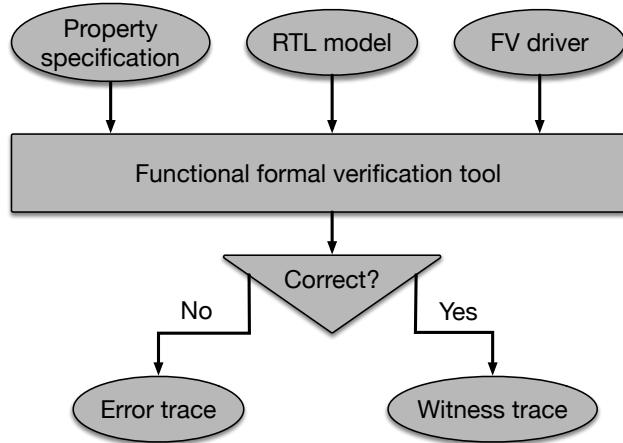

**Property verification circuit** is a composite circuit description that is meant to be an input to a verification engine to prove its unsatisfiability; it combines a design under verification (DUV) and a **property checker (PrC)**, distributes the exact same primary inputs to them every cycle (which are driven by the verification engine), forwards the DUV's primary outputs to the PrC and evaluates whether or not the PrC indicates a property violation at its *error* output. Pages: [xviii](#), [28](#), [31](#), [41–43](#), [62](#), [63](#), [121](#), [122](#), [126](#), [128](#), [129](#), [131](#), [138](#), [139](#), [142](#), [145](#), [150](#), [152](#), [155](#), [171](#), [172](#), [176](#), [177](#), [190](#), [191](#), [210](#), [214](#), [215](#), [223](#), [239](#), [243](#), [254](#)

**Relaxed functional equivalence checking** is a formal HW verification technique that, depending on the circuit types, employs either **combinational equivalence checking (CEC)** or **sequential equivalence checking (SEC)** to verify that a given circuit exhibits the same observable behavior as another one, relaxed by a certain amount of error tolerable in the target domain of the design under verification (DUV). Pages: [xviii](#), [208](#), [215](#), [217](#), [222](#)

**Routing resource** are all the wires and **programmable interconnect points (PIPs)** that form the interconnection network on an **FPGA**, which is used to route signals of the design to the logic components. Pages: [15](#), [70](#), [76](#), [80](#), [85](#), [87](#), [88](#), [91–95](#), [100](#), [106](#), [113](#), [160](#)

**Sequential circuit** is a circuit whose outputs depend on its current inputs and its internal state, i. e., it retains a continuously updated state that (usually) affects the observable behavior. Pages: [xxiii](#), [24](#), [27](#), [28](#), [31](#), [33](#), [42](#), [55](#), [63](#), [66](#), [76](#), [82](#), [84](#), [122](#), [128–132](#), [134](#), [144](#), [146](#), [149](#), [152](#), [155](#), [173](#), [175](#), [176](#), [209–212](#), [214](#), [216–218](#), [222](#), [223](#), [243](#), *Compare: Combinational circuit*

**Soft-core** describes a hardware circuit which is implemented in reconfigurable hardware (e.g., FPGAs) and that usually forms a functional block, e.g., a [CPU](#). Pages: [36](#), [50](#), [73](#), [200](#), [228](#), [232](#), [240](#), *Compare: Hard-core*

**Synchronous sequential circuit** is a [sequential circuit](#) where all sequential elements (e.g., [flip-flops \(FFs\)](#)) are clocked to one global clock. Pages: [xix](#), [65](#), [84](#), [120](#), [121](#), [127](#), [128](#), [131](#), [134](#), [135](#), [142](#), [150](#), [168](#), [173](#), [175](#), [185](#), [193](#), [198](#), [209](#), [225](#), [243](#)

**Trusted computing base** is the set of files and tools that need to be trusted by a user to perform a verification, i.e., this set constitutes the root of trust of the verification process. Pages: [xix](#), [41](#), [53](#), [59](#), [65](#), [66](#), [73](#), [123](#), [128](#), [131](#), [175](#), [191](#), [207](#), [238](#), [242](#)

**Virtual field-programmable gate array** is a special [FPGA overlay](#) that implements a fine-grained reconfigurable array itself. Pages: [xix–xxi](#), [5](#), [45](#), [55](#), [58](#), [60](#), [61](#), [65](#), [67](#), [69](#), [71](#), [76](#), [84](#), [119–121](#), [163](#), [225](#), [227](#), [231](#), [243](#), [245](#),

## INTRODUCTION

---

This chapter will outline and motivate the broad academical context in which this thesis exists in Section 1.1, detail the specific contributions to the body of research that our subsumed work represents in Section 1.2, and explain the structure of the entire thesis document in Section 1.3.

### 1.1 MOTIVATION

Reconfigurable hardware devices have gained increasing attention in academia as well as industry over the past few decades. Their software-like flexibility, combined with their spatial computation paradigm, i. e., spreading out computations in space rather than time, allow them to adapt to new challenges by becoming highly parallel or deeply pipelined application-specific compute units. For actual workloads, this ability enables them often to solve specific tasks much more energy efficient than any other type of computing device, which makes them highly attractive for environments that have to be mindful of how they spend their energy budget, like low-energy battery-powered devices, or high-energy warehouse-scale computers. [field-programmable gate arrays \(FPGAs\)](#), the most prominent representatives of the reconfigurable hardware device category, are in fact already deployed in many diverse areas such as avionics, supercomputing, video analysis, high-throughput cryptography, intrusion detection and prevention, and even on Mars [1, 2]. In all of these environments they perform a variety of functions, some of which are also mission critical.

When compared to traditional general-purpose [integrated circuits \(ICs\)](#) or [application-specific ICs \(ASICs\)](#), reconfigurable hardware devices tend to have much faster design cycles, due to high potential and good market support for design reusage in the form of so-called third-party [intellectual property cores \(IP-cores\)](#), and due to the fact that FPGAs are readily available as [commercial off-the-shelf \(COTS\)](#) devices and do not have to be physically manufactured as part of the design process. These faster cycles enable a significantly lowered time-to-market, which especially helps in markets that mainly work in a winner-takes-it-all fashion.

With the increased interest in these devices, came a growing market for them, especially when big international players made their moves, such as Intel buying Altera, or Microsoft outfitting whole data centers with FPGAs. A growing market, however, also has the downside of making reconfigurable hardware increasingly attractive as a target for

criminal elements and espionage, be it industrial or between nations, and hence research into reconfigurable hardware security has also gained a lot of traction over the past decades. The differences between ASICs and reconfigurable hardware devices also result in different attack vectors which could render devices susceptible to malicious modifications.

On the one hand, **FPGA** base arrays are indeed traditional **ICs** themselves, and thus inherit their attack possibilities, of which the untrusted offshore foundry is the most commonly assumed weak link in the fabrication chain. Trimberger [3] points out, however, that these base arrays do not hold complete designs yet, as they are missing the runtime device configuration, which is an essential component of the final device functionality. A potential adversary hence cannot target their attack based on the final circuit and would have to spread it as a probabilistic attack over the whole fabric, significantly lowering their chance of success. And especially for **COTS** devices Trimberger elaborates that adversaries have no way of knowing which device will end up being bought by whom, and to reliably attack the interesting targets they thus have to modify all produced base arrays, which will submit their malicious design changes to the inadvertent thorough testing of every customer that uses such a device in the future, resulting in a significantly elevated chance of exposure.

Although these factors lower the attractiveness of subverting the reconfigurable part of the base array, traditional IC security research is also not irrelevant for FPGAs devices, since there are many fixed-function building blocks on modern devices, which could be targeted instead of the programmable logic; in fact, such attacks have actually been observed in the wild [4]. The main threat to design security of the actual reconfigurable part, however, are attacks on the configuration instead of the base array. The device configuration, which is usually stored in a file called *configuration bitstream*, or simply *bitstream*<sup>1</sup>, can be compromised by several means (cp., e. g., [3, 5]):

**IP-CORES:** The design can be attacked through the inclusion of untrusted IP-cores. These could be modified either by their respective creator, or even by third parties during their creation or by intercepting them in transit.

**EDA TOOLS:** Compromised electronic design automation tools can modify the result of the translation from the design's source code to the device configuration, unbeknownst to their user.

**DIRECT TAMPERING:** An FPGA configuration in storage or transmission can also be directly changed by powerful adversaries who can interpret their proprietary content, e. g., most recently

---

<sup>1</sup> We will use the term *bitstream* in this thesis to refer to a device configuration in general, meaning it can be either stored in a file using a special format, or distributed to the corresponding configuration points on an FPGA device.

demonstrated by Ender, Moradi, and Paar [6] who even circumvented the encryption and authentication mechanisms for bitstreams.

**PHYSICAL ACCESS:** Since **FPGAs** are typically reprogrammable in the field by design, any attacker with physical access can potentially exchange the current configuration with a modified one.

Companies or engineers looking to create a design that benefits from the promise of a very fast time-to-market with FPGAs are thus facing a dilemma: To reach competitive productiveness they have to heavily rely on third-party **IP-cores** for large parts of their design, and they have no other choice than to use the **electronic design automation (EDA)** tool chain provided by the FPGA device vendor, but any of these could contain malicious modifications by an attacker. Such a creator thus has no way of knowing if their bitstream will implement (only) their intended behavior or will be modified before it reaches their customers, which could jeopardize their reputation. By following this process, which is indeed today's standard process to create new hardware, regardless whether it is an **IC** or reconfigurable hardware device, the creator thus implicitly trusts all involved third parties and transmission channels to be secure and non-malicious, just as the final customer trusts the creator and all intermediate parties who handle the design and device.

Since a trustworthy creator may thus actually sell maliciously modified hardware without realizing it, the only way to establish that a design or IP-core deserves trust is to verify it. A thorough verification is quite cumbersome and lengthy, however, especially if it is a black-box verification, i. e., one without knowing anything about the interior layout of the design / device, which is counterproductive to achieving a low time-to-market. The creator can moreover only verify all entities they receive themselves, but cannot make sure that their final design is not modified on its way to their customer, as in the attack presented by Ender, Moradi, and Paar [6], where the final user receives a valid encrypted and authenticated bitstream that is completely under the control of the attacker. This means that to establish full trust, the final user would have to perform their own verification of the creator's design, which is usually not a valid option due to, e. g., lack of resources.

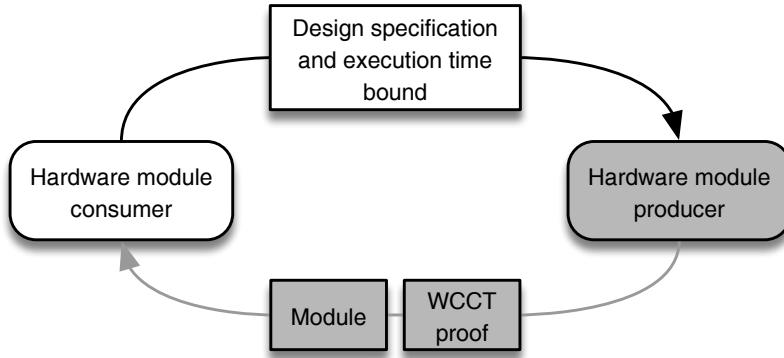

With the proposal of **proof-carrying hardware (PCH)**, Drzevitzky, Kastens, and Platzner [7] have introduced a method to overcome this dilemma of how to establish trust where thorough design verifications would have to be performed by parties who are ill equipped for them, or under considerable time pressure to meet market demands. Analogous to a software verification concept called **proof-carrying code (PCC)**, they have devised a scheme, where the sending party verifies

their own design and send a certificate of compliance to some predefined set of rules along with it. The recipient can then easily validate the certificate just-in-time and make sure that it belongs to the received design, and thereby gains the benefits of a thorough verification with just a fraction of its original cost in time and computational effort. As the name *proof-carrying hardware* implies, the certificate is meant to be evidence of a formal proof which has been shown for the design.

The original authors have defined the concept and have also created a first tool flow to showcase the successful utilization of the approach with some benchmarks. They have implemented a way to apply the **PCH** method, by having the sender create a certificate for the design implementation's functional equivalence to its original specification. This procedure is popular in the functional verification of hardware designs, and will catch any and all bugs in a design that alter its functionality, as it is a **formal verification (FV)** method. Unfortunately, eliminating all bugs is not quite enough to establish trust in a design, as we additionally have to consider the intent of an attacker who could undermine that trust. Vosatka [8] writes that a “malicious modification of a circuit that is designed to alter the circuit’s behavior in order to accomplish a specific objective” should not be considered to be the same as unintentional design bugs, since only the latter are bounded by the original specification, whereas the former deliberately goes beyond that bound.

As is true for most attack and defense environments, proof-carrying hardware is thus part of an arms race with ever more sneaky and subtle malicious modifications, today usually called **hardware Trojans**, versus a growing arsenal of verification, detection, prevention and design hardening methods. This thesis reflects our efforts to increase PCH’s clout in this race, by enabling studies of real PCH-protected circuits and increasing the expressiveness and applicability of the method.

## 1.2 THESIS CONTRIBUTIONS

This thesis adds to the body of research about proof-carrying hardware (PCH) and defines a new state of the art for its application to the verification of reconfigurable hardware device configurations:

1. As main contribution, we significantly extend the scope of PCH – from a theoretic concept with a proof-of-concept flow that is limited to abstract [FPGAs](#) and one safety policy, i. e., [combinational equivalence checking](#), to a more practical version with a wide range of verifiable properties and more complex safety policies (Chapters [5](#) and [6](#)).

2. As secondary contribution, we introduce our adaption, extension and embedding of a fine-grained FPGA [overlay](#), i. e., a [virtual field-programmable gate array](#), that is capable of bringing PCH-certified circuits onto actual modern reconfigurable hardware (Chapter [4](#)).

3. We underline the feasibility of applying our research by providing a Linux-based [reconfigurable system-on-chip \(rSoC\)](#) testbed for PCH (Section [4.4](#)) and supplementing it with two complete demonstrator setups that we successfully employed in live demonstrations to showcase the complete remote verification flow (Chapter [7](#)).

4. To complement these contributions and to fully leverage their potential, we furthermore present an advanced tool flow which comprises powerful state-of-the-art tools for verification and synthesis (Section [3.2](#)).

## 1.3 THESIS ORGANIZATION

This document is structured as follows. In Chapter [1](#), the current one, we introduce the research field and motivation for this thesis, the specific contributions and explain the thesis structure. Chapter [2](#) explains all relevant concepts and generally related work, first for reconfigurable hardware, then for functional verification in general and [PCH](#) specifically, and then concludes with a brief introduction of all tools and platforms used within the thesis.

In Chapter [3](#) we explain in detail why we chose the bitstream level for our research, despite the obvious disadvantage of not being able to understand the vendor's file format.

Chapter [4](#) discusses our contribution of a complete [rSoC](#) based on the combination of ReconOS, a powerful Linux-based architecture and execution environment for hybrid HW / SW systems, and ZUMA, a state-of-the-art fine-grained [virtual field-programmable gate array](#) which we have significantly extended, e. g., by devising a means to

perform timing-driven routing for circuits in the overlay which is rooted in the actual physical properties of the underlay. We have also defined a complete Linux-based rSoC with the overlay that we introduce in this chapter, which can be used as testbed and rich environment for bitstream-level verifications, as it leverages an open configuration bitstream format.

We discuss and elaborate the main contribution of this thesis, i. e., how we extended the scope of [proof-carrying hardware](#) to certify a wider range properties, in Chapter 5 for [property checking](#), and in Chapter 6 for [non-functional properties](#). The range of new possibilities using our proposed mechanisms include partial functional verification, verification without golden model or specification, and certification of non-functional properties, i. e., circuit properties that do not directly affect the observable behavior, such as a guarantee that some secret data will never be leaked.

Chapter 7 presents the PCH demonstrators, i. e., prototypes which have been developed to showcase the application of the research from the other chapters, such as the ability to generate PCH certificates from assertions formulated in the powerful [hardware verification language \(HVL\)](#) SystemVerilog. The demonstrators furthermore show successful applications of our comprehensive flow for PCH and its interaction with the [overlay](#) to include PCH-certified designs in modern [FPGAs](#).

The last two chapters, Chapter 8 and Chapter 9 conclude the thesis and present a brief outlook on possible future work in the area of proof-carrying hardware.

# 2

## BACKGROUND

---

|       |                                               |    |

|-------|-----------------------------------------------|----|

| 2.1   | Reconfigurable Hardware . . . . .             | 7  |

| 2.1.1 | Field-Programmable Gate Arrays . . . . .      | 10 |

| 2.1.2 | Design Flow . . . . .                         | 14 |

| 2.1.3 | Characteristics . . . . .                     | 15 |

| 2.2   | Hardware verification . . . . .               | 16 |

| 2.2.1 | Functional Verification . . . . .             | 17 |

| 2.2.2 | Simulation-based Verification . . . . .       | 20 |

| 2.2.3 | Formal Verification . . . . .                 | 23 |

| 2.2.4 | Model Checking . . . . .                      | 30 |

| 2.2.5 | Monitoring and Enforcement . . . . .          | 33 |

| 2.3   | Proof-carrying Hardware . . . . .             | 38 |

| 2.3.1 | Early Bitstream-Level Proof-carrying Hardware | 39 |

| 2.3.2 | Register-transfer Level PCHIP                 | 44 |

| 2.4   | Tools and Platforms . . . . .                 | 45 |

| 2.4.1 | ABC . . . . .                                 | 45 |

| 2.4.2 | VTR . . . . .                                 | 46 |

| 2.4.3 | Yosys . . . . .                               | 47 |

| 2.4.4 | PicoSAT and Tracecheck . . . . .              | 48 |

| 2.4.5 | CaDiCaL . . . . .                             | 48 |

| 2.4.6 | DRAT-trim . . . . .                           | 49 |

| 2.4.7 | Gratgen and Gratchk . . . . .                 | 49 |

| 2.4.8 | ReconOS . . . . .                             | 50 |

This chapter shall serve as a reference to relevant work which is related to the entirety of the thesis. Research related only to small aspects will be presented within the context of that aspect of the thesis, but in this chapter we will discuss the general research fields of reconfigurable hardware and computing in Section 2.1, challenges and general approaches to the verification thereof in Section 2.2, the body of research on **proof-carrying hardware (PCH)** which came before this thesis in Section 2.3, and some of the tools and platforms used within this thesis, such as ReconOS, the Linux-based **operating system (OS)** for reconfigurable HW / SW systems, or the Verilog-to-routing (VTR) tool flow, in Section 2.4.

### 2.1 RECONFIGURABLE HARDWARE

The focus of this thesis is to create formally verified guarantees for properties of circuits that are implemented on reconfigurable hardware, which is a special type of programmable hardware; a class of devices whose function can be changed after fabrication. The idea

of flexibly adaptable hardware is commonly attributed to Estrin [9], who proposed the concept in 1960 to “permit computations which are beyond the capabilities of present systems” by temporarily rearranging the hardware into “a problem oriented special purpose computer.” Actual devices that follow this idea have been around for roughly half a century by now, first in the form of masked programmable gate arrays (MPGAs) that comprise of a regular array of transistors, gates, or blocks, and which can be produced in bulk, and hence at a rather low price [10]. The devices are programmed by adding channels between the blocks in a final, application-specific production step, that can happen at a later point in time, thus enabling cost-efficient low-volume manufacturing of **integrated circuits (ICs)**, but without the option to later reprogram the device. The main benefit of MPGAs is thus the significantly shortened time-to-market, as the generic array itself can be manufactured in advance and then stored, and the adaptation of the generic structures with the application-specific channels can be achieved in a matter of weeks, giving such devices a significant advantage over traditionally produced ICs. This shorter lead time can have a large impact in a situation where there is competition for ICs of that functionality, as arriving six months later at the market can then result in a loss of revenue of about one third over the lifetime of the product [10], as in IC design, a disproportionate amount of said revenue goes to the product that is first available at the market [11].

Around the same time as MPGAs, another family of programmable devices was introduced, usually grouped together as simple programmable logic devices (SPLDs), that typically have a size equivalent to roughly 1000 logic gates [10]. Devices of this type usually consist of two or several arrays of logic, offering fixed functions with programmable connection points: A programmable logic array (PLA) for instance has a programmable *AND*-plane followed by a programmable *OR*-plane, allowing a designer to program the device to calculate any Boolean function that is small enough as sum of products over the available inputs by just enabling or disabling the junctions in the wiring of both planes. Over the course of a decade, SPLDs evolved into field-programmable devices (FPDs), which, according to Brown et al. [12], is “a device that can be configured by the user with simple electrical equipment,” in contrast to the high effort and special equipment that was necessary to reprogram the earlier devices. One example of this development is read-only memory (ROM), which evolved from programmable ROMs (PROMs) over UV light erasable PROMs (EPROMs) to electrically erasable PROMs (EEPROMs), which can be updated more or less instantly without any special tools by any user in the field.

Programmable logic devices (PLDs) continued to grow in size and complexity, especially when complex PLDs (CPLDs) were introduced in the beginning of the 1980s which combined several SPLDs into

one **IC** by arranging them as macro cells or logic array blocks (LABs) around a central programmable interconnect [10], thereby also greatly increasing the complexity of the functionality that can be implemented in this kind of devices. The abundance of logic resources available on CPLDs, their ability to store their configuration in non-volatile memory, and their predictable and fast timing, i. e., small **I/O** pin to I/O pin delay, make them a viable choice even today, for specific tasks where these features are necessary [10]. Since complex datapaths often require much storage, however, and not only many logic resources in a sea-of-gates as CPLDs offer, a new device type called **field-programmable gate array (FPGA)** was introduced a few years later, seeking to strike a different balance between the availability of logic and registers while adopting the programmable interconnect of CPLDs. FPGAs aim to combine the flexible programmability of PLDs with the high efficiency of MPGAs, by replacing the individually fabricated channels of the latter with a programmable interconnect, and the prefabricated fixed-function cells with programmable logic [10].

The main differences of CPLDs and **FPGAs** derive from their respective basic building blocks: where CPLDs consist of a number of SPLDs, and thus large and wide matrices of *AND* and *OR*-planes, FPGAs are much more fine-grained and are built from small **configurable logic blocks (CLBs)**, which in turn are realized with a number of very narrow **lookup tables (LUTs)** (typically at most 6 : 1) and registers, i. e., **flip-flops (FFs)** [10]. The CLBs of FPGAs lend themselves to complex sequential algorithms, but these also induce a high realization effort within the **computer-aided design (CAD)** flow, as the actual timing of the signals depends on the configuration of the logic and the interconnect, and it can thus be quite challenging to find a combination that is fast enough for a given problem. CPLDs on the other hand can be most advantageous for applications that are mostly combinational in nature and require little to none internal state information, as for these the fixed, unsegmented pathways within the device allow for a very fast and predictable signal propagation that is not dependent on the current circuit configuration, unless it introduces long feedback loops [10].

With their capability to be reprogrammed many times in the field, both device types surpass the original meaning of programmable HW, which is why their current programming is often referred to as *configuration*, to reflect its malleable nature. Miyazaki [13] distinguishes, i. a., the following configurable types of devices:

**CONFIGURABLE LOGIC** is configurable exactly once in a destructive process, e. g., burning a fuse, which prevents further reconfigurations. This type thus also describes the early programmable hardware such as MPGAs.

**RECONFIGURABLE LOGIC** is reconfigurable many times, but only by using a special setup or system which sets the device in

a reconfiguration mode. This is also referred to as "in-system programming", and would for instance encompass EPROMs.

**DYNAMICALLY RECONFIGURABLE LOGIC** provides the capability to be reconfigured on-the-fly, also denoted as "in-circuit reconfiguration". Devices of this type can be reconfigured in their regular operation environment and often from within the circuit itself, and are typically based on static random access memory (SRAM) cells that store the current hardware configuration in a volatile way. Hutchings and Nelson [14] subdivide this category even further in devices capable of global or local runtime reconfiguration, where the former would reset the whole device, while the latter would allow configured circuit parts to be left running undisturbed, while another area of the chip is being reconfigured.