FRAMEWORKS AND METHODOLOGIES FOR

SEARCH-BASED APPROXIMATE LOGIC SYNTHESIS

DISSERTATION

A thesis submitted to the

FACULTY FOR COMPUTER SCIENCE, ELECTRICAL ENGINEERING AND

MATHEMATICS

of

PADERBORN UNIVERSITY

in partial fulfillment of the requirements

for the degree of *Dr. rer. nat.*

by

LINUS MATTHIAS WITSCHEN

Paderborn, Germany

Date of submission: June 2022

**SUPERVISOR:**

Prof. Dr. Marco Platzner

**REVIEWERS:**

Prof. Dr. Marco Platzner

Prof. Dr. Sybille Hellebrand

Prof. Dr. Laura Pozzi

**ORAL EXAMINATION COMMITTEE:**

Prof. Dr. Marco Platzner

Prof. Dr. Sybille Hellebrand

Prof. Dr. Laura Pozzi

Prof. Dr. Christian Plessl

Dr. Michael Laß

**DATE OF SUBMISSION:**

June 2022

Dedicated to my parents.

And they that are wise shall shine

as the brightness of the firmament;

and they that turn many to righteousness

as the stars for ever and ever.

— Daniel 12:3

---

## ACKNOWLEDGMENTS

---

Many people supported me in realizing my dissertation and enabled me to achieve my goals. First and foremost, I would like to express my deepest gratitude to Prof. Dr. Marco Platzner for his support and guidance during my entire research, as well as for teaching me that good research is more than just academic skills. Furthermore, I want to thank him, Prof. Dr. Sybille Hellebrand, and Prof. Dr. Laura Pozzi for the time and effort they spent reviewing this dissertation and all committee members for evaluating my work.

I am indebted also to all my colleagues and co-workers who kept me sane through well-timed coffee breaks and kept me motivated by daydreaming of changing the future through research. Here, I want to note my colleagues from approximate computing: Hassan Ghasemzadeh Mohammadi and Muhammad Awais, who helped me advance my research, and especially Tobias Wiersema for guiding me through my Master's thesis and the many fruitful discussions. Moreover, I would like to recognize my student research assistants, project group members, and the students writing their thesis with me for contributing to my research projects.

Special thanks to Angela Gutierrez for slipping into the role of a rubber duck and helping me solve many of my research challenges by listening. You have been a pillar on my journey, and your affection made me forget about stressful times.

Finally, I am incredibly grateful to my family for their encouragement and support. Especially, I would like to thank my mother for her endless support and never ending care. In my profound appreciation, I esteem my late father's guidance throughout my (academic) life. He shaped me as a person and has always been a role model; following his advice, I did as well as I could...

---

## ABSTRACT

---

Approximate computing has emerged as one way to meet the challenge of improving a computing system's performance by trading off an application's quality against a target metric. This dissertation focuses on approximate computing at hardware level, where it is referred to as approximate logic synthesis (ALS) and has the goal of generating approximate circuits; specifically, this dissertation makes five contributions and comprehensively considers automated search-based ALS processes that are modeled with four main steps: *search*, *approximate*, *verify*, and *estimate*.

Firstly, this dissertation contributes the CIRCA framework that implements a general and fully configurable ALS process to provide an environment for comparing different ALS methods. Secondly, we propose the jump search methodology that minimizes syntheses and verifications by exploiting domain knowledge to rapidly generate approximate circuits. Thirdly, the technique MUSCAT contributes to the approximation step and utilizes formal verification techniques to construct approximate circuits that are valid-by-construction regarding their quality. The fourth contribution considers the verification step and is the concept of proof-carrying approximate circuits, which brings together the fields of approximate computing and proof-carrying hardware. Finally, this dissertation proposes a formal verification-based methodology that characterizes the search space of approximate circuits prior to the ALS process.

---

## ZUSAMMENFASSUNG

---

Approximate computing hat sich als ein Weg herauskristallisiert, die Verarbeitungsleistung von Rechensystemen weiter zu steigern, indem die Qualität einer Anwendung gegen eine Zielmetrik eingetauscht wird. Diese Dissertation betrachtet approximate computing auf der Hardwareebene, auf der es approximierte Schaltungen generiert und als approximate logic synthesis (ALS) bezeichnet wird. Konkret leistet die Arbeit fünf Beiträge und betrachtet automatisierte, suchbasierte ALS Prozesse, die in vier Schritten modelliert werden: *suchen, approximieren, verifizieren und abschätzen*.

Zunächst stellt die Dissertation das Framework CIRCA vor, das den ALS Prozess allgemeingültig und konfigurierbar implementiert und so eine Umgebung für den Vergleich von ALS Methoden bereitstellt. Anschließend wird das Suchverfahren jump search diskutiert, das approximierte Schaltungen schnell generiert, indem es Synthesen und Verifikationen mittels Domänenwissen minimiert. Des Weiteren wird die Approximationstechnik MUSCAT vorgestellt, die auf formaler Verifikation basiert und Schaltungen hinsichtlich ihrer Qualität korrekt konstruiert. Ferner betrachtet die Arbeit den Verifikationschritt und stellt das Konzept von proof-carrying approximate circuits vor, das die Felder approximate computing und proof-carrying hardware vereint. Abschließend behandelt die Arbeit ein auf formaler Verifikation basierendes Verfahren, das vorab den Suchraum von approximierten Schaltungen für den ALS Prozess charakterisiert.

---

## AUTHOR'S PUBLICATIONS

---

- [1] Alexander Boschmann, Andreas Agne, Georg Thombansen, Linus Witschen, Florian Kraus, and Marco Platzner. "Zynq-based acceleration of robust high density myoelectric signal processing." In: *Journal of Parallel and Distributed Computing* 123 (2019), pp. 77–89. DOI: [10.1016/j.jpdc.2018.07.004](https://doi.org/10.1016/j.jpdc.2018.07.004).

- [2] Alexander Boschmann, Andreas Agne, Linus Witschen, Georg Thombansen, Florian Kraus, and Marco Platzner. "FPGA-based acceleration of high density myoelectric signal processing." In: *Proceedings of the International Conference on ReConfigurable Computing and FPGAs (ReConFig)*. [Best New Applied Domain Paper Award]. IEEE, 2016. DOI: [10.1109/reconfig.2015.7393312](https://doi.org/10.1109/reconfig.2015.7393312).

- [3] Alexander Boschmann, Georg Thombansen, Linus Witschen, Alex Wiens, and Marco Platzner. "A Zynq-based dynamically reconfigurable high density myoelectric prosthesis controller." In: *Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE)*. 2017. DOI: [10.23919/DATE.2017.7927137](https://doi.org/10.23919/DATE.2017.7927137).

- [4] Linus Witschen. "A Framework for the Synthesis of Approximate Circuits." Master's Thesis. Paderborn, Germany: Paderborn University, Aug. 2017.

- [5] Linus Witschen. *CIRCA – A Modular and Extensible Framework for Approximate Circuit Generation*. [Online]. 2018. URL: <https://go.unipaderborn.de/circa>.

- [6] Linus Witschen, Muhammad Awais, Hassan Ghasemzadeh Mohammadi, Tobias Wiersema, and Marco Platzner. "CIRCA: Towards a Modular and Extensible Framework for Approximate Circuit Generation." In: *Microelectronics Reliability* 99 (2019), pp. 277–290. DOI: [10.1016/j.microrel.2019.04.003](https://doi.org/10.1016/j.microrel.2019.04.003).

- [7] Linus Witschen, Hassan Ghasemzadeh Mohammadi, Matthias Artmann, and Marco Platzner. "Jump Search: A Fast Technique for the Synthesis of Approximate Circuits." Workshop on Approximate Computing (AxC). Workshop without proceedings. 2019.

- [8] Linus Witschen, Hassan Ghasemzadeh Mohammadi, Matthias Artmann, and Marco Platzner. "Jump Search: A Fast Technique for the Synthesis of Approximate Circuits." In: *Proceedings of the Great Lakes Symposium on VLSI (GLSVLSI)*. ACM, 2019. DOI: [10.1145/3299874.3317998](https://doi.org/10.1145/3299874.3317998).

- [9] Linus Witschen, Tobias Wiersema, Hassan Ghasemzadeh Mohammadi, Muhammad Awais, and Marco Platzner. "CIRCA: Towards a Modular and Extensible Framework for Approximate Circuit Generation." Workshop on Approximate Computing (AxC). Workshop without proceedings. 2018.

- [10] Linus Witschen, Tobias Wiersema, and Marco Platzner. "Making the Case for Proof-carrying Approximate Circuits." Workshop on Approximate Computing (WAPCO). Workshop without proceedings. 2018. URL: <https://api.semanticscholar.org/CorpusID:52228901>.

- [11] Linus Witschen, Tobias Wiersema, and Marco Platzner. "Proof-carrying Approximate Circuits." In: *IEEE Transactions on Very Large Scale Integration (VLSI) Systems* 28 (9 2020), pp. 2084–2088. doi: [10.1109/TVLSI.2020.3008061](https://doi.org/10.1109/TVLSI.2020.3008061).

- [12] Linus Witschen, Tobias Wiersema, and Marco Platzner. "Search Space Characterization for AxC Synthesis." Workshop on Approximate Computing (AxC). Workshop without proceedings. 2020.

- [13] Linus Witschen, Tobias Wiersema, Masood Raeisi Nafchi, Arne Bockhorn, and Marco Platzner. "Timing Optimization for Virtual FPGA Configurations." In: *Proceedings of the International Symposium on Applied Reconfigurable Computing (ARC)*. Springer Lecture Notes in Computer Science, 2021.

- [14] Linus Witschen, Tobias Wiersema, Lucas David Reuter, and Marco Platzner. "MUSCAT: MUS-based Circuit Approximation Technique." In: *Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE)*. IEEE. 2022, pp. 172–177. doi: [10.23919/DATE54114.2022.9774604](https://doi.org/10.23919/DATE54114.2022.9774604).

- [15] Linus Witschen, Tobias Wiersema, Lucas David Reuter, and Marco Platzner. "Search Space Characterization for Approximate Logic Synthesis." In: *Proceedings of the Design Automation Conference (DAC)*. ACM, 2022. doi: [10.1145/3489517.3530463](https://doi.org/10.1145/3489517.3530463).

---

## TABLE OF CONTENTS

|       |                                                             |    |

|-------|-------------------------------------------------------------|----|

| 1     | Introduction                                                | 1  |

| 2     | Background                                                  | 9  |

| 2.1   | Approximate Logic Synthesis . . . . .                       | 9  |

| 2.1.1 | Overview . . . . .                                          | 9  |

| 2.1.2 | Approximate High-level Synthesis . . . . .                  | 11 |

| 2.1.3 | Boolean Rewriting . . . . .                                 | 12 |

| 2.1.4 | Netlist Transformation . . . . .                            | 13 |

| 2.2   | Quality Assurance . . . . .                                 | 14 |

| 3     | CIRCA: A Search-based Approximate Logic Synthesis Framework | 19 |

| 3.1   | Introduction . . . . .                                      | 19 |

| 3.2   | Classification of Existing Frameworks . . . . .             | 21 |

| 3.3   | Requirements for a Flexible Framework . . . . .             | 23 |

| 3.4   | The CIRCA Framework . . . . .                               | 24 |

| 3.4.1 | The Concept of CIRCA . . . . .                              | 24 |

| 3.4.2 | Search Space Exploration . . . . .                          | 26 |

| 3.4.3 | Approximation . . . . .                                     | 30 |

| 3.4.4 | Estimation . . . . .                                        | 31 |

| 3.4.5 | Quality Assurance . . . . .                                 | 31 |

| 3.4.6 | Classification of CIRCA . . . . .                           | 34 |

| 3.4.7 | The Configuration File . . . . .                            | 34 |

| 3.5   | Experimental Results . . . . .                              | 38 |

| 3.5.1 | Experimental Setup . . . . .                                | 38 |

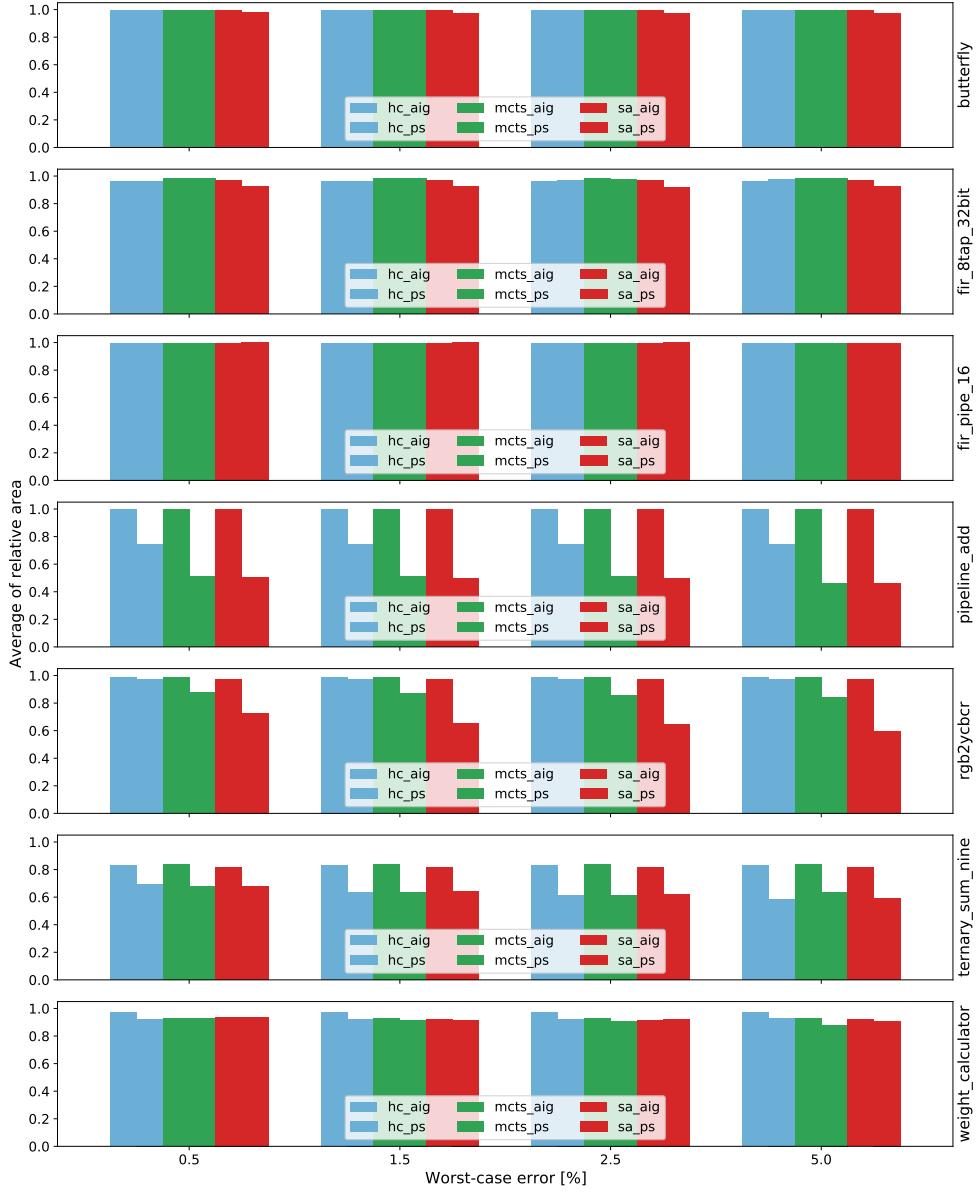

| 3.5.2 | Experimental Evaluation . . . . .                           | 39 |

| 3.6   | Conclusion . . . . .                                        | 43 |

| 4     | Jump Search: Fast Synthesis of Approximate Circuits         | 45 |

| 4.1   | Overview . . . . .                                          | 45 |

| 4.2   | Motivational Example and Conceptual Overview . . . . .      | 47 |

| 4.3   | Jump Search Methodology . . . . .                           | 49 |

| 4.3.1 | Pre-processing Phase . . . . .                              | 49 |

| 4.3.2 | Path Planning Phase . . . . .                               | 50 |

| 4.3.3 | Binary Search Phase . . . . .                               | 51 |

| 4.4   | Search Techniques and Their Limitations . . . . .           | 52 |

| 4.5   | Estimating a Candidate's Impact on Area . . . . .           | 54 |

| 4.6   | Estimating a Candidate's Impact on Error . . . . .          | 55 |

| 4.6.1 | Least Absolute Shrinkage and Selection Operator . . . . .   | 57 |

| 4.6.2 | Hilbert-Schmidt Independence Criterion LASSO . . . . .      | 57 |

| 4.6.3 | Decision Trees and Random Forests . . . . .                 | 59 |

| 4.6.4 | Comparison of the Feature Ranking Methods . . . . .         | 60 |

| 4.7   | Determining the Figure-of-merit . . . . .                   | 61 |

| 4.8   | Implementation of Jump Search . . . . .                     | 62 |

| 4.9   | Experimental Evaluation . . . . .                           | 64 |

|       |                                                                          |     |

|-------|--------------------------------------------------------------------------|-----|

| 4.9.1 | Experimental Setup . . . . .                                             | 64  |

| 4.9.2 | Experimental Evaluation of Jump Search . . . . .                         | 65  |

| 4.9.3 | Comparison of Synthesis and Verification Steps . . . . .                 | 67  |

| 4.9.4 | Evaluation of the Pre-processing Phase . . . . .                         | 67  |

| 4.9.5 | Discussion on the Figure-of-merits and Feature Ranking Methods . . . . . | 69  |

| 4.10  | Conclusion . . . . .                                                     | 72  |

| 5     | MUSCAT: A MUS-based Circuit Approximation Technique                      | 73  |

| 5.1   | Overview . . . . .                                                       | 73  |

| 5.2   | Methodology . . . . .                                                    | 75  |

| 5.2.1 | Cutpoints . . . . .                                                      | 75  |

| 5.2.2 | Approximation Miter . . . . .                                            | 76  |

| 5.2.3 | Minimal Unsatisfiable Subsets . . . . .                                  | 77  |

| 5.2.4 | Approximate Logic Synthesis Flow . . . . .                               | 78  |

| 5.2.5 | Discussion on the Insertion of Cutpoints . . . . .                       | 78  |

| 5.3   | Experimental Results . . . . .                                           | 79  |

| 5.3.1 | Implementation and Experimental Setup . . . . .                          | 79  |

| 5.3.2 | Overall Evaluation . . . . .                                             | 80  |

| 5.3.3 | Evaluation of Cutpoint Designs . . . . .                                 | 83  |

| 5.3.4 | Evaluation of Heuristics for Cutpoint Insertion . . . . .                | 84  |

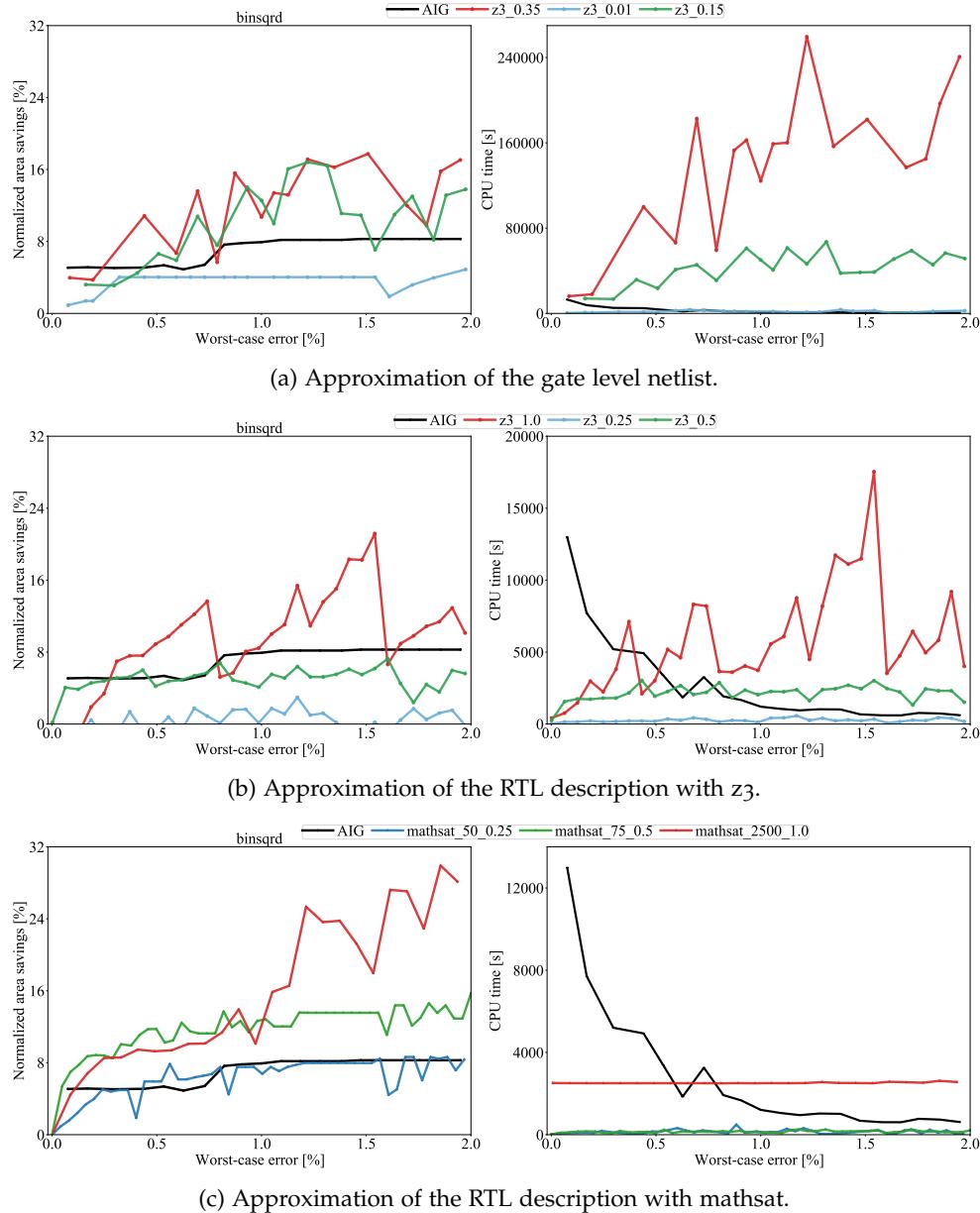

| 5.4   | Case Study: Square of a Binomial . . . . .                               | 85  |

| 5.4.1 | Overview . . . . .                                                       | 85  |

| 5.4.2 | Experimental Evaluation . . . . .                                        | 86  |

| 5.5   | Conclusion . . . . .                                                     | 89  |

| 6     | Proof-carrying Approximate Circuits                                      | 91  |

| 6.1   | Overview . . . . .                                                       | 91  |

| 6.2   | Proof-carrying Hardware . . . . .                                        | 92  |

| 6.3   | Proof-carrying Approximate Circuits . . . . .                            | 94  |

| 6.4   | Verification-based Approximate Logic Synthesis . . . . .                 | 96  |

| 6.4.1 | Approximate Logic Synthesis and Quality Assurance .                      | 96  |

| 6.4.2 | Creating Proof Certificates . . . . .                                    | 97  |

| 6.5   | Experimental Results . . . . .                                           | 99  |

| 6.6   | Conclusion . . . . .                                                     | 101 |

| 7     | Search Space Characterization for Approximate Logic Synthesis            | 103 |

| 7.1   | Overview . . . . .                                                       | 103 |

| 7.2   | Related Work and Novel Approach . . . . .                                | 104 |

| 7.3   | Search Space Characterization via Formal Verification . . . . .          | 107 |

| 7.3.1 | Augmenting the Candidates . . . . .                                      | 108 |

| 7.3.2 | Approximation miter . . . . .                                            | 109 |

| 7.3.3 | Search Space Characterization Algorithm . . . . .                        | 110 |

| 7.4   | Experimental Results . . . . .                                           | 113 |

| 7.5   | Conclusion . . . . .                                                     | 116 |

| 8     | Conclusion                                                               | 119 |

| 9     | Outlook                                                                  | 123 |

|       | Bibliography                                                             | 125 |

---

## LIST OF FIGURES

---

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.1 | Demonstration of approximated JPEG compression.<br>Taken from [38]. . . . .                                                                                                                                                                                                                                                                                                                                                                                | 2  |

| Figure 1.2 | Computing stack with focus of this dissertation highlighted in gray. . . . .                                                                                                                                                                                                                                                                                                                                                                               | 3  |

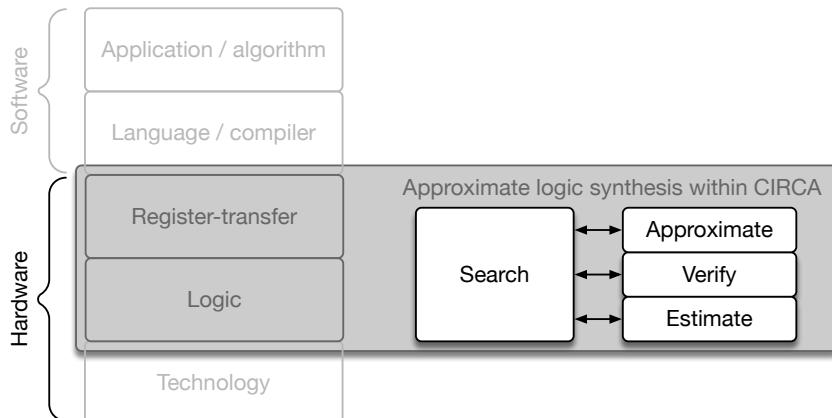

| Figure 3.1 | Approximate logic synthesis in the computing stack and CIRCA. . . . .                                                                                                                                                                                                                                                                                                                                                                                      | 19 |

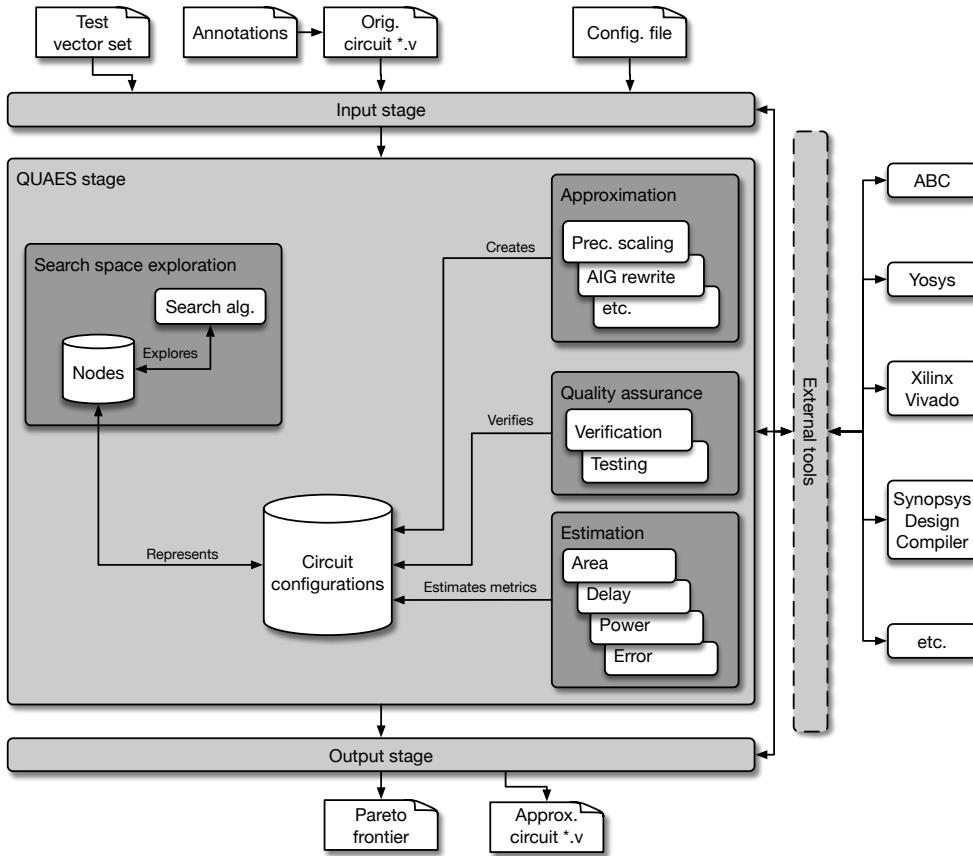

| Figure 3.2 | Overview of CIRCA's conceptual design. Extended from [101]. . . . .                                                                                                                                                                                                                                                                                                                                                                                        | 25 |

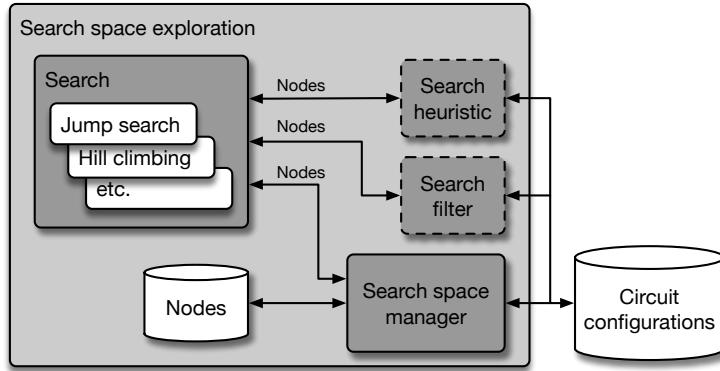

| Figure 3.3 | CIRCA's search space exploration block in more detail.<br>Dashed lines indicate optional blocks. . . . .                                                                                                                                                                                                                                                                                                                                                   | 27 |

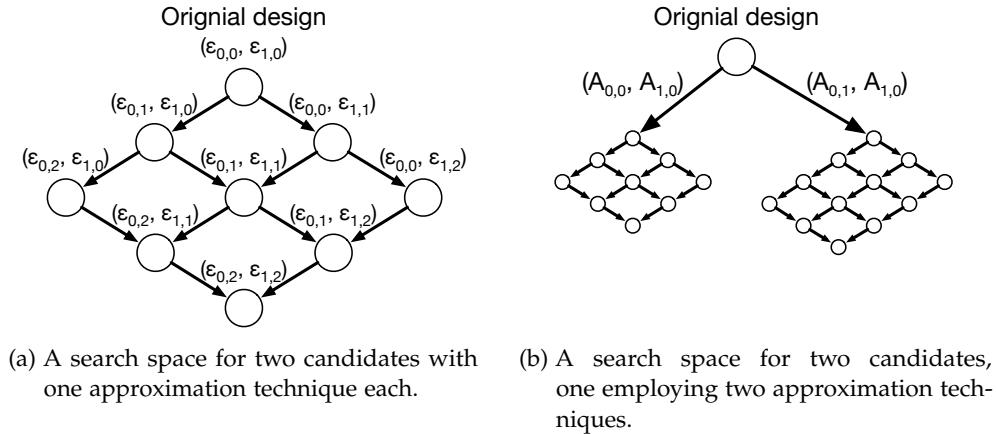

| Figure 3.4 | Exemplary search spaces as constructed by the general search space manager. . . . .                                                                                                                                                                                                                                                                                                                                                                        | 29 |

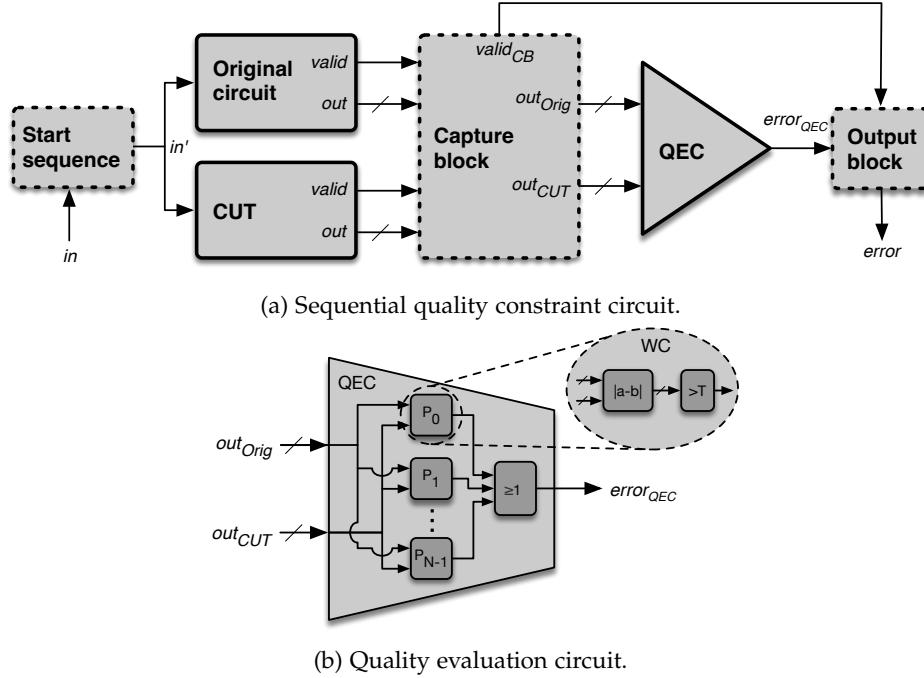

| Figure 3.5 | Overview of the sequential quality constraint circuit and the quality evaluation circuit. Taken from [101]. . . . .                                                                                                                                                                                                                                                                                                                                        | 32 |

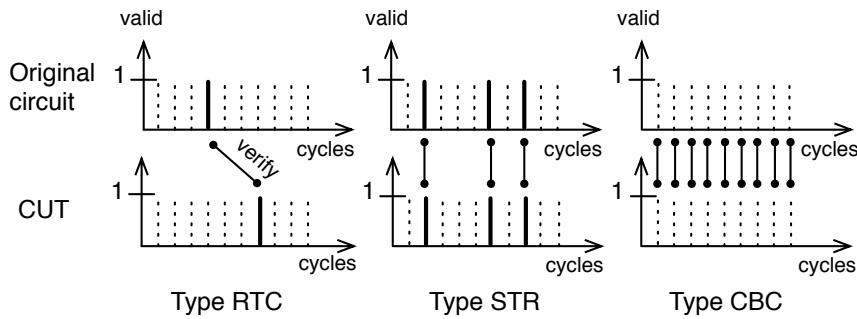

| Figure 3.6 | Circuit types with resulting verification steps. . . . .                                                                                                                                                                                                                                                                                                                                                                                                   | 33 |

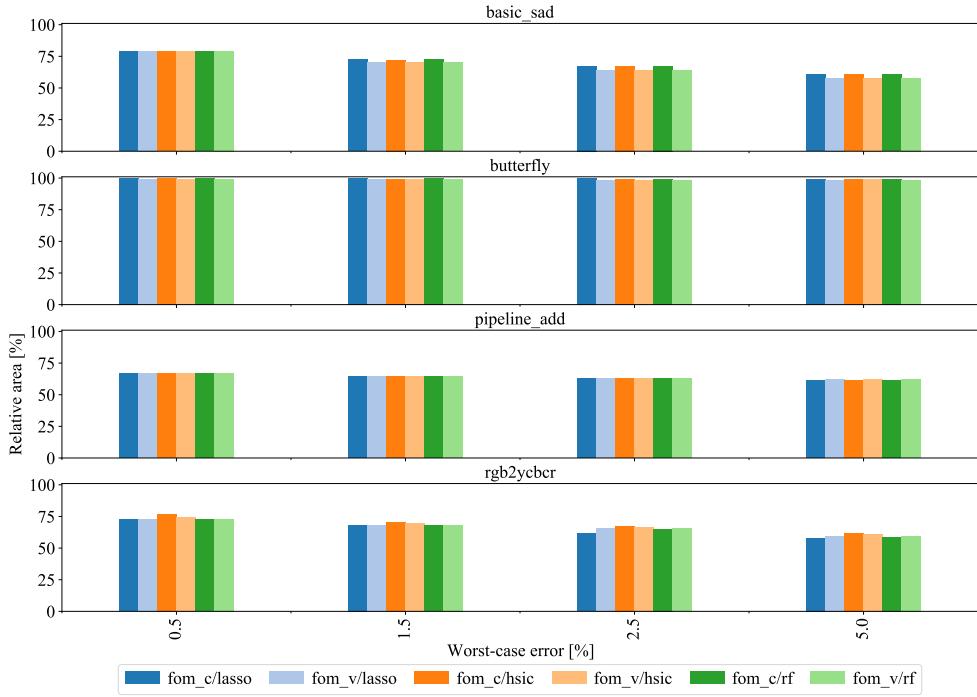

| Figure 3.7 | Resulting average of the relative area. Adapted from [101]. . . . .                                                                                                                                                                                                                                                                                                                                                                                        | 40 |

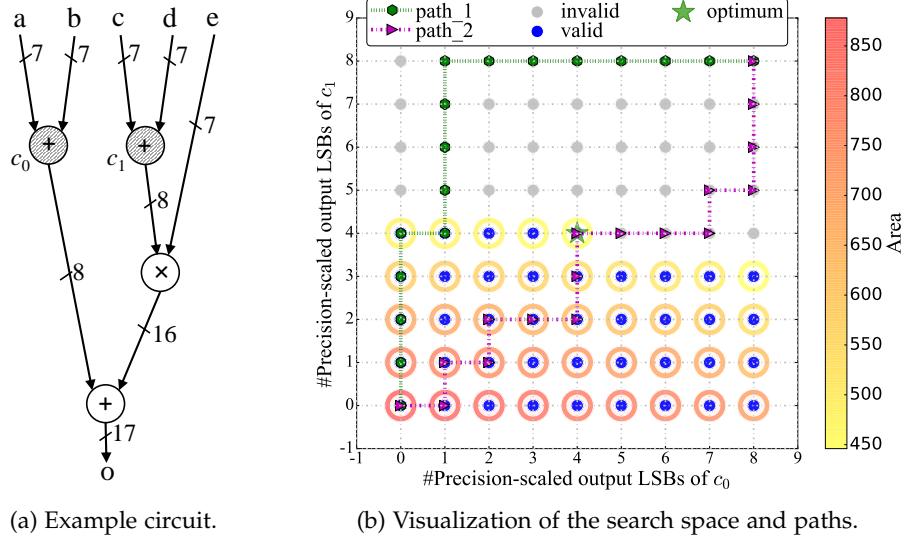

| Figure 4.1 | Exemplary circuit (a) along with its search space (b).<br>The approximation candidates of the circuit are highlighted in gray. To span the design space, precision scaling is utilized as approximation method and a worst-case (WC) error of 1.5% of the maximal output value is used as quality constraint. Out of the 81 circuits that form the design space 42 are valid. . . . .                                                                      | 48 |

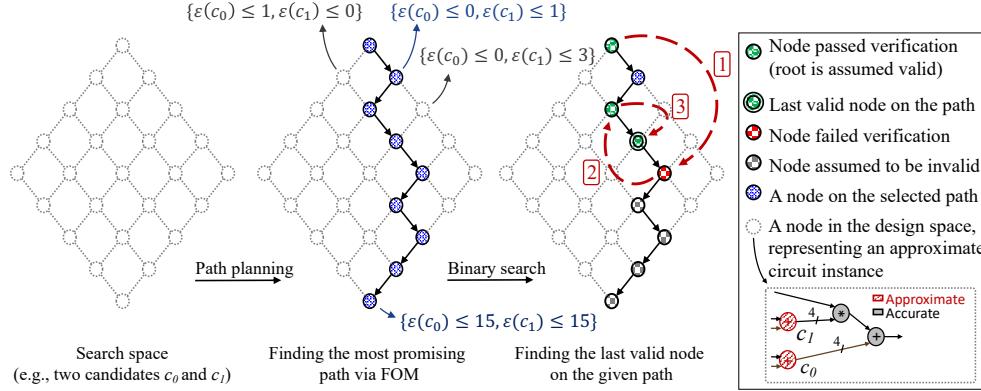

| Figure 4.2 | Visualization of the jump search phases. The circuit shown is a scaled-down version of the example of Figure 4.1a, where the two candidates $c_0$ and $c_1$ have four-bit outputs. Note that due to the scaled-down bit widths, jump search generates a path different from the one shown in Figure 4.1b. . . . .                                                                                                                                          | 51 |

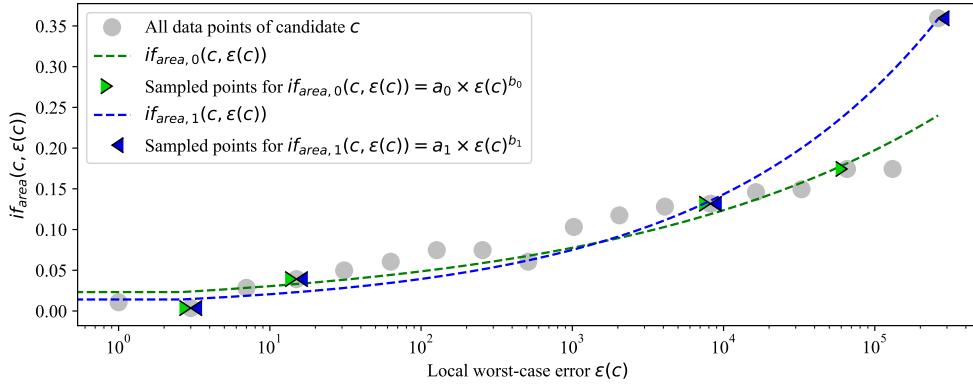

| Figure 4.3 | Relative area savings achieved for the benchmark ternary_sum_nine through precision-scaling an adder with an 18 bit output. The gray dots show all data points that can be acquired with precision scaling for the candidate. The green and blue triangles are the data points which have been used to determine the green fitting curve ( $a_0 = 0.0191, b_0 = 0.203$ ) and the blue fitting curve ( $a_1 = 0.0108, b_1 = 0.281$ ), respectively. . . . . | 55 |

|            |                                                                                                                                                                                                                                                                                                     |     |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

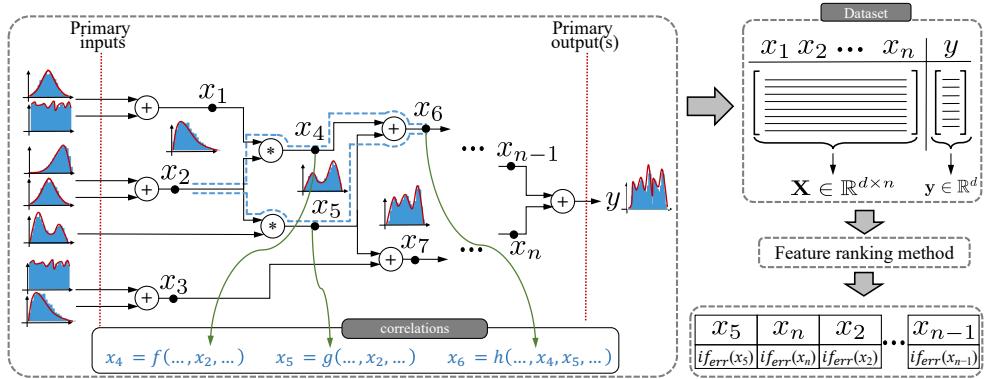

| Figure 4.4 | Training of feature ranking methods for the estimation of $\text{if}_{\text{err}}(c)$ . The result is a list of candidates sorted according to non-decreasing contributions to the overall circuit's error, and corresponding error impact values $\text{if}_{\text{err}}(c) \in [0, +1]$ . . . . . | 56  |

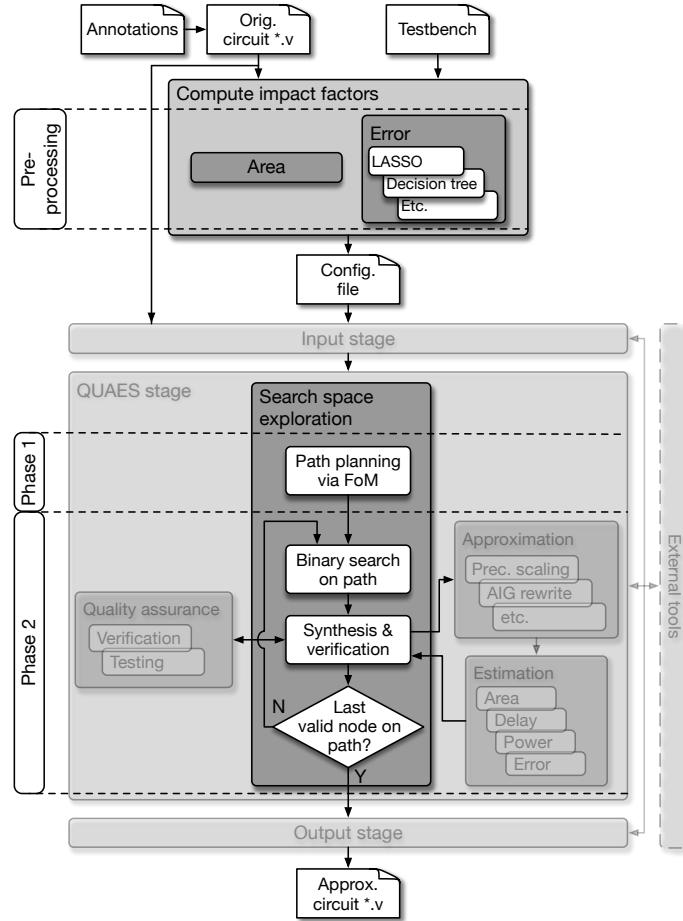

| Figure 4.5 | Overview of the jump search in the CIRCA framework [101]. Highlighting indicates modified parts of CIRCA. . . . .                                                                                                                                                                                   | 63  |

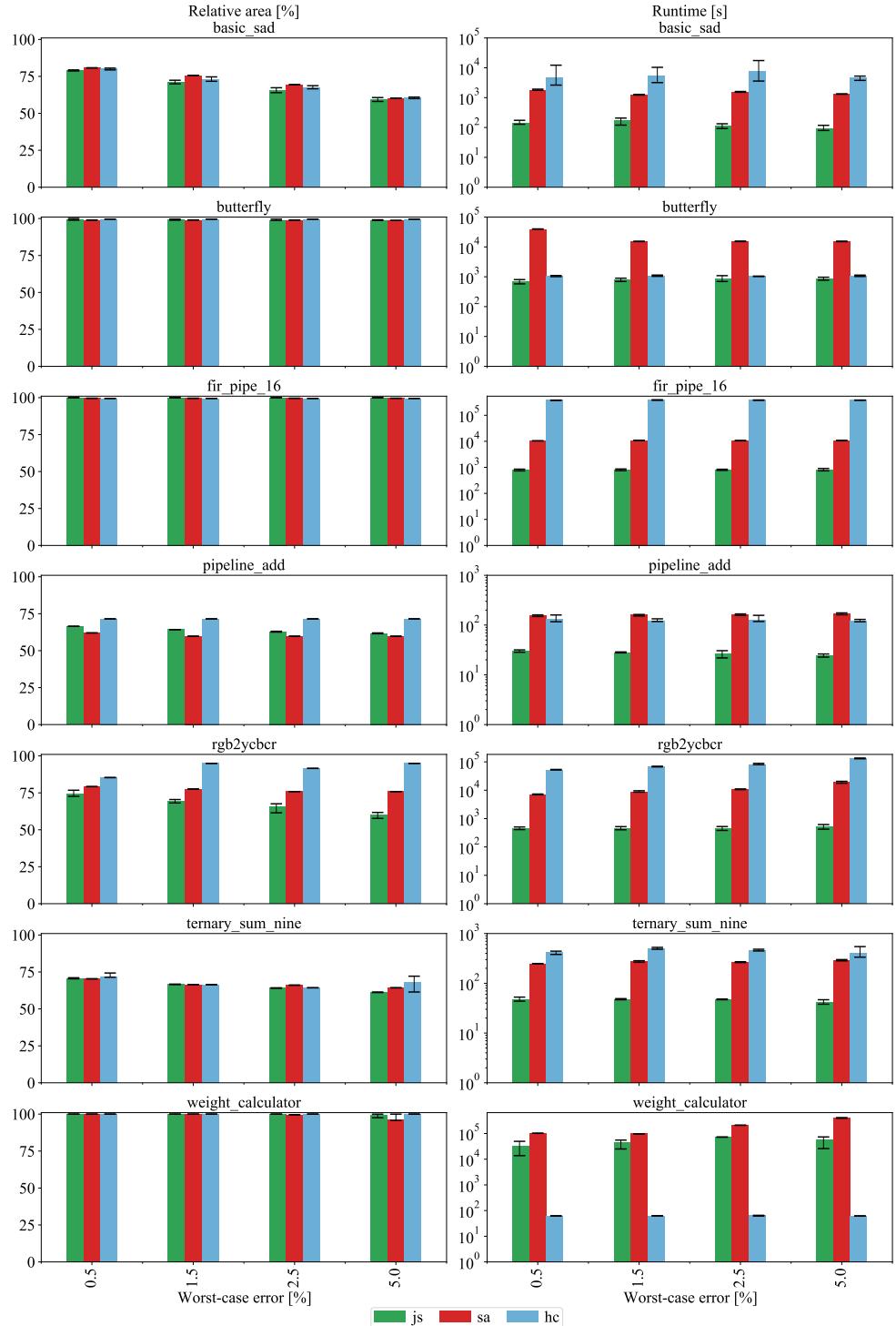

| Figure 4.6 | Average relative area and timing. The black bars with caps indicate the minimums and maximums from all experiments. . . . .                                                                                                                                                                         | 66  |

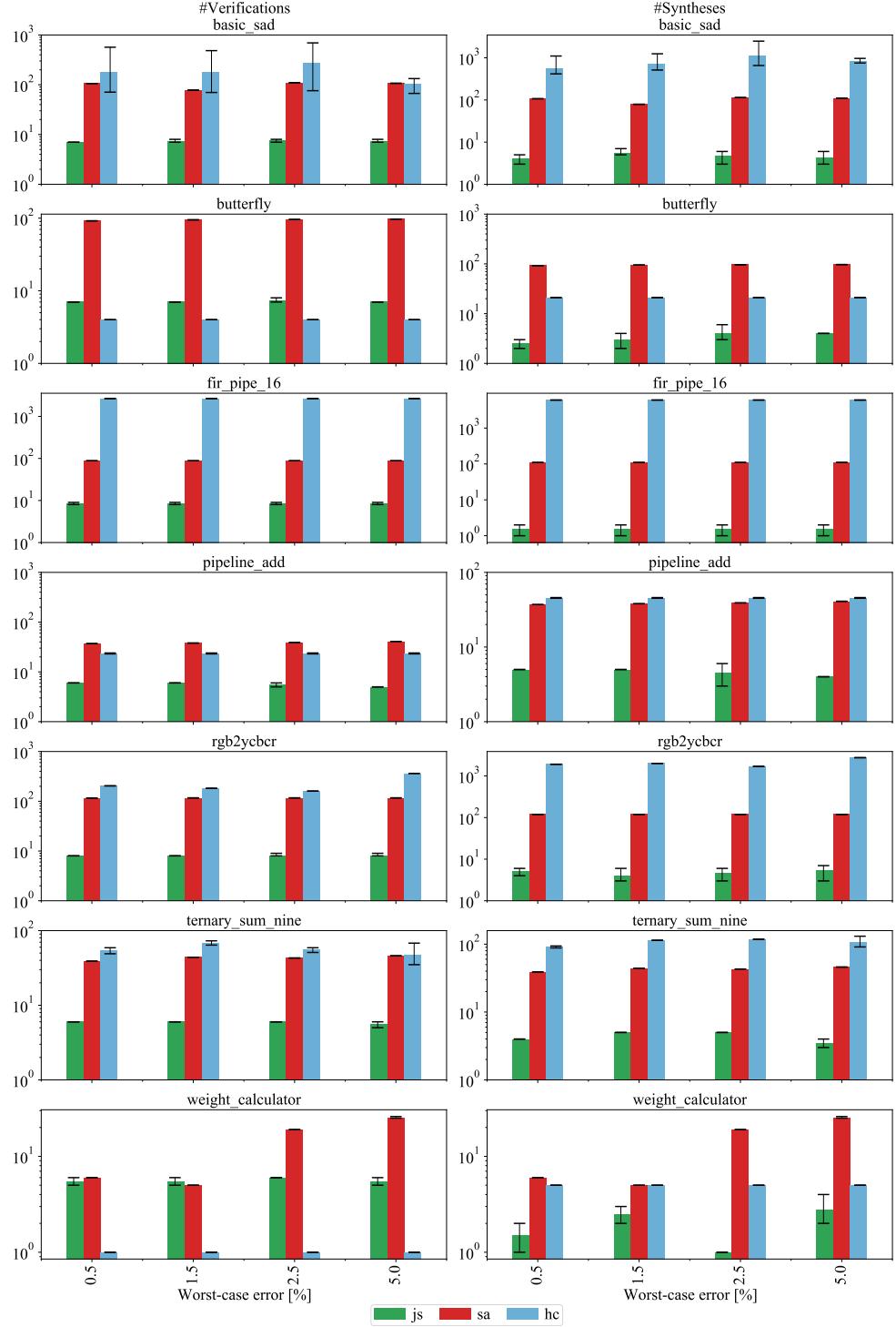

| Figure 4.7 | Average number of verifications and syntheses. . . . .                                                                                                                                                                                                                                              | 68  |

| Figure 4.8 | Normalized area for different combinations of feature ranking method and figure-of-merit. . . . .                                                                                                                                                                                                   | 70  |

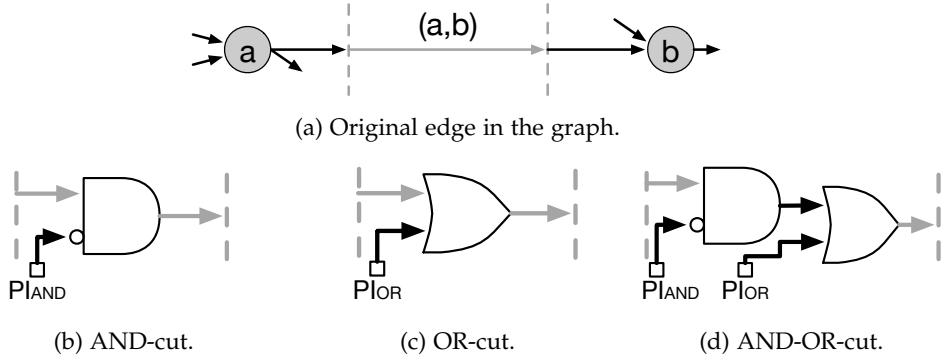

| Figure 5.1 | Concept of replacing an edge with a cutpoint in a netlist. Dashed gray lines indicate the cut, solid gray lines indicate the original connection, and boxes represent newly added primary inputs. Taken from [106].                                                                                 | 76  |

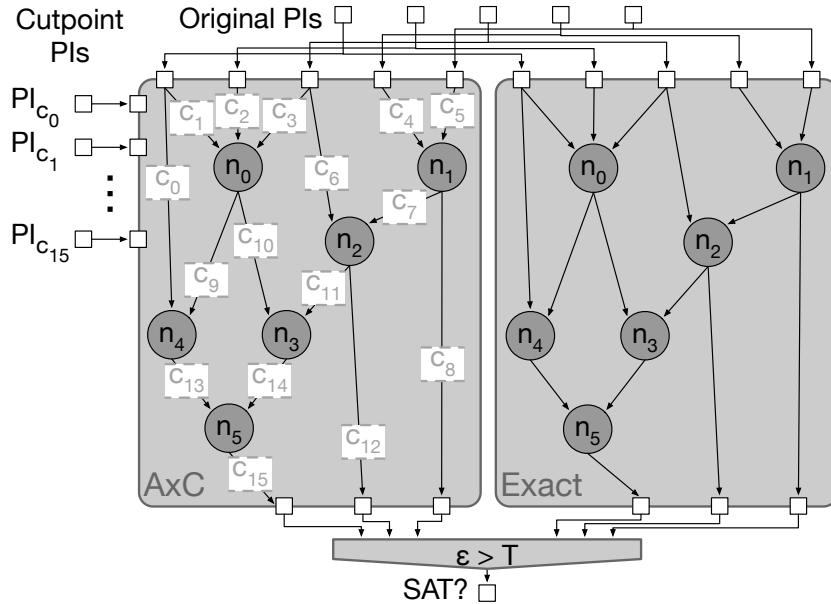

| Figure 5.2 | Approximation miter with the cutpoints $C = \{c_0, \dots, c_{15}\}$ and the corresponding control inputs $\text{PI}_c$ . Taken from [106]. . . . .                                                                                                                                                  | 77  |

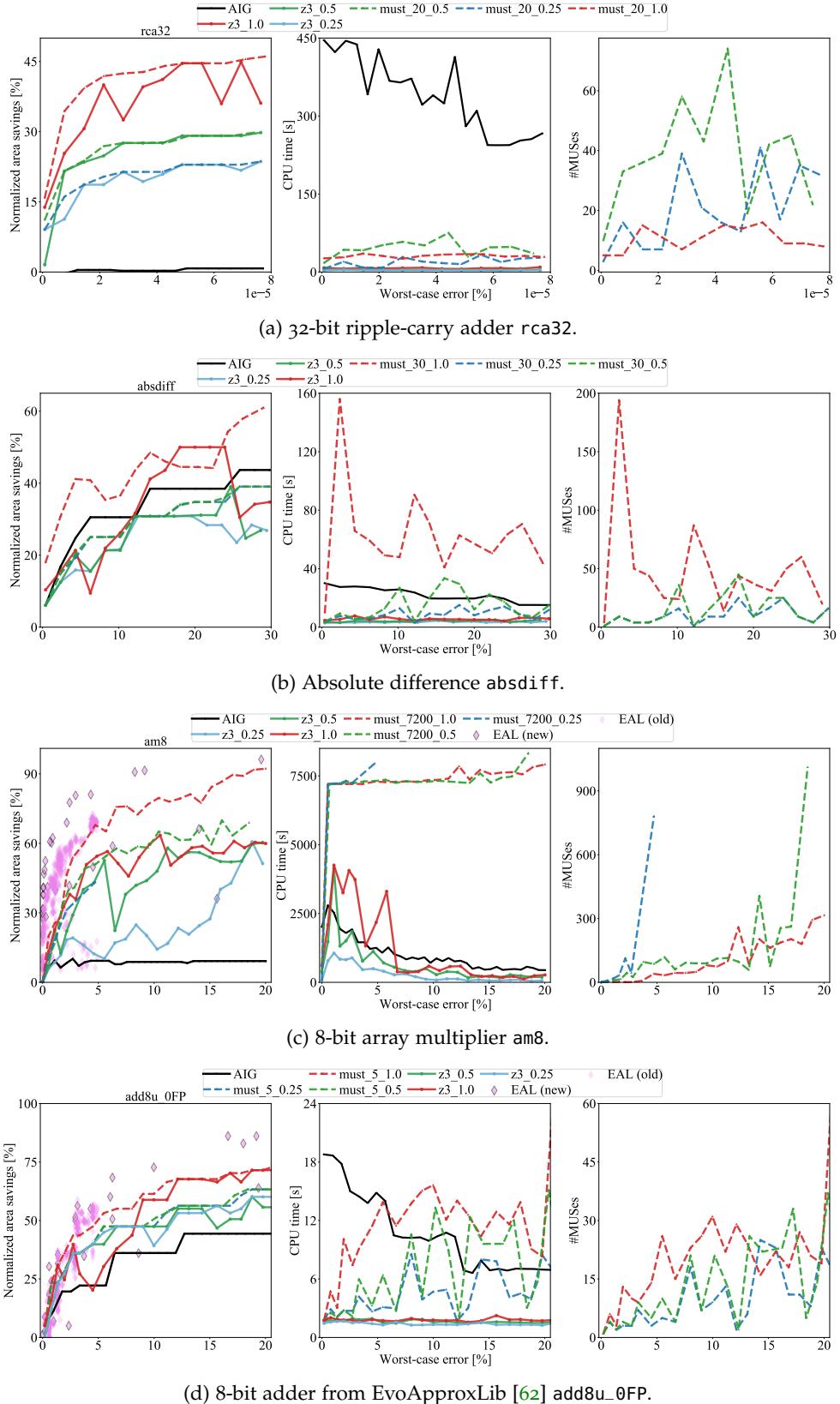

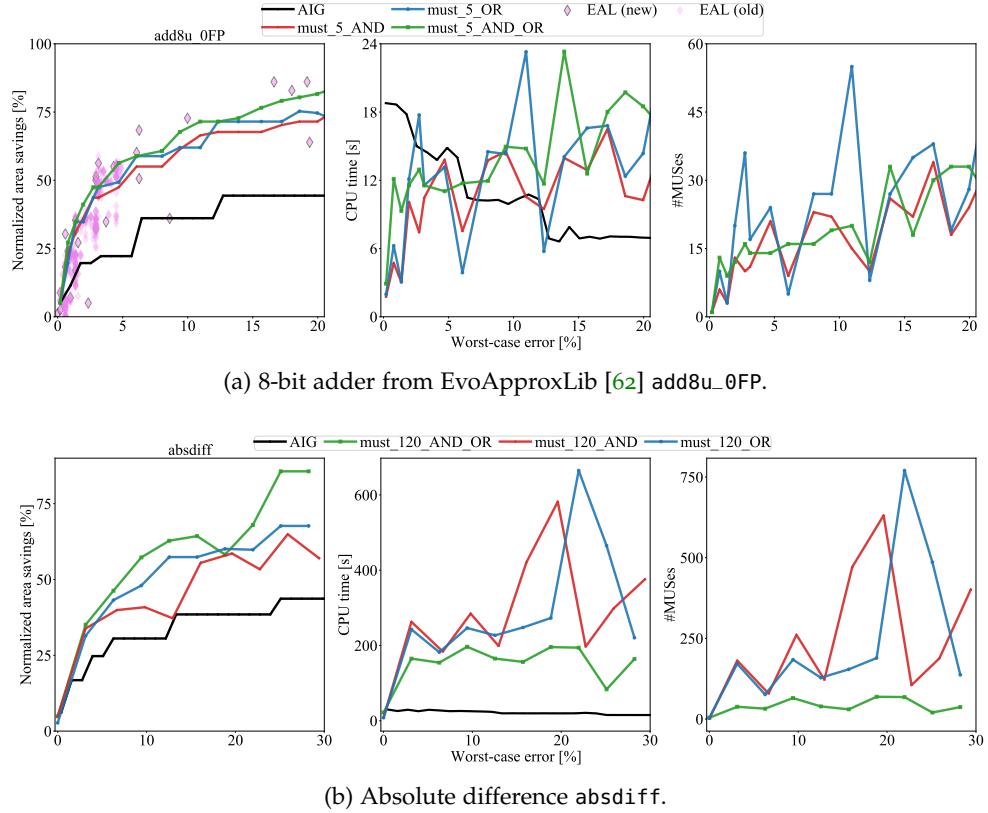

| Figure 5.3 | Comparison of MUSCAT (z3 and must) with different cutpoint percentages to AIG and EAL for different benchmarks and varying error bounds. . . . .                                                                                                                                                    | 82  |

| Figure 5.4 | Comparison of the method must with varying cutpoint designs for 100% of the cutpoints against AIG and components of the EvoApproxLib (two versions). . . . .                                                                                                                                        | 84  |

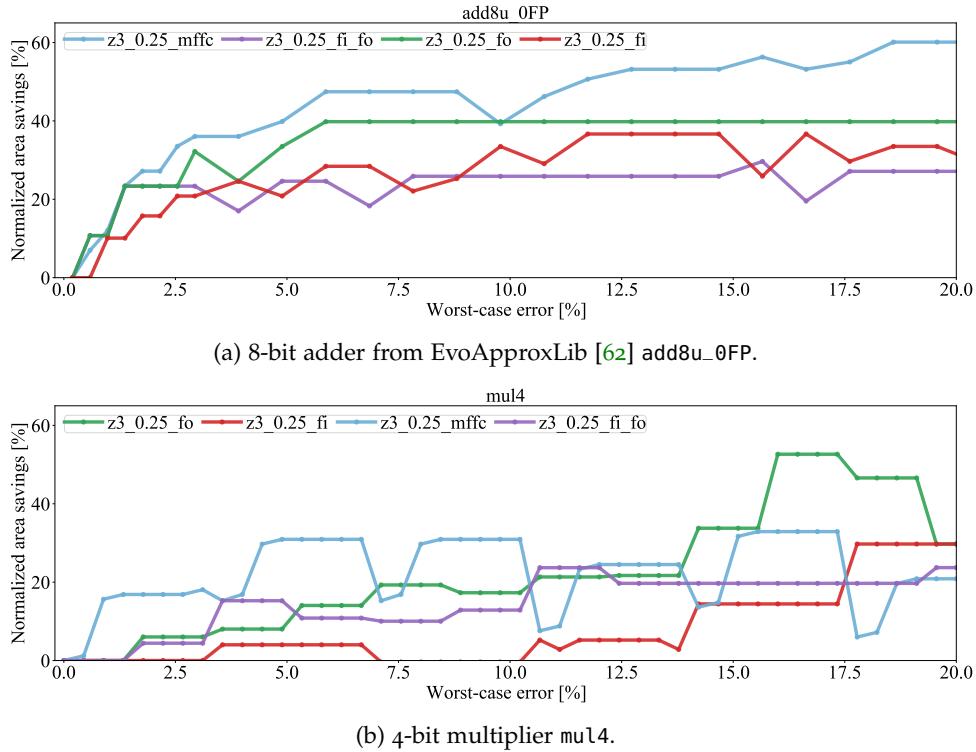

| Figure 5.5 | Comparison of different heuristics for the cutpoint insertion. . . . .                                                                                                                                                                                                                              | 85  |

| Figure 5.6 | Experimental results for the benchmark binsqrd. . . . .                                                                                                                                                                                                                                             | 87  |

| Figure 6.1 | Proof-carrying hardware flow. . . . .                                                                                                                                                                                                                                                               | 93  |

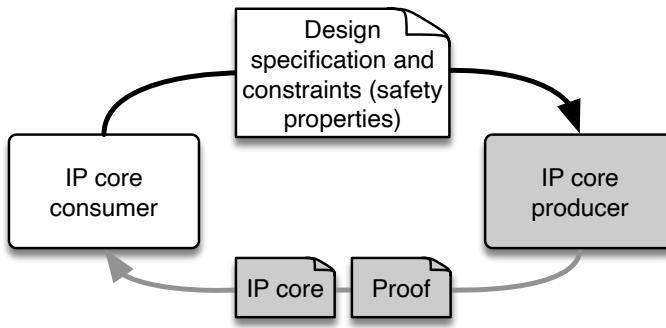

| Figure 6.2 | Conceptual flow of proof-carrying approximate circuits                                                                                                                                                                                                                                              | 94  |

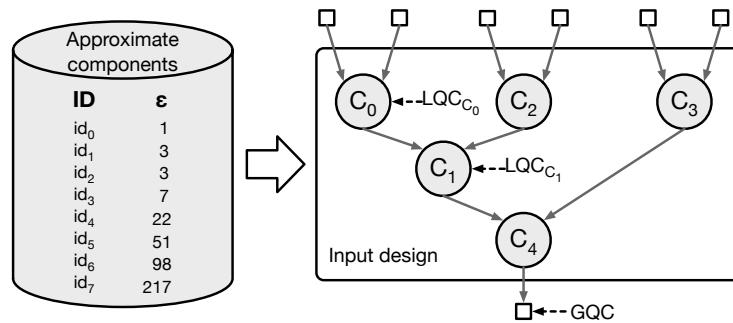

| Figure 7.1 | Exemplary design with approximate components. Taken from [107]. . . . .                                                                                                                                                                                                                             | 105 |

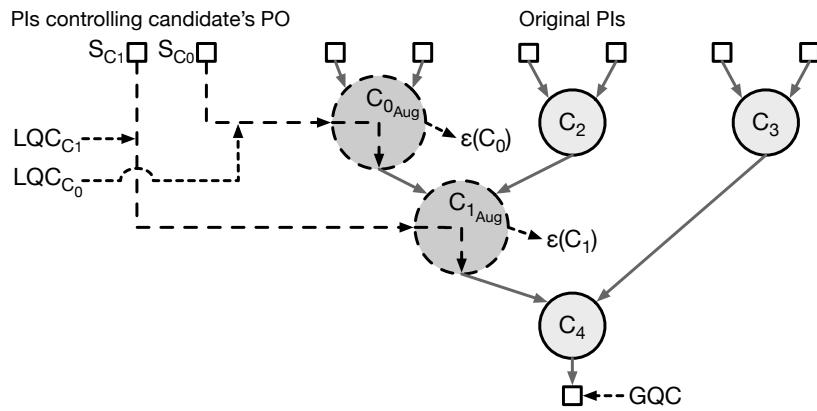

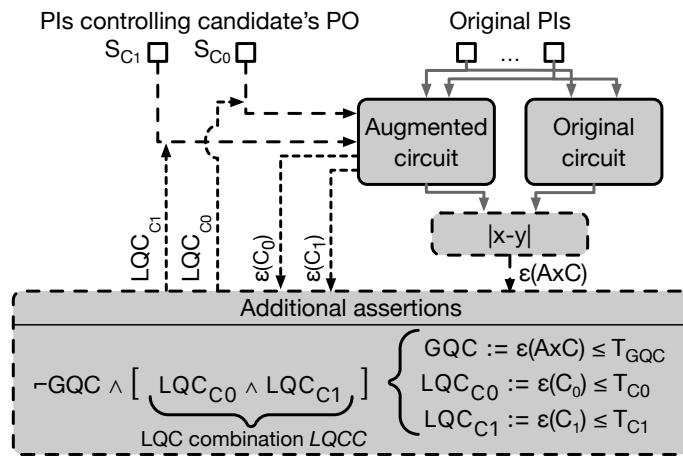

| Figure 7.2 | Extended example design showing the augmented candidates with their additional primary inputs and their formal signals $\epsilon(c)$ and $\text{LQC}_c, c \in C_{\text{set}}$ . Taken from [107]. . . . .                                                                                           | 108 |

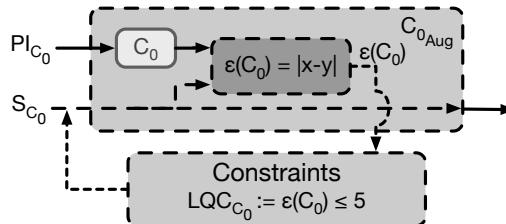

| Figure 7.3 | Detailed augmented candidate. Taken from [107]. . . . .                                                                                                                                                                                                                                             | 108 |

| Figure 7.4 | Approximation miter. Taken from [107]. . . . .                                                                                                                                                                                                                                                      | 109 |

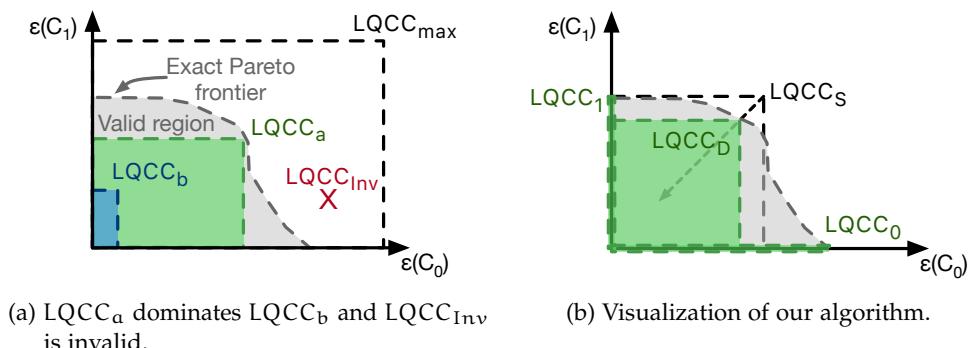

| Figure 7.5 | Search space example with two candidates, $C_0$ and $C_1$ . The candidates' errors, $\epsilon(C_0)$ and $\epsilon(C_1)$ , define the search space's dimensions. Taken from [107]. . . . .                                                                                                           | 110 |

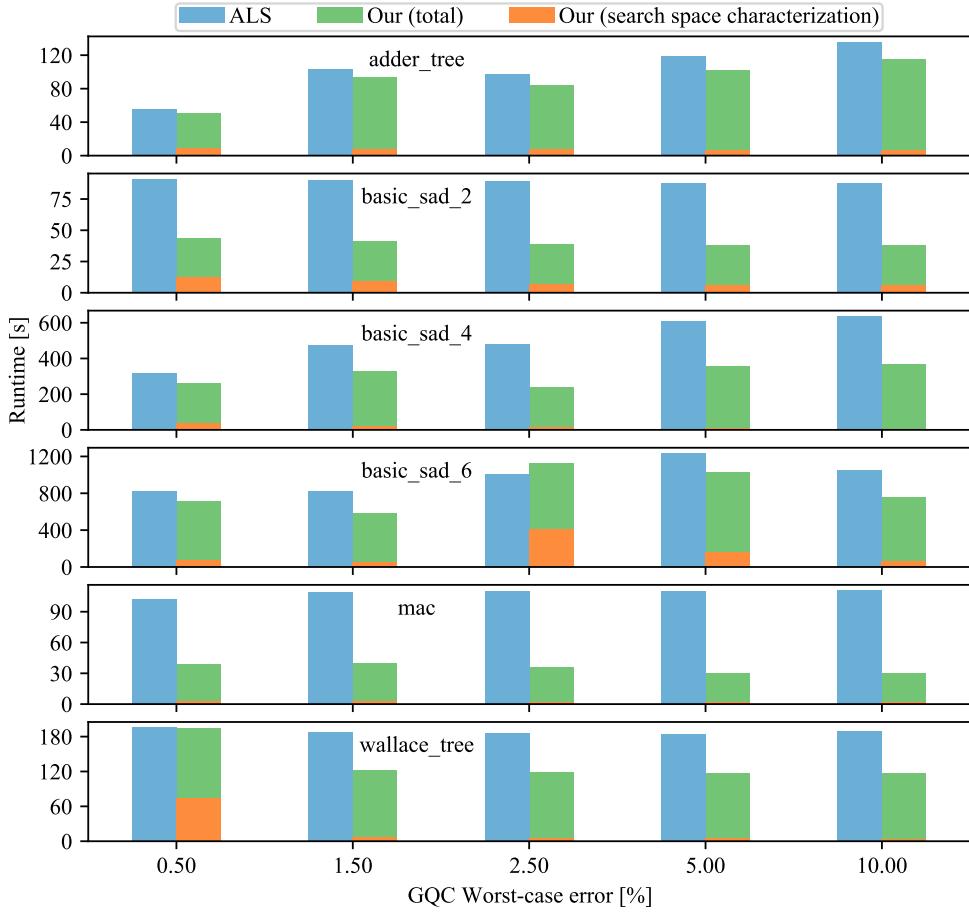

| Figure 7.6 | Runtimes of ALS and our methodology. Taken from [107]. . . . .                                                                                                                                                                                                                                      | 114 |

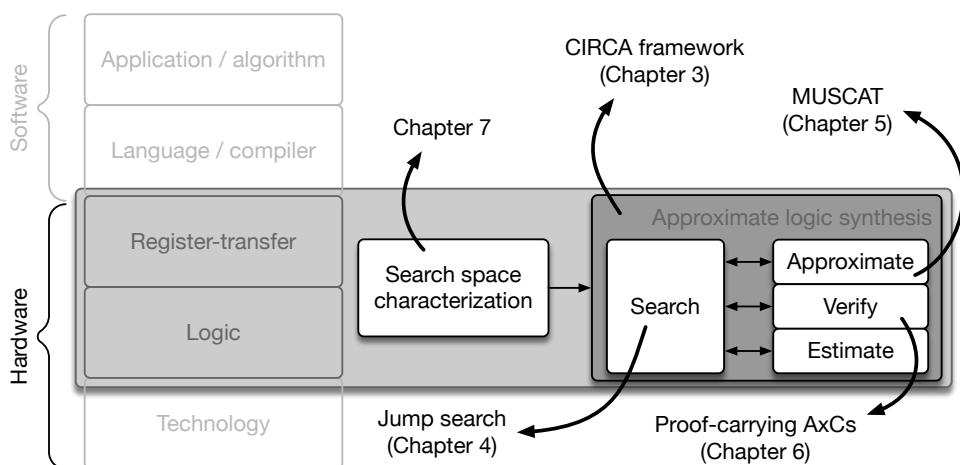

- Figure 8.1 Overview of approximate logic synthesis in the computing stack and the dissertation's contributions. . . . [119](#)

---

## LIST OF LISTINGS

---

|             |                                                                                     |    |

|-------------|-------------------------------------------------------------------------------------|----|

| Listing 3.1 | Configuration of the input design. . . . .                                          | 36 |

| Listing 3.2 | Configuration of the estimation block. . . . .                                      | 37 |

| Listing 3.3 | Configuration of the search space exploration block.                                | 37 |

| Listing 3.4 | Configuration of the approximation block and the<br>default configurations. . . . . | 38 |

| Listing 3.5 | Candidate-specific configurations. . . . .                                          | 38 |

---

## LIST OF TABLES

---

|           |                                                                                                                                                                                                                                                                                                                                                |     |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.1 | Overview over presented frameworks for approximate circuit generation. Adapted from Witschen et al. [101]                                                                                                                                                                                                                                      | 22  |

| Table 3.2 | Overview and classification of CIRCA for approximate logic synthesis. Adapted from Witschen et al. [101]                                                                                                                                                                                                                                       | 35  |

| Table 3.3 | Sequential benchmark circuits . . . . .                                                                                                                                                                                                                                                                                                        | 39  |

| Table 3.4 | CIRCA's average runtimes and number of selected nodes. . . . .                                                                                                                                                                                                                                                                                 | 42  |

| Table 4.1 | Overview of the benchmarks. . . . .                                                                                                                                                                                                                                                                                                            | 64  |

| Table 4.2 | Runtimes for determining $if_{area}$ . The number of candidates present in each benchmark circuit and the runtime for synthesizing the original benchmark circuit is listed. Along the total runtimes for synthesizing the circuit once per candidate and four times per candidate, the runtime for curve fitting is shown. . . . .            | 69  |

| Table 4.3 | Runtimes of the feature ranking methods for determining $if_{err}$ . . . . .                                                                                                                                                                                                                                                                   | 70  |

| Table 4.4 | Overview of the best combinations of figure-of-merit and feature ranking method for each benchmark and worst-case error bound. An * indicates that all approaches achieved the best result. . . . .                                                                                                                                            | 71  |

| Table 4.5 | Summary of the number of times a combination of figure-of-merit and feature ranking method achieved the best result. The first row or column indicates the number for the respective method in that column or row, respectively. The values in the matrix represent the combination of the figure-of-merit and feature ranking method. . . . . | 71  |

| Table 5.1 | Benchmark circuits. . . . .                                                                                                                                                                                                                                                                                                                    | 80  |

| Table 6.1 | Experimental results for the proof-carrying AxC approach. Taken from [105]. . . . .                                                                                                                                                                                                                                                            | 100 |

| Table 7.1 | Experimental results. Taken from [107]. . . . .                                                                                                                                                                                                                                                                                                | 115 |

| Table 7.2 | Experimental results for generating the AxCs from the valid LQC combinations. . . . .                                                                                                                                                                                                                                                          | 116 |

---

## INTRODUCTION

---

With the breakdown of Dennard scaling at the beginning of the century and the continuous slow-down – and eventually the end – of Moore’s law, chip designers are challenged to find new ways to increase processing performance under strict power and area constraints. The design paradigm approximate computing (AC) is one way of meeting the challenge.

Approximate computing exploits the fact that many domains show an inherent resilience against inaccuracies and even errors to trade off computational accuracy (or quality) against target metrics, e.g., hardware area, delay, or power consumption. Mittal [58] describes the trade-off as the gap between the level of *required* accuracy by the user and the *provided* accuracy by the computing system. Research groups from academia [24] and industry [17, 33, 57, 63] have shown that this gap can be found in numerous domains, including signal processing, audio, image and video processing, machine learning, and data analytics. For example, Chippa et al. [24] reported that representative applications from the domain of recognition, data mining, and search spend on average 83% of the runtime on resilient computations; thus, demonstrating the potential that approximate computing offers. An application’s resilience against inaccuracies and errors can be attributed to several factors [24, 58, 82, 112]:

- *Redundant input data*: Redundancy in the input data makes the application more robust against imprecisions.

- *Error attenuation*: Computational patterns, such as iterative refinement or statistical aggregation, in the application’s algorithm increase the resilience; thus, facilitating the processing of noisy, imprecise, or incomplete input data, e.g., data from physical sensors such as cameras or microphones.

- *Lack of golden result*: Rather than a golden result (or correct answer), a range of acceptable results exists, e.g., recommender systems or web searches.

- *Perceptual limitations*: Visual and audio perception of humans, for example, is limited and slight differences of individual pixels cannot be recognized.

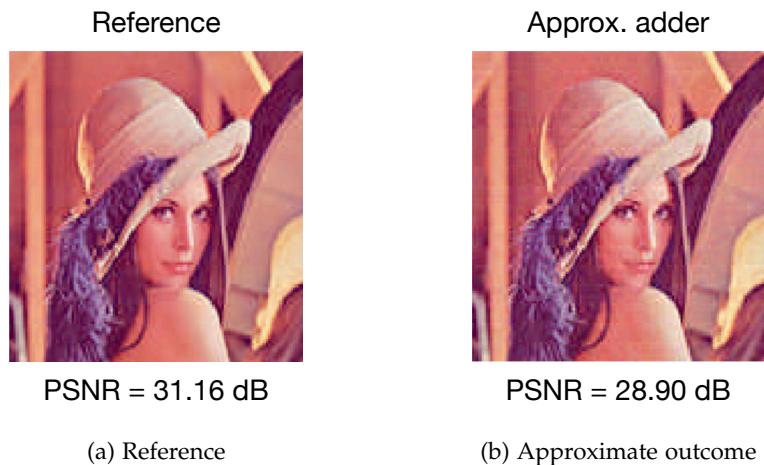

Figure 1.1 shows a practical example of approximate computing, demonstrating the resilience of an application and the potential of approximate

computing. Gupta et al. [38] replaced the precise adder cells with approximate counterparts within a hardware module for JPEG compression and, in this way, achieved power savings of around 53%. The left-hand image shows the original, precise compression outcome; the right-hand image shows an outcome produced by the approximate hardware. Compared to the precise outcome, the quality of the approximate outcome is reduced, as indicated by the lower peak signal-to-noise ratio (PSNR). However, the differences are merely visible due to perceptual limitations, and the approximate outcome is almost indistinguishable from the original, which justifies the acceptance of the suboptimal quality in return for the significantly reduced power consumption.

Figure 1.1: Demonstration of approximated JPEG compression. Taken from [38].

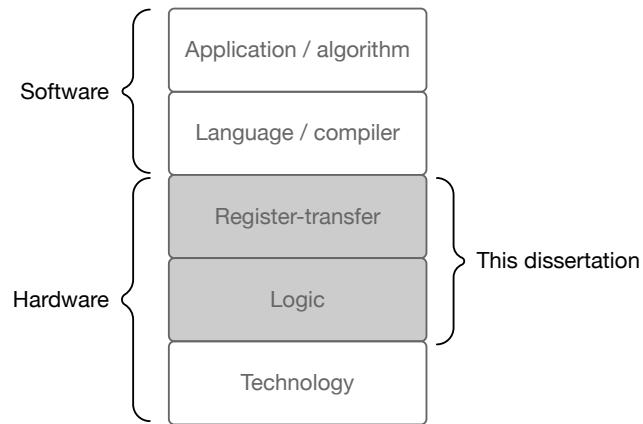

In fact, suboptimal quality of results and limited accuracy have always been present in computer science and engineering due to limited precision of data types, the use of (meta-)heuristics, or the exact or optimal result being out of reach. Approximate computing, however, goes further and exploits the resilience by applying approximations through the judicious introduction of errors to leverage the trade-off of quality and target metrics. Here, the approximations are complementary [25, 113, 119] and can be applied to all system components (processing, storage, and communication) at all levels of the computing stack (from applications down to semiconductor technology) [58, 82, 112]. Figure 1.2 shows the computing stack assumed in this dissertation that divides into a software and a hardware part.

The *application/algorithm* level represents the highest level of abstraction, and approximations target the application's algorithm via source-code transformations. Precision scaling (or quantization), for example, states a well-known, general approximation technique that reduces a variable's bit width to simplify computations and reduce the memory footprint. Other techniques target specific applications such as neural networks to improve the network's energy efficiency by approximating resilient neurons using, for instance, precision scaling or an approximated activation function [93].

Figure 1.2: Computing stack with focus of this dissertation highlighted in gray.

On the *language/compiler* level, programming or hardware description languages have been extended to allow developers to specify parts of the code that are amenable to approximations. *EnerJ* [72], for example, extends Java by approximate data types that enable the developer to declare which data can be processed by approximate processing units or stored in approximate storage. Compared to EnerJ, *Axilog* [115] locates at a lower level and extends the hardware description language Verilog by a set of language annotations to denote parts of the design for which relaxed quality constraints apply. For languages, the designer manually specifies the parts that may be subjected to approximation, what approximations are eventually applied, however, is decided by the compiler [18] or synthesis flow [69, 101] and also depends on the underlying approximate hardware which can comprise quality programmable processors [92], approximate hardware accelerators [34], and approximate storage [73]. General approximation techniques used by compilers are loop perforation [83], which reduces the loop count by skipping iterations, and code perforation [2], which skips computations in the algorithm. Both techniques reduce the computational workload, and thus, the application's computation time and the overall energy consumption.

On the hardware level, approximate computing is denoted as approximate logic synthesis (ALS) [75], which describes the process of generating approximate circuits (AxCs) for approximate hardware. The *register-transfer* level represents the most abstract hardware level in our computing stack and, at this level, precise components are replaced by approximate counterparts – ranging from simple components to complex hardware accelerators [34] or even complete processors [92]. Components subjected to approximations are denoted as *candidates*, and ALS at register-transfer level (RTL) seeks to find a combination of approximate candidates that optimizes the target metrics. Hence, ALS at RTL becomes a combinatorial problem where exhaustive enumeration is infeasible due to the large number of candidates that real-world hardware designs provide. Thus, automated ALS generally employs search or optimization algorithms to explore the design space [65, 69, 102] and approach the problem systematically. For the approximate candidates,

ALS can resort to approximate component libraries [44, 45, 62, 70, 81, 88], approximation techniques that operate on the candidate’s implementation at lower levels of abstraction [22, 41, 50, 91, 94, 106], or precision scaling to truncate least significant bits [69, 86, 101].

On the *logic* level, ALS modifies a circuit’s Boolean representation or transforms a circuit’s gate level netlist. Boolean techniques operate on abstract data structures, e.g., truth tables, and-inverter-graphs, or binary decision diagrams, and apply transformations to simplify the logic through Boolean matrix factorization [41], tying signals to constant values [22, 35], or extending the circuit’s set of don’t cares by approximate don’t cares [91]. Approaches transforming the circuit’s gate level netlist operate on a lower level of abstraction than Boolean approaches since the approximations target the description of the circuit’s electrical components and their connections. Pruning gates [77], substituting signals to enforce simplification [94], or random gate replacements [50] represent common netlist transformation techniques.

The *technology* level represents the lowest level of abstraction where transistors are – even manually – removed from a logic gate [38, 54] or timing-induced approximations are introduced [117, 118]. Timing-induced approximations involve over scaling a circuit’s supply voltage and/or the operating frequency, meaning that the circuit operates at a supply voltage below its nominal value or an operating frequency above its maximum, respectively. The effects of the timing-induced approximations are immediate since the quadratic relationship between voltage and power is exploited, or the circuit produces its output with less delay. However, timing-induced approximations require an expensive and complex timing-aware analysis of the circuit to detect and evaluate the failing timing paths; otherwise, the errors become uncontrollably large [75, 86, 112].

This dissertation focuses on approximate computing at hardware level, i.e., approximate logic synthesis; specifically, the focus is on automated search-based ALS processes on the register-transfer level and logic level, as highlighted in Figure 1.2. At these levels, the approximations deliberately modify the circuit’s original function and range from fine-grained to coarse-grained, i.e., from gates at logic level to more abstract components at RTL, while the provided abstraction allows for an efficient analysis of the circuit’s quality and target metrics.

Modeling approximate logic synthesis as a search or an optimization problem is common to perform the approximation systematically, and four main steps can be defined to describe a general search-based ALS process: *search*, *approximate*, *verify*, and *estimate*. This dissertation makes methodological contributions to three of the four steps (search, approximate, and verify). Furthermore, the dissertation contributes the flexible ALS framework CIRCA and a novel pre-processing technique for search space characterization. In summary, the main contributions of this dissertation are:

- *CIRCA* (Chapter 3, [101, 103]): We design and implement the framework CIRCA for search-based approximate logic synthesis. In a detailed analysis, we classify existing ALS frameworks on the basis of a set of orthogonal categories. Our analysis shows that existing frameworks suffer from an inflexible design that severely hampers the development and evaluation of new techniques for AxCs generation, as well as the comparison to existing ones. Using the analysis, we identify key requirements that an ALS framework should fulfill, yet the existing frameworks lack. With CIRCA, we present the first ALS framework that meets all requirements, and thus, presents a flexible framework to the approximate computing community to facilitate comparability among ALS methods.

- *Jump search* (Chapter 4, [102, 108]): We propose jump search, a novel technique for rapidly synthesizing approximate circuits and our contribution to the search step. ALS usually explores a large number of AxCs, but the required syntheses and verifications are costly; thus, forming a bottleneck for ALS. Jump search seeks to minimize the invoked syntheses and verifications by first selecting a set of AxCs-of-interest from the search space and then only evaluating a subset of the selected AxCs via synthesis and verification. The initial selection bases on a heuristic function that is free of synthesis and verification. Instead, the heuristic incorporates pre-computed *impact factors* that encode information on a candidate's impact on the target metric and the overall circuit error. In our experimental results, we show speed-ups of up to 468 $\times$  while achieving improvements in the target metrics comparable to commonly-used search algorithms.

- *MUSCAT* (Chapter 5, [106]): We present MUSCAT, a technique to approximate netlists and our novel contribution to the approximation step. MUSCAT substitutes connections with constant values by activating *cutpoints*. In this way, MUSCAT enables synthesis tools to simplify the logic by pruning dangling gates and propagating constants. Utilizing the concept of minimal unsatisfiable subsets from the field of formal verification, MUSCAT determines a maximal number of activated cutpoints and generates AxCs that are *valid-by-construction* regarding their quality constraints. We show that MUSCAT achieves up to 80% higher savings in the target metric hardware area than a state-of-the-art technique.

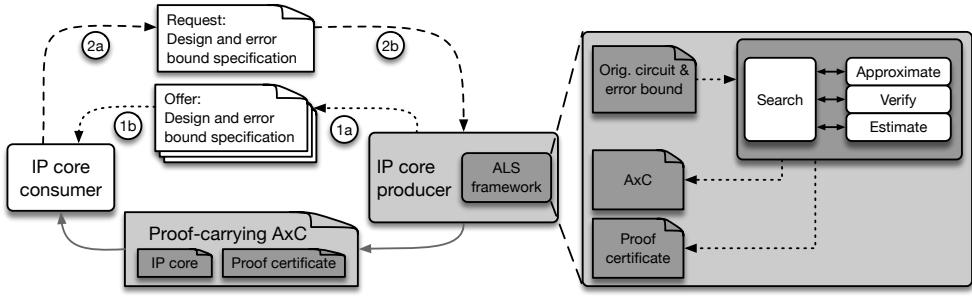

- *Proof-carrying approximate circuits* (Chapter 6, [104, 105]): The concept of proof-carrying approximate circuits brings together the fields of approximate computing and proof-carrying hardware, and is a novel contribution to the verification step. We utilize the concept of proof-carrying hardware [30] to annotate approximate circuits with *proof certificates*. The proof certificates allow the verification of the AxCs' quality without referring to a full formal verification of the quality constraints. A full verification generally shows long runtimes and is required to overcome trust issues between a producer and a consumer of an AxC. Using an AxC's proof certificate, however, allows the con-

sumer to verify the quality of the AxC quickly without having to trust the AxC producer; in fact, the burden of the full formal verification and the generation of the proof certificate is on the producer’s side, which has the computational resources to carry out the task efficiently and economically – in contrast to the consumer. In our experimental results, we reduce the consumer’s runtime for verifying an AxC by up to 99.83% over the producer’s runtime.

- *Search space characterization* (Chapter 7, [107, 109]): We present a formal verification-based methodology that performs *prior to* the ALS process and characterizes regions of the search space that only contains valid AxCs, i.e., AxCs that meet the quality constraints. We propose a novel *approximation miter* that makes our methodology independent of subsequently applied approximations and guarantees the validity of the as-valid characterized regions through the formal verification approach. Thus, the subsequent ALS process can employ any approximation technique and safely omit verifications for AxCs falling into the valid regions. In our experimental results, our approach achieves speed-ups of up to  $3.7 \times$  over a standard ALS that requires verifying all explored AxCs.

The remainder of this dissertation structures as follows:

Chapter 2 introduces the underlying concepts of this dissertation and discusses the state-of-the-art in the domain of approximate logic synthesis. In more detail, Section 2.1 describes the concepts of a general search-based ALS and discusses the state-of-the-art ALS methods on the register-transfer level and logic level. Section 2.2 elaborates on methods for the quality assurance of AxCs.

Chapter 3 presents CIRCA, our flexible ALS framework. Section 3.2 provides an analysis and a classification of existing ALS frameworks, Section 3.3 identifies key requirements for a flexible ALS framework, and Section 3.4 discusses CIRCA’s concept and architecture in detail. Section 3.5 evaluates CIRCA’s experimental results.

Chapter 4 proposes our synthesis methodology jump search. Section 4.2 motivates jump search’s concept, Section 4.3 presents the methodology, and Sections 4.5 and 4.6 discuss the different impact factors used in the heuristics presented in Section 4.7. Sections 4.8 and 4.9 detail jump search’s implementation and discuss the experimental results.

Chapter 5 presents our approximation technique MUSCAT. Section 5.2 discusses MUSCAT’s methodology, Section 5.3 presents comprehensive experimental results, and a case study in Section 5.4 probes MUSCAT’s potential at higher levels of abstraction, i.e., at register-transfer level.

Chapter 6 discusses the concept of proof-carrying approximate circuits. Section 6.2 elaborates on proof-carrying hardware, Section 6.3 discusses the

approach, Section 6.4 details the verification-based ALS process and the proof certificates, and Section 6.5 presents the experimental results.

Chapter 7 presents our methodology for characterizing valid regions in the search space prior to ALS. Section 7.2 discusses the related work and describes our novel approach. Then, Sections 7.3.1 and 7.3.2 detail on the construction of our novel approximation miter and Section 7.3.3 presents our methodology, before Section 7.4 evaluates the experimental results.

Chapter 8 concludes the dissertation, and Chapter 9 discusses future work.

# 2

---

## BACKGROUND

---

In the previous chapter, we have provided an introduction to the field of approximate computing and have set the focus for this thesis on approximate logic synthesis. In this chapter, we describe a general approximate logic synthesis process and discuss the state-of-the-art in this field. Then, we elaborate on methods for assuring the quality of the approximate outcome generated during the approximate logic synthesis process.

### 2.1 APPROXIMATE LOGIC SYNTHESIS

In this section, we first provide an overview of approximate logic synthesis in general and elaborate on the focus of this dissertation, i.e., automated search-based approximate logic synthesis. Then, we discuss the related work and the state-of-the-art, following in parts our published analyses [101, 106].

#### 2.1.1 *Overview*

Approximate computing (AC) on the hardware level is also referred to as approximate logic synthesis (ALS) [75]. ALS starts from an exact circuit design and applies approximations to optimize one or multiple target metrics, e.g., hardware area, delay, or power consumption. The approximations are applied to subcircuits or components amenable to approximations, so-called *candidates*. Candidates can be complex processing units or cuts in a gate level netlist and can be identified manually [115] or automatically [37, 65]. In order to ensure that an approximate circuit (AxC) provides sufficient quality to an application, the user imposes quality constraints upon the circuit's primary outputs (POs). Consequently, satisfying the user-defined quality constraints is a primary concern for an AxC. If an AxC adheres to the constraints, the AxC is considered *valid*; otherwise, the AxC is considered *invalid*. An input design provides many possible approximation opportunities, and existing work on ALS seeks to generate optimal AxCs either via analytical methods [42, 49, 79, 80] or search-based methods [20, 50, 65, 69, 76, 94].

Analytical methods are developed for a specific set of approximation techniques and error metrics, making the approach less flexible but generally runtime-efficient. Vašíček [90] additionally observed that analytical models at gate level might be fast, but increasing model granularity increases the complexity of their derivation due to non-trivial conditional probabilities.

Thus, constructing accurate yet simple mathematical models is currently impossible. Search-based methods, on the other hand, are more flexible and support a general set of approximation techniques and error metrics. However, search-based methods usually endure longer runtimes due to the increased generality.

This dissertation considers automated search-based ALS on the register-transfer level (RTL) and logic (or gate) level, where the original circuit design is iteratively approximated. In general, search-based ALS executes the following four main steps:

1. *Search* to explore the search space of approximate circuits.

2. *Approximate* to generate approximate circuits.

3. *Verify* to ensure that the approximate circuit satisfies the user-defined quality constraints and is valid.

4. *Estimate* (or *evaluate*) to determine the approximate circuit's target metrics.

In search-based ALS, a search or optimization algorithm explores the search space of AxCs and acts as central controller of the ALS process. In each iteration, the search explores new AxCs that are generated in an approximation step. The generated AxCs are then evaluated for the target metrics; a quality assurance step verifies the AxC's validity.

Scarabottolo et al. [75] classify the related work on ALS into three categories: 1) approximate high-level synthesis (AHLS), 2) Boolean rewriting, and 3) netlist transformation. The categories mainly differ in the level of abstraction and can complement each other [82, 86, 113, 119].

AHLS operates on the highest level of abstraction in ALS, the behavioral RTL, where designs are described, for example, in C/C++ or behavioral RTL Verilog. Both Boolean rewriting and netlist transformation locate on the logic level. Boolean rewriting approximates a Boolean representation of a design, e.g., truth tables or and-inverter-graphs (AIGs), and thus, operates on a more abstract level than netlist transformation that approximates a circuit's gate level netlist. Sections 2.1.2 to 2.1.4 provide an overview of prominent techniques and methods from the three categories. For more details, we refer the interested reader either to the corresponding publication of the method or to the survey of Scarabottolo et al. [75].

The three categories comprise methods that apply functional approximations, i.e., the implemented functionality of the circuit is simplified by introducing errors to the computations judiciously. In contrast to functional approximations stand timing-induced approximations applied on the technology level, which are out of the scope of this dissertation yet briefly explained for the sake of completeness.

Timing-induced approximations [68, 117, 118] are caused by voltage over-scaling or over-clocking and can be applied to any digital circuit [89]. With over-clocking, the circuit operates above its maximum operating frequency to lower the circuit's delay. Voltage over-scaling operates a circuit at a supply

voltage below its nominal value while maintaining the operating frequency. By exploiting the quadratic relationship between the supply voltage and the dynamic power dissipation, voltage over-scaling thus achieves power savings. Path delays, however, increase with decreasing supply voltage which, in turn, leads to timing errors. The timing-induced errors are extremely difficult to predict since the actual timing errors depend on the chip's design and layout. Thus, expensive timing-aware simulations on the final chip design must be performed for a thorough and reliable analysis, leading to a very time-consuming ALS process. In fact, without a systematic analysis, the errors can become uncontrollably large [75, 86, 112]. Furthermore, timing-induced approximations often achieve relatively small energy efficiency gains since circuits often contain many near-critical paths that the timing errors affect [60, 112]. Thus, most proposed approximation methods resort to functional approximations [112].

### 2.1.2 Approximate High-level Synthesis

Approximate HLS integrates approximate operators as building blocks, i.e., substitutes original candidates with approximate variants. To substitute the candidates, AHLS can utilize approximate candidates from a pre-generated approximate component library [45, 55, 62, 88] or employ dedicated approximation techniques from the logic level [22, 41, 56, 77, 91, 121, 122] to generate the approximate candidates during the ALS process. By employing methods from the lower levels, AHLS becomes, in a sense, an over-arching ALS process, which breaks ALS down into sub-problems that are solved on the lower levels, e.g., through Boolean rewriting methods or netlist transformations, and stitched back together in AHLS.

Nepal et al. [64, 65] proposed the ABACUS methodology that transforms a circuit into an abstract synthesis tree (AST). In an iterative approach, transformations on the AST are applied to create approximate circuits. The accuracy of the AxCs is evaluated by testing, area and power characteristics via ASIC synthesis using a standard cell library. The resulting three metrics are then combined into a fitness function, and the AxC with the best fitness is greedily selected as the starting circuit for the next iteration. This heuristic process runs for a user-defined number of iterations. Eventually, a Pareto front of designs is given, trading off accuracy for power.

The ASLAN framework [69] by Ranjan et al. is, to the best of our knowledge, the only framework able to approximate sequential circuits while guaranteeing error bounds. In a first step, ASLAN extracts combinational subcircuits amenable to approximation, i.e., the candidates. Then, a search space is generated by creating approximated versions of the candidates that vary in their local error constraints and estimated energy consumption. The applied approximation techniques are precision scaling and SALSA [91], although the authors also mention the applicability of other techniques. Finally, ASLAN employs hill climbing to find a locally optimal combination of approximated candidates. In each iteration, candidate versions with larger error

bounds are considered, and the combination resulting in the most significant energy savings is selected if the circuit adheres to the global error bound. Otherwise, the next-best combination of candidates is selected. Quality assurance relies on a so-called *sequential quality constraint circuit* that raises a flag if the error bound is violated. Since ASLAN deals with sequential circuits, time frame expansion is used to unroll both the original and the approximate circuit until they finish their computations. The resulting Boolean expression is then formally verified with a satisfiability (SAT) solver.

Barbareschi et al. [10] proposed the IDEÀ framework that employs a branch-and-bound algorithm. In each iteration, IDEÀ utilizes a depth-first search strategy and examines all approximation possibilities for a target candidate until no more approximations are possible, i.e., no further approximations can be applied to the candidate or the resulting AxC violates the user-defined quality constraints. Then, IDEÀ backtracks and explores the remaining branches until the search budget is exhausted. The branch-and-bound algorithm solely considers the quality of an AxC and IDEÀ only determines circuit parameters, such as area and power consumption, once all AxCs are found that meet the quality constraints. In this way, IDEÀ spends the largest amount of the search budget on identifying the best possible approximation of the early selected candidates in the design.

### 2.1.3 Boolean Rewriting

Boolean rewriting approximates the logical or Boolean representations of a circuit, such as truth tables or AIGs. The methodology BLASYS [41] relies on Boolean matrix factorization and factorizes a circuit's truth table into two smaller truth tables, which results in a smaller AxC after synthesis. Considering complete truth tables, however, limits BLASYS to small combinational circuits. For larger circuits, the authors propose to firstly factorize subcircuits for every factorization degree. Then, by integrating the approximated subcircuits into the overall design, BLASYS explores the search space until the user-defined error threshold is reached.

ALSRAC [56] by Meng et al. relies on approximate care sets, determined via logic simulation and expressed for internal nodes. Using the approximate care patterns, ALSRAC generates local approximate changes (or approximate resubstitutions), which are applied iteratively until the error threshold is reached.

Venkataramani et al. presented SALSA [91] which forms a so-called *quality constraint circuit* by providing the original and the approximate circuit, which initially is identical to the original circuit, with the same input and feeding the outputs of the circuits into a quality function that checks whether the given error bound holds. Forcing the error bound to hold, SALSA works backwards and applies standard don't care logic optimization techniques to reduce the area of the approximate circuit. Thus, the technique creates approximate combinational circuits that adhere to the error bound by construction.

Similar to SALSA, the approach of Chandrasekharan et al. [22] employs a setup with a quality constraint circuit but formally verifies the error constraint by combinational equivalence checking using a SAT solver. The approach represents a circuit's logic function as AIG and employs approximation-aware AIG rewriting as approximation technique, i.e., setting nodes to constant zero. Among all possible cuts on the critical paths of the circuit, the one with the smallest cut size is selected for rewriting. This heuristic is greedily iterated until there is no more possibility for rewriting without violating the error bound or the maximum number of iterations is reached.

Soeken et al. [85] represent the circuit description as a binary decision diagram (BDD) and apply approximations to reduce the size of the BDD. Fröhlich et al. [35] also utilize a BDD representation to determine an optimal BDD, i.e., a BDD with a minimum number of nodes, satisfying the quality constraints. Using BDDs allows the authors to make precise statements about the resulting error. However, the major weakness of these approaches is that BDDs are only applicable to small combinational circuits, i.e., BDDs do not scale well for large Boolean functions.

#### 2.1.4 Netlist Transformation

Netlist transformation techniques operate on a circuit's gate level netlist, and a commonly-used approach is gate level pruning (GLP) presented by Schlachter et al. [77, 78]. GLP disconnects a wire from the node driving it and inserts a constant as driver instead. As a result, a synthesis tool can optimize the logic by 1) removing (or pruning) dangling nodes and 2) simplifying the subsequent logic through constant propagation. To determine which node to prune, the authors rank the nodes by the product of their switching activity and their significance, a measure for the node's impact on the circuit's error. An iterative algorithm simulates the hardware design to compute each node's significance-activity product and evaluates whether the design meets the quality constraints. The algorithm then prunes the node with the lowest significance-activity product from the design in the next iteration. However, Scarabottolo et al. [74, 76] showed that a node's significance is often too conservative, leading to suboptimal AxCs.

Thus, Scarabottolo et al. [76] extended GLP to circuit carving. Circuit carving seeks to carve out the largest subcircuit in the design so that the resulting AxC still meets the quality constraints. The authors propose to use a node's significance as an error estimate and explore a binary search tree to determine whether a node is included in the subcircuit. However, as an AxC's actual error cannot be determined via the significances, a subsequent quality check is performed. An exploration of the complete binary search tree is considered intractable; hence, the authors defined pruning criteria for the tree. One criterion considers a node's estimated significance (or estimated error). To estimate the nodes' significance, the authors suggest simulating the complete circuit exhaustively, which is accurate but only applicable to small circuits, or employing an error estimation model, which has shown to

be often too conservative. In any case, the error estimation's accuracy dictates the approximate outcome.

In an attempt to increase the error estimation accuracy and improve the quality of results in GLP, Scarabottolo et al. [74] proposed Partition & Propagate (P&P). P&P partitions the design into cuts which are simulated exhaustively to determine each node's significance. Due to the exhaustive simulation, the accuracy of the nodes' significance becomes more accurate. The authors argue that the number of inputs to the cuts is small, and thus, simulation can be performed efficiently. Nevertheless, the approach can only specify an estimate of an error bound, which, as their experimental results show, may still be too conservative by several orders of magnitudes. Consequently, a subsequent quality verification is required.

Another netlist transformation approach is circuit design by evolutionary algorithms that iterate over thousands of circuit generations and modify netlists by mutation operators. This approach often leads to unusual yet efficient AxCs as, for example, shown by the adders and multipliers provided in the *EvoApproxLib* [62].

Venkataramani et al. proposed SASIMI [94], which uses a substitute-and-simplify approximation technique. SASIMI identifies near-identical signal pairs, i.e., two signals which show similar behavior, and substitutes one with the other to simplify the logic. First, SASIMI evaluates and ranks signal pairs with a heuristic function including area and delay parameters. Then, with a gradient ascent technique, more accurately hill climbing, the highest-ranked pair is selected for substitution. The process is iterated until the user-defined quality constraints are violated. Additionally, the authors suggest the concept of *quality configurable circuits*, which are circuits that can operate in either an accurate or approximate version.

The SCALS framework presented by Liu and Zhang [50] initially maps a gate level logic network to a target technology. In an iterative process, SCALS extracts sub-netlists from the mapped netlist to which randomly chosen approximations or optimizations are applied. The candidates are then evaluated by a function including the area and the error, gained through a testing approach. A Metropolis-Hastings algorithm steers the candidate selection and the search until reaching a predefined number of iterations. Additionally, the user can specify a confidence interval for the estimated error. To evaluate the confidence on the estimated error, SCALS employs the T-test [99].

## 2.2 QUALITY ASSURANCE

Approximations applied to a design's candidates cause errors that propagate and potentially amplify or attenuate. In fact, the correlation between the errors at the candidates and the circuit's primary outputs is generally complex, making it a complex task to determine the resulting error at the circuit's primary outputs. Thus, approximate logic synthesis must employ a quality assurance step that checks whether an AxC satisfies the user-defined quality

constraints. The quality constraints are defined either by application-specific metrics, e.g., structural similarity [96], or by general error metrics, which can be further distinguished into *worst-case* error metrics (also denoted as *non-statistical* error metrics) or *average-case* error metrics (also denoted as *statistical* error metrics). This dissertation focuses on the general error metrics and discusses commonly used metrics in the following.

Consider the Boolean function  $f : \mathbb{B}^n \rightarrow \mathbb{B}^m$  with  $n$  primary input bits and  $m$  primary output bits that describes the correct functionality of circuit  $C$ , and let the Boolean function  $\tilde{f} : \mathbb{B}^n \rightarrow \mathbb{B}^m$  of the  $A \times C \tilde{C}$  be an approximate function of  $f$ . The function  $\text{int}(x) : \mathbb{B}^m \rightarrow \mathbb{Z}$  translates the binary vector  $x$  to an integer value, e.g., considering the binary representation  $\text{int}(x) = \sum_{i=0}^{m-1} 2^i x_i$  (cf. [89]).

With the notation above, we can then define the following worst-case or non-statistical error metrics:

- *Worst-case absolute error*  $\epsilon_{WC}$ : The worst-case (WC) absolute error (short: worst-case error), which is sometimes also denoted as *error magnitude* or *error significance* [89], computes the maximum absolute difference between the outputs of the original circuit  $C$  and the  $A \times C \tilde{C}$  over all input values. In fact, the WC error is a fundamental error metric [89] and is mainly considered in this dissertation. The WC error is defined as follows:

$$\epsilon_{WC}(f, \tilde{f}) = \max_{\forall x \in \mathbb{B}^n} |\text{int}(f(x)) - \text{int}(\tilde{f}(x))| \quad (2.1)$$

- In its normalized form, we normalize the worst-case error  $\epsilon_{WC}$  to the maximum output value of  $f(x)$ :

$$\epsilon_{WC,\text{norm}}(f, \tilde{f}) = \frac{\epsilon_{WC}(f, \tilde{f})}{\max_{\forall x \in \mathbb{B}^n} \text{int}(f(x))} \quad (2.2)$$

- *Worst-case relative error*  $\epsilon_{WC,\text{rel}}$ : The worst-case relative error is similar to the worst-case error but computes the maximum relative difference between the original and the approximate outputs rather than the absolute difference. The worst-case relative error is defined as follows, where the division by  $\max(1, f(x))$  prevents a division by zero:

$$\epsilon_{WC,\text{rel}}(f, \tilde{f}) = \max_{\forall x \in \mathbb{B}^n} \frac{|\text{int}(f(x)) - \text{int}(\tilde{f}(x))|}{\max(1, f(x))} \quad (2.3)$$

- *Bit-flip error*  $\epsilon_{BF}$ : The bit-flip error, also denoted as *maximum Hamming distance* [89], computes the maximum number of bits that discern between the precise value of  $f$  and the approximate value of  $\tilde{f}$ . The bit-flip error is defined as follows:

$$\epsilon_{BF}(f, \tilde{f}) = \max_{\forall x \in \mathbb{B}^n} \left( \sum_{i=0}^{m-1} f_i(x) \oplus \tilde{f}_i(x) \right) \quad (2.4)$$

The average-case or statistical error metrics are defined as follows:

- *Mean absolute error  $\epsilon_{MAE}$* : The mean absolute error (or *average-case arithmetic error*) sums the absolute differences between the original and approximated function and averages the results over the number of inputs:

$$\epsilon_{MAE}(f, \tilde{f}) = \frac{1}{2^n} \sum_{\forall x \in \mathbb{B}^n} |\text{int}(f(x)) - \text{int}(\tilde{f}(x))| \quad (2.5)$$

- *Mean squared error  $\epsilon_{MSE}$* : The mean squared error is similarly computed as the mean absolute error; instead of computing the absolute difference, the difference between the original and the approximate function output is squared:

$$\epsilon_{MSE}(f, \tilde{f}) = \frac{1}{2^n} \sum_{\forall x \in \mathbb{B}^n} (\text{int}(f(x)) - \text{int}(\tilde{f}(x)))^2 \quad (2.6)$$

- *Mean relative error  $\epsilon_{MRE}$* : The mean relative error sums the relative errors between the original and the approximate function and averages the result over the number of inputs:

$$\epsilon_{MRE}(f, \tilde{f}) = \frac{1}{2^n} \sum_{\forall x \in \mathbb{B}^n} \frac{|\text{int}(f(x)) - \text{int}(\tilde{f}(x))|}{\max(1, \text{int}(f(x)))} \quad (2.7)$$

- *Error rate  $\epsilon_{ER}$* : The error rate (or *error probability*) specifies the percentage of inputs for which the outputs of the original and the approximate function differ:

$$\epsilon_{ER}(f, \tilde{f}) = \frac{1}{2^n} \sum_{\forall x \in \mathbb{B}^n} f(x) \neq \tilde{f}(x) \quad (2.8)$$

In order to assess the error or quality of an AxC, analytical methods [74, 76, 77, 80], testing-based approaches [65, 94], or formal verification [23, 69, 89–91] can be employed. Analytical methods employ error models for the input design, which allow to predict or estimate an AxC’s error prior to its generation [5, 80]. While analytical methods can perform the predictions efficiently, the error model must be accurate and fully specified for the input design to deliver meaningful estimations. In fact, analytical methods are usually utilized to provide information to the ALS process for guidance rather than to verify an AxC’s adherence to the quality constraints. Thus, the existing analytical approaches nevertheless rely on formal verification or testing in an additional quality assurance step to ensure the quality of a generated AxC [76, 77]. Furthermore, Vašíček observed that constructing accurate yet

simple mathematical models on the gate level is currently impossible, as described in Section 2.1.1.

Testing represents the most general approach for assessing the quality as the approach relies on circuit simulation, which works with any circuit design. In testing, a circuit simulator simulates the circuit using test vectors from a test vector set. For exhaustive simulation, the test vector set contains all possible inputs, meaning that all inputs are explicitly enumerated, which leads to an exponential worst-case execution time [90] and limits the approach to small-scale circuits. Thus, in practice, many authors scale the simulation's workload over the size of the test vector set and only employ a subset of all inputs. The larger the test vector set is, the higher is the confidence in the estimated error value. However, the testing runtime increases with the increasing size of the set [89].