# Cubic AlGaN/GaN Hetero-Junction Field-Effect Transistors Fabrication and Characterisation

Dem Department Physik

der Universität Paderborn

zur Erlangung des akademischen Grades eines

Doktors der Naturwissenschaften vorgelegte

**Dissertation**

von

Elena Tschumak

Paderborn, Januar 2010

# **Contents**

| A   | bstract                                                                           | i   |

|-----|-----------------------------------------------------------------------------------|-----|

| 1   | Introduction                                                                      | iii |

| 2   | Fundamentals                                                                      | 1   |

|     | 2.1 Properties of cubic III-Nitrides                                              | 1   |

|     | 2.2 Molecular Beam Epitaxy (MBE)                                                  | 3   |

|     | 2.3 Structural Characterisation Methods                                           | 5   |

|     | 2.3.1 High Resolution X-Ray Diffraction (HRXRD)                                   | 5   |

|     | 2.3.2 Atomic Force Microscopy (AFM)                                               |     |

|     | 2.3.3 Photoluminescence Spectroscopy (PL)                                         | 9   |

|     | 2.4 Device Structuring                                                            | 10  |

|     | 2.4.1 Photolithography and Structuring                                            | 10  |

|     | 2.4.2 FET Fabrication                                                             |     |

|     | 2.5 Electrical Characterization Methods                                           | 14  |

|     | 2.6 Simulation Calculations                                                       |     |

| 3   | Principals of Hetero-Junction Field-Effect Transistors                            | 17  |

|     | 3.1 Basic Device Structure                                                        | 18  |

|     | 3.2 Current-Voltage Characteristics                                               | 19  |

| 4   | Separation between Substrate and HFET Device                                      | 25  |

| 211 | 4.1 Model Calculations of Cubic AlGaN/GaN FETs on Different bstrates 25           |     |

| Ju  | 4.2 Carbonised Si (001)                                                           | 28  |

|     | 4.3 Ar <sup>+</sup> Implanted 3C-SiC (001)                                        |     |

|     | 4.4 Carbon Doping of Cubic GaN                                                    | 35  |

| 5   | Properties of Cubic AlGaN/GaN Field Effect Transistors                            | 43  |

|     | 5.1 Properties of Cubic Al <sub>x</sub> Ga <sub>1-x</sub> N/GaN Hetero-Structures | 43  |

|     | 5.2 HFETs of Cubic Al <sub>x</sub> Ga <sub>1-x</sub> N/GaN                        |     |

|     | 5.2.1 HFET with 200 nm c-GaN Buffer Layer on 3C-SiC (HFET A)                      | 49  |

|     | 5.2.2 HFET on 3C-SiC/Si (001) Substrate (HFET B)                                  |     |

|     | 5.2.3 Comparison of HFET with Normally-off (HFET C) and                           |     |

|     | Normally-on Characteristics (HFET D) on Ar <sup>+</sup> Implanted                 |     |

|     | 3C-SiC (001)                                                                      | 55  |

|     | 5.3 Comparison of Polar, Semi-polar and Non-polar AlGaN/GaN HFETs                 | 59  |

| 6 Role of Metal-Semiconductor Contacts for HFET Devices                                   |

|-------------------------------------------------------------------------------------------|

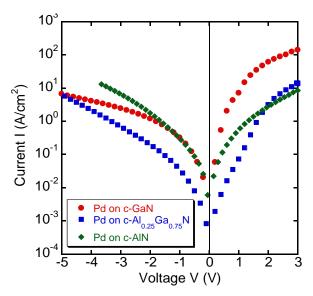

| 6.1 Schottky Barrier Gate61                                                               |

| 6.1.1 IV Characteristics of Schottky Contacts on c-GaN, c-AlGaN, and c-AlN 62             |

| 6.1.2 Gate Leakage                                                                        |

| 6.2 Role of Source and Drain Contact Resistance for HFET Devices                          |

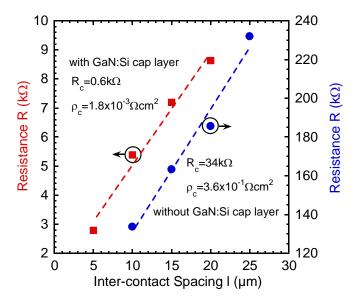

| 6.2.1 Reduction of Source and Drain Contact Resistance by n <sup>+</sup> GaN  Cap Layer70 |

| 6.2.2 Advancing Interface Ohmic Contact to AlGaN/GaN Hetero-<br>Structures 72             |

| 6.2.3 Temperature Dependence of Source and Drain Contact Resistance73                     |

| 7 Prospects for New HFET Structures                                                       |

| 7.1 Analysis of Crystalline Properties of c-GaN and c-AlGaN79                             |

| 7.2 Avoiding of Shunt Current80                                                           |

| 7.3 Effect of c-AlGaN δ-Doping82                                                          |

| 7.4 Variation of the c-AlGaN Barrier Thickness                                            |

| 7.5 Scaling of the HFET Device Dimensions84                                               |

| 7.6 Design of Potential Future c-AlGaN/GaN HFETs86                                        |

| Summary87                                                                                 |

| Appendix 89                                                                               |

| Appendix A: List of Symbols89                                                             |

| Appendix B: List of Abbreviations91                                                       |

| Appendix C: List of Room Temperature Parameters92                                         |

| Appendix D: List of Samples93                                                             |

| Appendix E: Drawing of Photomasks for FET Fabrication94                                   |

| Appendix F: Simulation Software                                                           |

| Appendix G: Conventional Interpretation of CV Data102                                     |

| Appendix H: List of Figures                                                               |

| Appendix I: List of Tables107                                                             |

| References                                                                                |

| Publication List                                                                          |

| Acknowledgements                                                                          |

## **Abstract**

Hetero-junction field-effect transistors made of metastable cubic AlGaN/GaN represent an alternative for devices made of stable hexagonal III-nitrides. Due to the absence of spontaneous and piezoelectric fields, cubic AlGaN/GaN provides an incentive for fabrication of hetero-junction field-effect transistors with both normally-on and normally-off characteristics.

In this work, field-effect transistors were fabricated of cubic AlGaN/GaN grown on carbonized silicon (3C-SiC/Si) and free standing Ar<sup>+</sup> implanted 3C-SiC substrates by molecular beam epitaxy. For electrical device isolation, a carbon doped GaN:C buffer was investigated. For this purpose, a new CBr<sub>4</sub> gas source was used and optimized.

Device structuring is performed by photolithography, liftoff process, reactive ion etching, and plasma enhanced chemical vapour deposition. Cubic AlGaN/GaN heterojunction field-effect transistors with normally-on and normally-off output characteristics depending on the doping of the AlGaN barrier were demonstrated. The devices are characterized by electrical dc current-voltage and capacitance-voltage measurements. The measurement data were analysed using a 1D-Poisson solver and the ATLAS device simulation program. Finally, sample structures for improved cubic AlGaN/GaN field-effect transistor devices were developed.

## 1 Introduction

AlGaN/GaN hetero-junction field-effect transistors (HFETs) are presently of major interest for use in electronic devices, in particular for high-power and high-frequency amplifiers. This is motivated by their potential in commercial and military applications, e. g. in communication systems, radar, wireless stations, high-temperature electronics and high-power solid-state switching. Currently, state of the art HFETs are fabricated of the *c*-plane surface of wurzite (hexagonal) AlGaN/GaN hetero-structures. Their inherent spontaneous and piezoelectric polarization fields produce extraordinary large sheet carrier concentrations at the AlGaN/GaN hetero-interface. Therefore, all these devices are of the normally-on type [1]-[3].

However, for switching devices and digital electronics field-effect transistors (FET) with normally-off characteristics are desirable. Recently HFETs of *c*-plane AlGaN/GaN with normally-off operations have been reported [4], [5]. Some groups used non-polar *a*-plane AlGaN/GaN to fabricate HFETs [6], [7] and demonstrated that the electrical output characteristics of these devices are different for different gate finger orientations on *a*-plane layers. However, no field-effect transistors have been realized with non-polar cubic group III-nitrides to date, although it was discussed recently by Abe et al. [8] that they would offer to fabricate HFETs without undesirable parasitic piezoelectric and spontaneous polarization fields and with equal electrical properties for all gate orientations. Furthermore, the cubic nitrides would allow using the same technology for normally-on and normally-off devices.

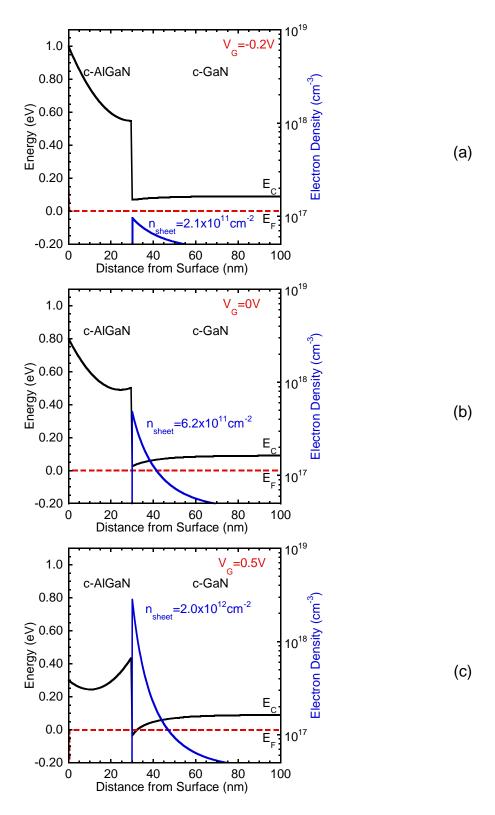

The difference between the hexagonal and cubic AlGaN/GaN systems is demonstrated in Figure 1.1, which shows the conduction band edge and the electron concentration calculated for (a) hexagonal and (b) cubic AlGaN/GaN hetero-structures with the same parameters. An electron accumulation at the AlGaN/GaN hetero-interface is expected in both structures, but the electron channel in the hexagonal hetero-structure is highly conductive with sheet carrier density of  $2\times10^{13}$  cm<sup>-2</sup> while the channel at the cubic hetero-interface is – with a carrier density that is two orders of magnitude lower – nearly depleted. However, it is possible to tune the charge sheet density of cubic AlGaN/GaN by intentional doping for fabrication of HFETs with normally-on characteristics.

The aim of this work was to realise HFETs based on cubic AlGaN/GaN, including the deposition of hetero layers by MBE, device structuring and their electrical characterization. However, to succeed with the realization of c-AlGaN/GaN HFETs certain conditions have to be fulfilled.

One of the most important conditions for such devices is a high insulating substrate or a semi-insulating layer between the substrate and the device to avoid buffer leakage. For

**Figure 1.1** Calculated conduction band edge and electron concentration of (a) a hexagonal and (b) a cubic AlGaN/GaN hetero-layer structure.

this purpose, two different substrates, namely carbonised silicon and Ar<sup>+</sup> implanted free standing 3C-SiC were investigated. The properties of c-AlGaN/GaN hetero layers on these substrates are introduced in Chapter 4.

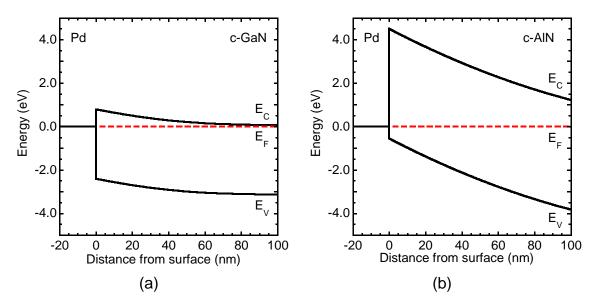

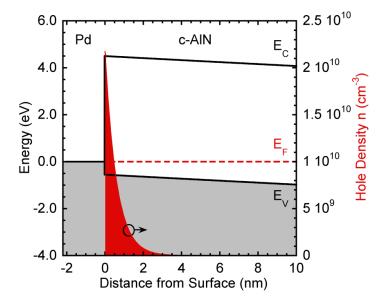

Then, low resistivity ohmic source and drain contacts are necessary to achieve high transconductance and a good Schottky gate contact to avoid gate leakage. Therefore, different metal contacts on c-GaN, c-AlGaN and c-AlN were investigated and described in Chapter 6. The measurement results were used to analyse the output characteristics of c-AlGaN/GaN HFETs and to model new optimized HFET structures, which are discussed in Chapter 7.

Additionally, the output characteristics of cubic AlGaN/GaN (c-AlGaN/GaN) HFETs depend on the thickness and doping of the c-AlGaN barrier layer and the lateral design of the device structure. Therefore the properties of the c-AlGaN/GaN hetero structures and HFETs were analysed with the aid of computer simulations.

The main part of this work is Chapter 5 in which cubic AlGaN/GaN HFETs are introduced and devices with both normally-on and normally-off output characteristics are demonstrated.

## 2 Fundamentals

In this work, hetero-junction field-effect transistors (HFETs) were fabricated of cubic AlGaN/GaN (c-AlGaN/GaN) and investigated concerning their output and transfer characteristics. To understand the electrical properties of the devices, model calculations were performed using a 1D-Poisson solver and the ATLAS device simulation software.

This chapter gives an introduction on the physical properties of cubic group-III nitrides, their epitaxial growth by molecular beam epitaxy and the characterization methods of their structural properties. A crucial part of this work was the design and fabrication of HFETs. Therefore, the device production process is described in detail in an extra subsection. Finally, a test assembly for current-voltage (IV) and capacitance-voltage (CV) measurements and basic parameters used for model calculations are introduced.

#### 2.1 Properties of cubic III-Nitrides

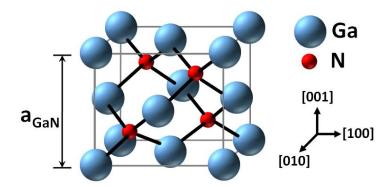

Group III-nitrides crystallize in the stable hexagonal (wurzite) or in the metastable cubic (zincblende) structure. The challenge of this work was the realization of HFETs based on *cubic* AlGaN/GaN which as a non-polar material – comparable to AlGaAs/GaAs – is capable for fabrication of normally-off devices. Figure 2.1 shows the crystallographic structure of cubic group III-nitrides using the example of cubic GaN (c-GaN). The structure is based on a face-centred unit cell with a base of two atoms. In case of stoichiometric growth conditions the metal is incorporated on the (0,0,0) lattice point, and the nitrogen is placed on the  $(\frac{1}{4},\frac{1}{4},\frac{1}{4})$  lattice site. In the direction of the basic vectors, the crystal consists of two alternating layers which contain only metal or nitrogen. The

**Figure 2.1** Zincblende structure of cubic GaN.

structure is very similar to that of a diamond with a strong covalent bond. This results in a high chemical inertness and thermodynamical stability. Based on the crystal symmetry cubic group III-nitrides exhibit isotropic electrical conductivity and no piezoelectric fields. These properties are important advantages of c-AlGaN/GaN which are used for HFET devices.

The c-AlGaN/GaN hetero-structures were deposited on cubic 3C-SiC substrate. Lattice constant a and band gap energies  $E_g$  of c-GaN, c-AlN, and 3C-SiC are summarized in Table 2.1. The lattice constant of c-Al<sub>x</sub>Ga<sub>1-x</sub>N is calculated by the linear interpolation of the c-GaN and c-AlN compounds called Vegard's law:

$$a(Al_xGa_{1-x}N) = x \cdot a(AlN) + (1-x) \cdot a(GaN).$$

(2.1)

For the band gap of Al<sub>x</sub>Ga<sub>1-x</sub>N alloys parabolic compositional dependence is traditionally assumed:

$$E_g(Al_xGa_{1-x}N) = f(x) - bx(1-x),$$

(2.2)

where the bowing parameter b captures the magnitude of the parabolic nonlinearity, and where

$$f(x) = x \cdot E_g(AlN) + (1 - x) \cdot E_g(GaN)$$

(2.3)

is simply the linear compositional dependence of the band gap in the absence of bowing [9]. The dispersion of the bowing parameter of hexagonal  $Al_xGa_{1-x}N$  reported by various researchers extends from b=-0.8 eV (upward bowing) to b=2.6 eV (downward bowing), most likely emanating from  $Al_xGa_{1-x}N$  alloys prepared by different techniques with varying quality [10]. However, there are no investigations for band gap parameters of cubic  $Al_xGa_{1-x}N$  alloys grown by molecular beam epitaxy to date. Therefore, only the linear component from Equation (2.3) was used for the estimation of the band gap of c- $Al_xGa_{1-x}N$  in this work.

**Table 2.1** Material parameter of c-GaN, c-AlN and 3C-SiC.

| Semiconductor Material | Lattice Constant a | Band Gap $E_g$                                  |  |

|------------------------|--------------------|-------------------------------------------------|--|

| c-GaN                  | 4.53 Å [11]        | 3.26 eV (direct) [11]                           |  |

| c-AlN                  | 4.37 Å [12]        | 5.3 eV (indirect) [13]<br>5.93 eV (direct) [13] |  |

| 3C-SiC                 | 4.359 Å [14]       | 2.4 eV (indirect) [15]<br>6.7 eV (direct) [15]  |  |

#### 2.2 Molecular Beam Epitaxy (MBE)

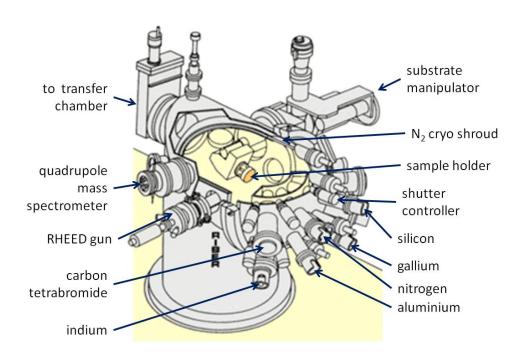

Cubic GaN layers and AlGaN/GaN hetero-structures were deposited by molecular beam epitaxy (MBE) [16] in a RIBER MBE 32 system with a HD-25 radio frequency (rf) activated plasma source by Oxford Applied Research. The sketch of the interior of the MBE UHV-chamber can be seen in Figure 2.2 which shows the sample holder facing the effusion cells. The growth position of the samples is the crossover point of the various molecular and atomic beams from the effusion sources. All effusion cells have an orifice of 2.5 cm in diameter and are located 12 cm from the substrate. To improve the uniformity of deposition, the sample holder can be rotated by the substrate manipulator. A liquid-nitrogen cooled shroud is used to enclose the entire growth area in order to minimize residual water vapour and carbon-containing gases in the vacuum chamber during epitaxial growth.

The loading of a sample holder is done via a load lock in order to avoid deterioration of the vacuum in the MBE chamber. To avoid unintentional doping (UID) of semiconductors, the MBE system and the source materials have to conform to stringent purity levels.

The MBE chamber is equipped with three RIBER ABN35 standard elemental sources which are used for the evaporation of Ga, Al and In for group III-nitride epitaxy. One additional standard cell is filled with Si and is used for silicon doping. The temperature of these effusion cells is measured at the bottom of the pyrolytic boron nitride (PBN) crucible by a thermocouple. The elemental source materials are of 99,9999 % (6N) purity.

Additionally, a self-made carbon tetra bromide (CBr<sub>4</sub>) source is connected directly to

**Figure 2.2** Sketch of the interior of the MBE UHV-chamber which shows the sample holder facing to the effusion cells.

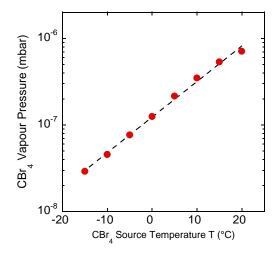

**Figure 2.3** Temperature dependent vapour pressure curve of the CBr<sub>4</sub> source measured at maximum valve opening.

the MBE chamber. It is used for doping of c-GaN with carbon (c-GaN:C). The CBr<sub>4</sub> is a colourless solid which sublimates already at room temperature. The CBr<sub>4</sub> flux is controlled by a needle valve and/or the source temperature. The source temperature can be varied between -15 °C and +50 °C. The temperature-dependent vapour pressure curve of the CBr<sub>4</sub> source measured at the sample position at maximum valve opening is depicted in Figure 2.3. The black dashed curve is an exponential fit of the measurement data. The gas supply line is heated to 80 °C to avoid CBr<sub>4</sub> resublimation. The gas injector is heated to 120 °C during the c-GaN:C growth. During the doping process, the CBr<sub>4</sub> molecules are cracked on the sample surface of 720 °C to carbon which is incorporated into c-GaN and other volatile bromine compounds which are pumped out.

As nitrogen source the Oxford Applied Research HD-25 plasma source was operated with a rf energy of 300 W to produce the active atomic nitrogen flux. The PBN aperture disc used for the plasma source has 25 holes each with a diameter of 0.3 mm. The rf energy is inductively coupled to a PBN nozzle tube into which the commercial ultra-high purity nitrogen is led via a mass flow controller.

In order to minimize hexagonal inclusions in the c-GaN layers and to obtain an optimum surface roughness, coverage of one monolayer Ga was established during growth [17]. All samples were deposited at a substrate temperature of 720 °C with a c-GaN growth rate of 115-120 nm/h. Prior to the growth process, substrates were cleaned by acetone, propanol and deionized water and were chemically etched by a buffered oxide etching (BOE, NH<sub>4</sub>F:H<sub>2</sub>O:HF=4:6:1).

Reflection high energy electron diffraction (RHEED) [18] was used to monitor the crystalline nature of the sample surface during sample growth (in-situ control). This method uses a high energy electron beam (10-20 kV acceleration voltage) which hits the surface at an angle of 1°-3°. The electrons are diffracted at the crystal surface and are forward scattered to a fluorescence screen. The resulting diffraction pattern on this screen is a superposition of the contribution of electrons that have been scattered from atomically flat regions of the crystal and those that have been transmitted through asperities rising

above the surface. Thus, the formed diffraction pattern gives information about the symmetry and periodicity of ordered layers near the surface and the position of atoms within the unit cell. The observed RHEED pattern of cubic III-nitrides was used to control the surface stoichiometry such a  $c-(2\times2)$  reconstruction during the growth interruption [19], to control the growth rate by measuring the c-AlGaN RHEED intensity oscillations [20] and to measure the Ga coverage of the c-GaN surface during growth [17].

#### 2.3 Structural Characterisation Methods

#### 2.3.1 High Resolution X-Ray Diffraction (HRXRD)

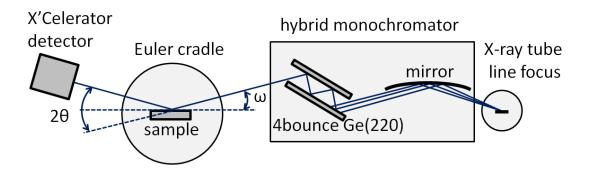

High resolution X-ray diffraction (HRXRD) was used to investigate c-GaN and c-AlGaN/GaN layers for their structural properties as dislocation density, hexagonal inclusions, Al mole fraction of c-Al<sub>x</sub>Ga<sub>1-x</sub>N and strain condition of c-AlGaN on c-GaN buffer. For this purpose, a Philips X'Pert materials research diffractometer was used with a copper anode emitting a  $K_{\alpha l}$  radiation of  $\lambda$ =1.54056 Å and a  $K_{\alpha 2}$  radiation of  $\lambda$ =1.54444 Å. A schematic sketch of the diffractometer is shown in Figure 2.4. The X-ray tube is equipped with a line focus and a hybrid monochromator which guarantees a beam divergence of 47 arcsec. The monochromator consists of a graded parabolic mirror in connection with a (220) channel-cut germanium crystal. The mirror parallelises the beam and the germanium crystal blocks the  $K_{\alpha 2}$  line. The sample is mounted onto an Euler cradle which allows an independent variation of the angle of incident  $\omega$ , the diffraction angle  $2\theta$ , the rotation around the surface normal  $\phi$  and the incident axis  $\psi$ , as well as a linear motion in the three directions x, y and z. A multichannel detector X'Celerator was used for measurements of  $\omega$ - and  $\omega$ -2 $\theta$ -line scans and for measurements of reciprocal space maps (RSM) [21].

For a mono-crystal the diffraction of X-rays can be described by the Bragg equation [22]

$$\lambda = 2d_{hkl} \cdot \sin \theta. \tag{2.4}$$

**Figure 2.4** Schematic drawing of the Phillips X'Pert MDR HRXR diffractometer consisting of X-ray tube, hybrid monochromator, Euler cradle and X'Celerator detector.

The triplet (hkl) denotes the Miller indices and  $d_{hkl}$  for cubic structure is given by

$$d_{hkl} = \frac{a}{\sqrt{h^2 + k^2 + l^2}} \tag{2.5}$$

where  $d_{hkl}$  is the spacing of the lattice planes, a the lattice constant,  $\lambda$  the wavelength of the X-ray radiation and  $\theta$  the incident angle of the radiation. More details of X-ray diffraction are given in [21].

Three different types of scans were performed to investigate the properties of the c-GaN and c-AlGaN/GaN layers, namely the  $\omega$ -2 $\theta$ -scans, the  $\omega$ -scans and the reciprocal space maps (RSM).

The  $\omega$ -2 $\theta$ -scans allow measurements where the angular rotation speed of the detector is twice that of the incident angle. In case of scanning symmetrical lattice points, this is equal to the reflection from the lattice planes parallel to the sample surface. We get information with respect to vertically aligned properties, like the composition of ternary alloys and lattice mismatch.

The  $\omega$ -scan or so-called rocking curve is a scan with the detector angle in a fixed position, while only the angle of incidence is changed. From the width of the reflex perpendicular to the surface the dislocation density D can be evaluated using the model by P. Gay [23] which is based on the formula

$$D = \frac{\Delta\theta^2}{9h^2} \tag{2.6}$$

where  $\Delta\theta$  is the full width of half maximum (FWHM) of the rocking curve in radians and b the length of the Burgers vector. For a zincblende structure the Burgers vector of a  $60^{\circ}$  dislocation is calculated by

$$b = \frac{a}{\sqrt{2}} \tag{2.7}$$

where a is the lattice constant of c-GaN.

A combination of different  $\omega$ -2 $\theta$ -scans slightly displaced along the  $\omega$ -direction results in an area map. This scanning method is known as RSM resulting in a two-dimensional intensity map. From the RSM it is possible to get the exact position of the reflection maximum and more information about the expansions in the different crystallographic directions.

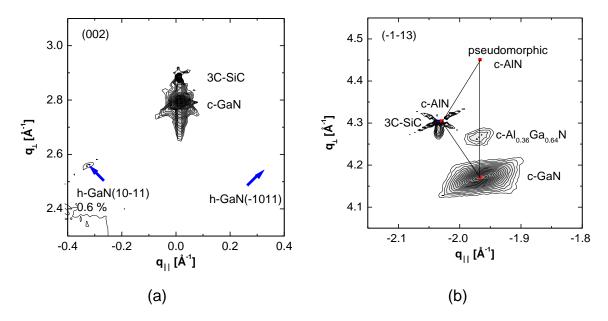

From the RSM around the (002) reflex of c-GaN the hexagonal GaN inclusions grown on (111) facets can be estimated. The RSM of a c-AlGaN/GaN hetero structure deposited on Ar<sup>+</sup> implanted 3C-SiC (sample 1855) is shown in Figure 2.5 (a). In this measurement mode, only reflexes of 3C-SiC and c-GaN buffer layer are clearly detected. The reflex of c-AlGaN is superposed to the wide c-GaN reflex and is not resolvable. The position of the hexagonal (10-11) and (-1011) GaN reflex is indicated by blue arrows. From the intensity ratio of the hexagonal to the cubic reflex 0.6 % hexagonal inclusions were estimated in this sample.

**Figure 2.5** Reciprocal space map of a c-AlGaN/GaN hetero structure on free standing 3C-SiC around (a) (002) and (b) (-1-13) reflex of c-GaN.

The position of the c-AlGaN reflex relative to the (-1-13) reflex of c-GaN in the RSM gives information about the Al mole fraction and the strain of c-AlGaN. Figure 2.5 (b) shows asymmetrical RSM around the (-1-13) reflex of the same c-AlGaN/GaN hetero structure (sample 1855). In this measurement mode, the reflexes of 3C-SiC, c-GaN and c-AlGaN are distinguishable. The theoretical positions of relaxed c-AlN and c-AlN pseudomorphically strained on c-GaN are indicated by red squares. The reflexes of the c-GaN and the c-AlGaN have the same  $q_{\parallel}$ =-1.97 Å<sup>-1</sup>. Therefore, the c-AlGaN layer is pseudomorphically strained on the c-GaN. Using Vegard's law (Equation 2.1) and the position of the c-Al<sub>x</sub>Ga<sub>1-x</sub>N and c-GaN reflexes an Al mole fraction of 36 % was established in the c-AlGaN layer.

#### 2.3.2 Atomic Force Microscopy (AFM)

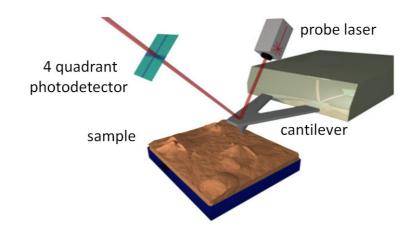

Atomic force microscopy (AFM) offers a way to get information about the surface morphology of epitaxial layers. This method allows to measure the surface roughness on an atomic scale. Figure 2.6 shows the schematic diagram of an AFM setup. AFM works by bringing an atomically sharp tip close to a surface. There is an attractive force between the tip and the surface and this force is kept at the same level throughout the experiment. As the probe tip scans back and forth over the surface, the tip will rise and fall with the different features on the surface. A laser beam is pointed to the tip and is reflected to a 4 quadrant photo detector. As the tip goes up and down the laser beam hits different parts of the sensor. With the information the sensor collects an image of the surface can be recreated.

**Figure 2.6** Schematic drawing of an AFM setup.

AFM was used to measure the root mean square (RMS) roughness of the sample's surface. The RMS in one dimension is defined as

$$RMS = \left[\frac{1}{L} \int_{0}^{L} (z(x) - \bar{z})^{2} dx\right]^{\frac{1}{2}}$$

(2.8)

where L is the scan width, z(x) the line profile and  $\bar{z}$  is the median value of the height. However, the roughness is not determined in real space, it is determined via Fourier transformation in frequency space. In frequency space the RMS is

$$RMS = \left[ \int_{f_1}^{f_2} P(f) df \right]^{\frac{1}{2}}.$$

(2.9)

P is the power spectral density which is defined as the square of the Fourier transformed line profile. For the line profile z(x) follows

$$P(f) = \frac{1}{L} \left[ \int_0^L e^{2\pi i f x} z(x) dx \right]^2.$$

(2.10)

As the topography of the scanned area is 2-dimensional and consists of discrete data points the spectral density power in two dimensions is calculated by the fast-fourier transformation (FFT) [24].

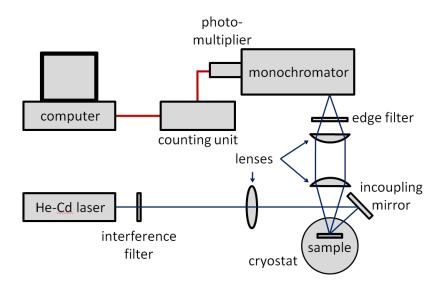

#### 2.3.3 Photoluminescence Spectroscopy (PL)

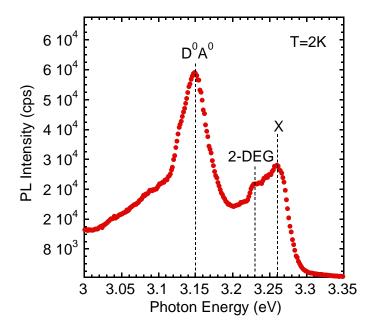

Photoluminescence (PL) spectroscopy was used to investigate the carbon defects in c-GaN:C epilayers and for optical detection of the electron channel at the c-AlGaN/GaN hetero-interface. The setup used for PL measurements is shown schematically in Figure 2.7. The luminescence was excited by a *Kimmons cw* HeCd laser with an excitation line of  $\lambda$ =325 nm ( $\hbar\omega$ =3.815 eV) and an output power of about 4 mW. The laser plasma lines were suppressed by an interference filter. The laser light was then focussed onto the mirror reflecting the light onto the sample. The PL signal was dispersed by a grating monochromator and detected using a GaAs photomultiplier and a photon counting system. A computer system was used for data collection and visualization. A He bath cryostat allowed temperature-dependent measurements in the range from T=2 K...300 K.

**Figure 2.7** Schematic diagram of the photoluminescence (PL) setup.

#### 2.4 Device Structuring

An important part of this work was the design and fabrication of HFET devices. The masks for the photolithography were drawn using a software *Solid Edge Design System* [25] and manufactured by the *Masken Lithographie & Consulting GmbH* (ML&C) [26]. Below, the HFET fabrication process by photolithography, thermal metallization, reactive ion etching (RIE) and plasma enhanced chemical vapour deposition (PECVD) is described in detail. Fundamentals of semiconductor processing technologies are given in [27].

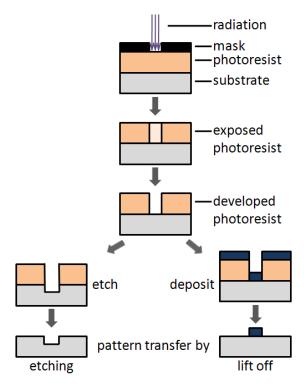

#### 2.4.1 Photolithography and Structuring

Photolithography is the most commonly used commercial technique to create lateral structures in semiconductor technology. The principle of photolithography is based on the transfer of lateral structures of a metal mask to the surface of a semiconductor. A mask for optical lithography consists of a transparent plate, called blank, covered with a patterned film of opaque material. The blank used in this work is made of fused quartz. The advantages of quartz is that it is transparent to deep UV ( $\leq$ 365 nm) and has a very low thermal expansion coefficient. The low expansion coefficient is important when the minimum feature size is less than  $\approx$ 1.5  $\mu$ m. The opaque material is typically a very thin ( $\leq$ 100 nm) film of chrome covered with an anti-reflective coating (ARC), such as chrome oxide, to suppress interferences at the wafer surface.

In order to guarantee an optimum structure transfer, the sample surface was cleaned with aceton, propanol and deionised water. The surface oxide was removed using a BOE solution (NH<sub>4</sub>F:H<sub>2</sub>O:HF=4:6:1). A positive photoresist Allresist AR-P 3510 was deposited on the sample surface using spin coating at 9000 rmp (rotations per minute) for 30 s and it was subsequently annealed at 100 °C for 2 min on a heating plate. The undiluted resist with a thickness of 2 µm was used for mesa etching with SiCl<sub>4</sub> and for large area contacts. For small sub-um structures such as gate, source and drain contacts the resist was diluted with the thinner Allresist AR 300-12. The thickness of the thinned resist layer was 400 nm. The photoresist was exposed under the photomask in contact mode using a mask aligner SÜSS KSM MJB3 for 20 s followed by the developing of the structure. The standard resist was developed in a developer/water (1:1) solution for 20 s and the thinned resist was developed in a developer/water (1:4) solution for 30 s. The developer type Allresist AR 300-35 was used. The patterned photoresist was used to structure sample layers by RIE or lift off. Finally, the resist was striped with the remover Allresist AR 300-70 at 70 °C. The substrate structuring using photolithography, etching and lift off is schematically shown in Figure 2.8.

**Figure 2.8** Transfer of a pattern to the photoresist for substrate structuring by etching and lift off.

#### 2.4.2 FET Fabrication

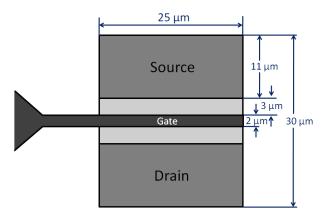

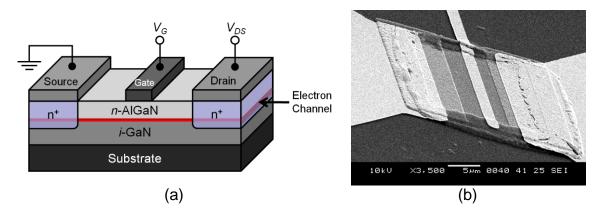

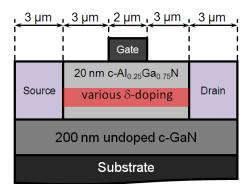

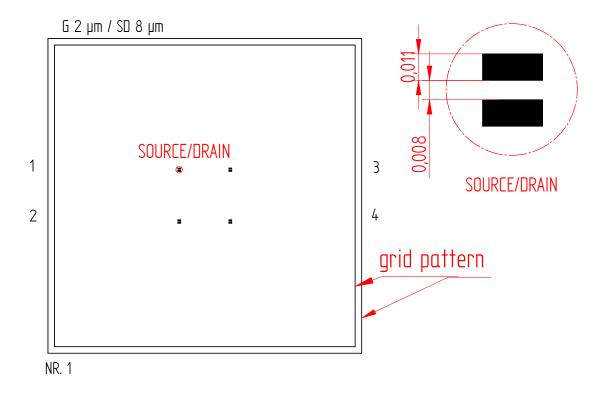

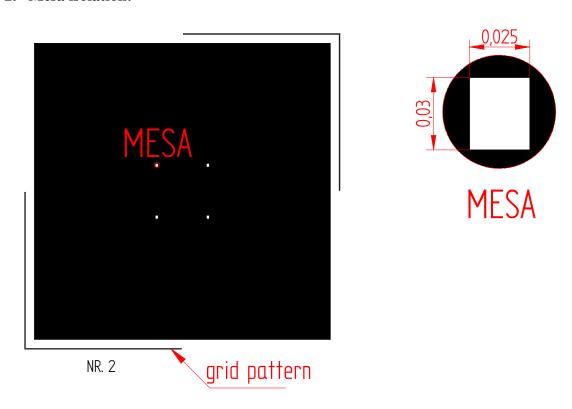

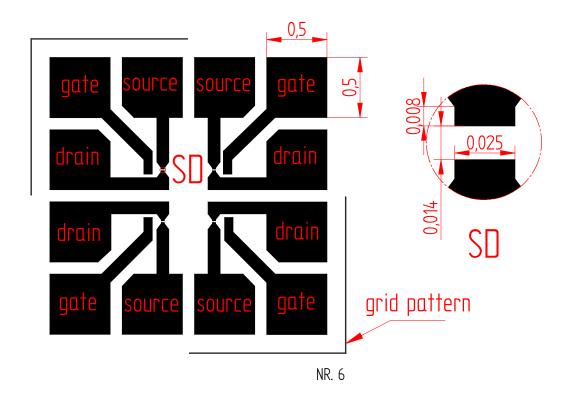

The active device has a size of  $25 \,\mu\text{m}\times30 \,\mu\text{m}$  as shown in Figure 2.9 and is a c-AlGaN/GaN mesa on free standing 3C-SiC or 3C-SiC/Si substrate. The source and drain contacts are of  $25 \,\mu\text{m}\times11 \,\mu\text{m}$  with a spacing of  $8 \,\mu\text{m}$ . The gate contact is  $2 \,\mu\text{m}$  long and is centred between source and drain. The device is surrounded by a SiO<sub>2</sub> isolation layer. Due to the small size it is not possible to contact the device directly. Therefore, large contact pads are connected with source, drain and gate which lie on the SiO<sub>2</sub> isolation layer.

**Figure 2.9** Dimensions of FET device structures fabricated using photolithography.

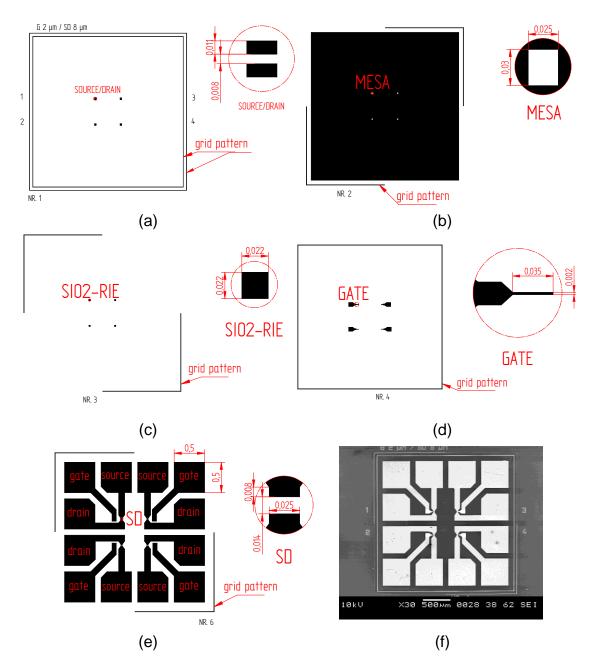

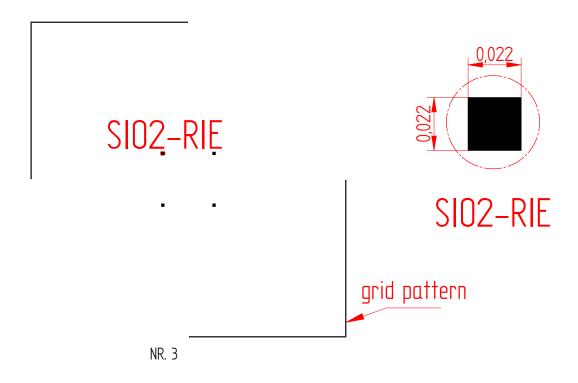

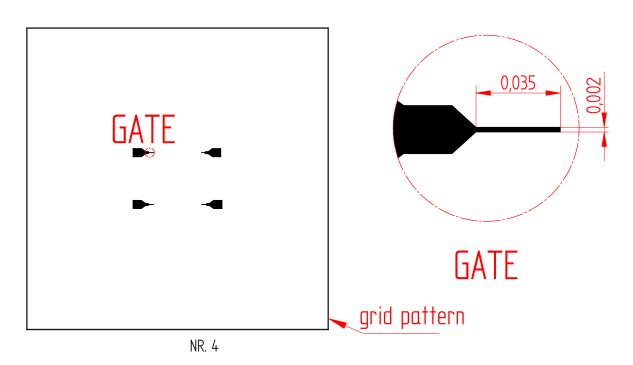

The fabrication of HFET devices is a complex process with six fabrication steps which are described below. The design of the photomasks used for the processing is shown in Figure 2.10 (a)-(e). The black parts in the design are transparent patterns in the mask and are regions on the sample used for etching or lift off process.

- **Step 1.** After the cleaning of the sample with organic solvents and BOE solution, metal stacks shown in Figure 2.10 (a) were thermally evaporated and then annealed in a rapid thermal annealing (RTA) system *ULVAC-RIKO MILA-3000* for the source and drain contacts. For this process, the thinned photoresist was used. In the same step, alignment marks (two grid patterns) were evaporated which are used as the reference for the exact positioning subsequent patterns to the first pattern.

- **Step 2.** The mesa isolation was performed by RIE with SiCl<sub>4</sub> using the mask from Figure 2.10 (b). The etching was performed in a RIE machine *OXFORD Instruments Plasmalab 80 Plus* without sample cooling at a SiCl<sub>4</sub> flux of 25 sccm, a chamber pressure of 10 mTorr, and a rf power of 300 W. The c-GaN etch rate was around 40 nm/min. The unthinned resist was used which was baked after the developing for 1 min at 100 °C on a hot plate.

- **Step 3.** A 200-300 nm thick SiO<sub>2</sub> insulation layer was deposited on the whole sample surface by PECVD with 425 sccm SiH<sub>4</sub> and 710 sccm N<sub>2</sub>O at a chamber pressure of 100 mTorr, a rf power of 20 W and a sample temperature of 300 °C in a PECVD machine *OXFORD Instruments Plasmalab 80 Plus*. The deposition rate was about 80 nm/min.

- **Step 4.** The SiO<sub>2</sub> area over the FET device was etched by RIE with 10.5 sccm Ar and 10.5 sccm CHF<sub>3</sub> at a chamber pressure of 35 mTorr, a rf power of 150 W without sample heating in a RIE Machine *Plasma Technology Plasmalab U80P*. The etch rate was about 35 nm/min. For this process the thinned photoresist and the mask from Figure 2.10 (c) was used.

- **Step 5.** The gate was evaporated using the thinned resist and the mask shown in Figure 2.10 (d). This contact was thermally annealed at 200 °C for 10 min on a heating plate.

- **Step 6.** Finally, the mask from Figure 2.10 (e) was used to evaporate the contact pads. The unthinned photoresist is the most suitable for this process. The large metal pads contact the source and drain stacks and the gate finger and they lie on the  $SiO_2$  isolation layer.

- Figure 2.10 (f) shows a SEM diagraph of a fabricated sample structure with four identical FET devices. An enlarged SEM diagraph of a single FET device can be seen in Figure 5.4 (b).

**Figure 2.10** (a)-(e) Design of the photomasks used for fabrication of c-AlGaN/GaN HFETs. (a) Mask for source and drain contacts. (b) Mask for mesa etching. (c) Mask for opening of the devices after deposition of  $SiO_2$  isolation layer. (d) Mask for gate contacts. (e) Mask for contact pads. The dimensions are given in mm. (f) SEM diagraph of a fabricated sample structure with four HFET devices.

#### 2.5 Electrical Characterization Methods

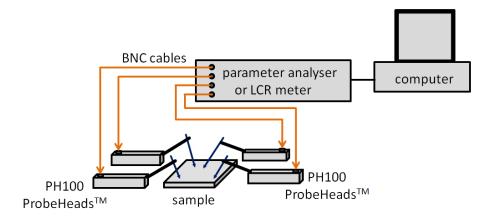

For the electrical characterization of samples, current-voltage (IV) and capacitance-voltage (CV) measurements were done. For IV measurements an *Agilent Precision Semiconductor Parameter Analyzer 4156C* was used. CV measurements were performed by an *Agilent Precision LCR Meter E4980A*.

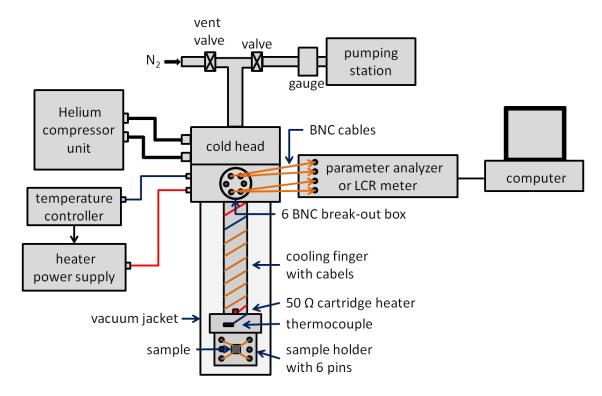

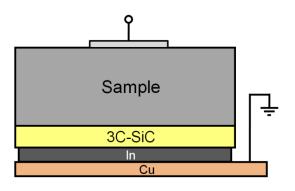

For temperature-dependent measurements a *Janis SHI* closed cycle refrigerator (CCR) system was used. A schematic drawing of the measurement setup for temperature-dependent IV and CV measurements is shown in Figure 2.11. This system can be used to perform electrical measurements between 7 K and 400 K. For cooling, a closed loop of helium gas is compressed and expanded, based on the Gifford-McMahon (G-M) thermodynamic cycle. A detailed description of the G-M cycle can be found in [28], [29]. The cold head is separated from the compressor by a couple of flexible high pressure tubes which transport the compressed helium into and out of the cold head. This enables easy handling of the cold head which weighs about 8 kg, while the 65 kg compressor is firmly positioned nearby. The cold head expands the helium gas to cool the sample. It is connected with a cooling finger and a sample mount. A heater and a thermocouple are installed on the cold finger and are used to precisely control the sample temperature by a *LakeShore 331* temperature controller. While the cold finger is cooled permanently, the heating power of the heater is varied according to the set temperature. The cooling finger is surrounded by a radiation shield (not shown here) and a vacuum jacket. To evacuate the

**Figure 2.11** Schematic drawing of the measurement setup for temperature dependent IV and CV measurements.

**Figure 2.12** Schematic drawing of the measurement setup for room temperature IV and CV measurements.

sample space a pumping station *PFEIFFER Vacuum TSH 071E* is used. The vacuum is controlled by a compact full range gauge *PFEIFFER Vacuum PKR 251*. For the venting a nitrogen supply is used.

The sample is connected with the sample holder by brazing with indium. Six pins on the sample holder allow to connect six contacts of the sample with six BNC connectors in the BNC break-out box which are connected via BNC cables with the measurement instruments.

For room temperature measurements the samples were contacted using a *SüssMicroTec PM5* manual probe system schematically shown in Figure 2.12. In this setup *SüssMicroTec PH100 ProbeHeads* with tungsten carbide probe needles with a tip radius of 7 µm were used.

All electrical measurements were performed in darkness. Measurement data were stored in a computer.

#### 2.6 Simulation Calculations

To understand the electrical measurement results of our cubic AlGaN/GaN heterolayers and HFET devices, model calculations of their energy-band diagrams and output/transfer characteristics were performed using a 1D-Poisson solver [30], [31] and ATLAS device simulation software [32], respectively. The simulation programs are described in Appendix F.

The material parameters of c-GaN and c-AlN used for calculations are given in Table 2.2. Parameters of ternary  $c-Al_xGa_{1-x}N$  were calculated by Vegard's law (Equation 2.1). Al mole fraction, thickness und donor concentration of the layers was varied according to the investigated samples. Therefore, more parameters are given in those sections describing calculation results.

**Table 2.2** Material parameter of c-GaN and c-AlN used for calculation of energy-band diagrams.

| Parameter                | c-GaN                             | c-AIN                             |  |

|--------------------------|-----------------------------------|-----------------------------------|--|

| Energy Gap               | 3.2 eV                            | 5.05 eV                           |  |

| Conduction Band Offset   |                                   | 1.33 eV                           |  |

| rel. Dielectric Constant | 8.9                               | 8.4                               |  |

| Electron Mobility        | $100 \text{ cm}^2/\text{Vs}$      | $100 \text{ cm}^2/\text{Vs}$      |  |

| Polarization             | $1 \times 10^{-8} \text{ C/cm}^2$ | $1 \times 10^{-8} \text{ C/cm}^2$ |  |

# 3 Principals of Hetero-Junction Field-Effect Transistors

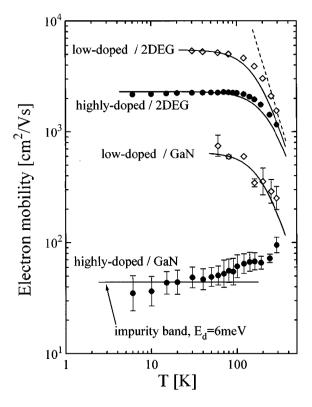

The hetero-junction field-effect transistor (HFET) is also known as the modulation-doped field-effect transistor (MODFET), high-electron-mobility transistor (HEMT), two-dimensional electron-gas field-effect transistor (TEGFET), and selectively doped hetero-junction transistor (SDHT) [33], [34]. The unique feature of the HFET is the hetero-structure, in which the wide-energy-gap material is doped and carriers diffuse to the undoped narrow-band gap layer at which hetero-interface a carrier channel is formed. The net result of this modulation doping is that the channel carriers in the undoped hetero-interface are spatially separated from the doped region and have high low-temperature mobilities because there is no impurity scattering. This phenomenon is demonstrated in Figure 3.1 where mobilities in the hexagonal bulk GaN are compared to those in the electron channel at the hexagonal  $Al_{0.15}Ga_{0.85}N/GaN$  interface.

**Figure 3.1** Temperature dependence of electron mobility for the 2-DEG in hexagonal AlGaN/GaN and the hexagonal GaN bulk layer with two different doping concentrations [35].

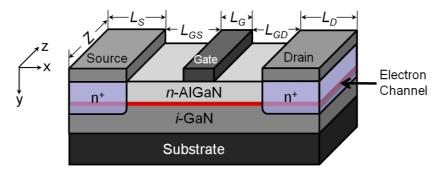

**Figure 3.2** Typical structure of an AlGaN/GaN HFET.

#### 3.1 Basic Device Structure

A basic HFET structure based on an AlGaN/GaN system is shown in Figure 3.2. It can be seen here that the barrier layer AlGaN under the gate is doped, while the GaN buffer layer is undoped. The doped barrier layer is typically around 30 nm thick. Very often, a  $\delta$ -doped charge sheet is used within the barrier layer and placed close to the channel interface instead of uniform doping. The source and drain contacts are ohmic while the gate is a Schottky barrier. Sometimes, a top layer of  $n^+$ -GaN on AlGaN is used for better source and drain ohmic contacts. The deeper  $n^+$ -regions of source/drain are formed either by ion implantation or introduced during the alloying step to contact the electron channel. For low values of drain-to-source bias, a current flows from drain to source through the electron channel. The carrier sheet density and consequently the conductivity of the channel are controlled by the gate bias. Increasing of the positive bias applied to the gate increases the depth of the potential well at the AlGaN/GaN interface. This results in enhanced sheet carrier density of the electron channel and, therefore, increased current conduction. Increasing of the negative gate bias decreases the depth of the electron channel and the sheet carrier density decreases thereby lowering the channel conductivity.

The most important dimension that characterises the HFET physical structure is the gate length  $L_G$ . This dimension determines the maximum frequency limits for HFET devices. Typical gate lengths are in the 0.1..2  $\mu$ m range. The gate width Z is another physical device dimension that is of primary importance to the determination of device behaviour. The device current is directly proportional to the gate width because the cross-section area available for the channel current is proportional to Z. For low-noise, low-current applications relatively small-gate-width devices are utilized. In contrast, large-gate-width devices are typically used for power applications. Other characteristic dimensions are the gate-to-source  $L_{GS}$  and gate-to-drain  $L_{GD}$  spacing and the drain  $L_{D}$  and source  $L_{S}$  length.

The actual layout of the HFET devices is more complex than implied by Figure 3.2. Connections must be made to all three terminals – source, gate and drain. These connections are large-area metal contact pads for probes or bond wires. The drawing of masks to use for the fabrication of HFET devices is shown in Chapter 2.4.2 and in Appendix E.

#### 3.2 Current-Voltage Characteristics

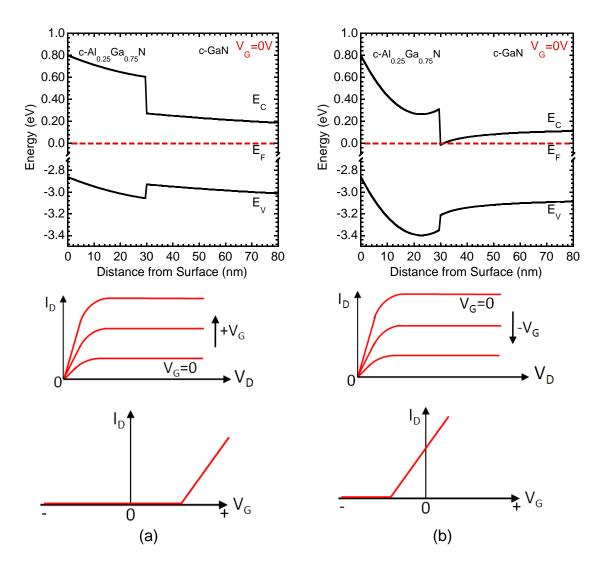

In this work, n-channel devices of cubic AlGaN/GaN with the channel formed by electrons were investigated. There are two different types of FETs dependent on the state of the transistor with zero gate bias. Their energy-band diagrams at equilibrium (calculated for a cubic Al<sub>0.25</sub>Ga<sub>0.75</sub>N/GaN hetero-layer) and schematic output and transfer characteristics are compared in Figure 3.3. FETs are called enhancement-mode, or normally-off if at zero gate bias the channel is depleted and the Fermi level  $E_F$  is below the conduction band edge  $E_C$ . The conductance of the electron channel is very low and a positive gate voltage must be applied to fill the channel with carriers. The counterpart is called depletion-mode, or normally-on, if the channel is conductive with zero gate bias. The Fermi level  $E_F$  crosses the conduction band edge at the AlGaN/GaN hetero-interface. Negative gate voltage must be applied to turn the transistor off.

**Figure 3.3** Band diagrams of c-AlGaN/GaN hetero-structures and schematic output and transfer characteristics of *n*-channel (a) normally-*off* and (b) normally-*on* HFETs.

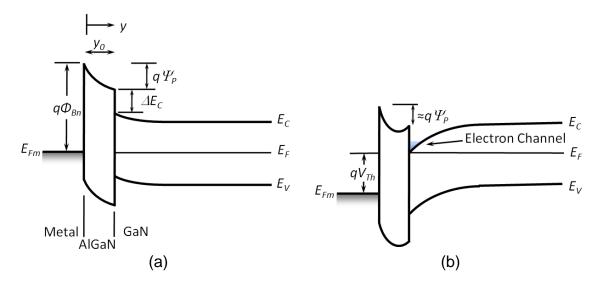

**Figure 3.4** Room temperature energy-band diagrams for a normally-off HFET at (a) equilibrium and (b) onset of threshold.

Based on the principle of modulation doping, the impurities within the barrier layer are completely ionized and carriers depleted away. Referring to the energy-band diagrams of Figure 3.4, the potential variation  $\psi_P$  within the depleted region is given by

$$\psi_P = \frac{q}{\varepsilon_S} \int_0^{y_0} N_D(y) y \, dy \tag{3.1}$$

for a general doping profile. For uniform doping, this built-in potential becomes

$$\psi_P = \frac{qN_D y_0^2}{2\varepsilon_S}. (3.2)$$

An important parameter for HFETs is the threshold voltage  $V_{th}$ , the gate bias at which the channel starts to form between the source and the drain. From Figure 3.4 (b), a first-order approximation shows that this occurs when the Fermi level  $E_F$  at the GaN surface coincides with the conduction band edge  $E_C$ . This corresponds to the bias condition of:

$$V_{th} \approx \phi_{Bn} - \psi_P - \frac{\Delta E_C}{q}. \tag{3.3}$$

It can be seen here that by choosing the doping profile and barrier height  $\phi_{Bn}$ ,  $V_{th}$  can be varied between positive and negative values. The example shown in Figure 3.4 has a positive  $V_{th}$ , and the transistor is called a normally-off device, which was the main objective of this work.

With a gate voltage larger than the threshold voltage, the charge sheet in the channel induced by the gate is capacitively coupled and is given by

$$Q_n = C_0(V_G - V_{th}), (3.4)$$

where

$$C_0 = \frac{\varepsilon_S}{y_0 + \Delta y} \tag{3.5}$$

and  $\Delta y$  is the channel thickness of the electron channel estimated to be around 8-10 nm. When a drain bias is applied, the channel has a variable potential with distance and its value with respect to the source is designated as  $\Delta \psi(x)$  (x is the direction from drain to source). It varies along the channel from 0 at the source to  $V_D$  at the drain. The channel charge  $Q_n(x)$  as a function of position becomes

$$Q_n(x) = C_0[V_G - V_{th} - \Delta \psi(x)]. \tag{3.6}$$

The channel current at any location is given by

$$I_D(x) = ZQ_n(x)v(x). (3.7)$$

Since the current is constant throughout the channel, integrating the above equation from source to drain (assuming  $L_{GS} = L_{GD} = 0$ ) gives

$$I_{D} = \frac{Z}{L} \int_{0}^{L} Q_{n}(x) v(x) dx.$$

(3.8)

With constant mobility, the drift velocity is simply given by

$$v(x) = \mu_n \mathcal{E}(x) = \mu_n \frac{d\Delta\psi}{dx}.$$

(3.9)

Substituting Equations (3.6) and (3.9) into Equation (3.8) we obtain after an integration

$$I_D = \frac{Z\mu_n C_0}{L} \left[ (V_G - V_{th})V_D - \frac{V_D^2}{2} \right]. \tag{3.10}$$

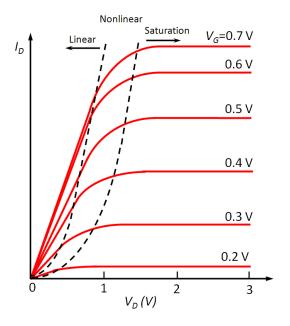

The output characteristics for a normally-off HFET are shown in Figure 3.5. In the linear region where  $V_D \ll (V_G - V_{th})$ , Equation (3.10) is reduced to an ohmic relationship

$$I_{D,lin} = \frac{Z\mu_n C_0 (V_G - V_{th}) V_D}{L}.$$

(3.11)

At  $V_{D,sat} = V_G - V_{th}$ ,  $Q_n(L)$  at the drain is reduced to zero (Equation (3.6)) corresponding to the pinch-off condition, and the current saturates with  $V_D$ . This gives a saturation drain current of

**Figure 3.5** Output characteristics of a normally-off HFET.

$$I_{D,sat} = \frac{Z\mu_n C_0}{2L} (V_G - V_{th})^2.$$

(3.12)

From the above equation, the transconductance  $g_m$  can be obtained:

$$g_{m\equiv} \frac{dI_{D,sat}}{dV_G} = \frac{Z\mu_n C_0 (V_G - V_{th})}{L}.$$

(3.13)

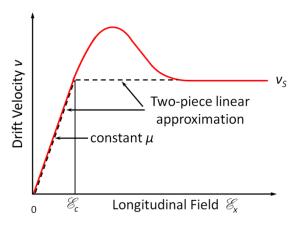

As the technology advances and pushes for device performance and density, the channel length gets shorter and shorter. The internal longitudinal field  $\mathscr{E}_x$  in the channel also increases as a result. Figure 3.6 shows the electron velocity-field  $(v-\mathscr{E})$  relationship where a two-piece linear approximation is also shown with a critical field  $\mathscr{E}_c$ . For low fields, the mobility is constant. This low-field mobility is used for the long-channel characteristics described before. In the extreme case of a very high field, the velocity approaches a value, saturation velocity  $v_s$ . In state-of-the art devices, the current becomes saturated with  $V_D$  before the pinch-off condition occurs, due to the fact that the carrier drift

**Figure 3.6** *v*- & relationship for the channel charge. Transfer/electron effect is shown for materials such as GaN. Two/piece linear approximation is indicated.

velocity is no longer linearly proportional to the electric field. In other words, in high fields the mobility  $\mu$ , which is defined as  $\mu = v/\mathscr{E}$  becomes field-dependent.

For devices with high mobilities such as HFETs this phenomenon is more severe. In case of a field dependent velocity  $I_{D,sat}$  and  $V_{D,sat}$  are given by

$$I_{D,sat} = \frac{ZC_0\mu_n}{L} \left(V_G - V_{th} - \frac{V_{D,sat}}{2}\right) V_{D,sat}, \tag{3.14} \label{eq:ID_sat}$$

$$V_{D,sat} = L \mathcal{E}_c + (V_G - V_{th}) - \sqrt{(L \mathcal{E}_c)^2 + (V_G - V_{th})^2}.$$

(3.15)

# 4 Separation between Substrate and HFET Device

A semi-insulating substrate or a GaN buffer layer is the fundament for many nitride-based device structures. Lateral conduction devices, such as the AlGaN/GaN HFET, require semi-insulating material beneath the device structure. A conductive buffer layer will not only lead to high leakage current and therefore poor pinch-off characteristics, but will also degrade the rf performance of the HFETs at high frequencies. Moreover, for electrical characterization test structures, e.g. Hall effect measurement or transmission line measurement (TLM) structures, the tested layer has to be insulated from the underlying conduction path. In this chapter, the necessity for isolation between the FET device and the substrate will be discussed first. Then, three possible insulating buffers for cubic nitrides will be introduced, namely the semi-insulating carbonised silicon 3C-SiC/Si, the Ar<sup>+</sup> implanted free standing 3C-SiC, and the carbon doping of cubic GaN using a CBr<sub>4</sub> source.

# 4.1 Model Calculations of Cubic AlGaN/GaN FETs on Different Substrates

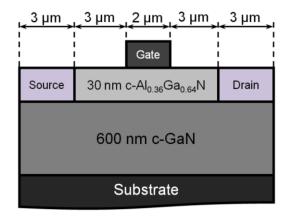

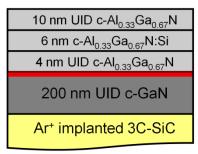

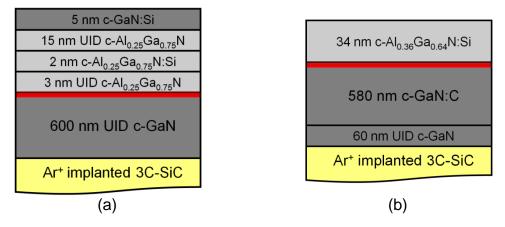

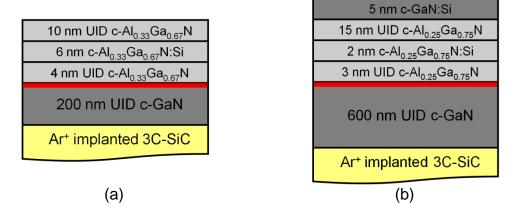

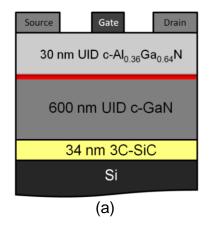

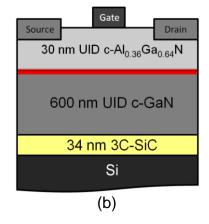

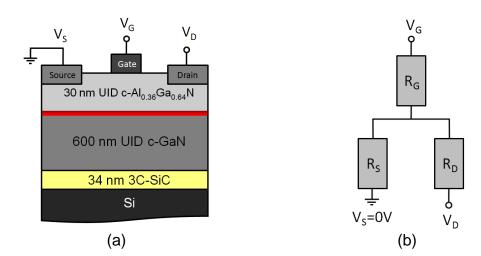

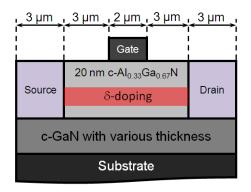

To clarify the necessity for buffer insulation, model calculations of cubic AlGaN/GaN FET devices on different substrates were performed by R. Granzner at the TU Ilmenau using the ATLAS simulation program. The hetero-structure from Figure 4.1 was used for the calculations. It was assumed that the ohmic source and drain contact were deposited on GaN contacting directly the electron channel. The Schottky gate contact was localised on top of c-AlGaN. Analogous to the real devices the gate length was 2  $\mu$ m and the gate-to-source and the gate-to-drain space was 3  $\mu$ m. For the calculations 30 nm cubic AlGaN with 36% Al mole fraction and a donor concentration of  $N_D(\text{AlGaN})=5\times10^{17}$  cm<sup>-3</sup> on 600 nm cubic GaN with a donor concentration of  $N_D(\text{GaN})=5\times10^{16}$  cm<sup>-3</sup> were used.

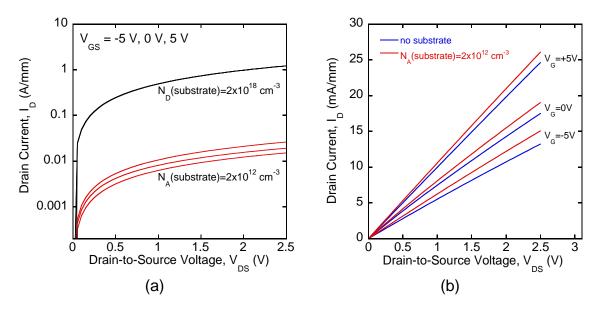

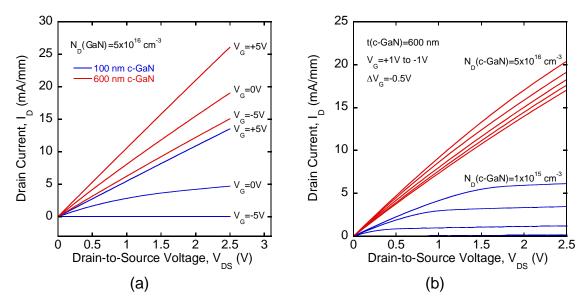

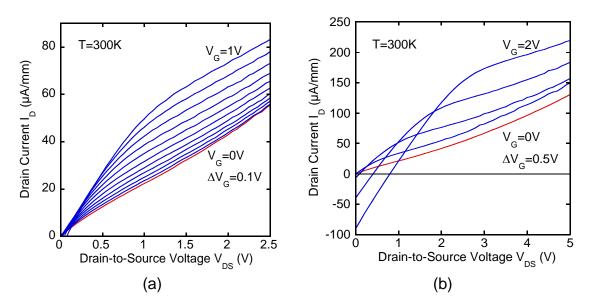

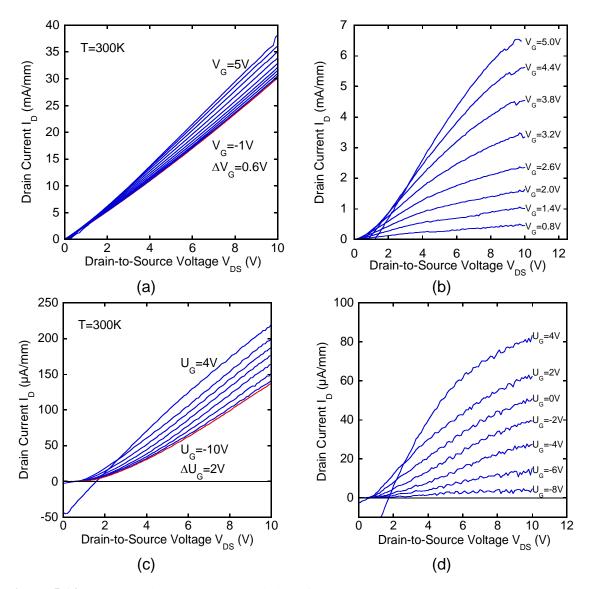

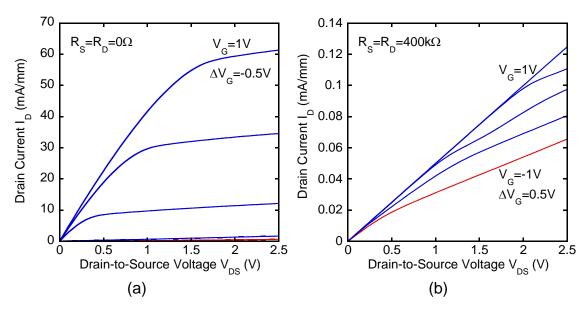

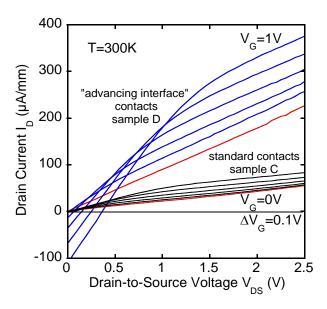

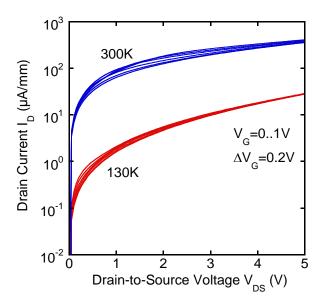

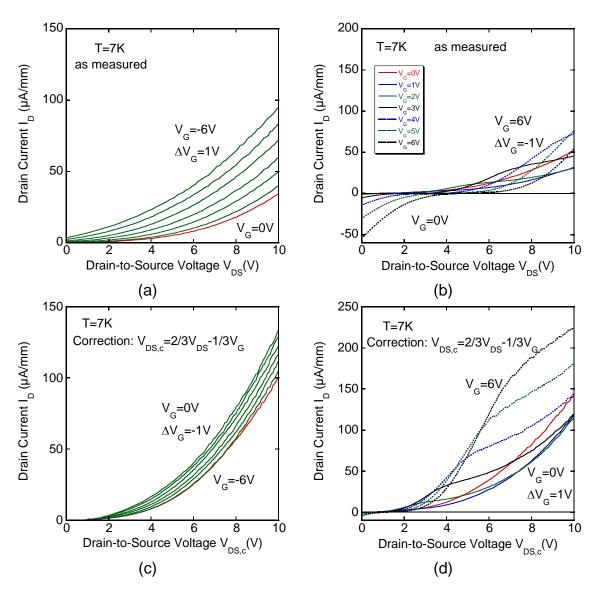

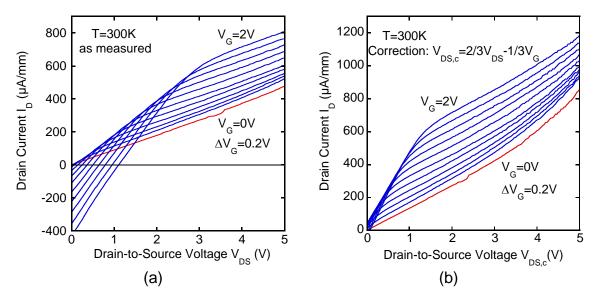

Figure 4.2 (a) shows the calculated  $I_D$ - $V_{DS}$  characteristics of HFET on two different substrates with a donor concentration of  $N_D$ =2×10<sup>18</sup> cm<sup>-3</sup> (black curves) and an acceptor concentration of  $N_A$ =2×10<sup>12</sup> cm<sup>-3</sup> (red curves) for gate voltages of  $V_G$ =-5 V, 0 V and 5 V. The drain-to-source current through the device with the highly doped substrate is two orders of magnitude higher than through the high-insulating substrate. Moreover, due to the high shunt current the field-effect is not observable. These calculations demontrate, that a semi-insulating substrate is essential for the fabrication of FETs. Calculated  $I_D$ - $V_{DS}$

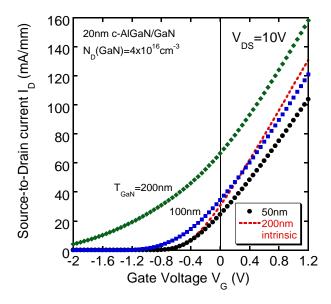

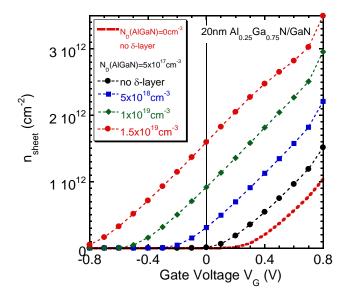

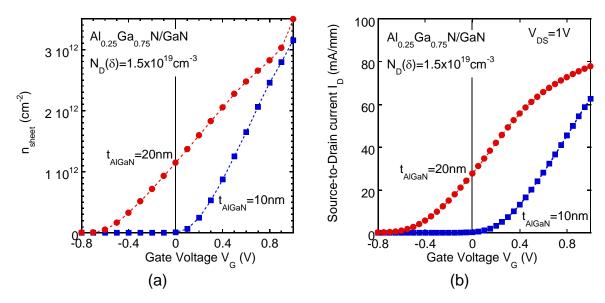

**Figure 4.1** Schematic cross-section of a FET structure for model calculations.

characteristics of the same device on a substrate with  $N_A$ =2×10<sup>12</sup> cm<sup>-3</sup> and without substrate are shown in Figure 4.2 (b). In both cases, a current in the same order of magnitude as the calculated field-effect is available at a gate voltage of  $V_G$ =-5 V. This shunt current is caused by the leakage through the 600 nm thick c-GaN buffer layer with a high donor density of  $N_D$ (GaN)=5×10<sup>16</sup> cm<sup>-3</sup>. This is pointed out by the calculation of  $I_D$ - $V_{DS}$  curves for devices on c-GaN with two different thicknesses of 100 nm and 600 nm and the same donor concentration of  $N_D$ (GaN)=5×10<sup>16</sup> cm<sup>-3</sup> shown in Figure 4.3 (a). The device with 100 nm c-GaN thickness is completely depleted at  $V_G$ =-5 V whereas the device with 600 nm c-GaN is conductive under the same conditions. Therefore, since the residual background carrier concentration of c-GaN is about 5×10<sup>16</sup> cm<sup>-3</sup>, the c-GaN buffer layer must not be thicker than 100 nm to avoid the parasitic shunt current.

**Figure 4.2** Simulated static output characteristics of the FET from Figure 4.1 for different substrate conductivity. The estimated donor density is  $N_D(\text{c-GaN})=5\times10^{16}\,\text{cm}^{-3}$  and  $N_D(\text{c-AlGaN})=5\times10^{17}\,\text{cm}^{-3}$ . (a) Comparison of FET on 3-SiC with  $N_D=2\times10^{18}\,\text{cm}^{-3}$  (black curves) and  $N_A=2\times10^{12}\,\text{cm}^{-3}$  (red curves). (b) Comparison of FET on 3-SiC with  $N_A=2\times10^{12}\,\text{cm}^{-3}$  (red curves) and FET without substrate (blue curves).

Figure 4.3 Simulated static output characteristics of the FET from Figure 4.1 for (a) 100 nm (blue curves) and 600 nm (red curves) GaN buffer layer with the same donor density of  $N_D = 5 \times 10^{16}$  cm<sup>-3</sup> and (b) for different donor densities of  $N_D = 5 \times 10^{16}$  cm<sup>-3</sup> (red curves) and  $N_D = 1 \times 10^{15}$  cm<sup>-3</sup> (blue curves) and the same c-GaN thickness of t = 600 mm.

The effect of the c-GaN doping on the shunt current is depicted in Figure 4.3 (b). The diagram shows calculated  $I_D$ - $V_{DS}$  characteristics of two HFETs with a GaN donor concentration of  $N_D(\text{GaN})=5\times10^{16}~\text{cm}^{-3}$  (red curves) and  $N_D=1\times10^{15}~\text{cm}^{-3}$  (blue curves) for  $V_G$ =-1V..1V. The GaN layer thickness was 600 nm for both samples. The device with  $N_D(\text{GaN})=5\times10^{16}~\text{cm}^{-3}$  GaN layer exhibits a shunt current which is five times higher than the calculated field-effect. The device with  $N_D$ =1×10<sup>15</sup> cm<sup>-3</sup> features no shunt current and is completely depleted already at  $V_G$ =-0.5 V. In comparison with this HFET the same device on 100 nm GaN with  $N_D(\text{GaN})=5\times10^{16}~\text{cm}^{-3}$  is depleted at a higher negative gate voltage of  $V_G$ =-5 V. This means that if the GaN buffer layer is conductive, the device is a combination of HFET and MESFET. After the electron channel at the AlGaN/GaN interface is depleted, negative gate voltages are necessary to deplete the GaN buffer layer. Therefore, the device shows normally-on behaviour.

In summary, for an efficient HFET a high resistant substrate is necessary. To avoid buffer leakage and to achieve a device with normally-off characteristics, a thin GaN buffer layer with a thickness of t<200 nm and a carrier concentration of n(GaN)<1×10<sup>16</sup> cm<sup>-3</sup> is an important precondition. In the following sections various alternatives for substrate insulation for epitaxy of cubic GaN and carbon doping of cubic GaN using a CBr<sub>4</sub> source as potential for the fabrication of compensated low-conductive epilayers will be discussed.

**Figure 4.4** RHEED pattern in <110> direction at 720 °C of (a) carbonised Si (001) and (b) 600 nm thick cubic GaN on carbonised Si (001).

#### **4.2** *Carbonised Si* (001)

One of the suitable substrates for epitaxy of cubic GaN is the so-called carbonised silicon (3C-SiC/Si) [36]. The 3C-SiC/Si substrates were fabricated by Dr. J. Pezoldt at the TU Ilmenau. For this substrate semi-insulating Si (001) with a resistivity of  $\rho$ =6 k $\Omega$ ·cm was used. 34 nm 3C-SiC was deposited on the substrate using UHV-CVD with the gases SiH<sub>4</sub>:C<sub>2</sub>H<sub>4</sub>:H<sub>2</sub>=1.6:1.0:10 sccm at substrate temperature of 1050 °C. The deposition time was 60 min. The carrier concentration of the 3C-SiC/Si substrate was p=7×10<sup>11</sup> cm<sup>-3</sup> measured by Hall effect. The substrate resistivity was  $\rho$ =10 k $\Omega$ ·cm measured by the four-point-method. One disadvantage of carbonised silicon is a high dislocation density of 3C-SiC due to a mismatch of 16.8 % between 3C-SiC and Si. The RMS roughness of the used 3C-SiC/Si was 1.6 nm.

Figure 4.4 shows the RHEED pattern of (a) 3C-SiC/Si and (b) 600 nm c-GaN grown on 3C-SiC/Si at 720 °C measured in <110> direction (sample 1747). The RHEED pattern of the substrate shows diffuse streaks overlaid with spotty reflexes. The RHEED pattern of the c-GaN shows sharper streaks and a  $(2\times2)$ -reconstruction.

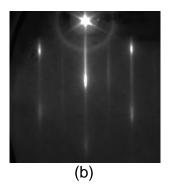

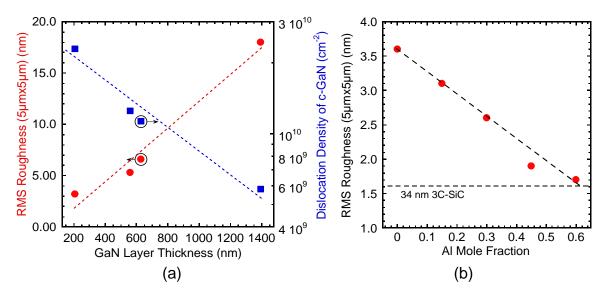

The RMS roughness of the 3C-SiC/Si was 1.6 nm and of the 600 nm GaN layer on the substrate it was 6 nm. The normalised high-resolution X-ray diffraction rocking curve of the symmetric (002) reflex of 3C-SiC/Si and 600 nm thick c-GaN is depicted in Figure 4.5 (a). The full width at half maximum (FWHM) of the ω-scans was 120 arcmin and 38 arcmin for the 3C-SiC and c-GaN, respectively. Since the FWHM is proportional to the dislocation density of a layer, the c-GaN epitaxy starts on the highly dislocation-rich 3C-SiC surface and the defects are released during the c-GaN growth. To investigate the hexagonal inclusions in c-GaN, the reciprocal space map (RSM) of the (002) reflex of c-GaN was measured as shown in Figure 4.5 (b). The hexagonal inclusions of this sample measured from the intensity ratio of the hexagonal (10-11) to the cubic (002) reflex were only 1 %.

Overall, the carbonised Si is a suitable semi-insulating substrate for cubic GaN epitaxy.

**Figure 4.5** (a) Normalized high-resolution X-ray diffraction  $\omega$ -scan of the symmetric (002) reflex of the 3C-SiC/Si and the 600 nm thick cubic GaN layer on the substrate. (b) Reciprocal space map of the (002) reflex of the 600 nm thick cubic GaN epilayer grown on 3C-SiC/Si (001).

#### 4.3 Ar+ Implanted 3C-SiC (001)

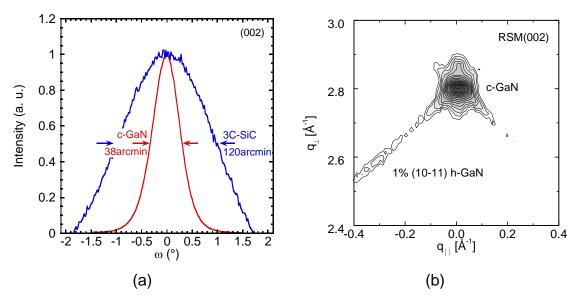

The most promising method for substrate insulation is up to now the Ar<sup>+</sup> implantation of 3C-SiC (001). For this process free standing 3C-SiC with a carrier concentration of  $n=2\times10^{18}$  cm<sup>-3</sup> was used and a three-fold energy implantation with Ar<sup>+</sup> ions at doses of  $6\times10^{14}$  cm<sup>-2</sup> at 160 keV,  $2.4\times10^{14}$  cm<sup>-2</sup> at 80 keV and  $1.2\times10^{14}$  cm<sup>-2</sup> at 40 keV were performed by Prof. Dr. J.K.N. Lindner at the University of Augsburg. The idea was to induce a low-mobility insulating damage layer near the 3C-SiC surface.

Figure 4.6 (a) and (b) shows calculated  $Ar^+$  density profiles in 3C-SiC and the calculated nuclear recoil energy profiles for the three implantation energies, respectively. The calculations were done using the simulation program SRIM2003.26 [37]. The total maximum  $Ar^+$  density of  $N_{Ar}=7\times10^{19}$  cm<sup>-3</sup> is estimated to be between 30 and 130 nm below the surface. The amorphisation of a crystalline structure occurs around the maximum of the recoil energy profile curve. According to the calculation the strongest lattice damage is expected between 10 nm and 100 nm under the substrate surface.

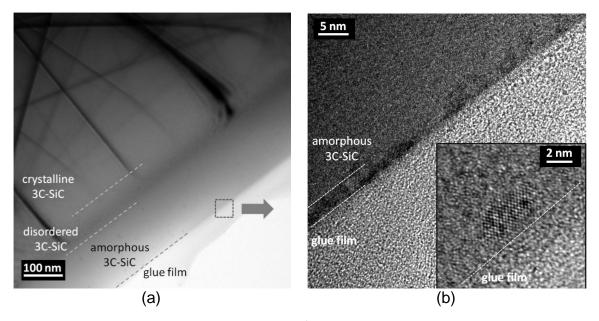

Microstructures of the irradiated SiC were examined using cross-sectional transmission electron microscopy (TEM). The measurements were performed by Prof. Dr. J.K.N. Lindner at the University of Augsburg. The general cross-sectional view of the sample is shown in Figure 4.7 (a) where the crystalline, disordered and amorphised SiC layers are exhibited. The dotted lines are drawn to guide the eye. The thickness of the amorphised SiC layer is about 130 nm and correlates with the simulated data. Under Ar<sup>+</sup> implantation conditions a few top atomic layers at the surface of about 5 nm thickness are still crystalline as distinguishable in a high resolution TEM image in Figure 4.7 (b). A similar

**Figure 4.6** Calculated (a) Ar<sup>+</sup> density profiles and (b) nuclear recoil energy profiles of Ar<sup>+</sup> ions implanted at 40 keV, 80 keV and 160 keV.

layer structure was demonstrated of 6H-SiC after Au<sup>+</sup> ion implantation in [38]. However, in our samples the crystalline region at the substrate surface is not continuous and consists of crystalline 3C-SiC domains surrounded by amorphous SiC as depicted in the inset of Figure 4.7 (b).

**Figure 4.7** Cross-sectional TEM images of Ar<sup>+</sup> implanted 3C-SiC: (a) a general view at a low magnification, (b) shows a near surface region at a larger magnification; the inset in (b) shows a crystalline 3C-SiC domain in an amorphous SiC layer at the substrate surface.

**Figure 4.8** FFT image of (a) the inset in Figure 4.7 and (b) a mono crystalline 3C-SiC bulk substrate.

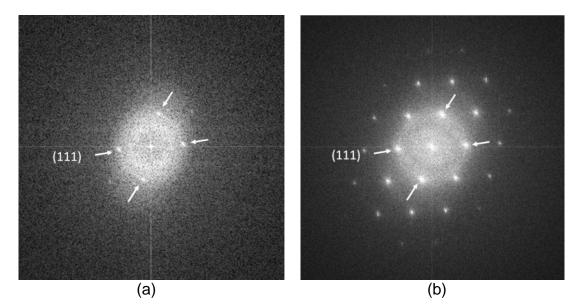

To verify the crystal orientation fast Fourier transformation (FFT) representing reflexes of the reciprocal crystal was performed of the inset of Figure 4.7 (b) and of a TEM image of a crystalline bulk 3C-SiC shown in Figure 4.8 (a) and (b), respectively. Four (111) reflexes are visible in the FFT image of the crystalline cluster at the substrate surface which are identical with the (111) reflexes of the 3C-SiC bulk material. This measurement shows that the thin crystalline 3C-SiC cluster layer exhibits the same crystal orientation as the bulk material and it has maintained its original orientation.

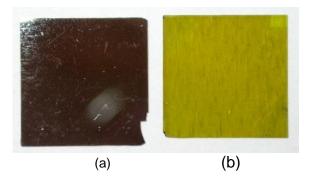

The formation of the amorphous SiC induces a colour change of the 3C-SiC. Free standing 3C-SiC is transparent yellow. After Ar<sup>+</sup> implantation the colour becomes opaque black as shown in Figure 4.9 (a) caused by the amorphous SiC and potentially by carbon clusters [39]. After thermal annealing at 800 °C for 30 min the SiC substrate becomes transparent as shown in Figure 4.9 (b), but it is still darker than the primary 3C-SiC.

**Figure 4.9** Ar<sup>+</sup> implanted 3C-SiC substrate (a) untreated and (b) after thermal annealing at 800 °C for 30 min.

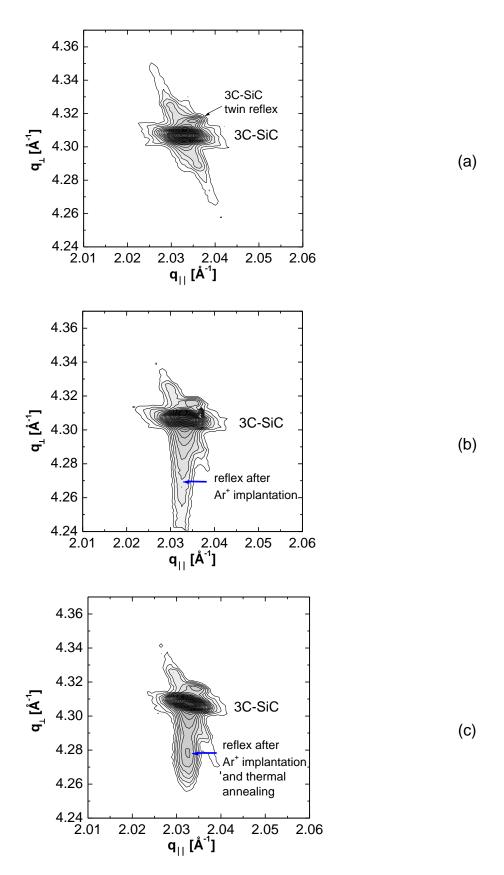

The changes of the crystalline structure of the 3C-SiC substrate were controlled by high resolution X-ray diffraction (HRXRD). RSMs around the cubic (113) reflex of free standing 3C-SiC before  $Ar^+$  implantation, after  $Ar^+$  implantation and after  $Ar^+$  implantation and subsequent thermal annealing are displayed in Figure 4.10 (a), (b) and (c), respectively. The RSM (113) of the untreated substrate features only a reflex of 3C-SiC (and a 3C-SiC twin reflex which is not typical and is observed only in wafer Nr. SFE14AT). After  $Ar^+$  implantation a broadening below the 3C-SiC reflex in  $q_\perp$  direction is observed. It can be explained by an expansion gradient of the 3C-SiC lattice constant in the disordered region due to additional Ar atoms. In addition it is known that amorphous SiC has an atomic density which is reduced by 20-30 % with respect to the crystalline state. One may therefore assume that damaged SiC exhibits an increased lattice constant.

Previous to c-GaN MBE the substrates are deoxidized at about 800 °C. Therefore, the Ar<sup>+</sup> implanted 3C-SiC was thermally annealed at 800 °C for 30 min. After the annealing process the broadening of the 3C-SiC reflex in the RSM has the shape of a separate reflex with a noticeable small FWHM. This is an evidence for a recrystallization of amorphous SiC by solid phase epitaxy studied in [40], [41] for 6H-SiC. For hexagonal SiC it was found that the recrystallization temperature varies between 750 °C and 1700 °C depending on different doses, ion species and the implantation temperature [42]. The volume increase of the 3C-SiC crystal after Ar<sup>+</sup> implantation and subsequent recrystallisation is 0.67 % calculated from the reflex positions of the both (113) 3C-SiC reflexes in Figure 4.10 (c). Thereafter, the lattice constant of the Ar<sup>+</sup> implanted 3C-SiC increases for 0.24 %. Additional Ar atoms in 3C-SiC crystal with a concentration of about  $8\times10^{19}\,\mathrm{cm}^{-3}$  should cause a volume increase of only 0.16 %. This value is a factor of 4 lower than that measured from the reflexes in RSM (113). Therefore, the volume change of the Ar<sup>+</sup> implanted 3C-SiC is caused not only by the additional Ar atoms but also by lattice defects such as vacancies. For further analysis of the 3C-SiC recrystallisation investigations of Ar<sup>+</sup> implanted substrates after thermal annealing are necessary.

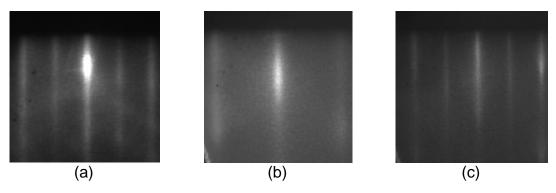

Figure 4.11 (a), (b) and (c) shows the RHEED patterns of a 3C-SiC,  $Ar^+$  implanted 3C-SiC and 600 nm c-GaN grown on  $Ar^+$  implanted 3C-SiC (sample 1855) measured at 720 °C in [110] direction. The RHEED pattern of both substrates was measured after the surface deoxidation at 800 °C. The RHEED pattern of the 3C-SiC offers a (2×4) reconstruction while a (1×1) reconstruction with diffuse streaks was observed in an  $Ar^+$  implanted 3C-SiC surface. The RHEED pattern of the c-GaN shows sharper streaks and a (2×2)-reconstruction detecting two-dimensional surface.

The RMS roughness of the 600 nm c-GaN layer on the Ar<sup>+</sup> implanted 3C-SiC was 6 nm comparable with the roughness of c-GaN on 3C-SiC. The FWHM of the rocking curve of the 600 nm c-GaN was 25 arcmin. To investigate the hexagonal inclusions in c-GaN the RSMs of the (002) reflex of c-GaN were measured. The hexagonal inclusions of GaN measured on the intensity ratio of the hexagonal (10-11) to the cubic (002) reflex were of 0.6 % maximum in all samples. Herewith it was shown that Ar<sup>+</sup> implanted 3C-SiC is a suitable substrate for cubic GaN epitaxy.

**Figure 4.10** HRXRD-RSM around the cubic (113) reflex of free standing 3C-SiC (a) untreated, (b) after  $Ar^+$  implantation, and (c) after  $Ar^+$  implantation and thermal annealing at 800 °C for 30 min.

**Figure 4.11** RHEED pattern measured in <110> direction at 720 °C of (a) 3C-SiC, (b)  $Ar^+$  implanted 3C-SiC and (b) 600 nm thick cubic GaN on  $Ar^+$  implanted 3C-SiC.

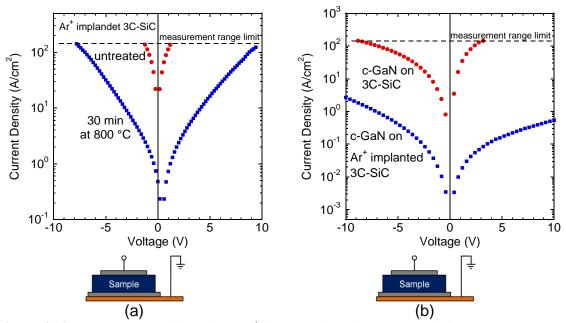

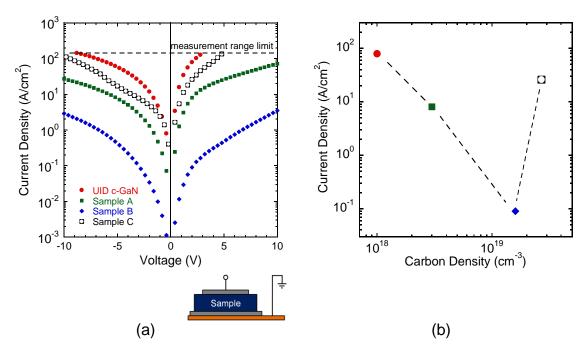

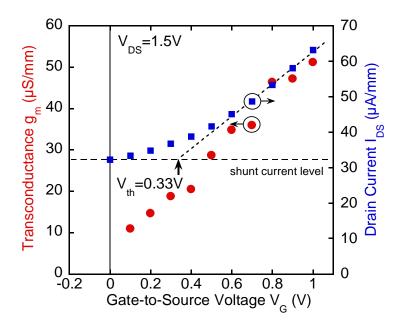

Electrical properties of  $Ar^+$  implanted 3C-SiC before and after thermal annealing were investigated by IV measurements which were performed between a Ti/Al/Ni/Au (15 nm/50 nm/15 nm/50 nm) contact on top and a large-area indium contact on the reverse side of the samples. The diameter of the top contact was 300  $\mu$ m. Figure 4.12 (a) shows IV curves of  $Ar^+$  implanted 3C-SiC before annealing and after thermal treatment at 800 °C for 30 min. The untreated substrate is highly conductive with a current density of I>35 A/cm<sup>2</sup> at V=1.5 V. After annealing the current is two orders of magnitude lower. Assuming that the thermal annealing induces a recrystallisation of an amorphised SiC layer, it can be concluded that the conductivity decrease of the 3C-SiC substrate is caused not by the amorphous SiC, but by residual defects remaining in the recrystallised layer.

**Figure 4.12** IV characteristics of (a) Ar<sup>+</sup> implanted 3C-SiC substrate before (red curve) and after thermal annealing (blue curves), and (b) c-GaN on free standing 3C-SiC without (red curve) and with Ar<sup>+</sup> implantation (blue curve).

Figure 4.12 (b) shows the IV curves of 600 nm c-GaN on 3C-SiC without and with Ar<sup>+</sup> implantation. These measurements were performed on Ti/Al/Ni/Au (15 nm/50 nm/15 nm/50 nm) contacts which were thermally annealed at 800 °C for 30 s. The current density through the c-GaN/3C-SiC is lower than through the 3C-SiC substrate caused by the low carrier density of c-GaN of  $n\approx 5\times 10^{16}$  cm<sup>-3</sup>. The current through the c-GaN on Ar<sup>+</sup> implanted 3C-SiC is a factor 2000 lower than that through the c-GaN on the untreated substrate measured at 2 V forward bias.

Thus, it was demonstrated that Ar<sup>+</sup> implantation of 3C-SiC is an effective method to induce an isolating layer between the c-AlGaN/GaN HFET devices and the highly conductive substrate with only low degradation of crystalline properties of epitaxial c-GaN layers.

#### 4.4 Carbon Doping of Cubic GaN

Another alternative for device isolation is the epitaxy of a semi-insulating c-GaN buffer layer. However, nominally undoped GaN typically shows *n*-type conductivity, presumably due to doping by residual oxygen impurities [43]. Therefore, achievement of a highly insulating GaN buffer prior to the deposition of AlGaN/GaN hetero structures has not been an easy task. To solve this problem, several approaches have been proposed. Using Fe [44], Be [45], and Zn [46] as acceptor-like point defects, semi-insulating hexagonal GaN films were also successfully grown by metal-organic chemical vapour deposition (MOCVD), MBE and hydride vapour phase epitaxy (HVPE) technique, respectively. Techniques incorporating carbon in hexagonal GaN buffer layers have been commonly used to obtain a highly resistive GaN buffer [47], [3], whereas the use of carbon tetrabromide (CBr<sub>4</sub>) as a carbon source shows great potential for doping of hexagonal GaN [48], [49]. The carbon doping of cubic GaN by CBr<sub>4</sub> was investigated in this work and the experimental results are summarized in this chapter.

The carbon source was a self-made  $CBr_4$  sublimation source connected directly to the MBE chamber. The cylinder with solid  $CBr_4$  powder is put into a heating jacket with a temperature controller. The source temperature can be varied from -15 °C and +50 °C. The gas line is permanently heated to 80 °C. The vapour pressure can be varied by the source temperature and by the opening the needle valve. Figure 2.3 shows the calibration curve of the  $CBr_4$  source. For this calibration the needle valve of the  $CBr_4$  source was fully opened (9-part), the source temperature was varied, and the beam equivalent pressure (BEP) was measured at the sample position.

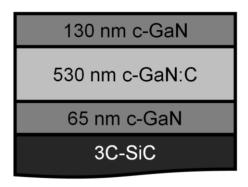

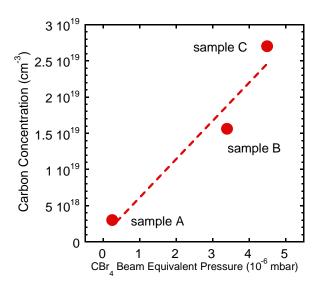

Figure 4.13 shows the cross sectional view of carbon doped samples. For this investigation a free standing 3C-SiC (001) substrate with a carrier density of  $n=2\times10^{18}~\rm cm^{-3}$  was used. A 65 nm thick UID c-GaN nucleation layer was deposited followed by a 530 nm c-GaN:C and a 130 nm UID c-GaN cap layer. The CBr<sub>4</sub> BEP of  $2.5\times10^{-7}$  mbar (sample 1832, A),  $3.4\times10^{-6}$  mbar (sample 1833, B) and  $4.5\times10^{-6}$  mbar (sample 1843, C) was preset. The undoped c-GaN cap layer was deposited to ensure similar electrical contacts on top of all samples. The reference sample was a 715 nm UID c-GaN layer (sample 1834, D).

**Figure 4.13** Cross-sectional view of investigated carbon doped C-GaN:C samples. The carbon BEP was set to  $2.2 \times 10^{-7}$  mbar,  $3.4 \times 10^{-6}$  mbar, and  $4.5 \times 10^{-6}$  mbar for three different samples, respectively.

The FWHM of the rocking curve of all c-GaN:C layers was about 25 arcmin. Thus, no deterioration in the structural quality is associated with carbon doping. This is supported by AFM scans which show a surface morphology typical of c-GaN MBE growth with a RMS roughness of 5-6 nm. To investigate the hexagonal inclusions in c-GaN:C RSMs around the (002) reflex of c-GaN were measured. The hexagonal inclusions of c-GaN:C measured on the intensity ratio of the hexagonal (10-11) to the cubic (002) reflex of c-GaN were comparable with those of the UID c-GaN sample. Thus no impact of carbon is seen on the structural or morphological properties of the films.

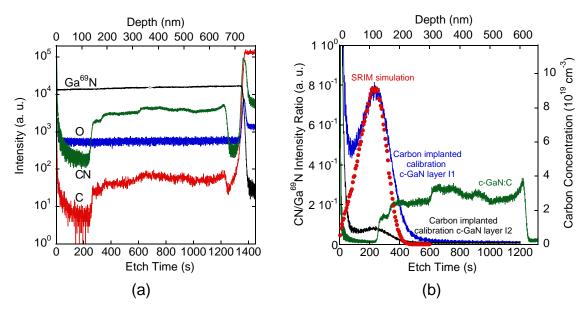

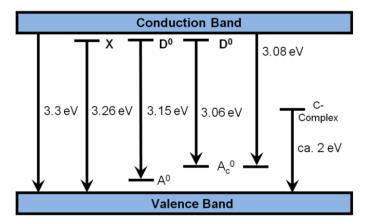

Time-of-flight secondary ion mass spectrometry (ToF-SIMS) was used to quantify the carbon incorporation behaviour. The measurements were performed by Dr. J.W. Gerlach at the IOM Leipzig. In Figure 4.14 (a) the measured depth profiles of Ga<sup>69</sup>N, O, CN, and C of c-GaN:C sample C grown at CBr<sub>4</sub> BEP of  $4.5 \times 10^{-6}$  mbar are depicted. Whereas the GaN concentration is constant all over the c-GaN epilayer thickness, a clear region with higher carbon concentration in the distance between 130 nm and 660 nm from the surface can be identified in the C-profile. This region is detected in the CN signal with higher intensity. Therefore, the intensity of the CN signal will be used for further analysis. The bromine concentration was at the SIMS detection limit of ~10<sup>15</sup> cm<sup>-3</sup>. Additionally, the oxygen level did not appear to increase beyond the low unintentionally impurity level of ~10<sup>16</sup> cm<sup>-3</sup> typical of our c-GaN films.

For the calibration of the measurement data a SIMS measurement of a carbon ion ( $C^+$ ) implanted 650 nm thick c-GaN layer (sample 1663) was done. The  $C^+$  implantation was performed by Dr. H. Karl at the University of Augsburg. For room temperature  $C^+$  implantation doses of  $1\times10^{15}$  cm<sup>-2</sup> (sample II) and of  $1\times10^{14}$  cm<sup>-2</sup> (sample I2) at 60 keV were used. Figure 4.14 (b) shows the CN/Ga<sup>69</sup>N signal profiles of the calibration c-GaN layers (blue and black curves) and c-GaN:C layer sample C (green curve). For the calibration of the carbon concentration scale the integrated carbon concentration of sample I1 and I2 were calculated using the C implantation doses. The red dotted curve is the simulated  $C^+$  implantation profile of the calibration sample I1 using the Monte-Carlo simulation software SRIM-2008. Thus, a maximum carbon concentration of  $9\times10^{19}$  cm<sup>-3</sup> was achieved in the calibration sample I1 and a medium carbon concentration of  $2.7\times10^{19}$  cm<sup>-3</sup> in the GaN:C sample C with the highest carbon doping density. In Figure 4.15 the incorporated carbon concentrations of samples A, B, and C are plotted vs. the

**Figure 4.14** (a) SIMS depth profiles of  $Ga^{69}N$ , O, CN and C of a c-GaN:C epilayer grown with  $CBr_4$  BEP of  $4.5 \times 10^{-6}$  mbar (sample C). (b)  $CN/Ga^{69}N$  ratio profiles of the same c-GaN:C sample and of a carbon implanted c-GaN calibration sample with simulated carbon concentration.

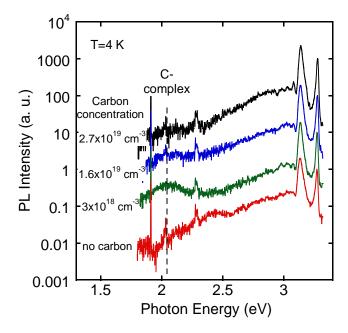

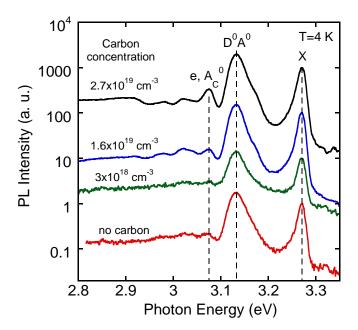

CBr<sub>4</sub> BEP, respectively. This measurement shows that the amount of the incorporated carbon is linearly related to the incident CBr<sub>4</sub> flux. The carbon concentration of  $3\times10^{18}$  cm<sup>-3</sup>,  $1.6\times10^{19}$  cm<sup>-3</sup> and  $2.7\times10^{19}$  cm<sup>-3</sup> was measured in samples A, B, and C, respectively.

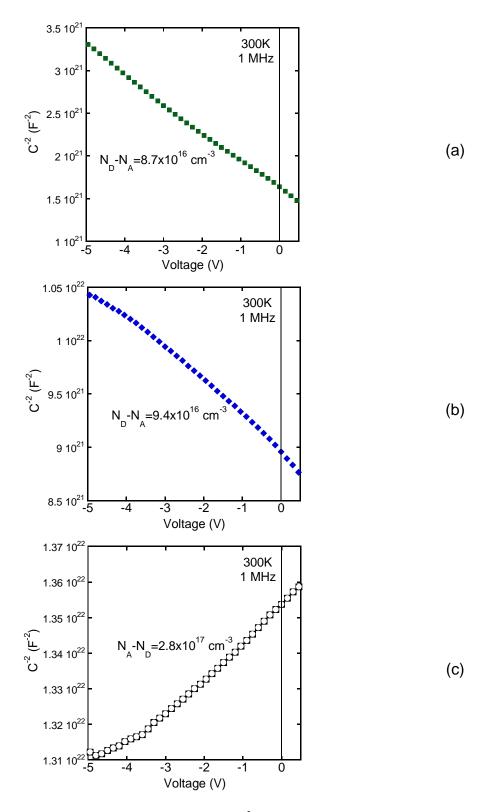

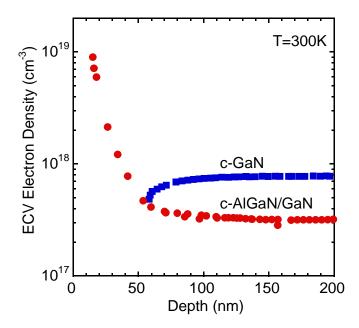

The net donor  $N_D$ - $N_A$  and acceptor  $N_A$ - $N_D$  concentration was investigated by capacitance-voltage (C-V) measurements. Figure 4.16 (a), (b), and (c) show room temperature C<sup>-2</sup>-V characteristics of the three carbon doped c-GaN samples A, B and C.

**Figure 4.15** Incorporated carbon concentration measured by SIMS vs. CBr<sub>4</sub> BEP.

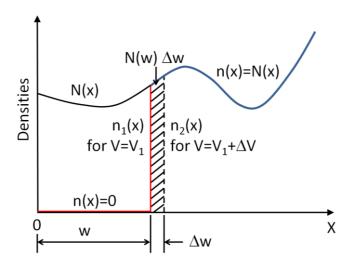

The measurements were performed at 1 MHz and 50 mV AC level. A noticeable difference of the measurement diagrams is the negative slope of the curves (a) and (b) and the positive slope of the curve (c). This behaviour points to a donor  $N_D$  surplus in samples A and B and to an acceptor  $N_A$  surplus in sample C. In order to investigate the doping profiles the model of parallel-plate capacitor was used with the abrupt approximation that the charge density  $\rho \approx qN_D$  for  $x < W_D$ ,  $\rho \approx 0$  for  $x > W_D$ , where  $W_D$  is the depletion width. According to this approximation the non-compensated impurity concentration can be calculated from [33]

$$N_D - N_A = \frac{2}{q\varepsilon_S A^2} \left[ -\frac{1}{dC^{-2}/dV} \right] \tag{4.1}$$

where A is the area of the contact and  $\varepsilon_s$  the dielectric constant of the semiconductor. The distance from the surface is given by

$$W_D = \frac{\varepsilon_s A}{C}. (4.2)$$

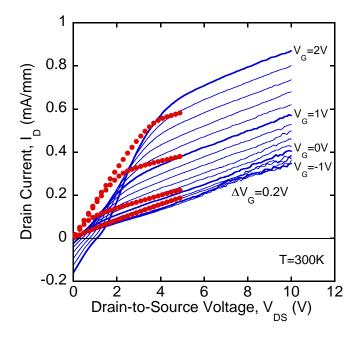

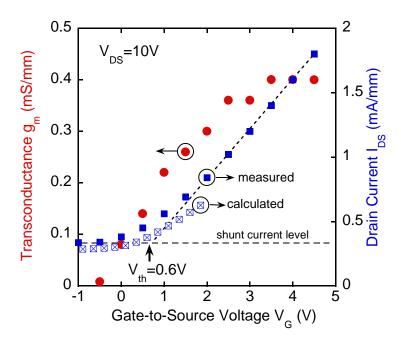

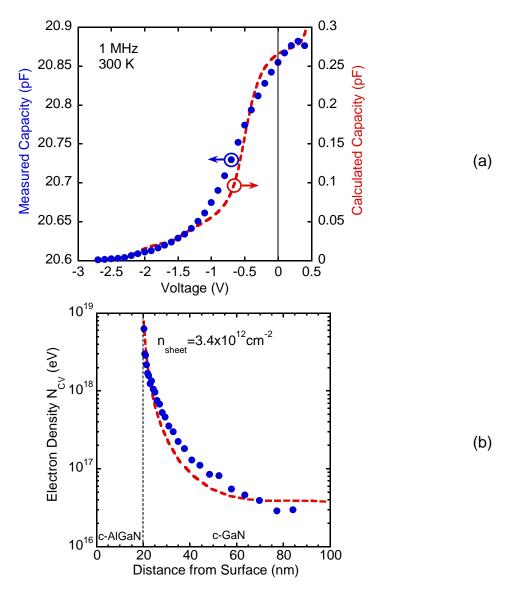

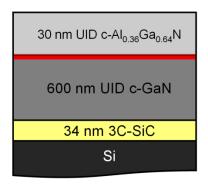

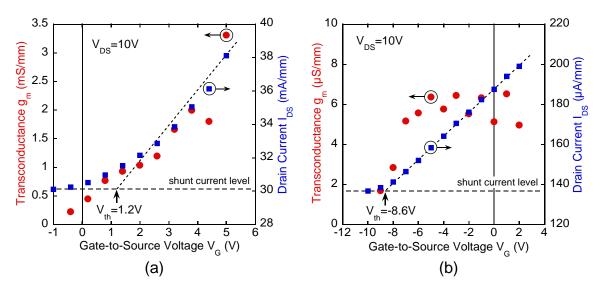

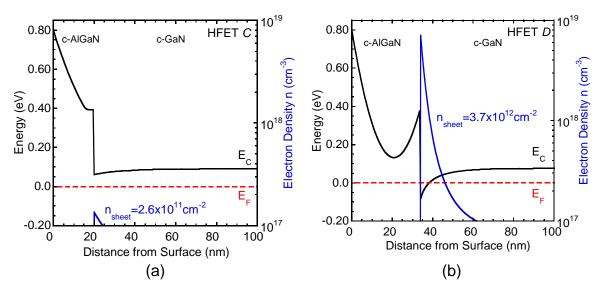

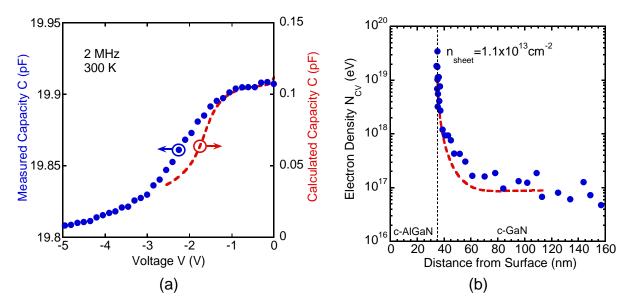

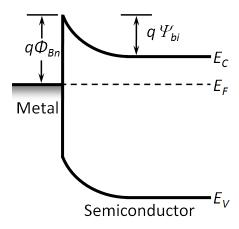

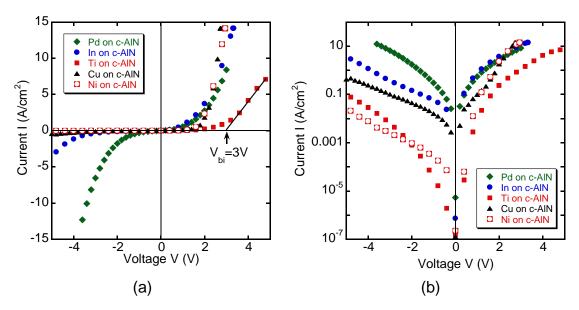

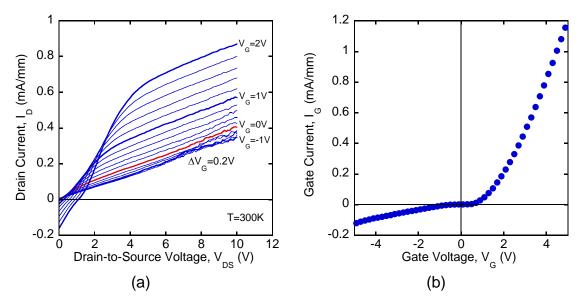

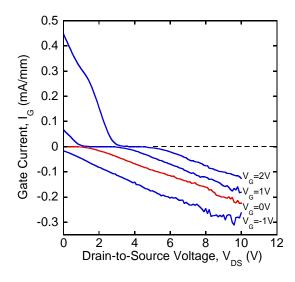

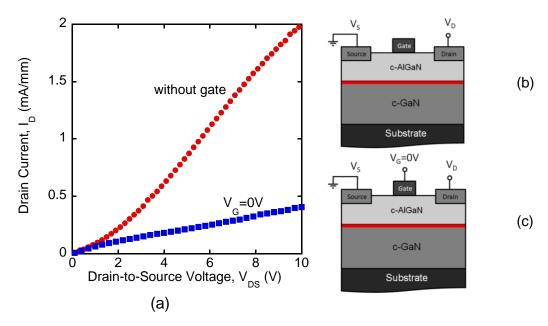

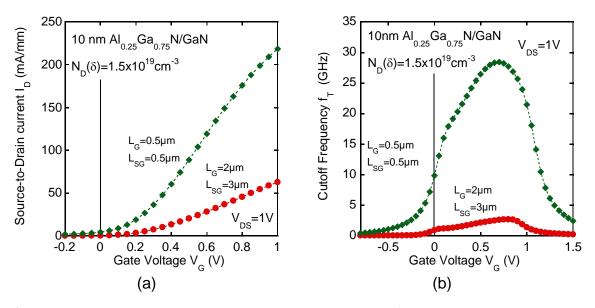

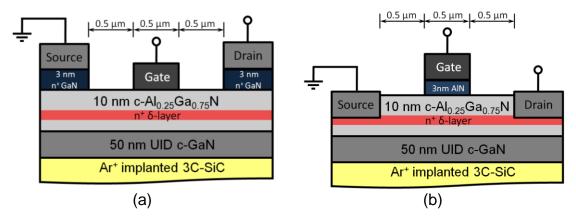

The linear curve behaviour of C<sup>-2</sup>-V measurement data points to homogeneous doping profiles of the samples in the measured depth section. Using Equation 4.1 the net doping density of  $N_D$ - $N_A$ =8.7×10<sup>16</sup> cm<sup>-3</sup>,  $N_D$ - $N_A$ =9.4×10<sup>16</sup> cm<sup>-3</sup> and  $N_A$ - $N_D$ =2.8×10<sup>17</sup> cm<sup>-3</sup> was calculated in sample A, B and C, respectively. The depletion width  $W_D$  was calculated using Equation 4.2 at V=0 V and is 245 nm for sample A and 575 nm for sample B. Due to the complex layer structure Equation 4.2 is not appropriate to calculate the depletion width of sample C. The measured net doping density of sample B is higher than that of sample A, but the  $N_D$  of sample A was apparently measured on the c-GaN:C layer and the  $N_D$  of sample B was measured on the UID c-GaN buffer below the c-GaN:C layer.