# **Design of Multi-GHz Data Converter Components**

A dissertation submitted in partial fulfillment of the requirements for the degree of DOKTORINGENIEUR (Dr.-Ing.) in Electrical Engineering

Faculty of Computer Science, Electrical Engineering and Mathematics

**University of Paderborn**

by Master of Science Samiran Halder Kolkata, India

# **Design of Multi-GHz Data Converter Components**

Zur Erlangung des akademischen Grades

DOKTORINGENIEUR (Dr.-Ing.)

der Fakultät für Elektrotechnik, Informatik und Mathematik

der Universität Paderborn

vorgelegte Dissertation

von

Master of Science Samiran Halder

aus Kalkutta, Indien

# **Design of Multi-GHz Data Converter Components**

Zur Erlangung des akademischen Grades

DOKTORINGENIEUR (Dr.-Ing.)

der Fakultät für Elektrotechnik, Informatik und Mathematik

der Universität Paderborn

vorgelegte Dissertation

von

Master of Science Samiran Halder

aus Kalkutta, Indien

Referent: Prof. Dr.-Ing. Andreas Thiede Korreferent: Prof. Dr.-Ing. Rolf Kraemer

Tag der mündlichen Prüfung: .....

Paderborn, den

Diss. EIM-E/253

# **DECLARATION**

This is to declare that the thesis entitled "Design of Multi-GHz Data Converter Components" submitted by Mr. Samiran Halder to the "Faculty of Computer Science, Electrical Engineering and Mathematics" of "University of Paderborn" for the partial fulfillment of the award of "DOKTORINGENIEUR (Dr.-Ing.)". Mr. Samiran Halder was awarded Master of Science degree from Indian Institute of Technology, Kharagpur, India, in 2005. This thesis was prepared by Mr. Samiran Halder under the supervision of Prof. Andreas Thiede of the "Faculty of Computer Science, Electrical Engineering and Mathematics" of "University of Paderborn". The results embodied in this thesis have not been submitted for any other degree or diploma in any other university or institution.

| ] | niran Halder) |

|---|---------------|

#### Abstract

# Design of Multi-GHz Data Converter Components by Samiran Halder

In the last few decades the communication bandwidth has evolved with an enormous speed and the requirement for high-speed data converters is directly dictated by that. In RF systems, the analog-digital interface is pushed towards the antenna, because the complex signal processing can be handled more efficiently in the digital domain. On the other hand it makes the design of these high-speed data converters more and more difficult.

In this dissertation the main design challenges in the field of multi-GHz data converters are discussed. The main research work is broadly divided into two parts. In the first part the different design techniques of multi-GHz analog to digital converters (ADC) are presented. In the other section the design of multi-GHz current steering digital to analog converters (DACs) have been discussed.

In the context of ADC design the front-end track and hold (THA) comes as the most critical part. This is because of the fact that any error introduced in this block cannot be compensated by the signal post-processing. In this research work an attempt has been made to improve the performance of the THA so that the stringent accuracy requirements of the quantization process can be relaxed. This is accomplished by enhancing the input range of the THA. Two different kind of THAs are developed. In both the THAs, different techniques are used to enhance the input range up to 2Vpp differential at the sampling rate of 10GHz. According to the authors knowledge these THAs are the only published THAs which can work with 2Vpp input signal and achieve an accuracy of more than 6.5-bit at a sampling rate of 10GHz. A new double sampled technique is proposed for the open loop THA architectures which can be instrumental to double the sampling speed of the THA with a little overhead of power dissipation compared to conventional open loop THAs. As a design example a 20GHz 6-bit comparator has been designed and measured successfully.

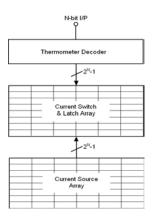

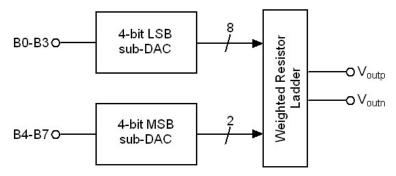

An 8-bit segmented current steering DAC has already been designed. As a tread-off between the accuracy and power consumption 50% segmentation is used. The MSB sub-DAC is implemented with conventional unary weighted DAC architecture. In the context of high-speed DAC design the binary to thermometer decoder comes as the design bottleneck in terms

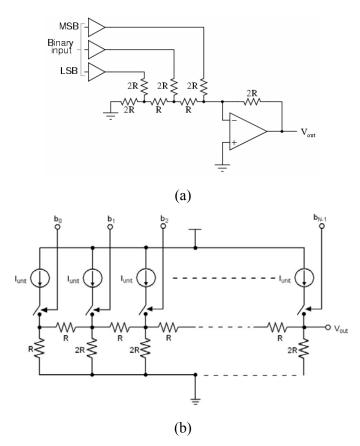

of speed and power. In this unary sub-DAC design a novel thermometer decoder is proposed which is mainly based on an HBT ROM structure. In simulation the 8-bit DAC shows an accuracy of 7.83 effective number of bits (ENOB) with 9GHz of single tone input sinusoidal and a sampling rate of 20GHz. The 4-bit LSB sub-DAC is already implemented with a weighted resistive ladder network. A novel binary weighted resistive ladder network is proposed. The 4-bit DAC is found to be functional up to 30GHz of sampling rate which shows the second best performance in terms of sampling speed for published SiGe high-speed DACs.

# **ACKNOWLEDGEMENTS**

I will always consider my experience of the past three and half years in the department of Circuit design, IHP Microelectronics GmbH, as one of the most wonderful and enjoyable parts of my life. I am so deeply indebted to many people during the work leading to this dissertation. First of all, I would like to express my sincere gratitude to Prof. Rolf Kraemer and, Prof. Andreas Thiede who has encouraged and guided me through all my research work. They are true advisor to me. I will benefit from their precious and generous advices lifelong.

I am grateful to Dr. Hans Gustat who always leave his doors open for me whenever I encountered technical problems or need his suggestion on my work. During my research work in IHP Microelectronics GmbH, he was my project leader and it would not be possible to accomplish the dissertation without his constant encouragement. He is virtually a mentor to me.

I owe my gratitude to Dr. Christoph Scheytt, head of the department Circuit design, for providing the opportunity to pursue my research work in good friendly atmosphere. His technical advices and insights are really valuable to the success of this research.

I would say thanks to all of the team members of department of Circuit design, which include Yaoming Sun, Sabbir A. Osmany, Kai Hu, Dr. Frank Herzel, Dr. Wolfgang Winkler, Dr. Klaus Schmalz. I am so fortunate to be able to work with such a group of extraordinary colleagues and good friends. I would like to specially thank Mr. Yevgen Borokhovych whose talent and persistence assured our achievements in the high-speed project.

The last but not the least people to mention are the most important ones in my life, my family. The accomplishment of this work would not be possible without them. My parents and sister are the great source of support and encouragement to my research and life. I cannot adequately express the love and gratitude I feel for them.

# <u>Index</u>

| Chapter 1 Introduction                                     |    |

|------------------------------------------------------------|----|

| 1.1. Motivation                                            |    |

| 1.2. Research Contribution                                 |    |

| 1.3. Organization of Thesis                                | 3  |

| Chapter 2 ADC Architecture                                 |    |

| 2.1. Introduction                                          | 5  |

| 2.2. Quantization                                          |    |

| 2.3.1. Static Errors in ADC                                | 8  |

| 2.3.2. Dynamic Errors in ADC                               |    |

| 2.3.2.1. Signal-to-Noise ratio (SNR)                       | 10 |

| 2.3.2.2. Total Harmonic Distortion (THD)                   | 11 |

| 2.3.2.3. Signal to Noise and Distortion Ratio (SNDR)       | 11 |

| 2.3.2.4. Spurious Free Dynamic Range (SFDR)                |    |

| 2.3.2.5. Effective Number of Bits (ENOB)                   |    |

| 2.3.2.6. Dynamic Range                                     |    |

| 2.4. Performance Analysis and Present Trends in ADC Design |    |

| 2.5.1. Flash ADC                                           |    |

| 2.5.2. Sub-ranging or Two step ADC                         |    |

| 2.5.3. Folding ADC                                         |    |

| 2.5.4. Time Interleaved ADC                                |    |

| 2.6. Conclusions                                           | 23 |

| Chapter 3 Design of Multi-GHz ADC Components               |    |

| 3.1. Introduction                                          |    |

| 3.2. Performance Matrices for Track and Hold Amplifier     |    |

| 3.3. Open Loop THA Architecture Review                     |    |

| 3. 3. 1. Open Loop THA with Switch Emitter Follower        | 28 |

| 3. 3. 2. Improved Open Loop THA Architecture               |    |

| 3.4. Implementation of Open Loop THA                       |    |

| 3. 4. 1. Implementation of Input Buffer                    |    |

| 3. 4. 1. 1. Complementary Emitter Follower                 |    |

| 3. 4. 1. 2. Cascode Input Buffer                           |    |

| 3. 4. 2. Implementation of Switched Emitter Follower       |    |

| 3. 4. 2. 1. Aperture Time                                  |    |

| 3. 4. 2. 2. Pedestal Error                                 |    |

| 3. 4. 2. 3. Hold Mode Feedthough                           |    |

| 3. 4. 2. 4. Aperture Jitter                                |    |

| 3. 4. 2. 5. Design optimization of the SEF                 |    |

| 3. 4. 3. Output Buffer                                     |    |

| 3. 4. 4. Implementation of Full THA                        |    |

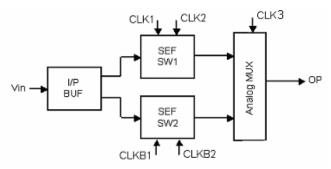

| 3. 5. Double Sampling THA                                  |    |

| 3. 5. 1. Input Buffer                                      |    |

| 3. 5. 2. Skew Insensitive Double sampling SEF              |    |

| 3 5 3 Anglog Multipleyer                                   | 18 |

| 3. 5. 4. Preliminary simulation results                             | 49  |

|---------------------------------------------------------------------|-----|

| 3.6. Experimental Results of implemented THAs                       |     |

| 3.7. Design of High-Speed Comparator                                |     |

| 3.8. Measurement Results of the Comparator                          |     |

| 3.9 Conclusions                                                     |     |

| Chapter 4 Current Steering DAC Architecture                         |     |

| 4.1. Introduction                                                   | 64  |

| 4.2. Current Steering DAC Architecture                              |     |

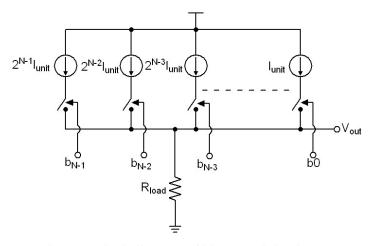

| 4.2.1. Binary Weighted Current Steering DAC                         |     |

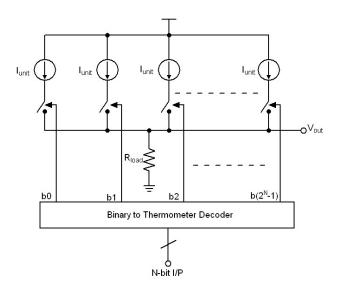

| 4.2.2. Unary weighted Current steering DAC                          |     |

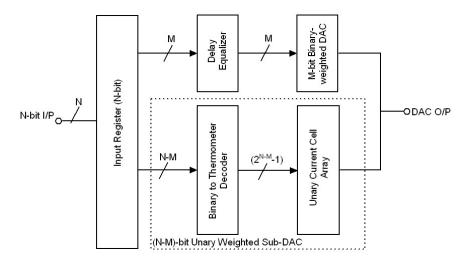

| 4.2.3. Segmented Current Steering DAC                               |     |

| 4.2.4. R-2R ladder DAC                                              | 69  |

| 4.3. Error sources in Current steering DAC                          | 70  |

| 4.3.1. Static Error Source                                          | 70  |

| 4.3.2. Dynamic Error Sources                                        | 72  |

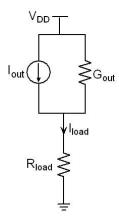

| 4.3.2.1. Finite Output Impedance                                    | 72  |

| 4.3.2.2. Asynchronous Switching                                     |     |

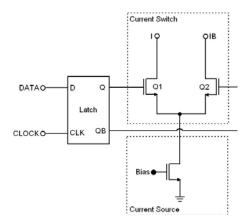

| 4.3.2.3. Current Switch Non-idealities                              | 79  |

| 4.4. Techniques to Enhance the Accuracy of Current Steering DAC     | 80  |

| 4.4.1. Layout Technique                                             |     |

| 4.5.2. Dynamic Element Matching                                     | 83  |

| 4.4.3. Current Cell calibration technique                           | 85  |

| 4.5. Conclusions                                                    | 88  |

| Chapter 5 Design of Multi-GHz DAC                                   |     |

| 5. 1. Introduction                                                  | 90  |

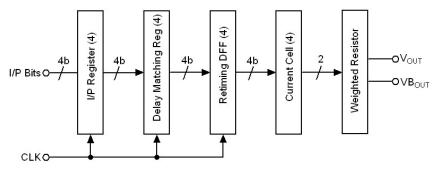

| 5.2.1. Design of 4-bit LSB Sub-DAC                                  |     |

| 5.2.1.1. Design of Input and Delay Matching Register                |     |

| 5.2.1.2. Design of Unit Current Cell                                |     |

| 5.2.1.3. Design of Retiming DFF                                     | 95  |

| 5.2.1.4. Design of Weighted Resistor Network                        |     |

| 5.2.2. Implementation of 4-bit MSB Sub-DAC                          | 98  |

| 5.2.2.1. Design of High-speed Thermometer Decoder                   | 98  |

| 5.2.2.2. Design of HBT ROM                                          |     |

| 5.2.3. Design of 8-bit Segmented Current Steering DAC               | 105 |

| 5.3. Simulation Results of the 8-bit Segmented Current steering DAC | 107 |

| 5.4. Measurement Results of 4-bit Modified Binary Weighted DAC      | 111 |

| 5.5. Conclusions                                                    | 115 |

| Chapter 6 Conclusions                                               |     |

| 6.1. Summary                                                        | 116 |

| 6.2. Future Works                                                   |     |

| References                                                          | 119 |

# List of Figures

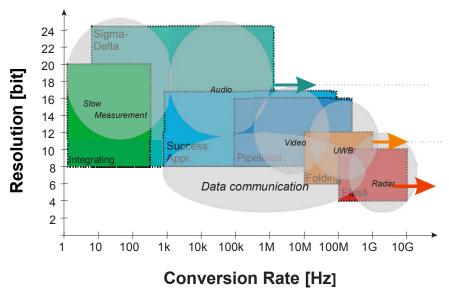

| Fig. | 1.1. Requirements of data converters for different applications                               | 2  |

|------|-----------------------------------------------------------------------------------------------|----|

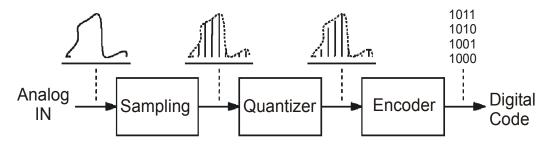

| Fig. | 2.1. Analog to digital conversion                                                             | 5  |

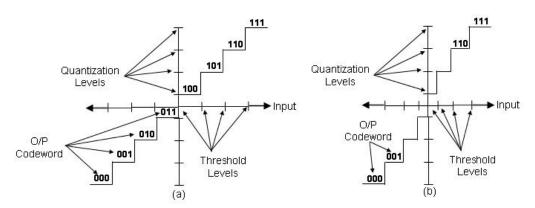

| Fig. | 2.2 Transfer characteristics of (a) uniform, (b) nonuniform quantization                      | 6  |

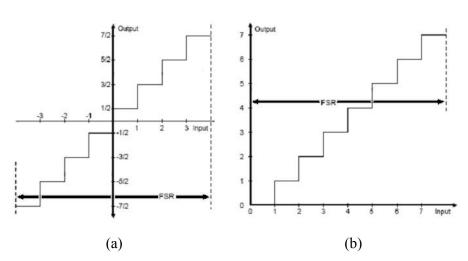

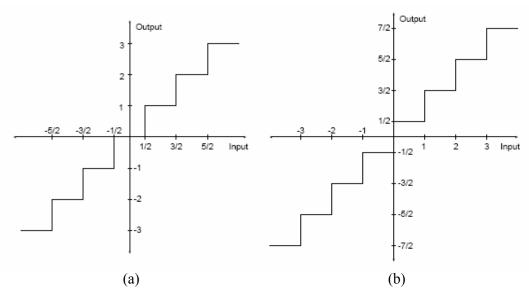

| Fig. | 2.3. Transfer function of (a) bipolar (b) unipolar quantization                               | 7  |

| Fig. | 2.4. (a) Mid-tread, (b) Mid-riser quantizer                                                   | 8  |

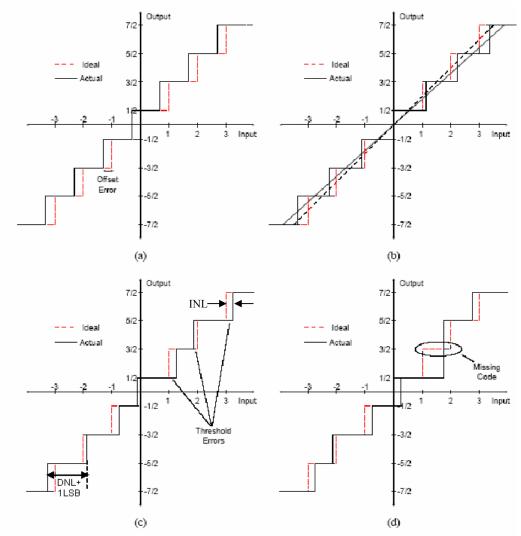

| Fig. | 2.5 (a) Offset error, (b) Gain error, (c) Threshold errors (INL & DNL), (d) Missing           | 9  |

|      | codes                                                                                         | 7  |

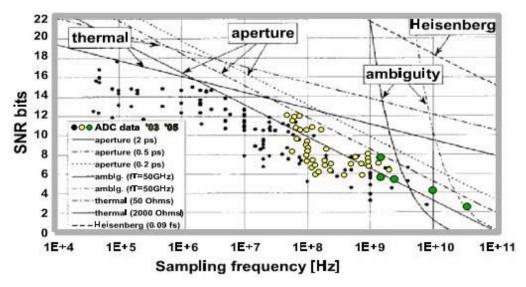

| Fig. | 2.6. Performance limits of ADC due to different physical phenomena                            | 14 |

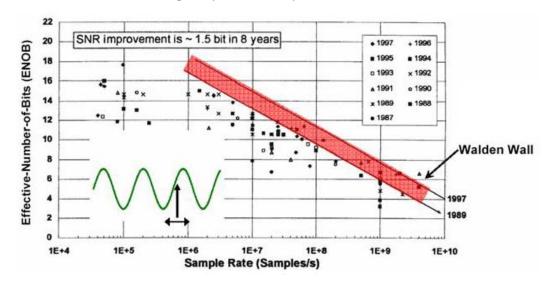

| Fig. | 2.7. Performance envelop improvement of ADC                                                   | 15 |

|      | 2.8. Performance of different ADC architectures                                               | 16 |

| Fig. | 2.9. Flash ADC architecture                                                                   | 17 |

| Fig. | 2.10. Block diagram of sub-ranging ADC                                                        | 19 |

| Fig. | 2.11. Simplified block diagram of Folding ADC                                                 | 20 |

| Fig. | 2. 12. Principle of folding                                                                   | 20 |

| _    | 2. 13. Folding signal generation                                                              | 21 |

| _    | 2. 14. Folding interpolating ADC Architecture                                                 | 22 |

|      | 2. 15. Block diagram of time interleaved ADC                                                  | 23 |

| _    | 3.1. Functional block diagram of THA                                                          | 26 |

| _    | 3. 2. Track and Hold terminologies                                                            | 27 |

| _    | 3. 3. Hold mode characteristics                                                               | 27 |

|      | 3.4. Block diagram of open loop THA                                                           | 28 |

| _    | 3.4. Block diagram of open loop THA                                                           | 29 |

| _    | 3. 6. Improved Open Loop THA                                                                  | 30 |

|      | 3. 7. Transient waveform at the input node (A) of the sampling switch                         | 31 |

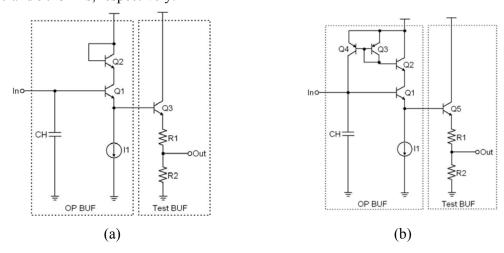

| _    | 3. 8. (a) Simple pnp emitter follower (b) npn-pnp emitter follower                            | 33 |

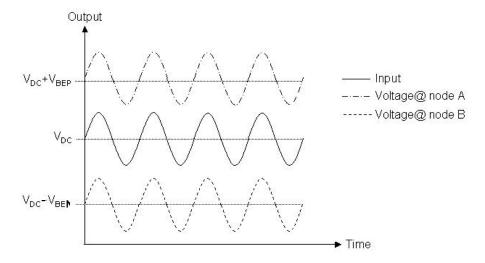

|      | 3. 9. The voltage wave forms at different nodes of npn-pnp emitter follower                   | 33 |

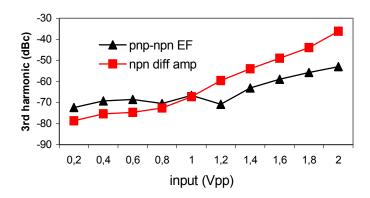

|      | 3. 10. 3 <sup>rd</sup> harmonic power of npn pnp emitter follower input buffer                | 34 |

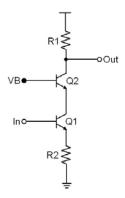

|      | 3. 11. Cascode input buffer                                                                   | 35 |

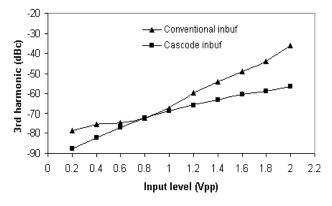

|      | 3. 12. 3 <sup>rd</sup> harmonic power of cascade input buffer                                 | 35 |

| _    | 3. 13. Switch emitter follower                                                                | 36 |

| _    | 3. 14. SEF approximation in the track mode                                                    | 37 |

|      | 3. 15. Hold mode feedthrough compensation capacitor                                           | 38 |

|      | 3. 16. 3 <sup>rd</sup> harmonic power at SEF of different bias currents and hold capacitances | 41 |

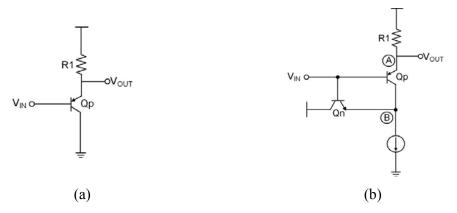

|      | 3. 17. (a) Simple output buffer (b) Output buffer with base current compensation              | 42 |

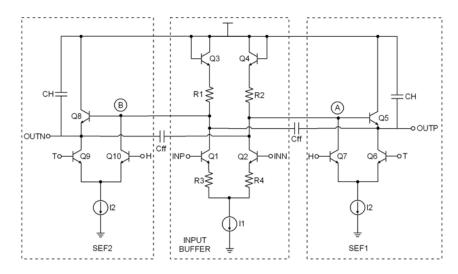

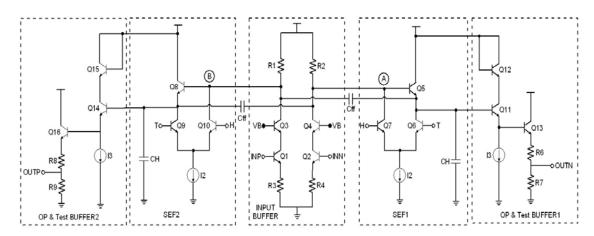

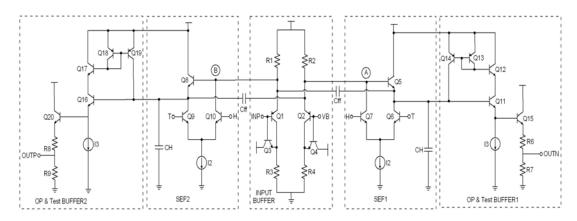

|      | 3. 18. Simplified schematic of npn THA                                                        | 43 |

|      | 3. 19. Simplified schematic of npn pnp THA                                                    | 44 |

| Fig. | 3. 20. Block diagram of proposed pseudo-differential double sampling open-loop                | 45 |

|      | THA                                                                                           |    |

|      | 3. 21. Input buffer of double sampled THA                                                     | 46 |

| _    | 3. 22. Clock timing skew                                                                      | 47 |

|      | 3. 23 Schematic of double sampled SEF                                                         | 48 |

| _    | 3. 24. Timing diagram of double sampling SEF                                                  | 48 |

| _    | 3. 25. Schematic of a pseudo differential path of the core double sampling THA                | 48 |

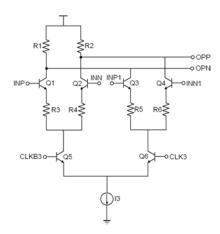

| Fig. | 3. 26. Schematic of Analog multiplexer circuit                                                | 49 |

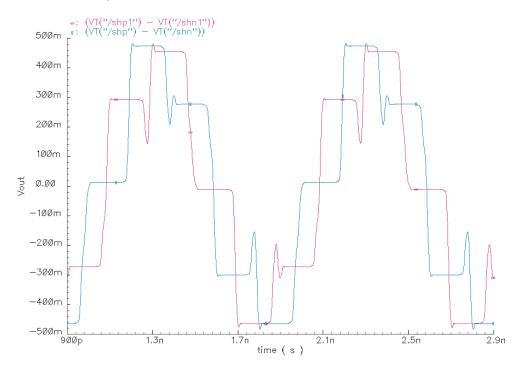

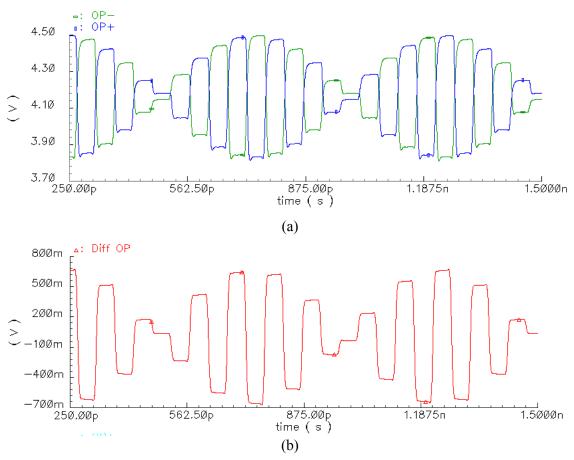

| Fig. 3. 27. Transient response of parallel pseudo differential output                                                                     | 50       |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------|

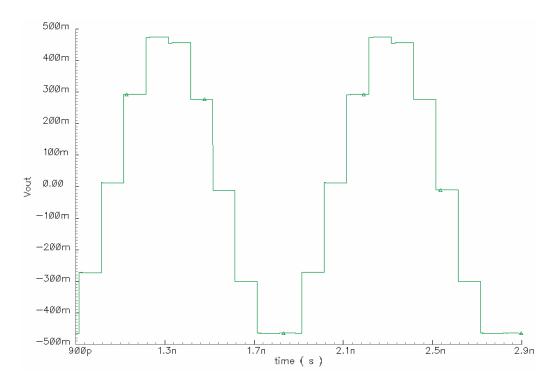

| Fig. 3. 28 Combined outputs of the parallel paths of double sampling THA                                                                  | 50       |

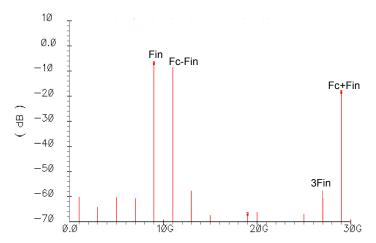

| Fig. 3. 29. Spectral components of the double sampling THA                                                                                | 51       |

| Fig. 3. 30. Output spectrum of double sampled THA                                                                                         | 51       |

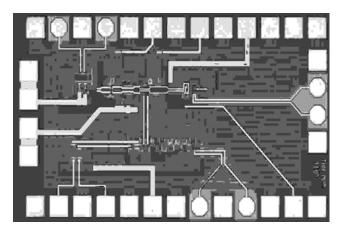

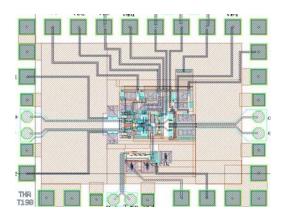

| Fig. 3. 31. Chip micrograph of npn THA                                                                                                    | 52       |

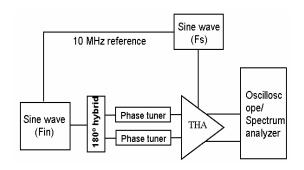

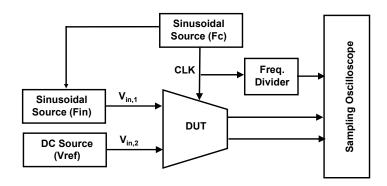

| Fig. 3. 32. Test setup for characterizing the THA                                                                                         | 53       |

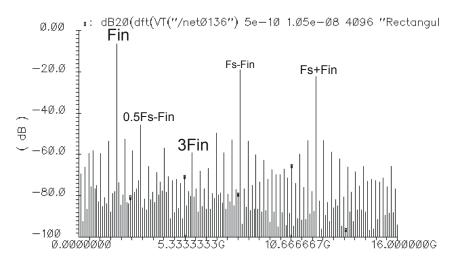

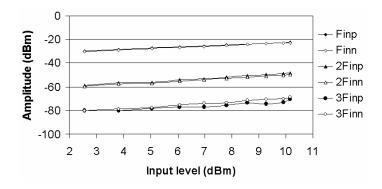

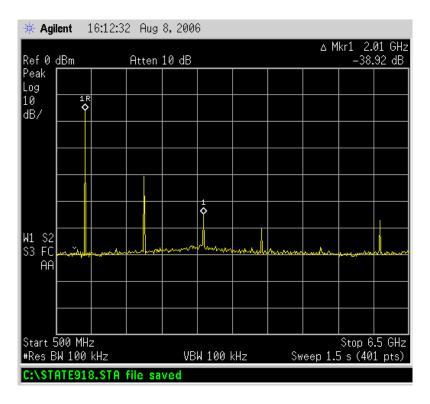

| Fig. 3.33. Measured single-ended frequency spectrum of the THA                                                                            | 53       |

| Fig. 3. 34. Measured spectral components of pseudo-differential outputs                                                                   | 54       |

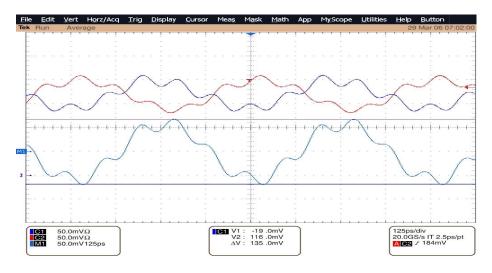

| Fig. 3. 35. Measured output waveform at 12Gs/s with 2GHz 2Vpp input                                                                       | 54       |

| Fig. 3. 36. Chip micrograph of npn pnp THA                                                                                                | 55       |

| Fig. 3. 37. Transient response of npn pnp THA for Fin=1GHz @10Gs/S                                                                        | 55       |

| Fig. 3. 38. Single output spectrum of npn pnp THA for Fin=1GHz and Fs=10GHz                                                               | 56       |

| Fig. 3. 39. Block diagram of high-speed comparator                                                                                        | 58       |

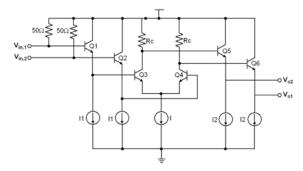

| Fig. 3. 40. Simplified schematic of the preamplifier                                                                                      | 59       |

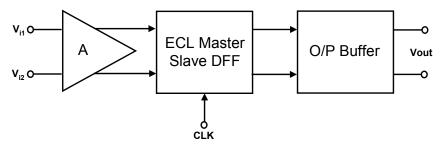

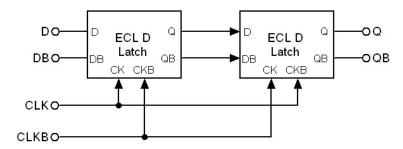

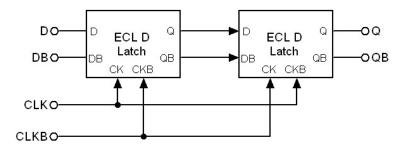

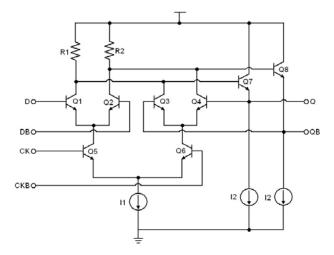

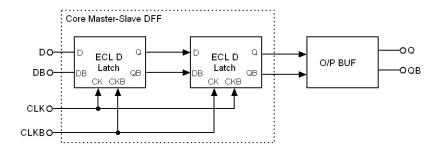

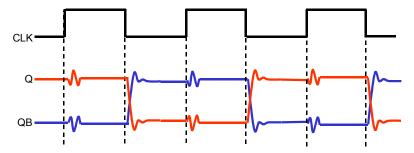

| Fig. 3.41. Block diagram of ECL master slave DFF                                                                                          | 59       |

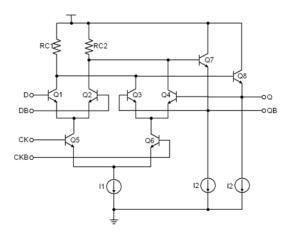

| Fig. 3.42. Simplified schematic of D latch                                                                                                | 60       |

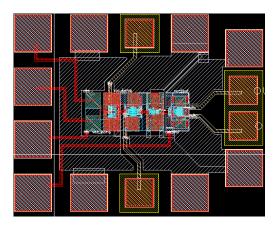

| Fig. 3. 43. Layout of 20GHz HBT comparator                                                                                                | 60       |

| Fig. 3. 44. Test setup for the comparator                                                                                                 | 61       |

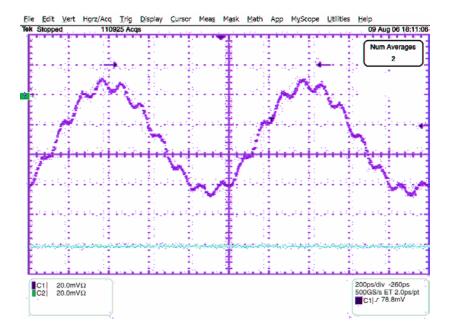

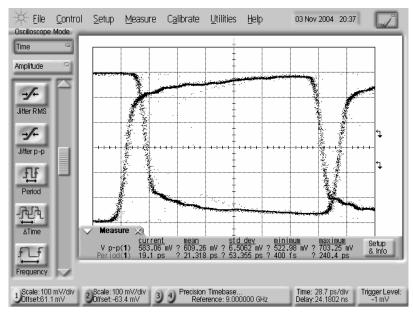

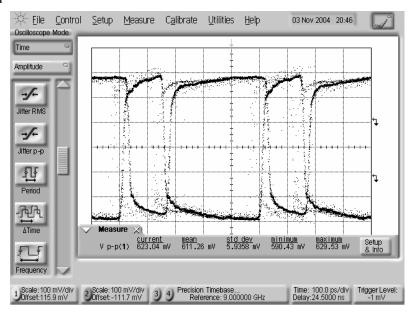

| Fig. 3.45. Magnified output waveform of the comparator for 2GHz 100mVpp                                                                   |          |

| sinusoidal with 20GHz of clock                                                                                                            | 61       |

| Fig. 3.46. Output waveform of the comparator for 2GHz 20mVpp sinusoidal with                                                              |          |

| 20GHz of clock                                                                                                                            | 62       |

| Fig. 4.1. Block diagram of binary weighted DAC                                                                                            | 66       |

| Fig. 4.2. Block diagram of binary weighted DAC                                                                                            | 67       |

| Fig. 4.3. Simplified block diagram of segmented current steering DAC                                                                      | 68       |

|                                                                                                                                           | 69       |

| Fig. 4. 4. (a) conventional (b) improved R-2R ladder DAC architecture                                                                     |          |

| Fig. 4.5. Small signal equivalent model of unit current source                                                                            | 73<br>75 |

| Fig. 4.6. Commonly used floorplan for unary weighted DAC                                                                                  |          |

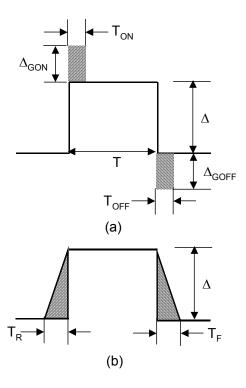

| Fig. 4.7. Simplified schematic of unit current cell<br>Fig. 4.8 (a) Representation of output glitch due to the charge injection and clock | 76       |

|                                                                                                                                           |          |

| feedthrough of current switch                                                                                                             | 79       |

| (b) Finite rise and fall time for the built-in-time constant of the current switch                                                        |          |

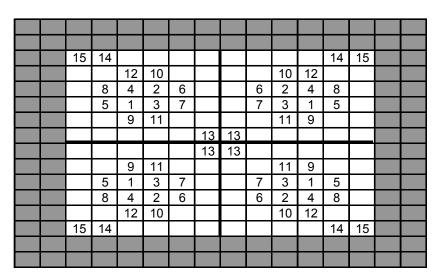

| Fig. 4.9. Floorplan of double centroid unary current source array                                                                         | 81       |

| Fig. 4.10. Linear gradient error reducing layout scheme                                                                                   | 82       |

| Fig. 4.11. An improved linear gradient error reducing layout scheme                                                                       | 82       |

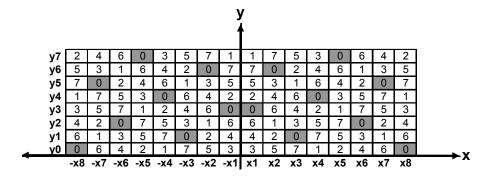

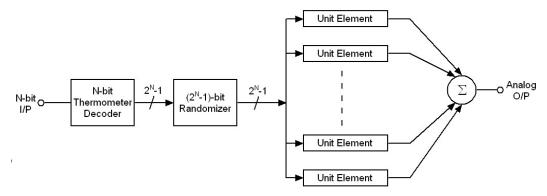

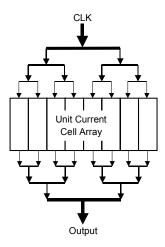

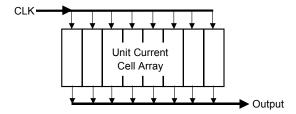

| Fig. 4.12. Architecture of dynamic element matching unary weighed DAC                                                                     | 83       |

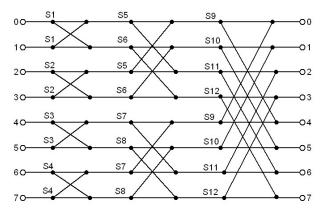

| Fig. 4.13. Example of three stage butterfly randomizer                                                                                    | 84       |

| Fig. 4.14. Block diagram of current source calibration                                                                                    | 86       |

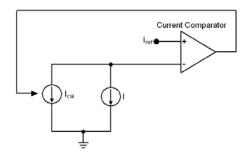

| Fig. 4.15. Block diagram of non-binary weighted DAC based calibration loop                                                                | 86       |

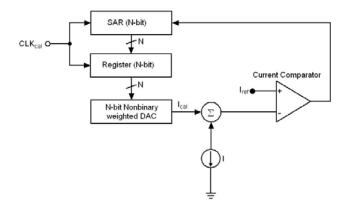

| Fig. 4.16. Block diagram of N-bit non-binary weighted calibration DAC                                                                     | 87       |

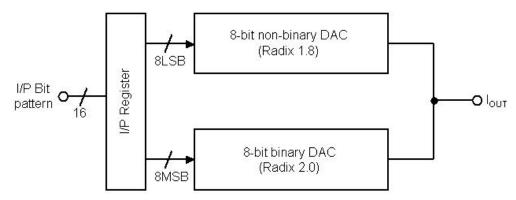

| Fig. 4.17. Block diagram of 8-bit non-binary weighted DAC                                                                                 | 87       |

| Fig. 4.18. Layout of 16-bit non-binary weighted DAC                                                                                       | 88       |

|                                                                                                                                           | 91       |

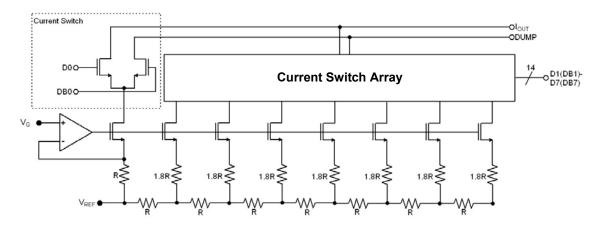

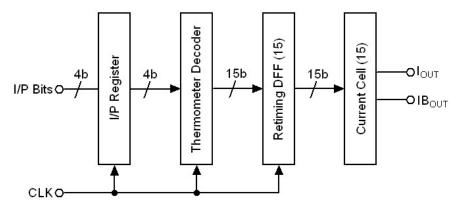

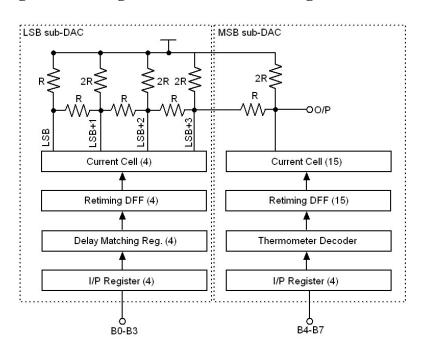

| Fig. 5.1. Block diagram of 8-bit modified segmented DAC architecture                                                                      | 91       |

| Fig. 5.2. Block diagram of LSB DAC                                                                                                        | 92<br>92 |

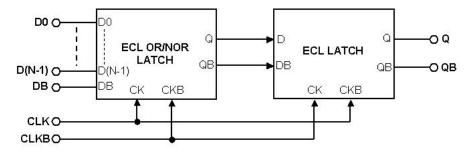

| Fig. 5.3. Block diagram of ECL master slave DFF                                                                                           |          |

| Fig. 5.4. Simplified schematic of ECL D-latch                                                                                             | 93       |

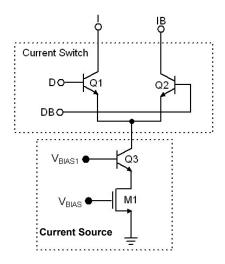

| Fig. 5.5. Simplified schematic of unit current cell                                                                                       | 94       |

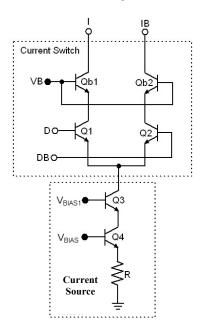

| Fig. 5.6. Schematic of improved unit current cell                                                                                         | 94       |

| Fig. 5. 7. Block diagram of retiming DFF                                                                                                  | 96       |

| Fig. 5. 8. Output waveform of an unbuffered DFF                                                                                           | 96       |

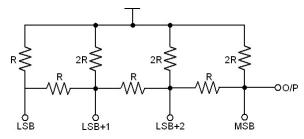

| Fig. 5. 9. R-2R Ladder network for 4-bit DAC                                                                                              | 97       |

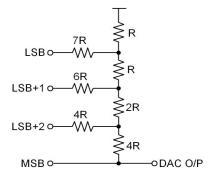

| Fig. 5.10. Schematic of modified weighted resistor network                                                                                                                  | 97  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 5.11. Block diagram of 4-bit MSB Sub-DAC                                                                                                                               | 98  |

| Fig. 5.12. Conventional binary to thermometer decoder                                                                                                                       | 99  |

| Fig. 5.13. Longest delay path from the input to the output                                                                                                                  | 100 |

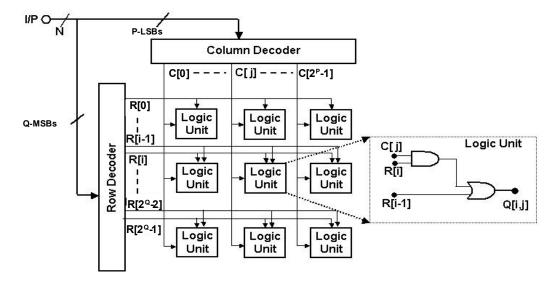

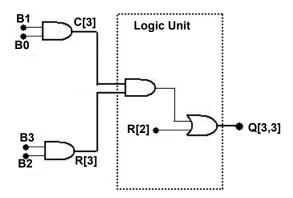

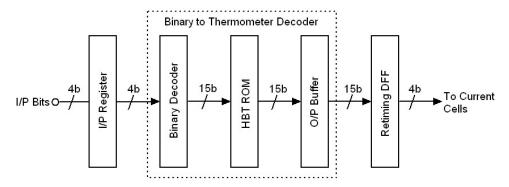

| Fig. 5.14. Block diagram of improved 4-bit binary to thermometer decoder                                                                                                    | 101 |

| Fig. 5.15. Block diagram of OR/NOR ECL DFF                                                                                                                                  | 101 |

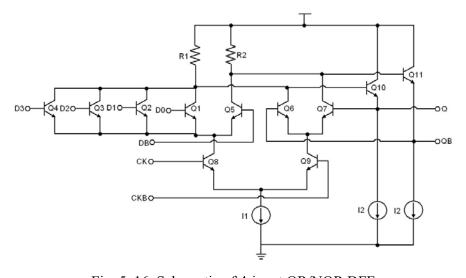

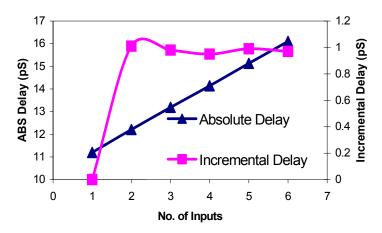

| Fig. 5. 16. Schematic of 4-input OR/NOR DFF                                                                                                                                 | 102 |

| Fig. 5.17. Plot of absolute and incremental delay with increasing no. of inputs for OR/NOR D-latch                                                                          | 103 |

| Fig. 5.18. Simplified schematic of pseudo differential ROM                                                                                                                  | 104 |

| Fig. 5.19. Block diagram of 8-bit segmented current steering DAC                                                                                                            | 105 |

| Fig. 5. 20. Tree-like clock and output routing                                                                                                                              | 106 |

| Fig. 5. 21. Delay compensated clock and output routing                                                                                                                      | 106 |

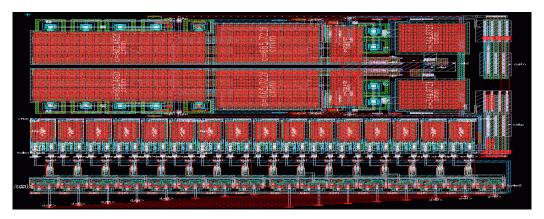

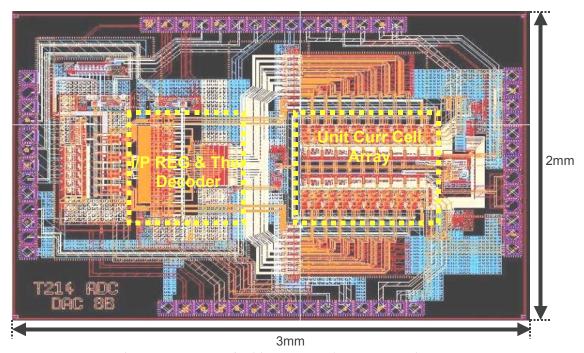

| Fig. 5.22. Layout of 8-bit segmented current steering DAC                                                                                                                   | 107 |

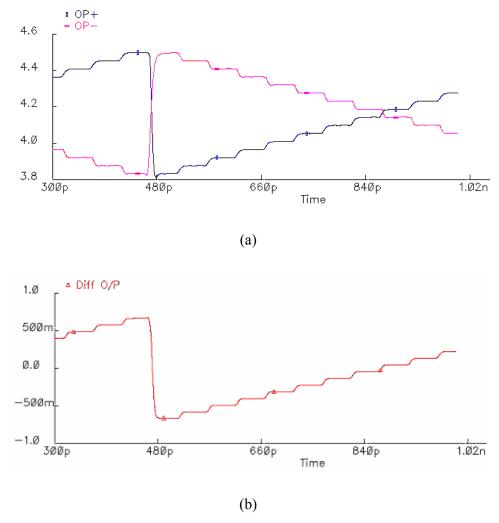

| Fig. 5.23. (a) Single-ended outputs, (b) Differential output of the DAC for digital ramp input                                                                              | 108 |

| Fig. 5. 24. (a) single-ended, (b) differential output signal of the DAC for $F_{in}$ =9GHz, $F_{s}$ =20GHz                                                                  | 109 |

| Fig. 5. 25. Output spectrum of the 8-bit DAC for F <sub>in</sub> =9GHz and F <sub>s</sub> =20GHz                                                                            | 110 |

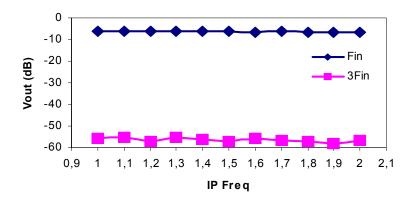

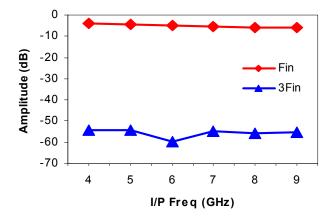

| Fig. 5. 26. Fundamental and 3 <sup>rd</sup> order frequency components for different input frequencies                                                                      | 110 |

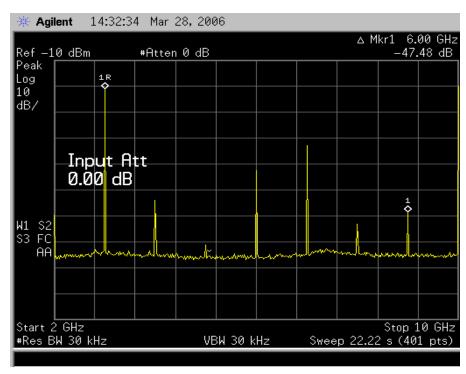

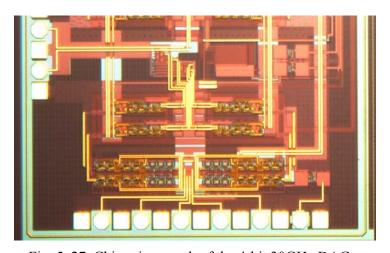

| Fig. 5. 27. Chip micrograph of the 4-bit 30GHz DAC                                                                                                                          | 111 |

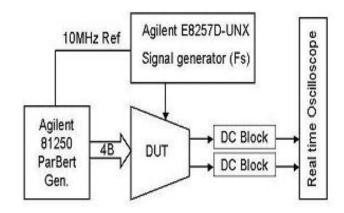

| Fig. 5. 28. Measurement setup for the 4-bit 30GHz DAC                                                                                                                       | 112 |

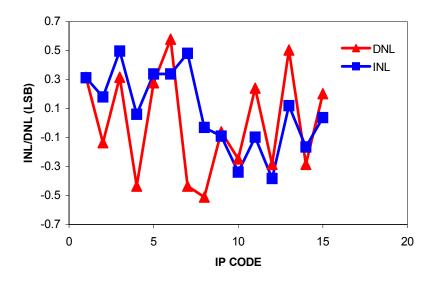

| Fig. 5. 29. INL/DNL plot of 4-bit 30GHz DAC                                                                                                                                 | 112 |

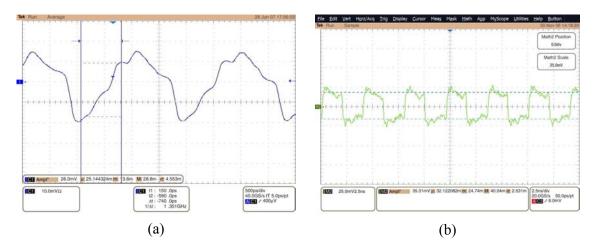

| Fig. 5. 30. (a) Sinusoidal reconstruction for F <sub>c</sub> =30GHz, I/P data rate=2.8GHz                                                                                   | 113 |

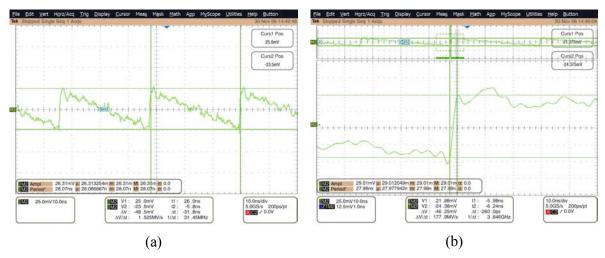

| (b) Step reconstruction for F <sub>c</sub> =30GHz, I/P data rate=0.5GHz<br>Fig. 5. 31. (a) Ramp reconstruction, (b) Rise time measurement for Fc=22GHz,<br>Data rate=0.5GHz | 113 |

# List of Tables

| Table. 3.1. Simulated performance summery of double sampled THA                 | 51  |

|---------------------------------------------------------------------------------|-----|

| Table. 3. 2. Performance summery npn and npn pnp THAs                           | 56  |

| Table 3. 3 Comparison with published Si/SiGe high speed THAs in SiGe technology | 57  |

| Table 3.4. Summary of measurement results                                       | 62  |

| Table 5.1. Summarized simulation results for 8-bit 20GHz DAC                    | 111 |

| Table 5.2. Summary of measurement results                                       | 114 |

| Table 5.3. Comparison with published Si/SiGe high speed DACs                    | 114 |

# **Chapter 1 Introduction**

#### 1.1. Motivation

Wireless communications have been the driving force in analog electronics development during the last decades. As the end products are produced for every-day use, the price, size, and weight of the devices play a large part in determining their design. Cost reduction and miniaturization require higher integration levels. Reasons for a high level of integration are increased reliability and product security.

In Fig.1.1 the requirements of data converters for different applications are plotted. Very high accuracy data converters are used in the slow instrumentation purposes, whereas the main applications of data converters are dominated by the communication systems. Wireless communication standards, such as Universal Mobile Telecommunication System (UMTS), Wireless Local Area Network (WLAN), Wireless Local Loop (WLL) or Local Multipoint Distribution Services (LMDS), are evolving towards higher data rates, thus allowing more services to be provided. In addition to that in communication radios, the analog digital interfaces are pushed towards the antenna as signal processing can more conveniently be done in digital domain. Currently almost all data converter vendors are providing analog to digital converter (ADC) or digital to analog converter (DAC) based on CMOS solutions with sampling rates at 1GHz and above. In some upcoming applications e.g. satellite or radar communication systems basestation applications with low to medium resolution data converters and multi-GHz sampling rate are going to be used. Such data converters are also very useful for broadband measuring instruments such as sampling oscilloscopes or arbitrary signal generators.

The state-of-the-art CMOS technology falls short to meet such stringent requirement for the data converters, where the SiGe BiCMOS technology quintessentially has an edge. While high-speed requirements can be fulfilled with the faster HBT devices, low-speed blocks can be implemented with CMOS devices. In this work the design aspects of high-speed data converts in 0.25µm SiGe BiCMOS technology are discussed. The main goals of this work are firstly, to investigate the dominating error sources in the data converter which restrict their performance, secondly to develop techniques to cope with those problems. Finally, to come

up with a set of data converter components which can be used as standalone systems as well as the building blocks for the complex ADC or DAC.

Fig. 1.1. Requirements of data converters for different applications

#### 1.2. Research Contribution

In section 1.1 it is discussed that the upcoming applications require multi-GHz of sampling rate data converters with low to medium resolution. In the thesis, an attempt has been made to develop some of the key components of ADC and DAC which can be used as a standalone system and as sub-blocks to build up complex high-speed, high accuracy data converters.

In the context of ADC design, the front-end track and hold amplifier (THA) comes as the bottleneck for the full system. This is because of the fact that any error introduced in this stage cannot be corrected by post processing the sampled analog signal. In this work an attempt has been made to improve the performances of the THA so that the tough requirements of the quantizer block can be relaxed. Two different kinds of THAs are implemented and measured successfully. In both the THAs, different techniques are used to enhance the input range up to 2Vpp differential at the sampling rate of 10GHz. To accomplish this requirement, the input buffer of the THAs are optimized. For the first time a cascode input buffer is used in the open loop THA design, while in another variant of THA a new complementary npn and pnp emitter follower is used. According to the authors knowledge these THAs are the only published THAs which can work with 2Vpp input signal and achieve an accuracy of more than 6.5-bit at a sampling rate of 10GHz.

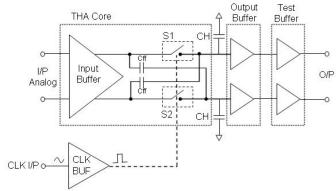

A new double sampled technique is proposed for the open loop THA architectures which can be instrumental to double the sampling speed of the THA with a little overhead of power dissipation compared to conventional open loop THAs. A novel double sampling switch is proposed which will make the sampling process insensitive to the clock skew, that appears as the bottleneck for the double sampling THAs and restricts the resolution.

With the advent of modern wireless communication systems different direct signal synthesis techniques are emerging as very popular. In this kind of systems the front-end DAC comes as the crucial component. The DAC should have low power dissipation and the resolution ranges from 4-12-bits. In this work an attempt has been made to design current steering DACs with a resolution of 4-8-bits and a sampling frequency ranging from 20GHz-30GHz. The 4-bit DAC is implemented with a weighted resistive ladder network. A novel binary weighted resistive ladder network is proposed. The 4-bit DAC is found to be functional up to 30GHz which shows the second best performance in terms of sampling speed for published SiGe high-speed DACs.

An 8-bit segmented current steering DAC has already been designed, where the 4-bit 30GHz DAC is used as the LSB sub-DAC. The MSB sub-DAC is implemented with conventional unary weighted DAC architecture. In the context of high-speed DAC design the binary to thermometer decoder comes as the design bottleneck in terms of speed and power. In this unary sub-DAC design a novel thermometer decoder is proposed which is mainly based on an HBT ROM structure. In simulation the 8-bit DAC shows an accuracy of 7.83 effective number of bits (ENOB) with 9GHz of single tone input sinusoidal and a sampling rate of 20GHz.

## 1.3. Organization of Thesis

In chapter 2 a brief review on different ADC architectures particularly suitable for high-speed applications are presented. Different static and dynamic parameters for ADCs are defined. A general trend of ADC performance improvement with time is discussed. Finally the advantages and disadvantages of different ADC architectures are critically analyzed.

In chapter 3 the design techniques for high-speed open loop THAs are presented. After a brief review of the most commonly used THA architectures the design methods of two different THAs with optimized high input swing are described. A new open loop double sampling THA architecture is presented to enhance the sampling speed of the THA. Finally the tested results of the implemented THAs are presented.

The design of a high-speed comparator is also described in chapter 3. Different common error sources of open loop comparators are analyzed. The design of a conventional open loop comparator is presented. Finally the measurement results of a 20GHz comparator are presented.

An architecture review of current steering DACs is presented in chapter 4. Different error sources associated with the current steering DAC are analyzed. The state-of-the-art techniques to enhance the static and dynamic performances are presented. But these techniques are found to be not very useful for the multi-GHz DAC design. Thus, a novel non-binary weighted DAC based current cell calibration technique is proposed which can be useful to enhance the performance of high-speed DACs.

The designs of a 4-bit as well as an 8-bit current steering DAC have been presented in chapter 5. In the 4-bit DAC implementation a novel resistive weighting network in used. The design of a 20GHz 8-Bit segmented current steering DAC is presented afterwards. A new HBT ROM based thermometer decoder architecture is proposed which could be instrumental to enhance the speed and latency requirements for high-speed unary weighted DACs. For the 8-bit DAC simulation results are presented. Finally measurement results of the 4-bit DAC and a brief comparison with the state-of-the-art multi-GHz SiGe DAC are presented.

Finally the conclusions are drawn in chapter 6. This chapter also includes the future scope of the research work.

# Chapter 2

# **Analog to Digital Converter**

great challenge for silicon-germanium (SiGe) technology.

2.1. Introduction

# The requirement of high-speed, high-resolution analog to digital converters (ADC) is directly dictated by the evolution of modern communication systems. Ultra-wideband and radar communication systems are going to use ADCs with a sampling rate of few gigahertz to few tens of gigahertz. Designing such high-speed ADCs with moderate resolution becomes a

The basic analog to digital conversion can be considered as summation of two main operations (see Fig. 2.1). The first operation is called sampling. In this process the continuous time analog signal is converted into a discrete time analog signal. After this, the sampled analog signal is approximated to some predefined discrete amplitudes. This process is known as quantization. Each of the discrete analog amplitudes is then assigned to a specific digital code.

Fig. 2.1. Analog to digital conversion

In this chapter the basic quantization process is discussed in section 2.2. The static and dynamic errors of the analog to digital converter are defined in section 2.3. A present scenario and design trends of ADC design are presented in section 2.4. The architectures of different ADCs which can be used for gigahertz range sampling rate are presented in section 2.5. Finally the conclusions are drawn in section 2.6.

# 2.2. Quantization

The quantization process can be defined as mapping of time discrete analog signal into a finite set of digital words. As mentioned in the earlier section the basic A/D conversion process can be characterized as sampling the continuous signal in the time domain and then assigning the time discrete amplitudes into some digital code words, i.e. quantization. In spite of this sometimes the terms A/D conversion and quantization are used synonymously. A quantizer can be uniquely described by its transfer function or quantization characteristic, which indicates the discrete outputs as a function of the continuous input signal. The quantization characteristic therefore contains two sets of information: the first includes the digital codes associated with each output state, and the second includes the threshold levels which are the set of input amplitudes at which the quantizer transits from one output code to the next (Fig. 2.2). Various kind of digital coding can be used. Those are namely natural binary, sign plus magnitude, offset binary, one's complement, two's complement, binary coded decimal (BCD), and Gray code; each of the coding scheme has its own advantages in particular application.

In a quantizer, if there exists M threshold levels, that will generate (M+1) output digital code words. The threshold levels are denoted by  $T_k$ , where k ranges from 1 to M. Quantization step (Q) is defined as,

$$Q = T_{k+1} - T_k (2.1)$$

Fig. 2.2 Transfer characteristics of (a) uniform, (b) nonuniform quantization The ideal threshold levels are denoted by  $T_k^*$ . This ideal threshold levels can be spread over the abscissa of the quantizer transfer function. As shown in Fig. 2.2(a) the quantization steps are equal. This kind of quantization is known as uniform quantization otherwise it is termed as nonuniform quantization as shown in Fig. 2.2(b). The optimum performance results

in when the threshold locations matche with the probability distribution function of the incoming signal. However, in the absence of a priori knowledge of the input signal statistics, uniform quantization outperforms other arrangements. Therefore, uniform quantizers are most commonly used.

Depending upon the location of origin the quantization process can be classified into two categories. In bipolar quantization the ideal threshold levels are spread symmetrically about the origin (Fig. 2.3a). On the contrary in unipolar quantization the threshold levels are placed either positive or negative direction with respect to the origin. In Fig. 2.3b an example of unipolar quantization presented.

The Full-Scale Range, FSR, of a uniform quantizer represents that portion of the transfer function domain spanned by all equal length intervals (M) between adjacent ideal thresholds. Thus the quantization step (Q) can be alternatively defined as,

$$Q = \frac{FSR}{M} \tag{2.2}$$

Fig. 2.3. Transfer function of (a) bipolar (b) unipolar quantizatioin

In Fig. 2.4 two of the most commonly used quantization transfer characteristics are presented. Those are known as mid-tread and mid-riser characteristics. For an N-bit bipolar or unipolar quantizer, mid-tread quantizer has  $M=2^N-1$  no. of quantization levels with a quantization level at origin in case of bipolar quantization or at FSR/2 for unipolar quantization. Mid-riser characteristics  $M=2^N$  no. of quantization levels with a threshold value at the origin for bipolar quantization (FSR/2 for unipolar quantization.). Thus practically for an N bit quantizer (M-1) threshold levels are required. In mid-riser characteristics  $M=2^N$  quantization levels directly mapped into  $2^N$  binary codes. For this reason the mid-riser

quantizer is more popular than the mid-read counterpart. In fig. 2.4b an ideal mid-riser transfer characteristic is shown for 3-bit quantizer. The quantization step Q for mid-riser quantizer is given by,

$$Q = \frac{FSR}{2^N} \tag{2.3}$$

Fig. 2.4. (a) Mid-tread, (b) Mid-riser quantizer

#### 2.3.1. Static Errors in ADC

Due to the imperfection in fabrication the real quantization transfer function deviates from the ideal one. The actual thresholds  $(T_k)$  have some error with respect to their ideal placements  $(T_k^*)$ . Such non-idealities are known as static or DC errors and can be defined in several ways. The definitions of static errors of quantizer are indicated in the transfer curve of a converter. As shown Fig. 2.5(a) the error which causes an equal amount of shift in all the thresholds is known as offset error of the quantizer. Non-ideality which causes a same amount of step size error for all of the quantization steps is known as gain error. The gain error is shown in Fig. 2.5b.

The most important measures of static error of quantizers are indicated by integral nonlinearity (INL) and differential nonlinearity (DNL). These properties actually indicate the accuracy of a converter and include the errors of quantization, nonlinearities, short-term drift offset and noise. Integral nonlinearity (INL), sometimes called relative accuracy, is defined as

the deviation of the output code of a converter from its ideal counterpart excluding a possible offset error. The nonlinearity should not deviate more than  $\pm 1/2$  LSB from the ideal transfer curve. This INL boundary implies a monotonic behavior of the converter. Monotonicity of an analog-to-digital converter means that no missing codes can occur [1].

Fig. 2.5 (a) Offset error, (b) Gain error, (c) Threshold errors (INL & DNL), (d) Missing codes

Differential nonlinearity (DNL) error gives the difference between two adjacent threshold values ( $T_k$ ,  $T_{k-1}$ ) compared to the quantization step (Q) of a converter generated by transitions between adjacent pairs of digital code numbers ( $D_k$ ) over the whole range of the converter. The DNL of ADC output  $D_k$  can be written in terms of LSB as,

$$DNL(D_k) = \frac{T_k - T_{k-1} - Q}{Q}$$

(2.4)

There is a direct connection between the INL and DNL. The INL for output code  $D_k$  can be obtained by summing the DNL until code k,

$$INL(D_k) = \sum_{i=1}^{k} DNL(D_k)$$

(2.5)

#### 2.3.2. Dynamic Errors in ADC

Dynamic performance parameters include information about noise, dynamic linearity, distortion, settling time errors, and sampling time uncertainty of an ADC. It should be noted that all the measures following are both frequency and signal amplitude dependent. Furthermore, unless otherwise specified, they are obtained with a full-scale input signal.

# 2.3.2.1. Signal-to-Noise ratio (SNR)

The quantization process introduces an irreversible error, which sets the limit for the dynamic range of an A/D converter. Assuming that the quantization error of an ADC is evenly distributed over any quantization level, the power of the generated noise in a  $1\Omega$  is [1] given by,

$$e^2 = \frac{Q^2}{12} \tag{2.6}$$

where,  $e^2$  is the quantization noise power and Q is the quantization step. If a single-tone sine wave signal with maximum amplitude is adopted for a full scale range (FSR) of a quantizer with a large number of bits (N $\geq$ 5), the signal power is given by,

$$S_p = \frac{FSR^2}{8} \tag{2.7}$$

Combining Eq. 2.3 and Eq. 2.7 and substituting in Eq. 2.6 the signal-to-noise ratio (SNR) for a single-tone sinusoidal signal can be obtained to be,

$$SNR = 2^{2N} \bullet \frac{3}{2} \tag{2.8}$$

SNR can be expressed in dB by the following equation,

$$SNR = (6.02N + 1.76) \, dB$$

(2.9)

When determining the SNR, the ratio between the frequency of the sine wave and the sampling frequency should be irrational. If the input signal deviates from the sine wave, the constant term, which depends on the amplitude RMS value of the waveform, differs from 1.76 dB. Eq. 2.9 indicates that each additional bit, N, gives an enhancement of 6.02 dB to the SNR. If oversampling is used, which means that the sample rate  $f_s$  is much larger than the

signal bandwidth  $f_{sig}$ , the quantization noise is averaged over a larger bandwidth and the signal-to-noise ratio becomes larger, written as,

$$SNR = 2^{N} \sqrt{\frac{3}{2}} \cdot \sqrt{OSR} = (6.02N + 1.76 + 10 \log(OSR)) \, dB$$

(2.10)

where, the oversampling ratio is given by OSR,

$$ORS = \frac{f_s}{2 \bullet f_{sig}} \tag{2.11}$$

In the Nyquist rate A/D converters, the signal bandwidth is normally equal to  $f_s = 2 \bullet f_{sig}$  resulting in an OSR equal to one, while Eq. 2.10 suggests that the signal-to-noise ratio increases by 3 dB per octave of oversampling.

#### 2.3.2.2. Total Harmonic Distortion (THD)

Any nonlinearity in an ADC creates harmonic distortion. In differential implementations, the even order distortion components are ideally canceled. However, the cancellation is not perfect if any mismatch or asymmetry is present. The total harmonic distortion (THD) describes the degradation of the signal-to-distortion ratio caused by the harmonic distortion. By definition, it can be expressed as an absolute value with,

$$THD = \frac{\sqrt{\sum_{j=2}^{(H+1)} V^2(j \bullet f_{sig})}}{V(f_{sig})}$$

(2.12)

where, H is no. of harmonics to be considered and  $V(f_{sig})$ ,  $V(j \bullet f_{sig})$  are the amplitudes of fundamental and j<sup>th</sup> harmonic respectively.

# 2.3.2.3. Signal to Noise and Distortion Ratio (SNDR)

A more realistic figure of merit for an ADC is the signal-to-noise and distortion ratio (SNDR), which is the ratio of the signal energy to the total error energy including all spurs and harmonics. SNDR is determined by employing the sine-fit test, in which a sinusoidal signal is fitted to a measured data and the errors between the ideal and real signal are integrated to get the total power of noise and distortion [2],[3]. If all tones and spurs other than the harmonic distortion are considered as noise, the signal-to-noise ratio can be obtained from the SNDR by subtracting the total harmonic distortion from it

$$SNR_{real} = SNDR - THD (2.13)$$

where SNDR and THD are given in absolute values.

# 2.3.2.4. Spurious Free Dynamic Range (SFDR)

In wireless telecommunication applications, large oversampling ratios are often used and the spectral purity of the A/D converter is important. For such situations, a proper specification is the ratio between the powers of the signal component and the largest spurious component within a certain frequency band, called spurious free dynamic range (SFDR). The SFDR is usually expressed in dBc as,

$$SFDR(dBc) = 10.log\left(\frac{V^2(f_{sig})}{V^2(f_{spur})}\right)$$

(2.14)

where  $V(f_{sig})$  is the amplitude of the fundamental sinusoidal input and  $V(f_{spur})$  the amplitude of the largest spurious. For an exact SFDR definition, the power level of the fundamental signal relative to the full-scale must also be given. Normally the limiting factor of the SFDR in ADCs is harmonic distortion. In most situations, the SFDR should be larger than the signal-to-noise ratio of the converter [4].

## 2.3.2.5. Effective Number of Bits (ENOB)

In ideal ADCs, the maximum analog bandwidth is equal to half the sampling bandwidth, according to the Nyquist theorem. The effective resolution bandwidth (ERB) is defined as the maximum analog frequency for which the signal-to-noise ratio of the system is decreased by 3 dB or 1/2 LSB with respect to the theoretical value. For a single-tone full-scale sinusoidal test signal with the maximum frequency within the ERB the effective number of bits (ENOB) can be defined according to the following equation,

$$ENOB = \frac{SNDR(dB) - 1.76}{6.02} \tag{2.15}$$

where, SNDR is taken as the figure of merit to calculate the ENOB. Although according to the requirements of different applications the ENOB can also be estimated by considering either of SNR, THD or SFDR as the measure of linearity.

## 2.3.2.6. Dynamic Range

Dynamic range (DR) is the input power range for which the signal-to-noise ratio of the ADC is greater than 0 dB. The dynamic range can be obtained by measuring the SNR as a function of the input power.

# 2.4. Performance Analysis and Present Trends in ADC Design

In the previous section the definitions of different static and dynamic parameters of ADC are presented. In this section an attempt has been made to analyze the ADC performances according those parameters. Although a comprehenive performance can be presented by the following set of parameters: stated resolution, sampling rate, SNR, SFDR and the power dissipation.

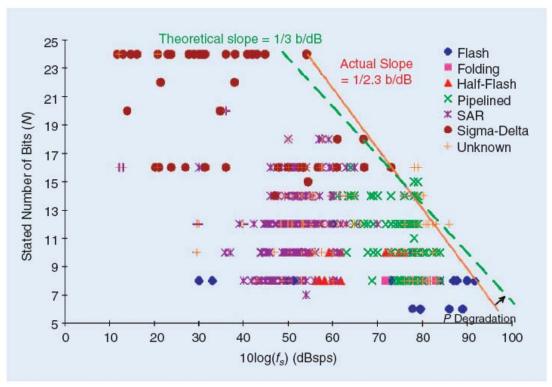

The pioneering work regarding the facts and trends of ADCs in terms of different dynamic performances was presented in [5] by R.H. Walden. The work has two main aspects; different physical processes which defines the upper or lower limits of ADC and the performance improvement in terms of time of ADC development. It revels a very interesting relation between the sampling rate and ENOB: resolution is decreased by 1-bit with doubling the sampling rate.

To analyze the performance of the ADC, SNR bits are taken as a figure of merit. The SNR bits are defined as follows,

$$SNR_{bits} = \frac{SNR(dB) - 1.76}{6.02}$$

(2.16)

It is been observed that the difference between the stated resolution of ADC and the SNR bits is about 1.5-bits. This is attributed to the nonlinearity and noise sources associated with different components of the ADC.

In the Fig. 2.6 the performance of different published and commercially available ADCs in terms of sampling frequency and the SNR bits are presented with the updated entries up to the year of 2005. Along with that, it also depicts the different physical horizons which dictate the limits for the ADC dynamic performances. The main parameters which influence the dynamic performances are thermal noise floor, aperture uncertainty in the sampling process and the comparator ambiguity or the comparator metastability. The last two effects will be discussed in details in chapter 3. The relation between these error sources and the maximum achievable SNR bits are derived in [5].

Fig. 2.6. Performance limits of ADC due to different physical phenomena [5]

The relation between the input referred thermal noise and the maximum attainable resolution in terms of SNR bits can be expressed as follows,

$$N_{thermal} = \log_2 \left( \frac{V_{FS}^2}{6kTR_{eff} f_{sample}} \right)^{1/2} - 1$$

(2.17)

Where the N<sub>thermal</sub> represents the maximum SNR bits which can be achieved for a given equivalent input referred noise resistance (R<sub>eff</sub>).  $V_{FS}$  is the full scale voltage of the ADC and  $f_{sample}$  is the sampling rate. T = Temperature in Kelvin. Boltzmann's constant,  $k = 1.38658*10^{-23} \,\text{J/K}$ .

Assuming that the rms aperture uncertainty  $\tau_a$  is known. Then the upper limit of the SNR bits (N<sub>aperture</sub>) for the given  $\tau_a$  can be presented as follows,

$$N_{aperture} = \log_2 \left( \frac{2}{\sqrt{3}\pi f_{sample} \tau_a} \right) - 1 \tag{2.18}$$

The relation between the SNR bits and the comparator ambiguity can expressed as,

$$N_{ambiguity} = \frac{\pi f_T}{6.93 f_{sample}} - 1 \tag{2.19}$$

Eq. 2.19 relates the transit frequency  $(f_T)$  of devices in a particular technology with the maximum resolution that can be achieved  $(B_{ambiguity})$  for the sampling rate of  $f_{sample}$ .

The ultimate limit of the ADC resolution and sampling rate is estimated from Heisenberg uncertainty principle. This defines the least amount of resolvable energy corresponding to the ½ of LSB which can be detected in a given time interval i.e. the half of the sampling period.

This limit is almost four orders of magnitude higher than the state of the art ADC reported as of now.

The performance envelop of ADC is shifting but in a much lower rate than the technology evolved. It is only 1.5 bits in every 8 years as indicated in [5]. Although in [5] ADCs up to 1997 have been considered, but the present scenario remains almost same. The main reason behind that could be the traditional approaches to solve the analog problems like device mismatch in the analog domain. Digital post processing may be helpful for this sort of problem but increases the complexity of the full system.

Fig. 2.7. Performance envelop improvement of ADC [5]

The performances of different ADC architectures are presented in [6]. It shows the highest resolution is achieved in sigma delta architectures. But it uses the large amount of oversampling ratio. The optimum performance in terms of sampling rate, resolution and power can be obtained by using pipeline architecture. But this is very difficult to implement for gigahertz range sampling regime. Flash architecture is the fastest and comes as the obvious choice for higher sampling rate. Higher power dissipation is the main concern with this architecture. A compromise can be found in the folding architecture where the no. of comparators is reduced by using the folding mechanism. In the next section the architectures which can be used for gigahertz range application are described along with the advantages and disadvantages are critically analyzed.

Fig. 2.8. Performance of different ADC architectures [6]

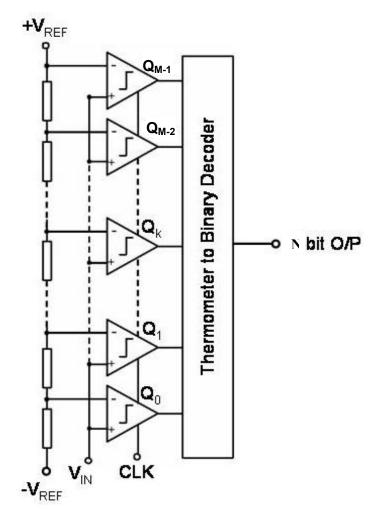

#### **2.5.1. Flash ADC**

The flash type ADC is the fastest among the all ADC architectures. A simplified block diagram of this architecture is presented in Fig. 2.9. For a N-bit ADC ( $2^N$ -1) number of quantization levels are to be resolved. In this architecture the quantization process is performed by using the same number of comparators (M) as the quantization levels. Thus the maximum amount of the parallelism is employed in this architecture. The reference voltages for the comparators are generated through a resistive ladder. The two ends of this reference ladder are connected with the positive ( $+V_{REF}$ ) and the negative ( $-V_{REF}$ ) references, which determine the full-scale voltage of the ADC. For a given input voltage, comparator outputs from  $Q_0$  to  $Q_K$  are logic high and rest of the comparator outputs are logic low. This output pattern is commonly known as thermometer code. The thermometer code is then converted to the binary output by a thermometer to binary encoder.

As the input signal is directly connected to the all comparators, the sampling speed is very fast for this architecture [7],[8]. The speed of the comparators generally limits this sampling rate. The front end sample and hold block can be avoided in this architecture as the sampling operation is directly accomplished by the comparators. Usually the latency is very low for

this kind of architecture typically one to two clock cycles, which makes it useful for feedback applications.

Fig. 2.9. Flash ADC architecture

Certainly the main disadvantage with this architecture is the huge no. of comparators. This number increases exponentially with increasing resolution (N) so does the area and power. Thus in practice this architecture is merely used for resolution more than 8-bits. The large no. of comparators spread over the whole area of a monolithic chip causes higher mismatch among the devices, thus the comparator offsets go high which also restrict the resolution of the full ADC. To overcome this problem large devices can be used but that causes higher capacitive load for the input and reduces the input bandwidth. An alternative solution can be found in the auto-zero comparators [9],[10] where the comparator itself comes with an offset correction mechanism. Generally these comparators have phases. In reset phase the input offset is corrected and in evaluatory phase the real comparison is done.

This technique is popular in CMOS technology but cannot be useful for sampling speed in gigahertz range where the bipolar comparators are mainly used.

A well-known technique to improve the static nonlinearity i.e. INL and DNL is to use averaging [11],[12]. In this technique each comparator is preceded by a preamplifier, whose output is coupled to the outputs of the adjacent preamplifiers via a resistive averaging network. As a result, the input signal for a comparator is not produced by its own preamplifier alone, but it is a weighted average of the outputs of the preamplifiers in a small neighborhood. Comparator offset is also reduced by the preamplifier gain and the preamplifier offset is an average of the random offsets of all the amplifiers participating in the averaging process.

Considering all the pros and cons, this architecture is rarely used in high resolution ADCs. The main application is restricted mainly to low resolution disk drive read channel, local area network interface etc. with sampling speed of few hundreds of megahertz. In [13],[14] CMOS flash converters are reported which can work in gigahertz range. The highest sampling speed is reported in [8], where bipolar devices are used for the implementation. Special attention is needed to reduce the clock jitter to enhance the resolution. May be a front end sample and hold can be used to relax the stringent clock jitter requirement in high end applications.

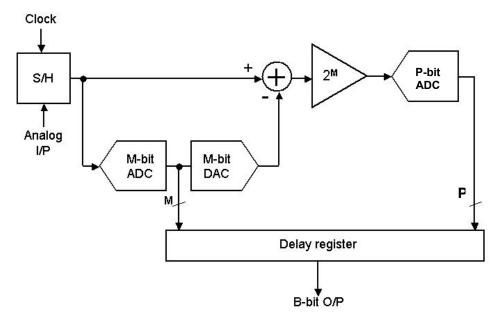

### 2.5.2. Sub-ranging or Two step ADC

An improvement in the flash architecture can be found sub-ranging or two step ADC. As the name implies the quantization process is performed in two steps. A N-bit ADC is implemented as a combination of two sub ADCs, an M-bit coarse converter which is followed by P-bit fine converter where,

$$N = M + P \tag{2.20}$$

These sub ADCs are implemented with flash architecture. Thus the total no. of comparators is reduced from  $(2^N-1)$  to  $(2^M+2^P-2)$ . A front-end sample and hold is required to ensure that both of the sub-ADCs are working with the same sampled analog input. After the coarse analog to digital conversion the digital output of the coarse converter is converted back into analog signal by an M-bit sub DAC. The output of the sub-DAC is subtracted from the held analog signal of the sample and held to generate the residual voltage. This residual

voltage is amplified by a factor of  $2^M$  to match the full-scale voltage of the fine ADC with the coarse ADC.

Fig. 2.10. Block diagram of sub-ranging ADC

One of the major drawbacks of this architecture is the non-ideality associated with the comparators. Ideally all of the comparator should have N-bit of accuracy. If the error exceeds the specified tolerance in the coarse converter, an overflow or underflow occurs at the output of the fine converter. To cope with this problem generally redundancy is used in either of the coarse or fine converter. The redundant sign digit (RSD) algorithm [15] similar to the pipeline architecture can be used to relax the comparator accuracy. A vivid analysis of the different error sources for RSD technique is done in [16]. It shows although the comparator accuracy can be relaxed but the accuracy requirement for the sub-DAC remains the same.

In the context of high-speed gigahertz range ADC design this architecture may be useful to reduce the no. of comparators and hence the power dissipation. But the complex residue generation process could appear as the bottleneck. Within a single hold period of the sample and hold three operations (coarse conversion, residue generation and fine conversion) are to be performed which imposes a tough timing constraint. This can be relaxed with inserting another sample and hold in front of the fine converter. But this will introduce another source of error and finally reduce the accuracy of the full converter.

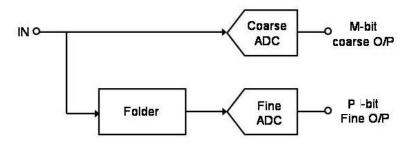

#### 2.5.3. Folding ADC

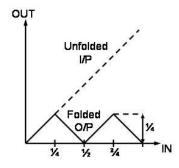

Fig. 2.11. represents a simplified block diagram of folding N-bit ADC. In this architecture the input signal is folded upward or downward after a specified interval as shown in Fig. 2. 12. In this particular example it is ¼ of the full-scale. The output is also same as the input interval. Thus reducing the no. of comparator by the same amount i.e. ¼ compared to the full flash architecture. The folding operation is accomplished by the folder or folding amplifier (Fig. 2. 11). In practice the folding amplifier has a specified amount of gain (in the present example 4) to generate the folding signal with the same full scale rather than the fraction of it. Hence the accuracy requirement of the comparators in the fine ADC is relaxed.

Fig. 2.11. Simplified block diagram of Folding ADC

The concept of folding is similar to the sub-ranging ADC. But here the prior knowledge of sub-range is not required. As a result of it the coarse and fine conversions can be done concurrently and the front-end sample and hold can be avoided which leads to high sampling rate. The output of the coarse ADC is finally used to decode the fine ADC output.

Fig. 2. 12. Principle of folding

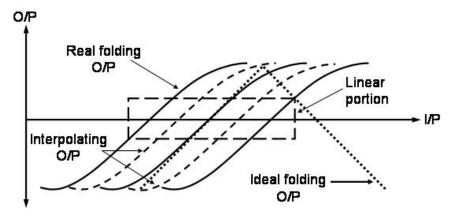

In practice, realizing a transfer function of folding amplifier with the triangle wave shape is very difficult, since especially the sharp corners tend to become smoothed due to the limited bandwidth. This problem can be solved by producing several versions of the folded signal; each shifted a different amount of input voltage in the x-direction, and using only the

linear part of each curve. This is illustrated in Fig. 2. 13. where five nonlinear curves are used instead of one linear one. The linear portion around the zero crossings of each curve is utilized for comparison. All the comparators responsible for detecting the signal in this range are connected to the circuit producing that particular curve. Often, the number of curves is increased up to the point where they equal the number of comparators. As a result, there is only one comparator per curve and it only has to detect the signal zero crossing, making the linearity of the curve unimportant.

Fig. 2. 13. Folding signal generation

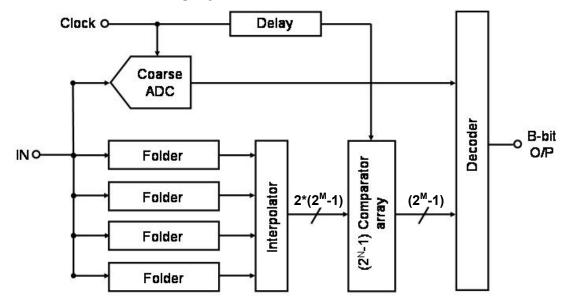

The folding amplifier is a complex block, but a large no. of folding block is not used. Instead interpolation technique is used. The interpolation curves are achieved by shifting the real folding signals in the y-direction (shown by the dashed lines in Fig. 2. 13). The interpolating signals do not represent the actual folding signal rather it represents the valid information only in the vicinity of the zero crossing. The main advantage of this technique is the fact that the process can be implemented by simple resistive ladders. Thus ideally a large no. of interpolating signals can be used without increasing the complexity. A block diagram of the folding ADC used in practical applications is shown in Fig. 2. 14. In this example four folding amplifiers are used. The coarse ADC determines the sub-range for the folding amplifiers. M-bits are resolved from the fine ADC. The folding amplifiers accomplished with the resistive interpolators define the zero crossings for the each comparator in the fine ADC. The outputs of the coarse and fine ADCs are fed to a decoder to generate N-bit output.

A possible implementation of the folding amplifier with bipolar devices is presented in [17]. The folding amplifiers are implemented with open loop parallel emitter couple pairs. As a result it becomes suitable for the high-speed applications. High  $g_m$  of the bipolar transistors guarantees the higher linearity of the folding amplifiers. The main disadvantage of the folding amplifier is the fact that the output frequency of the block is the product of the input

frequency and the no. of folding used (see Fig. 2. 12). Sometimes this comes as the decisive factor for the input bandwidth. This problem can be bypassed by using a front end sample and hold. The resolution of this architecture is limited to 8-10 bits. In [17] an 8-bit resolution is achieved with 2GHz of sampling rate.

Fig. 2. 14. Folding interpolating ADC Architecture

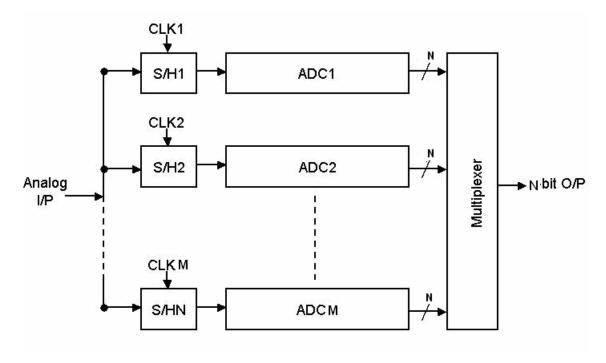

#### 2.5.4. Time Interleaved ADC

A simplified block diagram of the time interleaved ADC is presented in Fig. 2. 15. In this architecture, M no. of ADCs are used in parallel (known as channel) to enhance the sampling rate to M times of an individual ADC. Each ADC works on every M<sup>th</sup> sample value. At the output a multiplexer is used to select the output of the proper ADC to generate a single bit stream at the full sampling rate.

Up to a certain resolution the component mismatches are within the tolerance. But with increasing resolution severe problem with static characteristics occurs in this architecture due to the gain and offset mismatch of the different channels assuming that each channel works with the same linearity. The offset error can be overcome easily by using mixed mode [18] or full digital calibration [19] technique. Calibration of gain requires more complex circuitry [20].

Certainly the main problem in the dynamic behavior occurs due to the clock skew for different ADC channels. This can happen due to the clock generation circuitry or the possible propagation delay mismatch among the different sampling circuitry. One of the favorable solutions would be to use a front-end sample and hold working with the full

sampling rate. But in high frequency sampling regime, with the increasing no. of parallel channels it becomes very difficult to drive the large capacitive load. The clock skew problem can also be solved by digital post-processing. But it requires an accurate measurement of the clock skew in the sub-pico second range.

Fig. 2. 15. Block diagram of time interleaved ADC

Until now the best performance using this architecture is reported in [21] which in fact represents the best performance in terms of sampling speed and resolution in SiGe technology. In that work eighty parallel current mode pipeline ADCs were used. A complex DLL based clock generation scheme is employed to achieve lower clock skew among the blocks. An on-chip 1MB memory is used to store the output of the parallel channels and the final digital output is achieved after performing digital post processing on this data. Thus for real time application it is not suitable.

#### 2.6. Conclusions

In this chapter the basic quantization process is described. The mid-riser quantizers are found to be most commonly used quantization method. The static and dynamic errors associated with the quantization process are defined. The physical error sources which define the limit for the ADCs in terms of resolution and sampling rate are identified as the input

referred thermal noise, the aperture uncertainty in the sampling process and the comparator ambiguity.

Different ADC architectures which can be used for gigahertz range sampling are discussed. The flash type architecture is found to be the fastest but power dissipation is highest in this architecture. An alternative can be found in the time interleaved ADCs. In fact the best performance is achieved by using this architecture. But it comes with a large amount of digital post processing overhead which makes it unattractive for real time applications. The compromise in resolution, speed and power can be found in folding architecture where the coarse and fine conversion can be done concurrently. But the bandwidth limitation of the folding amplifier may come as a bottleneck. This can be overcome by front end sample and hold.

# **Chapter 3 Design of Multi-GHz ADC Components**

#### 3. 1. Introduction

In this chapter the design of two main ADC components are presented. These components can be used as standalone systems and as well as the building blocks for a complete ADC system. In the first part of this chapter the design of the track and hold amplifier (THA) is presented. For any high-speed high resolution ADC the front end THA comes as the most critical component. The error introduced in this block cannot be suppressed by post processing of the sampled signal.

The main operation of THA can be divided into two phases. In the first phase THA follows the input signal. Then it goes to the next phase in which it holds the sampled value for a finite time. In general these two phases have the same time intervals.

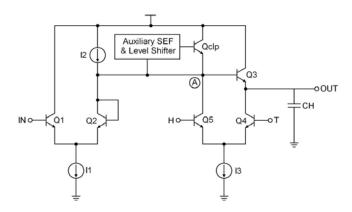

For high speed application open loop architectures are commonly used. Unlike the closed loop THAs, the global feedback from the input to the output is not present in this kind of topology. As a result of it the linearity is not very high. The nonlinearity increases with the increase in the input voltage range. On the other hand the quantization process can be efficiently done if the input range of the THA is high. In some of the applications almost 2Vpp differential input is required for the quantization process [17]. In modern state-of-the-art SiGe technologies with collector-emitter breakdown voltage (BV<sub>CEO</sub>) around 2V, such a high swing is difficult to obtain due to the nonlinearity inherent to all stages operating close to their swing limit. In this chapter two different open loop THA architectures are proposed which are capable to work with high input swing at the sampling rate of 10GS/s.

In the second part of this chapter the design of a 20GS/s comparator is presented. The comparator is implemented with the open loop architecture. In measurement it shows 5.8-bit of accuracy with 70mW of power dissipation.

The chapter is organized as follows, in section 3. 2 the definitions different parameters of THA performance matrices have been presented. Brief reviews of the most commonly used

THA architectures are presented in section 3.3. The design technique of two different THAs for high input swing is described in section 3. 4. In section 3. 5 a new architecture double sampling THA architecture is presented. The experimental results of the implemented THAs are presented in section 3. 6. In section 3.7 design of an open loop comparator is presented which is followed by the measurement results in section 3.8. Finally conclusions are drawn in section 3.9.

#### 3. 2. Performance Matrices for Track and Hold Amplifier

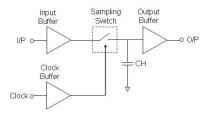

The basic track and hold operation is divided into two phases. In the first phase THA works as a unity gain amplifier and follows the input signal. In the second phase the THA holds the track voltage. A simplified functional block diagram of a THA is shown in Fig. 3.1. A unity gain input buffer is used to isolate the sampling circuit from the outer-world. The main track and hold function is accomplished by the sampling switch. This switch is controlled by a clock signal and the input analog signal is stored across the hold capacitor C<sub>H</sub>. Finally an output buffer is used to isolate the C<sub>H</sub> from the external load.

Fig. 3.1. Functional block diagram of THA

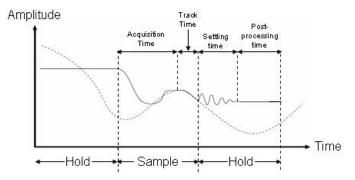

The performance of THA can be characterized by a number of parameters. The terminologies and definitions used to characterize THA vary with different manufactures. In this section mostly acceptable performance parameters are defined. As mentioned earlier in the track mode the THA works as a unity gain amplifier. Thus in this mode the THA is characterized by the same parameters like analog amplifier e.g. offset, gain, slew rate, bandwidth, nonlinearity, harmonic distortion and settling time. In Fig. 3.2 the terminologies related to THA timings in both the track and hold phases are depicted.

The acquisition time is the time interval, during which the THA must remain in the track mode to enable the circuit to accurately replicate the input signal, thereby ensuring that the subsequent hold mode output will lie within a specified error band of the input level that existed at the track-to-hold transition (after gain and offset effects have been removed). The

remaining time duration of the track mode exclusive of acquisition time is called the track time during which the THA output is a replica of its input.

The settling time is defined as the time duration between the beginning of track to hold mode transition and the time when THA output is settled down within a specified error band of the final hold value. The remaining time in the hold mode can be used for post processing e.g. analog signal processing, analog to digital conversion.

Fig. 3. 2. Track and Hold terminologies

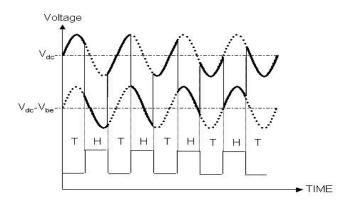

The track to hold transition determines many aspects of T/H performance. The delay time is the time elapsed from the execution of the external hold command until the internal track-to-hold transition actually begins. In practical circuits this switching occurs over a non-zero interval called the aperture time measured between initiation and completion of the track-to-hold transition. Practical circuits do not exhibit precisely the same time period for each sample. This random variation from sample to sample is caused by phase noise of the incoming clock signal and further exacerbated by electronic noise within the T/H itself. The standard deviation of the sample period is termed the aperture jitter and limits amplitude resolution in A/D conversion.

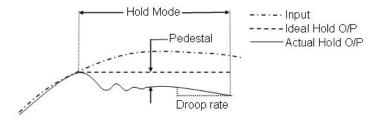

In Fig. 3.3 different error sources in the hold mode are being shown. During the transition from the track to hold mode an error in the hold voltage is introduced which is known as pedestal error. This error stems from the charge injection of the sampling switches.

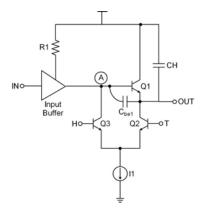

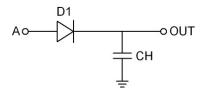

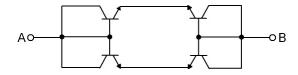

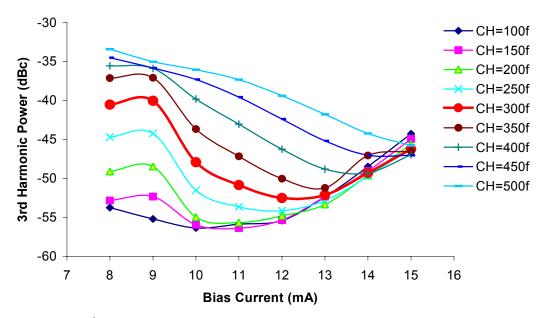

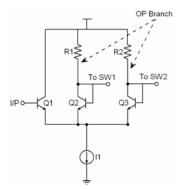

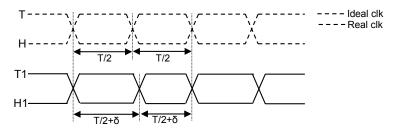

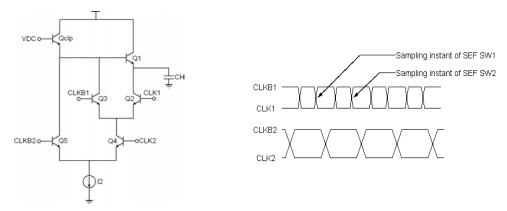

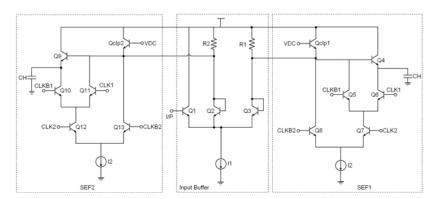

Fig. 3. 3. Hold mode characteristics