**Integrationstechniken für Feldeffekttransistoren

mit halbleitenden Nanopartikeln:

Einzel- und Multipartikel-Bauelemente**

Von der Fakultät für Elektrotechnik, Informatik und Mathematik

der Universität Paderborn

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften (Dr.-Ing.)

genehmigte Dissertation

von

Dipl.-Ing. Karsten Wolff

Erster Gutachter: Prof. Dr.-Ing. Ulrich Hilleringmann

Zweiter Gutachter: Prof. Dr.-Ing. John Thomas Horstmann

Tag der mündlichen Prüfung: 08.02.2011

Paderborn 2011

Diss. EIM-E/273

---

---

# Inhaltsverzeichnis

---

|                                                                               |           |

|-------------------------------------------------------------------------------|-----------|

| <b>Einleitung</b>                                                             | <b>1</b>  |

| <b>1 Grundlagen, Nanopartikel und deren Eigenschaften</b>                     | <b>5</b>  |

| 1.1 Ausgewählte physikalische Grundlagen . . . . .                            | 5         |

| 1.1.1 Raumladungszone . . . . .                                               | 5         |

| 1.1.2 Metall-Halbleiter-Grenzfläche . . . . .                                 | 6         |

| 1.1.3 Ladungsträgertransportmechanismen . . . . .                             | 12        |

| 1.2 Nanopartikel und deren Eigenschaften . . . . .                            | 15        |

| 1.2.1 Synthese . . . . .                                                      | 15        |

| 1.2.2 Dispergierprozess und Nanopartikeldispersionen . . . . .                | 19        |

| 1.2.3 Physikalische und elektrische Eigenschaften von Nanopartikeln . . . . . | 21        |

| <b>2 Transistoraufbau und -funktionsweise</b>                                 | <b>29</b> |

| 2.1 Dünnschichttransistoren . . . . .                                         | 29        |

| 2.2 Einzelpartikeltransistoren . . . . .                                      | 32        |

| 2.3 Funktionsweise . . . . .                                                  | 35        |

| 2.4 Parameterextraktion . . . . .                                             | 40        |

| <b>3 Integrationstechniken</b>                                                | <b>45</b> |

| 3.1 Abscheidungsdefinierte Nanostrukturierungstechnik . . . . .               | 45        |

| 3.2 Materialien der Opferschichten . . . . .                                  | 48        |

| 3.2.1 Fotolack AZ 5214E . . . . .                                             | 49        |

| 3.2.2 Fotolack AZ MiR 701 . . . . .                                           | 51        |

| 3.2.3 Schutzlack Bectron . . . . .                                            | 52        |

| 3.3 Prozesstechnik zum Kantenabscheideverfahren . . . . .                     | 55        |

| 3.3.1 Siliziumdioxid-PECVD mit reduzierter Prozesstemperatur . . . . .        | 55        |

| 3.3.2 Verfahren zur selektiven Entfernung des Nanospacers . . . . .           | 56        |

| 3.4 Abscheidung von Nanopartikeln . . . . .                                   | 60        |

| 3.4.1 Herstellung nanopartikulärer Schichten . . . . .                        | 60        |

| 3.4.2 Abscheidung von Einzelpartikeln . . . . .                               | 68        |

| <b>4 Feldeffekttransistoren mit Silizium-Nanopartikeln</b>                    | <b>73</b> |

| 4.1 Dünnschichttransistor . . . . .                                           | 73        |

| 4.2 Einzelpartikeltransistoren . . . . .                                      | 76        |

| 4.2.1 <i>Inverted Coplanar</i> -Architektur . . . . .                         | 77        |

| 4.2.2 <i>Inverted Staggered</i> -Architektur . . . . .                        | 86        |

|                                                                               |            |

|-------------------------------------------------------------------------------|------------|

| 4.2.3 Degradationsverhalten . . . . .                                         | 95         |

| 4.3 Zusammenfassung und Bewertung von Si-NP-FET . . . . .                     | 97         |

| <b>5 Feldeffekttransistoren mit Zinkoxid-Nanopartikeln</b>                    | <b>101</b> |

| 5.1 Einfluss der Umgebungsatmosphäre auf das Transistorverhalten . . . . .    | 102        |

| 5.2 Auswahl des Kontaktmetalls für die Drain- und Source-Elektroden . . . . . | 104        |

| 5.3 Dünnfilmtransistoren mit Rückseiten-Gate-Elektrode . . . . .              | 106        |

| 5.3.1 <i>Inverted Coplanar</i> -Architektur . . . . .                         | 106        |

| 5.3.2 <i>Inverted Staggered</i> -Architektur . . . . .                        | 110        |

| 5.3.3 Bewertung der Dünnfilmtransistoren . . . . .                            | 131        |

| 5.4 Einzelpartikeltransistoren mit Rückseiten-Gate-Elektrode . . . . .        | 132        |

| 5.4.1 <i>Inverted Coplanar</i> -Architektur . . . . .                         | 133        |

| 5.4.2 <i>Inverted Staggered</i> -Architektur . . . . .                        | 138        |

| 5.5 Bewertung und Fazit von ZnO-NP-FET mit Rückseiten-Gate-Elektrode .        | 141        |

| 5.6 Transistoren mit frei beschaltbaren Gate-Elektroden . . . . .             | 143        |

| 5.6.1 Gate-Dielektrikum . . . . .                                             | 143        |

| 5.6.2 Dünnfilmtransistoren mit PVP-Dielektrikum . . . . .                     | 148        |

| 5.6.3 Einzelpartikeltransistoren auf Glassubstrat . . . . .                   | 159        |

| 5.6.4 Bewertung von TFT mit frei beschaltbaren Gate-Elektroden . .            | 163        |

| <b>6 Schaltungen</b>                                                          | <b>165</b> |

| 6.1 Inverter . . . . .                                                        | 165        |

| 6.1.1 Inverter auf thermisch oxidiertem Siliziumsubstrat . . . . .            | 167        |

| 6.1.2 Inverter auf Glassubstrat . . . . .                                     | 169        |

| 6.2 Fazit . . . . .                                                           | 170        |

| <b>Zusammenfassung und Ausblick</b>                                           | <b>171</b> |

| <b>A Prozesstechnik</b>                                                       | <b>177</b> |

| A.1 Konventionelle Lithografie- und Strukturierungsverfahren . . . . .        | 177        |

| A.1.1 Optische Lithografie . . . . .                                          | 177        |

| A.1.2 EUV-Lithografie . . . . .                                               | 178        |

| A.1.3 Röntgenstrahlolithografie . . . . .                                     | 179        |

| A.1.4 Elektronenstrahlolithografie . . . . .                                  | 180        |

| A.1.5 Nanoimprint-Lithografie . . . . .                                       | 180        |

| A.2 Nanostrukturierung: Alternative Materialien der Opferschicht . . . .      | 181        |

| <b>B Finite-Elemente-Simulation</b>                                           | <b>185</b> |

| B.1 Simulationsumgebung . . . . .                                             | 185        |

| B.2 DESSIS-Quellcode . . . . .                                                | 186        |

| <b>Literaturverzeichnis</b>                                                   | <b>189</b> |

| <b>Eigene Veröffentlichungen und Patente</b>                                  | <b>211</b> |

| <b>Danksagung</b>                                                             | <b>213</b> |

---

---

# Ausgewählte Formelzeichen und Abkürzungen

---

## Allgemeine Variablen und Konstanten

|                  |                                |

|------------------|--------------------------------|

| $A$              | geometrische Fläche            |

| $A^{**}$         | effektive RICHARDSON-Konstante |

| $C$              | elektrische Kapazität          |

| $e_{\text{rel}}$ | relativer Fehler               |

| $f$              | Frequenz                       |

| $F_C$            | COULOMB-Kraft                  |

| $G$              | elektrischer Leitwert          |

| $h$              | PLANCKSches Wirkungsquantum    |

| $I$              | elektrische Stromstärke        |

| $I_s$            | elektrische Sperrstromstärke   |

| $J$              | elektrische Stromdichte        |

| $J_s$            | elektrische Sperrstromdichte   |

| $J_t$            | Tunnelstromdichte              |

| $k$              | BOLTZMANN-Konstante            |

| $L_B$            | Leiterbahnlänge                |

| $m^*$            | effektive Masse                |

| $m_0$            | Ruhemasse                      |

| $M$              | molare Masse                   |

| $P$              | elektrische Leistung           |

| $q$              | Elementarladung                |

| $Q$              | elektrische Ladung             |

| $R$              | elektrischer Widerstand        |

| $T$              | Temperatur                     |

| $T_{\text{bp}}$  | Siedepunkt                     |

| $V$              | elektrische Spannung           |

| $Z$              | Ordnungszahl im Periodensystem |

| $\mathcal{E}$    | elektrische Feldstärke         |

| $\epsilon_r$     | relative Dielektrizitätszahl   |

|                                |                                                  |

|--------------------------------|--------------------------------------------------|

| $\epsilon_s$                   | relative Dielektrizitätszahl bei SCHOTTKY-Effekt |

| $\epsilon_0$                   | Dielektrizitätskonstante                         |

| $\Theta$                       | Tunnelwahrscheinlichkeit                         |

| $\lambda$                      | Wellenlänge                                      |

| $\nu$                          | Wellenfrequenz                                   |

| $\xi$                          | Massenanteil/-konzentration                      |

| $\rho$                         | Raumladungsdichte                                |

| $\rho_R, \rho_{R,c}$           | spezifischer Widerstand, Kontaktwiderstand       |

| $\varrho$                      | Dichte                                           |

| $\sigma$                       | spezifischer Leitwert                            |

| $\tau, \tau_{dec}, \tau_{deg}$ | Zeit- bzw. Verzögerungskonstanten                |

| $\varphi$                      | elektrisches Potenzial                           |

| $\Psi$                         | Wellenfunktion                                   |

## Halbleitereigenschaften

|                        |                                                    |

|------------------------|----------------------------------------------------|

| $E_C$                  | Leitungsbandkante                                  |

| $E_F$                  | Fermienergie                                       |

| $E_g$                  | Bandlücke                                          |

| $E_i$                  | intrinsische Fermienergie                          |

| $E_V$                  | Valenzbandkante                                    |

| $E_{vac,HL}$           | Vakuumenergieniveau für Halbleiter                 |

| $E_{vac,M}$            | Vakuumenergieniveau für Metalle                    |

| $L_D$                  | DEBYE-Länge                                        |

| $n$                    | Elektronendichte                                   |

| $n_{int}$              | Ladungsträgerdichte an Grenzflächen                |

| $N_D, N_A$             | Donator- bzw. Akzeptorkonzentration                |

| $N_t$                  | Störstellendichte                                  |

| $N_{t,E}$              | energetische Störstellendichte                     |

| $p$                    | Löcherdichte                                       |

| $V_{bi}$               | <i>Built-in</i> -Spannung                          |

| $W_\rho$               | Raumladungszonenweite                              |

| $\mu$                  | Ladungsträgerbeweglichkeit                         |

| $W_{\phi_{Bn}}$        | Barrierenweite für Elektronen                      |

| $\phi_{Bn}, \phi_{Bp}$ | Barrierenhöhe für Elektronen bzw. Löcher           |

| $\phi_t$               | Barrierenhöhe in Störstellen, Tiefe der Störstelle |

| $\Delta\phi$           | Abnahme der Barrierenhöhe durch SCHOTTKY-Effekt    |

| $\phi_{HL}, \phi_M$    | Austrittspotenzial für Halbleiter bzw. Metalle     |

| $\chi$                 | Elektronenaffinität                                |

## Transistor- und Schaltungsparameter

|                                 |                                                                  |

|---------------------------------|------------------------------------------------------------------|

| $C_i$                           | Gate-Kapazität                                                   |

| $f_T$                           | Transitfrequenz                                                  |

| $g_d$                           | Ausgangsleitwert                                                 |

| $g_m$                           | Steilheit                                                        |

| $I_D, I_{DS}$                   | Drain- bzw. Drain-Source-Strom                                   |

| $I_G$                           | Gate-Leckstrom                                                   |

| $Q_s$                           | akkumulierte Ladung                                              |

| $t_i$                           | Schichtdicke des Gate-Dielektrikums                              |

| $V_A, V_{DD}, V_E$              | Ausgangs-, Versorgungs-, Eingangsspannung                        |

| $V_{DS}$                        | Drain-Source-Spannung                                            |

| $V_{GS}$                        | Gate-Source-Spannung                                             |

| $V_{th}, V_{t0}$                | Schwellenspannungsgrößen                                         |

| $\mathcal{E}_{DS}$              | Kanalfeldstärke                                                  |

| $\mathcal{E}_{BD}$              | Durchbruchfeldstärke                                             |

| $\alpha, \beta, \gamma, \delta$ | Modellparameter zum <i>DITL</i> -Effekt                          |

| $\mu_{eff}$                     | effektive Ladungsträgerbeweglichkeit                             |

| $\mu_{FE}, \mu_{FE0}$           | Feldeffektladungsträgerbeweglichkeit                             |

| $\mu_n, \mu_p$                  | Elektronen-, Löcherbeweglichkeit                                 |

| $\mu_{sat}$                     | Sättigungsladungsträgerbeweglichkeit                             |

| $\theta$                        | Modellparameter zur Gate-induzierten Schwellenspannungsabsenkung |

## Größen der Prozesstechnik und Schichtgeometrie

|             |                                                                           |

|-------------|---------------------------------------------------------------------------|

| $D_{NP}$    | Nanopartikeldurchmesser                                                   |

| $DoF$       | Tiefenschärfe                                                             |

| $f_{RF}$    | RF-Anregungsfrequenz                                                      |

| $h_{HL}$    | Schichtdicke der Halbleiterschicht                                        |

| $h_{h,OS}$  | Schichtdicke der Opferschicht                                             |

| $h_{h,SS}$  | Schichtdicke der Strukturschicht auf horizontalen Flächen                 |

| $h_{v,SS}$  | Schichtdicke der Strukturschicht auf vertikalen Flächen (Kantenbedeckung) |

| $k_{SS}$    | Konformität der Strukturschicht-Abscheidung                               |

| $NA_0$      | Nummerische Apertur in Luft                                               |

| $n_\lambda$ | optischer Brechungsindex                                                  |

| $N_\square$ | Partikelflächendichte                                                     |

| $R$         | Auflösungsvermögen einer Optik                                            |

| $S_q$       | RMS-Oberflächenrauheit                                                    |

| $T_a$       | Annealing-Temperatur                                                      |

| $\Gamma$    | Schichtbedeckungsgrad                                                     |

## Mathematische Operatoren und abkürzende Notationen

|                        |                     |

|------------------------|---------------------|

| $\text{Cov}\{\cdot\}$  | Kovarianz           |

| $\text{div}\{\cdot\}$  | Divergenz           |

| $\text{Korr}\{\cdot\}$ | Kreuzkorrelation    |

| $\text{Var}\{\cdot\}$  | Varianz             |

| $\overline{\{\cdot\}}$ | Mittelwert          |

| $\widehat{\{\cdot\}}$  | approximierte Größe |

## Abkürzungen

|                 |                                                                                                      |

|-----------------|------------------------------------------------------------------------------------------------------|

| $\text{AFM}$    | <u>A</u> tomic <u>F</u> orce <u>M</u> icroscope                                                      |

| $\text{ALD}$    | <u>A</u> tomic <u>L</u> ayer <u>D</u> eposition                                                      |

| $\text{ALILE}$  | <u>AL</u> uminum <u>I</u> nduced <u>L</u> ayer <u>E</u> xchange                                      |

| $\text{BSG}$    | <u>B</u> oro <u>S</u> ilikat <u>G</u> las                                                            |

| $\text{CVD}$    | <u>C</u> hemical <u>V</u> apor <u>D</u> eposition                                                    |

| $\text{DIBL}$   | <u>D</u> rain <u>I</u> nduced <u>B</u> arrier <u>L</u> owering                                       |

| $\text{DITL}$   | <u>D</u> rain <u>I</u> nduced <u>T</u> hreshold <u>L</u> owering                                     |

| $\text{DUV}$    | <u>D</u> eep <u>U</u> ltra <u>V</u> iolet                                                            |

| $\text{EPT}$    | <u>E</u> inzel <u>P</u> artikel <u>T</u> ransistor                                                   |

| $\text{EUV}$    | <u>E</u> xtreme <u>U</u> ltra <u>V</u> iolet                                                         |

| $\text{FEM}$    | <u>F</u> inite- <u>E</u> lemente <u>M</u> ethode                                                     |

| $\text{GND}$    | <u>G</u> rou <u>ND</u>                                                                               |

| $\text{HMDS}$   | <u>H</u> exa <u>M</u> ethyl <u>D</u> i <u>S</u> ilazan                                               |

| $\text{HS}$     | <u>H</u> igh- <u>S</u> pin                                                                           |

| $\text{IC}$     | <u>I</u> nverted <u>C</u> oplanar                                                                    |

| $\text{IS}$     | <u>I</u> nverted <u>S</u> taggered                                                                   |

| $\text{LPCVD}$  | <u>L</u> ow <u>P</u> ressure <u>C</u> hemical <u>V</u> apor <u>D</u> eposition                       |

| $\text{LS}$     | <u>L</u> ow- <u>S</u> pin                                                                            |

| $\text{LTO}$    | <u>L</u> ow <u>T</u> emperature <u>O</u> xide                                                        |

| $\text{MIS}$    | <u>M</u> etal- <u>I</u> nsulator- <u>S</u> emiconductor                                              |

| $\text{MOSFET}$ | <u>M</u> etal- <u>O</u> xide- <u>S</u> emiconductor <u>F</u> ield <u>e</u> ffect- <u>T</u> ransistor |

| $\text{NIL}$    | <u>N</u> ano <u>I</u> mpint <u>L</u> ithography                                                      |

| $\text{NIS}$    | <u>N</u> on <u>I</u> nverted <u>S</u> taggered                                                       |

| $\text{NMP}$    | <u>N</u> - <u>M</u> ethyl-2- <u>P</u> yrrolidon                                                      |

| $\text{OFET}$   | <u>O</u> rganic <u>F</u> ield <u>e</u> ffect- <u>T</u> ransistor                                     |

| $\text{OLED}$   | <u>O</u> rganic <u>L</u> ight <u>E</u> mitting <u>D</u> iode                                         |

| $\text{PDMS}$   | <u>P</u> oly <u>D</u> i <u>M</u> ethyl <u>S</u> iloxan                                               |

| $\text{PECVD}$  | <u>P</u> lasma <u>E</u> nhan <u>c</u> ed <u>C</u> hemical <u>V</u> apor <u>D</u> eposition           |

| $\text{PEN}$    | <u>P</u> oly <u>E</u> thylen <u>N</u> aphtalat                                                       |

| $\text{PET}$    | <u>P</u> oly <u>E</u> thylen <u>T</u> erephthalat                                                    |

|        |                                                                                     |

|--------|-------------------------------------------------------------------------------------|

| PGMEA  | <u>P</u> ropylen <u>G</u> lycol <u>M</u> onomethyl <u>E</u> ther <u>A</u> cetat     |

| PI     | <u>P</u> oly <u>I</u> mid                                                           |

| PL     | <u>P</u> hoto <u>L</u> uminiszenz                                                   |

| PMCF-m | <u>P</u> oly( <u>M</u> elamin- <u>C</u> o- <u>F</u> ormaldehyd)- <u>m</u> ethyliert |

| PMMA   | <u>P</u> oly <u>M</u> ethyl <u>M</u> eth <u>A</u> crylat                            |

| PMS    | <u>P</u> artikel- <u>M</u> assen- <u>S</u> pektroskopie                             |

| PP     | <u>P</u> oly <u>P</u> ropylen                                                       |

| PVD    | <u>P</u> hysical <u>V</u> apor <u>D</u> eposition                                   |

| PMS    | <u>P</u> oly(4- <u>V</u> inyl <u>P</u> henol)                                       |

| REM    | <u>R</u> aster <u>E</u> lektronen <u>M</u> ikroskopie                               |

| RFID   | <u>R</u> adio <u>F</u> requency <u>ID</u> entification                              |

| RIE    | <u>R</u> eactive <u>I</u> on <u>E</u> tching                                        |

| RLZ    | <u>R</u> aum <u>L</u> adungs <u>Z</u> one                                           |

| RMS    | <u>R</u> oot <u>M</u> ean <u>S</u> quare                                            |

| RTA    | <u>R</u> apid <u>T</u> hermal <u>A</u> nneling                                      |

| SB     | <u>S</u> CHOTTKY- <u>B</u> arriere                                                  |

| SCLC   | <u>S</u> pace <u>C</u> harge <u>L</u> imited <u>C</u> urrent                        |

| TEM    | <u>T</u> ransmissions <u>E</u> lektronen <u>M</u> ikroskopie                        |

| TEOS   | <u>T</u> etra <u>E</u> thyl <u>O</u> rtho <u>S</u> ilikat                           |

| TES    | <u>T</u> ri <u>E</u> thyl <u>S</u> ilan                                             |

| TFT    | <u>T</u> hin- <u>F</u> ilm <u>T</u> ransistor                                       |

| UV     | <u>U</u> ltra <u>V</u> iolett                                                       |

| VE     | <u>V</u> öllig <u>E</u> ntsalzt                                                     |

| WKB    | <u>W</u> ENTZEL- <u>K</u> RAMERS- <u>B</u> RILLOUIN                                 |

---

# Einleitung

---

Obwohl der Begriff der NANOTECHNOLOGIE ein besonderes Maß an Innovation und Fortschritt suggeriert, werden nanotechnologische Phänomene seit der Antike beschrieben. Insbesondere Nanopartikel und die damit verbundenen kolloidalen Dispersionen wurden häufig in ihren Erscheinungen beobachtet und ihre Auswirkungen genutzt. Als Beispiele hierfür seien kolloidale Flusssedimente im Babylon des 13. Jahrhunderts vor Christus, rotgefärbte Kirchenfenster durch Plasmonenresonanz in Gold-Nanopartikeln im mittelalterlichen Europa oder aber auch nanoskalige Rußadditive in Gummireifen zur Steigerung der Abriebfestigkeit ab dem frühen 20. Jahrhundert nach Christus genannt. Die ersten Anwendungen sind somit hauptsächlich der Materialwissenschaft und der Chemie zuzuordnen.

Das Interesse am Einsatz von Nanopartikeln in elektronischen Anwendungen wuchs erst mit der Suche nach Möglichkeiten, elektronische Schaltungen auf flexiblen Trägermaterialien (Substraten) und kosteneffizient in Druckverfahren (Rolle-zu-Rolle) herstellen zu können. Die konventionelle Siliziumhalbleitertechnologie kann zwar technisch für einen Großteil der Anwendungen eingesetzt werden, die Material- und Produktionskosten sind jedoch bezüglich des Nutzens unverhältnismäßig hoch [Wong09]. Zunächst konzentrierte sich die Forschung auf die organische Elektronik, deren entscheidender Nachteil die Degradation darstellt. Bis auf das Gebiet der organischen Leuchtdioden (OLED) existieren bislang nur sehr wenige marktreife Produkte [VDMA09]. Dabei wird das Marktpotenzial auf bis zu 43 Milliarden Euro im Jahr 2020 geschätzt [Maur10]. Mögliche Anwendungsgebiete sind unter anderem die Displaytechnik, Photovoltaik, Batterien, Sensoren, *RFID* und intelligente Textilien.

Im Laufe der letzten Jahre blieb die Degradation organischer Transistoren (*OFET*) ein dominantes Problem, so dass auch anorganische Halbleitermaterialien für die flexible Elektronik in Betracht gezogen wurden [SR07]. Diese lassen sich zwar als Dünnschichten in flexibler Elektronik integrieren, doch nur als kolloidale Dispersion lassen sich anorganische Materialien auch im Druckverfahren abscheiden. Insbesondere Zinkoxid (ZnO) wird als aussichtsreiches Material angesehen, da zur Prozessierung geringe Temperaturen benötigt werden, aber dennoch relativ leistungsstarke Transistoren möglich sind [OHM10, Wong09].

Das Einsatzgebiet der Nanopartikelelektronik besteht zunächst aus Anwendungen der *Makroelektronik*. Dieses Gebiet zielt nicht auf eine ausschließliche Erhöhung der Integrationsdichte wie die *Mikro- oder Nanoelektronik* ab, sondern auf die Größe des

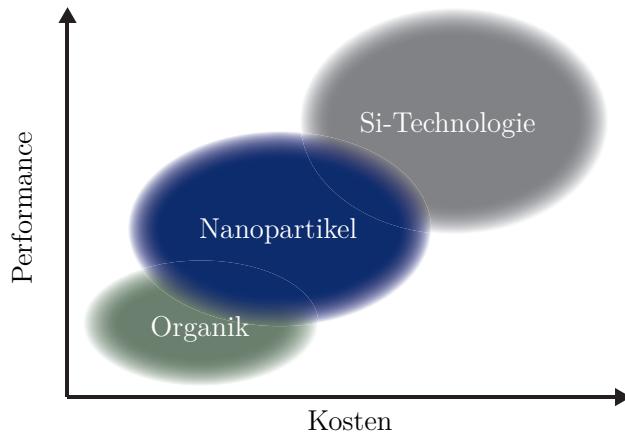

**Abbildung 1:** Einordnung der nanopartikelbasierten Elektronik im Kosten-Performance-Verhältnis

Gesamtsystems. In Applikationen, bei denen Größe eine untergeordnete Rolle spielt bzw. gezielt erwünscht ist (z. B. großflächige Displays), soll nanopartikelbasierte Elektronik im sogenannten *low-cost/low-performance*-Segment eingesetzt werden, also einem Bereich, in dem eine mittelmäßige Leistungsfähigkeit bei niedrigen Kosten akzeptabel ist. Es ist durchaus möglich, bessere Ladungsträgerbeweglichkeiten in anorganischen Nanopartikeln als in organischen Dünnschichten zu erreichen und gleichzeitig die Produktionskosten konstant zu halten, wenn nicht sogar zu senken. Die Nanopartikelhalbleitermaterialien stellen somit ein Bindeglied zwischen den organischen Halbleitern und der konventionellen Siliziumtechnik dar [siehe Abbildung 1].

Vorteilhafterweise zeigt sich, dass ein Teil der Forschungsergebnisse aus der OFET-Technologie auf die Nanopartikeltechnologie transferiert werden kann. So ist es möglich, auf dieselben Isolatoren und Substrate zurückzugreifen [Hali06, Wong09]. Auch die späteren Druckverfahren können unter Anpassung der Dispersionsrheologie auf die Nanopartikel elektronik übertragen werden.

## Zielsetzung

Im Mittelpunkt dieser Arbeit stehen Transistoren mit halbleitenden Nanopartikeln, die den Aufbau elektronischer Schaltungen auf isolierenden Substraten ermöglichen. Mit Blick auf alternative Herstellungsverfahren für flexible Trägermaterialien wird der maximal zulässige Temperaturbereich bereits in dieser Arbeit berücksichtigt. Unter diesen Maßgaben werden sowohl Dünnschicht- als auch Einzelpartikeltransistoren integriert, charakterisiert, Prozess- und Materialeinflüsse analysiert und die Leistungsfähigkeit bzw. Eignung der Bauelemente anhand von Standardtransistorparametern bewertet. Dieses ermöglicht die Selektion einer geeigneten Transistorarchitektur und Prozessführung. Die Vorgehensweise soll letztendlich zur Integration eines Inverters als einfache logische Schaltung führen. Die Materialauswahl konzentriert sich auf Silizium als Elementhalbleiter und Zinkoxid als transparenten Verbindungshalbleiter.

Für den Halbleiter Silizium beschäftigen sich bisherige Arbeiten nahezu ausschließlich mit vertikal integrierten Einzelpartikelbauelementen, also Transistoren mit einer Kanallänge in der Dimension des Nanopartikeldurchmessers. Von Nachteil ist der vertikale Aufbau der Transistoren, der mit einer aufwändigen Prozessführung und einer nicht bestimmhbaren Position der Bauelemente einhergeht, so dass eine gezielte Verschaltung einzelner Transistoren nicht möglich ist. Nanopartikuläres Zinkoxid als Halbleitermaterial wird in bisherigen Forschungsarbeiten nur als Dünnschichtmaterial eingesetzt. Die Erhöhung der Ladungsträgerbeweglichkeit – jedoch unter Vernachlässigung der Kontakteigenschaften – ist ein zentraler Punkt der aktuellen Forschung. Berichte über Zinkoxid in Einzelpartikelarchitekturen sind aus der Literatur nicht bekannt.

In der vorliegenden Arbeit werden daher lateral aufgebaute Einzelpartikeltransistoren sowohl mit Silizium- als auch Zinkoxid-Nanopartikeln vorgestellt. Darüber hinaus werden Dünnschichttransistoren mit beiden Partikelarten integriert, wobei eine Steigerung der Leistungsfähigkeit zunächst nicht im Vordergrund stehen soll.

## Gliederung

Zunächst werden in Kapitel 1 ausgewählte physikalische Grundlagen erläutert, die für die Funktionsweise der Transistoren eine entscheidende Rolle einnehmen. Hauptaugenmerk liegt auf dem Metall-Halbleiter-Kontakt, der das zentrale Element in der Gruppe der SCHOTTKY-Barrieren-Drain-/Source-Feldeffekttransistoren (SB-(MOS)FET) darstellt, zu der auch die vorgestellten Feldeffekttransistoren mit halbleitenden Nanopartikeln zählen. Weiterhin wird auf Ladungsträgertransportmechanismen eingegangen, die im Zusammenhang mit störstellenbehafteten Nanopartikeln und Grenzflächen auftreten. Daraufhin werden die Herstellungsverfahren von Nanopartikeln aus Halbleitermaterialien und der Einfluss einer Überführung des Feststoffs in kolloidale Suspensionen behandelt. Neben den allgemeinen Eigenschaften von Nanopartikeln und den Unterschieden zu den Materialien in ihrer Makroform werden Untersuchungen zur Grundcharakterisierung der verwendeten Silizium- und Zinkoxid-Nanopartikel vorgestellt.

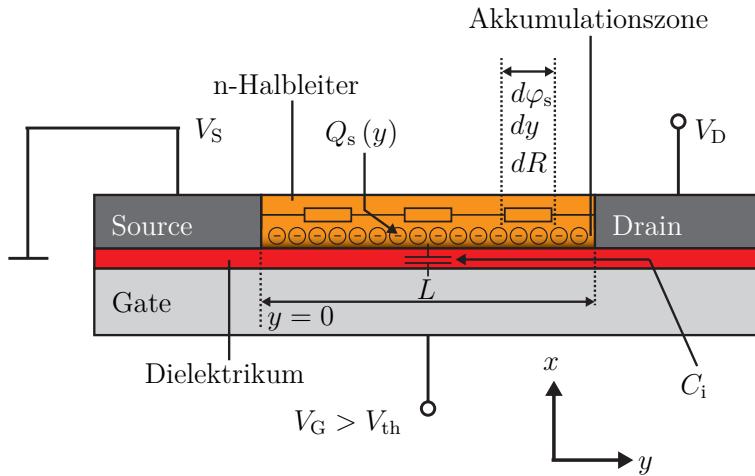

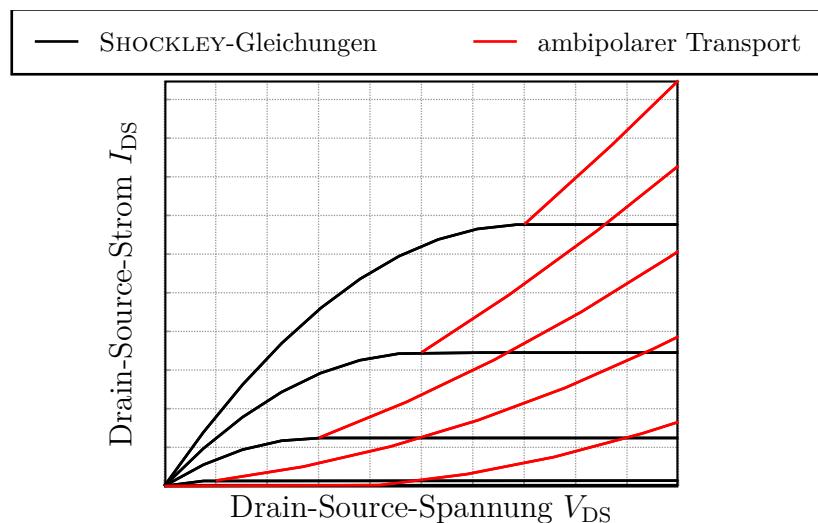

Im darauf folgenden Kapitel 2 werden typische Bauformen von Dünnschicht-Transistoren erläutert. Diese werden anschließend auch auf Einzelpartikeltransistoren übertragen und bewertet. Da die in dieser Arbeit zu präsentierenden Bauelemente auf dem Konzept der Feldeffekttransistoren beruhen, die pn-Übergänge konventioneller MOSFET aber durch Metall-Halbleiter-Kontakte ersetzt werden, wird sowohl das Funktionsprinzip der SB-MOSFET als auch die Herleitung stark vereinfachter Modellgleichungen erklärt. Zum Abschluss des Kapitels werden die Methoden zur Ermittlung der elektrischen Transistorparameter ausgeführt. Ein Standard für nanopartikelbasierte Transistoren steht bislang nicht zur Verfügung.

Wie bereits in der Einleitung erwähnt, wird sich der Dünnschichtprozesse der herkömmlichen Halbleitertechnologie bedient, um Bauelemente zu integrieren. Insbesondere im Zusammenhang mit der großflächigen und effizienten Integration von Einzelpartikeltransistoren

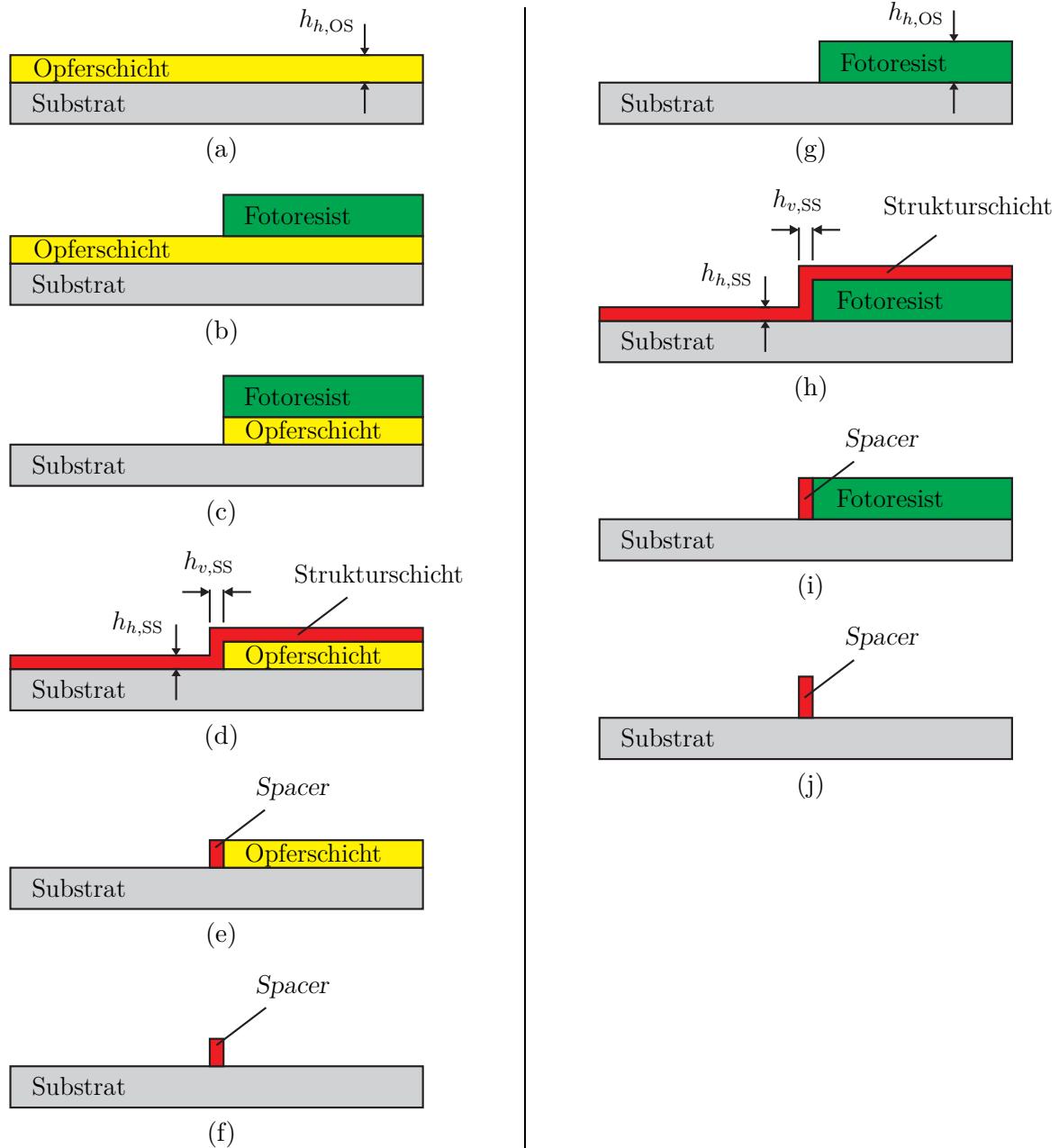

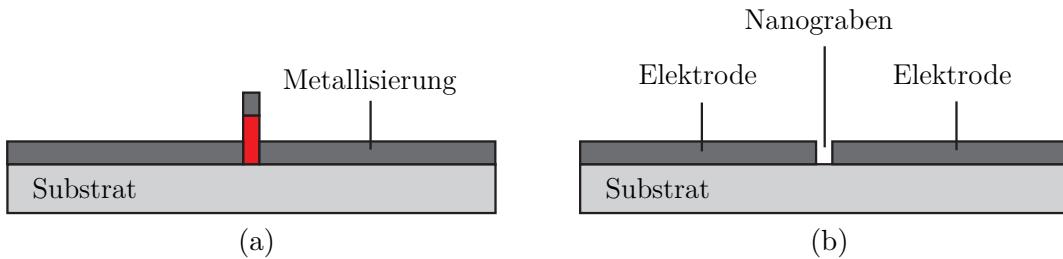

wird die technologisch realisierbare Schwelle auf herkömmlichem Wege überschritten, so dass die Problematiken der Strukturierungstechnik in Kapitel 3 kurz diskutiert und das sogenannte Kantenabscheideverfahren als alternative Lösung zur großflächigen Nanostrukturierung vorgestellt wird.

Inhalt des 4. Kapitels ist die Präsentation der Ergebnisse der experimentellen Integration von Feldeffekttransistoren mit Silizium-Nanopartikeln. Die Resultate unter Verwendung von Zinkoxid-Nanopartikeln werden in Kapitel 5 vorgestellt. In beiden Fällen sind die Transistoren sowohl als Dünnschicht- als auch als Einzelpartikeltransistoren in verschiedenen Architekturen mit gemeinsamer Rückseiten-Gate-Elektrode aufgebaut. Hierdurch ist es möglich, die Herstellungsverfahren und grundlegenden Eigenschaften zu untersuchen. Das Verhalten der Bauelemente und die Einflüsse der Prozesstechnik – beispielsweise die Auswirkungen einer thermischen Behandlung der Nanopartikel – auf die elektrische Charakteristik werden diskutiert. Anhand der gewonnenen Resultate wird im Hinblick auf den Schaltungsaufbau anschließend der Übergang zu frei beschaltbaren Transistoren mit ZnO-Nanopartikeln vollzogen.

Anhand der in den Kapiteln 4 und 5 gewonnenen Ergebnisse wird ein zum Schaltungsaufbau geeignetes Transistorkonzept ausgewählt und eine Inverterschaltung auf Silizium- bzw. Glassubstrat integriert. Die Charakterisierung und Bewertung der Inverterschaltungen wird in Kapitel 6 behandelt, wobei die Performance der Schaltungen zunächst zweitrangig ist; im Vordergrund steht die Demonstration der Realisierbarkeit.

# Grundlagen, Nanopartikel und deren Eigenschaften

---

Aufgrund des Aufbaus von Feldeffekttransistoren mit halbleitenden Nanopartikeln und der elektrischen Eigenschaften von Nanopartikeln werden im Folgenden die für diese Arbeit relevanten physikalischen Modelle für die Raumladungszone, den Metall-Halbleiter-Kontakt und für die Ladungsträgertransportvorgänge vorgestellt. Die Betrachtungen stützen sich im Wesentlichen auf [Sze81]. Weiterhin werden in Abschnitt 1.2 eine Auswahl von Synthes- und Dispergierverfahren von Nanopartikeln sowie die Eigenschaften von Nanopartikeln – insbesondere im Vergleich mit den entsprechenden Volumenmaterialien – erläutert.

## 1.1 Ausgewählte physikalische Grundlagen

### 1.1.1 Raumladungszone

Durch die im Vergleich zu Metallen geringere Ladungsträgerkonzentration in Halbleitern können elektrische Felder an der Oberfläche eines Halbleiters erst in der Tiefe kompensiert werden, während Metalle oder entartete Halbleiter eine oberflächennahe Gegenladung bereitstellen können und die Tiefe dieser Kompensationsschicht vernachlässigbar ist. Infolgedessen entsteht in Halbleitern eine Raumladungszone (RLZ). Die vollständige

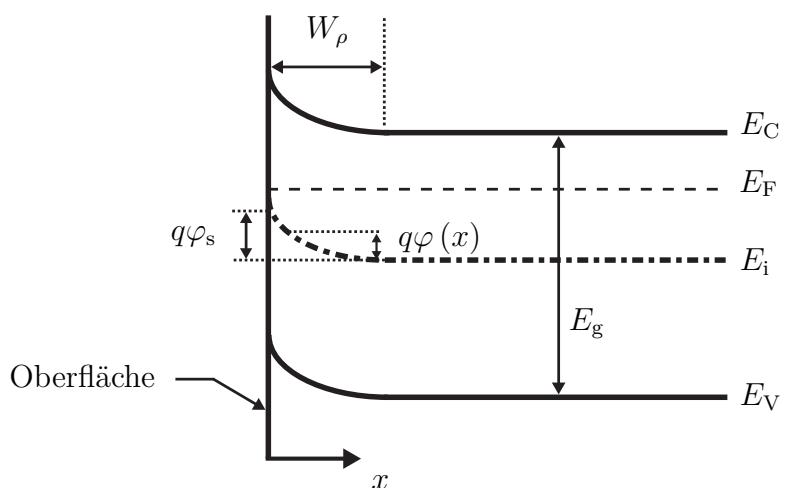

**Abbildung 1.1:** Banddiagramm eines n-Halbleiters mit Oberflächenpotenzial  $\varphi_s$

Kompensation des auf der Oberfläche festgelegten Potenzials  $\varphi_s$  tritt erst mit Erreichen der Raumladungszonenweite  $W_\rho$  ein. Diese lässt sich allgemein aus dem Potenzial  $\varphi(x)$  und den Ladungsträgerdichten im Gleichgewichtszustand  $n_{n0}$  und  $p_{n0}$  berechnen. Für die Ladungsträgerverteilungen und die Raumladung  $\rho$  gilt mit den Bezeichnungen in Abbildung 1.1

$$n_n(x) = n_{n0} \cdot \exp\left(-\frac{q\varphi}{kT}\right), \quad (1.1a)$$

$$p_n(x) = p_{n0} \cdot \exp\left(\frac{q\varphi}{kT}\right), \quad (1.1b)$$

$$\rho(x) = q \left[ N_D^+ - N_A^- + p_n(x) - n_n(x) \right]. \quad (1.1c)$$

Die hochgestellten Indizes in Gleichung (1.1c) deuten die Ionisierung der Donatoren  $N_D$  bzw. Akzeptoren  $N_A$  an. Der Verlauf des Bändermodells ist zur Verdeutlichung in Abbildung 1.1 abgebildet. Unter der Annahme einer Störstellenerschöpfung für einen n-Halbleiter<sup>1</sup> mit

$$N_D^+ = N_D, \quad (1.2)$$

sowie mit  $N_A^- = N_A = 0$  und der Störstellennäherung vereinfacht sich die Raumladungsdichte zu

$$\rho = qN_D, \quad (1.3)$$

womit sich die eindimensionale POISSON-Gleichung

$$\operatorname{div} E = -\frac{\partial^2 \varphi}{\partial x^2} = \frac{\rho}{\epsilon_0 \epsilon_r} = \frac{qN_D}{\epsilon_0 \epsilon_r} \quad (1.4)$$

ergibt. Die Gleichung (1.4) lässt sich unter den Randbedingungen  $\mathcal{E}(x \geq W_\rho) = 0$  und  $\varphi(x \geq W_\rho) = 0$  lösen. Die Weite der Raumladungszone für  $\varphi(0) = \varphi_s$  stellt sich nach

$$W_\rho = \sqrt{\frac{2\epsilon_0 \epsilon_r \varphi_s}{qN_D}} \quad (1.5)$$

ein. Für die Flächenladungsdichte der Raumladungszone gilt

$$\rho_{RLZ} = qN_D W_\rho. \quad (1.6)$$

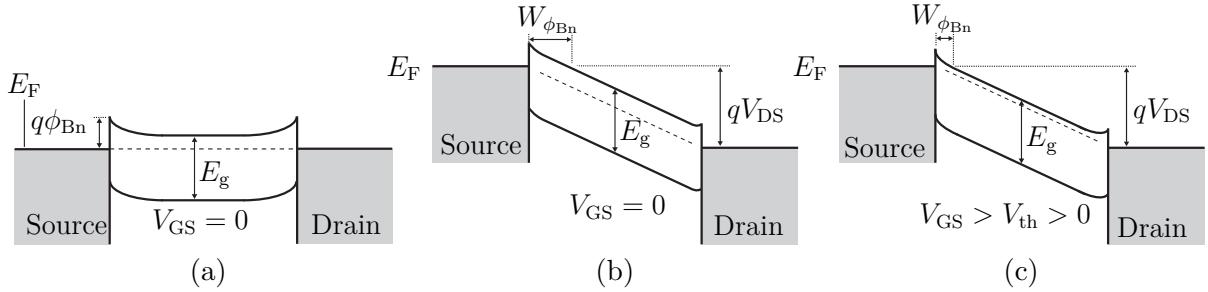

### 1.1.2 Metall-Halbleiter-Grenzfläche

Im Gegensatz zu konventionellen MOSFET, deren sperrende Eigenschaften auf zwei gegenüberliegenden pn-Homoübergängen basieren, stehen bei Feldeffekttransistoren mit halbleitenden Nanopartikeln die metallischen Drain- und Source-Elektroden im direkten Kontakt mit dem Kanalgebiet. Die Eigenschaften des Metall-Halbleiter-Kontaktes spielen daher eine zentrale Rolle für die Funktion Nanopartikel-basierter Bauelemente.

---

<sup>1</sup>Analog lässt sich die Herleitung auch für einen p-Halbleiter durchführen.

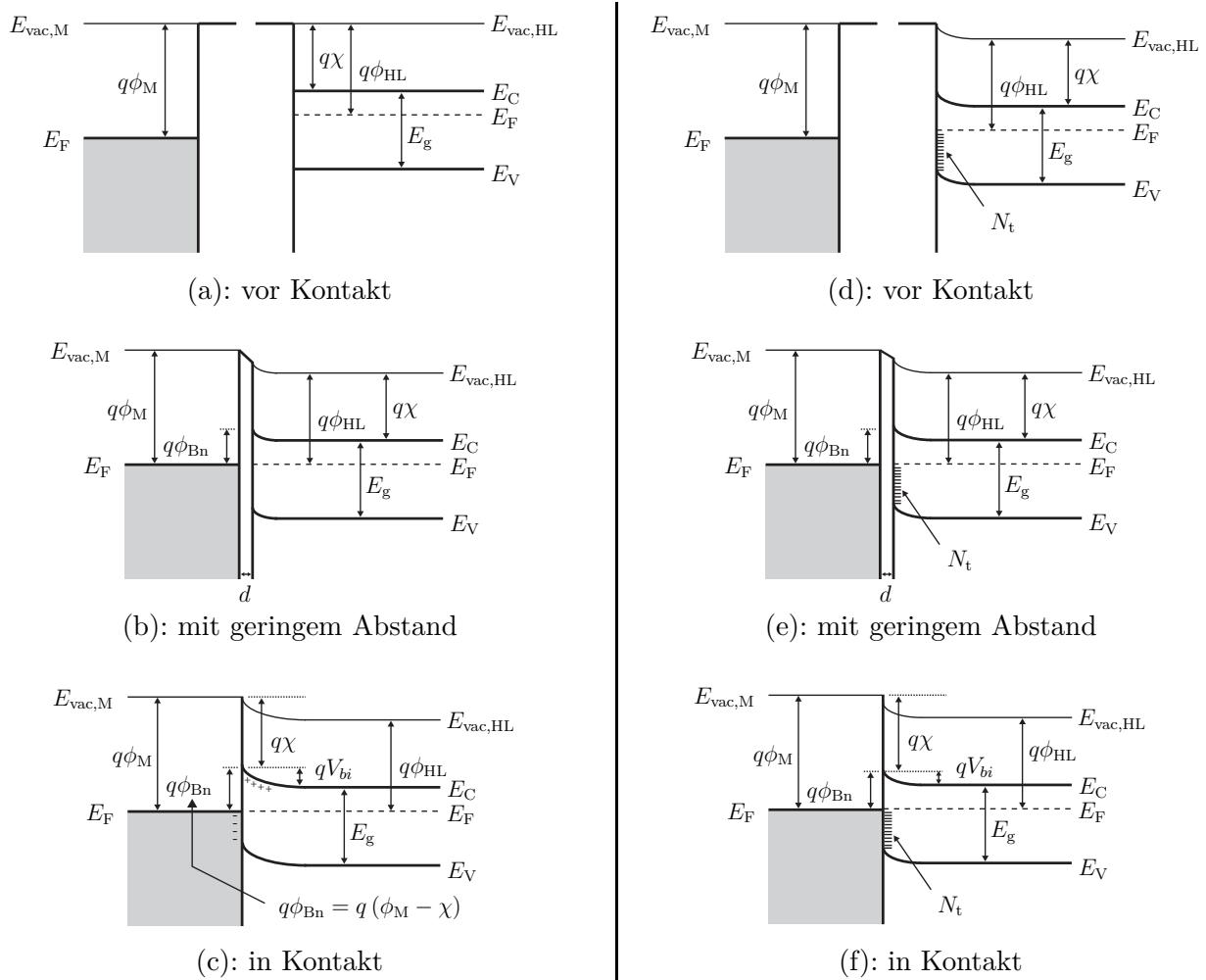

**Abbildung 1.2:** Banddiagramme von Metall-Halbleiter-Kontakten. (a)-(c): idealer Metall-Halbleiter-Kontakt, (d)-(f): Metall-Halbleiter-Kontakt mit Oberflächen-Störstellen im Halbleiter

Die genauen physikalischen Vorgänge am Metall-Halbleiter-Kontakt sind bislang nicht vollständig geklärt. Dennoch lässt sich der Metall-Halbleiter mit dem bekannten und stark vereinfachten MOTT-SCHOTTKY-Modell beschreiben [Scho38, Mott38].

Im idealen Fall ist das Kontakt-System gegeben durch das Metall mit der Fermienergie  $E_F$  und der Austrittsarbeit  $q\phi_M$  und dem (idealen) Halbleitermaterial, welches energetisch durch die Valenzbandkante  $E_V$ , die Leitungsbandkante  $E_C$ , das Fermienergieniveau  $E_F$  und die Elektronenaffinität  $\chi$  definiert ist. In Abbildung 1.2a ist das System graphisch dargestellt. Vor dem Kontakt befinden sich beide Materialien im thermodynamischen Gleichgewicht. Werden die beiden Materialien einander angenähert, so ist das System bestrebt, die Fermienergieniveaus anzugeleichen, indem sich im Metall eine negative Ladung und im Halbleiter eine positive Gegenladung bildet. Aufgrund der hohen Leitfähigkeit des Metalls kann die Ladung direkt als Oberflächenladung existieren, während sich im Halbleiter mit einer relativ geringen Ladungsträgerkonzentration die Ladung über

eine Raumladungszone verteilt. Hierdurch tritt im Barrierengebiet eine Krümmung der Energiebänder auf [siehe Abbildung 1.2b]. Im Grenzfall, dem direkten Kontakt beider Materialien, entsteht so eine Ladungsträgerbarriere. Für Elektronen und Löcher als Ladungsträger gilt für die Barrierenhöhen

$$\phi_{Bn} = \phi_M - \chi \quad (1.7a)$$

$$\phi_{Bp} = \frac{E_g}{q} - [\phi_M - \chi]. \quad (1.7b)$$

Die Barrierenhöhe wird demnach in erster Näherung durch die Austrittsarbeit des Metalls und die Elektronenaffinität des Halbleiters bestimmt. Im Falle einer negativen Differenz zwischen Austrittsarbeit des Metalls und Elektronenaffinität des Halbleiters entsteht eine Anreicherungsschicht und der Kontakt zeigt ohmsches Verhalten. Für die Summe der Barrierenhöhen für Minoritäts- und Majoritätsladungsträger ergibt sich die Bandlücke zu

$$E_g = q [\phi_{Bn} + \phi_{Bp}]. \quad (1.8)$$

Da in einem realen Halbleitermaterial zumindest Störstellen durch Abbruch der Gitterstruktur an der Oberfläche entstehen, müssen diese für das Verhalten des Metall-Halbleiterkontakte berücksichtigt werden. Es wird daher davon ausgegangen, dass an der Oberfläche eine Störstellenkonzentration der Dichte  $N_t$  vorliegt. Die Störstellen sind bis zum Fermiplateau besetzt, und die Energiebänder des Halbleiters sind im thermodynamischen Gleichgewicht auch ohne einen Kontakt zum Metall bereits aufgewölbt [siehe Abbildung 1.2d]. Bei Annäherung beider Materialien [siehe Abbildung 1.2e] tritt ebenso die Generation von grenzflächennahen Ladungen auf. Unter der Voraussetzung, dass die Dichte  $N_t$  ausreichend groß ist, um zusätzliche Ladungen aufzunehmen, tritt jedoch keine weitere nennenswerte Veränderung der Bandstruktur des Halbleiters auf. Im direkten Kontakt existiert wiederum eine Ladungsträgerbarriere  $\phi_{Bn}$ . Ihre Höhe ist nicht mehr von der Austrittsarbeit des Metalls abhängig, sondern wird durch die Oberflächeneigenschaften des Halbleiters bestimmt.

Für den Ladungsträgertransport an Metall-Halbleitergrenzflächen ist die Barrierenhöhe von besonderer Bedeutung, da sie direkten Einfluss auf die Anzahl der Ladungsträger hat, die von dem einen in das andere Material gelangen können. Daher ist der SCHOTTKY-Effekt zu berücksichtigen, der eine Absenkung der Barrierenhöhe durch das elektrische Feld am Übergang bewirkt. Der Effekt lässt sich an einer idealen Metalloberfläche erklären. Wird ein Elektron aus dem Metall herausgelöst, so muss die Austrittsarbeit  $q\phi_M$  geleistet werden. Gleichzeitig gilt, dass ein Elektron, welches sich an der Position  $x$  außerhalb des Metalls befindet, eine COULOMB-Kraft erfährt. Diese Kraft wird durch eine Spiegelladung, die sich im Metall an der Position  $-x$  befindet, hervorgerufen [KMR06]. Dabei ist die COULOMB-Kraft durch

$$F_C = -\frac{q^2}{4\pi\epsilon_0 (2x)^2} = -\frac{q^2}{16\pi\epsilon_0 x^2} \quad (1.9)$$

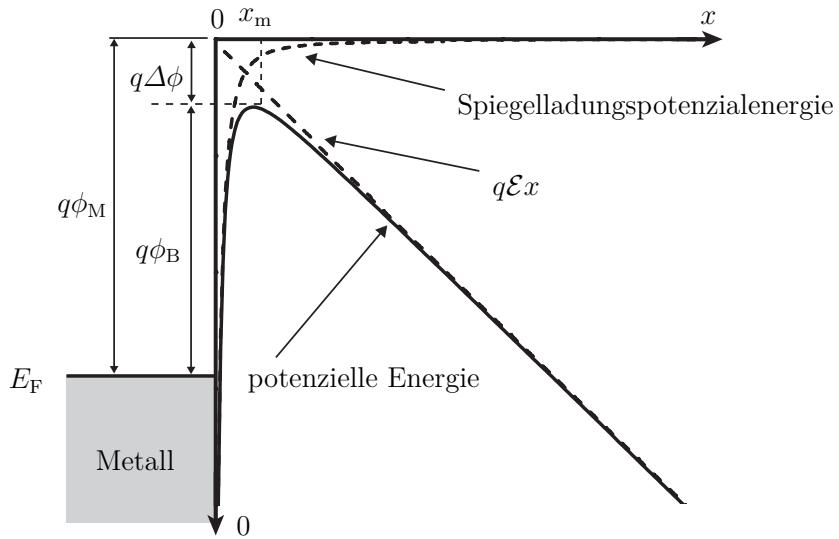

**Abbildung 1.3:** Energiediagramm des Übergangs von einer Metalloberfläche zum Vakuum

gegeben. Damit lässt sich die Arbeit angeben, die durch ein Elektron auf seinem Weg verrichtet werden muss, wenn es aus dem Unendlichen zum Punkt  $x$  geführt wird.

$$E(x) = \int_{-\infty}^x F_C dx = \frac{q^2}{16\pi\epsilon_0 x}. \quad (1.10)$$

Wenn ein externes elektrisches Feld  $\mathcal{E}$  angelegt wird, überlagert sich die Kraft des elektrischen Feldes auf das Elektron mit dem Feld der Spiegelladungskraft, so dass sich die resultierende Energie

$$E_{\text{ges}}(x) = \frac{q^2}{16\pi\epsilon_0 x} + q\mathcal{E}x \quad (1.11)$$

ergibt. Abbildung 1.3 zeigt schematisch die Metalloberfläche und die Verteilung der potenziellen Energie außerhalb des Metalls. Ein Elektron benötigt demnach nur die Energie  $q\phi_B$ , um das Metall zu verlassen, wobei  $q\phi_B = q(\phi_M - \Delta\phi)$  ist. Der SCHOTTKY-Effekt lässt sich auch auf den Metall-Halbleiter-Kontakt anwenden, wenn das elektrische Feld  $\mathcal{E}$  durch die maximale elektrische Feldstärke an der Grenzfläche und die Permittivität im Vakuum durch eine entsprechende Permittivität  $\epsilon_0\epsilon_s$  ausgetauscht werden. Die Größe  $\epsilon_s$  kann je nach Übergangszeit und dielektrischer Relaxationszeit verschieden von der relativen Dielektrizitätszahl  $\epsilon_r$  des Halbleiters sein. Die Absenkung der Ladungsträgerbarriere ist dann definiert als

$$\Delta\phi = \sqrt{\frac{q\mathcal{E}}{4\pi\epsilon_0\epsilon_s}}. \quad (1.12)$$

Weiterhin kann die Barriereförde durch ein externes elektrisches Feld beeinflusst werden, welches durch das Anlegen einer Spannung am Metall-Halbleiter-Übergang entsteht. Je nach Vorzeichen der Spannung kann die Barriere vergrößert oder verkleinert werden<sup>2</sup>.

<sup>2</sup>Typische Werte für  $\Delta\phi$  liegen nach Gleichung (1.12) im Bereich von 0,035 eV mit der relativen Permittivität  $\epsilon_s = 12$  und der elektrischen Feldstärke  $\mathcal{E} = 10^5$  V/cm [Sze81].

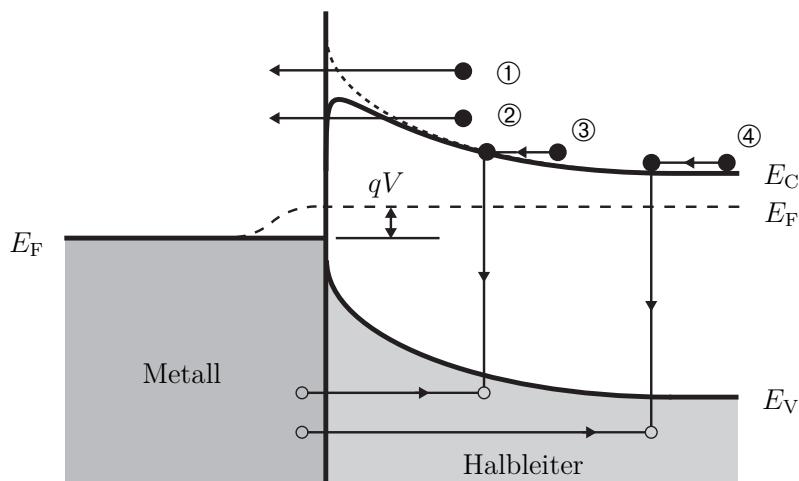

**Abbildung 1.4:** Transport-Prozesse am Metall-Halbleiter-Übergang in Vorwärtsrichtung:

① thermische Emission über die Barriere, ② Tunneleffekt durch die Barriere,

③ Rekombination in der Raumladungszone, ④ Löcherinjektion aus

dem Metall (Rekombination im neutralen Bereich) (nach [Sze81])

Der Ladungsträgertransport an Metall-Halbleiter-Grenzflächen wird im Gegensatz zum pn-Übergang durch Majoritätsladungsträger bestimmt. Die vier grundlegenden Transportprozesse sind in Abbildung 1.4 dargestellt. Sie treten parallel auf, wobei die Gewichtung je nach Materialbeschaffenheit und Feldstärken variiert. Gemäß der Abbildung sind die vier wichtigsten Mechanismen:

- ① (feldunterstützte) thermische Emission über die Barriere. Dieser Prozess ist dominant für Metall-Halbleiter-Übergänge mit moderaten Dotierstoffkonzentrationen und Temperaturen;

- ② Tunneleffekt durch die Barriere. Dominant bei hohen Dotierstoffkonzentrationen bzw. sehr schmalen Barrieren;

- ③ Rekombination in der Raumladungszone, vergleichbar mit einem pn-Homoübergang;

- ④ Rekombination im neutralen Bereich (Löcherinjektion vom Metall in den Halbleiter).

Für einen Ladungsträgertransport in Sperrrichtung treten diese Mechanismen ebenfalls auf. Hierbei ist jedoch zu berücksichtigen, dass die Barrieren aufgrund ihrer Form in anderer Weise auf den Transportprozess wirken.

Je nach Ladungsträgerbeweglichkeit des Halbleiters lässt sich der Strom über den Übergang berechnen; für Halbleiter mit großer Mobilität (z.B. Silizium) gemäß der *Theorie der thermischen Emission*. Bei geringen Mobilitäten ist die *Diffusionstheorie* anwendbar. Da die Ladungsträgerbeweglichkeiten für halbleitende Nanopartikel je nach Verarbeitung und Partikelmorphologie sehr verschieden sind, soll an dieser Stelle die Kombination aus beiden vorgenannten Theorien, die *Thermische Emissions - Diffusionstheorie*

genannt werden. Für nähere Erläuterungen und die Herleitung wird auf [Sze81] verwiesen<sup>3</sup>. Die Stromdichte  $J$  am Übergang ergibt sich zu

$$J = A^{**} T^2 \exp\left(-\frac{q\phi_{Bn}}{kT}\right) \left[ \exp\left(\frac{qV}{kT}\right) - 1 \right], \quad (1.13)$$

wobei  $A^{**}$  die effektive RICHARDSON-Konstante ist<sup>4</sup>. Die Größe  $A^{**}$  ist wiederum abhängig von der Rekombinationsgeschwindigkeit und der Übergangswahrscheinlichkeit der Ladungsträger am Metall-Halbleiter-Kontakt. Die Charakteristik ähnelt durch die exponentielle Abhängigkeit von der Spannung einer pn-Diode. Die Stromdichte ist zudem abhängig von der Barriereförde und nimmt exponentiell mit zunehmender Höhe ab.

Für den Tunneleffekt haben theoretische und experimentelle Untersuchungen gezeigt, dass die Stromdichte die Abhängigkeit

$$J = J_s \left[ \exp\left(\frac{qV}{nkT}\right) - 1 \right] \quad (1.14)$$

besitzt. Die Variable  $n$  wird als Idealitätsfaktor bezeichnet.

Für stark dotierte Halbleiter tritt eine Dominanz des Tunneleffekts auf. Der Anteil an der Stromdichte, der durch den Tunneleffekt getragen wird, ist durch

$$J_t \propto \exp\left(-\frac{q\phi_{Bn}}{E_{00}}\right) \quad \text{mit} \quad E_{00} = \frac{q\hbar}{2} \sqrt{\frac{N_D}{\epsilon_s m^*}} \quad (1.15)$$

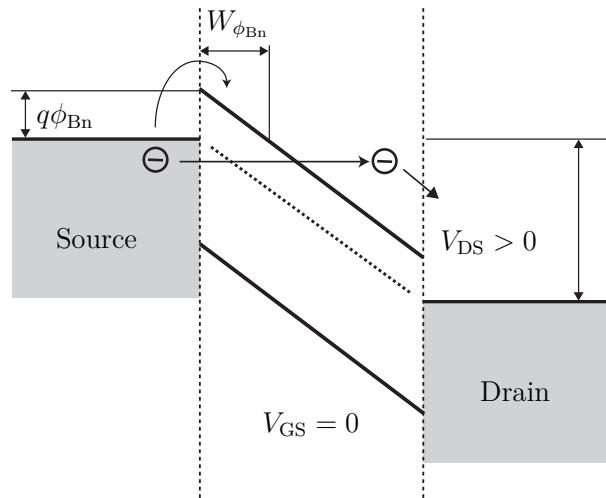

gegeben. Auch in diesem Fall ist zu erkennen, dass die Stromdichte von der Barriereförde  $\phi_{Bn}$  abhängig ist. Es lässt sich demnach schlussfolgern, dass die Barriereförde eine Schlüsselrolle in Halbleiterbauelementen spielt, deren Funktion auf Metall-Halbleiter-Kontakten gründet. Zwar ist die Barriereförde unter anderem abhängig von der Dotierung des Halbleiters, doch nimmt – unabhängig von der Dotierung – die Stromdichte exponentiell mit steigender Barriereförde ab. Es ist weiterhin zu bemerken, dass nicht nur die Barriereförde, sondern auch die Barriereförde  $W_{\phi_{Bn}}$  die Stromdichte beeinflusst. Diese ist bereits in Form der Spannung  $V$  bzw. der Dotierstoffkonzentration in den Gleichungen (1.13) und (1.15) inbegriffen. Wie in Abschnitt 2.3 gezeigt werden wird, bestimmt nicht ausschließlich die angelegte Spannung  $V$  (im Speziellen die Drain-Source-Spannung  $V_{DS}$ ) die Weite  $W_{\phi_{Bn}}$ , sondern auch das elektrische Feld, welches von der Gate-Elektrode ausgeht. Je nach Betriebszustand des Transistors dominiert entweder die thermische Emission oder der Tunneleffekt.

Es ist bislang nicht geklärt, inwiefern dieses stark vereinfachte Modell des Metall-Halbleiterübergangs, beruhend auf idealen Metallen und perfekten Einkristallen, auf die

<sup>3</sup>Im englischen Sprachgebrauch werden für die Theorien die Bezeichnungen *Thermionic Emission Theory*, *Diffusion Theory* bzw. *Thermionic Emission - Diffusion Theory* verwendet.

<sup>4</sup>Die ersten drei Faktoren der rechten Seite in Gleichung (1.13) können zur Sperrstromdichte  $J_s$  zusammengefasst werden, so dass  $J_s = A^{**} T^2 \exp\left(-\frac{q\phi_{Bn}}{kT}\right)$  gilt.

Kontakte zwischen Metallen und halbleitenden Nanopartikeln angewendet werden kann. Insbesondere Nanopartikel weisen eine hohe Störstellendichte und eine nanokristalline Struktur auf.

Für Silizium als weitverbreitetes Halbleitermaterial wird dieses Problem sehr kontrovers diskutiert. Es wurde lange davon ausgegangen, dass sich die Kontakt-eigenschaften in porösem Silizium – einem den Nanopartikeln strukturell ähnlichen System – entsprechend dem vorgestellten Modell einstellen. BEN-CHORIN ET AL. legten jedoch dar, dass aufgrund der hohen Zustandsdichte in porösem Material und eines *Hopping*-Transportmechanismus anstelle eines Ladungstransports über thermisch generierte Ladung die Kontakte quasi-ohmsches Verhalten zeigen [BCMK95]. Übertragen auf Silizium-Nanopartikelfilme folgte BURR ET AL. dieser Annahme [BSWK97], jedoch sind auch Beispiele bekannt, in denen das Verhalten von Nanopartikeltransistoren gezielt durch die Auswahl eines Kontaktmetalls von p- auf n-leitenden Typ verändert werden kann [DDB<sup>+</sup>06, SDB<sup>+</sup>07]. Dies ist aber nur möglich, wenn die Barriereneigenschaften der Metall-Halbleiter-Grenzflächen Einfluss nehmen. Es ist folglich anzunehmen, dass keine allgemeingültige Aussage getroffen werden kann, da zu viele Faktoren (Herstellungsverfahren, Verarbeitung, Reinheit etc.) auf die Eigenschaften der Übergänge einwirken.

Für die Realisierung von Nanopartikeltransistoren ist es zunächst nicht entscheidend, ob die Kontakte ohmsch oder gleichrichtend sind. Mit ohmschen Kontakten können ebenfalls Transistoren integriert werden, sofern der Ladungsträgerabtransport nach der Injektion durch das Halbleitermaterial stark eingeschränkt ist, also eine Anreicherung von Ladungsträgern in der Halbleiterschicht in unmittelbarer Nähe der Metall-Halbleiter-Grenzfläche stattfindet (Strombegrenzung). Sobald durch die Gate-Elektrode ein Feldeffekt auf den Kanal wirkt und die Leitfähigkeit erhöht wird, kann der Abtransport gesteigert werden, so dass sich der Transistor im leitenden Zustand befindet. Nähere Ausführungen zur Funktionsweise sind dem Abschnitt 2.3 zu entnehmen.

### 1.1.3 Ladungsträgertransportmechanismen

Da Nanopartikel und aus ihnen hergestellten Schichten im Allgemeinen eine sehr hohe Störstellendichte besitzen, sollen drei Transportmechanismen vorgestellt werden, die im engen Zusammenhang mit störstellenbehafteten Halbleitern und Isolatoren stehen.

#### Feldunterstützte thermische Emission (Frenkel-Poole-Effekt)

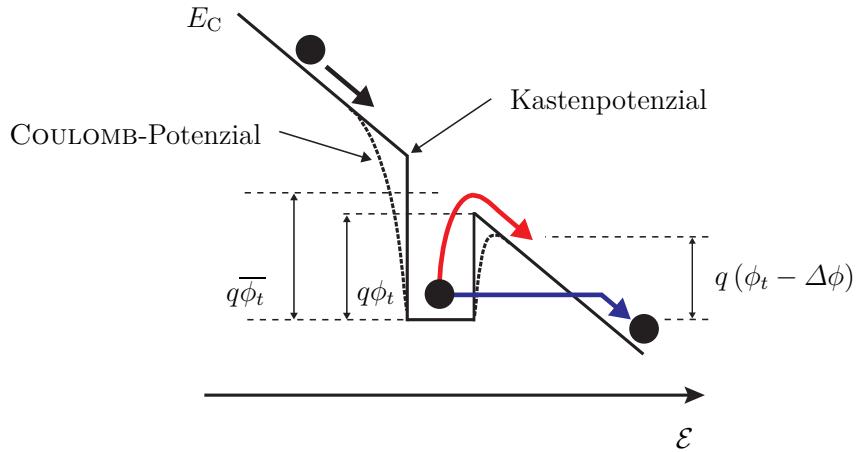

Der FRENKEL-POOLE-Effekt beschreibt den Ladungsträgertransport in störstellenbehafteten Feststoffen, in denen ein elektrisches Feld existiert [Fren38]. Grundlage des Mechanismus' ist das Anhaften von Ladungsträger an Störstellen und deren anschließende Anregung zum erneuten Übergang in das Leitungsband. Im Banddiagramm werden die Störstellen als Potenzialtopf endlicher Tiefe repräsentiert. Bei angelegtem elektrischen Feld werden die Energiebänder geneigt, so dass der Potenzialtopf gemäß Abbildung 1.5 die mittlere Tiefe  $q\bar{\phi}_t$  besitzt. Das elektrische Feld bewirkt in Bewegungsrichtung der Ladung eine Absenkung der Barrierenhöhe, so dass diese lediglich  $q\phi_t < q\bar{\phi}_t$  beträgt. Wird von der idealen Vorstellung eines Kastenpotenzials abgewichen und die COULOMB-Kräfte der Bildladung berücksichtigt, tritt (ähnlich dem SCHOTTKY-Effekt) eine weitere Absenkung der Barrierenhöhe um  $\Delta\phi$  auf (gestrichelter Bandverlauf). Ladungsträger können somit

**Abbildung 1.5:** Ladungsträgertransport durch FRENKEL-POOLE-Effekt (rot) und FOWLER-NORDHEIM-Tunneleffekt (blau)

den Potenzialtopf leichter verlassen, indem sie thermisch angeregt über den „Potenzialtopfrand“ bewegt werden [roter Pfeil in Abbildung 1.5]. Die Stromdichte in einer Isolator- bzw. Halbleiterschicht der Dicke  $d$  wird durch

$$J \propto V \cdot \exp\left(\frac{2a\sqrt{V}}{T}\right) \cdot \exp\left(-\frac{q\phi_t}{kT}\right) \quad \text{mit} \quad a = \sqrt{\frac{q}{4\pi\epsilon_0\epsilon_r d}} \quad (1.16)$$

beschrieben.

### Feldunterstützter Tunneleffekt (Fowler-Nordheim- Tunneleffekt)

Für den Ladungsträgertransport durch einen störstellenbehafteten Halbleiter bewirkt ein elektrisches Feld – vergleichbar zum FRENKEL-POOLE-Effekt – auch einen günstigen Übergang eines im Potenzialtopf gefangenen Ladungsträgers, wenn das Teilchen die Störstelle mittels Durchtunnellen der Barriere verlässt. Die Weite der Barriere wird durch das elektrische Feld dermaßen verringert, dass die Tunnelwahrscheinlichkeit stark zunimmt [blauer Pfeil in Abbildung 1.5]. Für den Zusammenhang zwischen Stromdichte und anliegender Spannung gilt

$$J \propto V^2 \cdot \exp\left(-\frac{b}{V}\right) \quad \text{mit} \quad b = \text{const.} > 0. \quad (1.17)$$

Es ist zu bemerken, dass die Stromdichte unabhängig von der Temperatur ist, da eine thermische Anregungsenergie für den Effekt nicht notwendig ist<sup>5</sup>.

<sup>5</sup>Hiervon abzugrenzen ist die thermisch unterstützte Tunnelemission, bei der das Energieniveau des Ladungsträgers durch Aufnahme von thermischer Energie zunächst erhöht wird. Mit zunehmendem Energieniveau nimmt die effektive Barrienerweite ab, so dass die Tunnelwahrscheinlichkeit ansteigt [SN07].

### Raumladungsbegrenzter Strom

Der Effekt des raumladungsbegrenzten Stroms<sup>6</sup> berücksichtigt den eigenen Einfluss der transportierten Ladungsträger auf das elektrische Feld, welches den Transport hervorruft. Als Erklärung dient die Vorstellung, dass die Feldlinien des elektrischen Feldes auf Ladungen enden. Somit schirmen Ladungsträger, die sich auf der Strecke zwischen zwei Elektroden befinden, das Feld von einer Elektrode ab. Historisch ist die Theorie über den raumladungsbegrenzten Stromfluss aus der Betrachtung von Isolatoren erwachsen; sie ist aber auch auf Halbleitermaterialien anwendbar. Als einfacher Fall sei ein perfekter Isolator mit einer vernachlässigbaren Anzahl freier Ladungsträger gegeben, der zudem störstellenfrei ist [LM70]. Die Strom-Spannungs-Charakteristik bei Injektion von Ladungsträgern wird dann durch

$$J \propto \frac{\epsilon_0 \epsilon_r \mu V^2}{L_B^3} \quad (1.18)$$

beschrieben. Diese Charakteristik wird nur durch die Überschussladungsträger hervorgerufen, die in das Material injiziert werden. Gleichung (1.18) ist in seiner Form dem MOTT-GURNEY-Gesetz ähnlich, das lediglich einen Vorfaktor von 9/8 enthält. Dieses lässt sich unter der Annahme, dass der Strom nur eine Driftstromkomponente enthält, aus der POISSON-Gleichung analytisch herleiten.

Befinden sich bereits freie Ladungsträger mit der Dichte  $n_0$  im Leitungsband, so ergibt sich das bekannte OHMSche Gesetz:

$$J = \frac{qn_0\mu V}{L_B}. \quad (1.19)$$

Der lineare Zusammenhang zwischen Strom und Spannung ist nur anwendbar, so lange die Dichte der thermisch generierten Ladungsträger wesentlich größer ist als die Dichte der injizierten Ladungsträger  $n_{\text{inj}}$ . Sobald die mittlere Dichte der injizierten Ladungsträger die Größenordnung von  $n_0$  erreicht, tritt wiederum der quadratische Zusammenhang in Gleichung (1.18) in den Vordergrund.

Da Isolatoren bzw. Halbleiter Störstellen aufweisen, müssen diese in die Berechnungen mit einbezogen werden, weil sie freie Ladungen einfangen und je nach Störstellenenergieniveau mehr oder weniger leicht wieder entlassen. Nach [LM70] ergibt sich für flache Störstellen, d. h. Störstellen für die  $|q\phi_t| < kT$  gilt, eine Strom-Spannungs-Charakteristik nach

$$J \propto \theta \frac{\epsilon_0 \epsilon_r \mu V^2}{L_B^3} \quad \text{mit} \quad \theta = \frac{n_0 + n_{\text{inj}}}{n_t}. \quad (1.20)$$

Auch in diesem Fall ist die Ähnlichkeit zum MOTT-GURNEY-Gesetz zu erkennen. Für den realistischen Fall einer energetisch verteilten Störstellenkonzentration weicht die Charakteristik vom quadratischen Verlauf ab. Wird eine BOLTZMANN-Verteilung der Störstellenkonzentration mit

$$N_{t,E}(E) = N_0 \cdot \exp\left(\frac{E - E_C}{kT_t}\right) \quad (1.21)$$

---

<sup>6</sup>Im englischen Sprachgebrauch ist die Bezeichnung *Space Charge Limited Current* mit der Abkürzung *SCLC* üblich [LM70]. Im folgenden Verlauf dieser Arbeit wird der raumladungsbegrenzte Strom ebenfalls mit *SCLC* abgekürzt.

angenommen, wobei  $T_t$  ein Temperaturparameter ist, der ein charakterisierendes Maß der Störstellenverteilung bezüglich der Energie darstellt, berechnet sich der Zusammenhang zwischen Stromdichte und Spannung als

$$J \propto \left[ \frac{\epsilon_0 \epsilon_r}{q N_0 k T_t} \right]^l \cdot \frac{V^{l+1}}{L_B^{2l+1}} \quad \text{mit} \quad l = \frac{T_t}{T}. \quad (1.22)$$

Wird berücksichtigt, dass für eine geringe Ladungsträgerinjektionsrate das OHMSche Gesetz gilt, lässt sich Gleichung (1.22) als Superposition von OHMSchem- und MOTT-GURNEY-Gesetz mit den Faktoren  $a$  und  $b$  vereinfacht als

$$J = aV + bV^{l+1} \quad (1.23)$$

darstellen. Dabei dominiert der erste Summand für geringe und der zweite für hohe elektrische Feldstärken. Aufgrund des linearen Zusammenhangs zwischen dem Faktor  $l$  und dem Parameter  $T_t$  beschreibt auch  $l$  die Verteilung der Störstellenkonzentration. Während ein großes  $l$  eine nahezu gleichverteilte Konzentration beschreibt, stellt  $l \leq 1$  den Fall flacher Störstellen aus Gleichung (1.20) dar, weil Störstellen in der Nähe des Leitungsbandes die Störstellen nahe des Quasi-Ferminiveaus dominieren [LM70].

## 1.2 Nanopartikel und deren Eigenschaften

Funktionale Elemente der im Rahmen dieser Arbeit entwickelten Feldeffekttransistoren sind halbleitende Nanopartikel. Dabei handelt es sich per Definition um Material mit Dimensionen unter 100 Nanometer, das sich in seinen chemischen und physikalischen Eigenschaften von massiven Materialien gleicher Zusammensetzung unterscheidet. Die Vielzahl der synthetisierbaren nanopartikulären Stoffe lässt sich anhand der Stoffklassen in drei Hauptgruppen unterteilen. Neben Nanopartikeln aus elektrischen Leitern (z. B. Gold) und Isolatoren (z. B. Siliziumdioxid), existiert die Gruppe der Halbleiter [Schm05, Fend98]. Da sich die vorliegende Arbeit ausschließlich mit Silizium-Nanopartikeln als Elementhalbleiter und Zinkoxid-Nanopartikeln als Verbindungshalbleiter beschäftigt, beschränken sich die folgenden Ausführungen auf diese beiden Materialien.

### 1.2.1 Synthese

Nanopartikel lassen sich durch kolloidale Synthese aus wässrigen Lösungen bzw. durch sogenannte Sol-Gel-Prozesse herstellen [YBK<sup>99</sup>, PBD<sup>99</sup>, VRR<sup>95</sup>, RPCV<sup>01</sup>]. Ebenso ist eine Synthese aus der Gasphase möglich, bei der ein oder mehrere *Precursor*-Gase durch einen geeigneten Energieeintrag derart zur Reaktion angeregt werden, dass nanopartikuläre Produkte aus dem gewünschten Material entstehen. Die notwendige Aktivierungsenergie kann in Form von thermischer, elektrischer<sup>7</sup> oder elektromagnetischer Energie<sup>8</sup>

<sup>7</sup>Hauptsächlich findet eine Anregung durch die Einkopplung einer elektrischen Leistung im Radiofrequenz (RF) statt. HOFMEISTER ET AL. und DUTTA ET AL. verwenden für die Si-Nanopartikelsynthese eine Anregungsfrequenz  $f_{RF} = 30 \text{ MHz}$  [HKD98, DBH95], KNIPPING ET AL. eine Frequenz  $f_{RF} = 2,45 \text{ GHz}$  [KWR<sup>04</sup>].

<sup>8</sup>KLEINWECHTER ET AL. nutzen zum Energieeintrag 2,45 MHz-Mikrowellen [KJK<sup>02b</sup>], HUISKEN ET AL. hingegen Laserlicht [HHK<sup>00</sup>].

zugeführt werden. Die Anregungen durch Laserlicht und durch gleichspannungsangeregte Gasentladung [ZX94] ermöglichen zwar die Nanopartikelsynthese, sind jedoch qualitativ und bezüglich des Materialertrags den Verfahren in Heißwand- oder Mikrowellenreaktoren unterlegen. Da sämtliche verwendete Nanopartikel entweder aus Heißwand- oder Mikrowellenreaktoren stammen, werden diese Prozesse aus Gründen der Vollständigkeit erläutert.

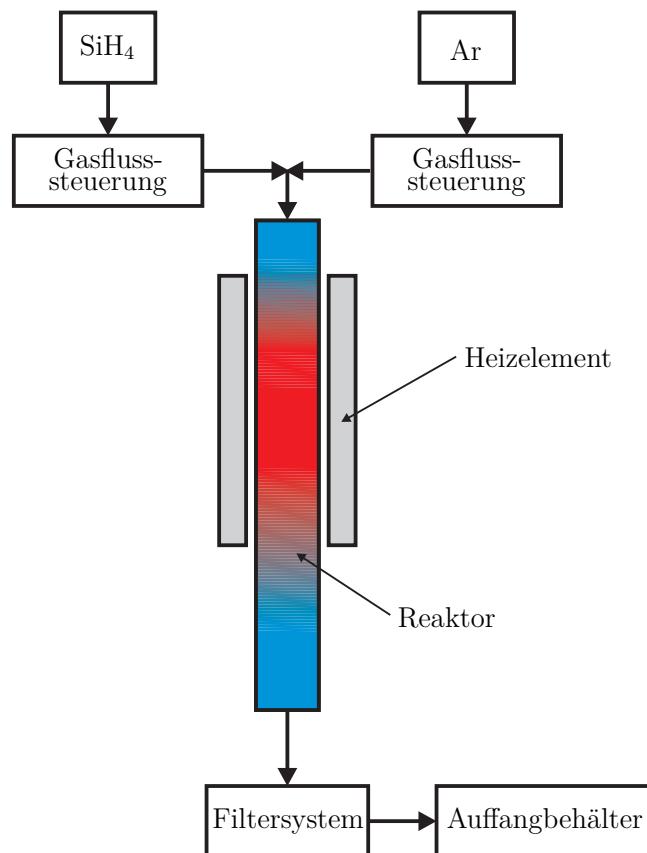

### Gasphasensynthese im Heißwand- und Flammenreaktor

Die Nanopartikelsynthese im Heißwandreaktor nach [WSR01] basiert auf einer thermischen Zersetzung von Silan ( $\text{SiH}_4$ ) bei hohen Temperaturen ( $\approx 1000^\circ\text{C}$ ) unter Atmosphärendruck. Vergleichbar mit dem APCVD-Verfahren<sup>9</sup> strömt ein Gasgemisch aus Argon und  $\text{SiH}_4$  mit einer Geschwindigkeit von 5...7 cm/s durch ein Reaktorrohr. Das Mischungsverhältnis der Gase beträgt 10%...40%  $\text{SiH}_4$  in Argon. Die Gase werden in einer beheizten Zone des Reaktors auf Prozesstemperatur aufgeheizt, so dass sich das Silan in der Reaktion

**Abbildung 1.6:** Schematischer Aufbau eines Heißwandreaktors zur Silizium-Nanopartikelsynthese nach [WSR01]

<sup>9</sup> **A**tmospheric **P**ressure **C**hemical **V**apour **D**eposition

zersetzt und sich Siliziumkristalle bilden. Der Primärpartikeldurchmesser liegt im Bereich von 15...30 nm. In der heißen Zone des Reaktors tritt eine Sinterung von Primärpartikeln auf, so dass Partikel mit Größen von 60...270 nm entstehen. Während diese sich entlang eines negativen Temperaturgradienten in Richtung des Auslasses bewegen, kühlen diese ab und koagulieren zu Agglomeraten. Die Agglomerate werden gefiltert und gesammelt. Der schematische Aufbau eines Heißwandreaktors zur Herstellung von Silizium-Nanopartikeln ist in Abbildung 1.6 dargestellt.

Die Agglomerate weisen lediglich schwache Bindungen der Einzelpartikel untereinander und eine geringe Dichte auf, so dass die Bindungen durch entsprechende Dispersionsverfahren aufgebrochen werden können [vergleiche Abschnitt 1.2.2]. Untersuchungen durch Röntgenbeugung und Transmissionselektronenmikroskopie ergeben eine polykristalline Struktur der Nanopartikel. Die Primärpartikelgröße ist im Wesentlichen abhängig von der Strömungsgeschwindigkeit bzw. der Verweildauer des Gasgemisches in der Heißzone, so dass die Größe in gewissen Grenzen frei eingestellt werden kann.

Da die nanopartikulären Pulver nach der Synthese mit dem Sauerstoff in der Luft beziehungsweise mit Sauerstoff aus anderen Medien (z. B. Ethanol als Dispergiermedium) in Kontakt kommen, tritt eine Oxidation der Silizium-Nanopartikel auf. Es bildet sich eine Hülle aus amorphem Siliziumdioxid, welche durch Infrarot-Spektroskopie nachgewiesen werden kann. Die Spektren enthalten Si-O- und Si-O-Si-H-charakteristische Linien [KWR<sup>04</sup>].

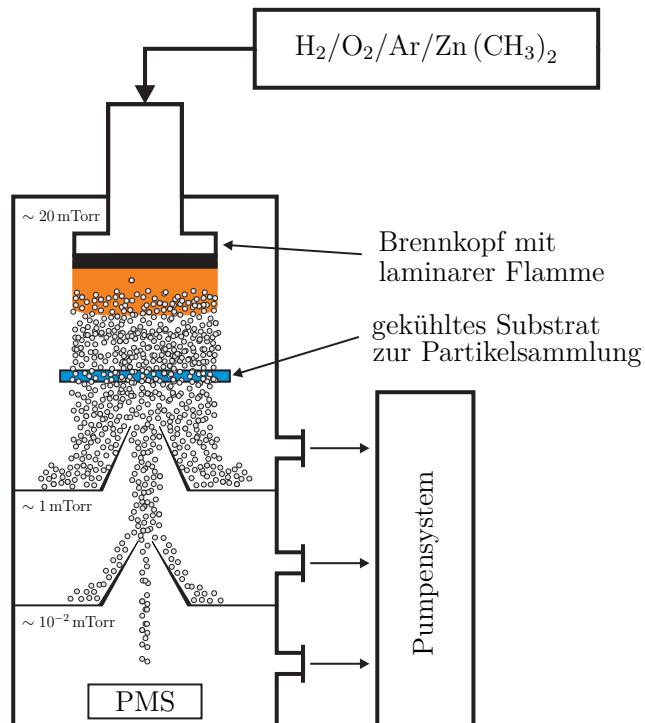

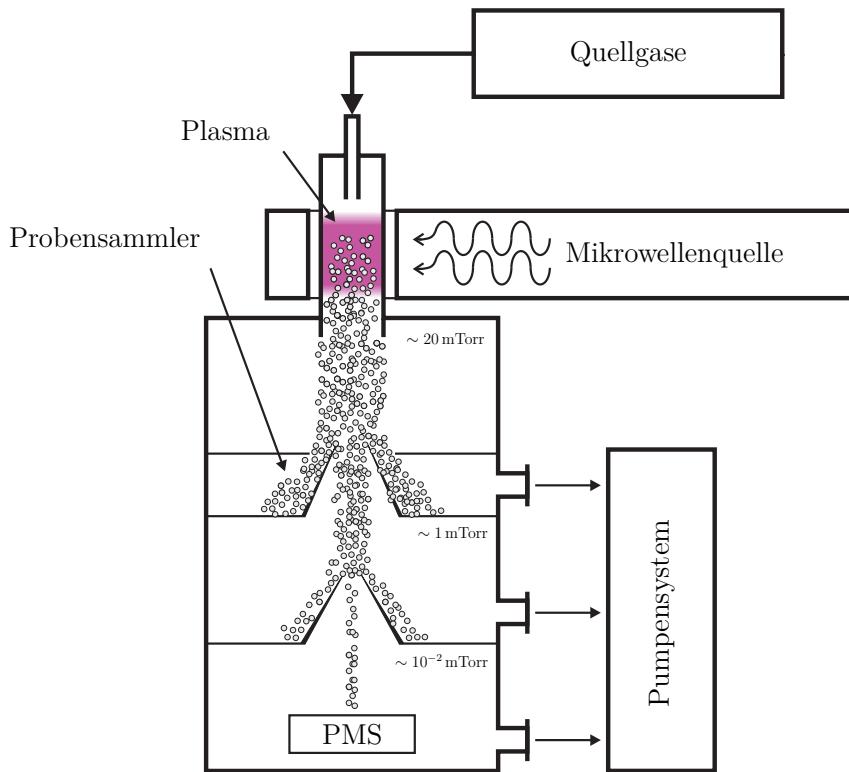

**Abbildung 1.7:** Schematischer Aufbau eines Flammreaktors zur Zinkoxid-Nanopartikelsynthese mit integrierter Partikel-Massen-Spektroskopie (PMS) zur in-situ-Messung der Partikelgrößenverteilung nach [KJK<sup>02b</sup>]

Soll zur Erzeugung von ZnO-Partikeln ebenfalls die thermische Zersetzung und Reaktion von Gasen eingesetzt werden, kommen anstatt Heißwandreaktoren sogenannte Flammenreaktoren zum Einsatz [KJK<sup>02b</sup>]. Durch die Reaktion von Dimethylzink ( $\text{Zn}(\text{CH}_3)_2$ ) und Sauerstoff bildet sich bei Unterdruck Zinkoxid. Das Gemisch enthält inertes Argon, um die Konzentration der Edukte einstellen zu können. Zusätzlich wird Wasserstoff in den Brennkopf geleitet, um eine kontrollierte  $\text{H}_2\text{-O}_2$ -Verbrennung als Energiequelle nutzen zu können. Die Gesamtreaktion findet nach

statt. Der Aufbau eines Flammenreaktors ist in Abbildung 1.7 ersichtlich. Die Primärpartikelgröße lässt sich durch Variation der Dimethylzink-Konzentration im Quellgas steuern, so dass ebenfalls die Größe frei eingestellt werden kann. Vergleichbar mit der Silizium-Nanopartikelsynthese im Heißwandreaktor bilden sich zwischen den ZnO-Partikeln Sinterhälse aus, so dass die effektive Partikelgröße ein Vielfaches der Primärpartikelgröße misst. Nachteil des Verfahrens ist die Behinderung der Nanopartikelformation durch die Anwesenheit des Wassers im Reaktor, welches unweigerlich durch die Verbrennung von Wasserstoff und Sauerstoff entsteht. Das Wasser verhindert eine gleichmäßige Nanopartikelbildung im gesamten Reaktor. Vielmehr kommt es zu einer ausgeprägten Synthese im Bereich kalter Flächen, wohingegen auf warmen Flächen keine Nanopartikel gewonnen werden können [KJK<sup>02b</sup>].

### Gasphasensynthese im Mikrowellenreaktor

Prinzipiell lassen sich Mikrowellenreaktoren sowohl zur Herstellung von Silizium- als auch von Zinkoxid-Nanopartikeln nutzen. Als Quellgase werden im Falle von Silizium Argon, Wasserstoff und Silan, im Falle von ZnO Argon, Sauerstoff und Dimethylzink verwendet [KWR<sup>04</sup>, KJK<sup>02b</sup>, GWKR05, VSH97].

Die Bauart der Mikrowellenreaktoren [vergleiche Abbildung 1.8] ähnelt stark dem Flammenreaktor aus Abschnitt 1.2.1. Anstatt der Verwendung eines Brennkopfes wird das Quellgasgemisch derart durch Mikrowellen (2,45 MHz) angeregt, dass ein Plasma entsteht, in dem die chemische Umsetzung der Ausgangsstoffe entsprechend den Gleichungen (1.24) und (1.25) stattfindet. Die benötigte Leistungsdichte ist abhängig von den zur Gasreaktion erforderlichen Energien und beträgt bei der Silizium-Nanopartikelsynthese  $5\ldots10 \text{ kW cm}^{-2}$ , bei der Zinkoxid-Synthese lediglich  $1\ldots2,5 \text{ kW cm}^{-2}$  [KWR<sup>04</sup>, KJK<sup>02b</sup>]. Die Partikelgröße lässt sich durch Änderung der Gasmischungsverhältnisse, des Prozessdrucks und der eingespeisten Leistung variieren. Die Synthese beider Materialien führt zu einkristallinen Nanopartikeln mit Primärpartikelgrößen von  $5\ldots25 \text{ nm}$ . Nach Abschluss der Gasphasenreaktion neigen auch die Partikel aus dem Mikrowellenreaktor zur Agglomeratbildung [KJK<sup>02b</sup>, GWKR05].

Auch die Siliziumpartikel aus dem Mikrowellenreaktor zeigen aufgrund der chemischen Reaktion mit umgebendem Sauerstoff amorphe Siliziumdioxidschichten an der Oberfläche. Das Siliziumdioxid besitzt dabei nur eine kleine Schichtdicke von wenigen Nanometern und ist unterstöchiometrisch [KWR<sup>04</sup>].

**Abbildung 1.8:** Schematischer Aufbau eines Mikrowellenreaktors zur Nanopartikelsynthese mit integrierter Partikel-Massen-Spektroskopie (PMS) zur in-situ-Messung der Partikelgrößenverteilung nach [KJK<sup>+</sup>02b]

Im Rahmen dieser Arbeit wurden auch dotierte Siliziummaterialien verwendet. Die Dotierung kann durch die Zugabe von entsprechenden Dotiergasen in den Reaktor erreicht werden. Für die p-Dotierung wird hierzu Diboran ( $B_2H_6$ ), für die n-Dotierung Phosphin ( $PH_3$ ) genutzt [SPK<sup>+</sup>08, LSP<sup>+</sup>08]. Der Dotierstoff wird während der Gasphasenreaktion in die Nanopartikel eingebaut, wobei die Dotierstoffkonzentration durch die Konzentration des Dotiergases im Reaktor beeinflusst werden kann.

## 1.2.2 Dispergierprozess und Nanopartikeldispersionen

Die einfachste und kostengünstigste Art, Nanopartikel in elektronische Schaltungen zu integrieren, besteht in der Verwendung von Dispersionen. Bei den verwendeten Dispersionen handelt es sich um ein homogenes Flüssigkeit-Feststoff-Gemisch, auch *Suspension* genannt, bei dem der Feststoffanteil nicht in Lösung geht, sondern erhalten bleibt. Es treten lediglich an der Oberfläche der Feststoffpartikel Wechselwirkungskräfte zwischen dem flüssigen Dispergiermittel und dem Feststoff auf, die die Partikel homogen im Dispergiermittel halten. Befindet sich die Größe der Feststoffteilchen im Größenbereich von 1 nm bis 1  $\mu$ m, so wird die Dispersion auch als *kolloidale Suspension* bezeichnet und der Feststoff als *Kolloid*. Die verwendeten Nanopartikelsuspensionen sind per Definition dieser Gruppe zuzuordnen [LSZ97].

Grundsätzlich werden zwei Ziele in der Kolloidwissenschaft verfolgt: während einige Anwendungen (z. B. die Filterung) eine Vermeidung von kolloiddispersen Systemen erfordert, benötigt der Einsatz von Dispersionen zur Herstellung gleichmäßiger Strukturen eine homogene Verteilung der Feststoffe. Daher ist das Vorliegen einer stabilen Dispersion bis zum Zeitpunkt der Verarbeitung unabdingbar. Im Allgemeinen streben physikalische Systeme stets zum Zustand der geringsten freien Energie; im Speziellen wird dieser Zustand bei Dispersionen durch Annäherung bzw. Zusammenhaftung der Partikel erreicht, da hierbei die freie Oberflächenenergie minimiert wird. Das Dispergiermedium bildet jedoch eine Barriere zum Erreichen des minimalenergetischen Zustandes. Eine Suspension ist demzufolge metastabil, d. h. sie ist solange stabil bis genügend Energie zur Verfügung steht, die Barriere zu überwinden und dem energetisch günstigeren Zustand entgegenzustreben. Die Wechselwirkungen, die die Eigenschaften eines kolloidalen Systems maßgebend beeinflussen, sind:

- zwischenmolekulare Kräfte,

- zwischenpartikuläre Kräfte,

- Wirkung des umgebenden Mediums,

- elektrostatische Kräfte

- und sterische Abstoßung.

Der Verlauf der Wechselwirkungsenergie zeigt in Abhängigkeit vom Abstand neben dem primären Energieminimum, das eine Zerstörung der Suspension bedeutet, ein sekundäres, flaches Minimum. Liegt die Tiefe dieses Minimums in der Größenordnung von wenigen  $kT$ , so bilden sich schwach gebundene Aggregate (Flocken), die jedoch leicht wieder zu lösen sind [Ever92].

Die Wahl des Dispergiermediums nimmt eine entscheidende Rolle für die Stabilität der Dispersion ein. Zumeist werden polare Flüssigkeiten genutzt, da diese eine ausreichende Barriere ausbilden können, um eine Reagglomeration zu vermeiden [RVG<sup>+</sup>08]. Die verwendeten Nanopartikeldispersionen basieren im Falle von Silizium auf Ethanol und im Falle von ZnO auf Wasser als Dispergiermittel. Sowohl Ethanol- als auch Wassermoleküle sind polar und erfüllen damit die Grundvoraussetzung für die Herstellung stabiler Suspensionen. Die Herstellung geschieht unter Mischung des Feststoffes in nanopartikulärer Pulverform, des Dispergiermittels und Zirkoniumoxid als Mahlstoff in Rührwerksmühlen. Zusätzlich können noch Dispergieradditive hinzugefügt werden, die die Stabilität der Suspension darüber hinaus verbessern. Auf die Verwendung solcher Additive wird jedoch in den Dispersionen, die zur Verfügung stehen, verzichtet. Das Zirkoniumoxid dient dem Eintrag von mechanischer Energie in das Kolloidsystem, wodurch zum Einen ein Aufbrechen von bereits bestehenden Agglomeraten, d. h. die Dispergierung von Primärpartikeln erreicht wird, und zum Anderen die Partikel noch kleiner zermahlen werden können. Der Energieeintrag kann eine strukturelle Veränderung der Nanopartikel bewirken. So wird beobachtet, dass ein zu langer Mahlvorgang die Kristallstruktur von Silizium-Nanopartikeln bis hin zur Amorphisierung verändert und damit auch die elektrischen Eigenschaften entscheidend verschlechtert [RAA<sup>+</sup>07].

Die verwendeten Dispersionen zeigen unabhängig vom Feststoffanteil eine ausreichende Stabilität [GHW10]. Die Silizium-Nanopartikeldispersionen zeigen mindestens für einen Monat, die Zinkoxid-Dispersionen mindestens für drei Monate keinerlei Veränderungen (z. B. Auftreten einer Phasenseparation).

### 1.2.3 Physikalische und elektrische Eigenschaften von Nanopartikeln

#### Allgemeine Eigenschaften von Nanopartikeln

Im Vergleich zu Schichten gleicher Materialien, die mittels physikalischer Gasphasenabscheidetechniken (PVD) oder chemischer Gasphasenabscheideverfahren (CVD) hergestellt werden, weisen Nanopartikel entscheidende Unterschiede auf. Die vorliegende Arbeit beschäftigt sich ausschließlich mit Nanopartikeln aus Silizium und Zinkoxid, so dass anhand dieser beiden Nanopartikelsorten die wesentlichen Eigenschaften von Nanopartikeln erläutert werden.

Das offensichtlichste Merkmal von Nanopartikeln ist ihre äußere Form. Aus der Gasphase synthetisierte Si- und ZnO-Nanopartikel treten in Form von Kugeln bzw. Ellipsoiden auf [WSR01, KWR<sup>+</sup>04, KJK<sup>+</sup>02b, DBH95, Fend98, HHK<sup>+</sup>00, HKD98]. Andere Synthese-Verfahren (z. B. die Sol-gel-Synthese) können ebenfalls diese Partikelformen ergeben [PBD<sup>+</sup>99, YBK<sup>+</sup>99], aber auch Formen wie die sogenannten *Nanorods* (Stäbchenform) [LJJ<sup>+</sup>08]. Als Ausnahme gelang es BAPAT ET AL. kubische Silizium-Nanopartikel zu erzeugen [BGD<sup>+</sup>07]. Zur Erklärung der Effekte in halbleitenden Nanopartikeln wird vereinfachend von sphärischen Partikeln ausgegangen, die bis zur Randschicht eine perfekte einkristalline Struktur aufweisen. Im Fall von Silizium wird von der typischen Diamantstruktur und bei ZnO von der ebenfalls typischen hexagonalen Wurtzitstruktur ausgegangen [Fasc05, Jaga06].

Grenzflächeneffekte spielen in Nanopartikeln und Nanopartikelschichten eine dominante Rolle, da die effektive Oberfläche einer dichtesten Kugelpackung um den Faktor  $\pi/2$  größer als die Grundfläche ist. Die projizierte Dichte oberflächenbedingter Störstellen ist demnach ebenfalls mit  $\pi/2$  skaliert. Chemisch betrachtet führt der Abbruch des Gitters an der Oberfläche zu freien Bindungen, die sehr leicht mit umgebenden Stoffen in Wechselwirkung treten können. Bei Silizium führt diese Eigenschaft in erster Linie zur Bildung einer unterstöchiometrischen Siliziumoxidschicht in Kontakt mit sauerstoffhaltigen Stoffen (Umgebungsluft, Ethanol, etc.) [KWR<sup>+</sup>04, Fend98, PMCK07]. Der Oberflächenprozess ist für Temperaturen unterhalb von 950°C selbstterminierend [LBP<sup>+</sup>94, LGP<sup>+</sup>00, LGH01], wobei die Schichtdicke des umgebenden Oxids ca. 2...5 nm [KWR<sup>+</sup>04] bzw. 10% des Primärpartikeldurchmessers beträgt [HHK99]. Neben der elektrisch isolierenden Wirkung des natürlichen Oberflächenoxides treten an der Grenzfläche zwischen der Siliziumoxidhülle und dem Siliziumkern Ladungszustände auf, die typischerweise in der Summe positiv sind [Hill04, Sze81]. Des Weiteren können dort Störstellenzustände – sogenannte Haftstellen oder *traps* – existieren, die freie Ladungsträger binden. Zinkoxid als Metalloxid hat bereits nahezu vollständig mit Sauerstoff reagiert, so dass keine weitere

nennenswerte chemischen Reaktion mit Sauerstoff im Sinne einer Oberflächenoxidbildung auftritt. Stattdessen können durch Reaktionen des Sauerstoffs bzw. durch die Besetzung von Sauerstofffehlstellen im Kristall reduzierende und oxidierende Prozesse ablaufen, die das elektrische Verhalten bzw. die Halbleitereigenschaften des Materials verändern [MO09, CCDN<sup>+</sup>09, EKS<sup>+</sup>09].

Bisher wurde davon ausgegangen, dass zumindest der Kern der Nanopartikel einkristallin aufgebaut ist. Diese Annahme ist jedoch nicht für alle Partikel gültig. Zwar gibt es eine Vielzahl an Forschungsarbeiten, in denen einkristalline Nanopartikel synthetisiert wurden [KWR<sup>+</sup>04, KJK<sup>+</sup>02b, HHK<sup>+</sup>00], doch wird in anderen Arbeiten auch von amorphen und polykristallinen Partikeln berichtet. Eine Mischform ist ebenso möglich [Fend98, WSR01, DBH95, CDD<sup>+</sup>95]. Dabei ist stets zu beachten, dass Korngrenzen sowohl Rekombinations- und Streuzentren als auch potenzielle Haftstellen darstellen, wodurch die Leitfähigkeit reduziert wird. Die kristalline Struktur lässt sich nicht nur durch die Herstellungsparameter variieren, sondern ist außerdem auch von der Partikelbehandlung, insbesondere vom Dispersionsverfahren abhängig. REINDL ET AL. zeigen, dass Silizium-Nanopartikel mittels einer Rührwerkskugelmühle zwar intrinsisch stabil dispergierbar sind, sich der Amorphisierungsgrad aber von 25% auf 76% verdreifacht [RAA<sup>+</sup>07]. Als Maßnahme gegen eine Amorphisierung lässt sich eine thermische Rekristallisation durchführen [Fend98]. Während der Temperung bilden sich innerhalb der Partikel einzelne Kristalldomänen, die letztendlich an Korngrenzen zusammenführen und somit polykristalline Partikel bilden [RFPB05, HOS06, Fend98]. Die Rekristallisation ist ein bekanntes Verfahren aus der Dünnschichttechnik und wird zum Beispiel bei der Herstellung von Dünnschichttransistoren eingesetzt [HXY06, Hill88, HG92].

Als Grenzfläche ist auch der Übergang zwischen zwei Nanopartikeln, z. B. innerhalb eines Agglomerates, anzusehen. Ein Annealing-Schritt ermöglicht die feste Verbindung der Nanopartikel über Sinterbrücken. Bei Silizium-Nanopartikeln setzt dieser Effekt für Temperaturen oberhalb von 700°C ein [STW<sup>+</sup>08, Fend98, KPL<sup>+</sup>95]. Für Zinkoxid-Nanopartikel zeigen eigene Arbeiten, dass ein sichtbares Zusammenwachsen für Annealing-Temperaturen bereits ab ca. 350°C in Sauerstoffatmosphäre stattfindet [WH10b].

In Abschnitt 1.2.1 wurde bereits erläutert, dass sich auch Silizium-Nanopartikel mit Fremdstoffen dotieren lassen. So ist eine Dotierung mit Bor für p-Halbleiter und mit Phosphor für n-Halbleiter möglich. Es ist jedoch zu beachten, dass einige der oben erwähnten Effekte (Grenzflächen, Korngrenzen, Morphologie etc.) als elektrische Störstellen in Erscheinung treten. Diese Störstellen maskieren den Dotiereffekt dermaßen, dass die Dotierung erst wirksam wird, wenn die Dotierstoffkonzentration die Störstellenkonzentration übersteigt [LSP<sup>+</sup>08]. Weiterhin sind Segregations- und Diffusionseffekte zu beobachten, so dass ein Teil des Phosphors sich während der Bildung an der Grenzfläche zur Oxidhülle vermehrt ansammelt, während bei Bor eine Anreicherung des Siliziumkerns mit dem Dotierstoff stattfindet [LSP<sup>+</sup>08, NA96].

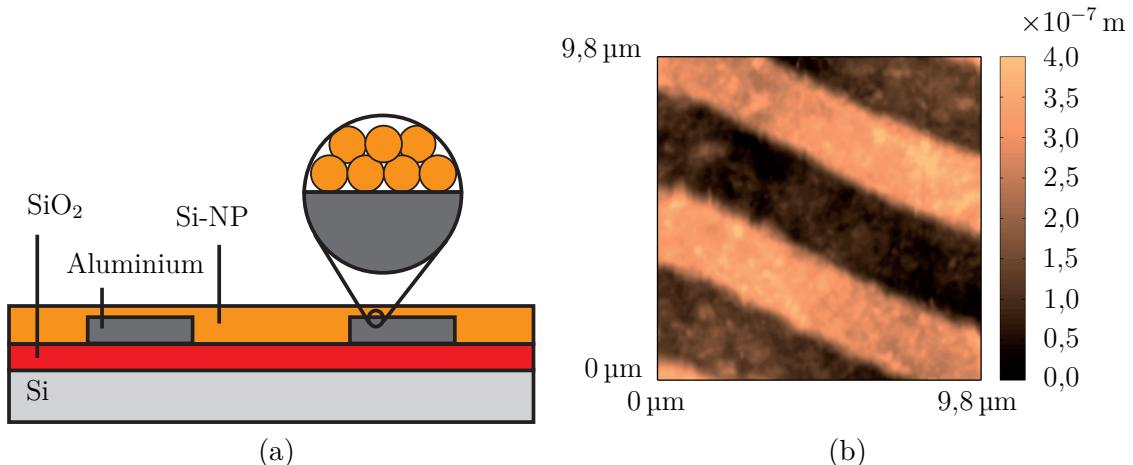

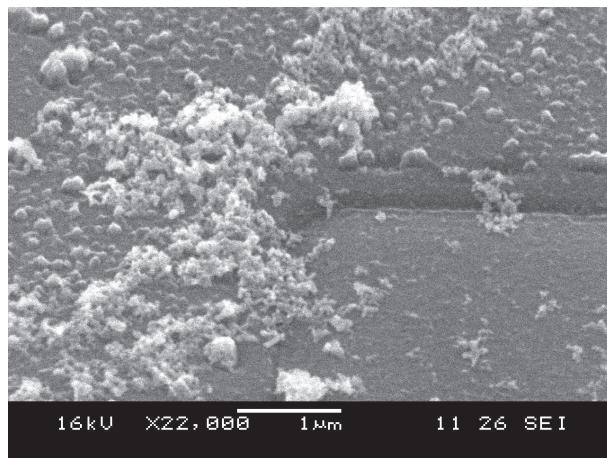

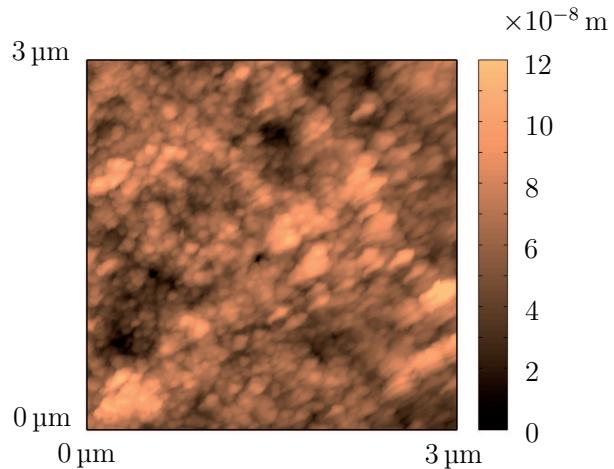

### Charakterisierung der verwendeten Nanopartikel

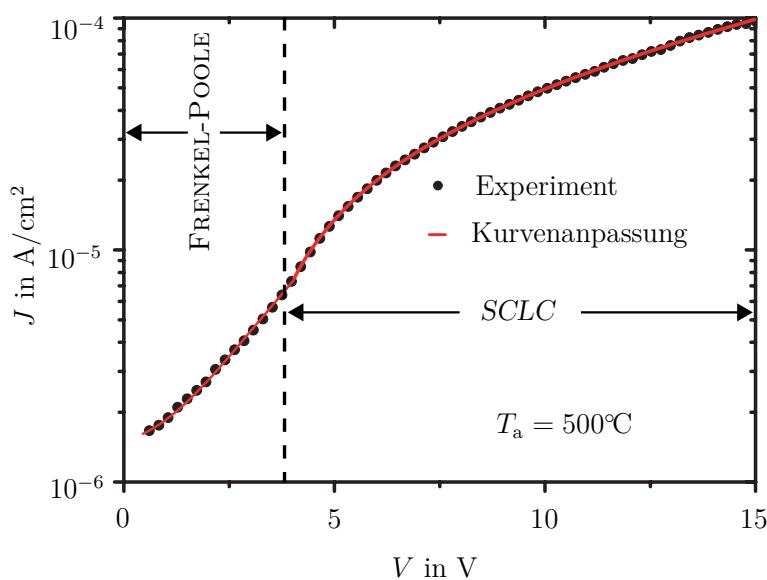

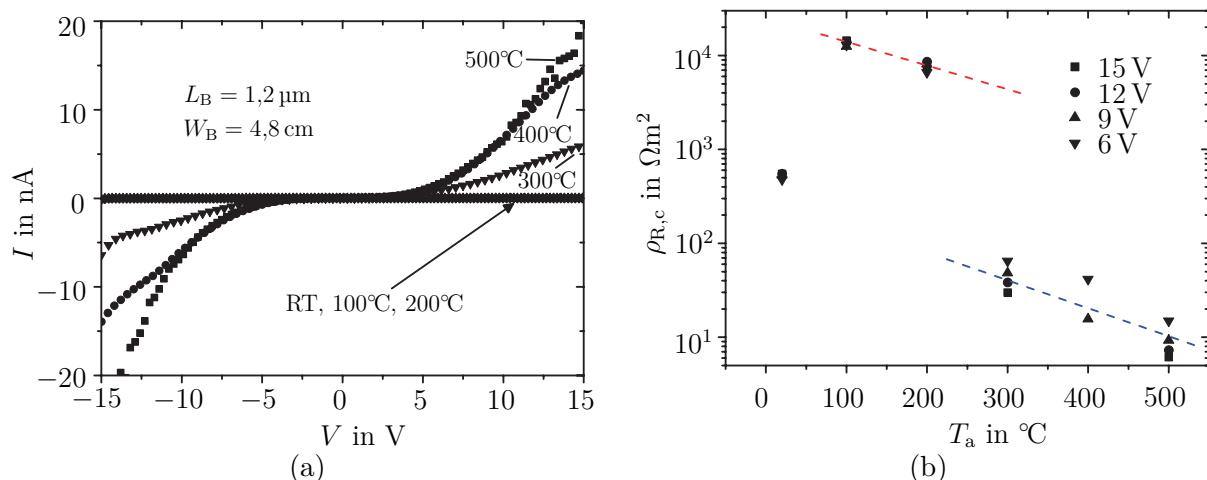

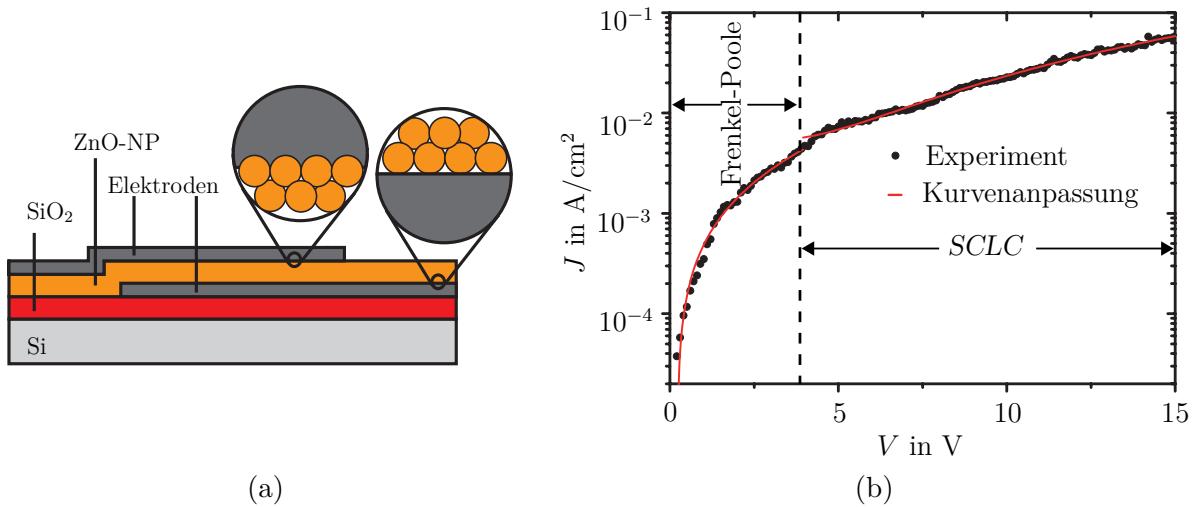

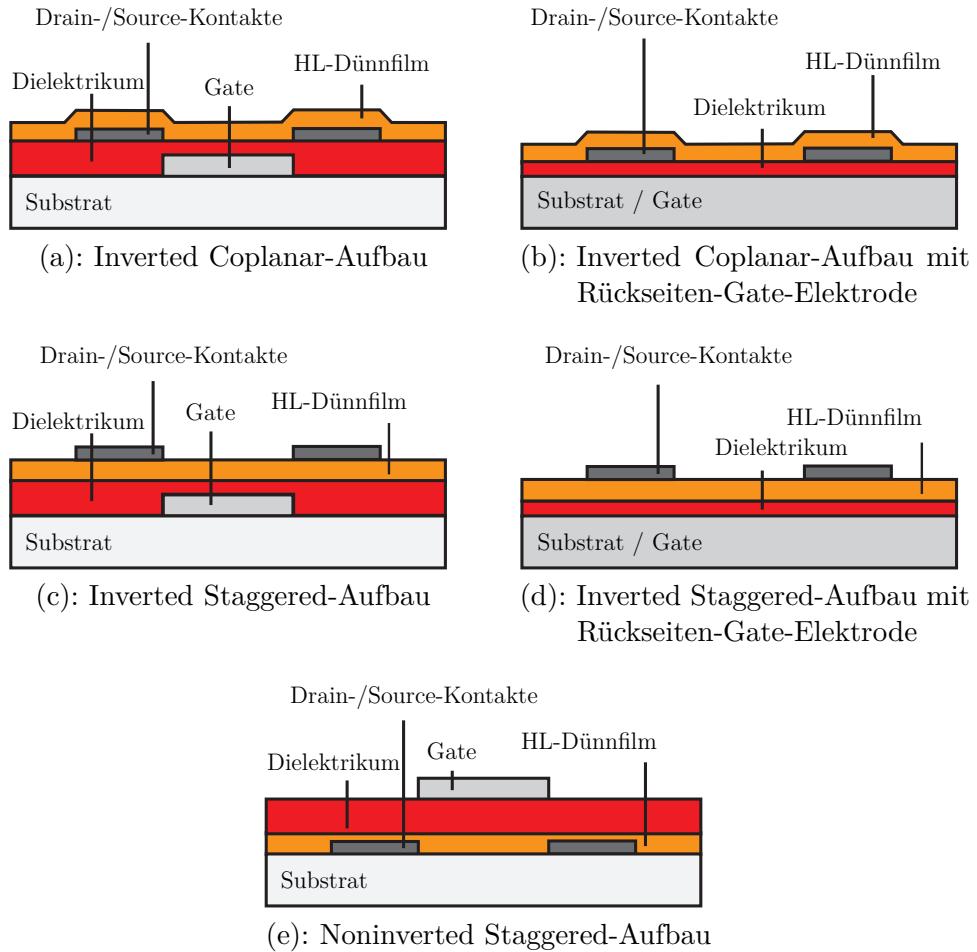

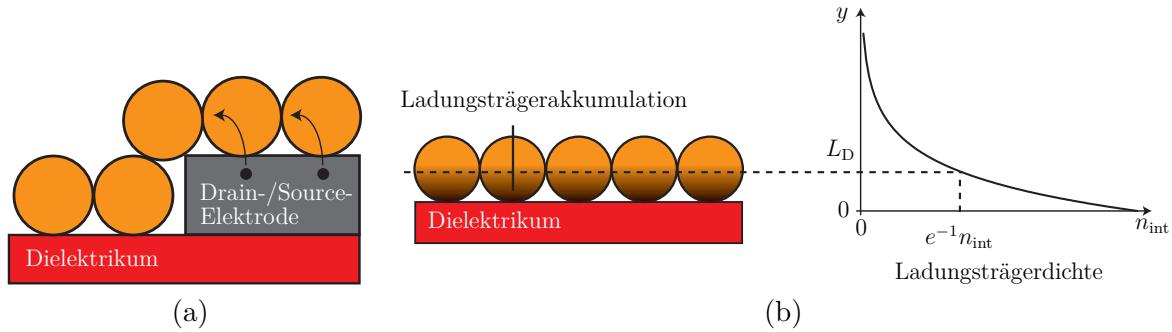

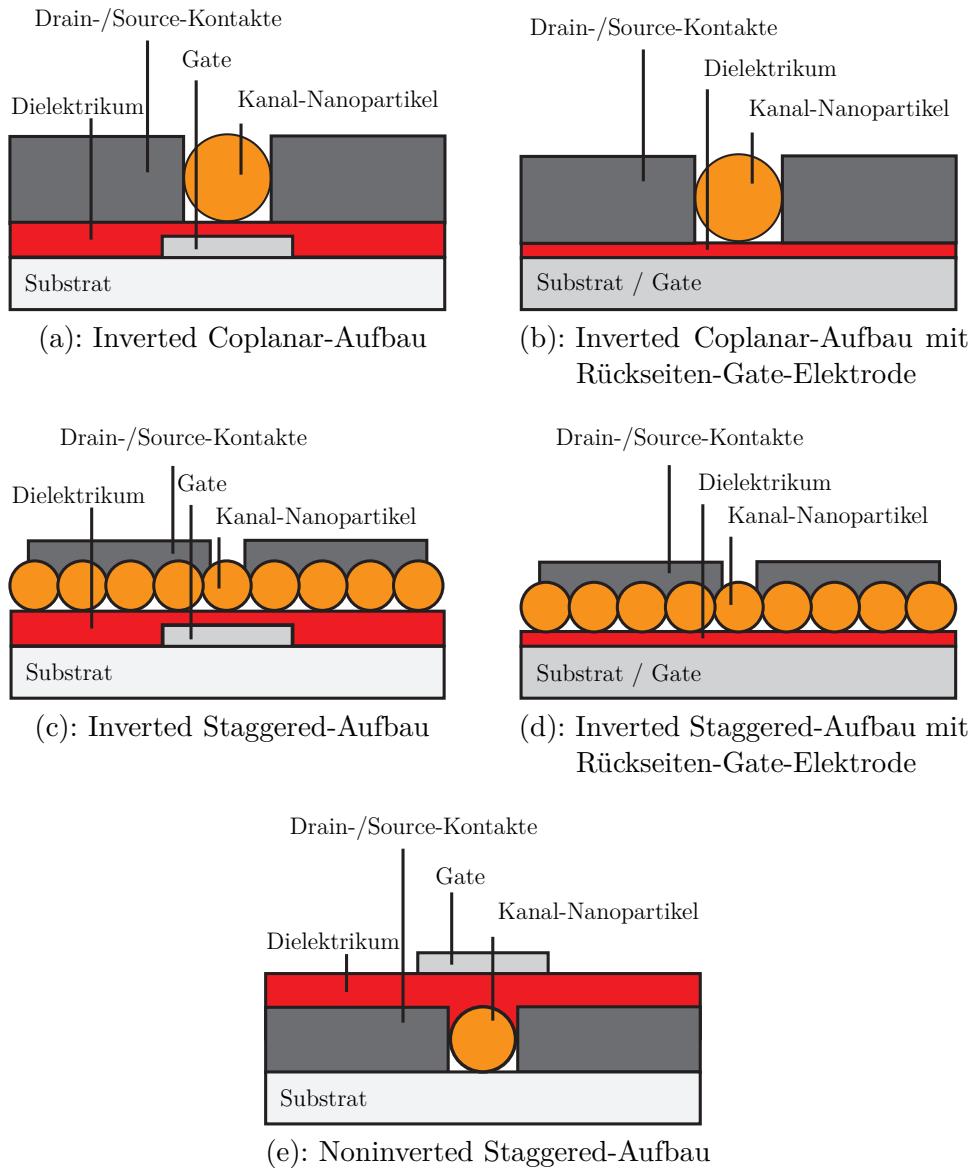

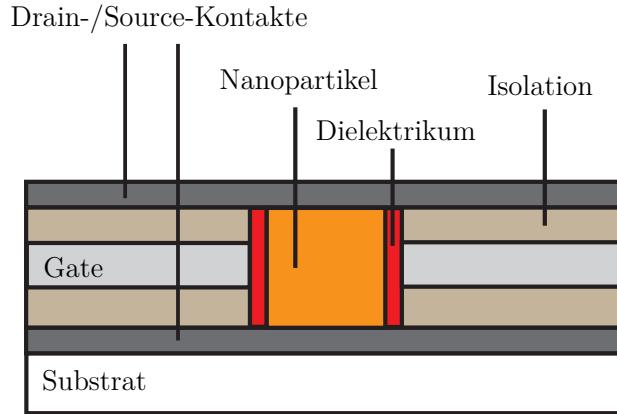

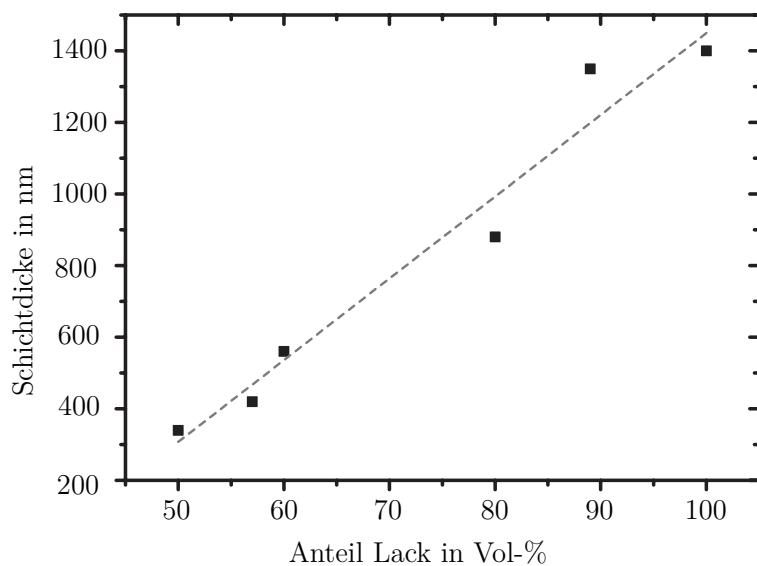

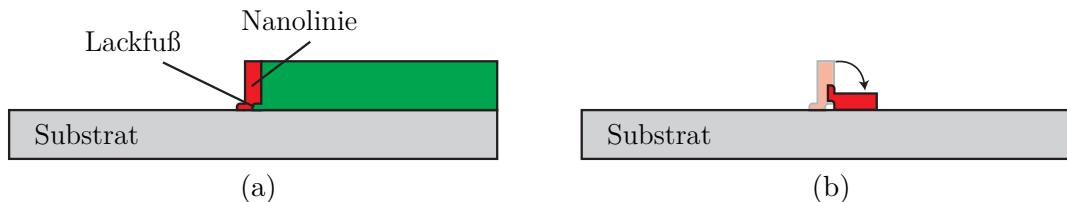

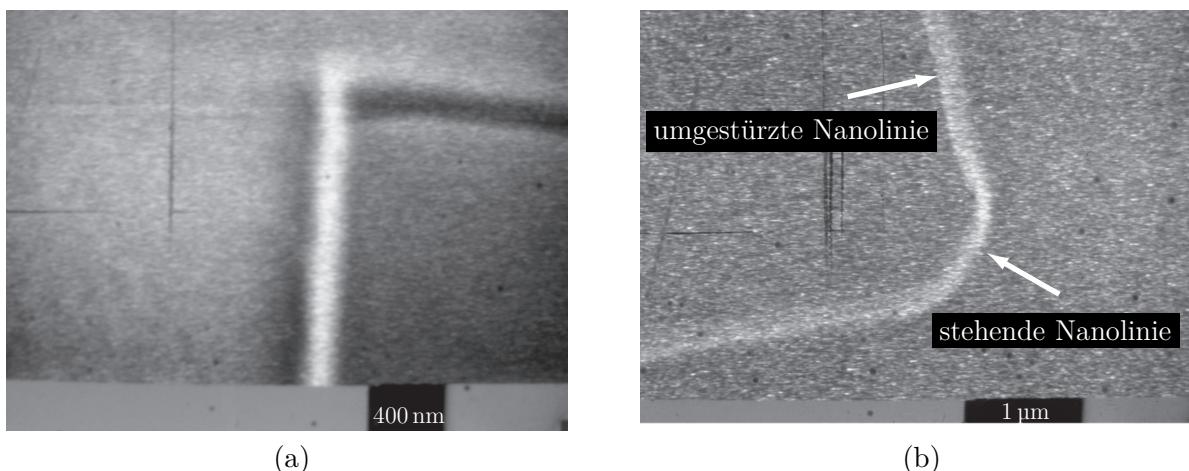

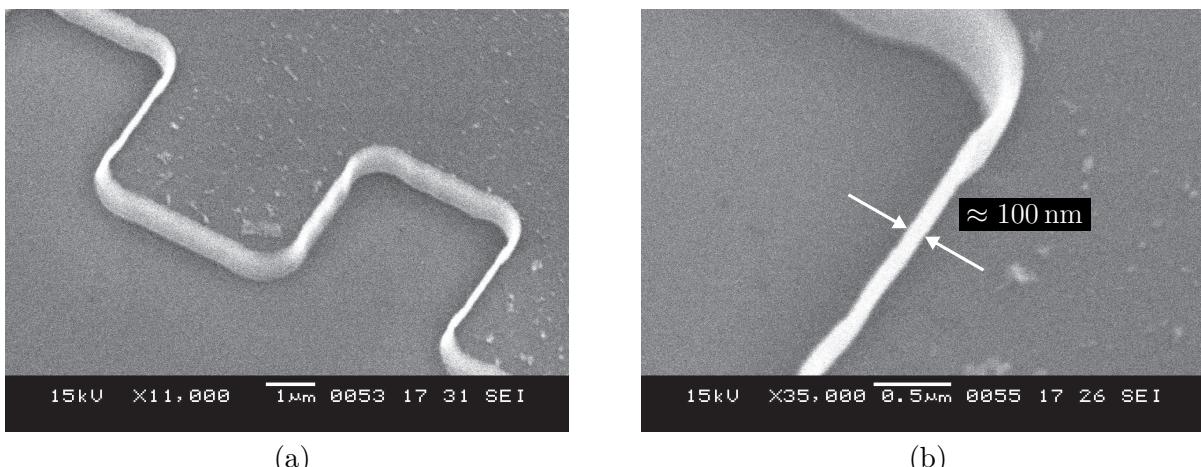

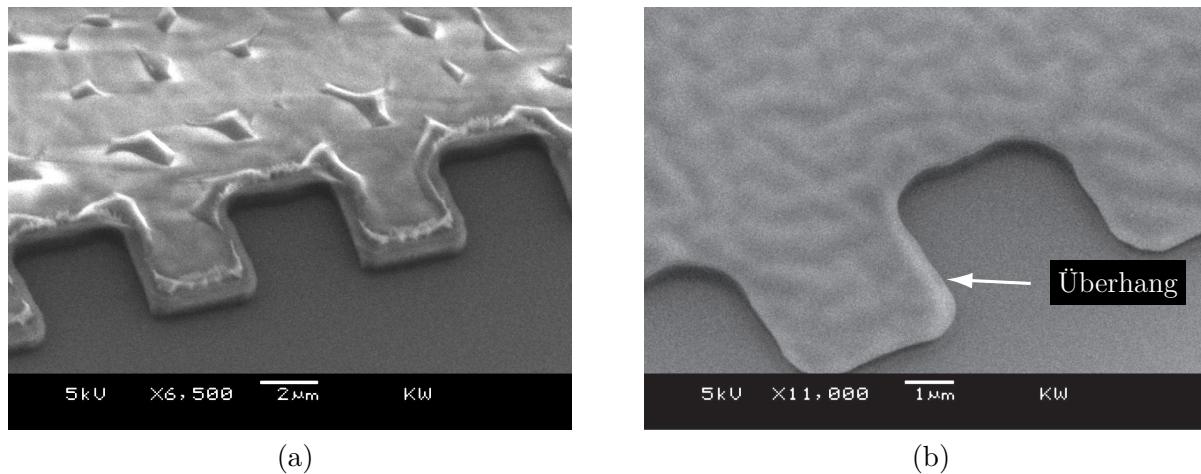

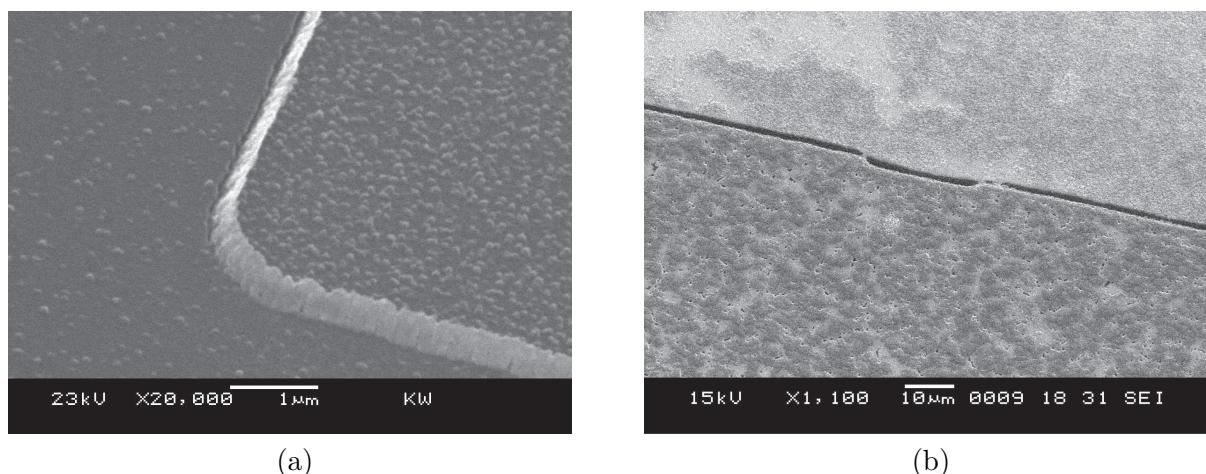

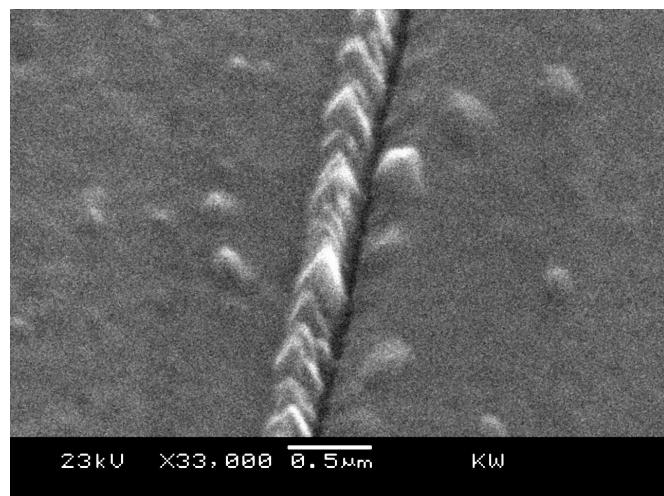

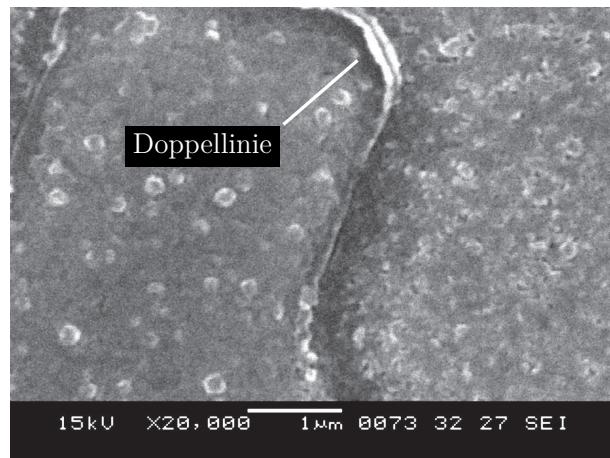

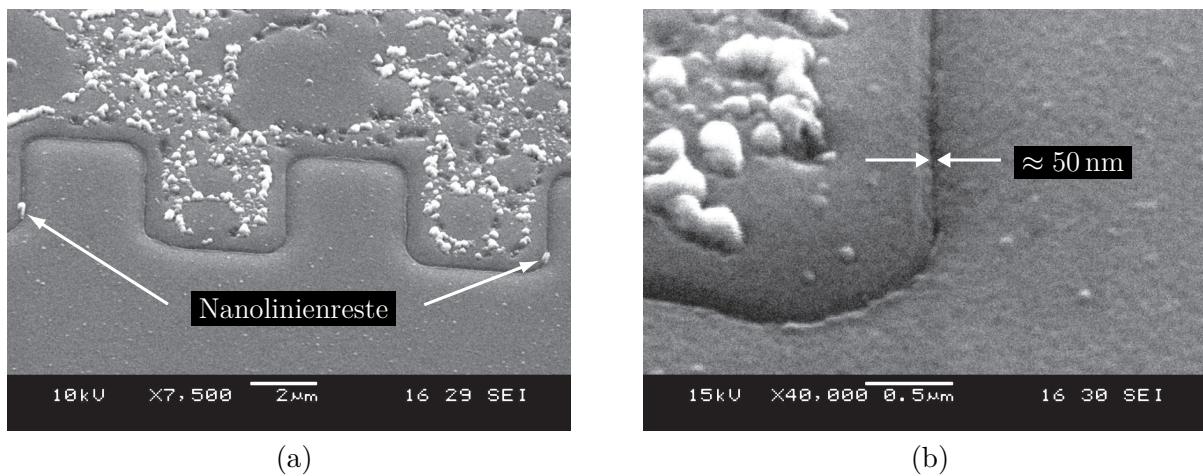

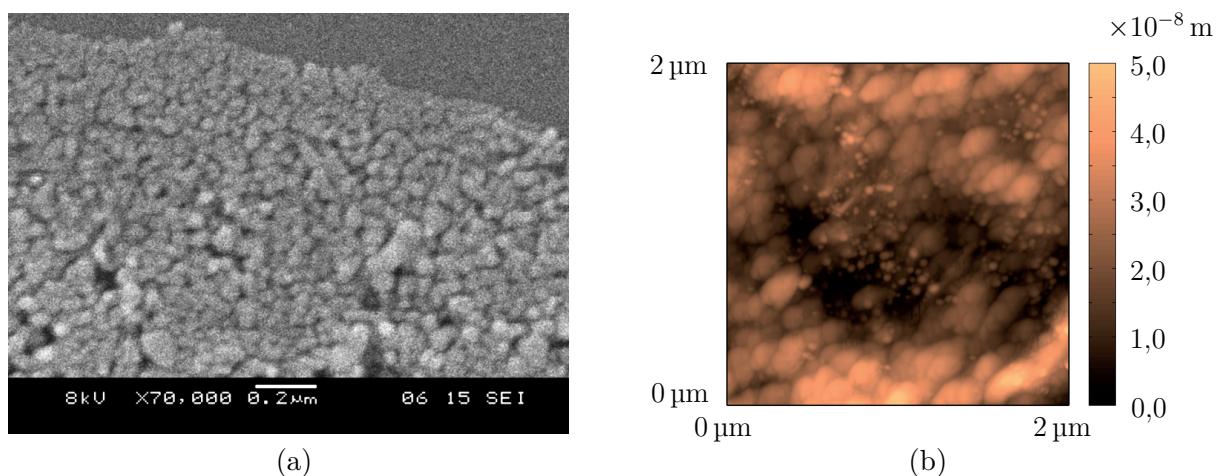

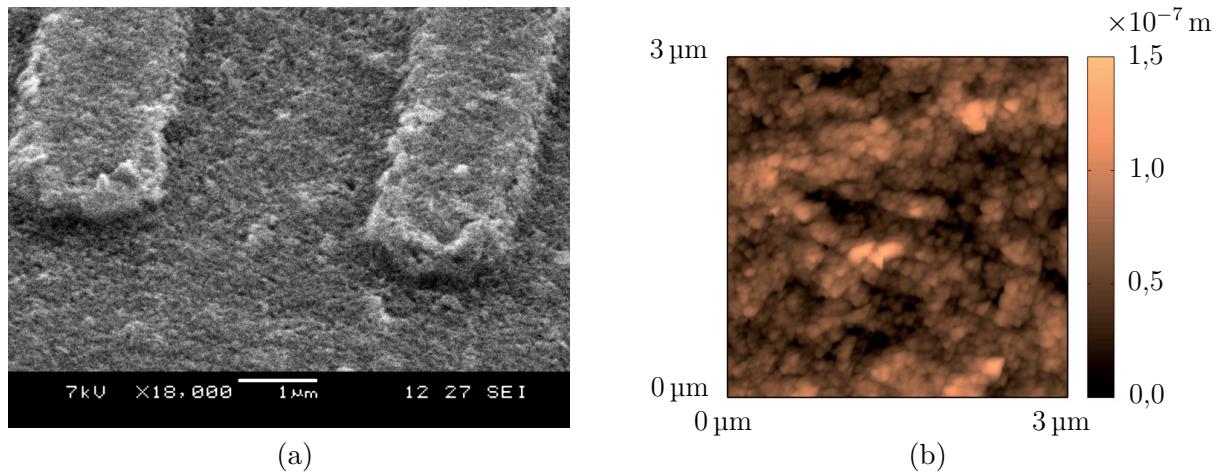

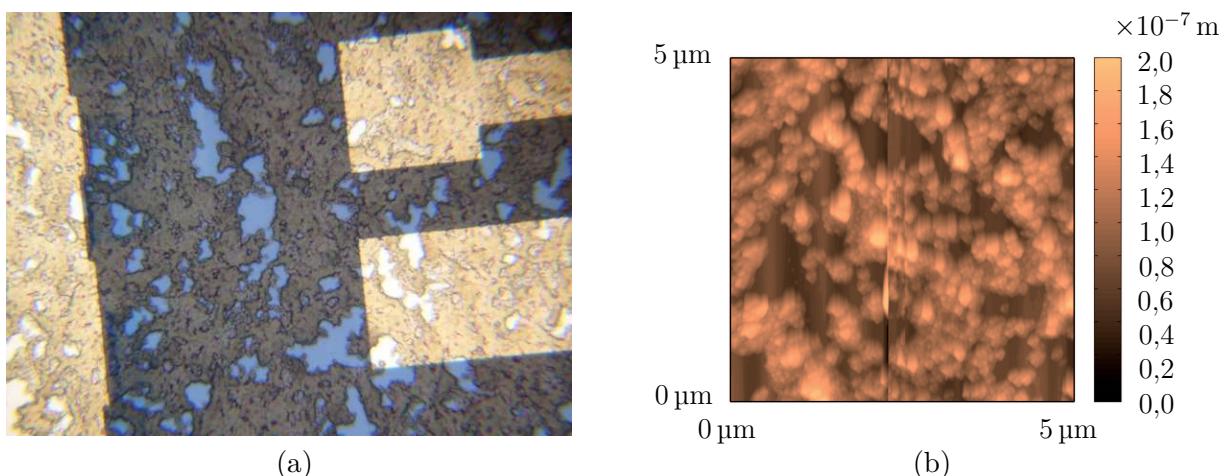

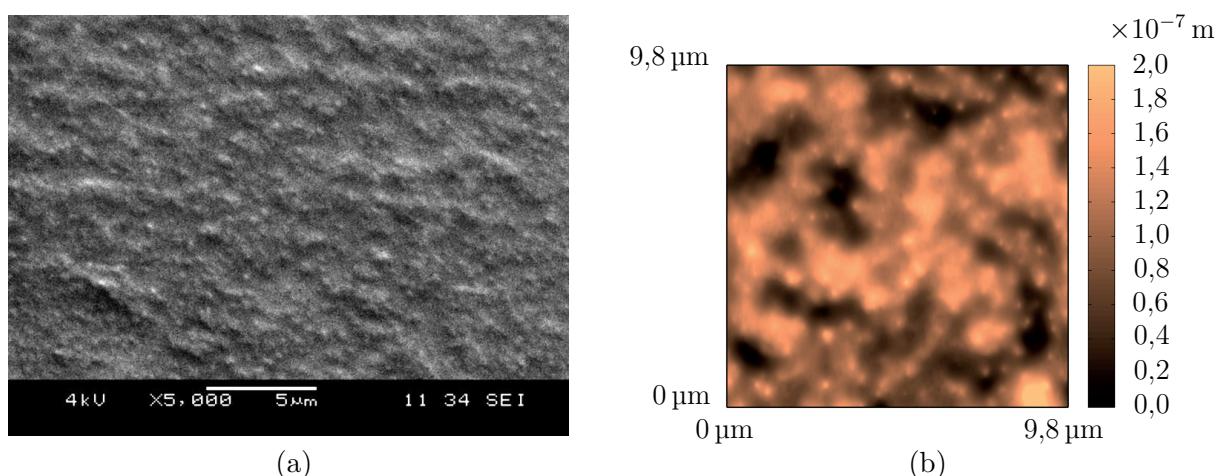

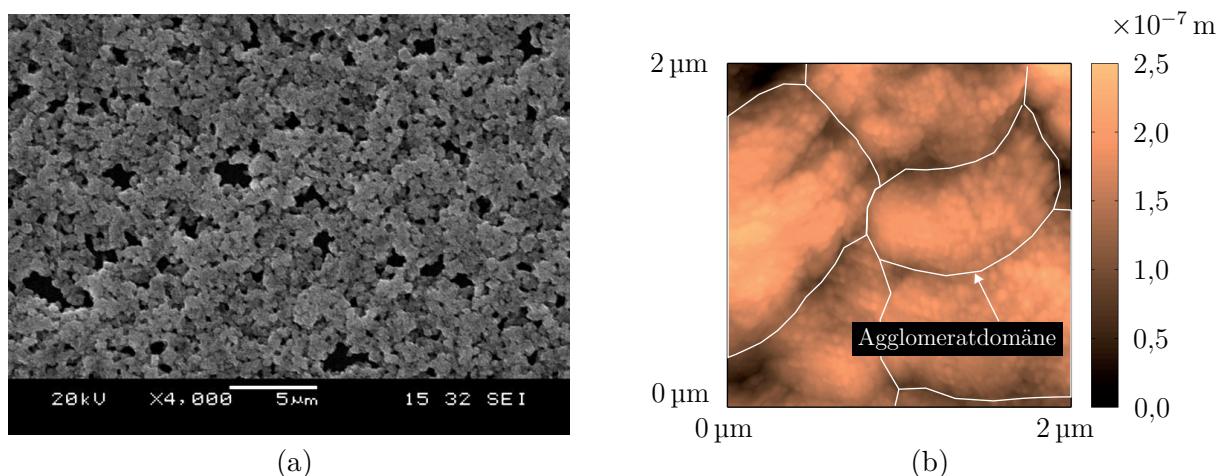

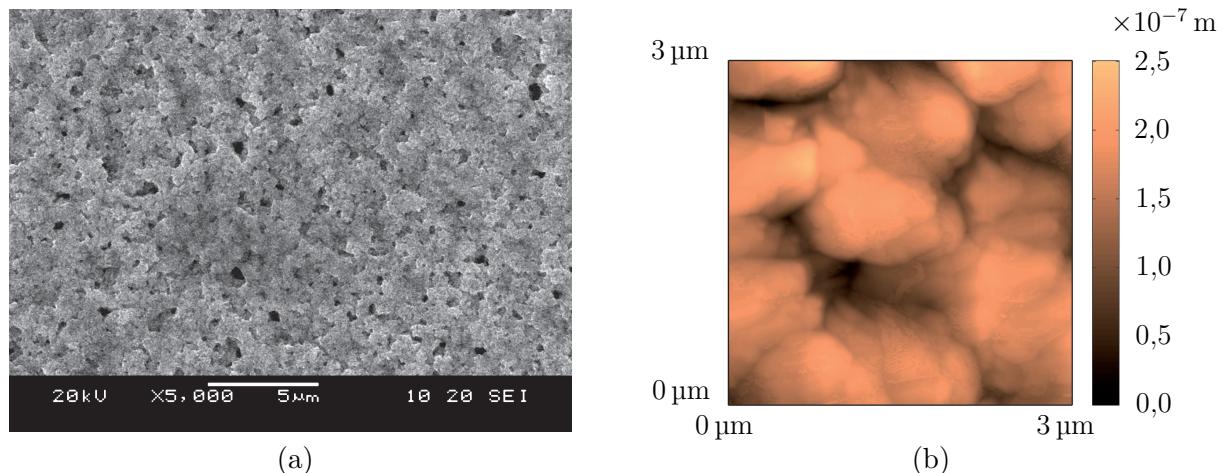

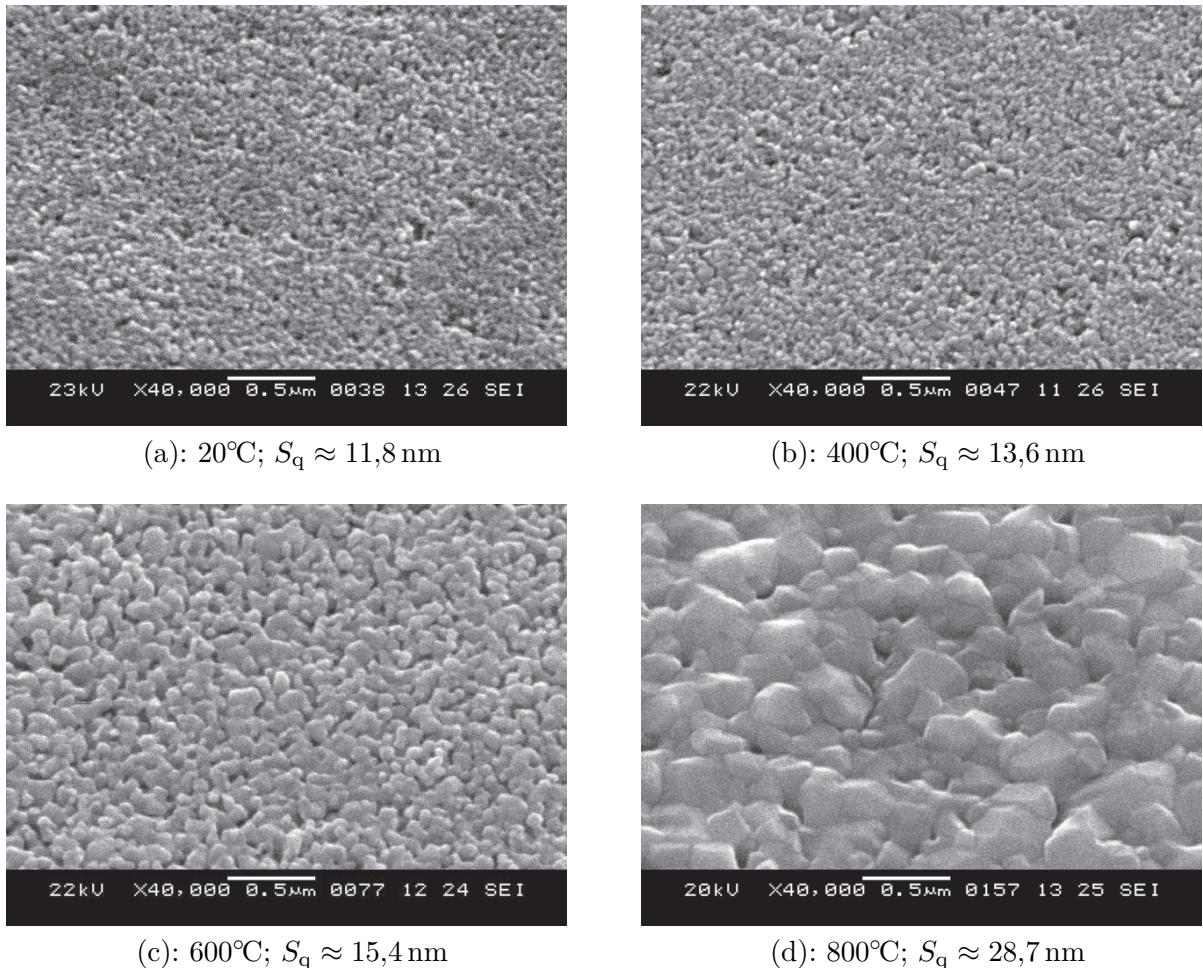

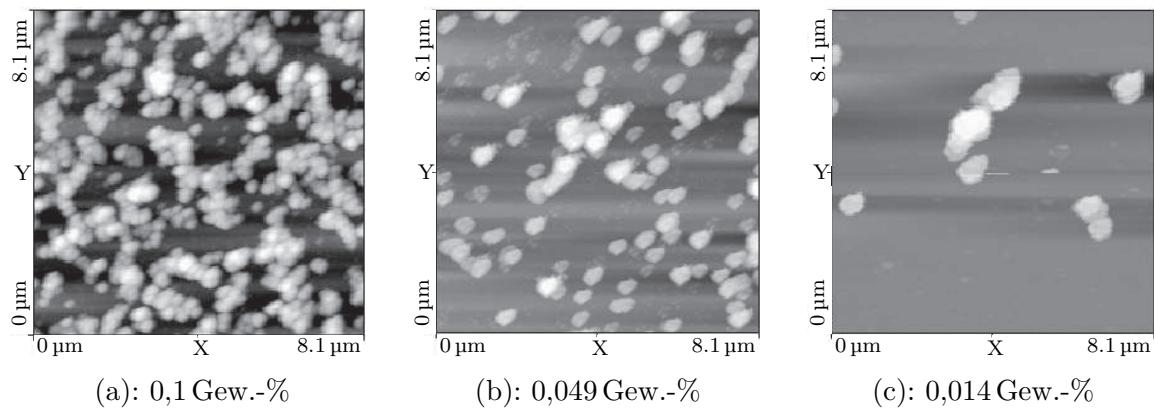

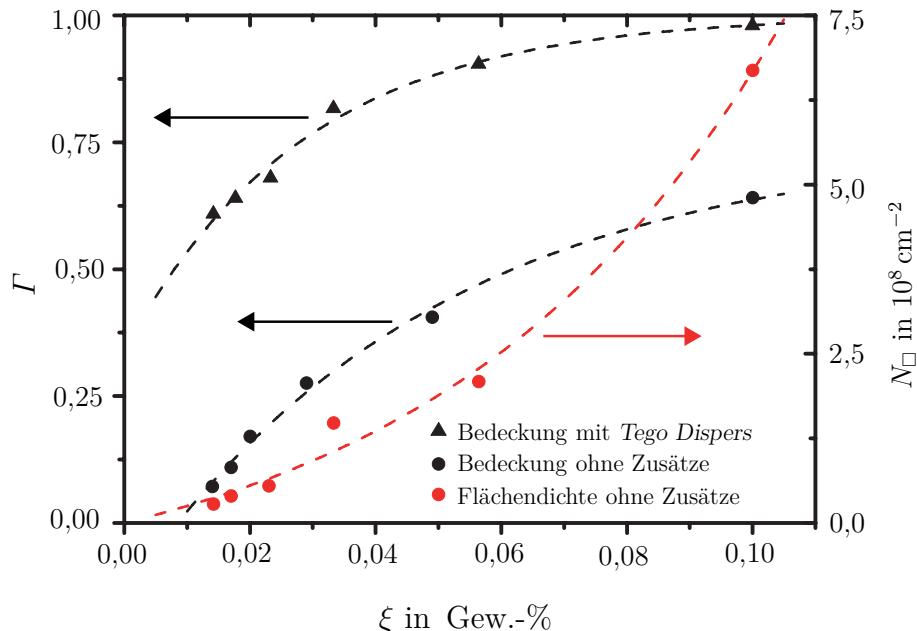

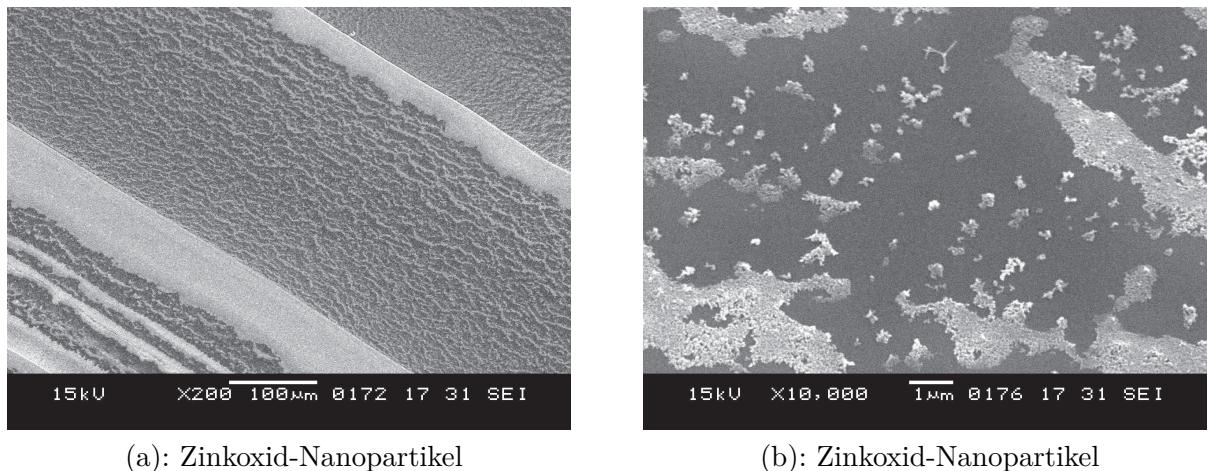

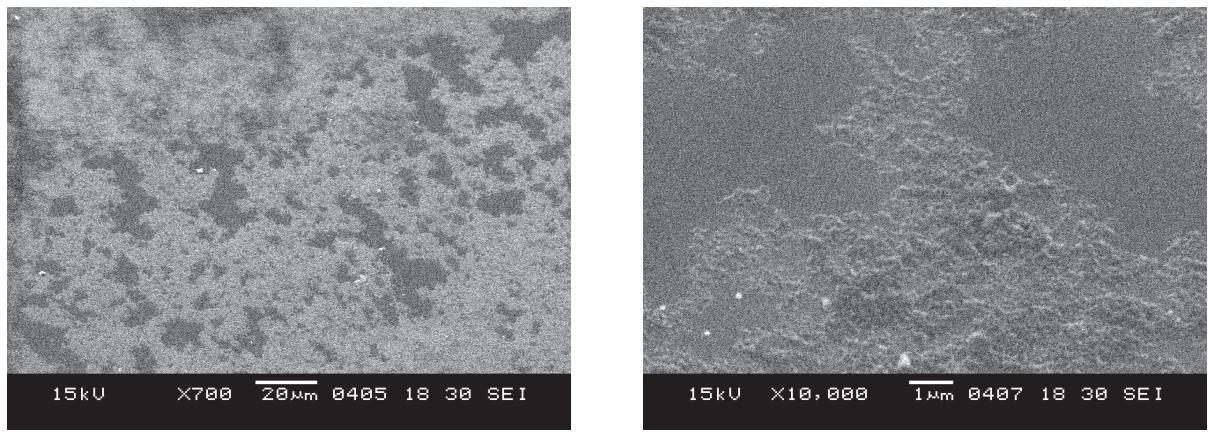

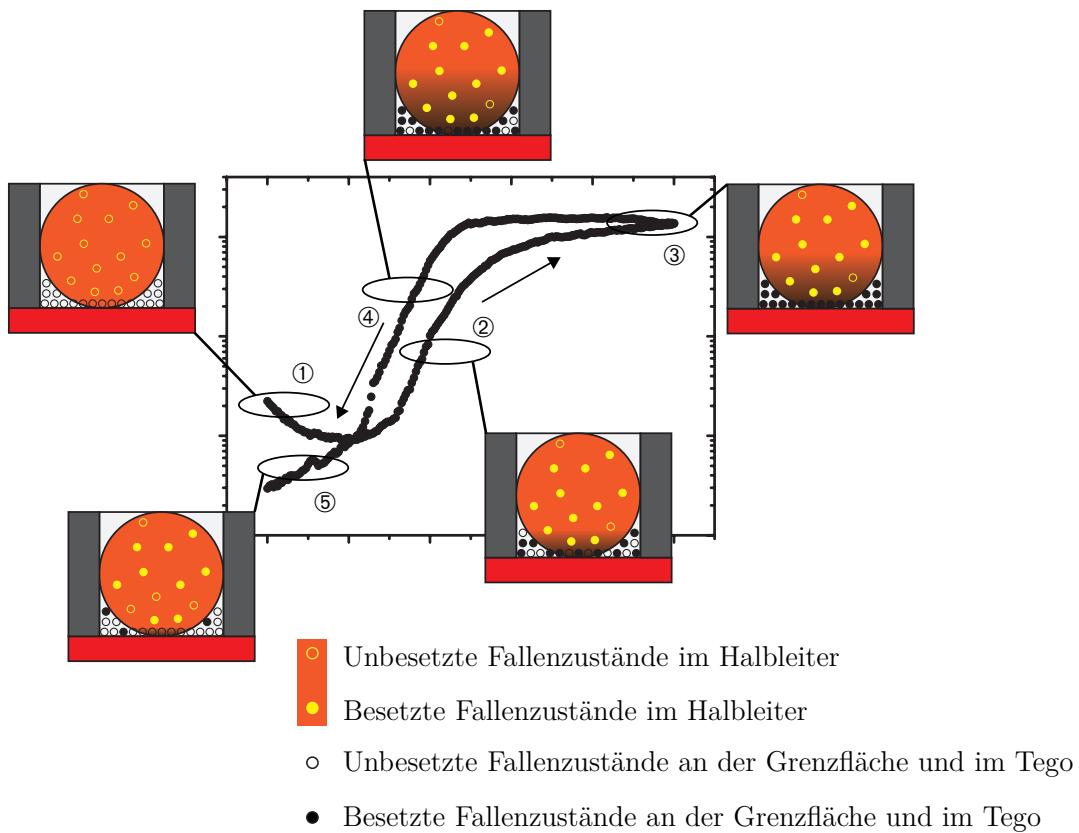

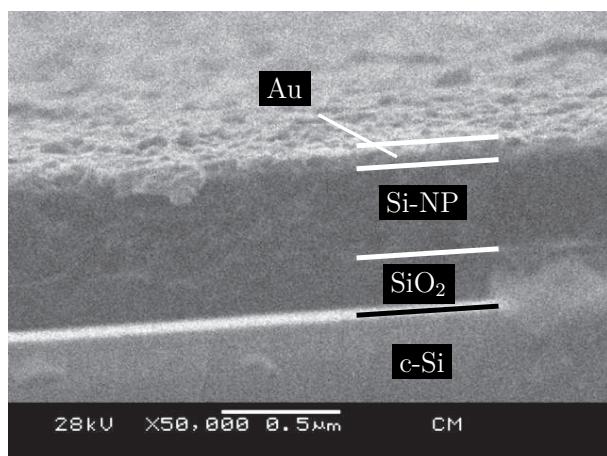

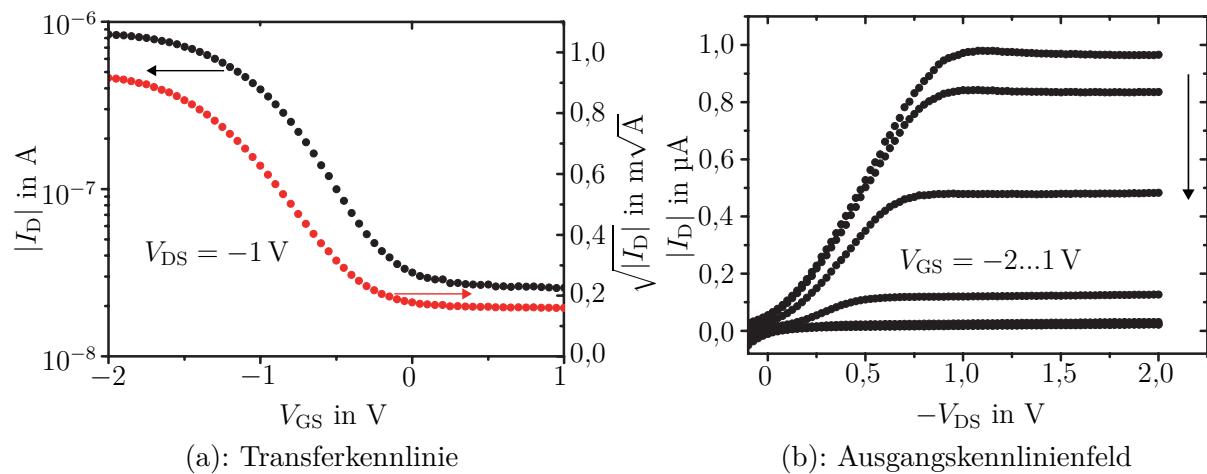

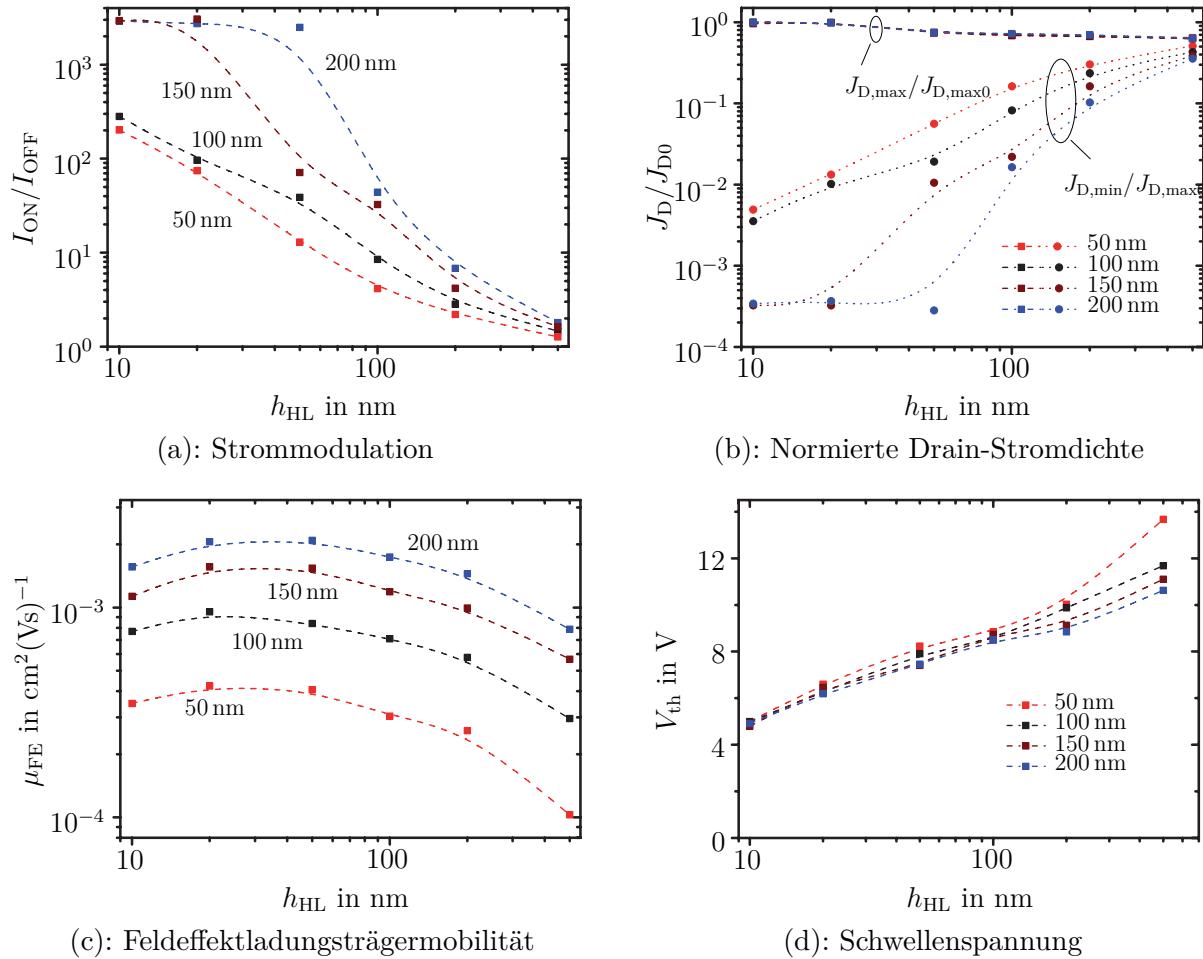

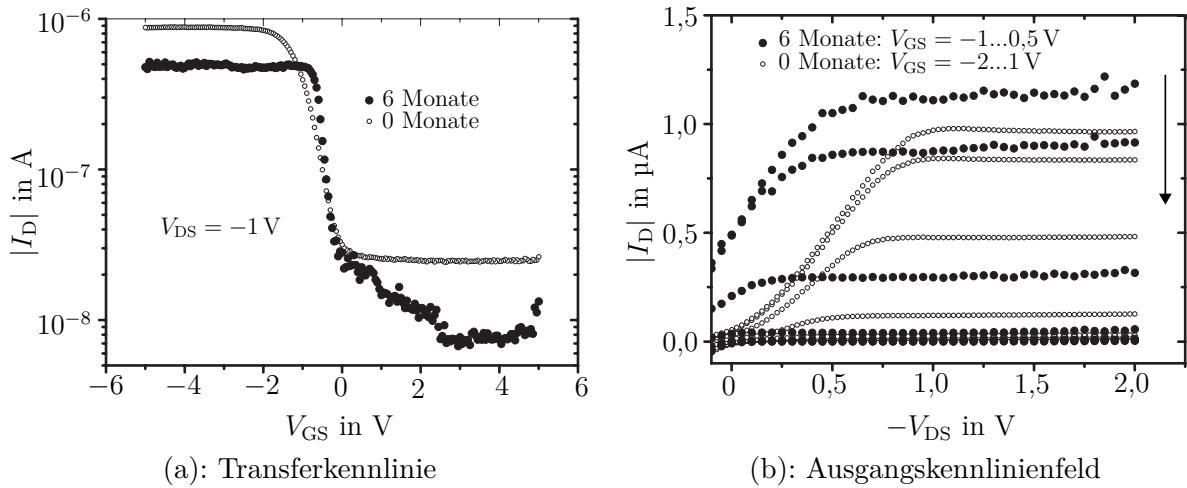

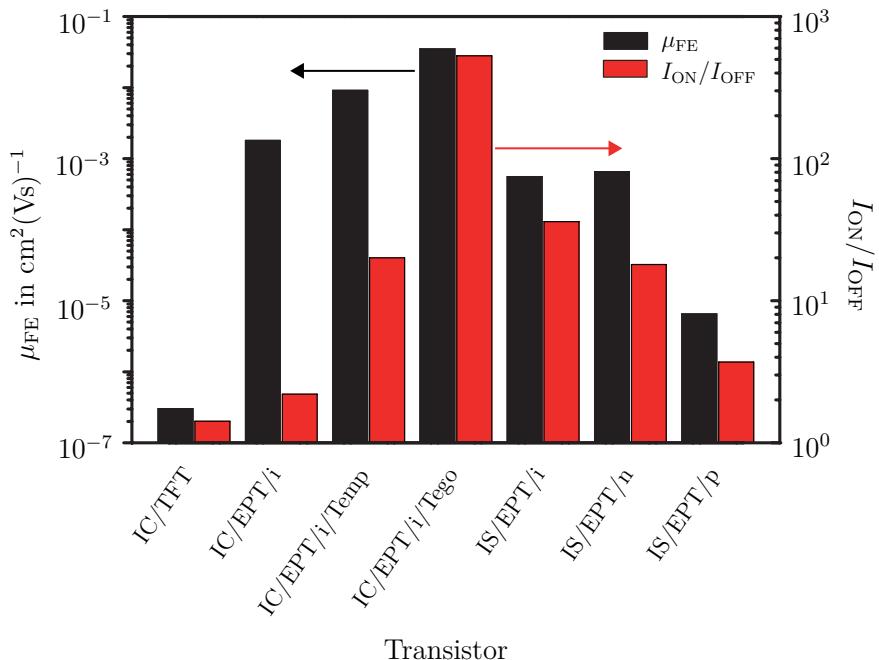

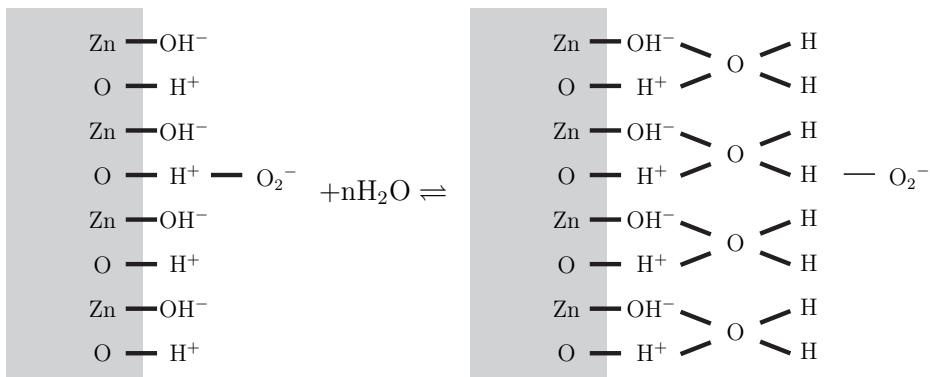

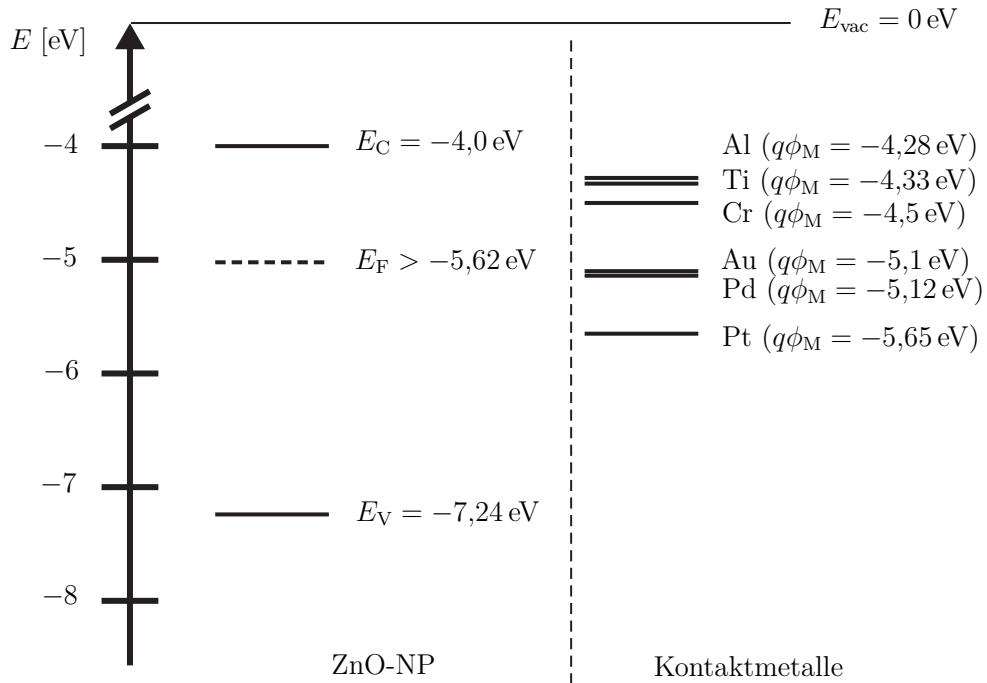

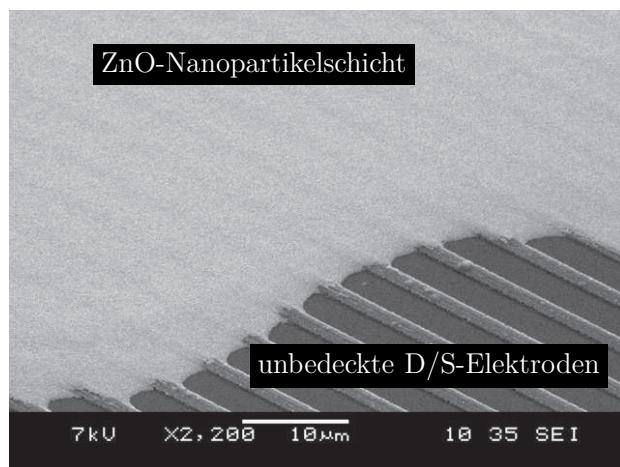

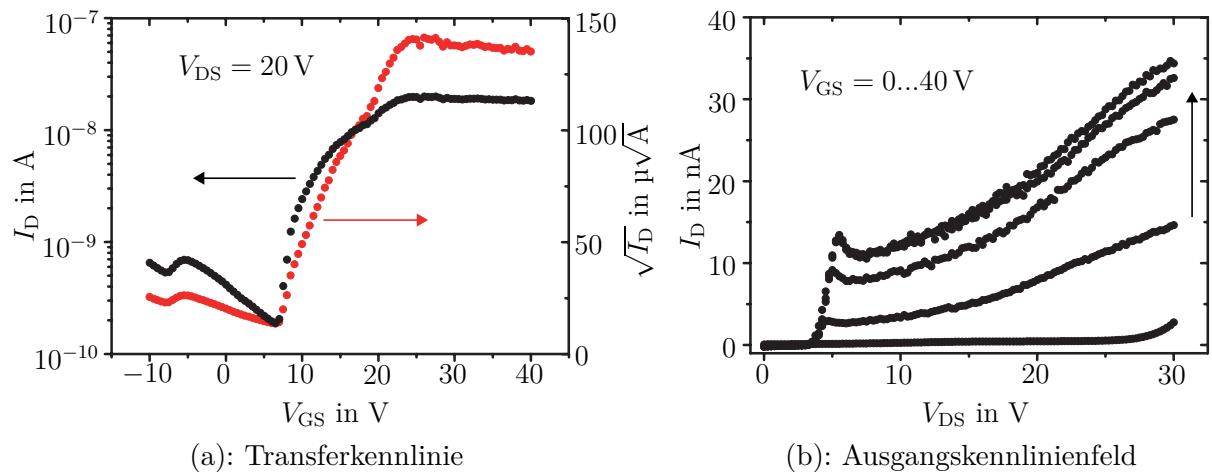

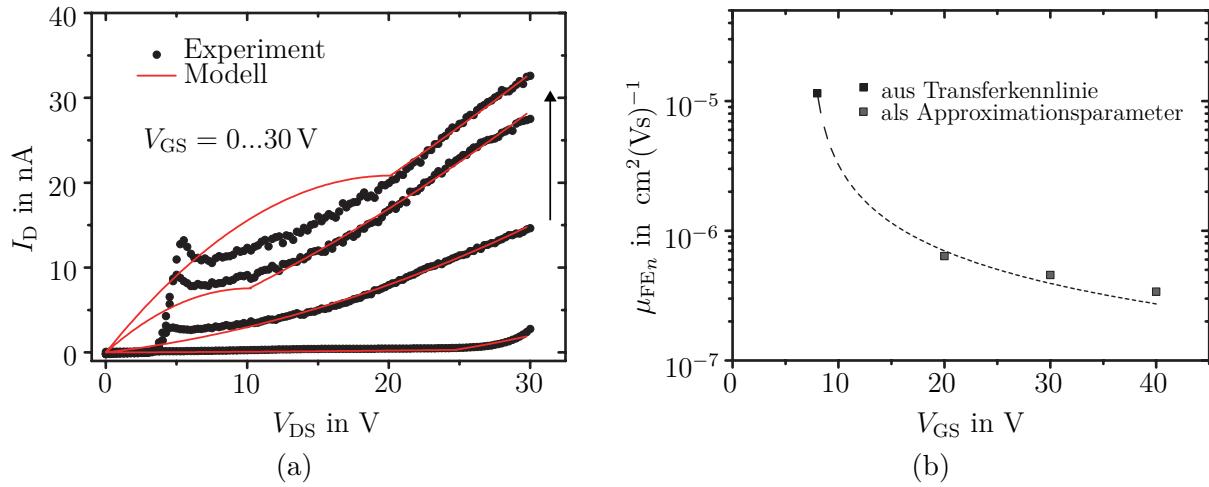

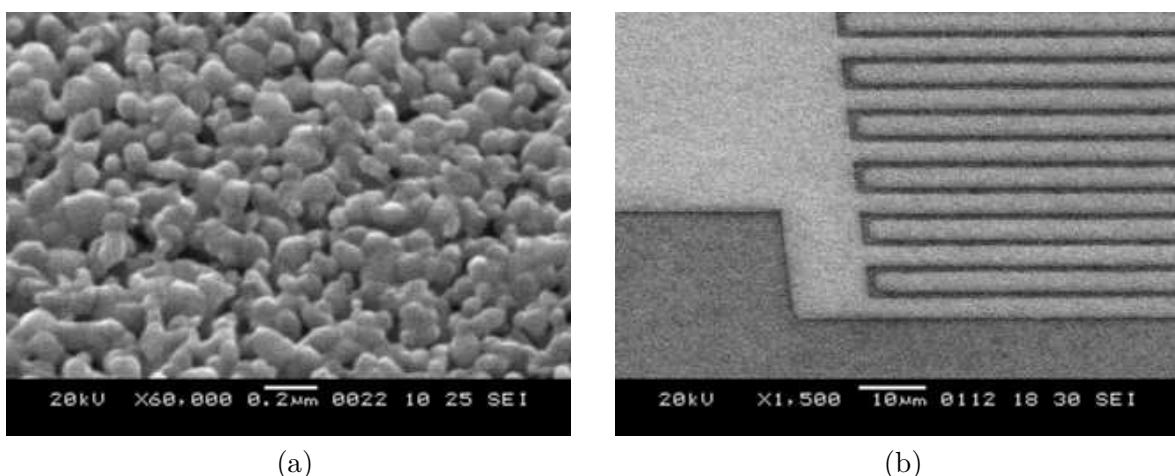

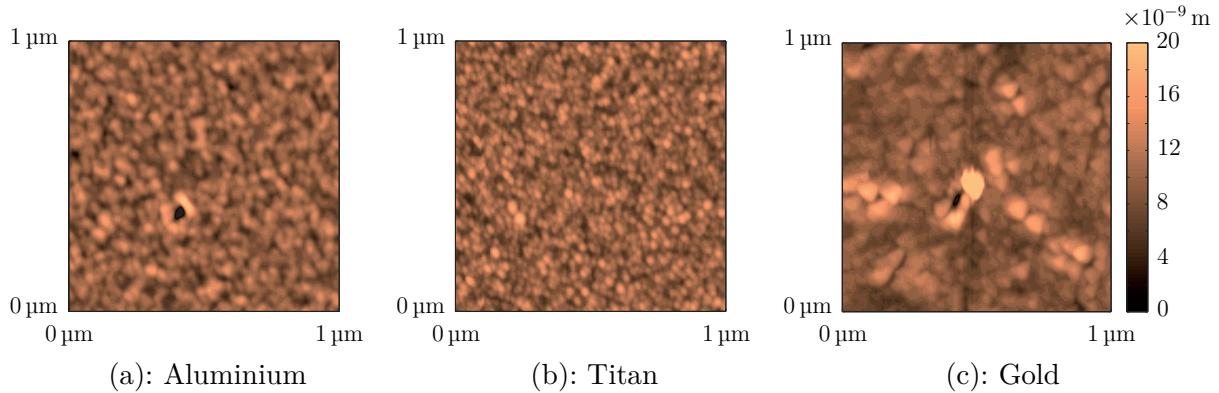

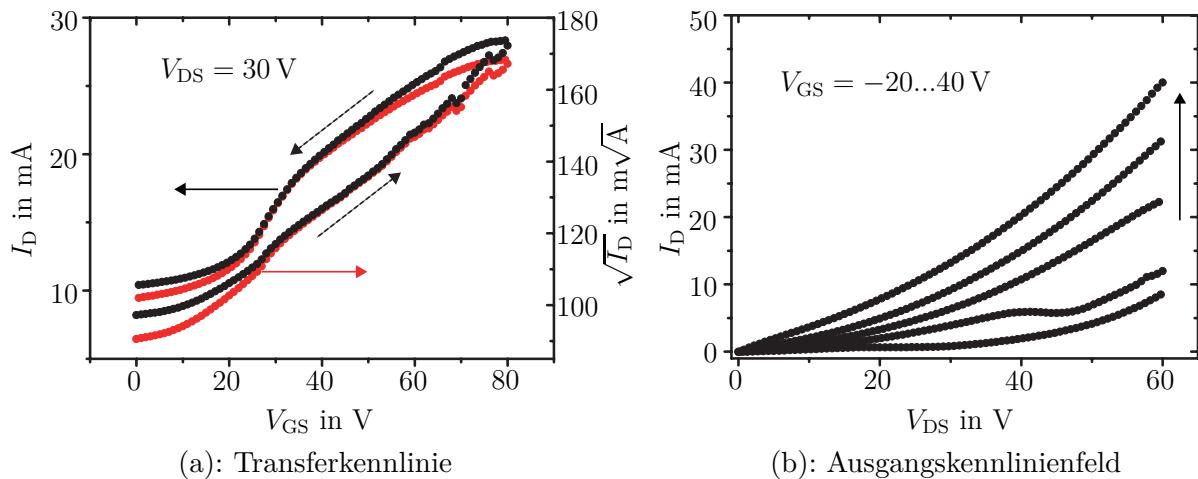

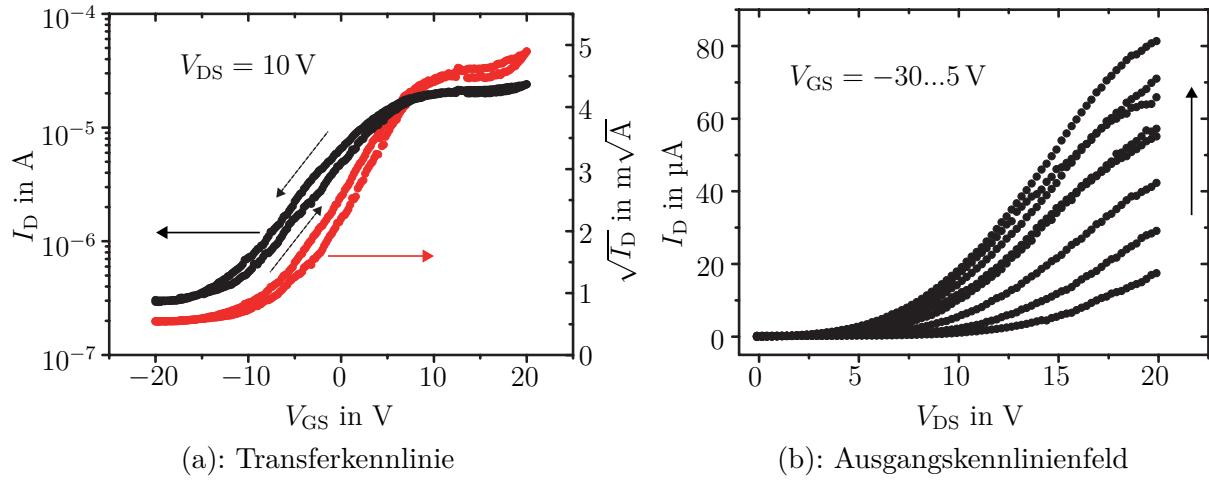

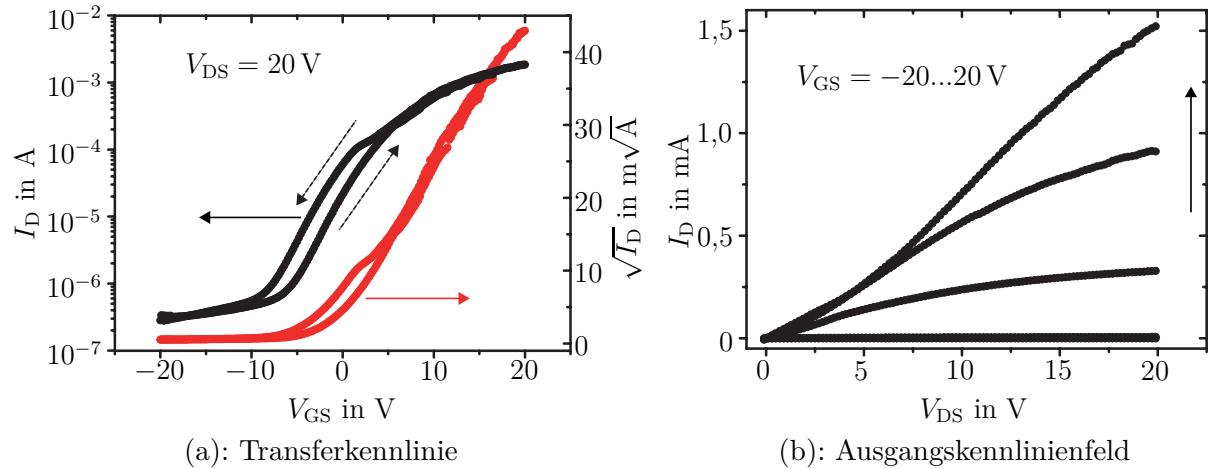

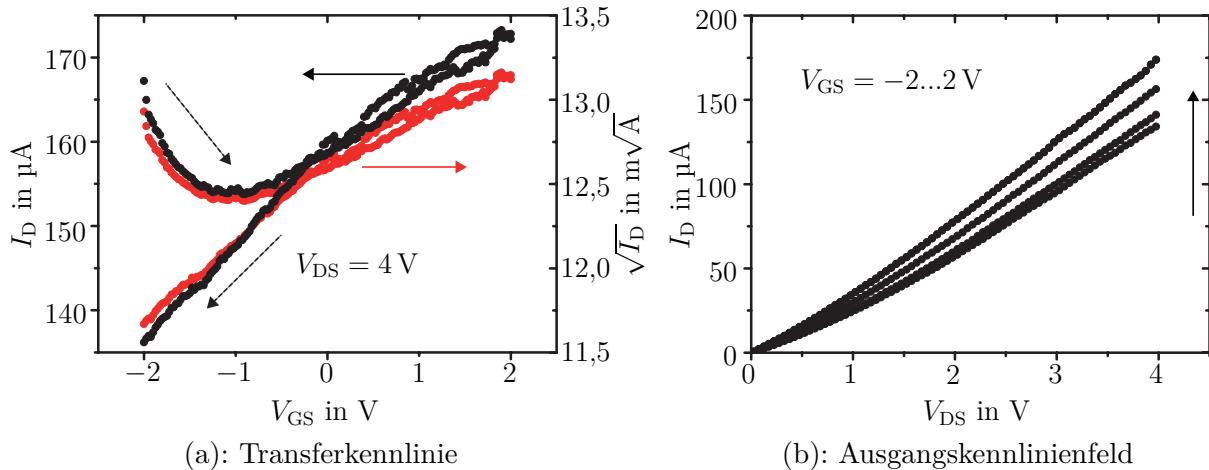

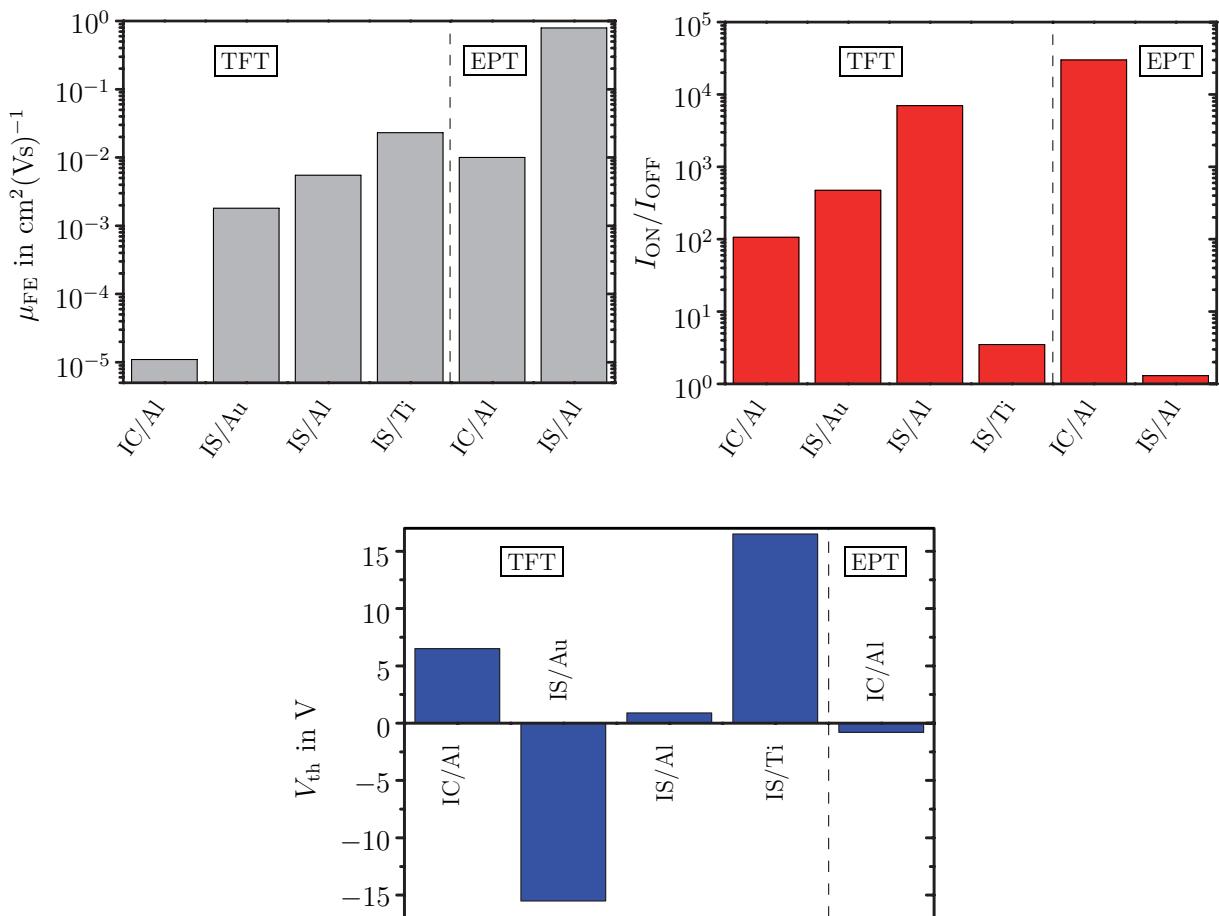

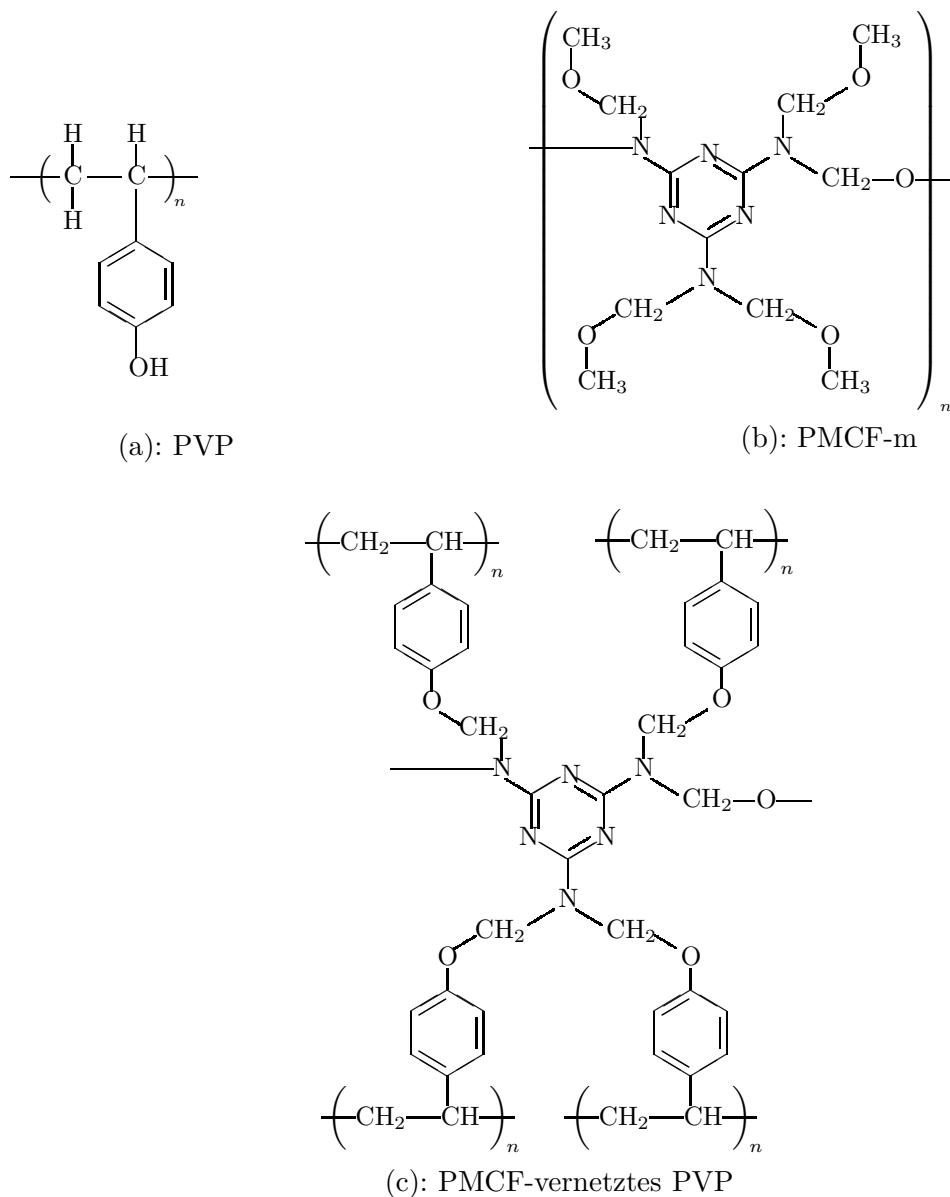

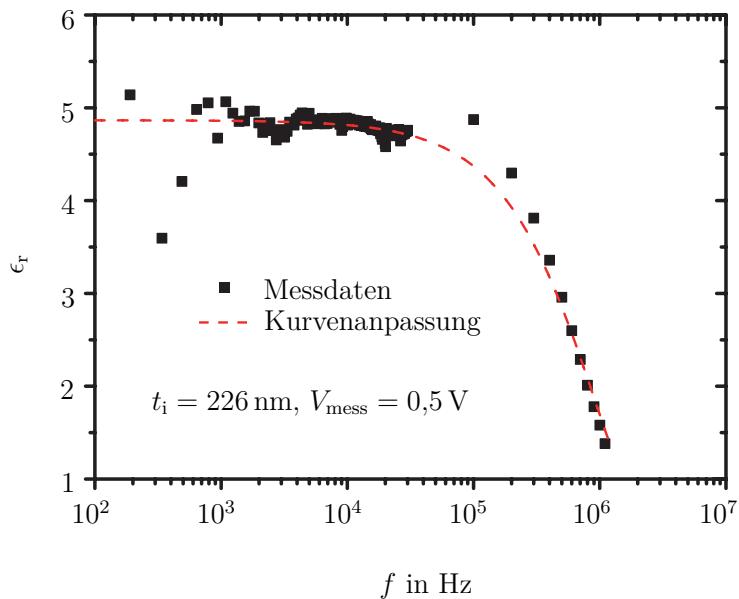

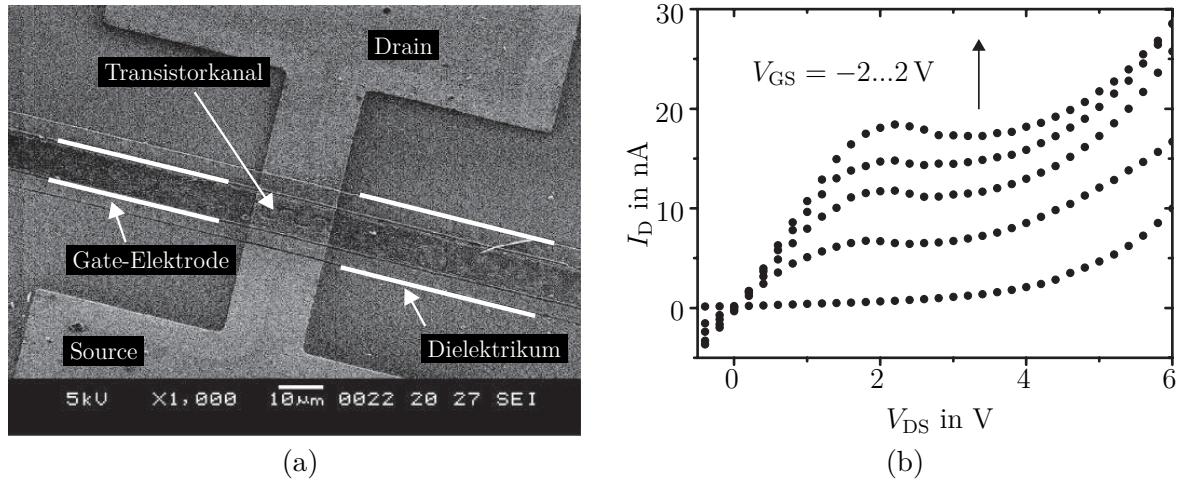

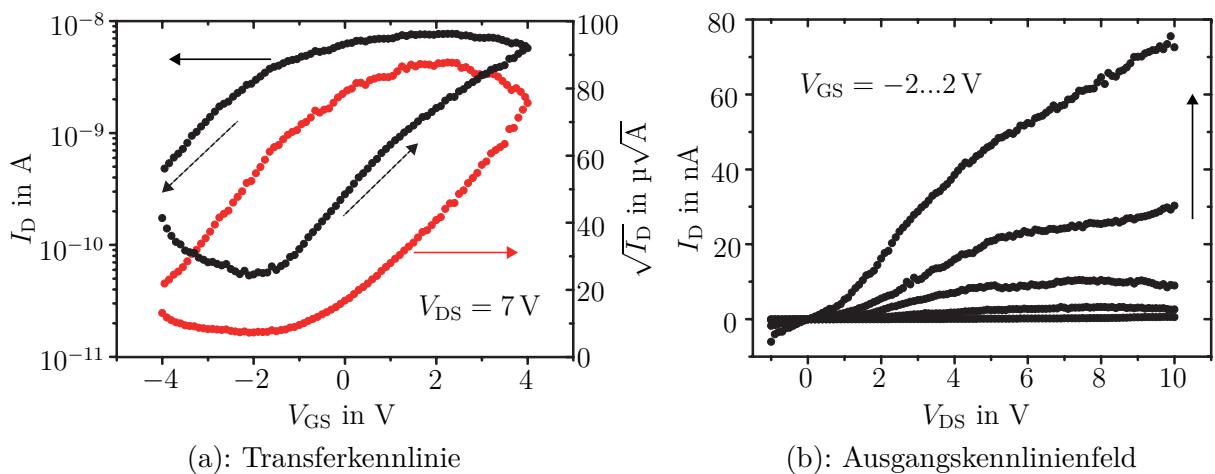

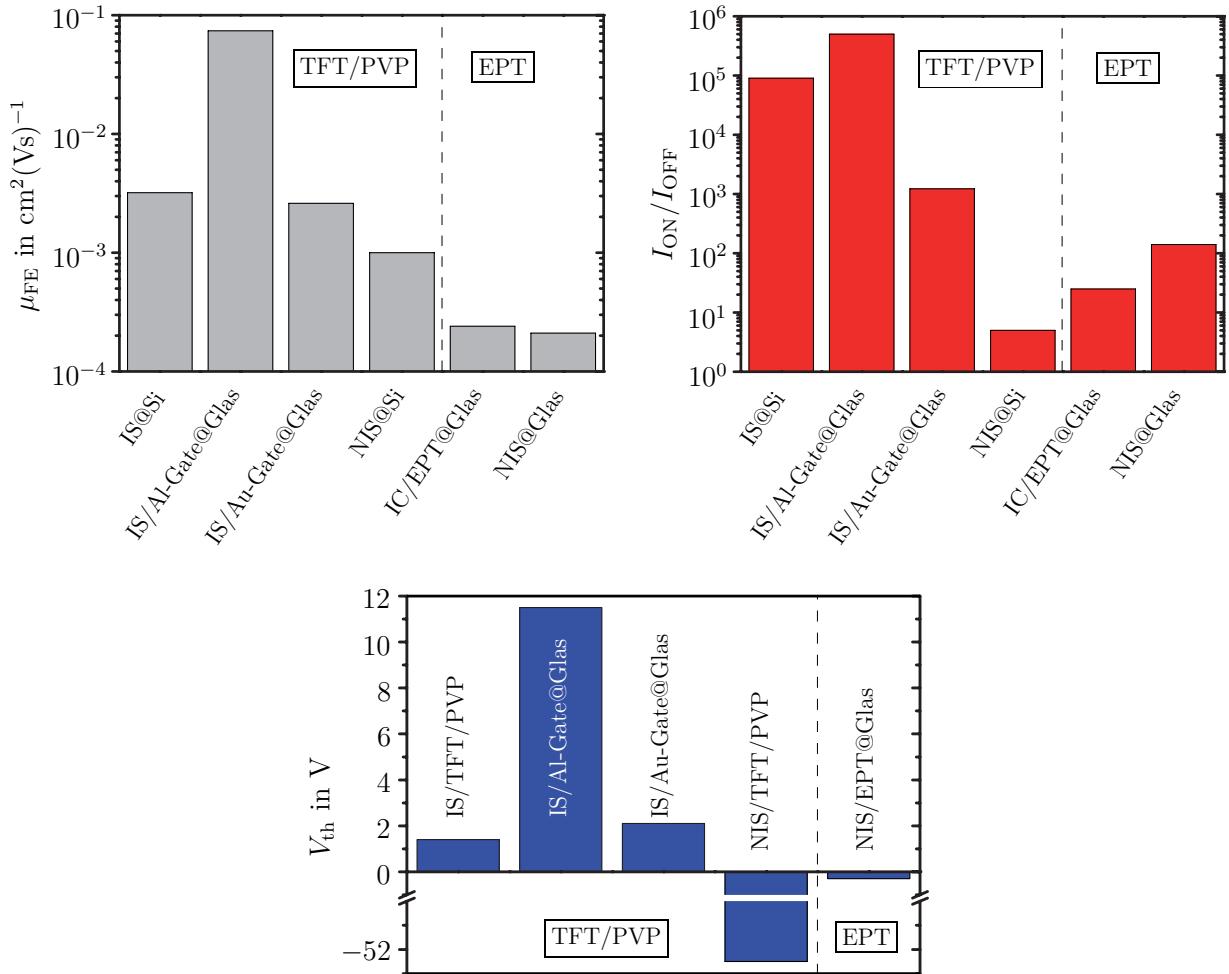

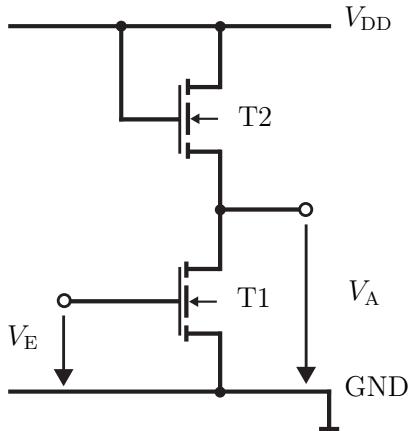

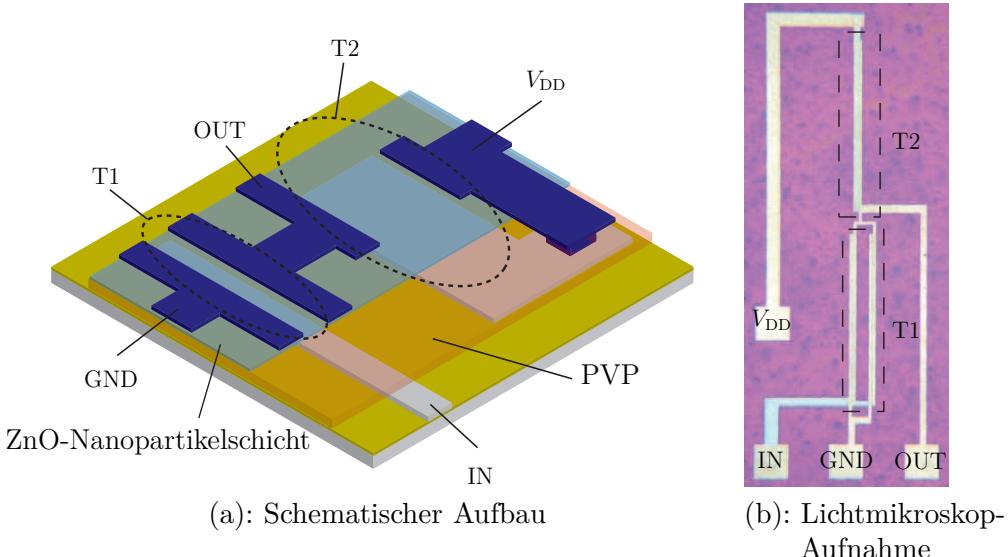

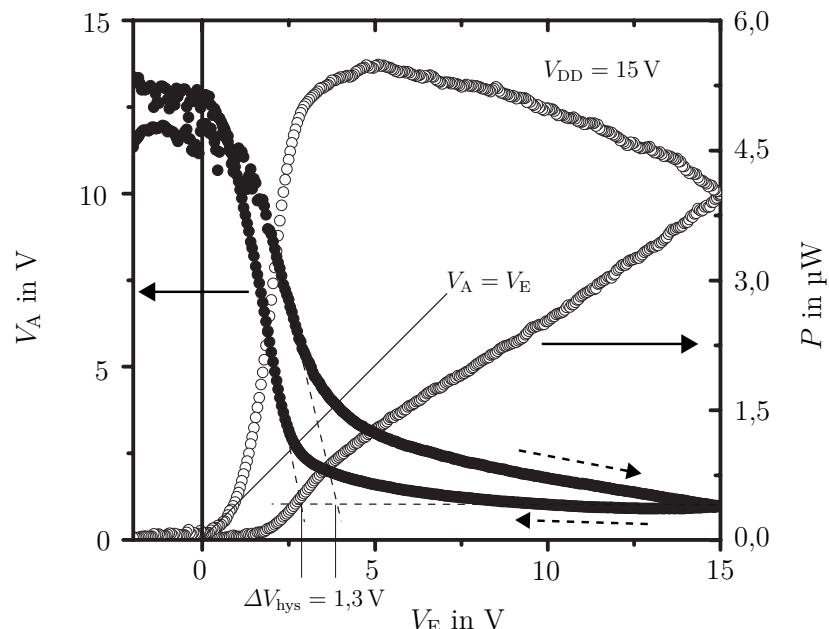

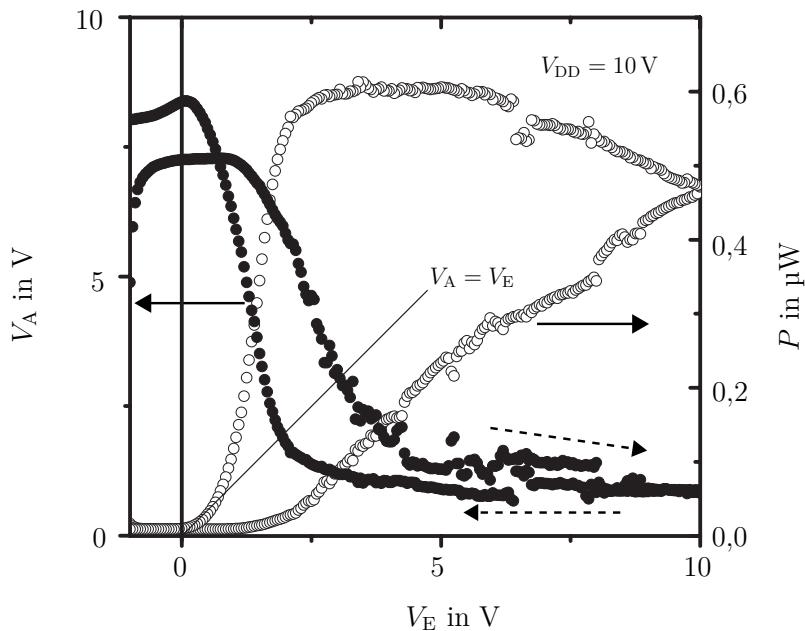

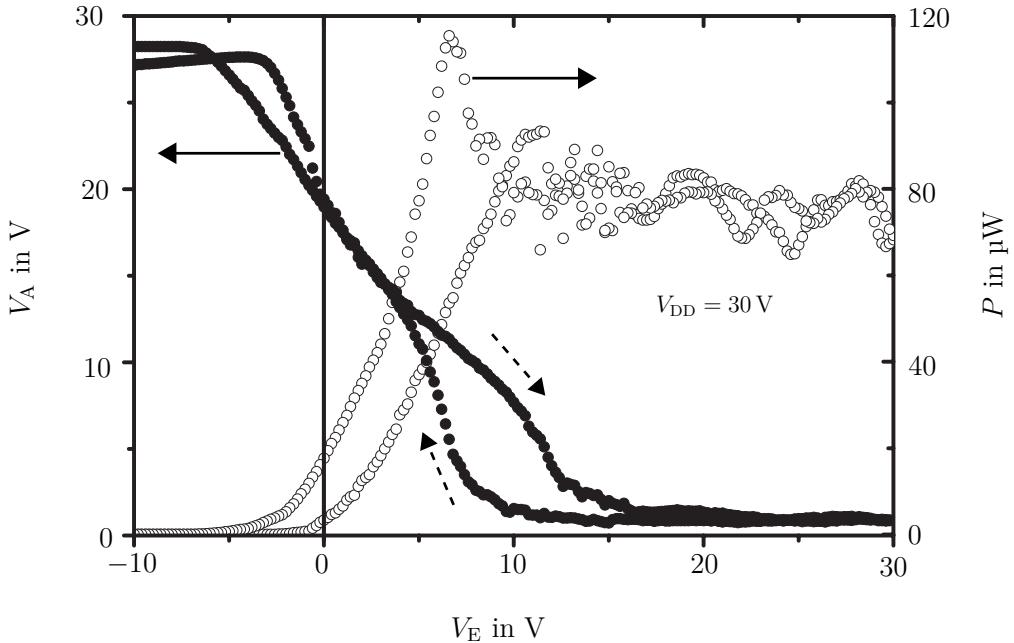

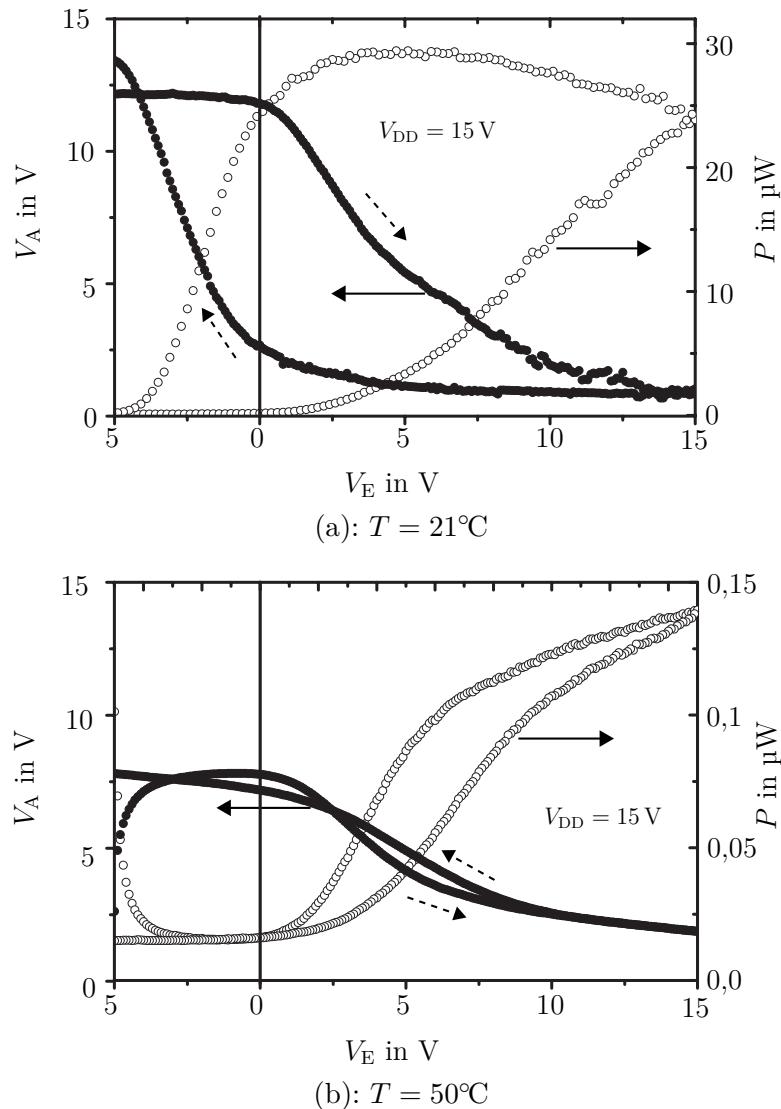

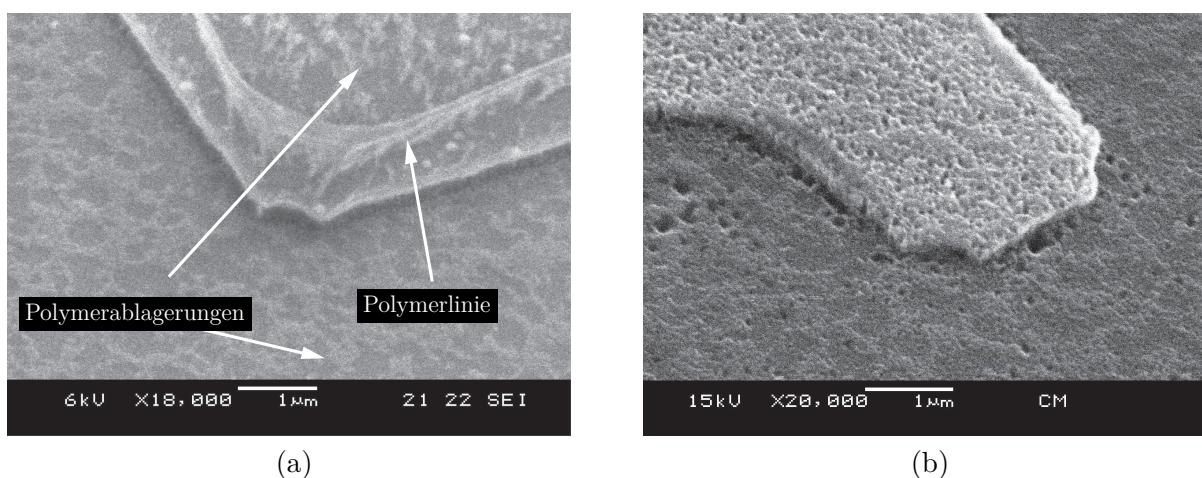

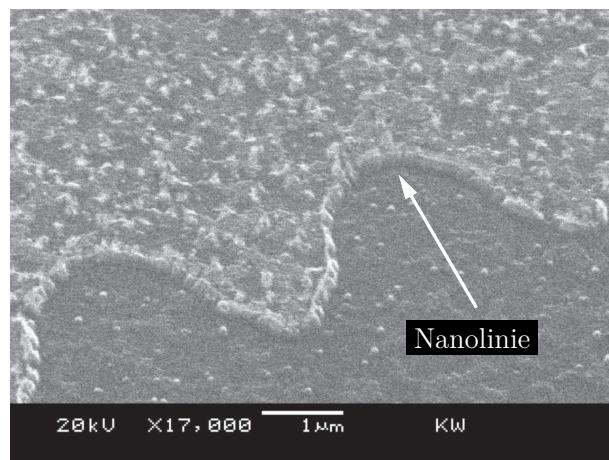

Die verwendeten Silizium-Nanopartikel werden von der Firma EVONIK DEGUSSA GMBH, CREAvis TECHNOLOGIES & INNOVATION bezogen<sup>10</sup>. Die Partikel liegen als Dispersion in Ethanol mit Massenanteilen von  $\xi(\text{Si}) = 0,1$  Gew.-% bzw.  $\xi(\text{Si}) = 6,25$  Gew.-% vor, so dass die Farbe von leicht bräunlich bis grau-braun variiert. Der Probenumfang beinhaltet Nanopartikel, die sowohl im Mikrowellenreaktor als auch im Heißwandreaktor synthetisiert wurden. Neben undotierten Nanopartikeln sind ebenfalls Nanopartikel verfügbar, die durch Zugabe von Phosphin oder Diboran während des Herstellungsprozesses eine entsprechende Dotierung aufweisen. Laut Herstellerangaben beträgt die Primärapartikelgröße ca. 16...20 nm und die mittlere Agglomeratgröße 70...90 nm. Die Stabilität der Dispersionen ist über einen Zeitraum von mindestens einen Monat gegeben, ohne dass eine Ausfällung des Kolloids sichtbar ist. Nach dieser Zeit kann eine ausreichende Redispergierung durch eine Ultraschallbehandlung erreicht werden.