*Prozesstechnik für

organische Feldeffekt Transistoren:

Kontakte, Dielektrika

und Oberflächenpassivierungen*

Zur Erlangung des akademischen Grades

DOKTORINGENIEUR (Dr.-Ing.)

der Fakultät für Elektrotechnik, Informatik und Mathematik

der Universität Paderborn

vorgelegte Dissertation

von

Dipl.-Phys. Christoph Pannemann

aus Paderborn

Referent: Prof. Dr.-Ing. U. Hilleringmann

Korreferent: Prof. Dr. V. Wagner

Tag der mündlichen Prüfung: 29. September 2006

Paderborn, den 1. November 2006

# Inhaltsverzeichnis

|                                                                                |           |

|--------------------------------------------------------------------------------|-----------|

| <b>Abbildungsverzeichnis</b>                                                   | <b>ix</b> |

| <b>Tabellenverzeichnis</b>                                                     | <b>x</b>  |

| <b>1 Einleitung</b>                                                            | <b>1</b>  |

| 1.1 Organische Halbleiter in Leuchtdioden und Solarzellen . . . . .            | 2         |

| 1.2 Der organische Feldeffekt Transistor . . . . .                             | 4         |

| <b>2 Grundlagen</b>                                                            | <b>6</b>  |

| 2.1 Elektronische Grundlagen organischer Halbleiter . . . . .                  | 6         |

| 2.1.1 Das Bändermodell organischer Halbleiter . . . . .                        | 7         |

| 2.2 Das elektrische Verhalten des organischen Feldeffekt Transistors . . . . . | 10        |

| 2.3 Das organische Halbleitermaterial Pentacen . . . . .                       | 15        |

| 2.4 Vor- und Nachteile organischer Halbleitermaterialien . . . . .             | 17        |

| 2.5 Abschätzung des Entwicklungspotenzials organischer Bauelemente . . . . .   | 19        |

| <b>3 Schichtherstellung und Transistoraufbau</b>                               | <b>22</b> |

| 3.1 Substrat . . . . .                                                         | 24        |

| 3.2 Dielektrikum . . . . .                                                     | 25        |

| 3.3 Drain- und Source-Kontakte . . . . .                                       | 27        |

| 3.4 Der organische Halbleiter . . . . .                                        | 30        |

| 3.5 Prozessabfolge zur Herstellung von OFETs . . . . .                         | 33        |

| <b>4 Elektrische Charakterisierung</b>                                         | <b>37</b> |

| 4.1 Einfluss des Dielektrikums . . . . .                                       | 38        |

|          |                                                                              |           |

|----------|------------------------------------------------------------------------------|-----------|

| 4.1.1    | Thermisch gewachsenes $SiO_2$                                                | 39        |

| 4.1.2    | TEOS                                                                         | 43        |

| 4.1.3    | $Si_3N_4$                                                                    | 45        |

| 4.1.4    | LTO                                                                          | 47        |

| 4.1.5    | PECVD                                                                        | 49        |

| 4.1.6    | $Ta_2O_5$                                                                    | 51        |

| 4.1.7    | Zusammenfassung                                                              | 52        |

| 4.2      | Einfluss der Aufdampfbedingungen auf die Morphologie der organischen Schicht | 53        |

| 4.2.1    | Schichtdicke                                                                 | 54        |

| 4.3      | Reinheit des organischen Halbleitermaterials                                 | 57        |

| 4.4      | Einfluss der Drain- und Source-Kontakte auf die Transistoreigenschaften      | 58        |

| 4.4.1    | Einfluss des Kontaktmetalls                                                  | 58        |

| 4.4.2    | Strukturierung der Kontakte                                                  | 61        |

| 4.4.3    | Kontaktwiderstand                                                            | 63        |

| 4.5      | Skalierbarkeit                                                               | 65        |

| 4.6      | Modellbildung mit Hilfe der MOS-Gleichungen                                  | 68        |

| <b>5</b> | <b>Alterungsuntersuchungen</b>                                               | <b>72</b> |

| 5.1      | Alterung unter Laborbedingungen                                              | 73        |

| 5.2      | Fraktionierung der Alterungsmechanismen                                      | 75        |

| 5.2.1    | Sauerstoff                                                                   | 75        |

| 5.2.2    | Einfluss ausgewählter Laborgase                                              | 78        |

| 5.2.3    | Luftfeuchtigkeit                                                             | 82        |

| 5.3      | Kapselungsversuche                                                           | 85        |

| <b>6</b> | <b>Aufbau logischer Schaltungen</b>                                          | <b>93</b> |

| 6.1      | Inverter                                                                     | 93        |

| 6.2      | Layout 1                                                                     | 94        |

| 6.3      | Layout 2                                                                     | 96        |

| <b>7</b> | <b>Zusammenfassung</b>                                                       | <b>99</b> |

---

|                             |            |

|-----------------------------|------------|

| 7.1 Ausblick . . . . .      | 101        |

| <b>Literaturverzeichnis</b> | <b>102</b> |

| <b>A</b>                    | <b>A</b>   |

| A.1 Reinigung A . . . . .   | A          |

| A.2 Reinigung C . . . . .   | A          |

| <b>Index</b>                | <b>C</b>   |

# Abbildungsverzeichnis

|      |                                                                                                               |    |

|------|---------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Preis-Frequenz Diagramm . . . . .                                                                             | 2  |

| 1.2  | Querschnitt durch eine organische Leuchtdiode/Solarzelle . . . . .                                            | 3  |

| 1.3  | Aufrollbares Display auf flexilem Kunststoffsubstrat . . . . .                                                | 4  |

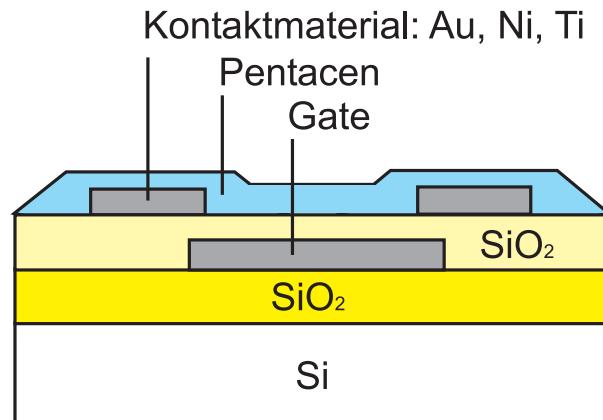

| 1.4  | Der organische Feldeffekt Transistor . . . . .                                                                | 5  |

| 1.5  | Der organische Feldeffekt Transistor mit isolierter Gate-Elektrode . . . . .                                  | 5  |

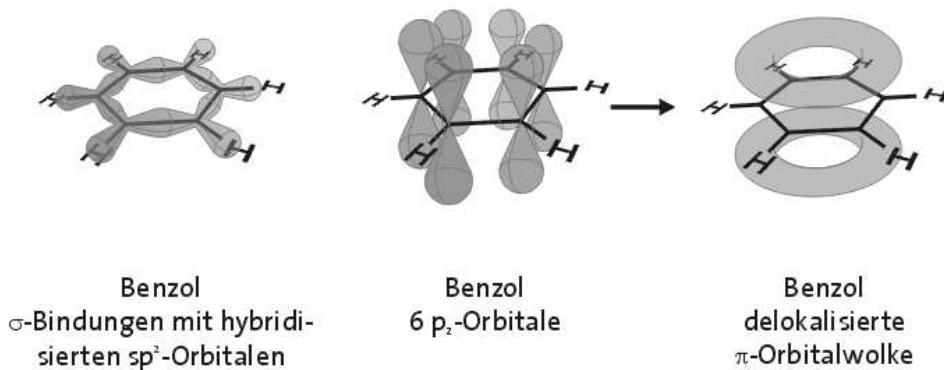

| 2.1  | Die $sp^2$ -Hybridisierung der Bindungsorbitale des Benzols . . . . .                                         | 6  |

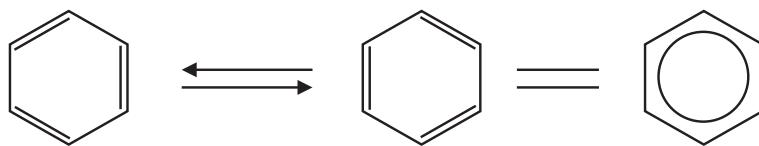

| 2.2  | Die Mesomerie des Benzols . . . . .                                                                           | 7  |

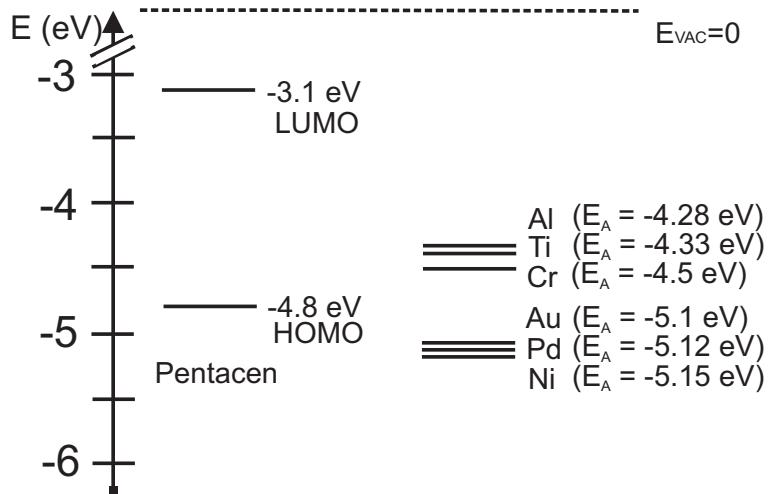

| 2.3  | Lage von HOMO und LUMO des Pentacens, relativ zum Vakuumniveau . . . . .                                      | 8  |

| 2.4  | Die Bandstruktur der Acene . . . . .                                                                          | 8  |

| 2.5  | Struktur des organischen n-Halbleiters C <sub>60</sub> . . . . .                                              | 9  |

| 2.6  | Das Bandmodell organischer Halbleiter . . . . .                                                               | 10 |

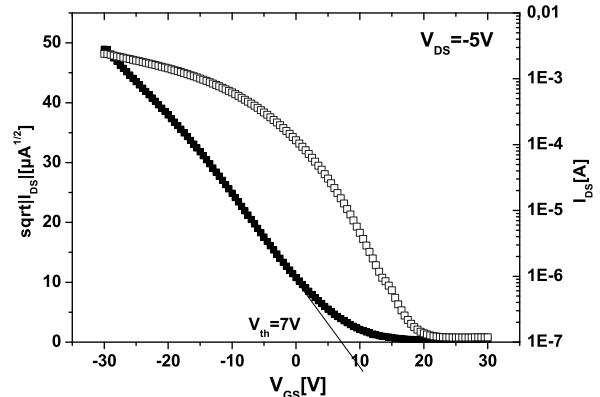

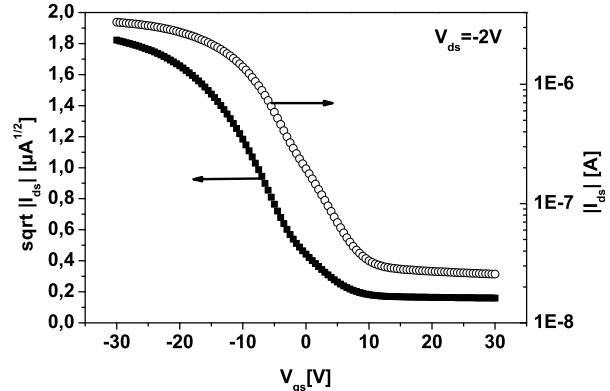

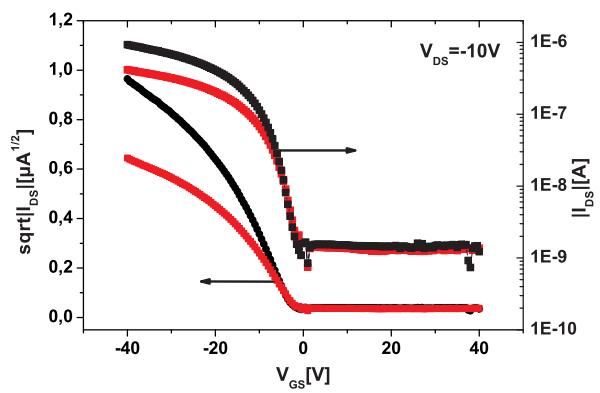

| 2.7  | Ermittlung der Schwellenspannung durch Extrapolation aus der Eingangskennlinie                                | 14 |

| 2.8  | Das organische Molekül Pentacen . . . . .                                                                     | 15 |

| 2.9  | Abhängigkeit der Ordnung im organischen Kristall von der Substrattemperatur während der Abscheidung . . . . . | 17 |

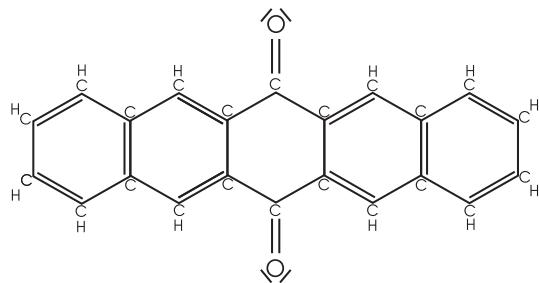

| 2.10 | Pentacen-Chinon . . . . .                                                                                     | 18 |

| 2.11 | Alterung durch Wassermoleküle . . . . .                                                                       | 19 |

| 3.1  | Die Planartechnologie . . . . .                                                                               | 23 |

| 3.2  | Die thermische Oxidation . . . . .                                                                            | 24 |

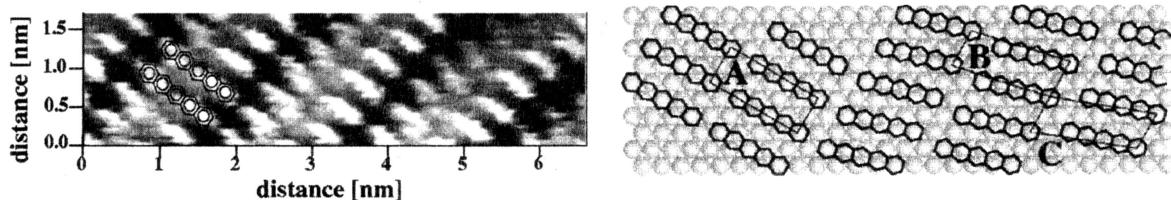

| 3.3  | Wachstum von Pentacen auf Gold . . . . .                                                                      | 28 |

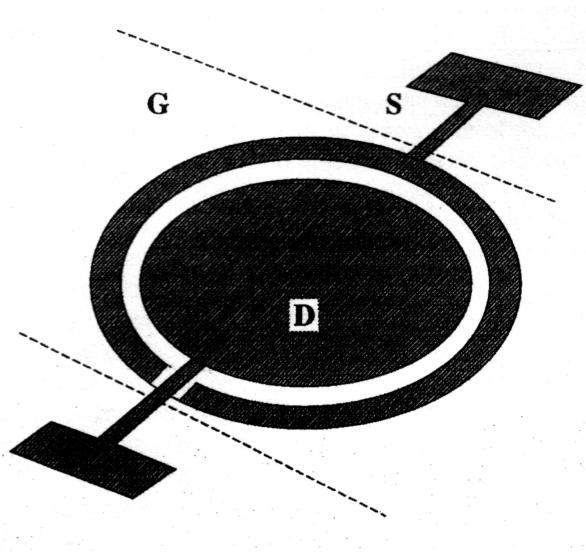

| 3.4  | Drain- und Source-Kontakte in Corbino-Typ Anordnung . . . . .                                                 | 30 |

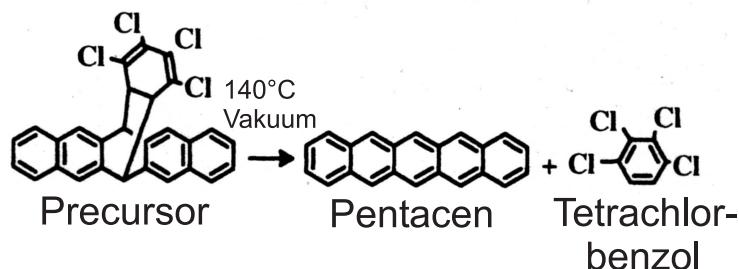

| 3.5  | Umwandlung eines Pentacen-Precursors . . . . .                                                                | 31 |

|      |                                                                                                                                                  |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

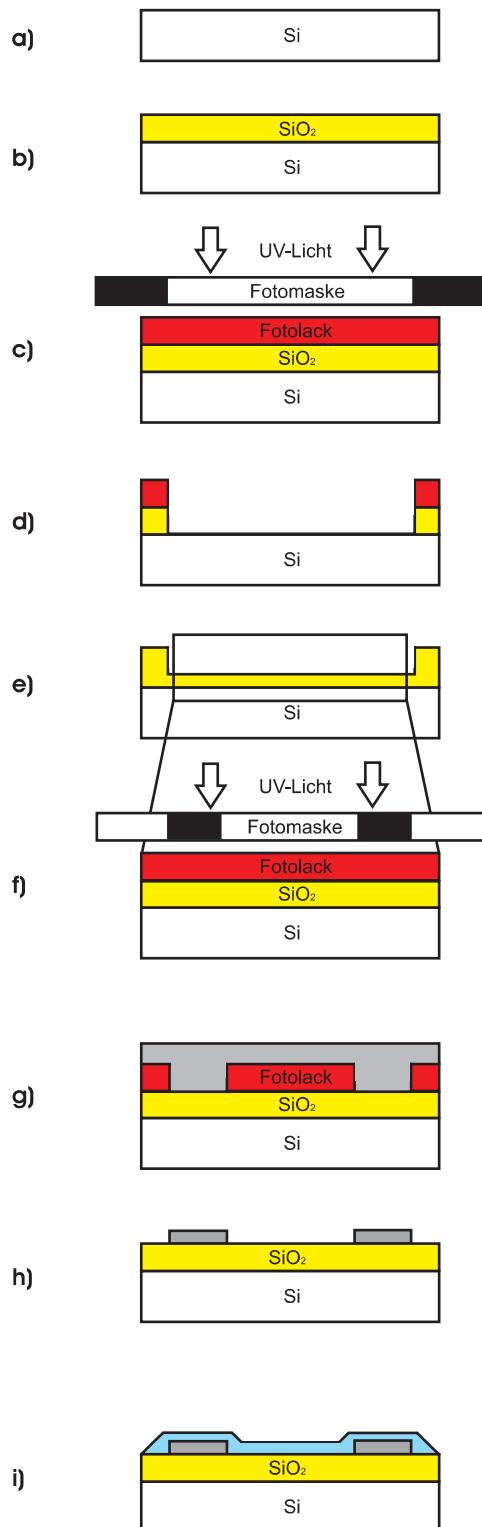

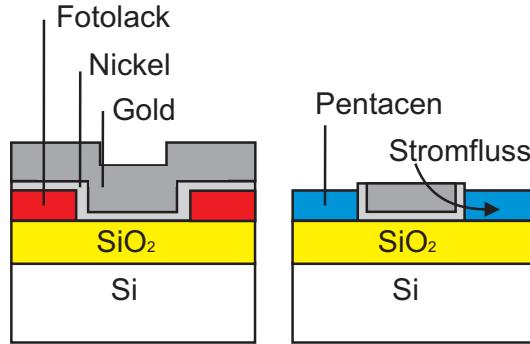

| 3.6  | Abfolge der Prozessschritte zur Herstellung eines OFETs . . . . .                                                                                | 34 |

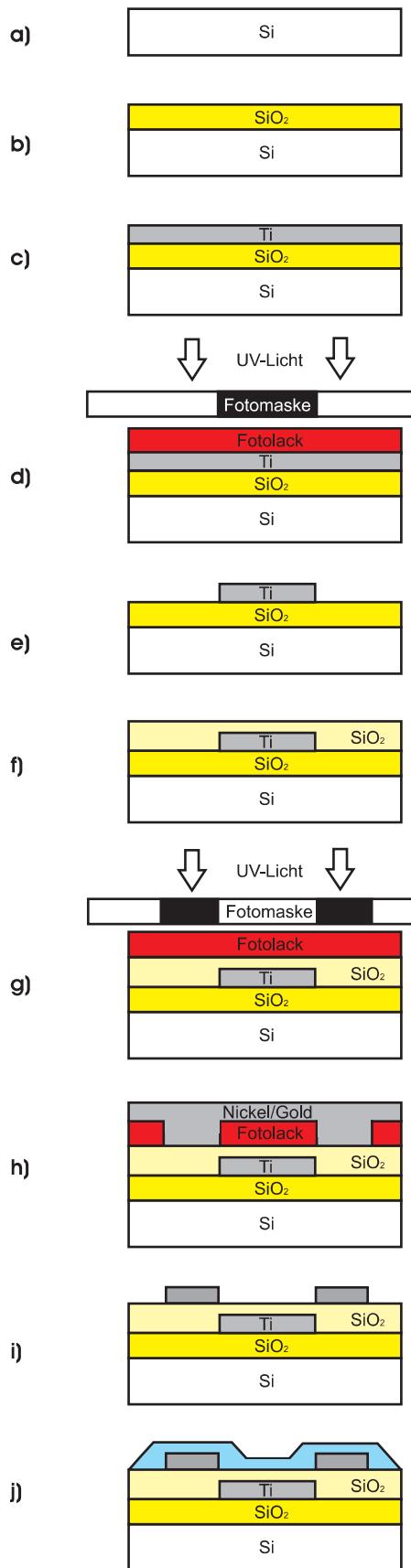

| 3.7  | Abfolge der Prozessschritte zur Herstellung eines OFETs mit isoliertem Gate-Kontakt . . . . .                                                    | 36 |

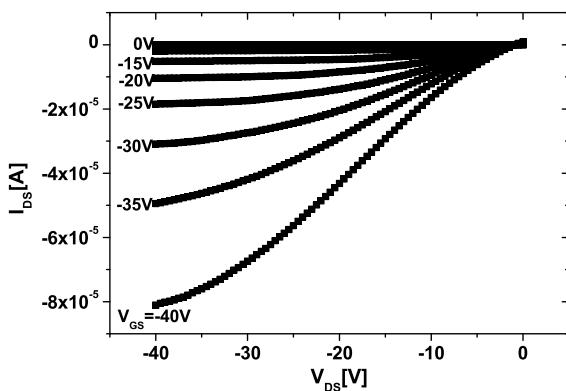

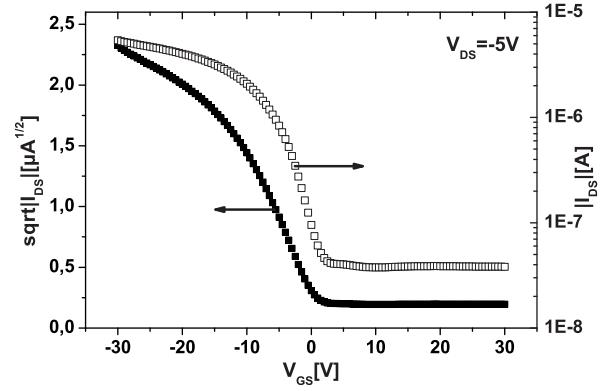

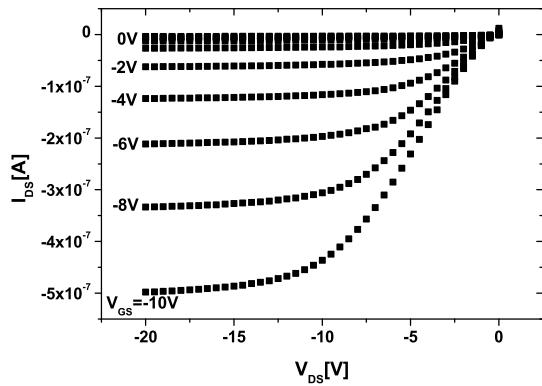

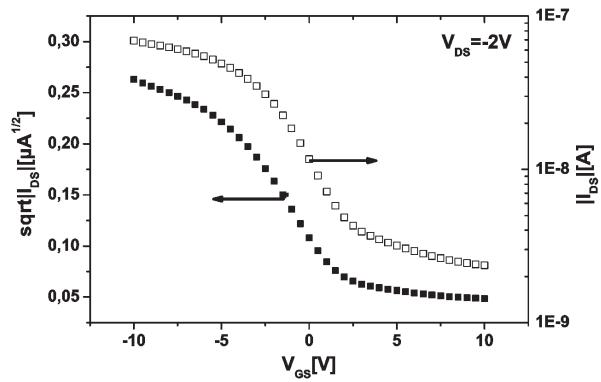

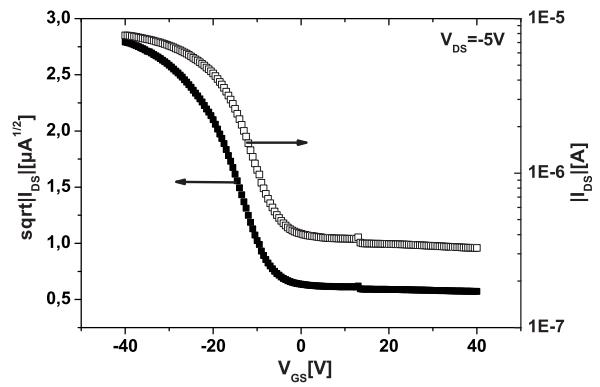

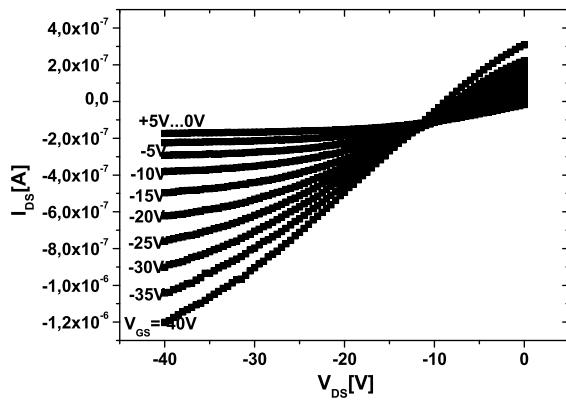

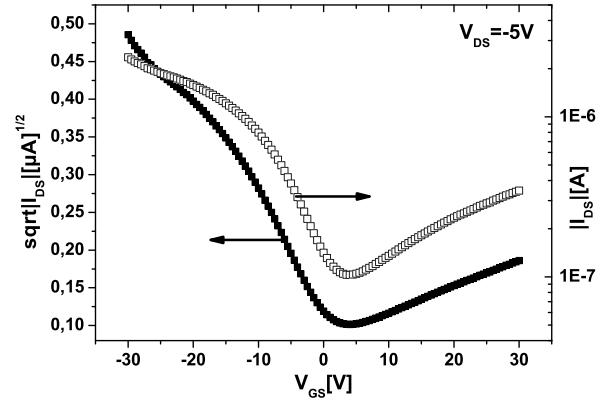

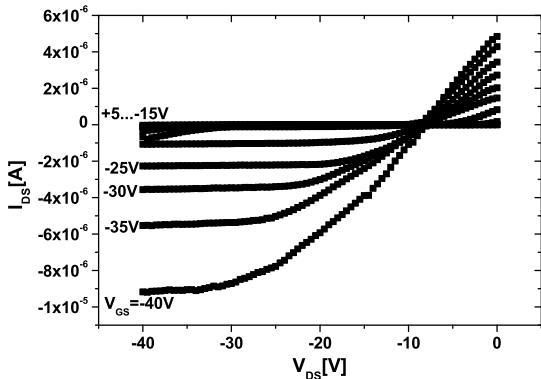

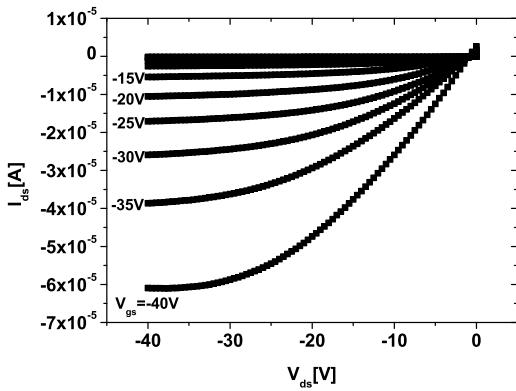

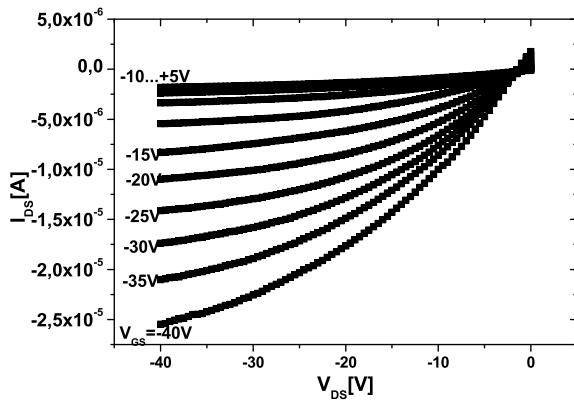

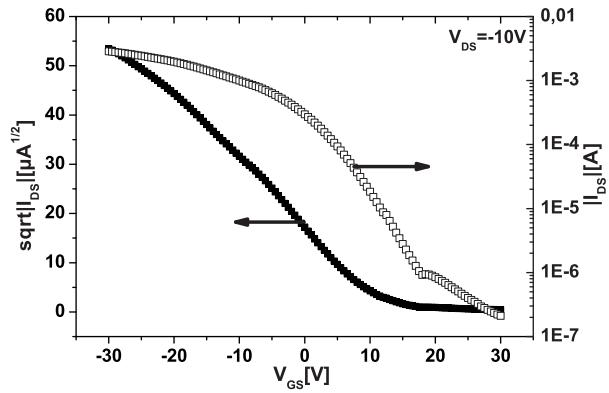

| 4.1  | Aus- und Eingangskennlinie eines OFETs mit $SiO_2$ als Dielektrikum . . . . .                                                                    | 39 |

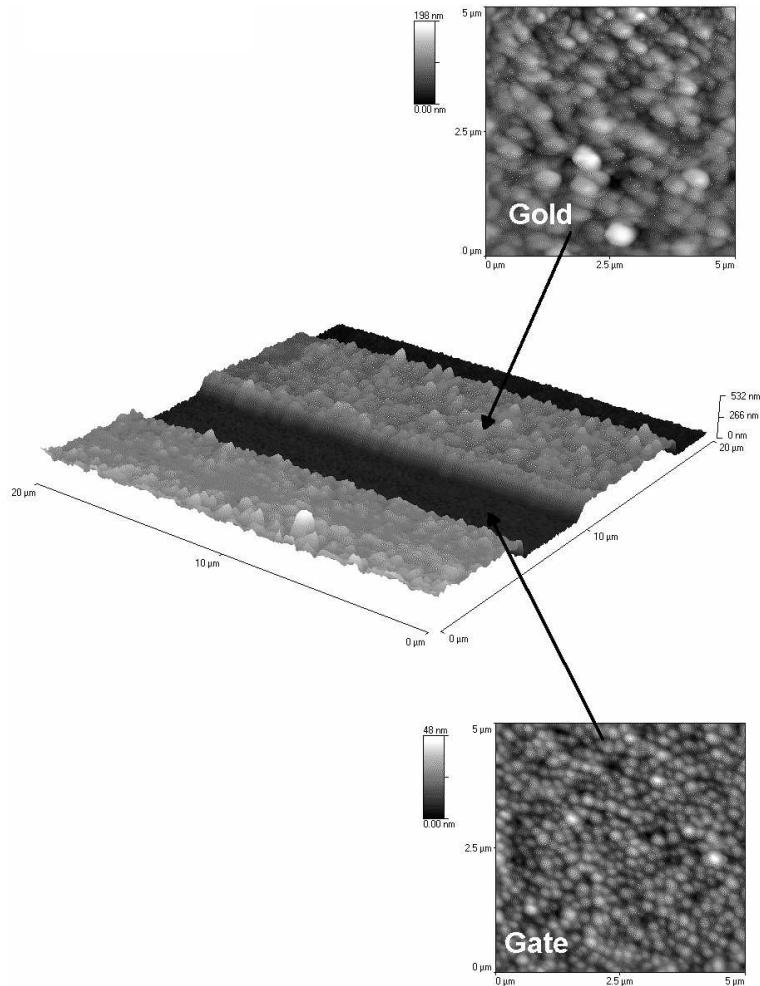

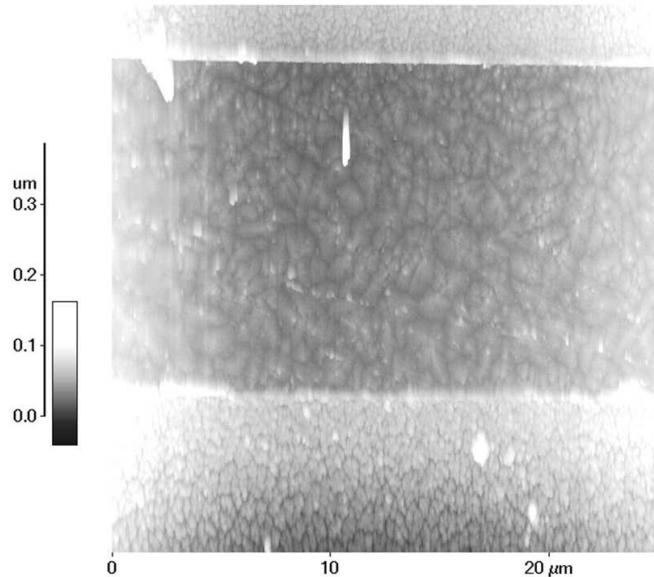

| 4.2  | AFM-Untersuchung des Pentacen-Wachstums auf $SiO_2$ und Gold . . . . .                                                                           | 40 |

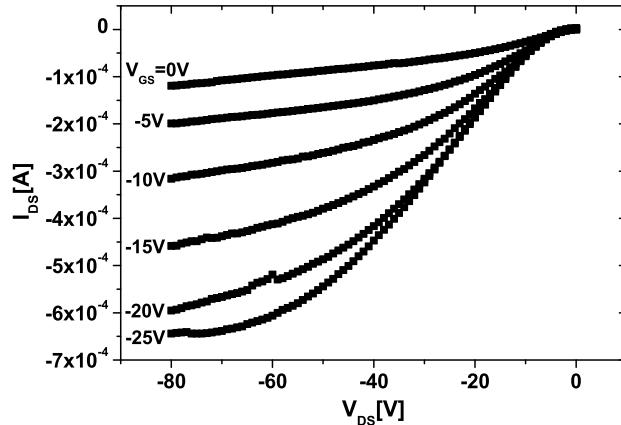

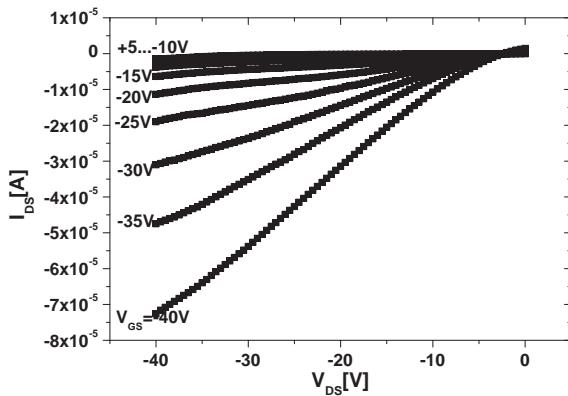

| 4.3  | Ausgangskennlinienfeld eines OFETs, gereinigt mit einem Sauerstoff-Plasma vor der Pentacen Beschichtung . . . . .                                | 41 |

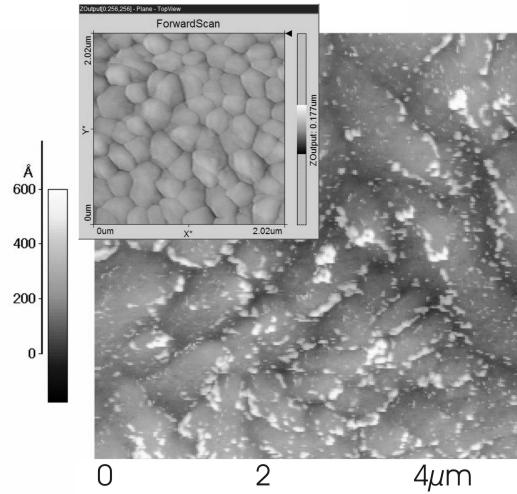

| 4.4  | AFM-Charakterisierung der Oberfläche des Pentacens . . . . .                                                                                     | 42 |

| 4.5  | AFM-Charakterisierung der Oberfläche des Pentacens im Transistorkanal . . . . .                                                                  | 43 |

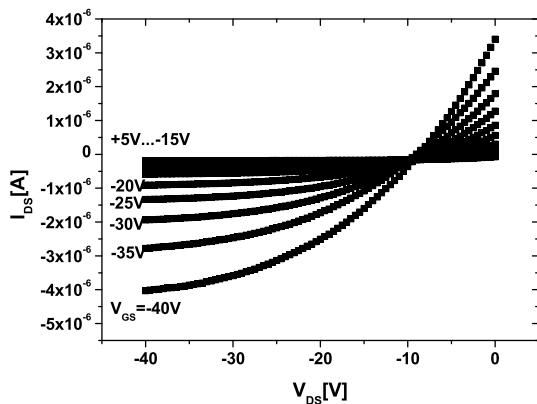

| 4.6  | Aus- und Eingangskennlinie eines OFETs mit TEOS als Dielektrikum . . . . .                                                                       | 44 |

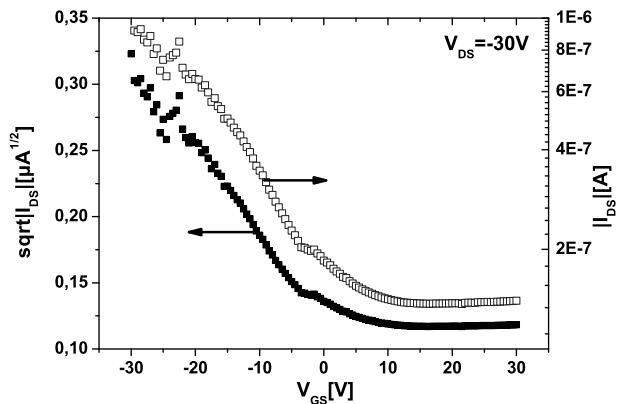

| 4.7  | Aus- und Eingangskennlinien eines OFETs mit $Si_3N_4$ als Dielektrikum . . . . .                                                                 | 46 |

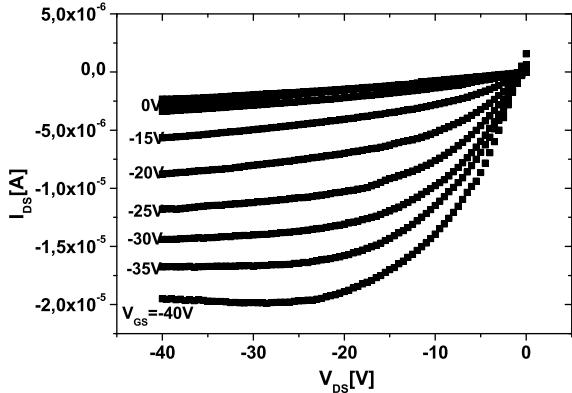

| 4.8  | Aus- und Eingangskennlinien von OFETs mit LTO als Dielektrikum . . . . .                                                                         | 48 |

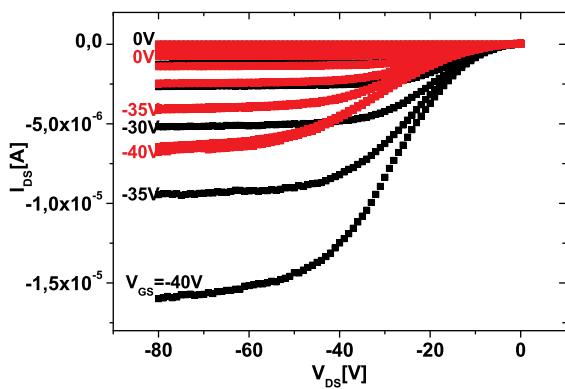

| 4.9  | Oxiddurchbruch durch hohe Spannungsbelastung . . . . .                                                                                           | 50 |

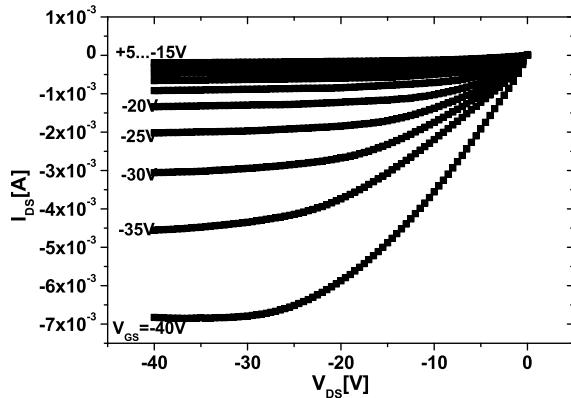

| 4.10 | Aus- und Eingangskennlinie eines OFETs mit einer Doppelschicht aus LTO und PECVD-Oxid als Dielektrikum . . . . .                                 | 51 |

| 4.11 | Aus- und Eingangskennlinie eines OFETs mit $Ta_2O_5$ als Dielektrikum . . . . .                                                                  | 52 |

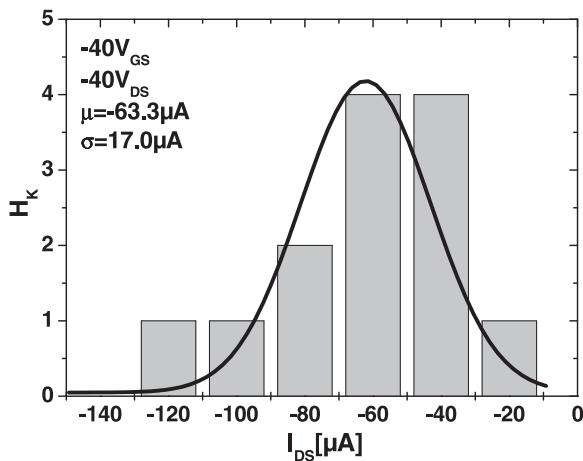

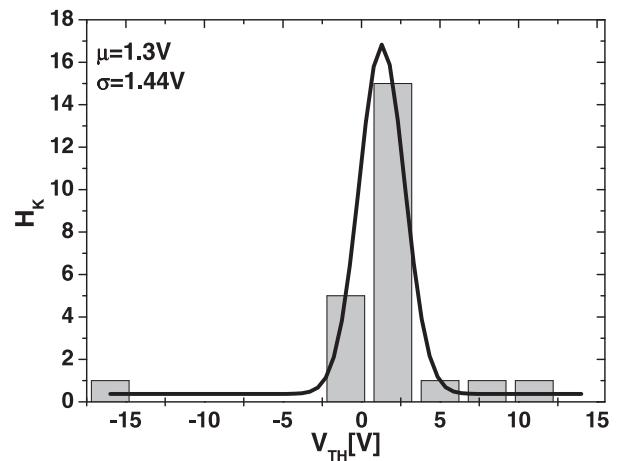

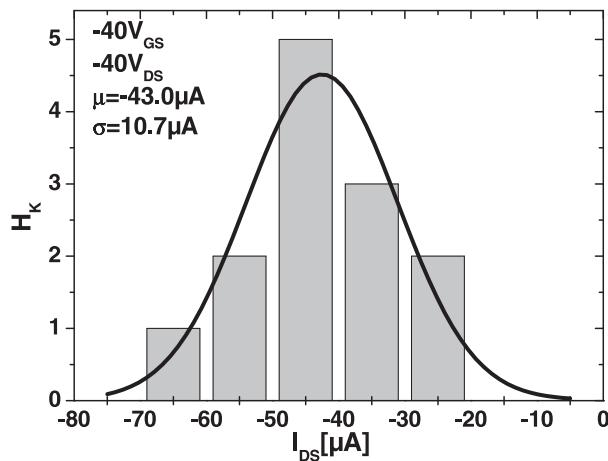

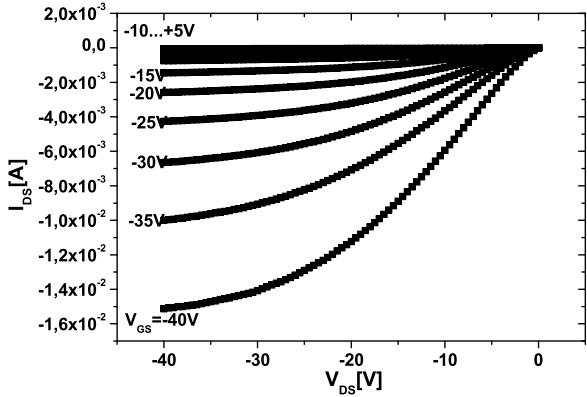

| 4.12 | Verteilung der maximalen Drain-Source-Ströme sowie der Schwellenspannungen bei einer Pentacen-Schichtdicke von $30\text{ nm}$ . . . . .          | 55 |

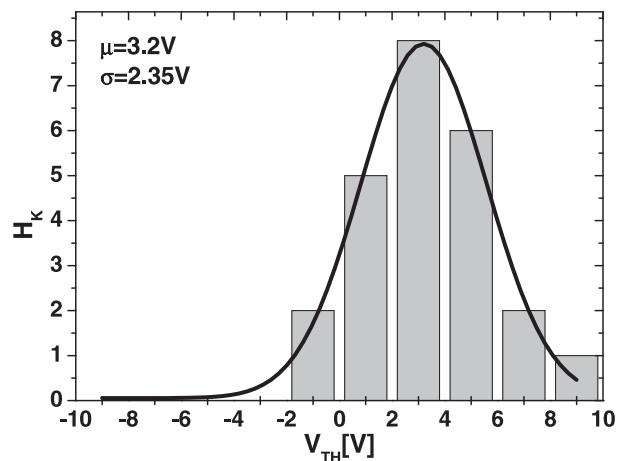

| 4.13 | Verteilung der maximalen Drain-Source-Ströme sowie der Schwellenspannungen bei einer Pentacen-Schichtdicke von $20\text{ nm}$ . . . . .          | 56 |

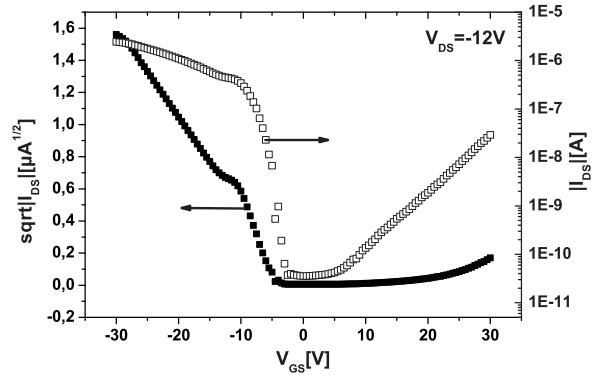

| 4.14 | Aus- und Eingangskennlinie eines OFETs mit aufgereinigtem Pentacen . . . . .                                                                     | 58 |

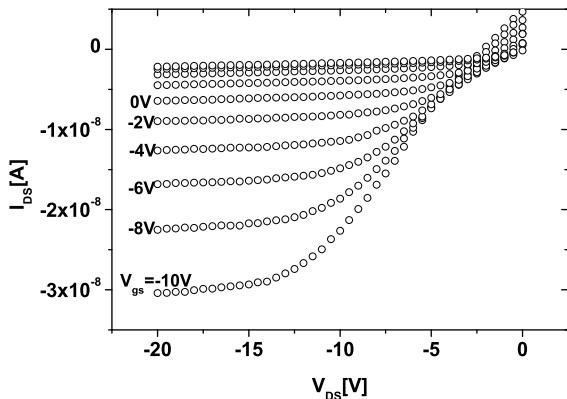

| 4.15 | Vergleich der Ausgangskennlinienfelder zwischen einem OFET mit Nickel-Kontakten und einem OFET mit Nickel-Gold-Kontakten . . . . .               | 59 |

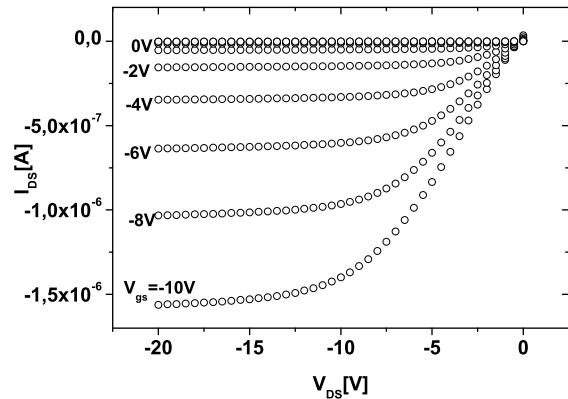

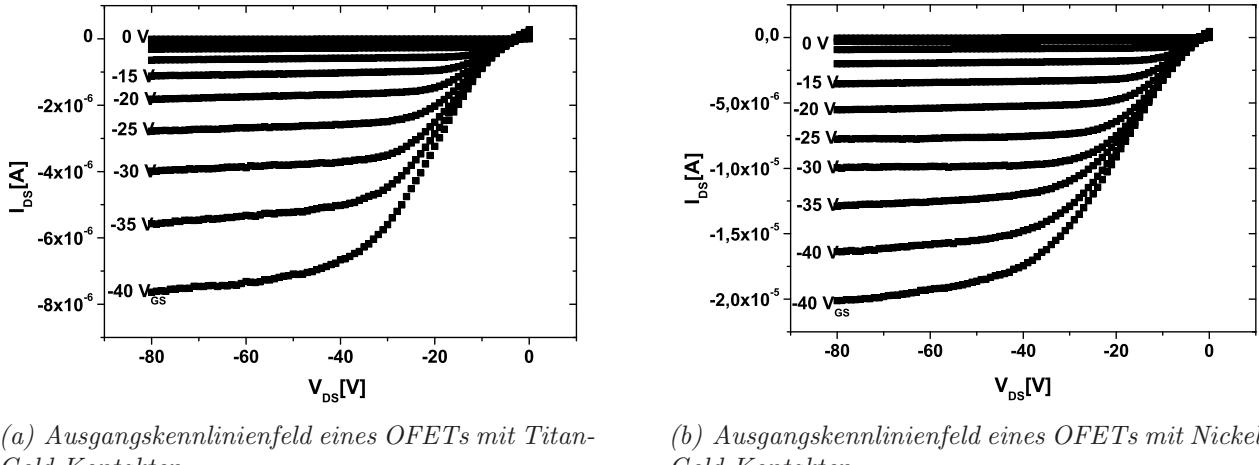

| 4.16 | Vergleich der Ausgangskennlinienfelder zwischen einem OFET mit Titan-Gold-Kontakten und einem OFET mit Nickel-Gold-Kontakten . . . . .           | 60 |

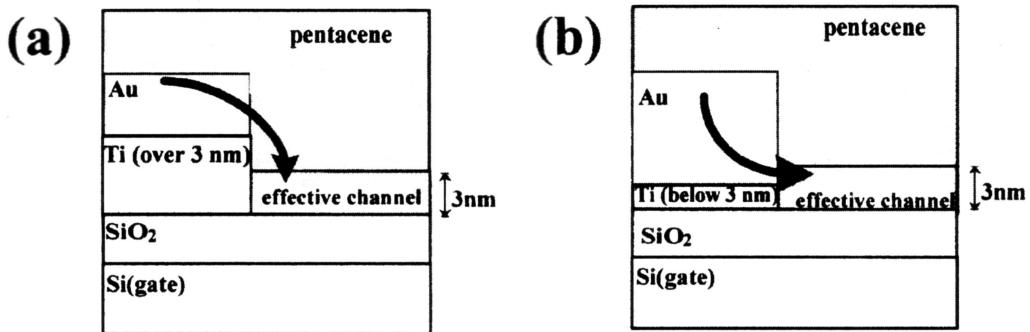

| 4.17 | Metall-Halbleiter-Kontakt mit Titan-Haftschicht . . . . .                                                                                        | 61 |

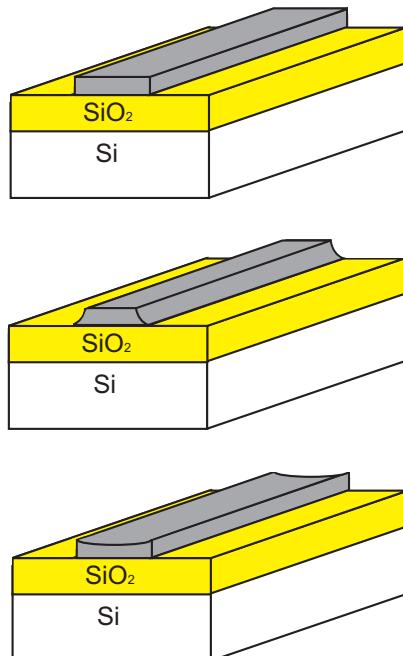

| 4.18 | Strukturierung der Drain- und Source-Kontakte durch Ätzen oder Lift-off . . . . .                                                                | 61 |

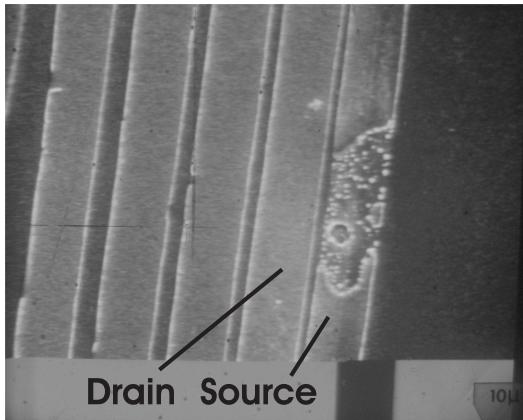

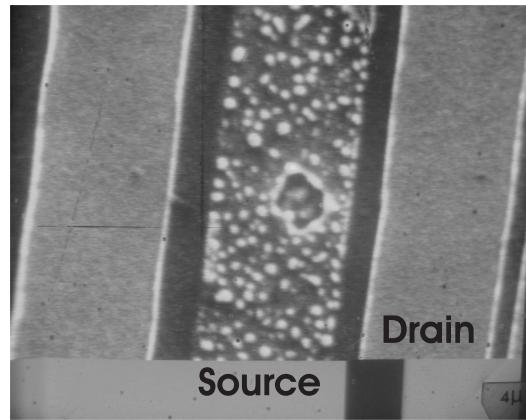

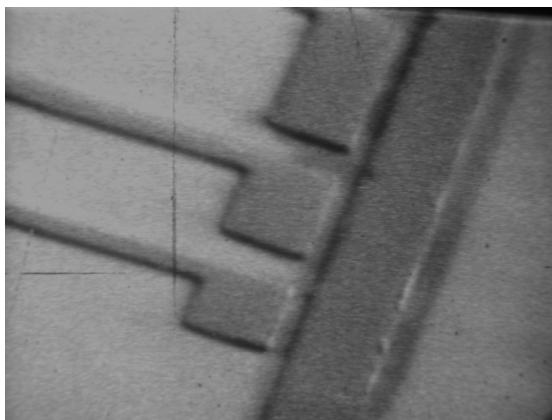

| 4.19 | REM-Aufnahme Lift-off strukturierter Drain- und Source-Kontakte . . . . .                                                                        | 62 |

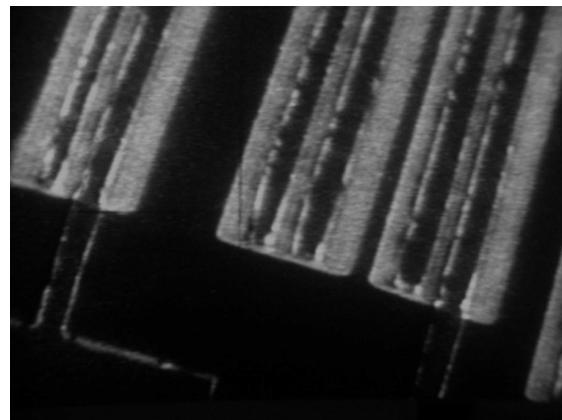

| 4.20 | Strukturierung der Drain- und Source-Kontakte mittels Lift-off . . . . .                                                                         | 63 |

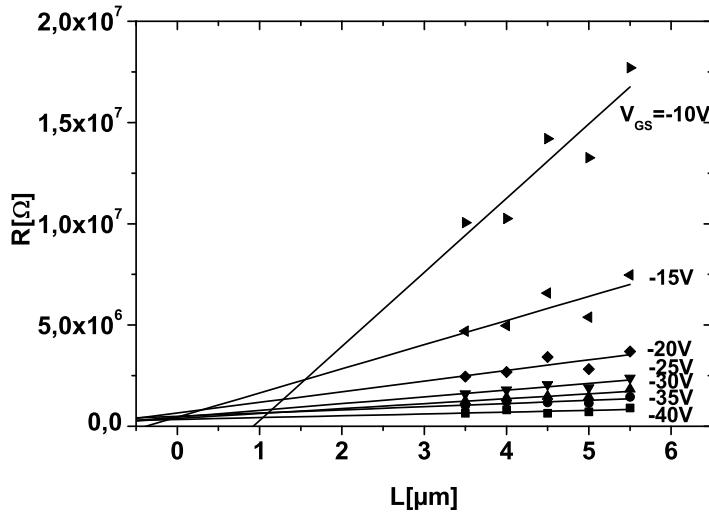

| 4.21 | Bestimmung des Kontaktwiderstands und der effektiven Kanallänge . . . . .                                                                        | 64 |

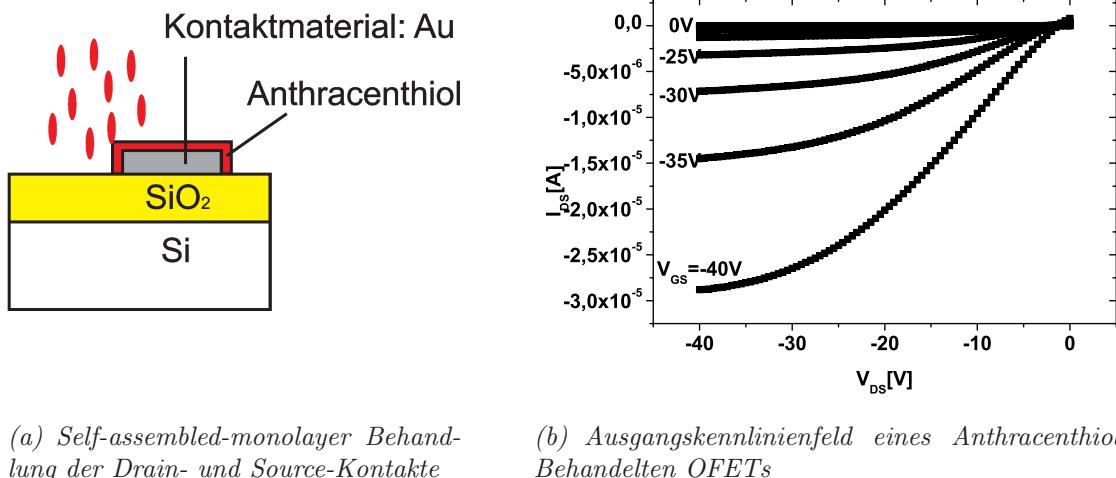

| 4.22 | Self-assembled-monolayer Behandlung der Drain- und Source-Kontakte / Ausgangskennlinienfeld eines mit Anthracenthiol behandelten OFETs . . . . . | 65 |

|                                                                                                                                                                                    |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

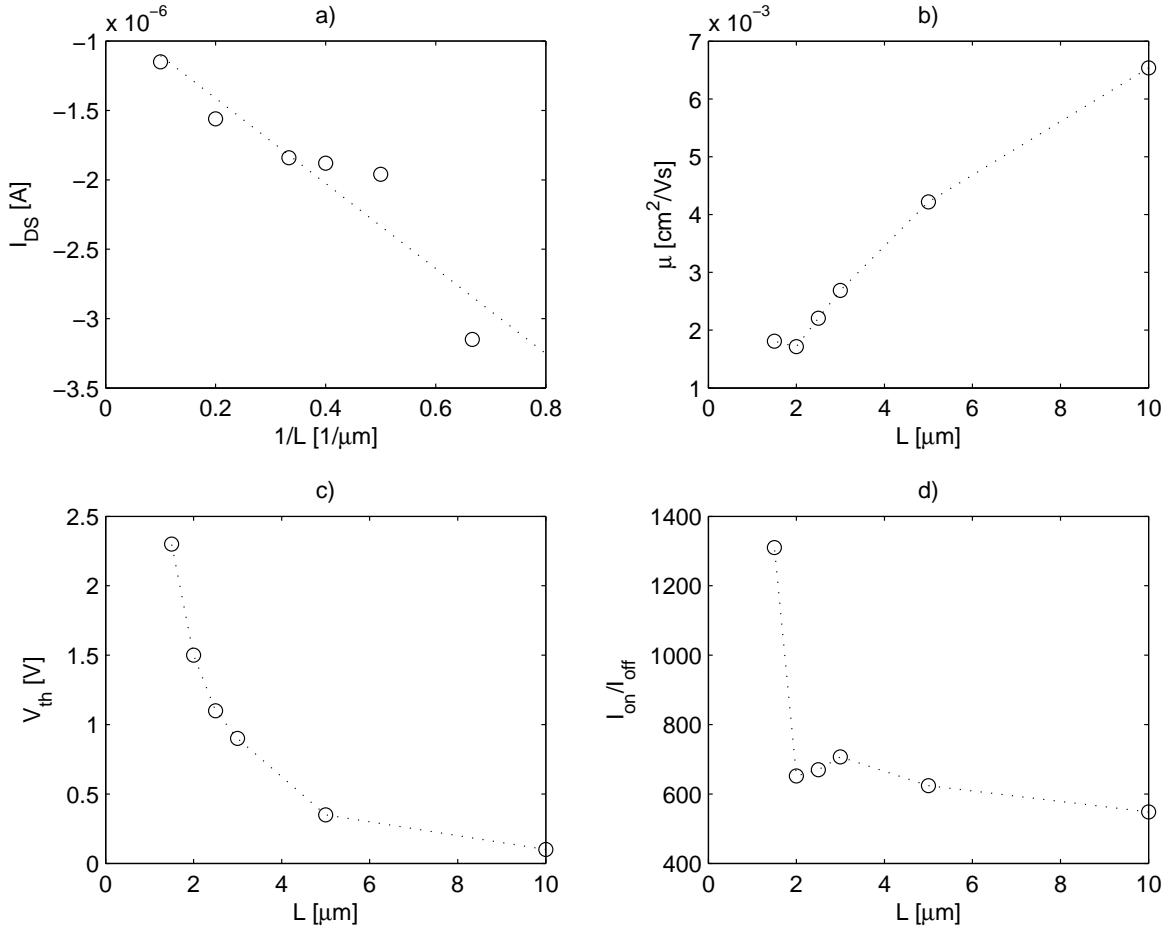

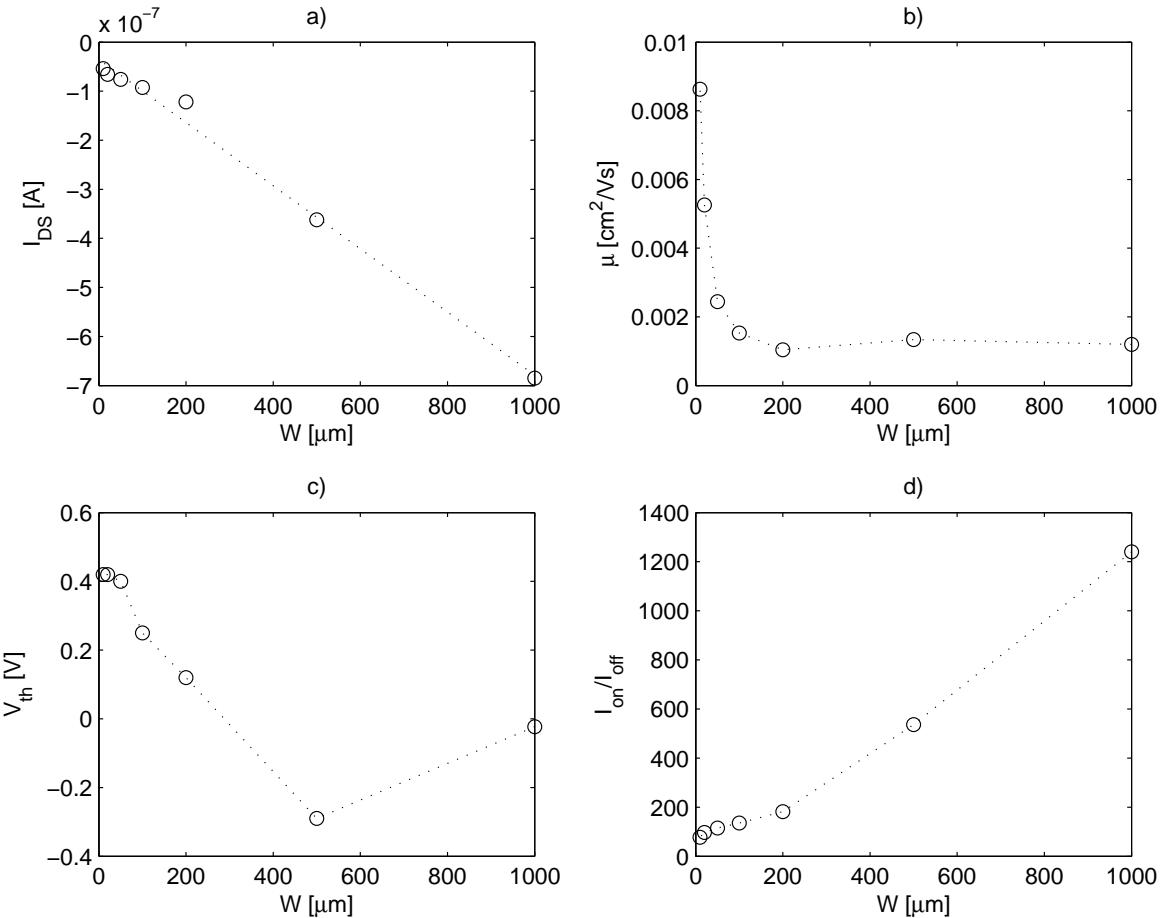

| 4.23 Längenabhängigkeit der Transistorparameter . . . . .                                                                                                                          | 67 |

| 4.24 Weitenabhängigkeit der Transistorparameter . . . . .                                                                                                                          | 68 |

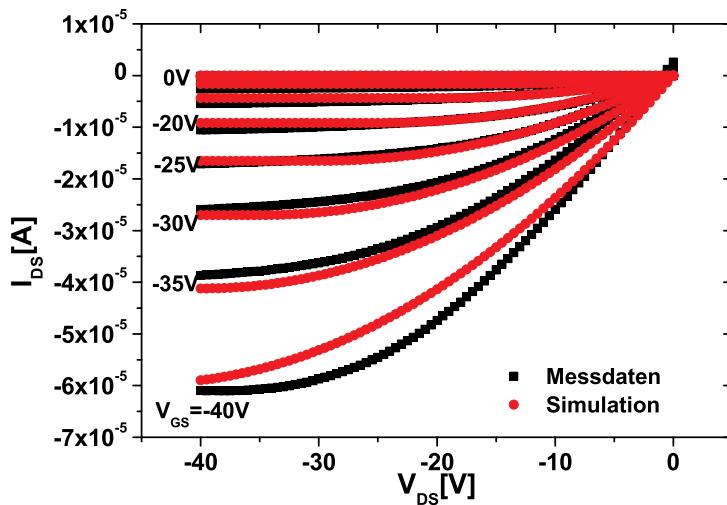

| 4.25 Modellierung des Ausgangskennlinienfeldes eines OFETs mit Nickel-Gold Kontakten . . . . .                                                                                     | 70 |

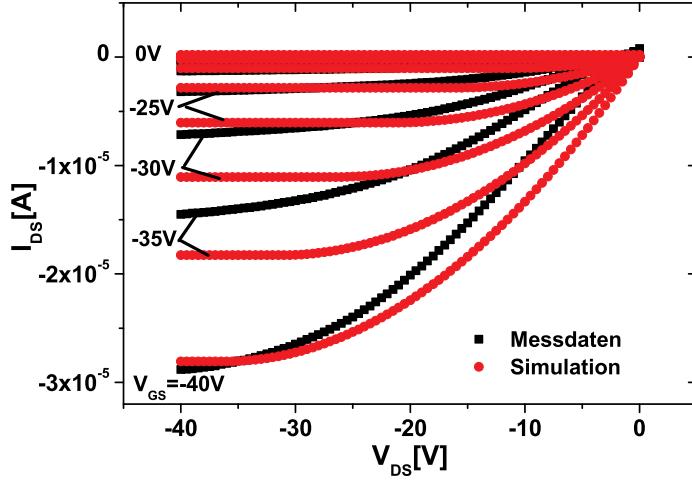

| 4.26 Modellierung des Ausgangskennlinienfeldes eines OFETs mit Anthracenthiol behandelten Nickel-Gold Kontakten . . . . .                                                          | 71 |

| <br>                                                                                                                                                                               |    |

| 5.1 Einfluss der Lagerung unter Laborbedingungen auf die Ein- und Ausgangskennlinie eines ungekapselten OFETs . . . . .                                                            | 73 |

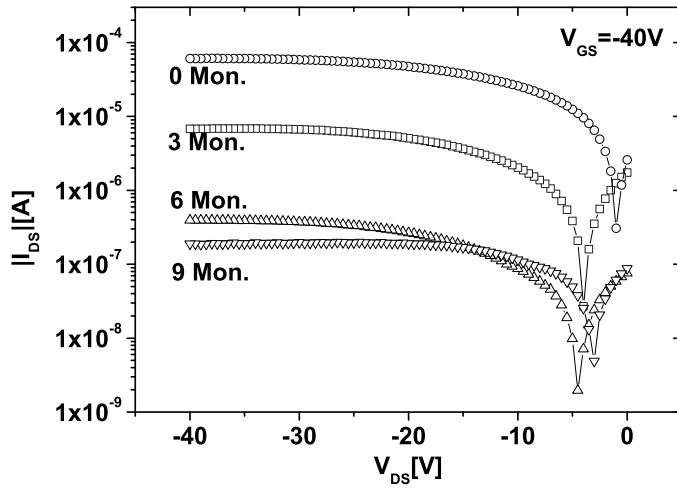

| 5.2 Verhalten des Sättigungsstroms bei $V_{GS} = -40\text{ V}$ während der Alterung über neun Monate . . . . .                                                                     | 74 |

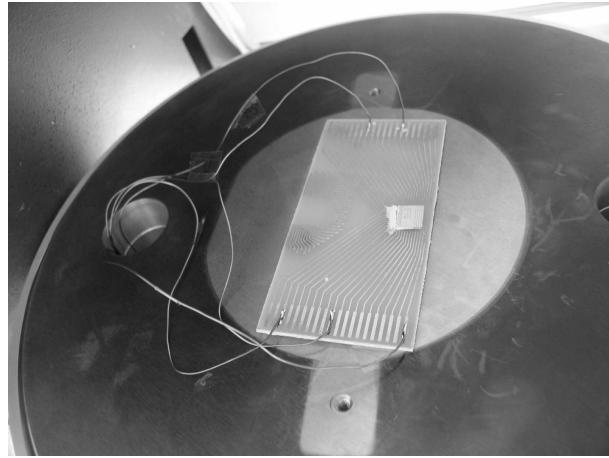

| 5.3 Gebondeter OFET auf der Mess-Platine . . . . .                                                                                                                                 | 76 |

| 5.4 Einfluss von Sauerstoff auf die Ein- und Ausgangskennlinie eines OFETs . . . . .                                                                                               | 76 |

| 5.5 Pentacen-Chinon . . . . .                                                                                                                                                      | 77 |

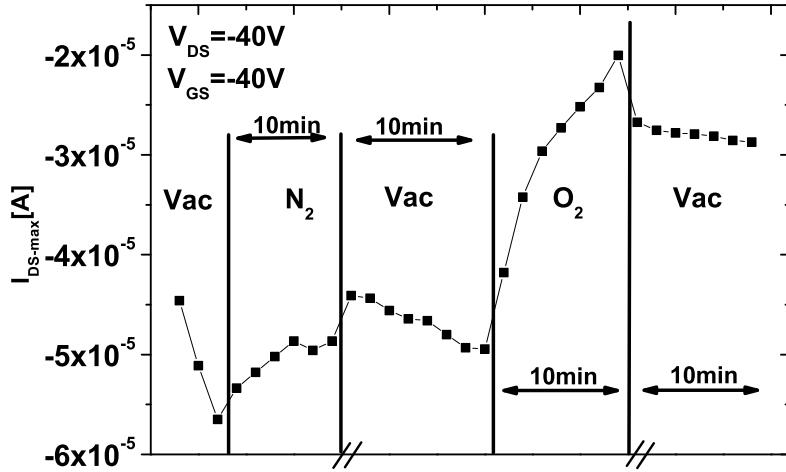

| 5.6 Verhalten des Sättigungsstroms bei $V_{GS} = -40\text{ V}$ und $V_{DS} = -40\text{ V}$ nach Exposition an Stickstoff bzw. Sauerstoff . . . . .                                 | 79 |

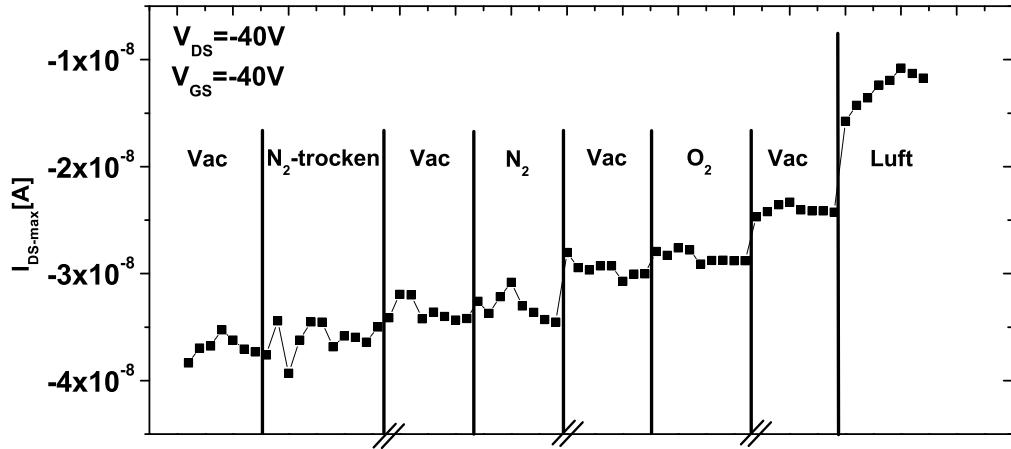

| 5.7 Verhalten des Sättigungsstroms bei $V_{GS} = -40\text{ V}$ und $V_{DS} = -40\text{ V}$ nach Exposition an trockenem Stickstoff, Stickstoff, Sauerstoff und Laborluft . . . . . | 81 |

| 5.8 Schwellenspannungsverschiebung in Abhängigkeit von der Luftfeuchtigkeit . . . . .                                                                                              | 82 |

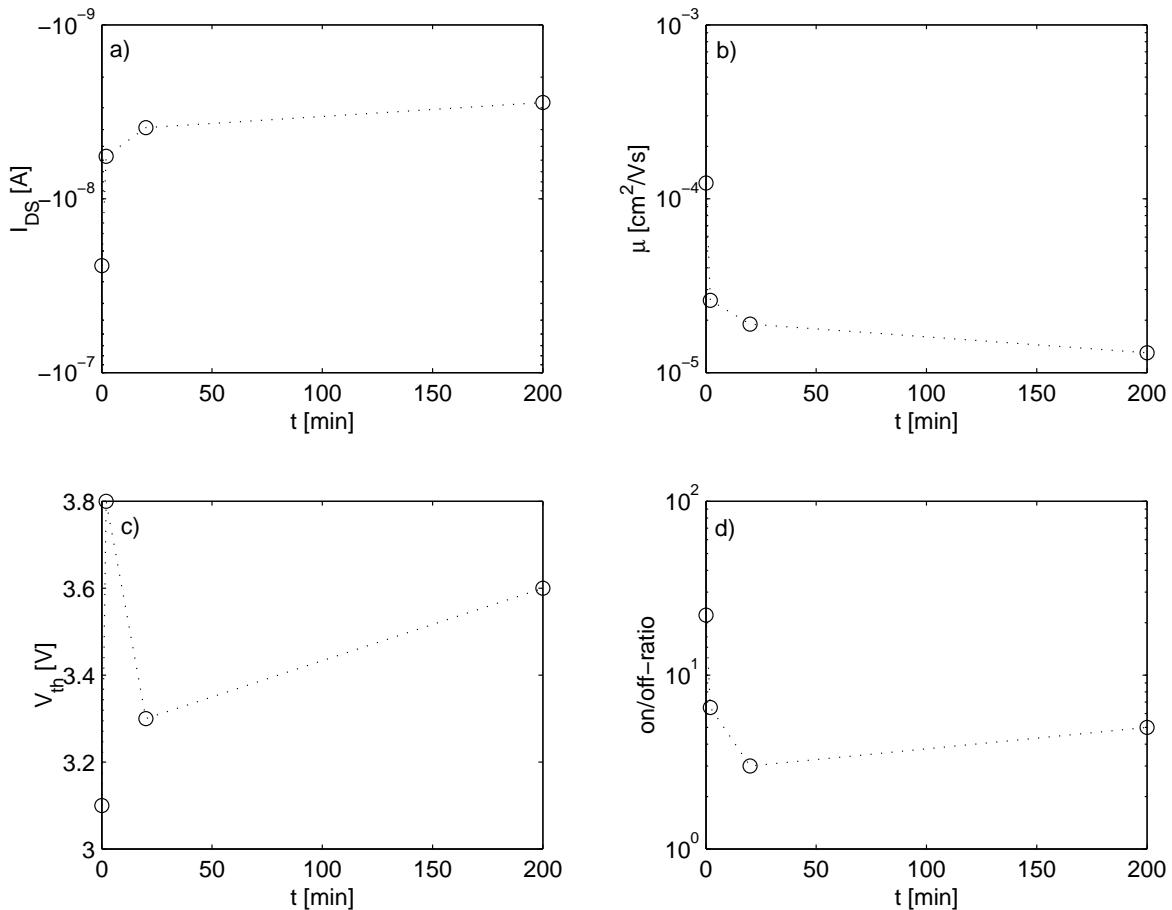

| 5.9 Verhalten charakteristischer Transistorkenndaten im Temper-Versuch . . . . .                                                                                                   | 84 |

| 5.10 Thermisch erzeugter 'dangling bond' am Pentacen . . . . .                                                                                                                     | 85 |

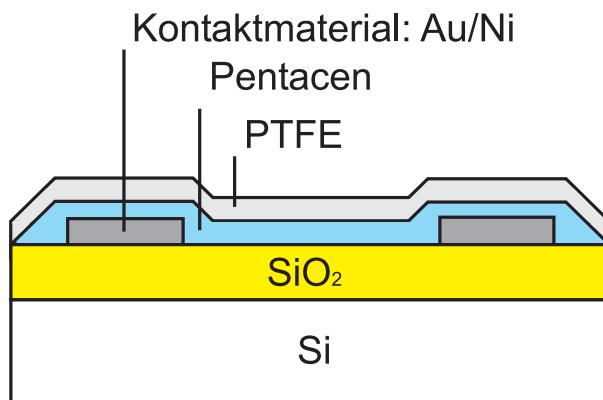

| 5.11 PTFE gekapselter OFET . . . . .                                                                                                                                               | 86 |

| 5.12 Einfluss der Beschichtung eines OFETs mit 20 nm dünnem PTFE auf die Transistorparameter . . . . .                                                                             | 87 |

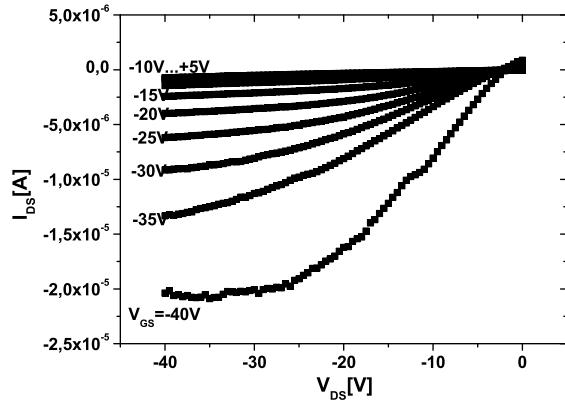

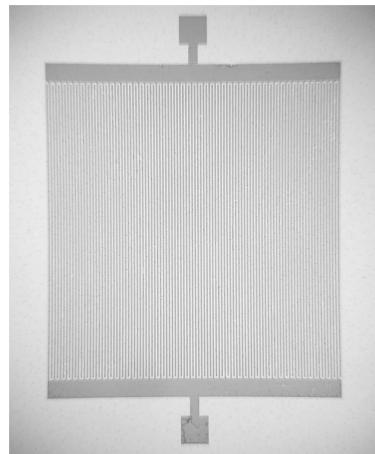

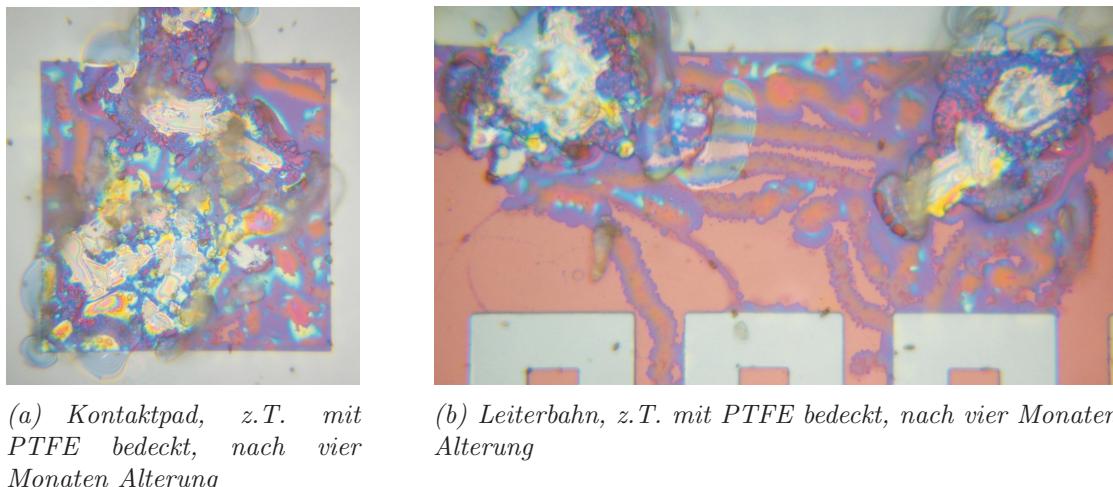

| 5.13 Mikroskopaufnahme eines OFETs mit 'interdigital strukturierten' Kontakten . . . . .                                                                                           | 88 |

| 5.14 Aus- und Eingangskennlinie eines OFET mit 'interdigital strukturierten' Kontakten                                                                                             | 89 |

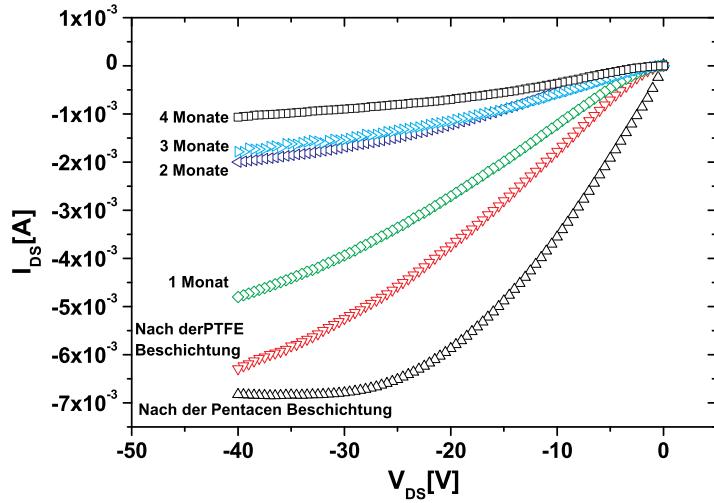

| 5.15 Alterung eines 'interdigital strukturierten' OFETs mit PTFE-Kapselungsschicht                                                                                                 | 90 |

| 5.16 Kontaktpad und Leiterbahn, z.T. mit PTFE bedeckt, nach vier Monaten Alterung                                                                                                  | 91 |

| <br>                                                                                                                                                                               |    |

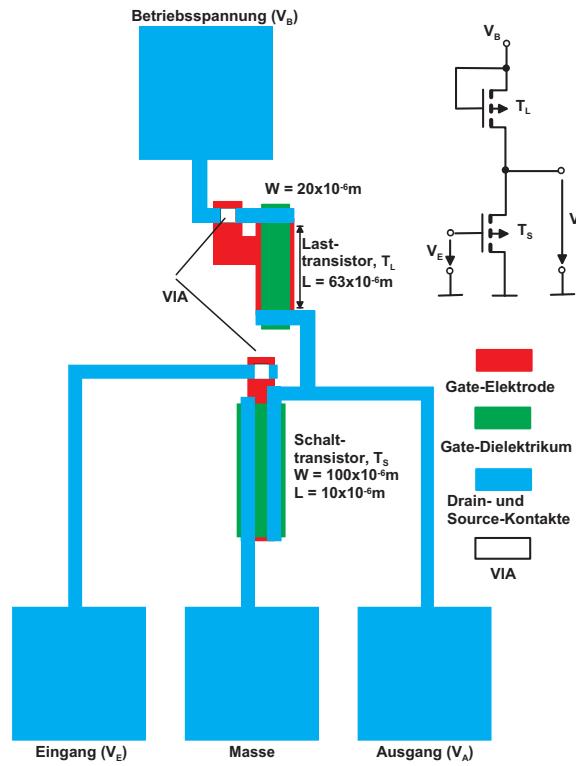

| 6.1 Aufbau einer Inverterschaltung, Layout 1 . . . . .                                                                                                                             | 94 |

| 6.2 Inverterkennlinie, Layout 1 . . . . .                                                                                                                                          | 95 |

| 6.3 Inverter, Layout 1 . . . . .                                                                                                                                                   | 96 |

| 6.4 Inverter, Layout2 . . . . .                                                                                                                                                    | 96 |

|                                           |    |

|-------------------------------------------|----|

| 6.5 Inverterkennlinie, Layout 2 . . . . . | 97 |

|-------------------------------------------|----|

# Tabellenverzeichnis

|     |                                                                                           |    |

|-----|-------------------------------------------------------------------------------------------|----|

| 4.1 | Zusammenfassung der Ergebnisse zur Charakterisierung der Dielektrika . . . . .            | 53 |

| 5.1 | Degradation der elektrischen Transistorparameter eines ungekapselten OFETs .              | 74 |

| 5.2 | Schwellenspannungswerte in Abhangigkeit verschiedener Drucke und Laborgase .            | 80 |

| 5.3 | Degradation der elektrischen Transistorparameter eines OFETs mit PTFE-Kapselung . . . . . | 90 |

# Kapitel 1

## Einleitung

Nach der Entdeckung halbleitender Eigenschaften in organischen Filmen zum Ende der 60' er Jahre des vergangenen Jahrhunderts wurden organische Halbleiter eher stiefmütterlich behandelt. Leistungsfähige mikroelektronische Schaltungen konnten mit der Siliziumtechnologie bereits seit Jahren hoch reproduzierbar und vergleichsweise preiswert hergestellt werden. Erst in den 90' er Jahren, als die Verbreitung mikroelektronischer Schaltungen im Alltagsgebrauch der Menschen wuchs, wurde das Interesse an organischen Halbleitern größer. Spätestens im Jahr 2000 mit der Verleihung des Nobelpreises in Chemie an Alan Heeger und seine Kollegen fand auch die breite Öffentlichkeit Interesse an den neuartigen Halbleitern und ihren Möglichkeiten. Inzwischen waren siliziumbasierte Schaltungen mit ihren Schaltgeschwindigkeiten in immer neue Dimensionen vorgestoßen, der durch den aufwändigen Herstellungsprozess bedingte Preis blieb jedoch konstant.

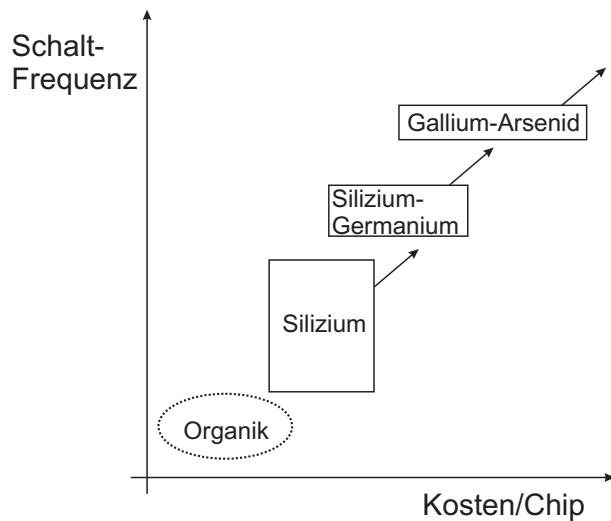

Parallel zur Weiterentwicklung der Siliziumtechnologie ist allerdings der Bedarf an preiswerten Schaltkreisen für einfachste Anwendungen in Spielzeugen oder zur Einmalverwendung, beispielsweise in der Medizin oder für Funketiketten in Handel und Logistik, stark angestiegen. Die von den anorganischen Schaltungen bei der Entwicklung zu immer schnelleren Taktfrequenzen hinterlassene Lücke im Niedrigpreissegment soll nun von den organischen Halbleitermaterialien geschlossen werden (siehe Abbildung 1.1).

Zwar sind die Schaltfrequenzen organischer Bauelemente heute noch vergleichsweise gering, einfache Anwendungen mit geringem Rechen- und Speicheraufwand lassen sich in naher Zukunft jedoch realisieren. Viele dieser Anwendungen werden heute alleine aus Kostengründen nicht in Siliziumtechnologie realisiert, preiswertere Schaltkreise würden der Technik jedoch zum Durchbruch verhelfen. Als Beispiel kann hierfür das 'Radio-Frequency-Identification-Tag' (RFID-Tag) genannt werden. Ein funkauslesbarer Speicher für Warenbestimmung und -preis könnte die heutige üblichen Strichcodes auf der Handelsware in Zukunft vollständig ersetzen und deren Funktion erweitern. Schon heute werden in der Waren-Logistik Funketiketten zur Ortung und Verfolgung von Warenpaletten eingesetzt. Da jedoch heute zum größten Teil noch Siliziumchips verwendet werden, ist der Preis für ein einzelnes RFID-Tag so hoch, dass sich ein Einsatz in Einweg-Etiketten, z.B. direkt auf der Ware, aus wirtschaftlichen Gründen nicht lohnt. Hier könnten organische Bauelemente in naher Zukunft zum Einsatz kommen.

Die Vorteile organischer Halbleitermaterialien liegen zum einen in der preiswerten Herstellung durch die chemische Industrie im großen Maßstab, was den Preis des Ausgangsmaterials gering

**Abbildung 1.1:** Während Germanium- und Silizium-Halbleiterbauelemente immer neue Schaltfrequenzbereiche erobern, eröffnet sich im unteren Preis- und Leistungssegment eine Lücke für organische Halbleiterbauelemente

hält. Zusätzlich eröffnen sich durch die Verwendung organischer Halbleitermaterialien grundsätzlich neue Produktionsverfahren für mikroelektronische Schaltungen. Durch die speziellen charakteristischen Eigenschaften der einzelnen Molekültypen lassen sich z.B. die Temperaturstabilität so genannter 'small molecules' oder die Löslichkeit von Polymeren in Lösungsmitteln bei der Herstellung dünner Filme ausnutzen. Je nach Molekültyp lassen sich damit dünne halbleitende Schichten durch thermisches Verdampfen bzw. Spin-coaten, Tintenstrahl- oder offset-Drucken [1][2][3] herstellen. Prinzipiell eignet sich jedes dieser Verfahren zur großflächigen Deposition dünner organischer Filme.

Durch die damit verbundene Unabhängigkeit vom Silizium als alleinigen Ausgangsmaterial für die Mikroelektronik ist die Verwendbarkeit flexibler Substratmaterialien statt der bislang benutzten starren Silizium-Wafer denkbar [4]. Dünne Kunststofffolien könnten als Basismaterial eingesetzt werden [5] und würden Druckprozesse im so genannten 'Rolle-zu-Rolle' Verfahren erlauben. Bei Anwendung eines geeigneten Druckprozesses ließe sich die Weltjahresproduktion mikrosystemtechnisch in Siliziumplanartechnik gefertigter Transistoren in wenigen Tagen in gleicher Stückzahl als organische Feldeffekt Transistoren (OFET) mit einer einzelnen Druckanlage bewältigen [6].

## 1.1 Organische Halbleiter in Leuchtdioden und Solarzellen

Wie in der anorganischen Halbleitertechnologie können mit organischen Halbleitern in Abhängigkeit von der elektronischen Bandlücke fotoelektrische Wandler als organische Leuchtdioden (OLED) oder Solarzellen, sowie elektronische Schalter als Transistoren gefertigt werden.

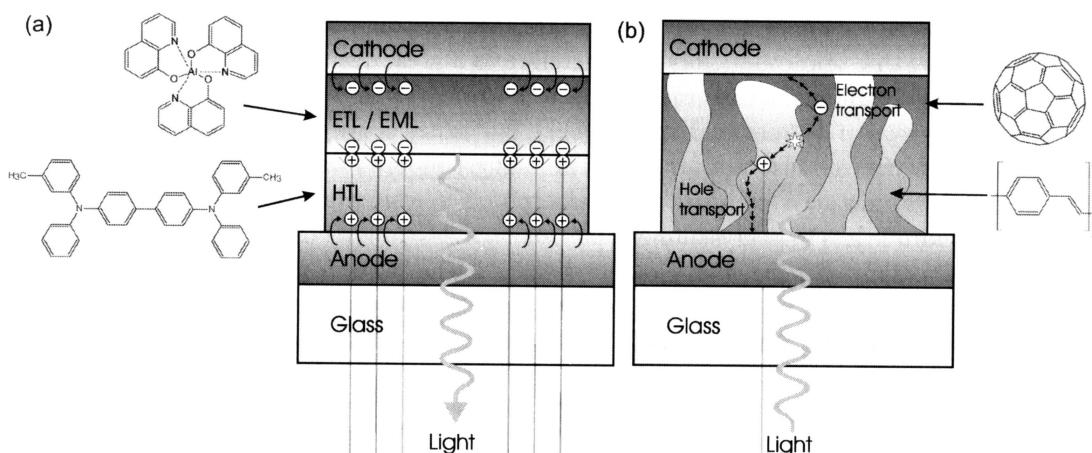

OLEDs und Solarzellen lassen sich durch aufeinander folgendes thermisches Verdampfen oder Spin-Coaten p- und n-leitender Materialien auf ein meist transparentes Substrat, wie z.B. ein mit Indium-Zinnoxid beschichtetes Quarzglas herstellen (siehe Abbildung 1.2). Als halbleitende Materialien eignen sich in Solarzellen als p-Leiter das Polymer PPV oder das kleine Molekül

Zink-Phtalocyanin, als n-Leiter kommt das thermisch verdampfbare Fullerene  $C_{60}$  in Frage. Um die Oberfläche des p-n-Übergangs zu vergrößern, bietet es sich an, eine Mischschicht aus p- und n-leitenden Materialien herzustellen [7]. Der Wirkungsgrad der Solarzellen hängt von der Anzahl der generierten Elektronen-Loch-Paare in Relation zur gesamten absorbierten Photonen-Zahl ab und liegt heute bei bis zu 3,5% [8]. Er steigt mit der Dicke der p-n-Übergangsschicht, da nur hier durch Photon-Wirkung Elektronen-Loch-Paare erzeugt werden können. Jedoch wirkt eine dicke organische Schicht auch dem Wirkungsgrad entgegen, da mit größerer Schichtdicke die Anzahl der rekombinierenden Ladungsträger beim Transport zu den in diesem Fall weiter entfernten Kontakten steigt.

Der spektrale empfindliche Bereich einer Solarzelle hängt von der Wahl des verwendeten Ausgangsmaterials und dessen Bandlücke ab [9]. Denkbar ist, zukünftig für eine breite spektrale Absorption Materialien mit entsprechenden elektronischen Eigenschaften zu entwickeln. Mögliche Einsatzgebiete für organische Solarzellen sind für bisher verwendete Solarpanele unwirtschaftliche geografische Regionen und Gebäudeseiten oder leichte ausrollbare Solarmodule für Weltraumsonden und Satelliten. Hier wurden bisher störungsanfällige Klappmechanismen für die starren Solarpanele eingesetzt.

**Abbildung 1.2:** Sowohl die organische Leuchtdiode (a) als auch die organische Solarzelle (b) basieren auf einer Heteroverbindung aus p- und n-leitenden organischen Halbleitern. ETL bezeichnet in dieser Abbildung die 'electron transport layer', HTL die 'hole transport layer' und EML die 'emission layer' (Nach [8])

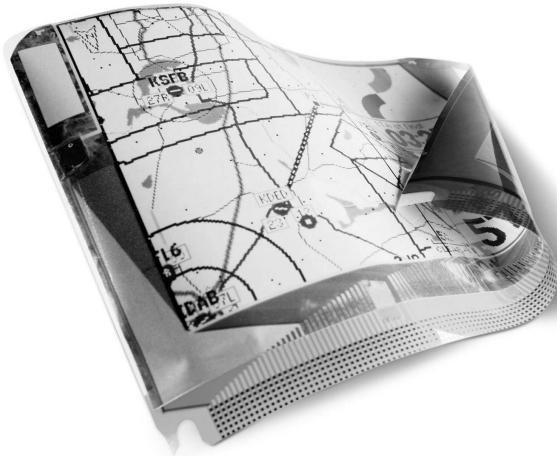

Das Funktionsprinzip der OLEDs basiert auf der Umkehrung des fotoelektrischen Effekts der Solarzellen. Hier werden Elektronen-Loch-Paare in einen p-n-Übergang injiziert, so dass es zur Rekombination des Ladungsträgerpaars unter Aussendung eines Photons kommt (siehe Abbildung 1.2). Die Wahl des Materials und damit der Bandlücke bestimmt die Farbe des ausgesandten Lichts [10]. Gegenüber heutigen TFT-Displays verzichten OLED-basierende Anzeigen auf eine Hintergrundbeleuchtung. Die selbstleuchtenden Elemente weisen hohe Betrachtungswinkel von nahezu 180° auf. Auch OLEDs lassen sich wie alle organischen Bauelemente auf flexiblen Substratmaterialien fertigen, was neuartigen Anwendungen, wie aufrollbaren Displays, den Weg ebnet (siehe Abbildung 1.3). Als Vorreiter der organischen Halbleiterbauelemente finden schon heute OLEDs in monochromen Anzeigen und Beleuchtungen, aber auch als RGB-Modul in Kleinbildschirmen von Autoradios und Digitalkameras Anwendung.

**Abbildung 1.3:** Gemeinsam mit OFETs als Treiberelement lassen sich OLEDs als Pixel-Bausteine in aufrollbaren Displays auf einem flexiblen Substrat integrieren

## 1.2 Der organische Feldeffekt Transistor

Neben biegsamen Leuchtdioden sind zur Verwirklichung aufrollbarer Displays auch flexible Schaltelemente zur Ansteuerung der Pixel notwendig [11] [12] [13]. Für organische Transistoren wird bislang das Prinzip des Feldeffekt Transistors favorisiert. Über eine Steuer-Elektrode, das so genannte Gate wird mittels einer angelegten Spannung die Ladungsträgerkonzentration im Halbleiter beeinflusst. So kann über die Gate-Source-Spannung der Stromfluss zwischen der Drain- und Source-Elektrode gesteuert werden (siehe Abbildung 1.4).

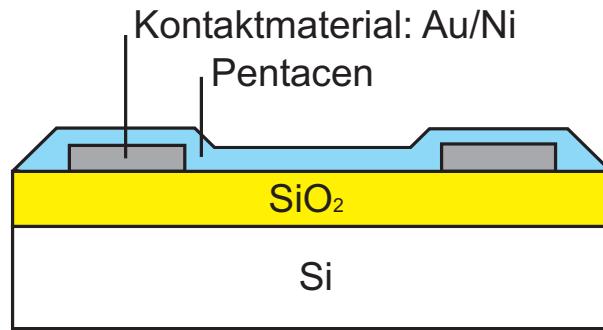

Pentacen als p-leitender Halbleiter wird im Anreichungsmodus betrieben, indem eine negative Spannung an die Gate-Elektrode angelegt wird. Dann werden die Löcher aus dem Pentacen-Film an der Grenzfläche zum Dielektrikum gesammelt und es bildet sich ein leitfähiger Ladungsträger-Kanal zwischen Drain- und Source-Kontakt aus [14]. Da organische Filme in der Regel eine sehr geringe Zahl freier Ladungsträger besitzen, müssen auch beim Pentacen für den Transistorbetrieb zusätzlich Ladungsträger aus dem Source-Kontakt in den Kanal fließen. Im Vergleich zur Siliziumtechnologie werden zum Betrieb der OFET heute noch hohe Spannungen bis zu 80V benötigt. Dies liegt an der noch geringen Ladungsträgerbeweglichkeit im organischen Halbleiter, die heute vergleichbar mit der von amorphemem Silizium ist [15] [16]. Die Ladungsträgerbeweglichkeit hängt unter anderem stark von der Morphologie der organischen Schicht ab (siehe Abschnitt 2.3). Eine ungeordnete Pentacen-Schicht verhindert eine hohe Ladungsträgerbeweglichkeit, da der Transport der Ladungsträger von Molekül zu Molekül durch einen geringen Molekülorbitalüberlapp behindert wird. Hohe Beweglichkeiten werden nur in hoch geordneten Filmen und Einkristallen erzielt. Eine Senkung der erforderlichen Gate-Source-Spannung wäre denkbar durch den Einsatz von Isolatoren mit großer Dielektrizitätszahl, wie beispielsweise Tantalpentoxid ( $\epsilon_r \approx 23$ ), oder die Senkung der Dicke des Dielektrikums im Gate-Bereich. Durch Verwendung eines Haftvermittlers kann auf das Wachstum der Pentacen-Schicht während des thermischen Verdampfens eingewirkt werden. Haftvermittler, wie beispielsweise das Octadecyltrichlorsilan, begünstigen eine hohe Ordnung im organischen Film.

*Abbildung 1.4:* Der organische Feldeffekt Transistor

Im einfachen experimentellen Aufbau wird oft auf die Strukturierung einer metallischen Elektrode verzichtet und stattdessen der hochdotierte Silizium-Wafer sowohl als Substrat, als auch als gemeinsames Gate für alle Transistoren auf der Scheibe verwendet (siehe Abbildung 1.4) [8]. Da zur Charakterisierung jeweils nur ein einzelner Transistor mittels Drain und Source kontaktiert wird, können Wechselwirkungen zwischen benachbarten Bauelementen ausgeschlossen werden. Wichtig ist nur eine ausreichende Isolierung der Zuleitungen zu Drain und Source mittels eines dicken Feldoxids, das die Gate-Bereiche ausschließt. Da bei der ganzflächigen Beschichtung der Transistoren mit dem Halbleitermaterial am Rand des Wafers ebenfalls das Substrat kontaktiert werden kann, sind geringe Leckströme möglich, aufgrund des hochohmigen organischen Halbleiters aber häufig vernachlässigbar.

Sollen einfache logische Schaltungen z.B. Inverter oder Ringoszillatoren realisiert werden, so werden frei ansteuerbare Gate-Elektroden benötigt (siehe Abbildung 1.5). Ein gleichzeitiges Ansprechen aller Gates ist hierbei nicht erwünscht. Weitere Strukturierungsschritte mittels Fotolithografie, Abscheide- und Ätztechnik sind notwendig, um eine Durchkontaktierung der elektrisch angesteuerten Gates durch das Dielektrikum zu ermöglichen. Unumgänglich ist hierbei auch die Verwendung eines für die metallischen Gate-Elektroden verträglichen Abscheideprozesses für das Dielektrikum.

*Abbildung 1.5:* Der organische Feldeffekt Transistor mit isolierter Gate-Elektrode für den Einsatz in einfachen logischen Schaltungen wie z.B. Invertern

# Kapitel 2

## Grundlagen

### 2.1 Elektronische Grundlagen organischer Halbleiter

Im Gegensatz zum anorganischen Halbleiter ist die Ursache des halbleitenden Effekts der organischen Halbleiter nicht im Kristall, sondern im Molekül selbst zu suchen. Im anorganischen Halbleitermaterial kommt erst durch die strenge Einhaltung der Gitterkonstanten als Abstand zwischen zwei Atomen im kristallinen Verbund die Ausbildung und der Charakter des Bandschemas zustande [17]. Im organischen Halbleiter dagegen liegen die Wurzeln des halbleitenden Effekts schon im Molekül und dessen Aufbau begründet. Als Grundgerüst des Moleküls dienen sowohl bei Polymeren als auch bei kleinen Molekülen Ketten von Kohlenstoffatomen. Als besonders stabil gilt dabei die abwechselnde Abfolge von Einfach- und Doppelbindungen, auch konjugierte Doppelbindung genannt. An den jeweiligen Kohlenstoffatomen kommt es dabei zu einer  $sp^2$ -Hybridisierung der Bindungsorbitale (siehe Abbildung 2.1).

**Abbildung 2.1:** Die  $sp^2$ -Hybridisierung der Bindungsorbitale ist Grundlage des delokalisierten  $\pi$ -Elektronensystems. Die Aufenthaltswahrscheinlichkeiten der Elektronen der  $p_z$ -Orbitale sind nach der Hückel-Theorie über das gesamte Molekül verschmiert (Nach [18])

Die Hauptlast der Bindung kommt dabei dem kugelförmigen s-Orbital zu, während das keulenförmige p-Orbital aus geometrischen Gründen einen schwächeren Anteil zu tragen hat. Bei langen Kohlenstoffketten oder aromatischen Molekülen wie dem Pentacen bestehen nach Hückel

[19] elektronische Wechselwirkungen der Elektronen des  $p_z$ -Orbitals mit entsprechenden Orbitalen weiterer Atome der Kohlenstoffkette. Das Resultat hieraus ist eine nicht verschwindende Aufenthaltswahrscheinlichkeit dieser Bindungs-Elektronen auf Atomen des gesamten Moleküls und eine große Zahl besetzbarer elektronischer Zustände. Die Aufenthaltswahrscheinlichkeit der Bindungs-Elektronen konjugierter  $\pi$ -Elektronensysteme ist über das gesamte organische Molekül verschmiert. Die Elektronen des  $p_z$ -Orbitals einer Doppelbindung sind nicht an ein Atom-Paar gebunden, sondern frei auf dem Molekül beweglich. Dieser Zustand wird als delokalisierte Doppelbindung bezeichnet. Abbildung 2.2 verdeutlicht die freie Beweglichkeit der delokalisierten Doppelbindung anhand der Mesomerie des Benzol-Moleküls.

**Abbildung 2.2:** Aufgrund der delokalisierten Doppelbindungen des Benzol-Moleküls können diese keinem der Kohlenstoffatome fest zugeordnet werden. Die linke und mittlere Darstellung treten mit gleicher Wahrscheinlichkeit auf; statt der einzelnen Doppelbindungen wird in der vereinfachten Darstellung (rechts) ein Kreis in das Benzol-Sechseck gezeichnet

## 2.1.1 Das Bändermodell organischer Halbleiter

Durch externe Anregung kann ein Elektron des  $\pi$ -Elektronensystems in einen angeregten Zustand übergehen. Die Anregung kann wie bei anorganischen Halbleitern in Form thermischer Energie oder auch durch Photonen genügend großer Energie erfolgen. Die Bandlücke des organischen Halbleiters wird durch die kleinste notwendige Energie für das Anheben eines Elektrons vom bindenden in ein anti-bindendes Orbital bestimmt. Analog zum Valenzband und Leitungsband des anorganischen Halbleiters wird im Fall organischer Halbleiter vom 'highest occupied molecular orbital' (HOMO) bzw. dem 'lowest unoccupied molecular orbital' (LUMO) gesprochen (siehe Abbildung 2.3). Die Energieniveaus eines Moleküls entstehen durch Linear-kombination der Atom-Energieniveaus (MO-LCAO-Ansatz, siehe [19]).

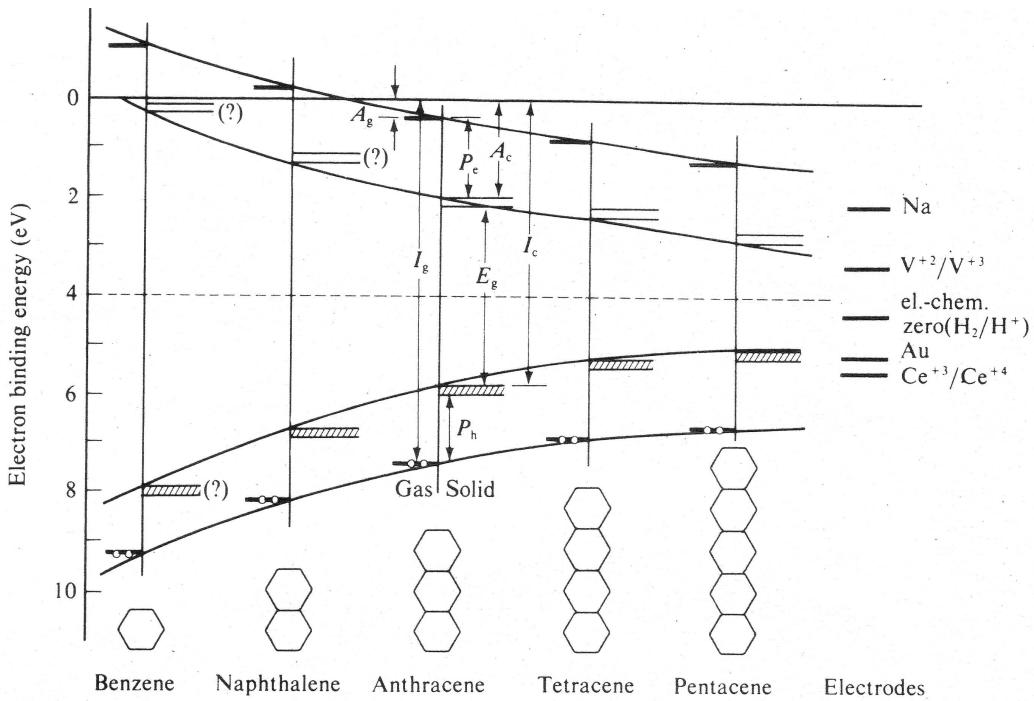

Die Dichte der elektronischen Zustände unter- und oberhalb der Bandkanten wird von der Größe und Verzweigtheit des Moleküls bestimmt. Da die elektronischen Zustände durch Wechselwirkung der  $\pi$ -Elektronen mit  $p_z$ -Orbitalen benachbarter Atome entstehen, steigt die Zahl der möglichen Zustände mit der Anzahl konjugierter Doppelbindungen und damit auch mit der Kettenlänge. Das in dieser Arbeit verwendete Halbleitermolekül Pentacen gehört zur Molekülgruppe der Acene. Wie aus Abbildung 2.4 ersichtlich, steigt mit zunehmender Kettenlänge die Anzahl der Energiezustände, resultierend in einer Abnahme der Bandlücke [20][21][22]. Weitere Zustände können durch die Reaktion des organischen Moleküls, beispielsweise mit dem Luftsauerstoff, während der Alterung eines OFETs entstehen (siehe Abschnitt 2.4). Diese Zustände entstehen auch innerhalb der Bandlücke, wo sie als Störstellen, so genannte 'traps', den Transport der Ladungsträger behindern.

**Abbildung 2.3:** Als  $p$ -leitender Halbleiter verfügt das Pentacen über eine flache energetische Lage von HOMO und LUMO. Zur Ladungsträgerinjektion bieten sich Metalle mit hohen Austrittsarbeiten ( $E_A$ ) wie z.B. Nickel, Palladium und Gold an (Nach [17])

**Abbildung 2.4:** Pentacen gehört zur Molekülgruppe der Acene. Mit wachsender Molekülkettenlänge nimmt die Anzahl der besetzbaren Zustände auf dem Molekül zu, die Bandlücke schrumpft (Nach [23])

Wie bei anorganischen Halbleitern existieren bei den organischen Halbleitern zwei Leitungstypen. Über den Leitungstyp entscheiden hier jedoch nicht der Charakter des Dotierstoffes, sondern hauptsächlich die Geometrie und die chemischen Eigenschaften des organischen Halbleitermoleküls. Das Fullerene  $C_{60}$  (siehe Abbildung 2.5) bildet als dünner Film n-leitende Eigenschaften aus. Bis zu sechs Elektronen kann das stark elektronegative Molekül auf seiner Oberfläche aufnehmen. Ursache der hohen Elektronegativität ist u.a. die sphärische Form des

Moleküls. Während sich in planaren Molekülen die p-Orbitale der Kohlenstoffatome gleichsam ober- und unterhalb der Molekülebene ausbreiten können, findet beim Fulleren eine Abstoßung der inneren p-Orbitale statt. Die räumliche Ausdehnung der äußeren p-Orbitale wird dadurch stärker ausgeprägt, die Ladungsdichte auf der äußeren Hülle des Fullerens erscheint geringer, also leicht positiv. Diese positive Ladung kann durch Aufnahme von weiteren Elektronen neutralisiert werden.

**Abbildung 2.5:** Das Fulleren  $C_{60}$  besitzt eine sphärische Form und hat einen stark elektronegativen Charakter

P-leitende Halbleiter wie das Pentacen können das Fehlen eines oder mehrerer Elektronen über ein weit verzweigtes Gerüst aus Doppelbindungen gut kompensieren. Die Elektronenaffinität des Moleküls ist deutlich geringer und drückt sich nicht zuletzt auch in der flacheren energetischen Lage von HOMO ( $-4.8\text{ eV}$ ) und LUMO ( $-3.1\text{ eV}$ ) aus (siehe Abbildung 2.3)[24].

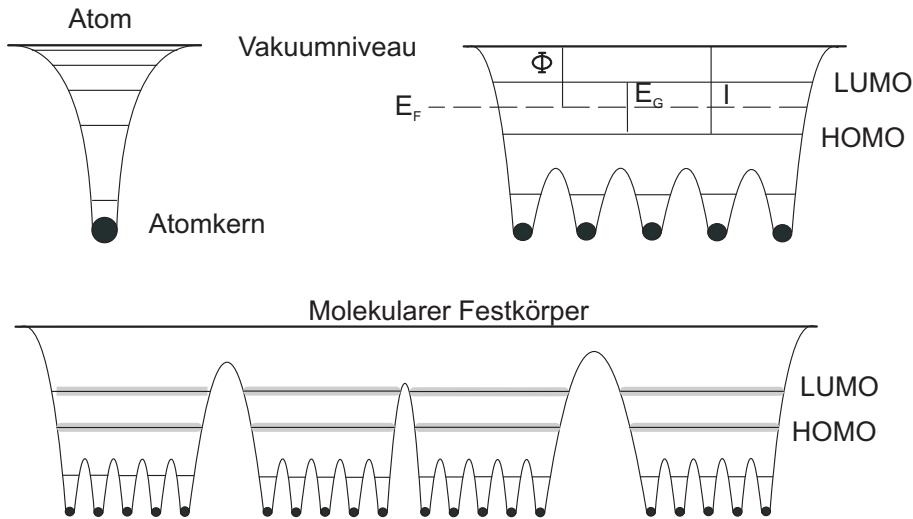

Der Elektronentransport auf dem organischen Molekül erfolgt über die angeregten Zustände des LUMO, der Löchertransport über das HOMO. Aufgrund der delokalisierten Doppelbindung kann der Ladungstransport über das Molekül durch ein Umklappen der Doppelbindung von einem Atom zum nächsten veranschaulicht werden. Über einen so ausgelösten Dominoeffekt kann ein Ladungsträger über das gesamte Molekül transportiert werden. Der Übergang zwischen benachbarten Molekülen erfolgt über einen Hopping-Mechanismus, der den Ladungsträger die Energiebarriere zwischen beiden Molekülen überwinden lässt (siehe Abbildung 2.6). Bei großer Ladungsträgerdichte im organischen Kristall ist die Zeitspanne zwischen zwei Hopping-Transporten auf einem Molekül so gering, dass dieses in der Zwischenzeit nicht aus dem angeregten Zustand relaxieren kann. Unter diesen Umständen ist die notwendige Aktivierungsenergie für das Hopping abgesenkt und es kommt bei den Ladungsträgern zu einem korrelierten Hopping bei erhöhter Ladungsträgerbeweglichkeit [25][26].

Das notwendige Überwinden der Energiebarrieren zwischen den Molekülen ist die Ursache für die geringere Ladungsträgerbeweglichkeit beim Hopping-Transport. Bei dem mit dem Pentacen verwandten Anthracen (siehe Abbildung 2.4) wird zwischen Hopping- und Bändertransport bei einer Ladungsträgerbeweglichkeit von  $1\text{ cm}^2/\text{Vs}$  unterschieden. Während man oberhalb dieses Werts von Bändertransport spricht, so ist unterhalb dieser Grenze Hopping-Transport anzutreffen [23]. Mit abnehmendem räumlichen Abstand zwischen den Molekülen prägt sich ein bandartiger Transportmechanismus aus. Der Bändertransport geht, verglichen mit dem Hopping-Transport, mit einer erhöhten Ladungsträgerbeweglichkeit einher. Für eine hohe Ladungsträgerbeweglichkeit ist eine hohe Ordnung der Moleküle im organischen Kristallverbund

**Abbildung 2.6:** Der Ladungstransport auf dem organischen Molekül erfolgt über angeregte Zustände. Zwischen den Molekülen erfolgt der Ladungstransport über Hopping-Mechanismen.  $\Phi$ =Fermi-Energie,  $E_F$ =Fermi-Level,  $I$ =Ionisationsenergie,  $E_G$ =Bandlücke

unumgänglich. Eine hohe Ordnung kann z.B. durch geeignete Herstellungsparameter beim thermischen Verdampfen organischer Moleküle erzeugt werden. Die Erzeugung der kristallinen Ordnung ist bei günstig gewählten Abscheideparametern ein selbstorganisierter Prozess (siehe Kapitel 2.3).

## 2.2 Das elektrische Verhalten des organischen Feldeffekt Transistors

Im standardisierten IEEE Messverfahren zur Charakterisierung von OFETs [27] wird vorgeschlagen, analog zur MOS-Technologie die Beschreibung des elektrischen Verhaltens und der Ladungsträgerbeweglichkeit über die Shockley-Gleichungen vorzunehmen [8]. Tatsächlich zeigen Modellierungsversuche vermessener Bauelemente durch die Shockley-Gleichungen, dass mit ihrer Hilfe eine Beschreibung des organischen Transistorverhaltens prinzipiell möglich ist [28]. Da die tatsächlichen elektrischen Abläufe innerhalb des organischen Halbleiterbauelements aufgrund ihrer Komplexität heute noch nahezu unerforscht bzw. umstritten sind, erfolgt die Beschreibung der in dieser Arbeit hergestellten OFETs zunächst basierend auf den nachfolgend vorgestellten Shockley-Gleichungen. Diese beschreiben den Stromfluss im Feldeffekt Transistor zwischen Drain- und Source-Kontakt und unterscheiden zwei Fälle:

$$I_{DS} = \frac{\mu \varepsilon_0 \varepsilon_r}{t_{ox}} \frac{W}{L} [(V_{GS} - V_{th})V_{DS} - \frac{1}{2}V_{DS}^2] \quad (2.1)$$

für den so genannten Trioden- oder linearen Anlaufbereich des Transistors, definiert durch:

$$V_{GS} - V_{th} > V_{DS}. \quad (2.2)$$

Der Sättigungsbereich eines Transistors wird nach Shockley beschrieben durch:

$$I_{DS} = \frac{\mu \varepsilon_0 \varepsilon_r}{2 t_{ox}} \frac{W}{L} [(V_{GS} - V_{th})^2] \quad (2.3)$$

für

$$V_{GS} - V_{th} \leq V_{DS}. \quad (2.4)$$

$I_{DS}$  bezeichnet hierbei den Strom durch den Transistor zwischen Drain- und Source-Kontakt,  $V_{GS}$  die Spannung zwischen Gate- und Source-Kontakt,  $V_{DS}$  die Drain-Source-Spannung,  $V_{th}$  die Schwellenspannung,  $\mu$  die Ladungsträgerbeweglichkeit,  $W$  die Transistorweite,  $L$  die Transistorlänge,  $t_{ox}$  die Dicke des Dielektrikums,  $\varepsilon_0$  die Dielektrizitätskonstante des Vakuums und  $\varepsilon_r$  die Dielektrizitätskonstante des Dielektrikums.

Im linearen Anlaufbereich mit  $V_{DS} \ll (V_{GS} - V_{th})$  wird der Leitwert im Transistorkanal durch:

$$g_m = \left( \frac{\partial I_{DS}}{\partial V_{GS}} \right)_{(V_{DS}=konstant)} = \frac{WC_i}{L} \mu V_{DS} \quad (2.5)$$

beschrieben, wobei  $C_i$  den Kapazitätsbelag des Dielektrikums darstellt.  $g_m$  wird in diesem Zusammenhang auch als Steilheit bezeichnet. Aufgelöst nach der Ladungsträgerbeweglichkeit  $\mu$  ergibt sich somit für den Anlaufbereich des Transistors:

$$\mu = \frac{\partial I_{DS}}{\partial V_{GS}} \frac{L}{WC_i V_{DS}}. \quad (2.6)$$

Für den Sättigungsbereich kann die Ladungsträgerbeweglichkeit über die Steigung der  $\sqrt{I_{DS}}$  –  $V_{GS}$  Kennlinie abgeschätzt werden. Aus der Shockley-Gleichung für den Sättigungsbereich erhält man:

$$\mu = \frac{\partial I_{DS}}{\partial V_{GS}} \frac{L}{WC_i} \frac{1}{(V_{GS} - V_{th})}. \quad (2.7)$$

Die Ladungsträgerbeweglichkeit im organischen Feldeffekt Transistor hängt von weiteren äußeren Einflüssen wie der Temperatur (beim Hopping-Transport), der Feldstärke der Gate-Source-Spannung (durch Auffüllen niedriger elektronischer Zustände mit steigender Gate-Source-Spannung und resultierender Absenkung der Hopping-Aktivierungsenergie) oder aber intrinsischen Faktoren wie der Morphologie des organischen Films ab. Während der Einfluss der Temperatur sich über die Angabe derselben oder die Feldstärke des Gate-Feldes über Art und Dicke des Dielektrikums abschätzen lassen, so ist beispielsweise die Morphologie der organischen Schicht schwer zu kontrollieren.

Die meisten Modelle zur Bestimmung der Ladungsträgerbeweglichkeit gehen von einer Gleichverteilung des Beweglichkeitswertes für alle Ladungsträger im Transistorkanal aus [8]. Dies ist jedoch nur bei einem nahezu einkristallinen Film anzunehmen, der nur bei idealen Aufwachsbedingungen entstehen kann. Geringe Abweichungen der Substrattemperatur, der Aufwachsrate oder der Reinheit der Oberfläche führen dagegen häufig zu einem Insel artigen Wachstum der organischen Kristallite. Pyramidale kristallin geordnete Strukturen werden dabei von einer

großen Anzahl von Korngrenzen durchzogen, so dass es lediglich am Fuße dieser Kristallite zu Berührungen kommen kann (siehe Abschnitt 2.3).

Es wird daher davon ausgegangen, dass oberhalb dieser ersten Molekül-Monolagen, die jedoch für den Großteil des Ladungstransports zuständig sind [29], gerade bei größeren elektrischen Gate-Feldern keine Gleichverteilung der Ladungsträgerbeweglichkeit anzutreffen ist. Innerhalb der einkristallinen Bereiche muss daher von einer viel größeren Ladungsträgerbeweglichkeit ausgegangen werden als bei Betrachtung des gesamten organischen Films. Durch Störstellen und elektronische Fallenzustände an den Korngrenzen, so genannte Traps, wird die Ladungsträgerbeweglichkeit im Mittel jedoch wieder deutlich reduziert [30]. Die Ladungsträgerbeweglichkeit hängt daher von der tatsächlichen Anzahl der freien Ladungsträger im Transistorkanal ab und kann durch [31]:

$$\mu_{Ofet} = \mu_{frei} \frac{Q_{frei}}{Q_{induziert}} = \mu_{frei} \frac{Q_{frei}}{Q_{frei} + Q_{getrapped}} \quad (2.8)$$

angenähert werden. Dabei beschreibt  $Q_{frei}$  die Anzahl freier Ladungsträger,  $Q_{induziert}$  die Zahl vom Gate-Source-Feld induzierter Ladungsträger und  $Q_{getrapped}$  die Zahl in Fallenzuständen gefangener Ladungsträger. Als  $\mu_{frei}$  ist die Ladungsträgerbeweglichkeit im ausgedehnten organischen Kristall ohne Störstellen und Traps einzusetzen.

Zur Bestimmung der Ladungsträgerbeweglichkeit  $\mu$  gibt es weitere Verfahren, die die Betrachtungsweise entweder auf das gesamte Bauelement unter Berücksichtigung der Kontaktwiderstände beziehen, oder sich auf die Angabe der Beweglichkeit im organischen Film beschränken. Der Vorteil der alleinigen Betrachtung des organischen Films ist, dass der bei OFETs nicht unerhebliche Kontaktwiderstand keinerlei Verfälschung des intrinsischen Wertes verursacht. Ein Beispiel für die Messung der Ladungsträgerbeweglichkeit sind so genannte 'time of flight' Experimente. Über einen kurzen Laserimpuls werden im organischen Film Elektronen-Loch-Paare generiert, deren Laufzeit zu den Kontakten in einem konstanten elektrischen Feld gemessen wird. Diese Methode findet häufig bei der Charakterisierung organischer Einkristalle Verwendung und kann für gezielte Wachstumsstudien verwendet werden [8].

Da die Charakterisierung von Bauelementen regelmäßig auf eine technologische Einstufung für den Einsatz in logischen Schaltungen hinausläuft, ist es meist sinnvoll, die Ladungsträgerbeweglichkeit auch im Zusammenhang mit dem Kontaktwiderstand zu betrachten. Eine Optimierung der Transistorschaltfrequenz kann daher nicht allein auf der Erhöhung der intrinsischen Ladungsträgerbeweglichkeit im Transistorkanal beruhen, sondern muss immer mit einer gleichzeitigen Betrachtung des Kontaktwiderstands einhergehen. Der Gesamtwiderstand  $R_{Gesamt}$  des Transistors setzt sich dabei aus den Kontaktwiderständen  $R_{Kontakt}$  und dem Kanalwiderstand  $R_{Kanal}$ , berechnet aus der Transistorgleichung für den Anlaufbereich (vgl. Gl. 2.1), wie folgt zusammen:

$$R_{Gesamt} = 2 \cdot R_{Kontakt} + \frac{\partial V_{DS}}{\partial I_{DS}} \Big|_{V_{DS} \rightarrow 0}^{V_{GS}} = 2 \cdot R_{Kontakt} + \frac{L}{W(C_i \mu(V_{GS} - V_{th}))}. \quad (2.9)$$

Der Kontaktwiderstand fließt hierbei doppelt ein, da für die Ladungsträger sowohl am Drain- als auch am Source-Kontakt ein Widerstand zu überwinden ist. Da die Ladungsträgerinjektion

jedoch nicht immer den gleichen Widerstand wie die Extraktion der Ladungsträger hervorruft, wird hierbei nur der Mittelwert berücksichtigt, der jedoch im allgemeinen zur Beurteilung eines Bauelementes ausreicht. Genauere Werte der Widerstände an Drain und Source können beispielsweise mit einem zum Potentiometer umgebauten Rasterkraftmikroskop (AFM) ermittelt werden [32].

Die Schwellenspannung als Bestandteil der Shockley-Gleichungen für Feldeffekt Transistoren ist ein Maß für die Ausbildung des leitfähigen Kanals zwischen Drain- und Source-Kontakt bei Anlegen einer definierten Gate-Source-Spannung. Im Falle des p-leitenden Pentacen wird bei einer negativen Schwellenspannung von einem selbstsperrenden und bei einer positiven Schwellenspannung von einem selbstleitenden Transistorverhalten gesprochen. Während im ersten Fall durch das Anlegen der Gate-Source-Spannung zunächst Ladungsträger im Transistorkanal akkumuliert werden müssen, so ist die Ladungsträgerkonzentration im zweiten Fall schon so groß, dass zum Sperren des Kanals eine positive Spannung notwendig ist, um alle Ladungsträger aus dem Kanal herauszutreiben.

Die Größe der Schwellenspannung hängt von vielen Eigenschaften des Bauelementes ab. Ein entscheidender Faktor ist im Falle des OFETs die Dichte von Störstellen im organischen Film und an der Grenzfläche zum Dielektrikum. Störstellen an den Korngrenzen des organischen Films rufen Potenzialschwellen hervor, die den Band ähnlichen Ladungstransport hemmen können. Die Potenzialschwellen müssen durch eine erhöhte Gate-Source-Spannung ausgeglichen werden, ausgedrückt in einer Verschiebung der Schwellenspannung. Weitere Einflussgrößen für den Wert der Schwellenspannung sind z.B. die Wahl und die Qualität des Kontaktmaterials. Nicht zu vernachlässigen ist schließlich noch die Möglichkeit eines unerwünschten Dotiereffekts, beispielsweise durch Luftsauerstoff, welcher in vielen organischen Halbleitern einen selbstleitenden Charakter verursacht. Für Zink-Phtalocyanin ist zum Beispiel bekannt, dass im Kontakt mit Sauerstoff eine deutliche Erhöhung des Leitwertes messbar ist [33].

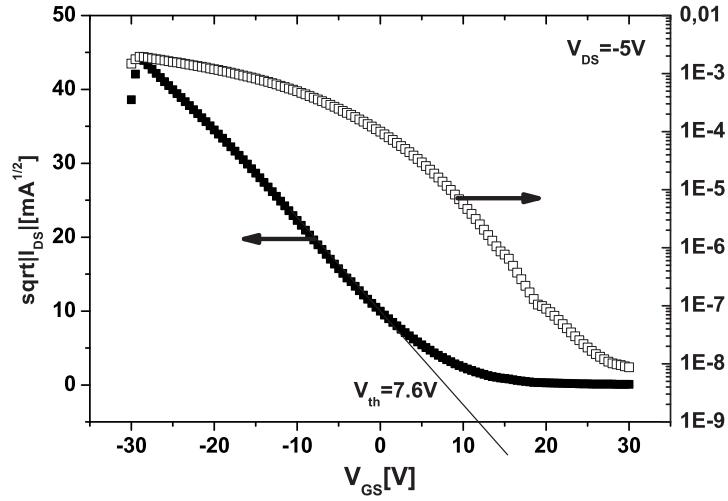

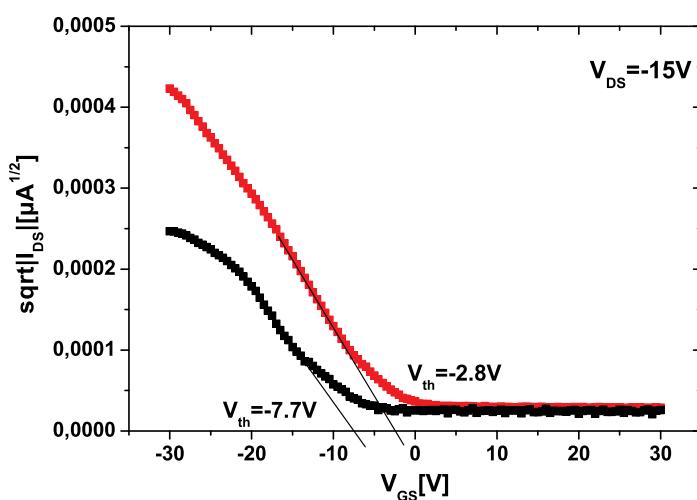

Zur Bestimmung der Schwellenspannung gibt es in der Literatur mehrere Ansätze. In der IEEE-Messvorschrift für organische Feldeffekt Transistoren [27] wird empfohlen, die Schwellenspannung aus der Eingangskennlinie zu bestimmen: Wie aus zahlreicher Beispielliteratur [34] [35] [36] [37] ersichtlich, wird dazu am Punkt maximaler Steigung der  $\sqrt{I_{DS}} - V_{GS}$  Kennlinie in Sättigung eine Gerade extrapoliert (siehe Abbildung 2.7). Der Schnittpunkt der extrapolierten Geraden mit der Abszisse ( $I_{DS} = 0 \text{ A}$ ) gibt hiernach den Schwellenspannungswert  $V_{th}$  des jeweiligen Transistors an [38]. Die Autoren von [31] bestreiten jedoch eine Eindeutigkeit des Wertes für die so ermittelte Schwellenspannung und weisen auf resultierende Schwierigkeiten bei der anschließenden Bestimmung der Ladungsträgerbeweglichkeit durch die Shockley-Gleichungen hin. Tatsächlich hängt die Schwellenspannung neben den oben genannten Bauelementfaktoren zumindest noch von der Temperatur ab [38]. Meijer et al. schlagen hier statt der Verwendung einer Schwellenspannung den Gebrauch einer so genannten 'switch-on Voltage' ( $V_{SO} = 0 \text{ V}$  für einen undotierten Halbleiter) vor. Diese soll lediglich die Gate-Source-Spannung darstellen, korrigiert um einen Spannungswert, der durch eine unerwünschte Dotierung bestimmt wird.

Die in dieser Arbeit veröffentlichten Werte für die Schwellenspannung wurden entsprechend der IEEE-Messvorschrift, wie oben beschrieben, durch Extrapolation aus der  $\sqrt{I_{DS}} - V_{GS}$  Kennlinie ermittelt. Da Modellierungen zeigen, dass die im Rahmen dieser Arbeit gefertigten OFETs aufgrund eines dominierenden Kontaktwiderstands im Anlaufbereich bzw. Übergangsbereich des Transistors der Drain-Source-Strom eine stärkere Übereinstimmung mit der quadratischen

**Abbildung 2.7:** Ermittlung der Schwellenspannung durch Extrapolation aus der Eingangskennlinie im Punkt maximaler Steigung. Der Schnittpunkt der Gerade mit der Gate-Spannungsachse ergibt den Wert für die Schwellenspannung

Abhängigkeit von der Gate-Source-Spannung aufweisen (siehe Kapitel 4.6), wurden die hier beschriebenen Schwellenspannungswerte meist abweichend von [27] im Anlaufbereich der Kennlinie ermittelt.

Alle in diesem Abschnitt vorgestellten Verfahren beruhen auf unterschiedlichen physikalischen Modellen, die teilweise aus der MOS-Technik übernommen wurden und somit nur bedingt zur Beschreibung von OFETs beitragen können. Trotzdem wird zum Ermitteln der Schwellenspannung auch in der Literatur auf diese Verfahren zurückgegriffen, da bisher keine umfassende und überzeugende Theorie zur Beschreibung der Schwellenspannung in OFETs existiert.

Da jedes dieser möglichen Verfahren jeweils verschiedene Werte für die Schwellenspannung liefert, ist es zur Angabe einer Schwellenspannung in Veröffentlichungen also unabdingbar, die verwendete Methode zu nennen. Der Weg zur Bestimmung der Schwellenspannung über die Quadratwurzel der Eingangskennlinie ist das Verfahren mit der in der Fachwelt größten Zustimmung. Es ist am weitesten verbreitet und liefert so die größte Vergleichbarkeit der Ergebnisse.

Das Einschaltverhalten des Transistors wird über den Subschwellenspannungstromanstieg

$$S = \frac{dV_{GS}}{d \log(I_{DS})} \quad (2.10)$$

charakterisiert. Die Steigung der logarithmisch aufgetragenen Eingangskennlinie ist ein gutes Maß für die Ausbildung und Qualität eines elektrisch leitfähigen Kanals nahe des Dielektrikums als Reaktion auf das Anlegen einer Gate-Source-Spannung. Während in der MOSFET-Technologie ein geringer Subschwellenspannungstromanstieg eine gute Grenzfläche zwischen dem Dielektrikum und dem Halbleiter prognostiziert, so kann im Falle eines OFETs ebenfalls eine gute Kontaktwiderstand an den Drain- und Source-Kontakten vermutet werden [8]. Dieser

spielt bei organischen Feldeffekt Transistoren eine viel größere Rolle und ist dazu noch von der Gate-Spannung abhängig.

## 2.3 Das organische Halbleitermaterial Pentacen

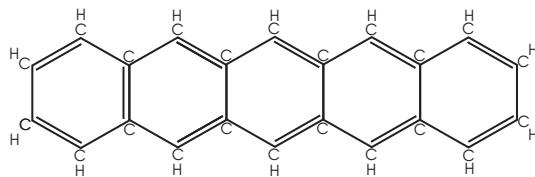

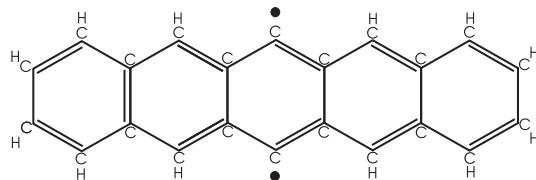

Das Basismaterial der in dieser Arbeit vorgestellten Feldeffekt Transistoren ist der p-leitende Halbleiter Pentacen,  $C_{22}H_{14}$  mit einer Bandlücke von  $1.7\text{eV}$  (siehe Kap. 2.1.1), einer Molekülmasse von  $278.35\text{ g/mol}$  und einer für organische Materialien typischen Dichte von  $1.3\text{ g/cm}^3$ . Mit dieser Molekülmasse zählt es zu den so genannten 'kleinen Molekülen', die weitläufig unter dem Begriff 'small molecules' zusammengefasst werden. Das Pentacen besteht aus fünf linear angeordneten Benzol-Ringen (siehe Abbildung 2.8), welche ein planares Molekül ergeben. Pentacen weist dadurch eine hohe Spiegel- und Rotationssymmetrie auf, was das Molekül nahezu unpolar erscheinen lässt.

*Abbildung 2.8: Kekulé-Struktur des Pentacen-Moleküls*

Die Planarität spielt nicht zuletzt für die Ausbildung des delokalisierten Elektronensystems eine wichtige Rolle, sorgt sie doch für eine gleichmäßige Ausbreitung der  $\pi$ -Orbitalwolke ober- und unterhalb der Molekülebene. Auch für die Entwicklung einer Ordnung im organischen Kristallverbund ist die planare Ausführung des Pentacens von Vorteil. Pentacen lässt sich im Hochvakuum, geheizt auf eine Temperatur oberhalb von  $220 - 240^\circ\text{C}$  durch thermisches Verdampfen auf ein Substrat, z.B. einen Silizium-Wafer, als dünner Film abscheiden. Sind die Aufdampfparameter geeignet gewählt, so bildet sich im Pentacen-Film eine hohe Ordnung der Pentacen-Moleküle ähnlich eines Fischgrätenmusters aus [22][39][40]. Entscheidend für einen geordneten organischen Film mit hoher Ladungsträgerbeweglichkeit sind die Substrattemperatur, die Aufdampfrate, der Abstand zwischen der Verdampferquelle und dem Substrat, die Reinheit des verwendeten Materials und der Prozessdruck [16].

Die Reinheit des verwendeten Materials ist von nicht unerheblicher Bedeutung. Verunreinigungen des Quellmaterials der thermischen Verdampfung besitzen möglicherweise eine geringere Verdampfungstemperatur als das Pentacen und lagern sich in der Aufwärmphase der Verdampfung auf der Oberfläche des Dielektrikums und damit im für den Stromfluss entscheidenden Bereich des Transistors an. Hier können die Verunreinigungen beispielsweise als Keime für ein ungeordnetes Wachstum dienen. Findet die Verdampfung bei zu hohem Druck statt, so können vermehrt Bestandteile aus dem Restgas des Rezipienten in den abgeschiedenen Film eingebaut werden. Neben der Störung des Filmwachstums ist auch eine Beeinflussung der Transistor-schwellenspannung bei Anwesenheit ionischer Verunreinigungen durchaus denkbar. Eingebaut in den molekularen Film werden Verunreinigungen zudem oft zu Traps, die den Ladungstransport behindern.

Das in dieser Arbeit verwendete Pentacen wird in höchster angebotener Reinheit (99.9%) von der Firma Aldrich bezogen und ohne weitere Aufreinigung verwendet. Zu Vergleichszwecken wird eine Charge Pentacen vom Fraunhofer-Institut Dresden verwendet. Dieses wurde einer mehrfachen Dreizonensublimation unterzogen, die durch eine Temperaturgradient-Abscheidung Substanzen mit der von Pentacen abweichenden Verdampfungstemperatur extrahiert [7].

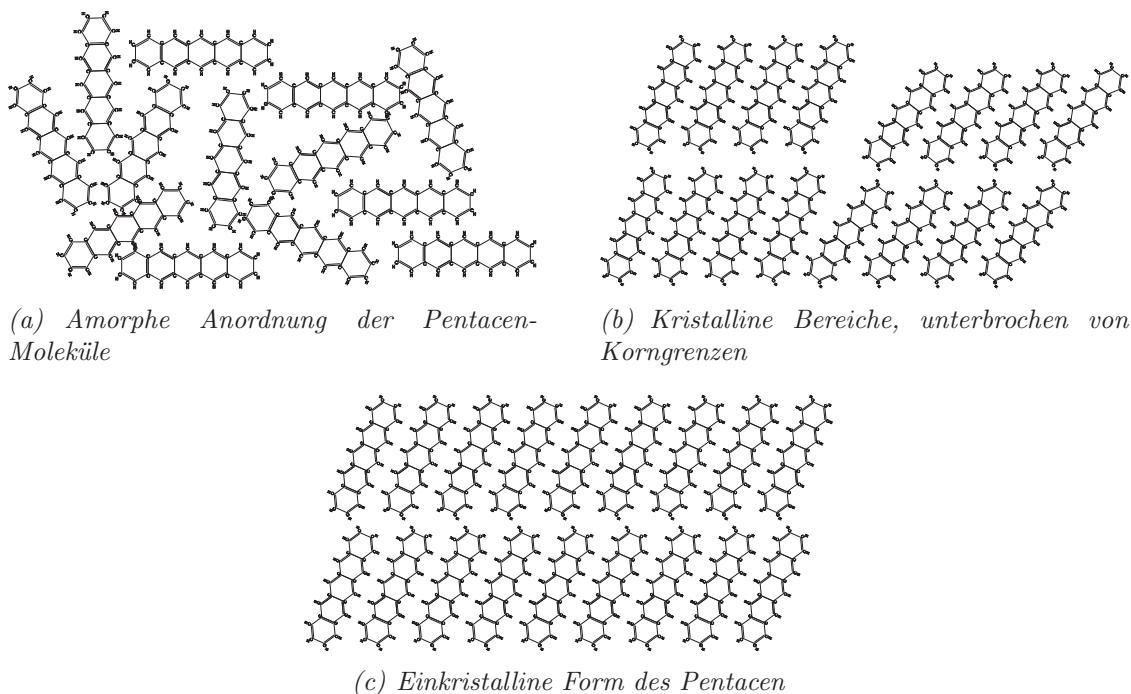

Die Substrattemperatur spielt für die Beweglichkeit der verdampften Moleküle auf der Substratoberfläche eine wichtige Rolle. Da sich die auftreffenden Moleküle selbstorganisiert [4] an das Ende eines bereits vorhandenen Films oder an einen Keim anlagern, benötigen sie noch eine gewisse kinetische Energie, um auf der Substratoberfläche mobil zu sein. Ist die Substrattemperatur zu gering, so wird den auftreffenden Molekülen vom kalten Substrat die verbliebene kinetische Energie sofort entzogen. Sie erstarren in der Lage, wie sie auf die Oberfläche auftreffen, meist zu einem amorphen Film, der so genannten 'bulk'-Phase (siehe Abbildung 2.9(a)).

Ist die Substrattemperatur zu hoch gewählt, so kommt es unter Umständen zu einem erneuten Abdampfen des Pentacens von der Oberfläche; nachfolgende Moleküle werden beim Auftreffen auf das Substrat gestreut. Nur bei geeigneter Temperatur, die in der Literatur für Pentacen mit ca.  $60 - 70^\circ\text{C}$  angegeben wird [41][42][43], ist eine ideale Anlagerung der Pentacen-Moleküle an die bereits vorhandene Schicht gegeben. Durch van-der-Waals Wechselwirkungen, resultierend aus der Nullpunktsunruhe der äußeren Elektronen des Moleküls, gibt es eine energetisch günstige Anordnung, bei der sich benachbarte Moleküle parallel zueinander ausrichten und einen geringen räumlichen Abstand einnehmen (siehe Abbildung 2.9(c)). Dabei entsteht die so genannte einkristalline Phase. Durch zusätzliche Wechselwirkung des Pentacen-Moleküls mit dem Substrat stellen sich die Moleküle unter einem Winkel von ca.  $85^\circ$  entlang ihrer Hauptmolekülachse auf die Spitze [34][39][44][45][46]. Eine chemische Bindung mit dem Substratmaterial geht das Pentacen dabei jedoch nicht ein [47] [48].

Einen ähnlichen Einfluss auf die Form und Qualität des Schichtwachstums hat die Aufdampfrate des organischen Materials. Wird die Rate zu groß gewählt, so bleibt auf der Substratoberfläche eingetroffenen Molekülen bis zum Auftreffen der nächsten Moleküle nicht genügend Zeit, sich mit bereits vorhandenen Molekülen zu einem geordneten Film zusammenzuschließen. Das Resultat ist die Bildung von pyramidenförmigen Molekül-Kristallen, die nur in ihrer Basis in direkten Kontakt mit benachbarten Inseln treten können (siehe Abbildung 2.9(b)).

Es ist nachvollziehbar, dass diese pyramidalen Strukturen nur bedingt zum Ladungstransport beitragen können, da sie mit benachbarten Kristallen nur am Fuße elektrisch verbunden sind. Neben diesem offensichtlichen Effekt kann die Inselbildung weitere Nachteile mit sich bringen: An den Korngrenzen der Inseln lagern sich im Rahmen der Alterung des organischen Films mit der Zeit vermehrt Wasser- und Sauerstoffmoleküle an, die Ursache für Störstellen sind und eine Reduktion der Ladungsträgerbeweglichkeit sowie eine Verschiebung der Schwellenspannung des OFETs zur Folge haben.

Pentacen ist bekannt für eine hohe Ladungsträgerbeweglichkeit im organischen Kristallverbund, hier werden theoretische Ladungsträgerbeweglichkeiten von bis zu  $75 \text{ cm}^2/\text{Vs}$  vorhergesagt [49]. Verglichen mit weiteren häufig verwendeten organischen Halbleitermaterialien nimmt das Pentacen eine Spitzenposition in der Ladungsträgerbeweglichkeit in realen Bauelementen ein [44]. Auf dem Pentacen-Molekül selbst ist die Ladungsträgerbeweglichkeit stark anisotrop. Während entlang der Hauptmolekülachse eine geringe Ladungsträgerbeweglichkeit vorherrscht, ist senkrecht dazu die größte Beweglichkeit der Ladungsträger auf dem Molekül messbar [22][50][51].

**Abbildung 2.9:** Abhängig von der Substrattemperatur und der Aufwachsrate während der thermischen Verdampfung des Pentacens bilden sich a) eine amorphe Phase, b) eine Phase kristalliner Inseln (unterbrochen von Korngrenzen) c) oder der organische Einkristall [44]

Diese Eigenschaft, kombiniert mit der Tatsache, dass sich die Pentacen-Moleküle während des thermischen Verdampfens vorrangig auf die Molekülspitze gestellt anordnen, ist die Grundlage für eine hohe Ladungsträgerbeweglichkeit im organischen Bauelement. Sorgfältig präparierte Pentacen-Filme weisen in den ersten Monolagen oberhalb des Dielektrikums eine hohe Ordnung der Pentacen-Moleküle auf. Durch einen geringen Abstand im fischgrätenartig geordneten Film ist ein effizienter Ladungstransport zwischen den Molekülen durch einen hohen  $\pi$ -Orbital-Überlapp gewährleistet.

Da auch auf dem Molekül der Ladungstransport parallel zum Dielektrikum mit hoher Ladungsträgerbeweglichkeit abläuft, resultiert diese Anordnung der Pentacen-Moleküle in einer hohen mittleren Ladungsträgerbeweglichkeit in den ersten Pentacen-Monolagen.

## 2.4 Vor- und Nachteile organischer Halbleitermaterialien

Wie bei jeder technischen Neuerung müssen auch für organische Halbleiter die Vor- und Nachteile der Technologie gegeneinander aufgewogen werden.

Das am häufigsten verwendete Argument für die Entwicklung organischer Halbleiter ist der spätere Preis eines solchen Bauelementes. Sowohl bei der chemischen Synthese des Basismaterials, das sich in hoher Reinheit im großen Maßstab herstellen lässt, als auch bei der späteren Verarbeitung zur Herstellung der elektronischen Elemente durch großflächige Verarbeitung fallen nur geringe Kosten an. Alleine bei der Herstellung und Reinigung von Silizium-Wafern sind mehrere

Energie zehrende Hochtemperaturschritte von über 1000°C notwendig [52]. Die Prozessierung rein organischer Bauelemente findet hauptsächlich, schon alleine wegen der niedrigschmelzenden Substratmaterialien, im Temperaturbereich unter 200°C statt [53].

Neben den Energiekosten ist dabei auch der Umweltaspekt bei der Herstellung nicht zu vernachlässigen. Dieser spielt auch bei der weiteren Prozessierung in der Siliziumtechnologie eine Rolle, wird hier doch eine Vielzahl von Säuren und Lösungsmitteln eingesetzt. Auf hochgiftige Flusssäure zum Ätzen von  $SiO_2$  kann z.B. bei Verwendung von Kunststoffsubstraten völlig verzichtet werden.

Als weiterer Kostenfaktor kann die Prozessierbarkeit organischer Halbleiter in großflächigen Abscheideprozessen genannt werden. Je nach Material kann die halbleitende Schicht durch thermisches Verdampfen kleiner Moleküle oder durch Spin-coating, Tintenstrahl-Drucken oder Offset-Drucken löslicher Polymere erzeugt werden. Jedes dieser Verfahren eignet sich für die kostengünstige Beschichtung großer Flächen in der industriellen Fertigung. Hervorzuheben sind dabei besonders das thermische Verdampfen wie auch das Offset-Drucken für eine kostengünstige 'Rolle-zu-Rolle' Produktion, vergleichbar mit dem Zeitungsdruck.

Ein weiteres Argument für organische Halbleitermaterialien ist, dass der Entwicklung neuer Molekül-Eigenschaften praktisch keine Grenzen gesetzt werden können. Immer neue Moleküle mit geänderten oder neuen Seitengruppen werden entwickelt und ermöglichen die Erweiterung der elektronischen und physikalischen Eigenschaften des jeweiligen Molekül-Typs.

Jedoch hat die Verwendung organischer Halbleiter in elektronischen Bauelementen einen klaren Nachteil. In Kontakt mit Sauerstoff und Feuchtigkeit unterliegen die organischen Moleküle einer raschen Alterung, die durch gleichzeitige Bestrahlung mit ultraviolettem Licht noch beschleunigt wird. Das in der organischen Photovoltaik vielfach benutzte Fullerene  $C_{60}$  beispielsweise bildet unter UV-Licht Bestrahlung einen angeregten Zustand aus, der mit Sauerstoff z.B. aus der Luft reagiert und das Molekül aufbrechen lässt.

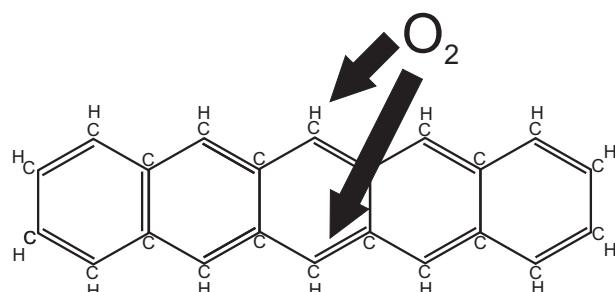

Das in dieser Arbeit verwendete Pentacen bildet in Anwesenheit von Sauerstoff eine Chinon-Verbindung aus [54] (siehe Abbildung 2.10), wobei es zu einer Störung des delokalisierten  $\pi$ -Elektronensystems kommt [55]. Dies hemmt den Ladungstransport über das Molekül durch Streuung der Ladungsträger an den Defekten der elektronischen Bänder und drückt sich nach außen in einer reduzierten Ladungsträgerbeweglichkeit aus. Zusätzlich bilden sich dabei neue Molekülenergieniveaus aus, die die Ursache für Störstellen im organischen Film darstellen.

**Abbildung 2.10:** In Anwesenheit von Sauerstoff, z.B. aus der Umgebungsluft, weist das Pentacen eine hohe Reaktivität zum Pentacen-Chinon ( $C_{22}H_{12}O_2$ ) auf. Der Sauerstoff lagert sich dabei vorrangig an den mittleren Benzol-Ring des Pentacens an [55]

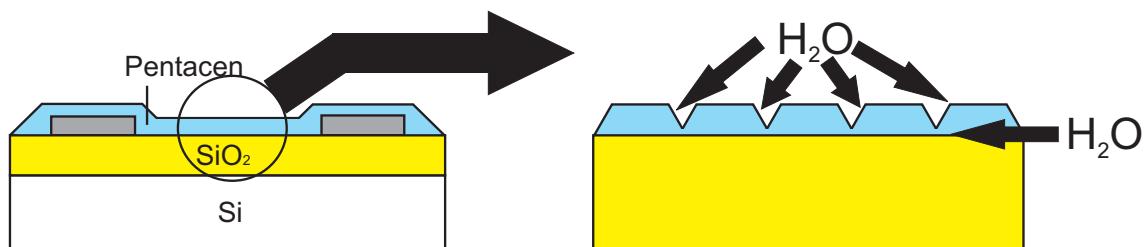

Wassermoleküle gelangen zumeist über die Luftfeuchtigkeit in die organische Schicht. Im elektrischen Feld des Transistors dissoziert das Wassermolekül [55]. Die so entstandenen Ionen lagern sich häufig an den Korngrenzen zwischen kristallinen Molekülbereichen oder auch an der Grenzfläche zwischen dem Dielektrikum und dem organischen Film an [56] (siehe Abbildung 2.11). In beiden Fällen kommt es durch Ladungseffekte zur Ausbildung von Potenzialbarrieren. Im ersten Fall führt dies zur Hemmung des Stromflusses durch den Transistorkanal, im zweiten Fall sind sie die Ursache für die Verschiebung der Schwellenspannung bei den OFETs.

**Abbildung 2.11:** Durch Anlegen der Gate-Source-Spannung lagern sich Wassermoleküle aus der Umgebungsluft an die Grenzfläche zwischen Dielektrikum und Halbleiter, sowie an den Korngrenzen des ungekapselten organischen Films an

Da diese Alterungsmechanismen unkontrolliert und teilweise auch reversibel [57] die elektrischen Parameter organischer Bauelemente beeinflussen, stellen sie das schwer wiegendste Problem bei der Herstellung organischer Schaltungen dar. Beispielsweise verhindern unkontrollierbare Schwankungen der Ladungsträgerbeweglichkeit die Entwicklung zuverlässig arbeitender Schaltungen. Eine verlässliche Kapselung der organischen Bauelemente gegen die Faktoren der Alterung ist daher unerlässlich.

## 2.5 Abschätzung des Entwicklungspotenzials organischer Bauelemente

Verglichen zur anorganischen Halbleitertechnologie weisen die organischen Halbleitermaterialien und Bauelemente einen mehr als 30-jährigen Forschungsrückstand auf. Trotz dieses erheblichen Entwicklungsdefizits ist es einigen Elektronikkonzernen schon heute möglich, erste einfache Anwendungen organischer Halbleiter als OLEDs in einfachen Multisegment-Anzeigen (Ladezustand-Anzeige im Rasierer), kleinflächigen Dot-Matrix-Displays (Autoradio, MP3-Player) und ersten TFT-Bildschirmen (Digitalkamera) am Markt zu platzieren. Das enorme Potenzial der organischen Halbleiter ist gerade an den bislang noch recht einfachen Anwendungen sehr gut erkennbar: Die Brillanz des Farbdisplays der oben erwähnten Digitalkamera überwog in der Beschreibung der Fachpresse alle weiteren technischen Eigenschaften der Kamera. Die Haltbarkeit dieser neuartigen Bauelemente ist heute jedoch noch sehr begrenzt, so dass sich beim Hersteller des Autoradio-Displays schon sechs Monate nach Markteinführung im Jahre 2000 eine Vielzahl von Garantiefällen wegen defekter Anzeigen häuften.

Grundsätzlich scheinen OLED basierte Displays aus momentaner Sicht die größten Chancen zu besitzen, als erste Gattung organischer Bauelemente am breiten Markt vertreten zu sein, wurden hier in den vergangenen 15 Jahren doch die größten Fortschritte, beispielsweise bei der

Lumineszenz, erzielt [4]. Hindernisse scheinen aus heutiger Sicht hauptsächlich in der Kapselfung und Langzeithaltbarkeit der Bauelemente zu liegen. Der relativ einfache Aufbau durch eine mehrlagige Abscheidung von Elektrodenmaterialien und p- bzw. n-Halbleiterschichten auch ohne Via-Kontaktierungen durch einzelne Ebenen hindurch scheint im Vergleich zu OFETs und organischen Solarzellen auch in der industriellen Fertigung gut beherrschbar zu sein. Großflächig bereits gut zu kontrollierende Herstellungs- und Abscheideverfahren werden zunächst großformatige flexible Leuchtdiodenelemente für den Wohnbereich oder Fahrzeugbau hervorbringen. Wenig später werden Industrievertretern zufolge RGB-Displays in schnell wachsender Bildschirmdiagonale folgen. Im Gegensatz zu monochromen Leuchtdiodenelementen werden die Displays zunächst nicht in flexiblen Ausführungen gefertigt werden können. Eine Ansteuerelektronik aus organischen Transistoren ist dafür eine zwingende Voraussetzung.

Die Entwicklung einer Steuerelektronik für organische Displays erfordert einen komplexen Schaltungsaufbau, sowie eine Prozessführung und ein Schaltungsdesign in mehreren Ebenen. Die bisher in der Mikroelektronik verwendeten Verfahren wie Fotolithografie und Ätzverfahren [52] lassen sich nicht ohne weiteres auf die Prozesse der für organischen Bauelemente angestrebten 'Rolle zu Rolle' Technologie übertragen. Neben den Herausforderungen in der Herstellung, ist bisher noch wenig über den Schaltungsaufbau und die Alterung der Schaltungen bekannt.

Für einen zuverlässigen Schaltungsbetrieb sind Designregeln, wie in der Silizium-Halbleitertechnik, unausweichlich, jedoch noch völlig unbekannt. Durch den andauernden elektrischen Betrieb der Schaltungen verursachte chemische Reaktionen zwischen Isolatoren, Halbleitern und polymeren Leitern sind nicht auszuschließen und bisher noch unerforscht. Daher ist anzunehmen, dass sich zunächst einfache Schaltkreise mit wenigen Elementen und Prozessebenen, wie in RFID-Etiketten [58] am Markt etablieren können. Großformatige Display-Ansteuerungen auf flexiblen Substraten werden vermutlich erst in einem zeitlichen Abstand folgen.

Aus heutiger Sicht wird als wahrscheinlich letztes organisches Bauelement die organische Solarzelle die Märkte erobern. Eine vielschichtige Problematik in der Herstellung ist die Ursache dafür. Neben ungelösten Alterungserscheinungen, gerade in Verbindung mit dem für die Photovoltaik notwendigen Tageslicht [59] spielt sicherlich der im Vergleich zur Silizium-Photovoltaik noch viel zu geringe Wirkungsgrad eine große Rolle. Hauptgrund hierfür ist unter anderem der ungeklärte Aufbau der aktiven Schicht. Zum Ende der neunziger Jahre wurden so genannte 'Double-Cable'-Moleküle [8][60] als erstrebenswertes Ziel für einen effizienten Ladungsabtransport mit großen Anstrengungen erforscht. Nur wenige Jahre später wurde jedoch wieder davon abgerückt. Die hohen Rekombinationsraten der Elektronen-Loch-Paare in diesen Molekülen wurden zunächst unterschätzt. Im heutigen Interesse ist nun eine effiziente Ladungsträgergeneration. Solange diese grundlegenden Erkenntnisse über den Aufbau der aktiven Schicht fehlen, rücken mögliche Herausforderungen in der Herstellung von organischen Solarzellen in weite Ferne.

Im Allgemeinen und unabhängig von der Art des Bauelements kann den organischen Bauelementen sicherlich eine bedeutende Rolle in der zukünftigen Mikroelektronik zugesprochen werden. Schon heute findet in weiten Bereichen der Chemie ein gezieltes Molekül-Design für vorher definierte charakteristische Eigenschaften statt. Sind Grundlagen der elektronischen Eigenschaften organischer Halbleitermoleküle erst einmal weitgehend verstanden, so eröffnen sich heute noch unüberschaubare Möglichkeiten, Moleküle mit definierten Bandlücken oder Ladungsträgerbeweglichkeiten gezielt zu synthetisieren. Die angestrebte Unabhängigkeit vom anorganischen Si-

liziumkristall und die Verwendung flexibler Substrate erschließen der Mikroelektronik gleich zwei neue Freiheitsgrade zur Realisierung heute noch ungeahnter elektronischer Systeme.

# Kapitel 3

## Schichtherstellung und Transistoraufbau

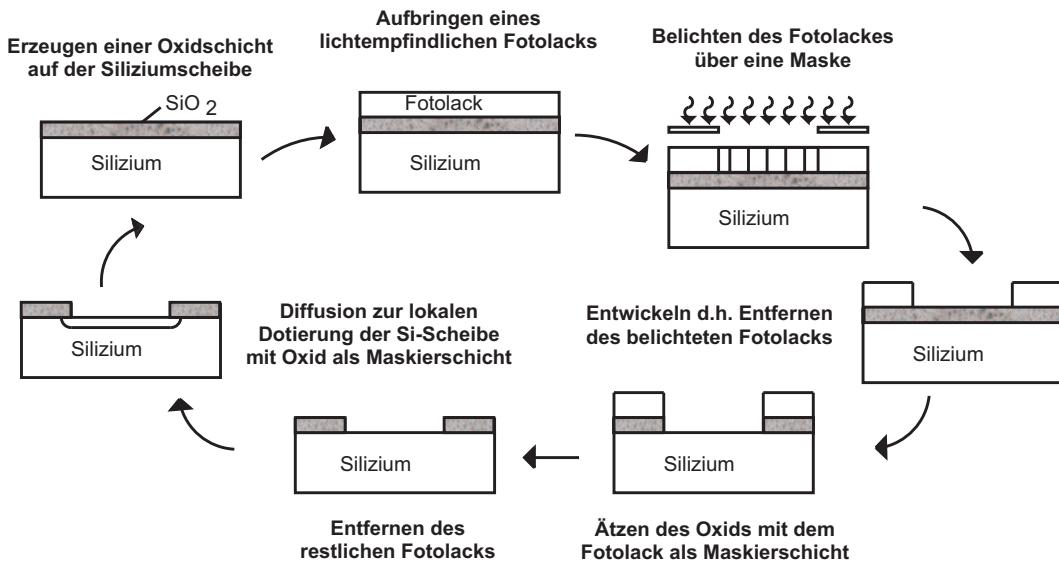

Die Präparation der in dieser Arbeit vorgestellten OFETs erfolgt durch eine an die Silizium-Halbleitertechnologie angelehnte Prozessierung mittels Fotolithografie und Planartechnologie. Die einzelnen Prozessschritte der Planartechnik werden im allgemeinen ganzflächig auf den gesamten Wafer angewendet. Grundsätzlich lassen sie sich in Abscheideverfahren, Fotolithografie, Ätzverfahren und Reinigungsverfahren einteilen (Details in [52], siehe Abbildung 3.1)). In der MOS-Transistorfertigung wird zu den genannten Techniken noch die Ionenimplantation genutzt, die jedoch in der organischen Halbleitertechnologie keine Anwendung findet.

Die Anwendung der Prozessschritte zur Erzeugung von mikrosystemtechnischen Strukturen erfolgt meist in gleicher Reihenfolge: Zunächst wird durch eine Depositionstechnik die zu strukturierende Schicht erzeugt. Im Anschluss wird durch Belacken mit einem bezüglich UV-Licht empfindlichen Lack die spätere Maskierungsschicht aufgebracht, welche nachfolgend mit einer speziellen Chrom-Fotomaske und UV-Licht belichtet wird. Es folgt ein Entwicklungsschritt, der die Strukturen der Fotomaske im Lack freilegt. Die in einem Ofen gehärtete Lackmaske dient so beim abschließenden Ätzen zur Maskierung der zu schützenden Bereiche. Frei liegende Flächen werden abgetragen und die anfangs abgeschiedene Schicht so strukturiert.

Ein entscheidender Vorteil der Planartechnik ist, dass sich bei einer großen Homogenität der angewendeten Prozessschritte über die Wafer-Oberfläche eine Vielzahl identischer Chips mit hoher Reproduzierbarkeit und geringer Strukturgröße fertigen lassen. Ein Nachteil der Verwendung der Fotolithografie ist, dass zur Erzeugung z.B. der Transistoren nur die bereits auf der Fotomaske vorhandenen Strukturen genutzt werden können. Die Fotolithografie ist daher relativ unflexibel, bezüglich kurzfristiger Design-Änderung von Bauelementen und deren Schaltungen.

Bei der Literaturrecherche zu Beginn dieser Arbeit wird deutlich, dass die Präparation von OFETs dort mehrheitlich im Maßstab mehrerer Mikrometer Kanallänge erfolgt. Oftmals werden die Kontakte statt durch Fotolithografie auch durch thermisches Verdampfen des Kontaktmetalls über eine Schattenmaske definiert. Diese Vorgehensweise resultiert üblicherweise in einer geringen Strukturtreue und großen Transistorabmessungen. Reproduzierbar im Mikrometermaßstab hergestellte OFETs sind zu Beginn der Experimente wenig verbreitet. Ein Ziel dieser Arbeit ist es daher, mit Hilfe der Planartechnologie und Fotolithografie hoch reproduzierbare Schaltelemente bei geringer Strukturgröße auch bei OFETs zu etablieren.

Transistorabmessungen im Mikrometermaßstab erfordern jedoch auch einen erheblichen Auf-

**Abbildung 3.1:** Die Planartechnologie findet in der mikrosystemtechnischen Fertigung von Transistoren eine weite Verbreitung. Abscheideverfahren, Fotolithografie und Ätztechniken werden ganzflächig auf den Wafer angewendet und solange wiederholt, bis alle Strukturen erzeugt worden sind (Nach [52])

wand, in Bezug auf die Sauberkeit während der Präparation. Da die produzierten Strukturgrößen in der gleichen Größenordnung der Staubpartikel in der Umgebungsluft liegen, können diese schon zu Kurzschlüssen, Maskenschäden oder Abschattungen bei der Fotolithografie führen. Die Fertigung der zu vermessenden OFETs erfolgt daher grundsätzlich in einem Reinraum der Klasse 1000. Die Klassifizierung entspricht einer Partikeldichte von weniger als 1000 Partikeln kleiner als  $5 \mu\text{m}$  in einem Volumen von einem Kubikfuß [61]. Zum Vergleich: In einem Kubikfuß ungefilterter Raumluft befinden sich mehr als 1 Mio solcher Partikel. Besonders partikelkritische Prozessschritte, wie beispielsweise die Fotolithografie, werden zusätzlich unter Luftfilternden Flow-Boxen durchgeführt.

Jedoch können Partikel nicht nur durch die Raumluft oder den Menschen über Hautkontakt oder Atemluft auf die Wafer-Oberfläche gelangen. Auch durch einige Prozessschritte, z.B. bei der Oxidabscheidung im PECVD-Prozess (siehe Kapitel 3.2) oder durch Ölnebel aus Pumpensystemen in Vakuumanlagen, gelangen Verunreinigungen auf das Substrat. Daher ist es unerlässlich, dass zumindest zu Beginn der Präparation (um definierte Anfangsbedingungen zu erhalten) und nach partikelträchtigen Arbeitsschritten eine Reinigung der Wafer erfolgt. Diese kann entweder durch Abblasen mit Pressluft oder besser, durch chemische Reinigung in einer Abfolge von Tensid-, Ultraschall- und Säurebehandlung durchgeführt werden. Zur nasschemischen Reinigung werden im Rahmen dieser Arbeit die Reinigungsverfahren 'Reinigung A' sowie 'Reinigung C' benutzt, welche in [62] und im Anhang dieser Arbeit ausführlich beschrieben sind.

### 3.1 Substrat

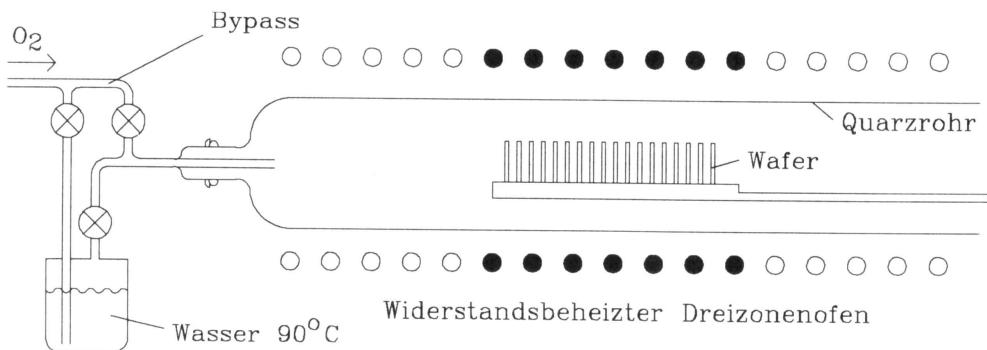

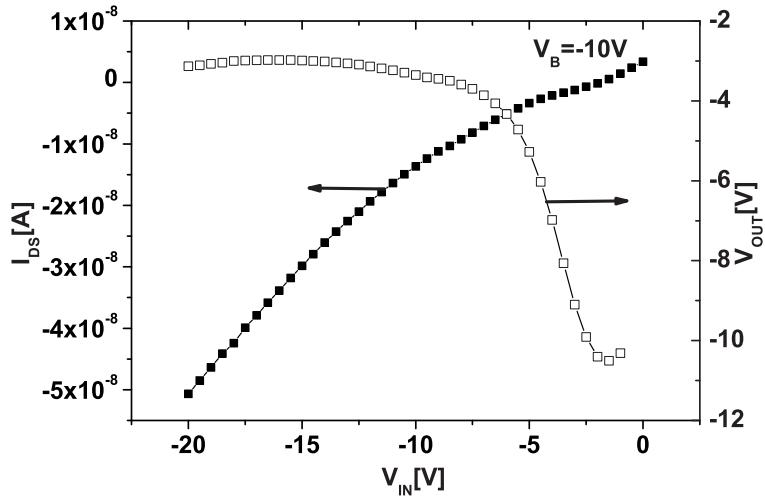

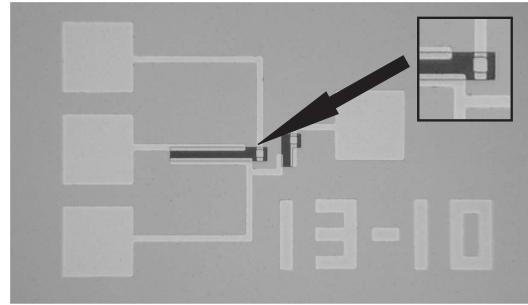

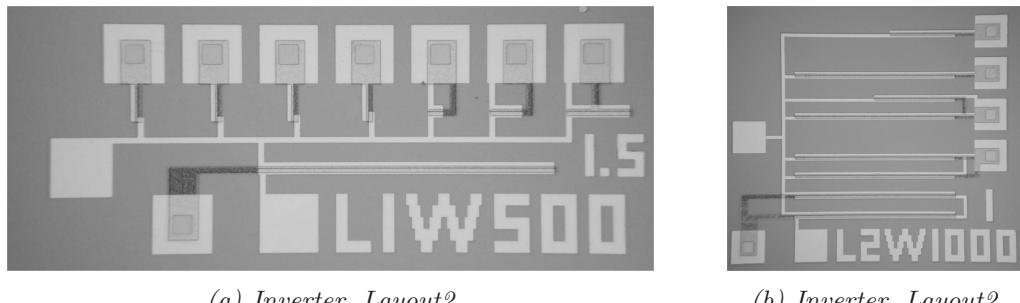

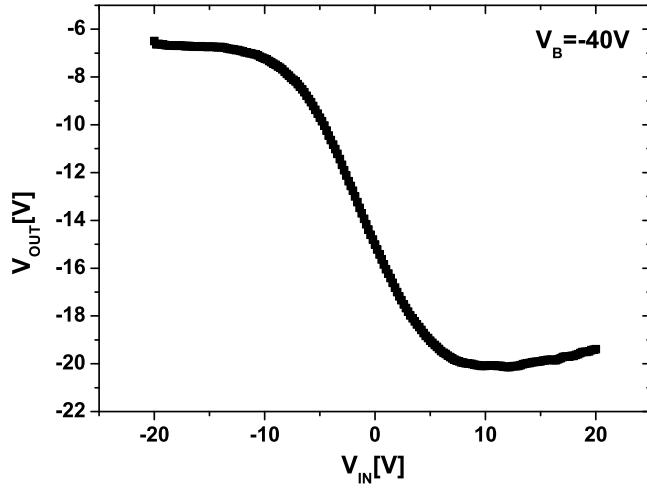

Während in aktuellen Forschungsberichten heute vermehrt über die Verwendung polymerer Substrate und Dielektrika berichtet wird [63] [64] [65], sind zu Beginn dieses Forschungsprojekts neue Erkenntnisse über das Wachstum der organischen Schicht auf anorganischen Isolatoren und die elektrischen Eigenschaften organischer Feldeffekt Transistoren (auch in Verbindung mit der Alterung des Halbleitermaterials) das Ziel der Experimente. Parallel zur Strukturierung auf Silizium-Wafern durchgeführte frühe Versuche mit polymeren Substraten zeigen die Schwierigkeiten der Prozessführung auf Kunststoffsubstraten auf. Die Verwendung der Kunststoffsubstrate liefert daher zunächst keine Erfolg versprechenden Ergebnisse. Vielfältige Unverträglichkeiten der Kunststoffsubstrate und Isolatoren mit Ätz- und Reinigungslösungen der Halbleitertechnologie lassen dabei die Wahl eines geeigneten Präparationsweges zur Herausforderung anwachsen. Der Wunsch einer hohen Reproduzierbarkeit der Ergebnisse und die als ein Schwerpunkt dieser Arbeit durchgeführten Alterungsuntersuchungen legen daher die Wahl von Silizium als Substratmaterial nahe. Gerade auch für die Separation von Alterungsmechanismen ist die Verwendung eines degradationsverminderten Substrats von entscheidender Bedeutung.