## Analyse und Entwurf von Methoden zur Ressourcenverwaltung partiell rekonfigurierbarer Architekturen

Zur Erlangung des akademischen Grades

#### **DOKTOR-INGENIEUR**

der Fakultät Elektrotechnik, Informatik und Mathematik

der Universität Paderborn

genehmigte Dissertation

von

M.Sc. Dipl.-Ing. Markus Köster aus Detmold

Referent: Prof. Dr.-Ing. Ulrich Rückert

Korreferent: Prof. Dr. techn. Marco Platzner

Tag der mündlichen Prüfung: 6. Juni 2007

Paderborn, den 11. Juni 2007

D 14-231

## Danksagung

Die vorliegende Arbeit wurde während meiner Tätigkeit als Stipendiat des Graduiertenkollegs "Automatische Konfiguration in offenen Systemen" der Deutschen Forschungsgemeinschaft (DFG) an der Universität Paderborn unter der Anleitung von Prof. Dr. Ulrich Rückert angefertigt. Für das von der DFG gewährte Stipendium möchte ich mich besonders bedanken.

Ich möchte mich herzlich bei all jenen Personen bedanken, die mich auf unterschiedliche Art und Weise unterstützt und zu dieser Arbeit beigetragen haben. Besonderem Dank gilt Prof. Ulrich Rückert dafür, dass er diese Arbeit ermöglicht hat und mich in seine Arbeitsgruppe aufgenommen hat. Seine konstruktive Kritik hat mir beim Abschluss dieser Arbeit sehr geholfen. Ein großer Dank gilt Dr. Mario Porrmann für die stete Hilfsbereitschaft und die zahlreichen fachlichen Diskussionen, die zu dieser Arbeit beigetragen haben. Ebenso möchte ich mich bei ihm für das sorgfältige Korrekturlesen der vorliegenden Arbeit bedanken.

Ein besonderer Dank geht an Dr. Heiko Kalte für die außergewöhnlich gute und intensive Zusammenarbeit und für die Unterstützung als Koautor in einigen der im Rahmen dieser Promotion entstanden Veröffentlichungen. Ich möchte mich außerdem bei Prof. Marco Platzner für die Übernahme des Koreferats bedanken. Mein Dank gilt ebenso Prof. Adolf Grauel, der mich dazu ermutigt hat, den Schritt der Promotion zu wagen.

Allen Mitgliedern des Fachgebietes Schaltungstechnik danke ich für das angenehme und gemeinschaftliche Arbeitsklima. Hier geht ein besonderer Dank an meinen Bürokollegen Ralf Eickhoff für viele interessante Diskussionen auch außerhalb des Themas der rekonfigurierbaren Hardware.

Besonders danke ich Alexandra Jacob für ihre Geduld, ihre liebevolle Unterstützung und das abschließende Korrekturlesen dieser Arbeit. Zuletzt möchte ich mich für den Rückhalt und die Unterstützung aus meiner Familie bedanken.

# Inhaltsverzeichnis

| 1 | Einl | eitung                     |                                    | 1  |  |  |  |

|---|------|----------------------------|------------------------------------|----|--|--|--|

|   | 1.1  | Zielset                    | zung der Arbeit                    | 3  |  |  |  |

|   | 1.2  | Aufbai                     | u der Arbeit                       | ۷  |  |  |  |

| 2 | Rek  | Rekonfigurierbare Hardware |                                    |    |  |  |  |

|   | 2.1  | Archite                    | ekturkonzepte                      | 8  |  |  |  |

|   |      | 2.1.1                      | Granularitätsebenen                | 8  |  |  |  |

|   |      | 2.1.2                      | Systemanbindung                    | 9  |  |  |  |

|   |      | 2.1.3                      | Konfigurationsansätze              | 11 |  |  |  |

|   | 2.2  | Partiel                    | l rekonfigurierbare Architekturen  | 12 |  |  |  |

|   |      | 2.2.1                      | Zweidimensionale Systemansätze     | 13 |  |  |  |

|   |      | 2.2.2                      | Eindimensionale Systemansätze      | 14 |  |  |  |

|   |      | 2.2.3                      | Systemansatz mit fester Aufteilung | 16 |  |  |  |

| 3 | Mod  | dellieru                   | ng                                 | 19 |  |  |  |

| _ | 3.1  |                            | Modell                             | 20 |  |  |  |

|   |      | 3.1.1                      | Zustände einer Modulinstanz        | 24 |  |  |  |

|   |      | 3.1.2                      | Platzierung eines Moduls           | 26 |  |  |  |

|   |      | 3.1.3                      | Vergleichbare Modelle              | 28 |  |  |  |

|   | 3.2  |                            | fplanung                           | 30 |  |  |  |

|   |      | 3.2.1                      | Platzierungsablauf                 | 31 |  |  |  |

|   |      | 3.2.2                      | Konfigurationsablauf               | 33 |  |  |  |

|   | 3.3  | Analys                     | severfahren                        | 37 |  |  |  |

|   |      | 3.3.1                      | Simulationsumgebung SARA           | 39 |  |  |  |

|   |      | 3.3.2                      | Zeitenmodell                       | 45 |  |  |  |

|   | 3.4  | Zusam                      | menfassung                         | 49 |  |  |  |

| 4 | Hon  | nogene                     | Architekturen                      | 51 |  |  |  |

| - | 4.1  | _                          | rungsverfahren                     | 52 |  |  |  |

|   |      | 4.1.1                      | Verwaltung freier Zellen           | 53 |  |  |  |

|   |      | 4.1.2                      | Positionsbestimmung                | 58 |  |  |  |

|   |      | 4.1.3                      |                                    | 61 |  |  |  |

|   | 4.2  |                            | ative Analyse                      | 63 |  |  |  |

|   |      |                            | Metriken                           | 67 |  |  |  |

ii Inhaltsverzeichnis

|                     |                             | 4.2.2 Vergleich der Systemansätze                 | 70  |  |  |  |  |  |

|---------------------|-----------------------------|---------------------------------------------------|-----|--|--|--|--|--|

|                     |                             | 4.2.3 Einfluss der Platzierungszeit               | 80  |  |  |  |  |  |

|                     |                             | 4.2.4 Einfluss der Konfigurationszeit             | 88  |  |  |  |  |  |

|                     | 4.3                         | Defragmentierung                                  | 92  |  |  |  |  |  |

|                     |                             | 4.3.1 Partielle Kompaktierung                     | 94  |  |  |  |  |  |

|                     |                             | 4.3.2 Simulative Analyse                          | 99  |  |  |  |  |  |

|                     | 4.4                         | Zusammenfassung                                   | 101 |  |  |  |  |  |

| 5                   | Heterogene Architekturen 10 |                                                   |     |  |  |  |  |  |

|                     | 5.1                         | Platzierungsverfahren                             | 106 |  |  |  |  |  |

|                     |                             | 5.1.1 Anpassung bestehender Platzierungsverfahren | 107 |  |  |  |  |  |

|                     |                             | 5.1.2 SUP-Fit                                     | 109 |  |  |  |  |  |

|                     |                             | 5.1.3 RUP-Fit                                     | 117 |  |  |  |  |  |

|                     |                             | 5.1.4 Vereinfachungen im 1D-Systemansatz          | 121 |  |  |  |  |  |

|                     | 5.2                         | Simulative Analyse                                | 122 |  |  |  |  |  |

|                     |                             | 5.2.1 2D-Systemansatz                             | 125 |  |  |  |  |  |

|                     |                             | 5.2.2 1D-Systemansatz                             | 128 |  |  |  |  |  |

|                     | 5.3                         | Defragmentierung                                  | 132 |  |  |  |  |  |

|                     |                             | 5.3.1 Partielle Verdrängung                       | 133 |  |  |  |  |  |

|                     |                             | 5.3.2 Simulative Analyse                          | 135 |  |  |  |  |  |

|                     | 5.4                         | Zusammenfassung                                   | 139 |  |  |  |  |  |

| 6                   | Zusa                        | nmenfassung und Ausblick                          | 141 |  |  |  |  |  |

| Lit                 | teratı                      | verzeichnis                                       | 145 |  |  |  |  |  |

| Αŀ                  | bildı                       | gsverzeichnis                                     | 158 |  |  |  |  |  |

| Tabellenverzeichnis |                             |                                                   |     |  |  |  |  |  |

| GI                  | ossar                       |                                                   | 163 |  |  |  |  |  |

## 1 Einleitung

Die Anforderungen an die Leistungsfähigkeit, den Flächenbedarf und die Energieeffizienz von mikroelektronischen Systemen sind in den letzten Jahren kontinuierlich gestiegen. Insbesondere mobile eingebettete Systeme, wie z. B. Mobiltelefone,

müssen derart gestaltet sein, dass sie platzsparend, leistungsfähig, energieeffizient

und flexibel sind. Zusätzlich verkürzen sich die Lebenszyklen mikroelektronischer

Produkte, so dass die zur Verfügung stehenden Entwicklungszeiten (engl.: Time-toMarket) abnehmen müssen. Ein Ansatz, diesen Anforderungen gerecht zu werden,

verspricht die Verwendung von rekonfigurierbarer Hardware.

In der Regel besteht rekonfigurierbare Hardware aus einem Feld von konfigurierbaren Verarbeitungseinheiten, die über eine programmierbare Kommunikationsinfrastruktur miteinander verbunden sind. Die Verarbeitungseinheiten beinhalten meist elementare Funktionen (z. B. logische oder arithmetische Operationen). Durch das Zusammenschalten der Verarbeitungseinheiten über die gegebene Kommunikationsinfrastruktur lassen sich einfache Schaltungen bis hin zu komplexen Systemen auf einem Chip (engl.: System-On-Chip) realisieren. Das Konzept der rekonfigurierbaren Hardware hat neue Perspektiven beim Entwurf mikroelektronischer Systeme eröffnet. Der Durchbruch der rekonfigurierbaren Hardware kam mit der Entwicklung des FPGAs (engl.: Field-Programmable Gate Array).

Im Jahr 1985 wurde von der Firma Xilinx das erste FPGA (XC2064) mit 64 konfigurierbaren Logikzellen und 1200 Gatteräquivalenten eingeführt [85]. Die Konfiguration der Logikzellen des XC2064 wurde ermöglicht durch das Programmieren eines SRAM-basierten Konfigurationsspeichers. Der Inhalt des Konfigurationsspeichers legt die Funktionen der Logikzellen und deren Verbindungen fest. Eine *partielle Rekonfiguration*, d. h., die Veränderungen der Funktionen einzelner Logikzellen zur Laufzeit war mit dem XC2064 nicht möglich. Erst etwa 10 Jahre später - im Jahr 1996 - wurden die ersten partiell rekonfigurierbaren FPGAs eingeführt (Xilinx XC6200 Serie [86]), welche aus bis zu 16384 Logikzellen und bis zu 100000 Gatteräquivalenten bestanden. Durch partielle Rekonfiguration können auf dem FPGA konfigurierte Systemkomponenten dynamisch angepasst oder komplett durch andere Systemkomponenten ausgetauscht werden. Auf diese Weise lassen sich Recheneinheiten realisieren, die in der Funktion variabel und zur Laufzeit anpassbar sind.

Seit der Einführung von partiell rekonfigurierbaren FPGAs sind weitere 10 Jahre vergangen. Die heutigen Xilinx Virtex-5 FPGAs [96] besitzen bis zu 330000 Logikzellen und darüber hinaus zusätzliche Zellen, wie z. B. verteilte Speicherblöcke. Mit der Integration von verschiedenen Zelltypen weichen die heutigen FPGAs von ihrer

2 1 Einleitung

einst homogenen Struktur ab und weisen eine heterogene Fläche von konfigurierbaren Zellen auf. Die Anzahl von Gatteräquivalenten ist von 1200 beim XC2064 auf über 7 Millionen beim Virtex-5 LX330T angestiegen.

FPGAs sind bis heute die am weitesten verbreiteten rekonfigurierbaren Architekturen. Die Marktzuwächse im Bereich der rekonfigurierbaren Hardware sind enorm. Die Firma Xilinx hat im Jahr 2006 einen Umsatz von 1,73 Mrd.US\$ erzielt und konnte den Umsatz im Vergleich zum Vorjahr um 10,2% steigern. Das vielversprechende Konzept der partiellen Rekonfigurierbarkeit wurde bis jetzt jedoch nur vereinzelt genutzt, was unter anderem auf folgende Gründe zurückzuführen ist:

Fehlender automatisierter Entwurfsablauf: Wenn ein Universalprozessor mit einer rekonfigurierbaren Funktionseinheit gekoppelt wird, können Berechnungen einer Anwendung entweder auf dem Prozessor oder in Form von rekonfigurierbarer Hardware ausgeführt werden. Software-basierte Anwendungen sind meist in einer hohen Programmiersprache, wie z. B. ANSI-C oder Java, spezifiziert. Um eine solche Anwendung mit Hilfe von dynamisch rekonfigurierbarer Hardware zu beschleunigen, können Teile der Anwendung als dynamisch rekonfigurierbare Systemkomponenten realisiert werden. Die automatische Erzeugung von Systemkomponenten in einer synthetisierbaren Hardware-Beschreibungssprache aus einer Programmspezifikation in Form einer Hochsprache wie ANSI-C ist jedoch nur eingeschränkt möglich (vgl. [60]) und verlangt meistens zusätzliches Expertenwissen im Bereich des Hardware-Entwurfs. Ein einfacher Entwurfsablauf für Anwendungen zur Ausführung auf partiell rekonfigurierbarer Hardware ist damit nicht gegeben.

Fehlende Systemansätze zur Realisierung: Um den Datenaustausch zwischen Universalprozessor und einer rekonfigurierbaren Funktionseinheit zu ermöglichen, wird ein Systemansatz mit einer flexiblen Kommunikationsinfrastruktur benötigt. Bei der Platzierung von dynamisch rekonfigurierbaren Systemkomponenten muss eine Anbindung an die Kommunikationsinfrastruktur des vorhandenen Systems geschaffen werden. Dabei werden Mechanismen benötigt, die eine partielle Rekonfiguration erlauben, ohne die Funktionsweise anderer platzierter Systemkomponenten und der Kommunikationsinfrastruktur zur Laufzeit zu beeinträchtigen.

Fehlende Methoden zur Ressourcenverwaltung: Die dynamisch platzierbaren Systemkomponenten sind unterschiedlich komplex und variieren daher in der Anzahl der benötigten Ressourcen. Um die zur Verfügung stehenden Ressourcen der rekonfigurierbaren Architektur möglichst effizient zu nutzen, werden Methoden zur Ressourcenverwaltung benötigt. Die Methoden umfassen einerseits die Verwaltung der freien und belegten Ressourcen und andererseits die Platzierung der von der Anwendung geforderten Systemkomponenten. In Abhängigkeit des zugrunde liegenden Systemansatzes und der gegebe-

nen Kommunikationsinfrastruktur ergeben sich dabei Einschränkungen in der Menge der möglichen Positionen bei der Platzierung einer Systemkomponente.

Diese Arbeit widmet sich dem Thema der Ressourcenverwaltung von partiell rekonfigurierbaren Architekturen. Im Speziellen wird dabei auf die Platzierung von System-komponenten zur Laufzeit eingegangen. Die Ziele dieser Arbeit werden im Einzelnen im folgenden Abschnitt dargestellt.

## 1.1 Zielsetzung der Arbeit

Ein wesentliches Ziel dieser Arbeit ist die Analyse von Systemansätzen zur Umsetzung partiell rekonfigurierbarer Hardware. Der Schwerpunkt der Analyse liegt dabei auf dem Vergleich der Leistungsfähigkeit der verschiedenen Systemansätze im Hinblick auf die Platzierung von Hardware-Modulen zur Laufzeit. Im Einzelnen ergeben sich dabei folgende Fragen:

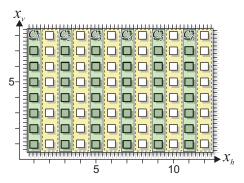

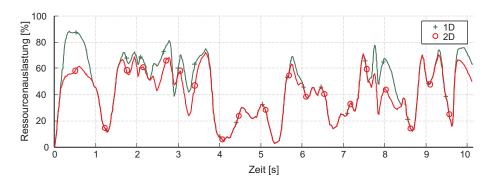

- Welcher Systemansatz führt zur größten Ressourcenauslastung der gegebenen rekonfigurierbaren Architektur?

- Die Bestimmung der Position eines Hardware-Moduls erfordert eine Rechenzeit, die von dem gewählten Platzierungsverfahren abhängt. Welchen Einfluss hat das Platzierungsverfahren und die benötigte Rechenzeit auf die Leistungsfähigkeit eines Systemansatzes?

- Nachdem die Position eines geforderten Hardware-Moduls bestimmt wurde, folgt die partielle Rekonfiguration der Architektur anhand der Konfigurationsdaten des Hardware-Moduls. Welchen Einfluss hat die für den Konfigurationsprozess erforderliche Konfigurationszeit auf die Leistungsfähigkeit eines Systemansatzes?

- Lässt sich die Leistungsfähigkeit eines Systemansatzes durch Defragmentierung verbessern?

Da heutige FPGAs aus Zellen verschiedenen Typs (Speicherblöcke, Signalverarbeitungszellen) bestehen, ergeben sich bei der Platzierung von dynamisch rekonfigurierbaren Systemkomponenten Einschränkungen bezüglich der möglichen Positionen der entsprechenden Hardware-Module. Auf diese Weise entsteht eine Heterogenität, die in den Platzierungsverfahren berücksichtigt werden muss. Ein wichtiges Ziel dieser Arbeit ist die Analyse, ob die im Zusammenhang mit homogenen rekonfigurierbaren Architekturen bekannten Platzierungsverfahren auch für heterogene Architekturen adaptiert werden können. Im Rahmen der Analyse heterogener rekonfigurierbarer Architekturen ergeben sich dabei folgende Fragen:

4 1 Einleitung

• Wie wirkt sich die Heterogenität heutiger partiell rekonfigurierbarer Architekturen auf die Platzierungsverfahren aus?

- Welche Eigenschaften muss ein Systemansatz für heterogene rekonfigurierbare Architekturen aufweisen, um eine hohe Ressourcenauslastung zu erzielen?

- Lässt sich die Leistungsfähigkeit eines Systemansatzes für heterogene rekonfigurierbare Architekturen durch Defragmentierung verbessern?

Neben der Beantwortung der oben aufgeführten Fragen werden neue Methoden zur Ressourcenverwaltung im Hinblick auf heterogene Architekturen vorgestellt, die dazu beitragen sollen, das Konzept der partiellen Rekonfigurierbarkeit auf einfache Weise nutzbar zu machen. Ein wichtiger Beitrag dieser Arbeit ist die Entwicklung eines neuen Platzierungsansatzes, welcher die im Zusammenhang mit heterogenen rekonfigurierbaren Architekturen vorhandene eingeschränkte Anzahl der möglichen Positionen von Hardware-Modulen berücksichtigt. Im folgenden Abschnitt wird der Aufbau der Arbeit skizziert.

#### 1.2 Aufbau der Arbeit

Kapitel 2 behandelt die Grundlagen der rekonfigurierbaren Hardware. Dabei wird auf die verschiedenen Architekturkonzepte von rekonfigurierbarer Hardware eingegangen, die sich in unterschiedliche Granularitätsebenen klassifizieren lassen. Ferner werden die verschiedenen Varianten der Systemanbindung, ebenso wie die unterschiedlichen Konfigurationsansätze beschrieben. Die Merkmale von partiell rekonfigurierbaren Architekturen, sowie mögliche Anwendungsszenarien werden herausgestellt. Im Zusammenhang mit partiell rekonfigurierbarer Hardware ergeben sich verschiedene Systemansätze, die im Einzelnen kurz vorgestellt werden.

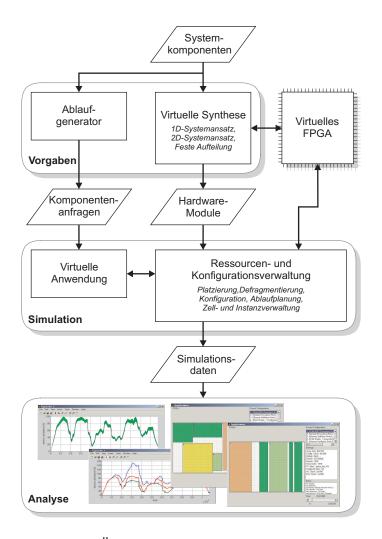

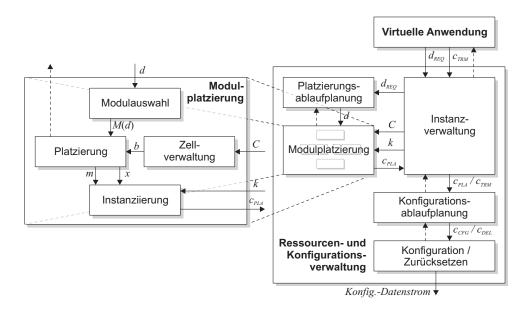

Kapitel 3 stellt die Modellierung vor, die die Grundlage der in dieser Arbeit beschriebenen Methoden bildet. Mithilfe des in dieser Arbeit entwickelten DMC-Modells lassen sich Methoden zur partiellen Rekonfigurierbarkeit wie die Platzierung oder die Ablaufplanung formal beschreiben. Um die im weiteren Verlauf der Arbeit betrachteten Systemansätze und die entsprechenden Platzierungsverfahren zu analysieren, wurde die Simulationsumgebung SARA entwickelt, welche auf dem DMC-Modell beruht. Die Bestandteile und die verschiedenen Parameter von SARA werden im Einzelnen erläutert.

Kapitel 4 beschäftigt sich mit der Platzierung von Hardware-Modulen in homogenen rekonfigurierbaren Architekturen. Die Platzierung von Hardware-Modulen zur Laufzeit weist eine Ähnlichkeit zum Online-Packungsproblem auf, so dass die Gemeinsamkeiten und Unterschiede charakterisiert werden. Die Platzierung eines Hardware-Moduls lässt sich dabei in die *Verwaltung der freien Zellen* und in die *Positionsbestimmung* unterteilen. Es werden verschiedene Verfahren zur Verwaltung der freien

5

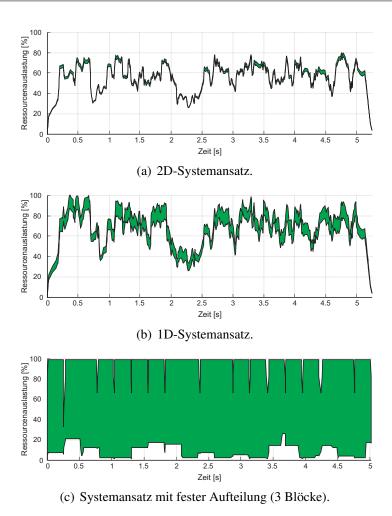

Zellen vorgestellt. Ebenso wird auf die im Zusammenhang mit Online-Packungsproblemen bekannten Verfahren zur Positionsbestimmung eingegangen und die für rekonfigurierbare Hardware erforderlichen Anpassungen beschrieben. Um die verschiedenen Systemansätze und Platzierungsverfahren simulativ zu vergleichen, werden Metriken für dynamisch rekonfigurierbare Hardware eingeführt. Anhand von Simulationen und den beschriebenen Metriken werden die verschiedenen Systemansätze miteinander verglichen. Ferner wird der Einfluss der Platzierungszeit und der Konfigurationszeit der Hardware-Module analysiert. Des Weiteren werden verschiedene bekannte und neu entwickelte Defragmentierungsverfahren vorgestellt. Anhand von Simulationen wird gezeigt, inwieweit die Defragmentierung die Leistungsfähigkeit eines Systemansatzes im Hinblick auf die resultierende Ressourcenauslastung verbessern kann.

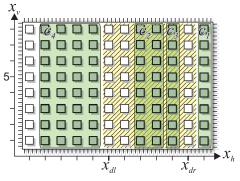

Kapitel 5 setzt sich mit der Platzierung von Hardware-Modulen in heterogenen rekonfigurierbaren Architekturen auseinander und ist ähnlich strukturiert wie das vorherige Kapitel. Dabei wird zunächst auf die Problematik der Platzierung von Hardware-Modulen in heterogenen Architekturen eingegangen. Die Unterschiede und die erforderlichen Anpassungen der von homogenen Architekturen bekannten Platzierungsverfahren werden dargestellt. Ein wichtiger Bestandteil dieses Kapitels ist die Einführung eines neuen Platzierungsansatzes für heterogene rekonfigurierbare Architekturen. Darauf aufbauend werden die Platzierungsverfahren SUP-Fit und RUP-Fit vorgestellt. Neben der Einführung neuer Platzierungsverfahren wird ein für heterogene rekonfigurierbare Architekturen geeignetes Defragmentierungsverfahren vorgestellt. Anhand von Simulationen wird anschließend der Einfluss der Defragmentierung auf die Leistungsfähigkeit eines Systemansatzes untersucht.

Im Kapitel 6 werden die wesentlichen Ergebnisse der vorliegenden Arbeit zusammengefasst und abschließend bewertet. Zusätzlich wird ein Ausblick auf mögliche Erweiterungen der in dieser Arbeit besprochenen Methoden zur Ressourcenverwaltung gegeben.

6 1 Einleitung

## 2 Rekonfigurierbare Hardware

Die Ausführung einer Anwendung oder eines Algorithmus kann im herkömmlichen Sinn auf grundsätzlich zwei verschiedene Arten umgesetzt werden. Eine Möglichkeit ist die Anwendung in Form von Hardware, z. B. als anwendungsspezifische Schaltung (ASIC), zu realisieren. Aufgrund des speziell für die Anwendung ausgelegten Hardware-Entwurfs erlauben ASICs eine schnelle und effiziente Verarbeitung der Anwendungsdaten. Jedoch kann die Schaltung nach der Fertigung nur begrenzt angepasst werden, so dass im Fall einer notwendigen Anpassung die Herstellung eines neuen ASICs unumgänglich ist. Ebenso sind die Kosten eines ASICs insbesondere bei geringer Stückzahl sehr hoch. Die zweite Art und Weise der Umsetzung einer Anwendung ist die Implementierung in Software. Hierbei wird die Anwendung als Programm realisiert, das aus einzelnen Instruktionen besteht, die sequenziell auf einem zugrunde liegenden Prozessor ausgeführt werden. Im Vergleich zur Hardware-Realisierung benötigt die Software-Realisierung durch die sequenzielle Ausführung der Instruktionen insgesamt eine längere Ausführungszeit der Anwendung. Die Verwendung von Software gestattet jedoch die Anpassung der Anwendung auch nach der Fertigung, so dass im direkten Vergleich zur statischen Hardware-Realisierung eine höhere Flexibilität geschaffen wird.

Rekonfigurierbare Hardware ist eine weitere Alternative zur hardware- und software-basierten Realisierung einer Anwendung. In der Literatur werden für den Begriff Rekonfigurierbare Hardware auch die Synonyme Reconfigurable Computing oder Adaptive Computing verwendet. Rekonfigurierbare Architekturen, wie z. B. Feldprogrammierbare Gatter Anordnungen (FPGAs), bestehen aus einer regelmäßigen Anordnung konfigurierbarer Zellen, die mit einer ebenfalls konfigurierbaren Verbindungsstruktur miteinander verbunden sind. Anwendungen werden ähnlich wie im klassischen Hardware-Entwurf z. B. in Form von Hardware-Beschreibungssprachen wie VHDL [43] spezifiziert. Mithilfe von computergestützten Entwurfswerkzeugen (EDA) werden entsprechende Konfigurationsdaten synthetisiert, die die einzelnen Funktionen der Zellen und deren Verbindungen beinhalten. Die rekonfigurierbare Architektur wird zu Beginn durch einen Konfigurationsprozess mit den Konfigurationsdaten initialisiert. Auf diese Weise lassen sich Anwendungen in Form von digitalen Schaltungen auf rekonfigurierbare Architekturen abbilden. Bezüglich rekonfigurierbarer Hardware werden Anwendungen somit in Form von Konfigurationsdaten repräsentiert. Rekonfigurierbare Hardware bietet damit eine ähnliche Flexibilität wie Software, denn die konfigurierten Schaltungen können auch nach der Fertigung angepasst werden. Bei einer Realisierung mit rekonfigurierbarer Hardware kann durch Parallelisierung eine viel höhere Performanz erzielt werden als durch eine entsprechende Software-Realisierung. Beispiele von entsprechenden Anwendungen, die mit rekonfigurierbarer Hardware realisiert wurden, sind in [21, 32, 68, 74] aufgeführt.

In Abschnitt 2.1 werden die im Bereich der rekonfigurierbaren Hardware vorhandenen Architekturkonzepte beschrieben. Dabei ergeben sich unterschiedliche Granularitätsebenen, die sich grundsätzlich in grobgranulare und feingranulare Architekturen unterteilen lassen. Des Weiteren wird auf die unterschiedlichen Varianten der Systemanbindung von rekonfigurierbarer Hardware, ebenso wie auf die verschiedenen Konfigurationsansätze eingegangen. Abschnitt 2.2 behandelt die spezielle Klasse der partiell rekonfigurierbaren Architekturen. Im Hinblick auf das Konzept der partiellen dynamischen Rekonfiguration ergeben sich zweidimensionale und eindimensionale Systemansätze, sowie Systemansätze mit fester Aufteilung. Auf die Unterschiede der Ansätze wird im Einzelnen eingegangen.

## 2.1 Architekturkonzepte

Im Zusammenhang mit rekonfigurierbarer Hardware gibt es eine Vielzahl von verschiedenen Architekturkonzepten. Die wesentlichen Unterschiede ergeben sich in der Betrachtung der Granularitätsebene, der Systemanbindung und des Konfigurationsansatzes. In diesem Abschnitt wird auf die Unterschiede der einzelnen Architekturkonzepte eingegangen.

#### 2.1.1 Granularitätsebenen

Rekonfigurierbare Architekturen lassen sich grundsätzlich in *feingranulare* und *grobgranulare* rekonfigurierbare Architekturen unterscheiden. Feingranulare rekonfigurierbare Architekturen zeichnen sich durch eine große Anzahl an Zellen aus, die aus einfachen Logikblöcken mit einer geringen Anzahl an Ein- und Ausgängen bestehen. Um eine beliebige Verschaltung der einzelnen Zellen zu ermöglichen, sind in feingranularen rekonfigurierbaren Architekturen eine Vielzahl von unterschiedlichen Verbindungsressourcen vorhanden, die meist in horizontaler und vertikaler Richtung verlaufen. Die Zellen sind üblicherweise über eine Switch-Matrix mit der Verbindungsstruktur angeschlossen. Ein Beispiel einer feingranularen Architektur ist das FPGA. Typische Beispiele sind die Xilinx Virtex FPGAs [88] und Altera Stratix FPGAs [5], deren Zellen aus Look-Up-Tables (LUT) mit einem 4-bit-Eingang und einem 1-bit-Ausgang bestehen. Weitere Beispiele feingranularer Architekturen sind GARP [40] (4 × 2-bit-Eingang, 2-bit-Ausgang) und LP-PGA [33] (3-bit-Eingang, 1-bit-Ausgang).

Die Zellen grobgranularer rekonfigurierbarer Architekturen sind typischerweise viel größer als die Zellen feingranularer Architekturen und bestehen meist aus arithmetischen Logikeinheiten (ALUs) mit Wortbreiten von 8-bit oder größer. Im Ver-

gleich zu feingranularen rekonfigurierbaren Architekturen ist die Anzahl der Zellen wesentlich geringer. Ebenso ist die Kommunikationsinfrastruktur einer grobgranularen rekonfigurierbaren Architektur meist nicht so flexibel und weniger umfangreich. Die geringe Anzahl an Zellen und die entsprechend geringere Anzahl an rekonfigurierbaren Kommunikationsressourcen führt zu einer geringen Menge an Konfigurationsdaten, so dass der Konfigurationsprozess einer grobgranularen rekonfigurierbaren Architektur oft kürzer ist als der einer feingranularen. Beispiele grobgranularer rekonfigurierbarer Architekturen sind RaPiD [27], MATRIX [57], Piperench [35], DReAM [9], Totem [20], PACT-XPP [7] und IMEC ADRES [56].

Manche Architekturen lassen sich jedoch nicht eindeutig den fein- oder grobgranularen rekonfigurierbaren Architekturen zuordnen. Daher ist zusätzlich die Klasse der *mittel*- oder *mediumgranularen* rekonfigurierbaren Architekturen entstanden. Ein Beispiel einer mediumgranularen Architektur stellt die CHESS-Architektur [55] dar, deren Zellen aus 4-bit-ALUs bestehen, die über eine 4-bit-Busarchitektur miteinander verbunden sind.

Um die Ausführung bestimmter Anwendungen zu optimieren, sind in den heutigen rekonfigurierbaren Architekturen verschiedenartige Zellen mit unterschiedlichen Größen integriert, so dass eine heterogene Struktur entsteht. So bestehen etwa die Xilinx Virtex-II Pro FPGAs [93] nicht nur aus Logikzellen, sondern ebenfalls aus eingebetteten Prozessoren und Speicherblöcken. Im Vergleich zu den Logikzellen sind in Virtex-II FPGAs nur eine geringe Anzahl von Speicherblöcken vorhanden, die nicht gleichmäßig sondern in gesonderten Spalten angeordnet sind. Diese Form der heterogenen rekonfigurierbaren Architekturen lässt sich nicht mehr eindeutig einer der genannten Granularitätsebenen zuordnen, so dass heterogene Architekturen daher auch als *multigranulare* Architekturen bezeichnet werden können.

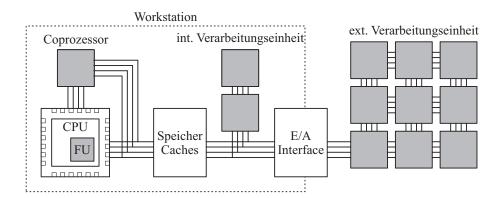

### 2.1.2 Systemanbindung

Ein System mit rekonfigurierbarer Hardware besteht typischerweise aus mindestens einem Prozessor, einem oder mehreren Blöcken mit rekonfigurierbarer Hardware und Speicherelementen. Wie von Compton und Hauck in [21] beschrieben, lassen sich Systeme mit rekonfigurierbarer Hardware anhand der verschiedenen Arten der Prozessorkopplung klassifizieren. Eine Übersicht der verschiedenen Arten der Prozessorkopplung ist in Abbildung 2.1 dargestellt.

Innerhalb des Systems kann rekonfigurierbare Hardware als eigenständige externe Verarbeitungseinheit angebunden sein. Die Kommunikation zwischen dem Prozessor und der rekonfigurierbaren Hardware erfolgt dabei über die Ein-/Ausgabe-Schnittstelle. Bei dieser Art der Prozessorkopplung wird von einer unregelmäßigen Kommunikation ausgegangen, bei der geringe Datenmengen ausgetauscht werden oder die rekonfigurierbare Hardware zeitintensive Berechnungen autonom durchführt, ohne dabei mit dem Prozessor zu kommunizieren.

Abbildung 2.1: Verschiedene Arten der Prozessorkopplung in Systemen mit rekonfigurierbarer Hardware [21].

Rekonfigurierbare Hardware kann auch als interne Verarbeitungseinheit angebunden sein, so dass die rekonfigurierbare Hardware wie in einem Multi-Prozessorsystem als zusätzlicher Prozessor betrachtet werden kann. Die Kommuni-kation zwischen Prozessor und rekonfigurierbarer Hardware erfolgt dabei über den internen Prozessorbus oder den internen Speicher. Beispiele einer solchen Kopplung sind PCI-PipeRench [51] und PAM [80].

Eine noch engere Kopplung ist dann gegeben, wenn die rekonfigurierbare Hardware in Form eines Koprozessors mit dem Prozessor verbunden ist. Der Prozessor und die rekonfigurierbare Hardware können auf diese Art direkt oder indirekt über Speicher miteinander kommunizieren. Die rekonfigurierbare Hardware führt dabei die Berechnung unabhängig vom Prozessor durch. Beispiele von Koprozessorkopplungen sind GARP [40], REMARC [58] und NAPA [62].

Die engste Kopplung wird erreicht, wenn ein Block mit rekonfigurierbarer Hardware in dem Prozessor eingebettet ist (engl.: Reconfigurable Function Unit (RFU)). In diesem Fall wird die rekonfigurierbare Hardware Teil des Prozessors und kann genutzt werden, um den Befehlssatz des Prozessors mit anwendungsspezifischen Instruktionen zu erweitern. Die Kommunikation zwischen Prozessor und rekonfigurierbarer Hardware geschieht direkt über die internen Register des Prozessors. Beispiele dieser Art von Prozessorarchitekturen sind OneChip [16], Chimaera [39], FIP [66] und DISC [84].

Eine ähnliche enge Kopplungsvariante ergibt sich, wenn der Prozessor in einer rekonfigurierbaren Architektur eingebettet ist (vgl. [75]). Der Prozessor kann dabei als *Hardmacro*<sup>1</sup> realisiert sein, wie z. B. der eingebettete IBM PowerPC 405 in Xilinx Virtex-II/Pro FPGAs [93] oder der ARM 922T in Altera Excalibur Bausteinen [3]. Der Prozessor kann ebenso als so genannter *Softcore-Prozessor* in Form von Konfigurationsdaten vorliegen. Zu Beginn wird die rekonfigurierbare Hardware mit den

<sup>&</sup>lt;sup>1</sup>In vielen Arbeiten wird anstelle des Begriffs *Hardmacro* der Begriff *Hardcore* verwendet, der in dieser Arbeit jedoch aus Gründen der Doppeldeutigkeit vermieden wird.

Konfigurationsdaten des Softcore-Prozessors initialisiert. Beispiele solcher Softcore-Prozessoren sind Xilinx Microblaze [94], Altera Nios II [4] und S-Core [50].

#### 2.1.3 Konfigurationsansätze

Die meisten der derzeit verwendeten rekonfigurierbaren Architekturen besitzen einen SRAM-basierten Konfigurationsspeicher, der auf unterschiedliche Weise aufgebaut ist und adressiert werden kann. Daher ergeben sich verschiedene Konfigurationsansätze, die sich wie in [21] dargestellt in Single-Kontext-Architekturen, Multi-Kontext-Architekturen und partiell rekonfigurierbare Architekturen klassifizieren lassen.

Single-Kontext-Architekturen sind seriell rekonfigurierbare Architekturen, die sich nur komplett rekonfigurieren lassen. Beim Konfigurationsprozess müssen immer alle Speicherstellen des Konfigurationsspeichers beschrieben werden. D. h., die Konfigurationsdaten beinhalten die Konfigurationsbits aller rekonfigurierbaren Ressourcen (Zellfunktionen und Verbindungen) der Architektur und stellen somit einen *Kontext* der Architektur dar. Single-Kontext-Architekturen besitzen eine einfache Konfigurationsschnittstelle, da die Reihenfolge der Konfigurationsbits in den Konfigurationsdaten gegeben ist und keine Adressinformationen verarbeitet werden müssen. Während des Konfigurationsprozesses kann die Architektur nicht aktiv genutzt werden. Auch bei geringen Unterschieden zwischen der neuen und der aktuellen Konfiguration wird immer ein kompletter Konfigurationsprozess benötigt, so dass Single-Kontext-Architekturen nur eingeschränkt für Systeme mit dynamischer Rekonfiguration zur Laufzeit geeignet sind. Beispiele von Single-Kontext-Architekturen sind Altera Stratix FPGAs [5].

Ebenso wie Single-Kontext-Architekturen sind Multi-Kontext-Architekturen seriell rekonfigurierbar und erlauben ebenfalls nur eine komplette Rekonfiguration. Jedoch können im Gegensatz zu den Single-Kontext-Architekturen mehrere Kontexte parallel gespeichert werden, zwischen denen beliebig umgeschaltet werden kann. Der Umschaltvorgang ist vergleichbar mit dem Umschalten eines Multiplexers, so dass innerhalb von wenigen Nanosekunden ein anderer Kontext aktiviert werden kann. Ein wesentlicher Vorteil dieses Ansatzes ist das Konfigurieren von neuen Kontexten, während ein anderer Kontext aktiv ist. Dadurch wird die Ausführung des aktiven Kontextes nicht durch einen Konfigurationsprozess unterbrochen. Multi-Kontext-Architekturen sind damit für Systeme mit dynamischer Rekonfiguration zur Laufzeit geeignet. Die Verteilung der Hardware-Module in den einzelnen Kontexten stellt jedoch ein Partitionierungsproblem dar, bei dem sichergestellt werden muss, dass Hardware-Module, die zur gleichen Zeit benötigt werden, auch in den gleichen Kontexten vorhanden sind. Beispiele von Multi-Kontext-Architekturen sind DPGA [24], CSRC FPGA [63] und Time-Multiplexed FPGA [77].

Während bei Single- und Multi-Kontext-Architekturen immer die komplette Rekonfiguration eines Kontextes erforderlich ist, erlauben partiell rekonfigurierbare Architekturen die Rekonfiguration eines Teils der Architektur, ohne dabei die aktiven Berechnungen des restlichen Teils zu beeinflussen. Die in den folgenden Kapiteln beschriebenen Methoden und Konzepte beziehen sich ausschließlich auf partiell rekonfigurierbare Architekturen, so dass im folgenden Abschnitt detailliert auf das Prinzip der partiellen Rekonfigurierbarkeit eingegangen wird.

## 2.2 Partiell rekonfigurierbare Architekturen

Partiell rekonfigurierbare Architekturen erlauben die gezielte Rekonfiguration eines Teils der Architektur, während der verbleibende Teil seine bisherige Funktion unverändert weiter ausführt. Auf diese Weise lassen sich bei Bedarf Systemkomponenten in Form von Hardware-Modulen zur Laufzeit auf der Architektur platzieren und wieder entfernen. Der Konfigurationsspeicher von partiell rekonfigurierbaren Architekturen ist mit einem konventionellen SRAM-Speicher vergleichbar. Die Konfigurationsdaten eines Hardware-Moduls beinhalten die Konfigurationsbits und die entsprechenden Adressen der benötigten rekonfigurierbaren Ressourcen (Zellfunktionen und Verbindungen). Die Adressen spiegeln somit die Positionen der einzelnen Ressourcen wider. Der Konfigurationsprozess eines Hardware-Moduls entspricht dem sequenziellen Schreiben der Konfigurationsdaten in dem Konfigurationsspeicher. Durch Adressverschiebungen kann das Hardware-Modul an unterschiedlichen Positionen platziert werden. Das gezielte Rekonfigurieren einzelner Bereiche der rekonfigurierbaren Architektur reduziert die Konfigurationsdatenmenge und ebenso die benötigte Konfigurationszeit erheblich.

Das Konzept der partiellen Rekonfigurierbarkeit wird - wie in [65] dargestellt - in Anwendungen in den Bereichen Software-Defined-Radio und Videodatenverarbeitung eingesetzt. Darüber hinaus gibt es bis jetzt jedoch nur wenige Anwendungen, die das Konzept der partiellen Rekonfigurierbarkeit nutzen, was im Wesentlichen auf den Mangel an Entwurfswerkzeugen zurückzuführen ist. Erste Methoden zur Unterstützung partieller Rekonfigurierbarkeit sind in den heutigen EDA-Werkzeugen integriert. Dennoch fehlt es an einem ganzheitlichen Systemansatz, der die einfache Nutzung partieller Rekonfigurierbarkeit ermöglicht.

Die uneingeschränkte Platzierung von Hardware-Modulen beliebiger Form bietet die größte Flexibilität hinsichtlich der Belegung der zur Verfügung stehenden Hardware-Ressourcen. Jedoch verursacht eine solch hohe Flexibilität ebenso eine hohe Komplexität in der Verwaltung der freien und belegten Ressourcen zur Laufzeit. Mit zunehmenden Einschränkungen in der Form und den Platzierungsmöglichkeiten der gegebenen Hardware-Module sinkt die Komplexität der Ressourcenverwaltung. Mit der Komplexität sinkt jedoch ebenso die Flexibilität des Systemansatzes. Bezüglich der Eigenschaft der partiellen Rekonfigurierbarkeit ergeben sich somit die folgenden Fragen:

• Wie flexibel muss ein Systemansatz im Hinblick auf partielle Rekonfigurierbarkeit sein?

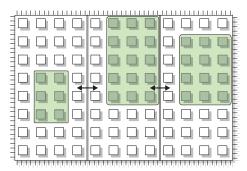

Abbildung 2.2: 2D-Systemansatz für partiell rekonfigurierbare Architekturen.

Welchen Einfluss haben die Verfahren zur Verwaltung der freien und belegten Ressourcen auf die Leistungsfähigkeit eines Systemansatzes?

Der unterschiedliche Grad an Flexibilität wird in den folgenden Abschnitten anhand von drei Systemansätzen verdeutlicht. Die dargestellten Systemansätze spiegeln zu gleich die grundsätzlichen Möglichkeiten der Umsetzung eines Systems mit partiell rekonfigurierbarer Hardware wider.

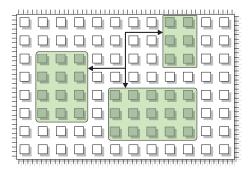

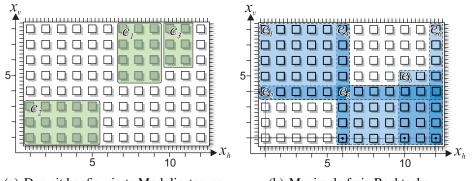

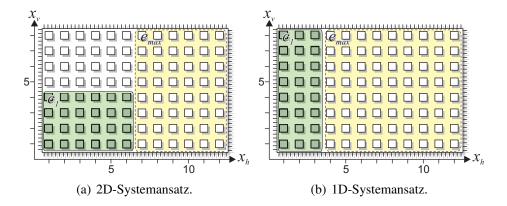

#### 2.2.1 Zweidimensionale Systemansätze

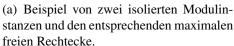

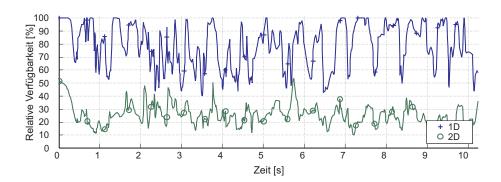

Im zweidimensionalen Systemansatz haben die zur Laufzeit platzierten Hardware-Module eine rechteckige Form und können beliebig auf der rekonfigurierbaren Architektur platziert werden. Abbildung 2.2 zeigt das Prinzip des 2D-Systemansatzes. Derzeit gibt es nur wenige Architekturen, die sich zweidimensional partiell rekonfigurieren lassen. Beispiel einer solchen Architektur ist das Xilinx XC6200 FPGA [86]. Der in Bazargan et al. [8] und Diessel et al. [25] dargestellte 2D-Systemansatz basiert auf dem Ansatz von Brebner [13], bei dem von einem System mit einem Prozessor und damit verbundener partiell rekonfigurierbarer Hardware ausgegangen wird. Das System verwendet ein Betriebssystem, dessen Tasks zur Laufzeit entweder als Hardware-Modul in rekonfigurierbarer Hardware oder als Software-Prozess des Prozessors implementiert werden kann. In dem Ansatz wird davon ausgegangen, dass keine Kommunikation zwischen den Tasks stattfindet. Wenn ein Hardware-Modul aus Mangel an freien Ressourcen nicht platziert werden kann, wird anstelle des Hardware-Moduls ein entsprechender Software-Prozess gestartet. In Steiger et al. [72] wird der gleiche Ansatz verwendet, wobei sich innerhalb der rekonfigurierbaren Hardware zusätzlich ein statischer Bereich befindet, der für Betriebssystemdienste reserviert ist.

Es ergeben sich grundsätzlich zwei Möglichkeiten, um eine Kommunikation zwischen den platzierten Hardware-Modulen zu ermöglichen. Die erste Möglichkeit ist die Realisierung einer statischen Kommunikationsinfrastruktur. Bestimmte Routingressourcen werden daher reserviert und von den Hardware-Modulen ausschließlich

Abbildung 2.3: 1D-Systemansatz für partiell rekonfigurierbare Architekturen.

zur Kommunikation untereinander genutzt. Ein solcher Ansatz wird in Sedcole et al. [65] für Xilinx Virtex FPGAs vorgestellt. Jedoch lassen sich Hardware-Module bei diesem Ansatz nur an den Positionen platzieren, die eine Verbindung mit der Kommunikationsinfrastruktur ermöglichen. Die Flexibilität der Platzierung wird daher eingeschränkt. Die zweite Möglichkeit der Realisierung einer Kommunikation zwischen den Hardware-Modulen ist die Anpassung der Routingressourcen zur Laufzeit mit dem Ziel, die derzeit platzierten Hardware-Module miteinander zu verbinden. Hübner et al. haben in [41] einen Ansatz für Xilinx Virtex FPGAs vorgestellt, welcher die Hardware-Module über rekonfigurierbare vertikale Routingkanäle mit einer statischen horizontalen Kommunikationsinfrastruktur verbindet. Die Hardware-Module können vertikal beliebig entlang des Routingkanals verschoben werden. Um die Verbindung eines Hardware-Moduls mit dem Routingkanal zur Laufzeit herzustellen, muss der Routingkanal entsprechend rekonfiguriert werden. Im Gegensatz zu einer statischen Kommunikationsinfrastruktur wird daher ein zusätzlicher Konfigurationsaufwand benötigt. Jedoch bietet die Verwendung rekonfigurierbarer Routingkanäle eine größere Flexibilität in der Modulplatzierung.

Im 2D-Systemansatz gibt es im Allgemeinen keine Einschränkungen bezüglich der Seitenverhältnisse der Hardware-Module. Wenn jedoch die Höhe der Hardware-Module konstant gehalten wird, so dass die Module entsprechend ihrer Komplexität nur in der Breite variieren, dann ergibt sich der *1D-Systemansatz*, der als Sonderfall des 2D-Systemansatzes betrachtet werden kann und im folgenden Abschnitt näher erläutert wird.

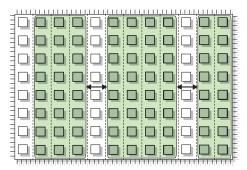

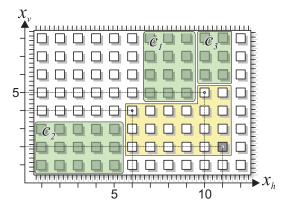

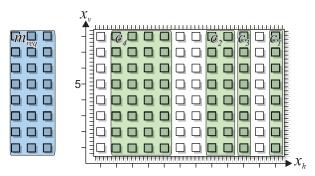

### 2.2.2 Eindimensionale Systemansätze

Viele der heutigen verfügbaren rekonfigurierbaren Architekturen lassen sich eindimensional partiell rekonfigurieren. Beispiele solcher Architekturen sind GARP [40], Chimaera [39], PipeRench [35, 64] und Xilinx Virtex FPGAs [89, 92, 93]. Aufgrund der spaltenweisen partiellen Rekonfigurierbarkeit ergibt sich der 1D-Systemansatz, welcher in Abbildung 2.3 dargestellt ist.

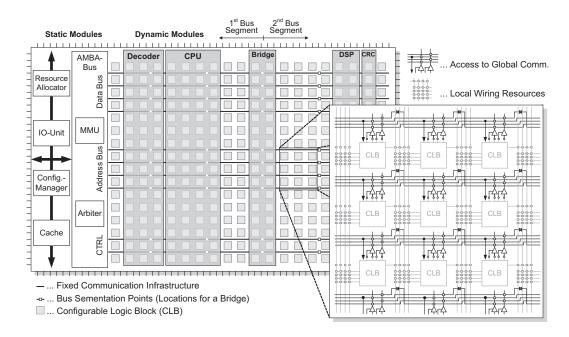

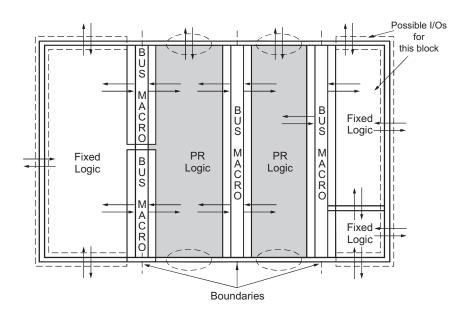

Abbildung 2.4: 1D-Systemansatz für Xilinx Virtex FPGAs [E1].

Eine der ersten Arbeiten, die sich mit dem 1D-Systemansatz für partiell rekonfigurierbare Hardware beschäftigt, ist Brebner et al. [15]. In dem beschriebenen 1D-Systemansatz haben alle Hardware-Module eine konstante Höhe und können lediglich in horizontaler Richtung platziert werden. Die Hardware-Module variieren in der Breite in Abhängigkeit ihrer Komplexität. Die Fläche innerhalb eines Hardware-Moduls wird vertikal in die Bereiche Betriebssystemschaltung, Modulkommunikationsschaltung und Anwendungsschaltung unterteilt. Die Betriebssystemschaltung beinhaltet Systemfunktionen wie die Verwaltung der Hardware-Module. Der Austausch von Daten zwischen den Hardware-Modulen geschieht durch die Modulkommunikationsschaltung. Die Anwendungsschaltung stellt den größten Teil des Hardware-Moduls dar und repräsentiert die eigentliche Anwendung des Hardware-Moduls.

Kalte et al. [E1] haben einen ähnlichen 1D-Systemansatz vorgestellt, der für Xilinx Virtex-FPGAs ausgelegt ist. Abbildung 2.4 zeigt einen Überblick des Ansatzes. Die rekonfigurierbare Architektur wird in einen statischen Teil (Static Modules) und einen dynamischen Teil (Dynamic Modules) partitioniert. Der statische Teil umfasst die Verwaltung der Konfigurationsdaten und der freien Ressourcen. Ebenso wird im statischen Teil die Kommunikation zwischen den Hardware-Modulen und den externen Komponenten organisiert. Hardware-Module können zur Laufzeit entlang der statischen horizontalen Kommunikationsinfrastruktur platziert werden und über einen Systembus miteinander kommunizieren. Bei der Konfiguration eines Hardware-Module kann die Position durch Manipulation der Konfigurationsdaten anhand des in [44] beschriebenen REPLICA-Filters beeinflusst werden. Die Hardware-Module sind der-

Abbildung 2.5: Systemansatz mit fester Aufteilung für partiell rekonfigurierbare Architekturen.

art synthetisiert, dass die zur Realisierung des Systembusses verwendeten Routingressourcen nicht anderweitig genutzt werden.

Im 1D-Systemansatz gibt es keine Einschränkungen bezüglich der Breite eines Hardware-Moduls. Wenn neben der Höhe auch die Breite der Hardware-Module konstant gehalten wird, so dass jedes Hardware-Modul die gleiche Fläche besitzt, dann ergibt sich der *Systemansatz mit fester Aufteilung*, der somit als Sonderfall des 1D-Systemansatzes betrachtet werden kann und im folgenden Abschnitt detailliert beschrieben wird.

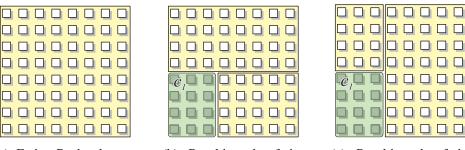

### 2.2.3 Systemansatz mit fester Aufteilung

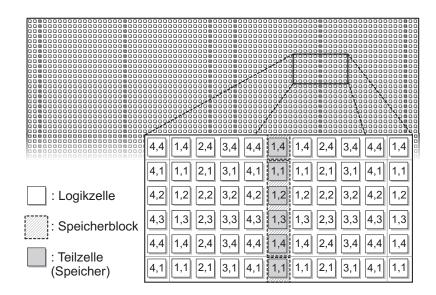

Im Systemansatz mit fester Aufteilung wird die rekonfigurierbare Architektur in eine feste Anzahl von Blöcken gleicher Größe unterteilt. Die Blöcke sind mit einer statischen Kommunikationsinfrastruktur miteinander verbunden. Zur Laufzeit werden Hardware-Module in entsprechende freie Blöcke platziert. Innerhalb eines Blocks sind die Schnittstellen zur Kommunikationsinfrastruktur an einer festen Position. Die Hardware-Module sind derart synthetisiert, dass sie sich mit der Kommunikationsinfrastruktur verbinden. Daher kann immer nur ein Hardware-Modul in einem Block konfiguriert werden. Einer der ersten Systemansätze mit fester Aufteilung wird von Brebner in [13, 14] beschrieben. Brebner stellt dabei die *Swappable Logic Unit* (SLU) als eine elementare rekonfigurierbare Einheit vor, die eine feste Größe und Position auf der rekonfigurierbaren Architektur besitzt. Eine Anwendung kann dabei nicht nur aus einer, sondern auch aus mehreren SLUs aufgebaut sein. Die SLU kann somit als rekonfigurierbarer Block betrachtet werden.

Ein Systemansatz mit fester Aufteilung für Xilinx Virtex FPGAs wird in [91] vorgestellt. Abbildung 2.6 zeigt eine Übersicht des Ansatzes mit zwei partiell rekonfigurierbaren Blöcken. Das FPGA wird dabei in statische Flächen (Fixed Logic) und dynamische Flächen (PR Logic), die die partiell rekonfigurierbaren Blöcke darstel-

Abbildung 2.6: Systemansatz mit fester Aufteilung für Xilinx Virtex FPGAs [91].

len, unterteilt. Zur Kommunikation werden so genannte *Bus Macros* verwendet, die die Kommunikation zwischen benachbarten Blöcken ermöglicht.

Ein erweitertes System mit 4 partiell rekonfigurierbaren Blöcken wird in Ullman et al. [78] vorgestellt. Das System ist für Xilinx Virtex-II FPGAs ausgelegt und beinhaltet neben den 4 Blöcken den Softcore-Prozessor Microblaze. Die partiell rekonfigurierbaren Blöcke sind über einen Systembus mit dem Prozessor verbunden. Das System dient der Umsetzung elektronischer Funktionen im Automobilbereich und markiert damit zugleich ein konkretes Anwendungsbeispiel für partiell rekonfigurierbare Hardware.

Weitere Beispiele für Systemansätze mit fester Aufteilung sind SCORE [17], Caronte [31] und Erlangen Slot Machine [10].

## 3 Modellierung

Mit der steigenden Komplexität und Heterogenität heutiger partiell rekonfigurierbarer Architekturen bedarf es einem allgemein verwendbaren Modell, welches den Vergleich der verschiedenen Architekturen und deren Methoden zur Umsetzung partieller Rekonfiguration ermöglicht. Bestehende Modellierungsansätze (wie z. B. [8, 11, 49]) sind meist architekturspezifisch oder widmen sich speziellen Problemen der Rekonfigurierbarkeit. Die in diesem Kapitel vorgestellte Modellierung und deren grundlegende Mechanismen zur Platzierung und Ablaufplanung eignen sich für Architekturen beliebiger Granularitätsebenen und ermöglichen die Analyse der Architektur und deren Mechanismen zur Realisierung partieller Rekonfiguration auf hoher Abstraktionsebene. Die in diesem Kapitel beschriebenen Modelle und Verfahren gelten für die im Kapitel 4 erläuterten homogenen rekonfigurierbaren Architekturen ebenso wie für die im Kapitel 5 beschriebenen heterogenen rekonfigurierbaren Architekturen.

Grundlage der in dieser Arbeit definierten Methoden bildet das im Abschnitt 3.1 vorgestellte *DMC-Modell*<sup>1</sup>. Das Modell unterteilt die Platzierung eines Hardware-Moduls in die drei Abstraktionsebenen *Systemkomponente*, *Hardware-Modul* und *Modulinstanz*. Das DMC-Modell stellt den Zusammenhang der verschiedenen Abstraktionsebenen her und beschränkt sich auf die wesentlichen Größen, die für die Umsetzung partieller Rekonfigurierbarkeit zur Laufzeit erforderlich sind.

Mithilfe des DMC-Modells lassen sich Methoden zur partiellen Rekonfiguration, wie die Platzierung oder die Ablaufplanung, formal beschreiben. Im Abschnitt 3.2 werden verschiedene Verfahren zur Ablaufplanung diskutiert. Die Ablaufplanung wird dabei auf der Ebene der Platzierung und der Ebene des Konfigurationsprozesses betrachtet. Im Gegensatz zur Platzierung, bei der unterschiedliche Verfahren für homogene und heterogene Architekturen existieren, ist die Ablaufplanung - wie im Abschnitt 3.2 beschrieben - architekturunabhängig.

Eine analytische Bewertung von verschiedenen Architekturen und deren Methoden zur Umsetzung partieller Rekonfiguration ist wie im Folgenden dargelegt nur begrenzt möglich. Aus diesem Grund ist die im Abschnitt 3.3.1 vorgestellte Simulationsumgebung SARA (Simulationsumgebung zur Analyse Rekonfigurierbarer Architekturen) entwickelt worden, welche auf dem DMC-Modell basiert. Mithilfe von

<sup>&</sup>lt;sup>1</sup>Die Abkürzung *DMC* leitet sich aus den Bezeichnungen der Mengen der Abstraktionsebenen her (*Systemkomponenten D, Hardware-Module M* und *Modulinstanzen C*).

20 3 Modellierung

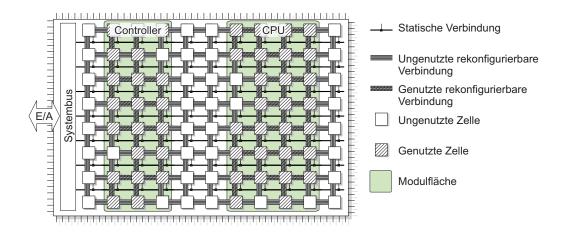

Abbildung 3.1: Schematische Darstellung einer rekonfigurierbaren Architektur mit statischen und rekonfigurierbaren Verbindungsressourcen.

SARA lassen sich verschiedene Systemansätze und entsprechende Platzierungsverfahren simulativ bewerten.

#### 3.1 DMC-Modell

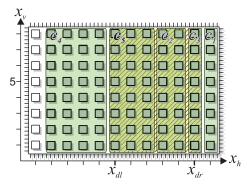

Das hier beschriebene Modell legt eine rekonfigurierbare Architektur (wie in Abbildung 3.1 dargestellt) zugrunde. Die Architektur besteht aus partiell rekonfigurierbaren Zellen, die in einem rechteckigen Feld angeordnet sind und über eine Verbindungsstruktur miteinander verbunden sind. Die Modellierung ermöglicht die Betrachtung feingranularer rekonfigurierbarer Architekturen, wie z. B. FPGAs, und grobgranularer rekonfigurierbarer Architekturen, wie z. B. RaPiD [27], PipeRench [35] oder PACT-XPP [7]. Im Folgenden werden jedoch lediglich feingranulare Architekturen betrachtet.

Die Architektur kann, wie in homogenen Architekturen üblich, aus Zellen eines Typs bestehen. Ein Beispiel für eine homogene Architektur ist ein FPGA, das lediglich aus konfigurierbaren Logikzellen besteht, wie das Xilinx XC6200 FPGA [86]. Ebenso lassen sich heterogene Architekturen mit verschiedenen Zelltypen betrachten. Ein Beispiel einer solchen heterogenen Architektur ist ein FPGA mit Logikzellen, Speicherblöcke (BlockRAM) und Zellen zur Signalverarbeitung, wie das Xilinx Virtex-4 FPGA [95]. Bezüglich der Modellierung gilt die Annahme, dass alle Zellen gleich groß sind, so dass die Architektur in Form einer Matrix repräsentiert werden kann.

Die Verbindungsressourcen der rekonfigurierbaren Architektur werden unterteilt in statische Verbindungsressourcen für die *systemweite Kommunikation* und rekonfigurierbare Verbindungsressourcen für die *modulinterne Kommunikation*. Die systemweite Verbindungsstruktur ermöglicht die Anbindung der zur Laufzeit partiell kon-

3.1 DMC-Modell 21

figurierten Hardware-Entwürfe an das System. Eine mögliche Form der systemweiten Kommunikation ist ein Systembus, wie in [47] beschrieben. Ein solcher Systembus ist ebenfalls in Abbildung 3.1 angedeutet. Eine Alternative ist die paketbasierte Kommunikation über ein Network-On-Chip, wie in [2, 54, 76] erläutert. Zur Laufzeit wird die für die modulinterne Kommunikation reservierte rekonfigurierbare Verbindungsstruktur anhand der Konfigurationsdaten des partiell zu rekonfigurierenden Hardware-Entwurfs angepasst. Abbildung 3.1 zeigt als Beispiel die konfigurierten Hardware-Entwürfe *Controller* und *CPU*.

Durch partielle Rekonfiguration ungenutzter Zellen und ungenutzter rekonfigurierbarer Verbindungsressourcen können Hardware-Entwürfe zur Laufzeit dem System hinzugefügt werden, indem die Konfigurationsdaten des Hardware-Entwurfs an die entsprechende Konfigurationsschnittstelle der Architektur gesendet werden. Bezüglich der Modellierung wird angenommen, dass der Konfigurationsvorgang sequenziell geschieht, d. h., es können nicht mehrere Hardware-Entwürfe zur gleichen Zeit konfiguriert werden.

Das im Folgenden vorgestellte DMC-Modell basiert auf der obigen spezifizierten rekonfigurierbaren Architektur und beschreibt die für die Platzierung relevanten Parameter auf den Ebenen Systemkomponente, Hardware-Modul und Modulinstanz. Abbildung 3.2 stellt den Zusammenhang der drei Abstraktionsebenen dar. Eine Systemkomponente  $d \in D$  ist als abstrakte Spezifikation eines Hardware-Entwurfs zu verstehen. Eine solche Spezifikation kann in Form einer Hardware-Beschreibungssprache wie z. B. VHDL oder in Form einer schematischen Darstellung vorliegen. D sei die Menge aller dem System bekannten Systemkomponenten. Beim Hardware-Entwurf auf statischen Architekturen wird aus einer solchen Systemkomponente mithilfe eines Synthesewerkzeugs eine Implementierung mit fest zugewiesenen Ressourcen und entsprechend fest zugewiesenen Verbindungen erzeugt. Im Zusammenhang mit partiell rekonfigurierbaren Architekturen ergibt sich ein weiterer Schritt zwischen der Beschreibung und der endgültigen Implementierung, denn im Gegensatz zum Entwurf auf statischen Architekturen ist die endgültige Position der Implementierung zum Zeitpunkt der Synthese unbekannt. Bei der Layoutsynthese auf rekonfigurierbaren Architekturen erzeugt das Platzieren und Verdrahten nicht eine absolute, sondern eine relative Zuordnung der gegebenen Zellen und deren Verbindungen, denn die endgültige Position der Implementierung wird erst zur Laufzeit bestimmt. Das Ergebnis der Layoutsynthese ist somit eine vorsynthetisierte Implementierung der Systemkomponente, welche im Folgenden als Hardware-Modul (kurz Modul) bezeichnet wird.

**Definition 3.1** (Hardware-Modul). Ein Hardware-Modul  $m = (d, r, a, q) \in M$  ist eine vorsynthetisierte Implementierung einer Systemkomponente  $d \in D$ , wobei  $r \in \mathbb{N}^{N_{cell}}$  die Anzahl der benötigten Ressourcen ist.  $N_{cell}$  gibt die Anzahl der verschiedenen Zelltypen an. Der Parameter  $a \in \mathbb{N}^{N_{sys}}$  beschreibt die benötigte Fläche des Moduls auf der Architektur. Die Dimension  $N_{sys}$  des Parameters a entspricht dabei der Dimension des zugrunde liegenden Systemansatzes. Der Vektor  $q \in \mathbb{R}^{N_{cost}}$  beinhaltet

22 3 Modellierung

Abbildung 3.2: Übersicht des DMC-Modells.

Implementierungskosten.  $N_{cost}$  gibt die Anzahl der verschiedenen Kostenparameter wieder. M beschreibt die Menge aller dem System bekannten Module.

Die Ressourcen  $r=(r_{CLB},r_{MEM},r_{MUL},\ldots)\in \mathbb{I}\!N^{N_{cell}}$  eines Hardware-Moduls m=(d,r,a,q) beinhalten lediglich die Anzahl der benötigten Zellen. Verbindungsstrukturen und I/O-Blöcke werden hier nicht als Ressourcen betrachtet. Die Implementierungskosten  $q\in \mathbb{I}\!R^{N_{cost}}$  eines Hardware-Moduls m=(d,r,a,q) können z. B. die Konfigurationszeit oder die Priorität des Moduls sein.

Wenn die übergeordnete Anwendung eine Systemkomponente, wie z. B. einen Controller, anfordert, dann ist die geometrische Form der resultierenden Implementierung und deren Position auf der rekonfigurierbaren Architektur für die Anwendung unbedeutend, solange jede Implementierung auf der gleichen Beschreibung aufbaut und eine einheitliche ortsunabhängige Kommunikationsinfrastruktur zugrunde liegt.

3.1 DMC-Modell 23

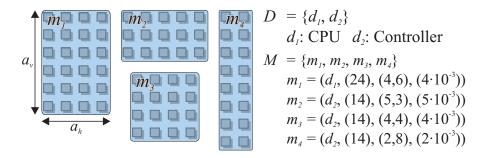

Abbildung 3.3: Beispiele verschiedener Hardware-Module.

**Beispiel 3.1.** Abbildung 3.3 zeigt Beispiele verschiedener Hardware-Module in einem 2D-Systemansatz. Jedes Modul  $m=(d,r,a,q)\in M$  basiert auf einer Systemkomponente  $d\in D$ , wobei die Menge der Systemkomponenten D aus einer CPU und einem Controller besteht. Der Ressourcenvektor  $r=(r_{CLB})$  beschreibt die Anzahl der benötigten Logikzellen. Im 2D-Systemansatz ist der Flächenbedarf  $a=(a_h,a_v)\in \mathbb{N}^2$ . Der Kostenparameter  $q=(t_{CFG})$  stellt die erforderliche Konfigurationszeit dar.

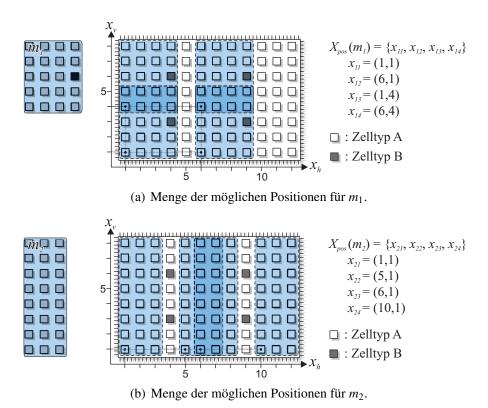

Die Erzeugung eines Hardware-Moduls geschieht durch einmalige statische Implementierung der Systemkomponente zur Entwurfszeit. Aus dieser Implementierung werden die für das Hardware-Modul benötigten Konfigurationsdaten extrahiert und gespeichert. In Bezug auf FPGAs existiert somit zu jedem Hardware-Modul ein entsprechender partieller Konfigurationsdatenstrom. Mögliche Positionen für die Platzierung eines Hardware-Moduls ergeben sich überall dort, wo die gleichen Anordnungen der verwendeten Ressourcen und der modulinternen Verbindungsstruktur auftreten. Erst zur Laufzeit wird die Position eines Hardware-Moduls bezüglich der rekonfigurierbaren Architektur festgelegt und die entsprechenden Ressourcen zugewiesen. Der Prozess des Bestimmens einer Position wird im Folgenden als *Platzierung* bezeichnet.

Wird das Hardware-Modul an eine geeignete Position platziert, muss das Modul an die systemweite Verbindungsstruktur angebunden werden. Die Anbindung an die systemweite Verbindungsstruktur erfolgt durch Zuweisung einer individuellen Adresse. Das platzierte und adressierbare Hardware-Modul steht dem System individuell zur Verfügung und wird als *Modulinstanz* bezeichnet. Die Bildung einer Modulinstanz aus einem Hardware-Modul ist vergleichbar mit der Bildung einer Komponenteninstanz aus einer VHDL-Komponente im Zusammenhang mit der Hardware-Beschreibungssprache VHDL [43].

**Definition 3.2** (Modulinstanz). Eine Modulinstanz  $c = (m, x, s, k) \in C$  beschreibt ein auf der Architektur abgebildetes Modul  $m \in M$ , wobei  $x \in X_{pos}(m)$  die Position der Instanz ist und  $X_{pos}(m)$  die Menge der möglichen Positionen für das Modul m. Die Position beschreibt den Zellabstand der unteren linken Ecke der Modulinstanz zur unteren linken Ecke der Architektur. Die Dimension der Menge

24 3 Modellierung

Abbildung 3.4: Zustände einer Modulinstanz und deren Transitionen.

$X_{pos}$  entspricht dabei der Dimension des Systemansatzes. Der Parameter  $s \in S$  beschreibt den aktuellen Zustand der Modulinstanz, wobei die Menge der Zustände  $S = \{PLA, CFG, EXE, TRM, DEL\}$  ist. Die Bedeutungen der Zustände und deren Transitionen werden im Abschnitt 3.1.1 näher erläutert. Der Vektor  $k \in \mathbb{N}^{N_{com}}$  beinhaltet Kommunikationsparameter, wie z. B. die Adresse, die der Instanz zugewiesen ist. C stellt die Menge der momentan platzierten Modulinstanzen dar.

Wenn die systemweite Kommunikationsinfrastruktur aus einem Systembus besteht, so beinhaltet der Kommunikationsparameter eine der Modulinstanz dynamisch zugewiesene individuelle Adresse. Die dynamische Adresszuweisung ermöglicht die Platzierung mehrerer Instanzen eines gleichen Hardware-Moduls. In [36] werden verschiedene Verfahren zur Realisierung einer dynamischen Adresszuweisung bezüglich dynamisch rekonfigurierbarer Systeme vorgestellt. Ein einfaches Verfahren ist z. B. die positionsbasierte Adresszuweisung, d. h., die Adresse der Modulinstanz hängt von deren Position ab.

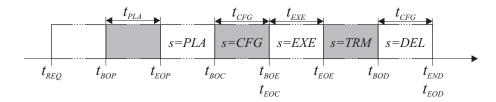

#### 3.1.1 Zustände einer Modulinstanz

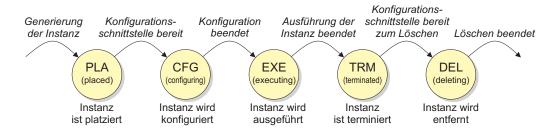

Von dem Zeitpunkt der Generierung bis zum Ende des Löschvorgangs durchläuft eine Modulinstanz mehrere Zustände. Gemäß Definition 3.2 sei die Zustandsmenge  $S = \{PLA, CFG, EXE, TRM, DEL\}$ . Abbildung 3.4 zeigt die einzelnen Zustände einer Modulinstanz und deren Transitionen.

Im Folgenden werden die Zustände im Einzelnen beschrieben, ausgehend von der Situation, dass die übergeordnete Anwendung eine bestimmte Systemkomponente  $d \in D$  anfordert. Infolgedessen ermittelt der Platzierungsalgorithmus ein passendes Modul  $m \in M(d)$  mit dazugehöriger Position  $x \in X_{pos}(m)$  und generiert eine entsprechende Modulinstanz c, die der Menge C hinzugefügt wird. Die einzelnen Schritte der Platzierung werden im späteren Abschnitt 3.1.2 näher erläutert. Nach der Generierung befindet sich die Modulinstanz c in dem Zustand PLA (engl.: Placed). Die für die Ausführung erforderlichen Zellen sind nun der Modulinstanz zugewiesen. Die Zellen sind jedoch noch nicht konfiguriert und die Instanz verbleibt solange im Zu-

3.1 DMC-Modell 25

Abbildung 3.5: Beispiele verschiedener Modulinstanzen.

stand *PLA*, bis die Konfigurationsschnittstelle des Systems für die Konfiguration der Zellen verfügbar ist.

Mit Beginn des Konfigurationsprozesses wechselt die Instanz in den Zustand *CFG* (engl.: Configuring) und verbleibt dort solange, bis alle Zellen konfiguriert sind. Nach Beendigung des Konfigurationsvorgangs wechselt die Modulinstanz in den Zustand *EXE* (engl.: Executing). Die Instanz ist nun aktiv und führt die geforderte Funktion aus. Nachdem die Ausführung der Modulinstanz beendet ist, wechselt die Instanz in den Zustand *TRM* (engl.: Terminated). Die der Instanz zugewiesenen Zellen werden nun nicht mehr benötigt und müssen durch Rekonfiguration in einen initialen Zustand zurückgesetzt werden. Das Zurücksetzen der Zellen ist erforderlich, um ein unvorhersehbares Fehlverhalten der Zellen und deren Verbindungsstruktur bei nachfolgenden Konfigurationsprozessen zu vermeiden. Ähnlich wie im Zustand *PLA* verbleibt die Instanz solange im Zustand *TRM*, bis die Konfigurationsschnittstelle des Systems für das Zurücksetzen der Zellen verfügbar ist. Mit Beginn des Zurücksetzens der Zellen, was im Folgenden auch als *Löschvorgang* bezeichnet wird, wechselt die Instanz in den Zustand *DEL* (engl.: Deleting). Nach Beendigung des Löschvorgangs wird die Instanz aus der Menge der platzierten Modulinstanzen *C* entfernt.

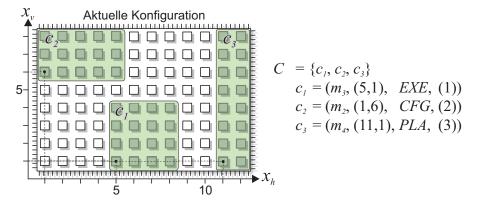

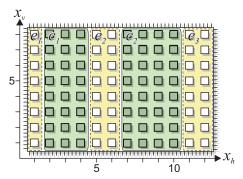

**Beispiel 3.2.** Abbildung 3.5 zeigt Beispiele verschiedener Modulinstanzen in einem 2D-Systemansatz. Jede Instanz  $c = (m, x, s, k) \in C$  basiert auf einem Hardware-Modul  $m \in M$ , wobei M der Menge der Module aus Beispiel 3.1 entspricht. Im 2D-Systemansatz ist die Position  $x = (x_h, x_v) \in X_{pos}(m)$ . Der Kommunikationsparameter k = (ADR) stellt die Adresse der Instanz dar. Während die Instanzen  $c_1$  im Zustand der Ausführung (s=EXE) ist, befindet sich die Instanz  $c_2$  im Zustand der Konfiguration (s=CFG). Die Instanz  $c_3$  ist bereits platziert (s=PLA) und wartet auf die Freigabe der Konfigurationsschnittstelle, die derzeit noch mit der Konfiguration von  $c_2$  beschäftigt ist.

Auf die hier beschriebene Weise durchläuft jede Modulinstanz die verschiedenen Zustände der Zustandsmenge S. Ausgangspunkt ist dabei immer die Generierung der

26 3 Modellierung

Modulinstanz, welche das Ergebnis der erfolgreichen Platzierung eines Moduls ist. Die einzelnen Schritte der Platzierung eines Moduls werden im nachfolgenden Abschnitt näher erläutert.

#### 3.1.2 Platzierung eines Moduls

Im Folgenden wird die Platzierung eines Moduls anhand des DMC-Modells erläutert. Wie im Abschnitt 2.2.1 beschrieben, stellen der Systemansatz mit fester Aufteilung und der 1D-Systemansatz eine Untermenge des 2D-Systemansatzes dar. Daher wird im Folgenden die Platzierung im allgemein gültigen 2D-Systemansatz angegeben. Im 2D-Systemansatz variieren die Flächenausdehnung eines Moduls und die Position einer Instanz in horizontaler und vertikaler Richtung. Die Fläche eines Moduls ist daher durch  $(a_h, a_v) \in \mathbb{N}^2$  definiert, wobei  $a_h$  die Flächenausdehnung in horizontaler Richtung und  $a_v$  die Flächenausdehnung in vertikaler Richtung angibt. In Analogie zur Fläche wird die Position einer Instanz durch  $(x_h, x_v) \in X_{pos}(m)$  beschrieben, wobei  $x_h$  die horizontale Position und  $x_v$  die vertikale Position darstellt.

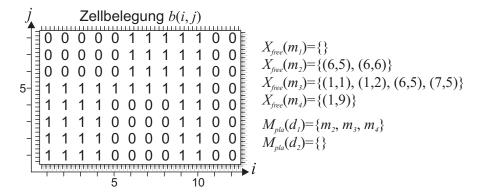

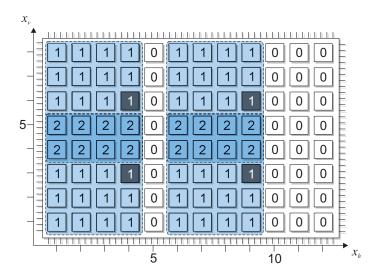

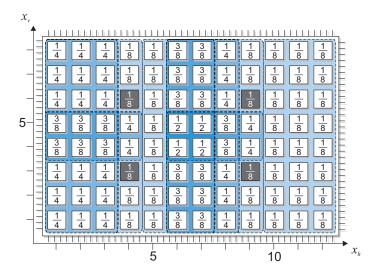

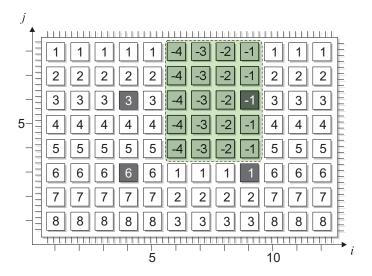

Welche Zellen der rekonfigurierbaren Architektur belegt oder frei sind, lässt sich anhand der Zellbelegung b(i, j) erkennen.

**Definition 3.3** (Zellbelegung). Sei  $N_{col}$  die Anzahl der Spalten und  $N_{row}$  die Anzahl der Reihen der rekonfigurierbaren Architektur. Die Zellbelegung b(i,j) mit  $1 \le i \le N_{col}$  und  $1 \le j \le N_{row}$  stellt die aktuelle Belegung der rekonfigurierbaren Architektur dar. Ist b(i,j) = 0, so wird die Zelle an der Position (i,j) von einer vorhandenen Modulinstanz  $c \in C$  genutzt. Ist b(i,j) = 1, so ist die Zelle an der Position (i,j) frei. Gegeben sei die horizontale Position  $x_h(c)$  und die vertikale Position  $x_v(c)$  einer vorhandenen Instanz  $c \in C$ . Ferner sei m(c) das zugrunde liegende Modul  $m \in M$ ,  $a_h(m)$  die Breite des Moduls und  $a_v(m)$  die Höhe des Moduls. Dann ergibt sich die Zellbelegung b(i,j) wie folgt:

$$b(i,j) = \begin{cases} 0 & wenn \ \exists c \in C \ | \ x_h(c) \le i < x_h(c) + a_h(m(c)) \land \\ & x_v(c) \le j < x_v(c) + a_v(m(c)) \end{cases}$$

(3.1)

Anhand der Zellbelegung b(i, j) lässt sich die Menge der freien Positionen  $X_{free}(m)$  eines Moduls m bestimmen an den das Modul platziert werden kann.

**Definition 3.4** (Menge der freien Positionen). Gegeben sei die Zellbelegung b(i,j) der rekonfigurierbaren Architektur. Dann ist die Menge der freien Positionen  $X_{free}(m)$  eines Moduls m wie folgt definiert:

$$X_{free}(m) = \left\{ (x_h, x_v) \mid (x_h, x_v) \in X_{pos}(m) \land \sum_{i=x_h}^{n_h} \sum_{j=x_v}^{n_v} b(i, j) = a_h(m) \cdot a_v(m) \right\}$$

(3.2)

$$n_h = x_h + a_h(m) - 1 , \qquad n_v = x_v + a_v(m) - 1$$

3.1 DMC-Modell 27

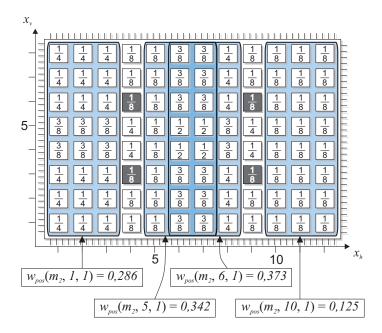

Abbildung 3.6: Beispiel einer Zellbelegung mit der Menge der freien Positionen und der resultierenden Menge der platzierbaren Module.

Mithilfe der Menge der freien Positionen lässt sich die *Menge der platzierbaren Module*  $M_{pla}(d)$ , die auf der geforderten Systemkomponente d basieren, bestimmen.

**Definition 3.5** (Menge der platzierbaren Module). Es sei  $M(d) \subseteq M$  die Menge der Module, die auf der Systemkomponente d basieren. Dann ist die Menge der platzierbaren Module  $M_{pla}(d)$  einer Systemkomponente d wie folgt definiert:

$$M_{pla}(d) = \left\{ m \mid m \in M(d) \land X_{free}(m) \neq \{\} \right\}$$

(3.3)

Abbildung 3.6 zeigt ein Beispiel der Zellbelegung b(i,j) mit der Menge der freien Positionen  $X_{free}(m)$  der einzelnen Module und der resultierenden Menge der platzierbaren Module  $M_{pla}(d)$  der Systemkomponenten. Mithilfe der Mengen  $X_{free}(m)$  und  $M_{pla}(d)$  kann die Platzierung eines Moduls in den folgenden vier Schritten beschrieben werden:

1. Die Grundvoraussetzung für die Platzierung eines Moduls der geforderten Systemkomponente *d* ist das Vorhandensein hinreichend freier Ressourcen auf der Architektur. Dabei muss folgende Bedingung erfüllt sein:

$$M_{pla}(d) \neq \{\} \tag{3.4}$$

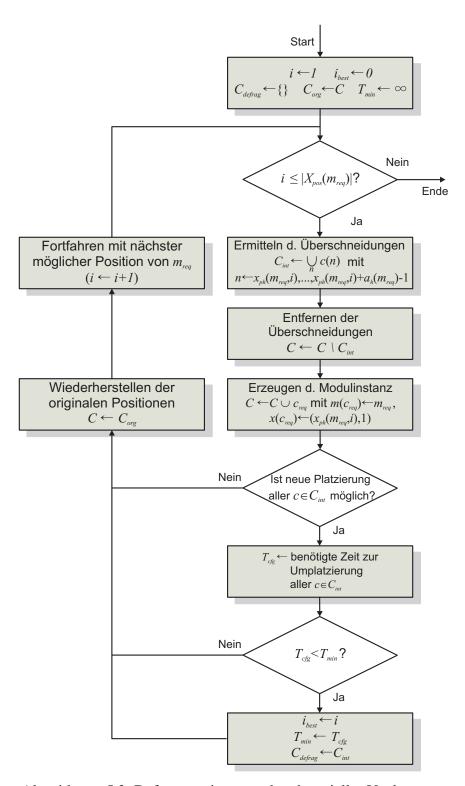

D. h., es muss mindestens ein Modul der geforderten Systemkomponente *d* auf der Architektur platzierbar sein. Ist diese Bedingung nicht erfüllt, so kann die Platzierung abgewiesen oder so lange hinausgezögert werden, bis durch das Entfernen von ausgeführten Modulinstanzen hinreichend viele Ressourcen verfügbar sind. Eine weitere Möglichkeit, die Platzierung dennoch zu ermöglichen, ist die Neuanordnung der bereits platzierten Modulinstanzen mit dem Ziel, ausreichend freie zusammenhängende Ressourcen zu erlangen, die die Platzierung eines Moduls ermöglichen. Diese Art der Umplatzierung wird auch als *Defragmentierung* bezeichnet und wird im Abschnitt 4.3 näher erläutert.

28 3 Modellierung

2. Wenn die obige Platzierungsbedingung erfüllt ist, so wird anhand eines Platzierungsalgorithmus ein geeignetes Modul  $m \in M(d)$  mit einer entsprechenden Position  $x = (x_h, x_v) \in X_{free}(m)$  bestimmt. Die hierbei verwendeten Platzierungsalgorithmen lassen sich grundsätzlich in Algorithmen für homogene Architekturen (siehe Abschnitt 4.1) und Algorithmen für heterogene Architekturen (siehe Abschnitt 5.1) unterteilen.

- 3. Mithilfe des aus dem vorherigen Schritt hervorgegangenen Moduls m und der dazugehörigen Position  $x = (x_h, x_v)$  wird eine Modulinstanz c = (m, x, s, k) erzeugt. Wie im Abschnitt 3.1.1 erläutert, ist der initiale Zustand einer Modulinstanz s = PLA. Der Kommunikationsparameter k beinhaltet z. B. die Adresse, die der Instanz zugewiesen ist. Ein mögliches Verfahren zur Bestimmung der Adresse ist die in [36] beschriebene positionsbasierte Adresszuweisung, bei der jeder möglichen Position eine feste Adresse zugeordnet ist.

- 4. Die zuvor generierte Modulinstanz c wird der Menge der momentan platzierten Modulinstanzen hinzugefügt  $C \leftarrow C \cup c$ . Die entsprechenden Ressourcen gelten nun als belegt, so dass sich folgende Änderung der Zellbelegung ergibt:

$$b(i,j) \leftarrow 0 \quad \forall i,j: x_h \le i < x_h + a_h(m) \land x_v \le j < x_v + a_v(m) \tag{3.5}$$

Die nun generierte Instanz c ist solange Element der Menge C, bis die verschiedenen Zustände durchlaufen sind und die Instanz durch das Zurücksetzen der Zellen von der Architektur entfernt ist. Nach dem Entfernen ist die resultierende Menge der momentan platzierten Modulinstanzen daher  $C \leftarrow C \setminus c$ .

### 3.1.3 Vergleichbare Modelle

Vergleichbare Arbeiten zu dem zuvor beschriebenen DMC-Modell sind das HySAM-Modell von Bondalapati und Prasanna [11]. Dieses Modell kann verwendet werden, um Anwendungen daraufhin zu analysieren, ob sie zu Ausführung auf rekonfigurierbarer Logik geeignet sind. Das Modell basiert auf einer Systemarchitektur, bestehend aus einem Mikroprozessor, der über einen Bus mit einer rekonfigurierbarer Logikeinheit (engl.: Configurable Logic Unit (CLU)) verbunden ist. Die auszuführende Anwendung wird dabei in eine Sequenz von Funktionen  $F = \{F_1, \ldots, F_n\}$  unterteilt, wobei jede einzelne Funktion entweder auf dem Mikroprozessor oder auf der CLU ausgeführt werden kann. Auf diese Weise kann zur Laufzeit entschieden werden, ob eine Funktion in Software oder in rekonfigurierbarer Hardware ausgeführt wird. Jede Funktion ist mindestens einer CLU-Konfiguration  $C = \{C_1, \ldots, C_m\}$  zugeordnet, wobei eine CLU-Konfiguration aus mehreren Funktionen bestehen kann. Eine CLU-Konfiguration stellt damit den Kontext der rekonfigurierbaren Fläche dar. Das Modell orientiert sich demnach an dem Prinzip der Multi-Kontext-Architekturen, wie

3.1 DMC-Modell 29

in [63, 77] beschrieben. Das HySAM Modell findet Einsatz in der Simulationsumgebung DRIVE [12], welche eine interaktive Analyse der zugrunde liegenden Systemarchitektur ermöglicht. Mithilfe von DRIVE lassen sich Ausführungszeiten bestimmen und die Auslastung der Ressourcen nachbilden. Bezüglich des DMC-Modells kann eine Funktion mit einem Hardware-Modul gleichgesetzt werden. Ebenso kann eine Konfiguration mit der Menge der momentan platzierten Modulinstanzen C verglichen werden.

Lange und Middendorf beschreiben in [48, 49] das Modell der *hyperrekonfigurier-baren Architektur*. Hyperrekonfigurierbarkeit meint dabei eine dynamische Anpassung der Rekonfigurationsmöglichkeiten der Architektur, so dass die Rekonfigurationsschritte und die damit verbundene Rekonfigurationszeit für eine gegebene Anwendung optimiert werden können. Die Rekonfiguration wird dabei auf der Ebene der *Hyperkontexte* und der Ebene der *Kontexte* betrachtet. Hyperkontexte definieren die Rekonfigurationsmöglichkeiten der Architektur. Ähnlich wie im HySAM Modell spezifizieren Kontexte das Verhalten von aktiven Ressourcen. Das Modell betrachtet im Wesentlichen Rekonfigurationseigenschaften einer Architektur und geht dabei nicht im Speziellen auf partielle Rekonfigurierbarkeit ein. Bezüglich des DMC-Modells kann ein Kontext mit der Menge der momentan platzierten Modulinstanzen *C* verglichen werden.

Bazargan et al. verwenden in [8] ein Modell, welches auf so genannte *RFUOPs* (engl.: Reconfigurable Functional Unit Operations) aufbaut. Das Modell betrachtet den Flächenbedarf, den Start- und Endzeitpunkt einer *RFUOP*. Die Menge *ACC* beschreibt alle erfolgreich platzierten *RFUOPs* und deren zugewiesenen Positionen. Da der Start- und Endzeitpunkt der *RFUOPs* als gegeben betrachtet wird, dient das Modell zur Beschreibung von Offline-Platzierungsverfahren, d. h., die Start- und Endzeitpunkte und die Positionen der einzelnen *RFUOPs* werden zur Entwurfszeit bestimmt. Das Modell lässt dabei den Aspekt der Rekonfigurationszeit von *RFUOPs* außer Acht.

Das in Steiger et al. [72] beschriebene Modell betrachtet Tasks als rechteckförmige Flächen rekonfigurierbarer Ressourcen. Das Modell wird verwendet, um Platzierungs- und Ablaufplanungsverfahren für echtzeitfähige rekonfigurierbare Systeme zu beschreiben. Ein Task  $T_i$  ist gegeben durch die Breite  $w_i$  und Höhe  $h_i$  und durch den Zeitpunkt der Anfrage  $a_i$ . Darüber hinaus beschreibt  $e_i$  die Ausführungszeit und  $d_i$  die Deadline, wobei gilt  $d_i \geq a_i + e_i$ . Durch die Betrachtung gegebener Ausführungszeiten und Deadlines ist das Modell für Echtzeitsysteme ausgelegt. Da die Ausführungszeiten der Tasks gegeben sind, gestaltet sich die Platzierung der Tasks zur Laufzeit als dreidimensionales Packungsproblem. Neben der Breite  $w_i$  und der Höhe  $h_i$  beschreibt die Ausführungszeit  $e_i$  die dritte Dimension eines Tasks. Ein geplanter Task (engl.: Scheduled Task) beschreibt einen Task, dessen Anfangszeitpunkt und Position vom Platzierungsalgorithmus zugewiesen wurde. Insofern lässt sich ein geplanter Task mit einer Modulinstanz im DMC-Modell vergleichen.

Das DMC-Modell hebt sich im Wesentlichen durch Betrachtung der Ebenen Systemkomponente, Hardware-Modul und Modulinstanz von den oben genannten Modellierungen ab. Insbesondere die Betrachtung der Zustände der derzeit platzierten Modulinstanzen ermöglicht unter anderem die Berücksichtigung von Konfigurationsund Löschvorgängen, welche in den meisten Modellierungen nicht betrachtet werden. Darüber hinaus erlaubt das DMC-Modell neben der Modellierung homogener rekonfigurierbarer Architekturen ebenso die Modellierung heterogener rekonfigurierbarer Architekturen.

Die in dieser Arbeit betrachteten Platzierungsverfahren beziehen sich auf den Fall, dass Anfragezeitpunkte und Ausführungszeiten der Systemkomponenten zur Entwurfszeit unbekannt sind. Die Ausführungszeit eines entsprechenden Hardware-Moduls ist z. B. dann unbekannt, wenn das Ende der Ausführung an Bedingungen geknüpft ist oder von äußeren Parametern des Systems abhängt. Bei der Platzierung werden daher lediglich die Modulflächen der entsprechenden Hardware-Module betrachtet. Trotz unbekannter Ausführungszeiten ist bei der Platzierung eines Hardware-Moduls eine Ablaufplanung erforderlich, wie sie im folgenden Abschnitt näher beschrieben wird.

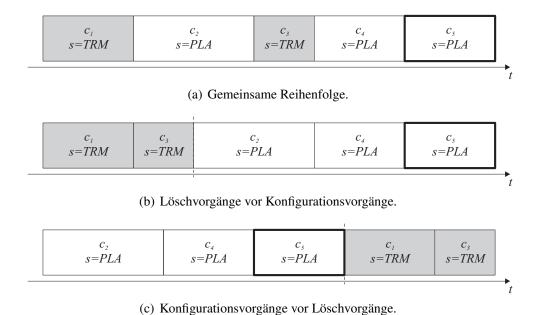

## 3.2 Ablaufplanung

Die Ablaufplanung ist insbesondere dann mit der Modulplatzierung verknüpft, wenn die Ausführungszeit der Modulinstanz bekannt ist. In diesem Fall lässt sich die Ablaufplanung und Platzierung als gemeinsames dreidimensionales Packungsproblem formulieren und zur Entwurfszeit (siehe [23, 30]) oder zur Laufzeit (siehe [71]) mit entsprechenden Verfahren lösen. Sobald die Ausführungszeiten der Hardware-Module unbekannt sind, können Ablaufplanung und Platzierung nicht mehr als gemeinsames Optimierungsproblem betrachtet werden. Trotz der unbekannten Ausführungszeiten ist dennoch eine Ablaufplanung erforderlich, denn sowohl die Platzierung eines Moduls als auch der Konfigurationsprozess einer Modulinstanz kann nur sequenziell durchgeführt werden. Wenn beispielsweise zur Laufzeit mehrere Komponentenanfragen zur gleichen Zeit gestellt werden, so muss anhand einer Ablaufplanung bestimmt werden, welche der Komponentenanfragen als Erstes der Platzierung übergeben wird. Die Ablaufplanung unterteilt sich demnach in Platzierungsablaufplanung und Konfigurationsablaufplanung. Bei der Platzierungsablaufplanung wird entschieden, welches Modul der derzeit angeforderten Systemkomponenten als Nächstes platziert wird. Nach der Platzierung befindet sich die generierte Modulinstanz im Zustand PLA (vgl. Abbildung 3.4). Bei der Konfigurationsablaufplanung wird entschieden, welche der im Zustand PLA oder im Zustand TRM befindlichen Modulinstanzen als Nächstes konfiguriert bzw. gelöscht wird. Es besteht daher ein zeitlicher Zusammenhang zwischen der Platzierungsablaufplanung und der Konfigurationsablaufplanung.

31

### 3.2.1 Platzierungsablauf

Die Ablaufplanung der Platzierung beinhaltet zum einen die Festlegung der Platzierungsreihenfolge der derzeit angeforderten Systemkomponenten und zum anderen die Handhabung fehlgeschlagener Modulplatzierungen. Modulplatzierungen können grundsätzlich nicht parallel durchgeführt werden, da der Platzierungsalgorithmus zur Bestimmung der Position eines Moduls einen eindeutigen Suchraum benötigt. Eine Platzierungsablaufplanung wird genau dann benötigt, wenn gleichzeitig oder mit geringer Verzögerung mehrere Systemkomponenten angefragt werden, so dass mindestens eine Platzierung nicht unmittelbar durchgeführt werden kann. Die Platzierungsablaufplanung trifft die Entscheidung, welche Systemkomponente als Nächstes platziert wird.

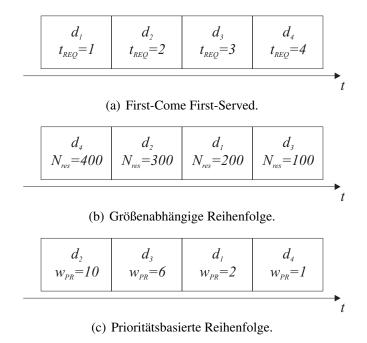

Es besteht daher eine Parallele zu nicht-präemptiven Prozess-Scheduling-Verfahren im Bereich der Betriebssysteme. In [73] werden verschiedene Scheduling-Verfahren diskutiert, wobei sich z. B. die folgenden Verfahren auf die Platzierungsablaufplanung übertragen lassen:

First-Come First-Served (FCFS): Eines der einfachsten Verfahren zur Festlegung der Platzierungsreihenfolge ist das *First-Come-First-Served-*Verfahren, welches die Platzierungen in der Reihenfolge der Komponentenanfragen durchführt. Auf diese Weise wird sichergestellt, dass die Modulplatzierung einer neuen Komponentenanfrage nicht beliebig verzögert wird. Das Verfahren ist besonders gut geeignet, wenn Komponentenanfragen gleichberechtigt sind und keine Priorisierung einzelner Komponentenanfragen vorhanden ist.