# **Run-time Reconfigurable RTOS for Reconfigurable Systems-on-Chip**

## **Dissertation**

A thesis submitted to the

**Faculty of Computer Science, Electrical Engineering and Mathematics**

of the

**University of Paderborn**

and to the

**Graduate Program in Electrical Engineering (PPGEE)**

of the

**Federal University of Rio Grande do Sul**

in partial fulfillment of the requirements for the degree of

*Dr. rer. nat.*

and

*Dr. in Electrical Engineering*

**Marcelo Götz**

November, 2007

*Supervisors:*

Prof. Dr. rer. nat. Franz J. Rammig, University of Paderborn, Germany

Prof. Dr.-Ing. Carlos E. Pereira, Federal University of Rio Grande do Sul, Brazil

*Public examination in Paderborn, Germany*

Additional members of examination committee:

Prof. Dr. Marco Platzner

Prof. Dr. Urlich Rückert

Dr. Mario Porrmann

Date: April 23, 2007

*Public examination in Porto Alegre, Brazil*

Additional members of examination committee:

Prof. Dr. Flávio Rech Wagner

Prof. Dr. Luigi Carro

Prof. Dr. Altamiro Amadeu Susin

Prof. Dr. Leandro Buss Becker

Prof. Dr. Fernando Gehm Moraes

Date: October 11, 2007

# Acknowledgements

This PhD thesis was carried out, in his great majority, at the Department of Computer Science, Electrical Engineering and Mathematics of the University of Paderborn, during my time as a fellow of the working group of Prof. Dr. Franz J. Rammig. Due to a formal agreement between Federal University of Rio Grande do Sul (UFRGS) and University of Paderborn, I had the opportunity to receive a bi-national doctoral degree. Therefore, I had to accomplish, in addition, the PhD Graduate Program in Electrical Engineering of UFRGS. So, I hereby acknowledge, without mention everyone personally, all persons involved in making this agreement possible.

I wish to, first, express my deep gratitude to my supervisor Prof. Dr. Franz Josef Rammig for supervising, advising and tutoring me during my whole PhD journey. His understanding, patience, knowhow and constant encouragements were essential to bring me to the success of finishing this work. In the same way, I wish to thank specially my co-supervisor, Prof. Dr. Carlos Eduardo Pereira, for his equal support, even before starting this PhD thesis. The many fruitful talks, in which he shared with me his knowledge and experience, had strong influence in my decision of being a researcher and starting this PhD.

I am also glad of having being part of Prof. Rammig's working group, of having the opportunity to work on different research projects, to advise Bachelor and Master Students, and to supervise students during labs of his lectures. Furthermore, I am glad of having many chances for fruitful talks, discussions, brainstorming, that I had with my colleagues in the great atmosphere of the working group. All these facts together, have positively contributed to the success of this work.

My thanks go also to both examination committees: in Germany composed by Prof. Dr. Marco Platzner, Prof. Dr. Urlich Rückert, Dr. Mario Porrmann; and in Brazil composed by Prof. Dr. Flávio Rech Wagner, Prof. Dr. Luigi Carro, Prof. Dr. Altamiro Amadeu Susin, Prof. Dr. Leandro Buss Becker, Prof. Dr. Fernando Gehm Moraes. They, together with my both supervisors, spent their times reading this thesis and provided me a positive feedback during the PhD-defense.

I wish also to thank all my former colleagues, which helped be somehow during my PhD research. Their different points of view, wide range of interests and knowledge, were very important to improve the level of my work. My particular thanks go to Dr. Achim Rettberg, for spending his time in listening and discussing my research topic, and for offering his partnership and friendship, which was always pushing me forward in several moments. In the same way, I wish to thank Florian Dittmann, who shared with me his great knowledge in Reconfigurable Computing. With these two colleagues, I had several publications, which were extremely important in my research. Thank you both for your cooperation.

Further, I whish to extend my thankfulness to all my other colleagues: Dr. Sabina Rips, Tales Heimfarth for several and fruitful discussions, Yuhong Zhao, Katharina Stahl, Peter Janacik, Timo Kersten, Simon Oberthuer, Norma Montealegre, Dr. Carsten Böke, Dr. Martin Kardos, Dr. Klaus Danne, Dr. Stefan Ihmor, and Prof. Dr. Christophe Bobda. I wish to thank specially Dalimir Orfanus, which with his friendship gave me strong support in my last part of my PhD journey.

I must not forget my working students, Stefan Finke and MSc. Tao Xie, which helped me in implementing an important part of my concepts. Without them, this thesis would take longer to be finished.

I will never forget my friend Arne Rolf Spiller, who had crucial importance in my first years in Germany. With his unconditional friendship and support, I surpassed my self on several circumstances. He and his parents, Erwin and Ursula, are my second family now. Thank you for being so receptive and lovely.

Finally, I wish to thank my sister Fabiana and my loving mother Antônia Elvira, which pushed me forward in my studies, since I started in the school until today. Last, but not least, my lovely thanks go to Adriana Aparecida Paz, my girlfriend, who never abandoned me, even having an ocean between us. She was very important for the success of this work, due to his patience and support, and especially for her comprehensiveness and loveliness.

November, 2007.

# Abstract

Embedded systems are massively present in our lives and they are becoming omnipresent. This has demanded strong efforts in research for providing new solutions for the challenges faced in the design of such systems. For instance, the requirements of high computational performance and flexibility of the contemporary embedded systems are continuously increasing. A single architecture must be able to support, in certain cases, different kind of applications with different requirements which can start asynchronously and dynamically (changing environments). Reconfigurable computing seems to be a potential paradigm for these scenarios as it can provide flexibility and high computational performance for modern embedded systems. Of especial interest are those architectures where a microprocessor is tightly connected with a reconfigurable hardware (hybrid platform), constituting a so called reconfigurable System-on-Chip (RSoC). However, the complexity in designing such systems rises. Therefore, the usage of an Operating System (OS) is essential to provide the necessary abstraction of the computational resources in reconfigurable computing. Moreover, due to the intrinsic overhead caused by the reconfiguration activities and the potential sharing of computational resources the necessity for support provided by an OS is unquestionable. Nevertheless, embedded system platforms lack in computational resources. This fact requires a careful design of an OS for such a system, since it also consumes its resources.

Along with the application tasks, the OS can profit from a RSoC based architecture by reconfiguring itself over this hybrid platform. Thereby, the OS can make use of the remaining resources that are not currently required by the application for its execution. Within this context, this work presents the design of proper methodologies, strategies, hardware and design support for a proper management of dynamic reconfiguration activities of a Real-Time Operating System (RTOS) running on a RSoC based platform. The intention thereby, is to promote the self-reconfiguration of the RTOS services on this hybrid platform, so that the computational resources of this execution platform are used in an efficient way.

# Zusammenfassung

Eingebettete Systeme haben eine starke Präsenz in unseren alltäglichen Leben bekommen, in vielen Bereichen sind sie allgegenwärtig geworden. Dieses ist eine Herausforderung für die Forschung im Bereich solcher Systeme. Ständig müssen neue adäquate Lösungen gefunden werden. Durch die zunehmenden Anforderungen nimmt die Leistung und Flexibilität bei eingebetteten Systemen ständig zu. Zum Beispiel, eine einzelne Architektur muss in der Lage sein, in bestimmten Fällen, mehrere Applikationen mit verschiedenen Anforderungen zu unterstützen, die asynchron und dynamisch ablaufen können (dynamische Umgebungen). Rekonfigurierbare Rechensysteme scheinen ein potentielles Paradigma für diese Szenarien zu sein, weil sie Flexibilität und hohe Rechenleistung für moderne eingebettete Systeme liefern können. Von besonderem Interesse sind jene Architekturen, wo ein Mikroprozessor mit rekonfigurierbarer Hardware fest verbunden ist (hybride Plattform). Eine solche hybride Plattform nennt man rekonfigurierbares System-on-Chip (RSoC). Jedoch nimmt die Komplexität in solchen Systemen ständig zu. Deshalb ist die Anwendung eines Betriebssystems (OSs) wesentlich, um eine notwendige Abstraktion von den vorhandenen Ressourcen in rekonfigurierbaren Rechensystemen zu ermöglichen. Weiterhin, ist durch die gemeinsame Nutzung von Ressourcen einer solchen Architektur und deren Verwaltung in Bezug auf die Rekonfiguration, der Einsatz eines OS zwingend notwendig. Dennoch sind die Ressourcen in eingebetteten Systemen begrenzt. Deshalb muss beim Entwurf eines OS für ein solches System sorgfältig vorgegangen werden, da das OS an sich schon Ressourcen verbraucht.

Zusammen mit den Applikationen kann das OS auch von den RSoC Architekturen profitieren dadurch, dass das OS sich selbst auf der hybriden Plattform rekonfigurieren kann. Somit kann das OS die übrigen Ressourcen nutzen, die nicht gegenwärtig von der Applikation benutzt werden. In diesen Rahmen präsentiert die vorliegende Arbeit den Entwurf von geeigneten Methodologien, Strategien, Hardware und Entwurfssunterstützungen für eine geeignete Verwaltung von dynamischen Rekonfigurierungsaktivitäten eines Echtzeitbetriebssystems (RTOSs), das auf einer RSoC basierten Plattform läuft. Die Intention dabei ist es die Selbst-Rekonfiguration der RTOS Dienste auf einer hybriden Plattform zu ermöglichen, wodurch die vorhandenen Ressourcen der Plattform effektiv ausgenutzt werden können.

# Resumo

Sistemas embarcados estão cada vez mais presentes em nossas vidas e estão se tornando onipresentes. Este fato tem demandado grandes esforços em pesquisa para criação de propostas e soluções para os desafios gerados no desenvolvimento destes sistemas. Por exemplo, uma arquitetura moderna de sistemas embarcados requer alto poder de computação e também grande flexibilidade, e a demanda por estes requisitos tem crescido constantemente. Uma única arquitetura deve executar, em certos casos, diferentes aplicações com diferentes requisitos e com inicio de execução indeterminado, caracterizando desta maneira um ambiente dinâmico. A computação reconfigurável aparece como um paradigma promissor para estes casos pois consegue prover alto poder de computação juntamente com flexibilidade requeridas pelos sistemas embarcados modernos. Especialmente interessantes são arquiteturas baseadas em System-on-Chip reconfiguráveis (RSoC), nas quais um microprocessador está fortemente conectado a um hardware reconfigurável (plataforma híbrida). Porém a complexidade no desenvolvimento destes tipos de sistemas cresce, tornando o uso de um sistema operacional (SO) indispensável. Entretanto, uma plataforma de execução de um sistema embarcado sofre pela escassez de recursos. Este fato exige um cuidado especial no desenvolvimento de um SO uma vez que este também usa os recursos desta plataforma.

Juntamente com as tarefas da aplicação, o SO também pode tirar proveito de uma plataforma baseada em RSoC onde este é capaz de se auto reconfigurar sobre esta plataforma híbrida. Deste modo, o SO pode usar os recursos computacionais, correntemente não requeridos pelas aplicações, para a sua execução. Dentro deste contexto, este trabalho apresenta o design de metodologias, estratégias e suporte em hardware e software para o gerenciamento apropriado das atividades de reconfigurações dinâmicas de um sistema operacional de tempo-real (RTOS), que é executado em uma plataforma baseada em RSoC. A intenção com isto é a de proporcionar ao RTOS meios com os quais este é capaz de se auto reconfigurar nesta arquitetura híbrida com a intenção de atingir um uso mais eficiente dos recursos computacionais desta plataforma de execução.

---

# Contents

---

|                                                           |              |

|-----------------------------------------------------------|--------------|

| <b>List of Figures</b>                                    | <b>xvii</b>  |

| <b>List of Tables</b>                                     | <b>xix</b>   |

| <b>List of Algorithms</b>                                 | <b>xxi</b>   |

| <b>List of Symbols</b>                                    | <b>xxiii</b> |

| <b>1. Introduction</b>                                    | <b>1</b>     |

| 1.1. Motivation . . . . .                                 | 2            |

| 1.2. Thesis Goals . . . . .                               | 3            |

| 1.3. Thesis Contributions . . . . .                       | 4            |

| 1.4. Thesis Outline . . . . .                             | 4            |

| <b>2. Background</b>                                      | <b>7</b>     |

| 2.1. Embedded System Design . . . . .                     | 7            |

| 2.2. Reconfigurable Computing Overview . . . . .          | 9            |

| 2.2.1. Coupling CPU and Reconfigurable Hardware . . . . . | 11           |

| 2.2.2. Reconfigurable System Design . . . . .             | 11           |

| 2.3. Reconfigurable Hardware Technology . . . . .         | 13           |

| 2.3.1. Hybrid Architecture . . . . .                      | 14           |

| 2.3.2. Configuration Techniques . . . . .                 | 15           |

| 2.3.3. Partial Reconfiguration Feature . . . . .          | 16           |

| 2.4. Chapter Conclusions . . . . .                        | 17           |

| <b>3. Related Work Survey</b>                             | <b>19</b>    |

---

|           |                                                                |           |

|-----------|----------------------------------------------------------------|-----------|

| 3.1.      | (Re)Configurable Operating Systems . . . . .                   | 19        |

| 3.1.1.    | Statically Reconfigurable OS . . . . .                         | 20        |

| 3.1.2.    | Dynamically Reconfigurable OS: Application Triggered . . . . . | 21        |

| 3.1.3.    | Dynamically Reconfigurable OS: System Triggered . . . . .      | 23        |

| 3.1.4.    | Towards Online Reconfigurable DREAMS . . . . .                 | 24        |

| 3.1.5.    | Further Comments . . . . .                                     | 24        |

| 3.2.      | Operating System for Reconfigurable Computing . . . . .        | 25        |

| 3.2.1.    | Low-level OS Support for Reconfigurable Hardware . . . . .     | 26        |

| 3.2.2.    | Application Model . . . . .                                    | 29        |

| 3.2.3.    | OS Services for Reconfigurable Hardware . . . . .              | 29        |

| 3.2.4.    | RTOS issues in High Level Design . . . . .                     | 30        |

| 3.2.5.    | Offline Approaches . . . . .                                   | 31        |

| 3.2.6.    | Run-time Support . . . . .                                     | 32        |

| 3.2.7.    | Multitasking Issues . . . . .                                  | 35        |

| 3.2.8.    | Dynamically Hybrid Architectures . . . . .                     | 36        |

| 3.3.      | Further Approaches . . . . .                                   | 37        |

| 3.3.1.    | Hardware Accelerator for RTOS . . . . .                        | 37        |

| 3.3.2.    | Multithreading on Hybrid Architectures . . . . .               | 38        |

| 3.4.      | Chapter Conclusions . . . . .                                  | 40        |

| 3.4.1.    | Correlation With This Thesis . . . . .                         | 40        |

| 3.4.2.    | Additional Comments . . . . .                                  | 41        |

| <b>4.</b> | <b>Run-time Reconfigurable RTOS</b>                            | <b>43</b> |

| 4.1.      | System Overview . . . . .                                      | 43        |

| 4.1.1.    | Target Applications . . . . .                                  | 44        |

| 4.1.2.    | Target RTOS . . . . .                                          | 45        |

| 4.1.3.    | Instrumented OS API . . . . .                                  | 46        |

| 4.1.4.    | Run-time Reconfiguration Manager - RRM . . . . .               | 49        |

| 4.2.      | Hardware Architecture . . . . .                                | 49        |

| 4.3.      | Design Support . . . . .                                       | 50        |

| 4.4.      | Chapter Conclusions . . . . .                                  | 51        |

| <b>5.</b> | <b>Modeling &amp; Problem Formulation</b>                      | <b>53</b> |

| 5.1.      | Component Assignment . . . . .                                 | 53        |

| 5.1.1.    | Constraints Definition . . . . .                               | 54        |

| 5.1.2.    | Objective Function Definition . . . . .                        | 55        |

| 5.1.3.    | Allocation Example . . . . .                                   | 56        |

| 5.2.      | Reconfiguration Costs . . . . .                                | 56        |

| 5.2.1.    | Temporal Specification . . . . .                               | 58        |

| 5.3.      | Communication Costs . . . . .                                  | 59        |

| 5.4.      | Chapter Conclusions . . . . .                                  | 61        |

| <b>6.</b> | <b>Run-Time Methods</b>                                        | <b>63</b> |

| 6.1.      | OS Service Allocation . . . . .                                | 63        |

---

|                                                            |            |

|------------------------------------------------------------|------------|

| 6.1.1. OS Service Assignment Phase . . . . .               | 64         |

| 6.1.2. OS Service Assignment Example . . . . .             | 64         |

| 6.1.3. Balance <i>B</i> Improvement Phase . . . . .        | 65         |

| 6.1.4. Balance <i>B</i> Improvement Example . . . . .      | 67         |

| 6.1.5. Reconfiguration Cost Reduction . . . . .            | 68         |

| 6.2. Communication-aware Allocation Algorithm . . . . .    | 69         |

| 6.3. Handling Reconfiguration Activities . . . . .         | 71         |

| 6.4. OS Component Reconfiguration . . . . .                | 72         |

| 6.4.1. Applying Total Bandwidth Server . . . . .           | 74         |

| 6.4.2. Deriving Migration Conditions . . . . .             | 75         |

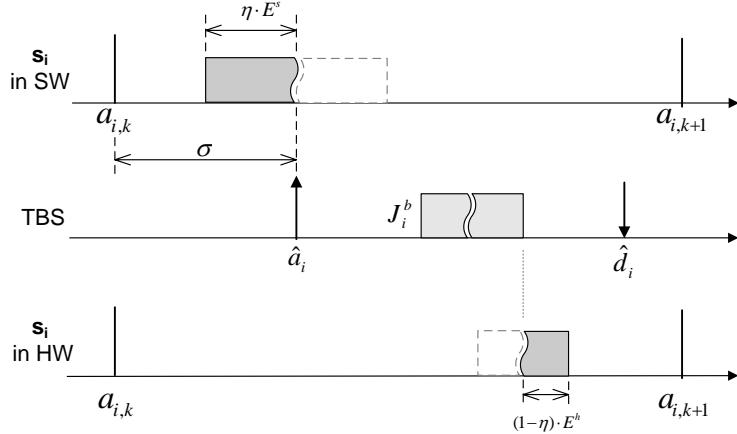

| 6.4.3. Software to Hardware Migration . . . . .            | 75         |

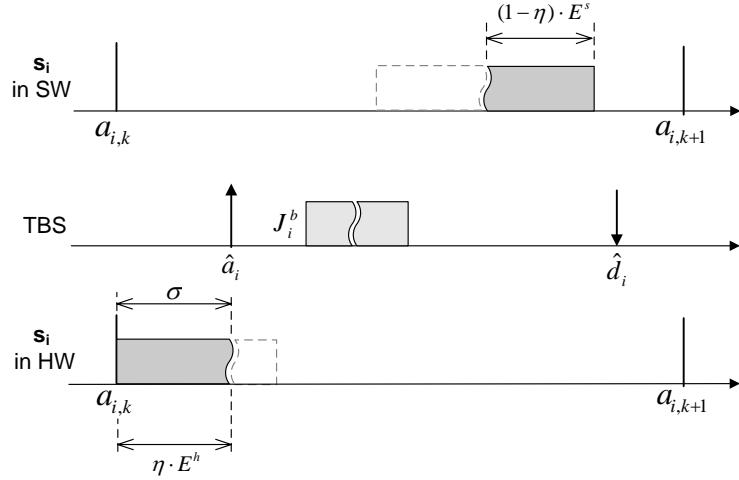

| 6.4.4. Hardware to Software Migration . . . . .            | 77         |

| 6.4.5. Software Service Reconfiguration . . . . .          | 77         |

| 6.4.6. Hardware Service Reconfiguration . . . . .          | 78         |

| 6.4.7. Migrating by Preempting . . . . .                   | 78         |

| 6.5. Schedulability Analysis . . . . .                     | 81         |

| 6.6. OS Components Scheduling . . . . .                    | 82         |

| 6.6.1. Partial Schedule . . . . .                          | 83         |

| 6.6.2. Complete Schedule . . . . .                         | 84         |

| 6.7. Chapter Conclusions . . . . .                         | 85         |

| <b>7. Methods Evaluation</b>                               | <b>87</b>  |

| 7.1. OS Components Allocation . . . . .                    | 87         |

| 7.1.1. OS Components Assignment . . . . .                  | 87         |

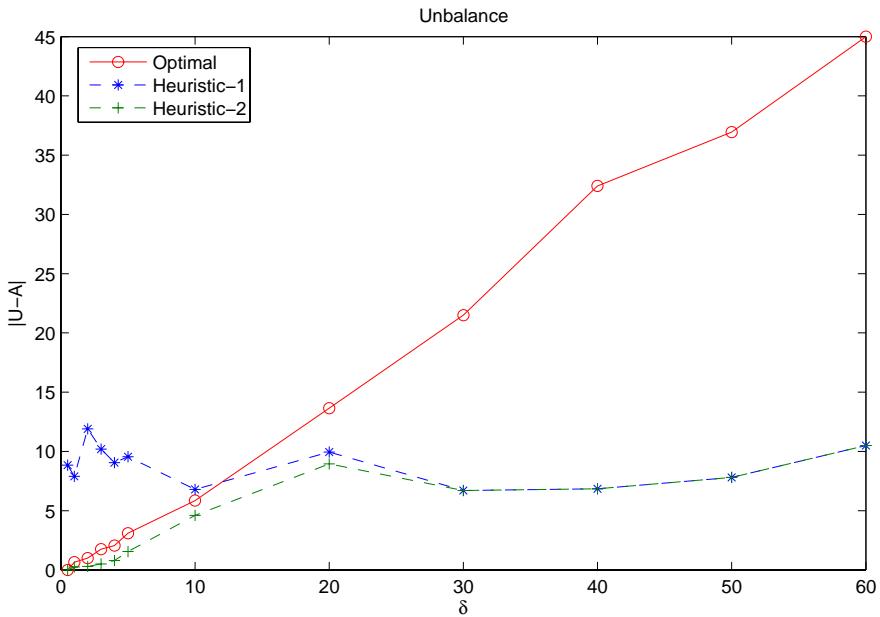

| 7.2. Balancing Heuristic . . . . .                         | 88         |

| 7.2.1. Reconfiguration Cost Reduction . . . . .            | 89         |

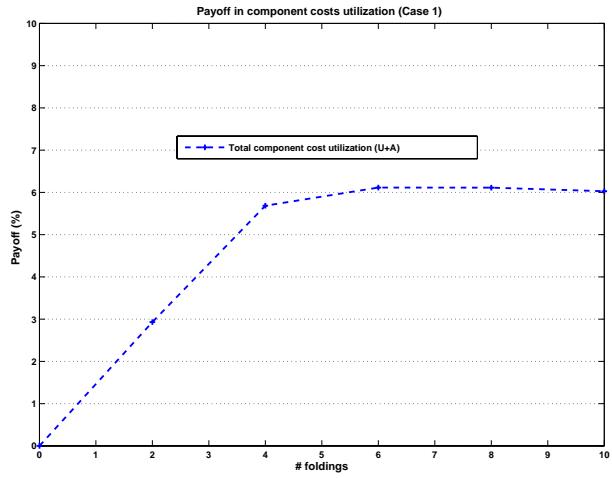

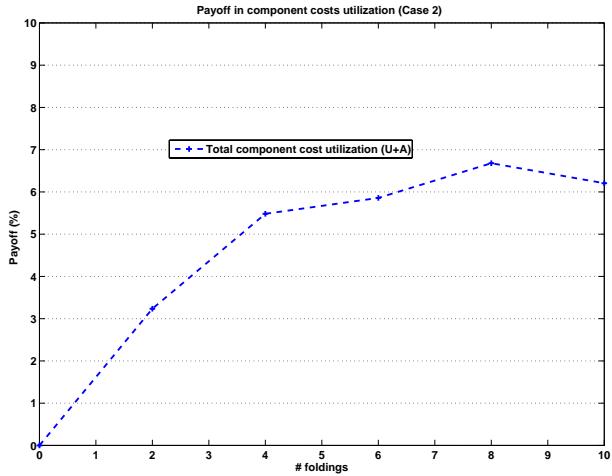

| 7.3. Components Reconfiguration Scheduling . . . . .       | 91         |

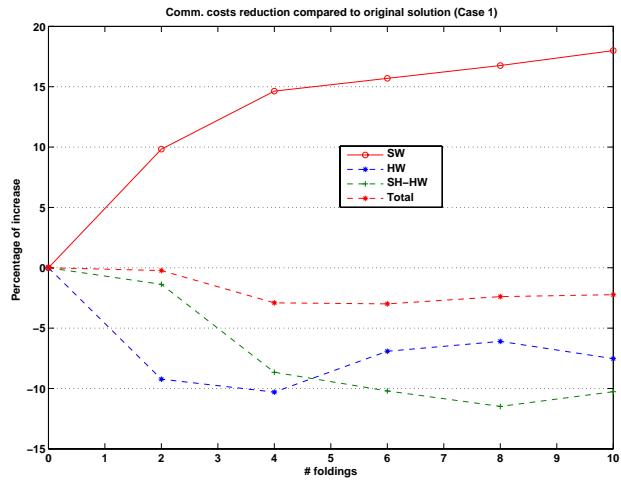

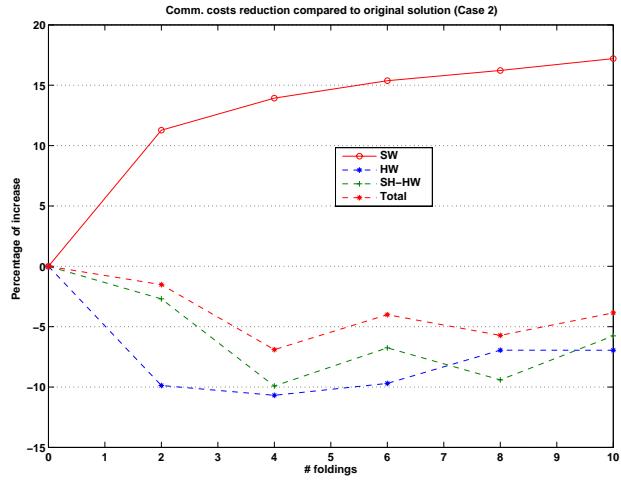

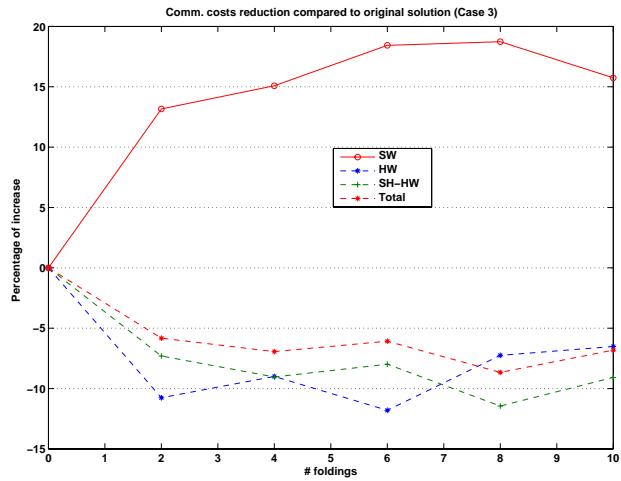

| 7.4. Communication costs reduction . . . . .               | 92         |

| 7.5. Chapter Conclusions . . . . .                         | 95         |

| <b>8. Design Support</b>                                   | <b>97</b>  |

| 8.1. Hardware-Software Interface Synthesis . . . . .       | 98         |

| 8.1.1. OS Driver Extension . . . . .                       | 99         |

| 8.1.2. Software Interface for Reconfigurable IPs . . . . . | 99         |

| 8.1.3. Integration into IFS Tool . . . . .                 | 100        |

| 8.1.4. Further Extension for DREAMS . . . . .              | 101        |

| 8.2. Relocatable Tasks Design . . . . .                    | 101        |

| 8.2.1. Unified Task Representation . . . . .               | 102        |

| 8.2.2. A Framework for Relocatable Task Design . . . . .   | 104        |

| 8.3. Chapter Conclusions . . . . .                         | 107        |

| <b>9. Case Study</b>                                       | <b>111</b> |

| 9.1. Target OS Service . . . . .                           | 111        |

| 9.2. Relocatable Triple-DES . . . . .                      | 113        |

|                                                        |            |

|--------------------------------------------------------|------------|

| 9.3. Testbed Set Up . . . . .                          | 115        |

| 9.4. Quantitative Results . . . . .                    | 116        |

| 9.5. Chapter Conclusions . . . . .                     | 118        |

| <b>10. Conclusion &amp; Outlook</b>                    | <b>121</b> |

| 10.1. Summary . . . . .                                | 121        |

| 10.2. Outlook . . . . .                                | 123        |

| <b>A. Further Evaluation Results</b>                   | <b>125</b> |

| <b>B. HW/SW Interface Generation</b>                   | <b>129</b> |

| <b>C. Hardware/Software Task Design</b>                | <b>131</b> |

| C.1. Hardware Task Controller Template . . . . .       | 131        |

| C.2. Sequence Graphs for Two Migration Cases . . . . . | 131        |

| <b>D. TBS Server Bandwidth Estimation</b>              | <b>135</b> |

---

## List of Figures

---

|      |                                                                                              |    |

|------|----------------------------------------------------------------------------------------------|----|

| 1.1. | Reconfigurable OS for RSoC: Overview. . . . .                                                | 3  |

| 2.1. | HW/SW partitioning scheme. . . . .                                                           | 9  |

| 2.2. | Performance versus Flexibility tradeoff. . . . .                                             | 10 |

| 2.3. | Example of dynamic reconfiguration usage [33]. . . . .                                       | 11 |

| 2.4. | CPU and RH: Coupling types. . . . .                                                          | 12 |

| 2.5. | Typical SoC architecture (a) and a RSoC architecture (b) [38]. . . . .                       | 13 |

| 2.6. | FPGA comprises a set of CLBs. . . . .                                                        | 13 |

| 2.7. | Viertex-II Pro architecture overview [40]. . . . .                                           | 14 |

| 2.8. | CoreConnect block diagram [40]. . . . .                                                      | 15 |

| 2.9. | Example of device partition for 1D (a) and 2D (b) partition models. . . . .                  | 17 |

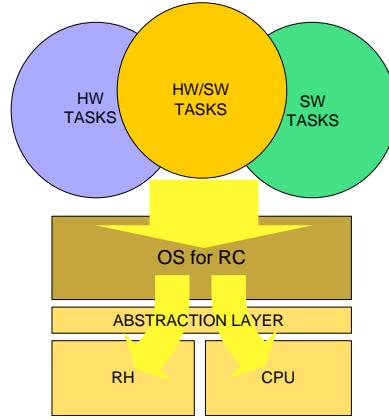

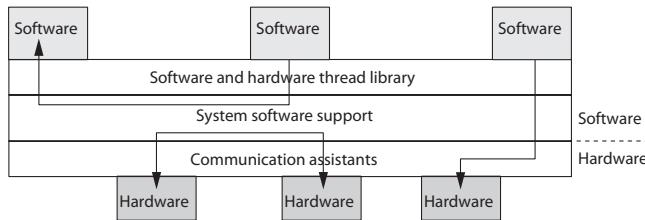

| 3.1. | Execution environment envisioned by the Reconfigurable Computing research community. . . . . | 26 |

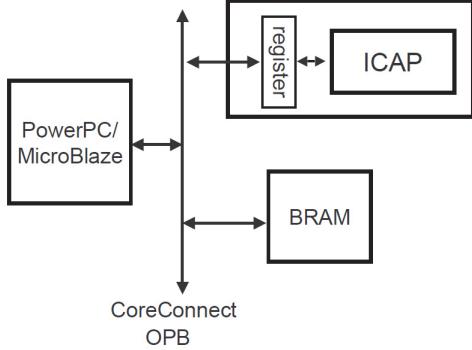

| 3.2. | Self-programming hardware architecture [87]. . . . .                                         | 27 |

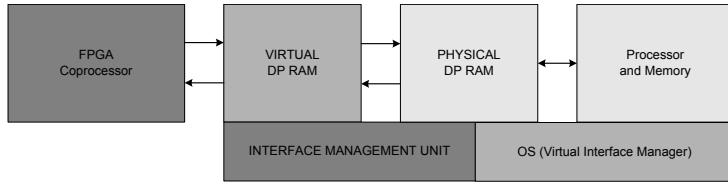

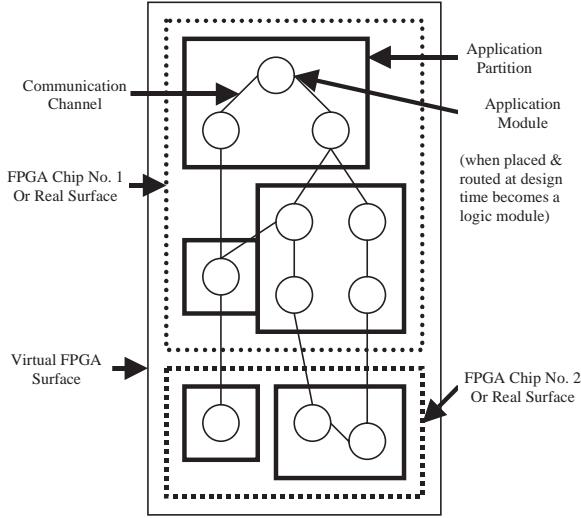

| 3.3. | Virtualized interface [90]. . . . .                                                          | 28 |

| 3.4. | Software and hardware threads connected through a virtualization layer [93]. . . . .         | 28 |

| 3.5. | A task graph on FPGA [98]. . . . .                                                           | 33 |

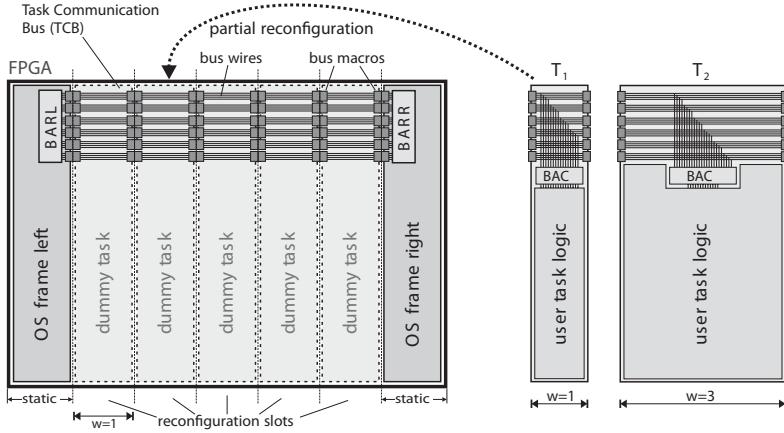

| 3.6. | OS frame and task communication block [114]. . . . .                                         | 34 |

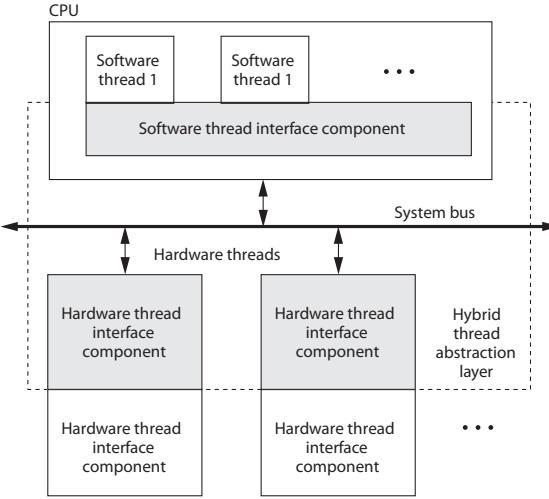

| 3.7. | Hybrid thread abstraction layer [148]. . . . .                                               | 39 |

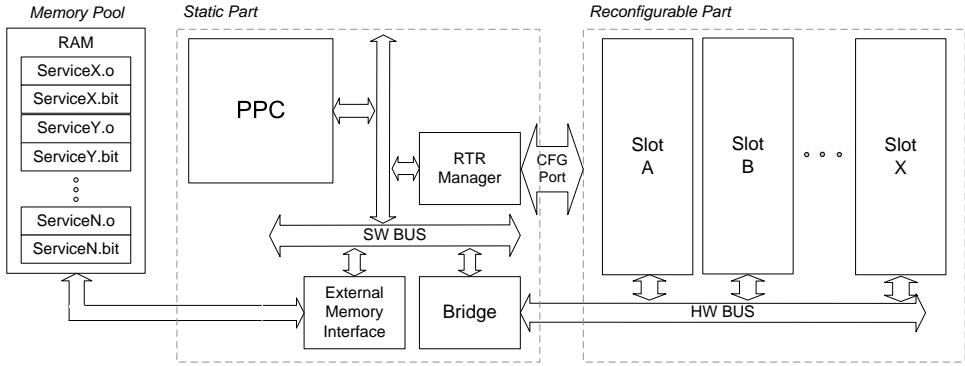

| 4.1. | System overview. . . . .                                                                     | 44 |

| 4.2. | Proposed microkernel based architecture. . . . .                                             | 45 |

| 4.3. | Call patterns experienced by an OS service. . . . .                                          | 47 |

| 4.4. | System architecture. . . . .                                                                 | 51 |

|                                                                                                                                                                                          |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1. System architecture highlighting the communication channels. . . . .                                                                                                                | 60  |

| 5.2. Sample of an OS component graph. . . . .                                                                                                                                            | 60  |

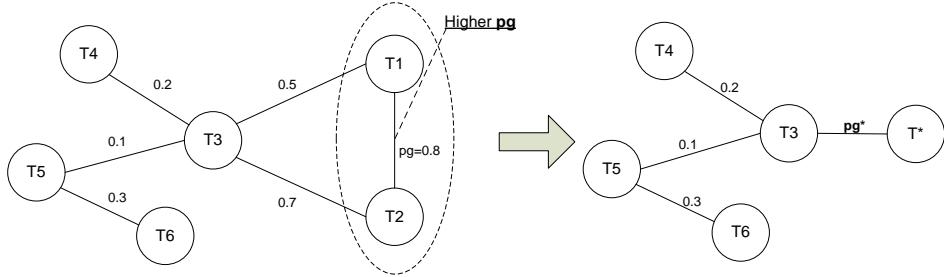

| 6.1. Example of two components being clustered. . . . .                                                                                                                                  | 71  |

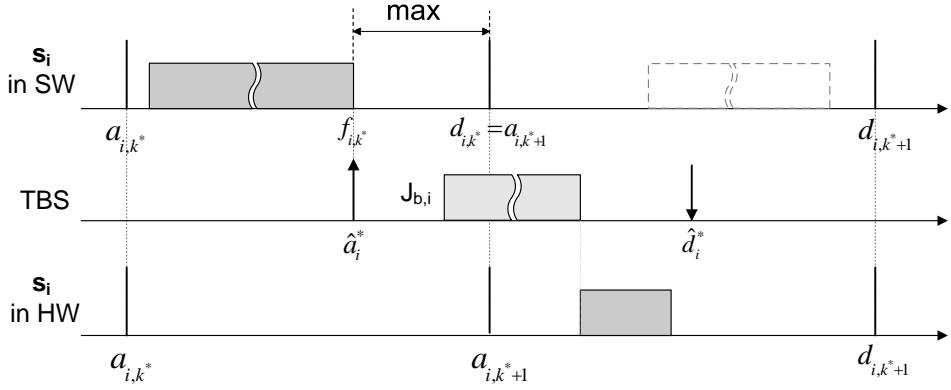

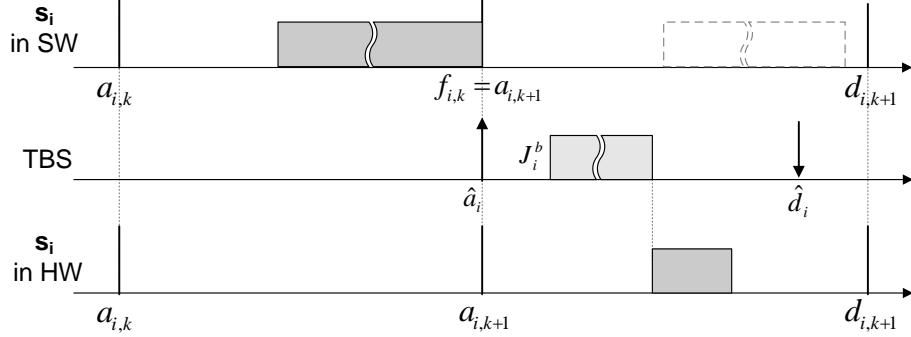

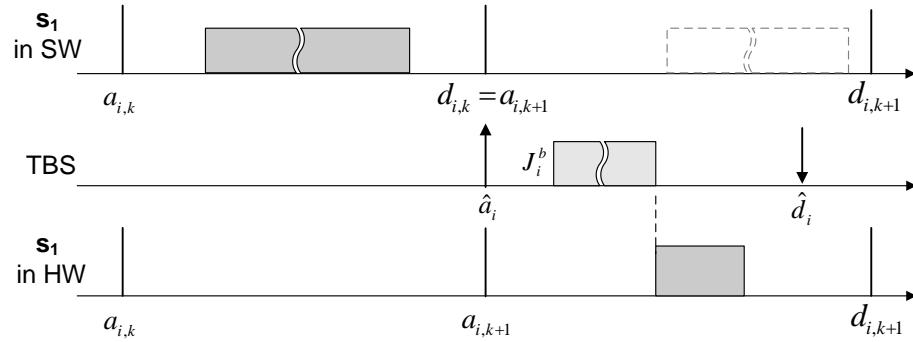

| 6.2. Optimal arrival time $\hat{a}_i$ for $J_i^b$ . . . . .                                                                                                                              | 76  |

| 6.3. Worst-case arrival time $\hat{a}_i$ for $J_i^b$ . . . . .                                                                                                                           | 76  |

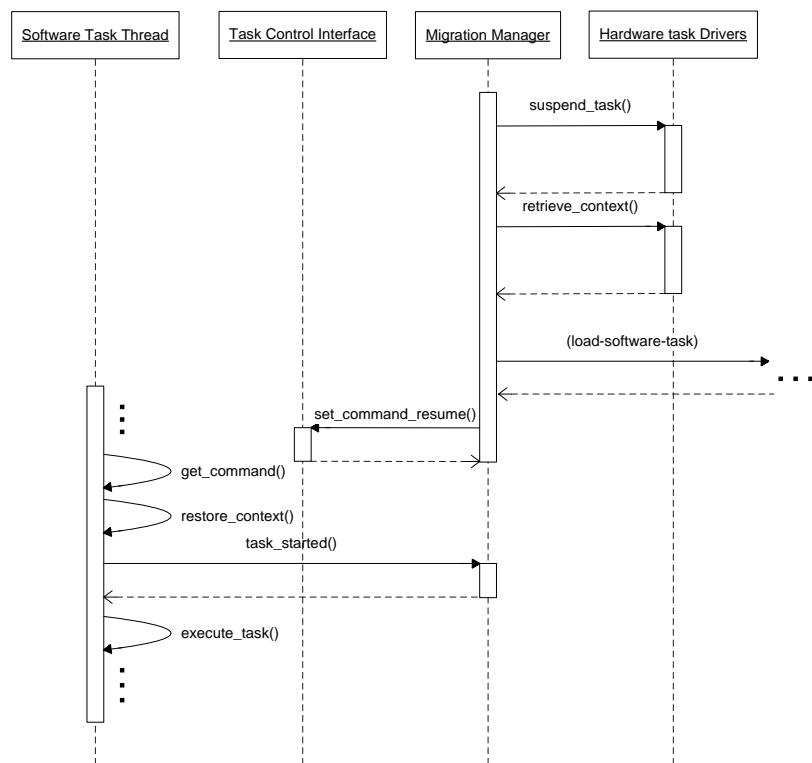

| 6.4. Migrating by preempting: software to hardware. . . . .                                                                                                                              | 79  |

| 6.5. Migrating by preempting: hardware to software. . . . .                                                                                                                              | 81  |

| 7.1. Unbalance average for different $\delta$ constraints. . . . .                                                                                                                       | 88  |

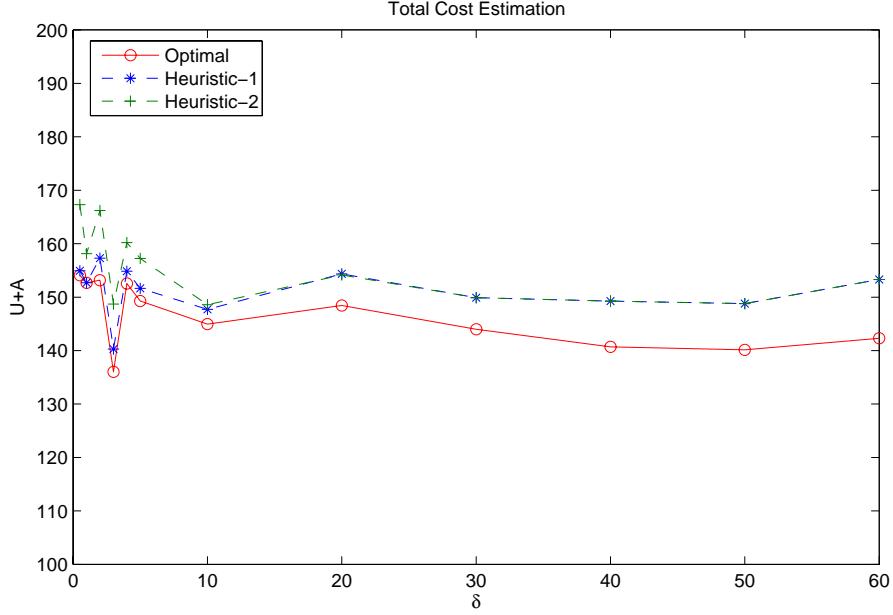

| 7.2. Total cost assignment average for different $\delta$ constraints. . . . .                                                                                                           | 89  |

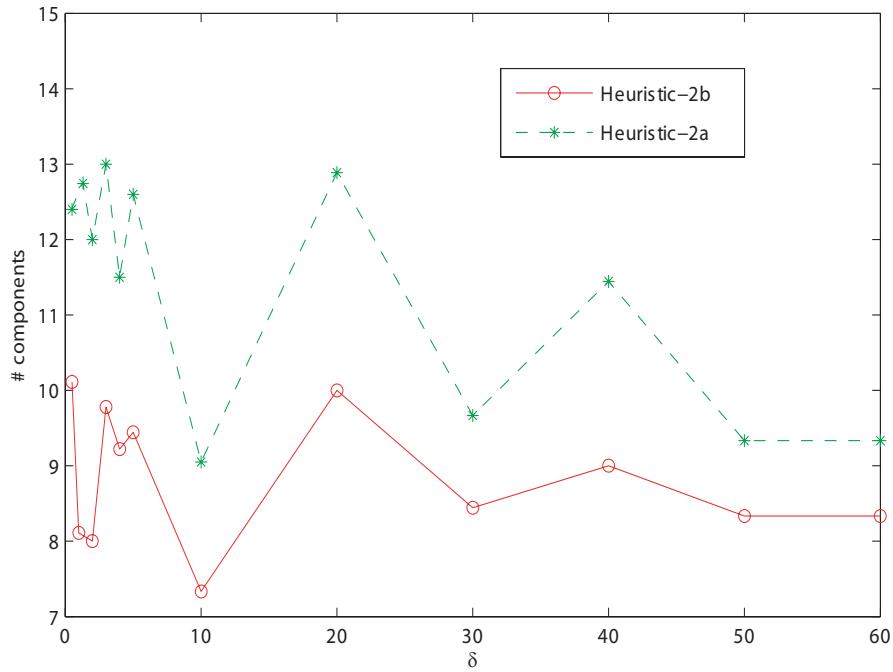

| 7.3. Number of components being reconfigured for different $\delta$ constraints.<br>Heuristic-2a: original balancing algorithm. Heuristic-2b: modified bal-<br>ancing algorithm. . . . . | 90  |

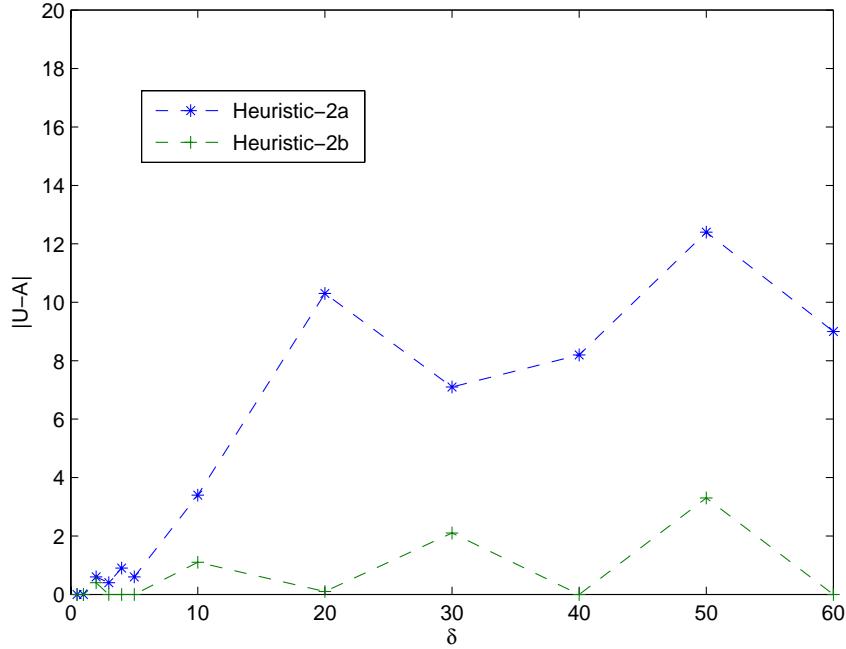

| 7.4. Unbalance average for different $\delta$ constraints. . . . .                                                                                                                       | 91  |

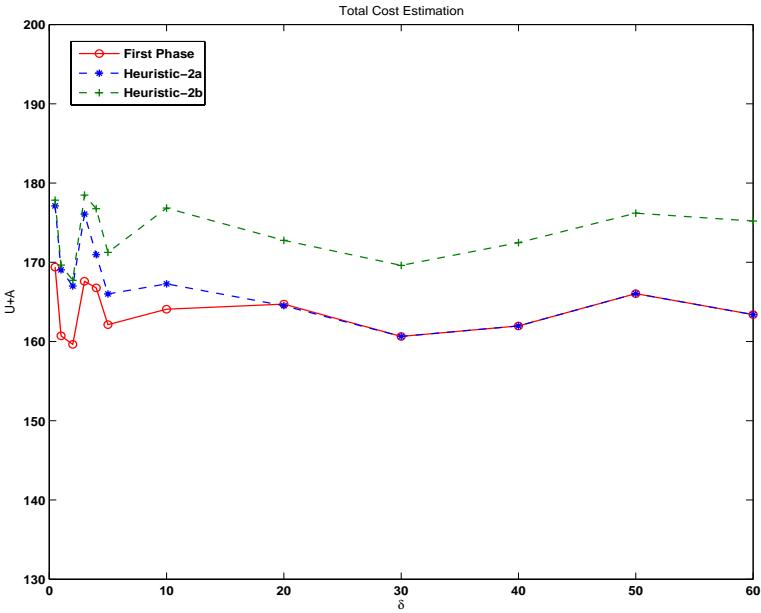

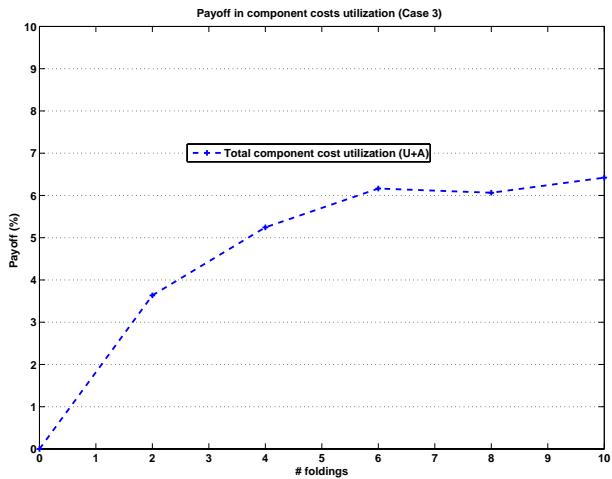

| 7.5. Payoff in $U+A$ due to the balancing algorithm modified for reconfigura-<br>tion costs reduction. . . . .                                                                           | 92  |

| 7.6. Component reconfiguration scheduling: heuristic algorithm evaluation. .                                                                                                             | 93  |

| 7.7. Evaluation results comparison. . . . .                                                                                                                                              | 94  |

| 7.8. Payoff in overall resource usage due to clustering process. . . . .                                                                                                                 | 95  |

| 8.1. Virtex-II Pro hardware/software interface. . . . .                                                                                                                                  | 98  |

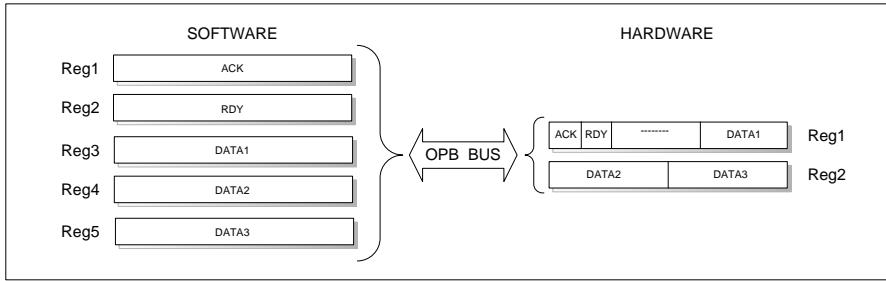

| 8.2. Mapping between physical and virtual registers. . . . .                                                                                                                             | 99  |

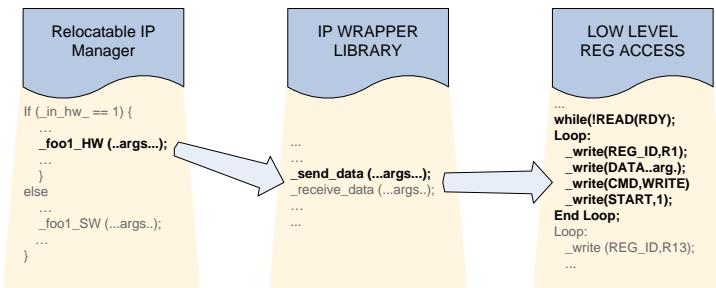

| 8.3. A method <code>foo1_HW</code> build upon library calls. . . . .                                                                                                                     | 101 |

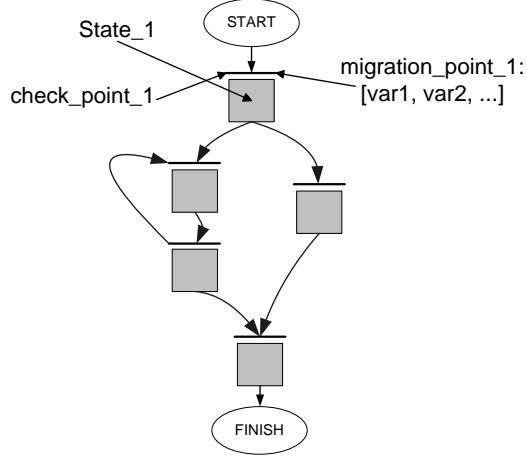

| 8.4. State transition graph representation of a relocatable task. . . . .                                                                                                                | 103 |

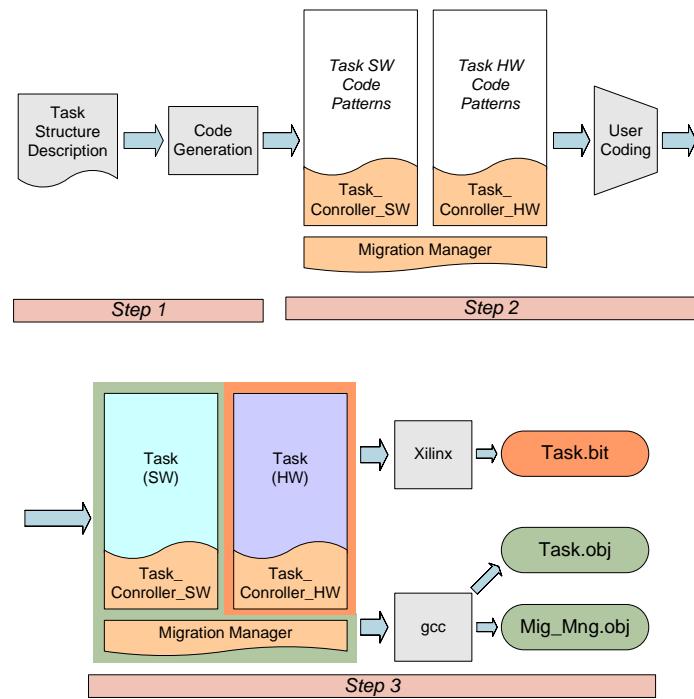

| 8.5. Design flow supported by the framework. . . . .                                                                                                                                     | 104 |

| 8.6. Informal description of TSD. . . . .                                                                                                                                                | 105 |

| 8.7. Hardware task overview. . . . .                                                                                                                                                     | 107 |

| 9.1. Triple-DES and its basic DES cipher block. . . . .                                                                                                                                  | 112 |

| 9.2. CBC mode for block ciphers. . . . .                                                                                                                                                 | 112 |

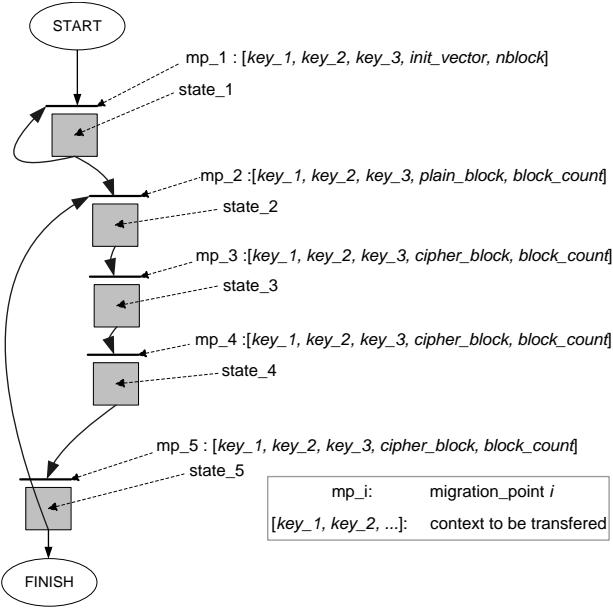

| 9.3. State transition graph corresponding to Algorithm 6. . . . .                                                                                                                        | 114 |

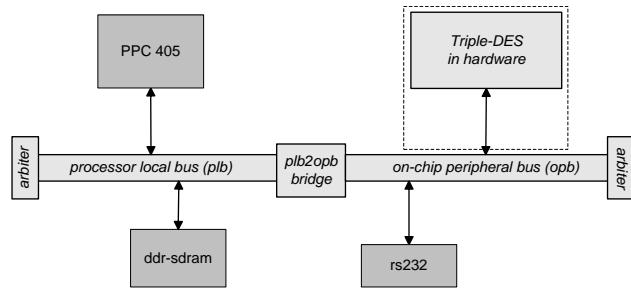

| 9.4. Basic hardware platform. . . . .                                                                                                                                                    | 115 |

| 10.1. System overview. . . . .                                                                                                                                                           | 122 |

| A.1. Comparison among communication costs reduction for three different sit-<br>uations. . . . .                                                                                         | 126 |

| A.2. Comparison among payoffs in overall resource utilization for three differ-<br>ent situations. . . . .                                                                               | 127 |

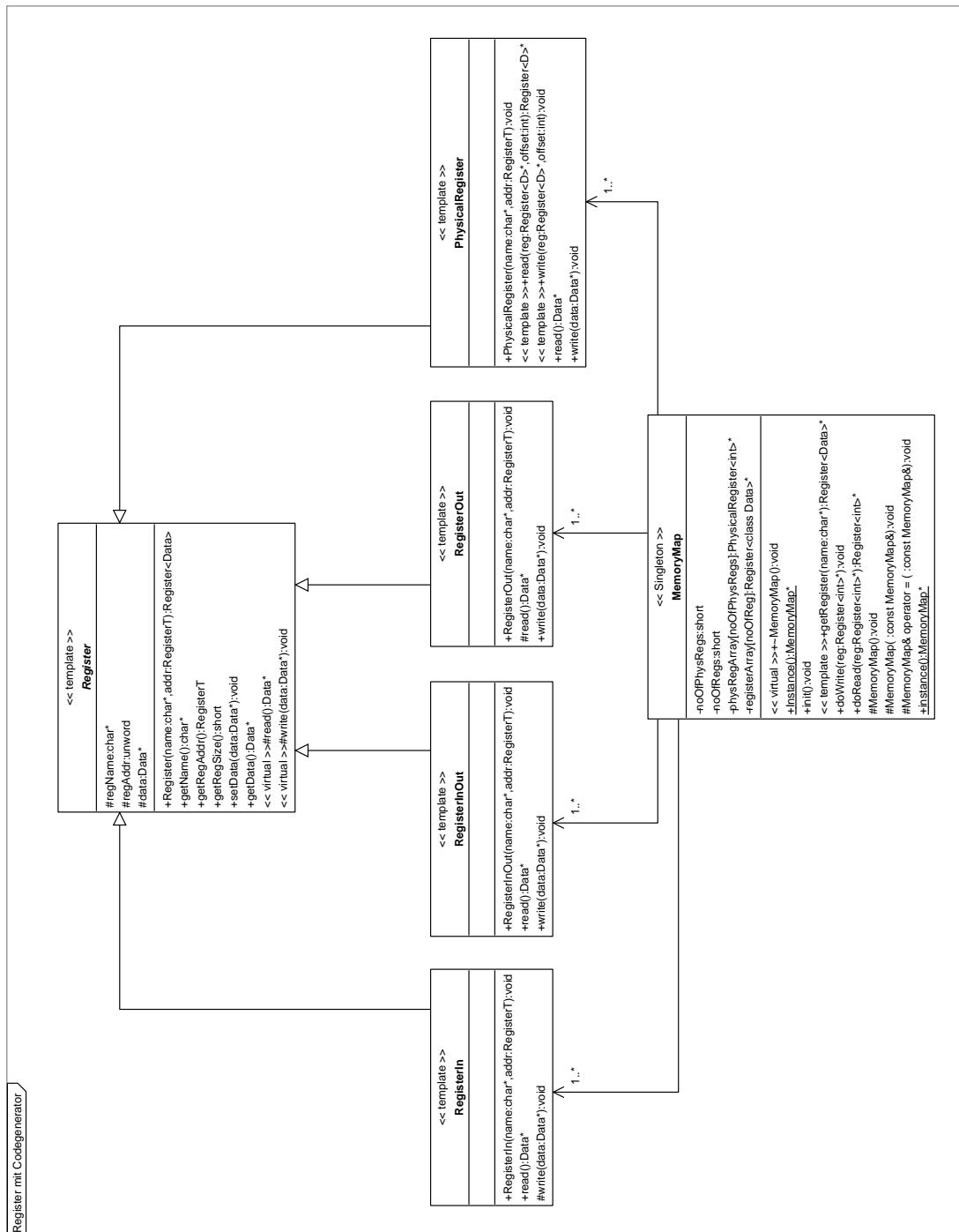

| B.1. Class Diagram of possible interface registers. . . . .                                                                                                                              | 130 |

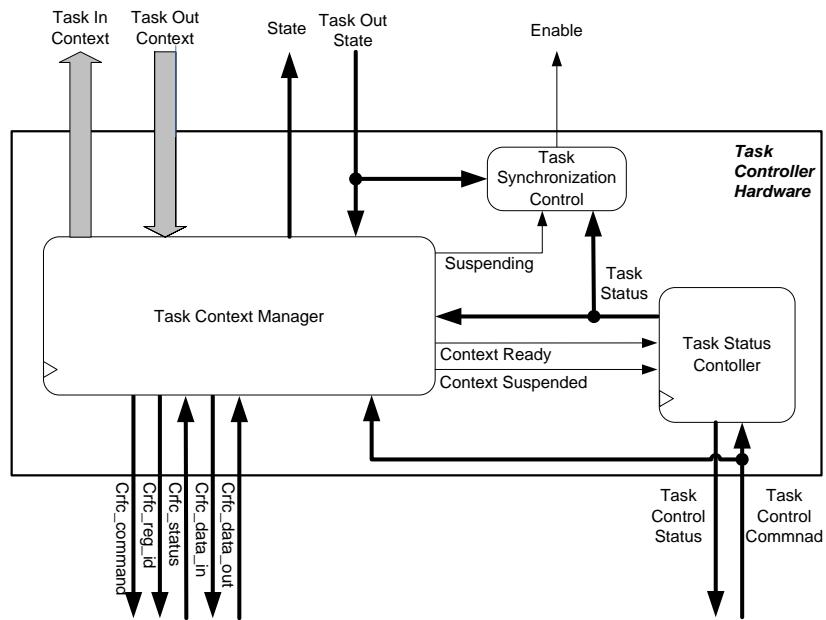

| C.1. The controller template for a hardware task. . . . .                                                                                                                                | 132 |

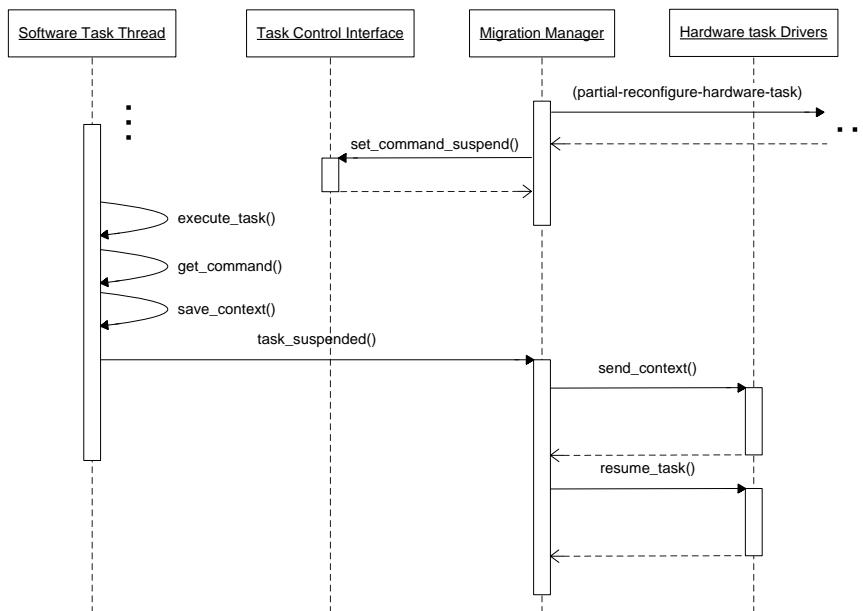

| C.2. Sequence graph specifying the task migration from software to hardware. .                                                                                                           | 132 |

|                                                                                      |     |

|--------------------------------------------------------------------------------------|-----|

| C.3. Sequence graph specifying the task migration from hardware to software. . . . . | 133 |

| D.1. Relocation from software to hardware: An Example. . . . . . . . . . .           | 135 |

---

## List of Tables

---

|      |                                                                                                                  |     |

|------|------------------------------------------------------------------------------------------------------------------|-----|

| 3.1. | OS classification according to the reconfiguration <i>Time</i> and <i>Initiator</i> . . . . .                    | 24  |

| 5.1. | Different allocation possibilities for two services, and the respective overall cost and balance values. . . . . | 57  |

| 5.2. | Time costs related to each migration case. . . . .                                                               | 58  |

| 5.3. | Service definition related to its periodic execution. . . . .                                                    | 59  |

| 6.1. | Example of three components and their respective costs. . . . .                                                  | 65  |

| 6.2. | Assignment algorithm applied in the example presented in Table 6.1. . . . .                                      | 66  |

| 6.3. | Example of a complete OS service allocation. . . . .                                                             | 68  |

| 9.1. | FPGA and memory utilization. . . . .                                                                             | 116 |

| 9.2. | Context data transfer: average time measured. . . . .                                                            | 118 |

---

## List of Algorithms

---

|    |                                                  |     |

|----|--------------------------------------------------|-----|

| 1. | Service assignment heuristic. . . . .            | 65  |

| 2. | Heuristic for balancing $B$ improvement. . . . . | 67  |

| 3. | Improved heuristic for balancing $B$ . . . . .   | 69  |

| 4. | Partial schedule. . . . .                        | 84  |

| 5. | Whole schedule. . . . .                          | 85  |

| 6. | Triple-DES pseudo algorithm. . . . .             | 113 |

---

## List of Symbols

---

|                 |                                                                                                                     |

|-----------------|---------------------------------------------------------------------------------------------------------------------|

| $\mathcal{S}$   | Set of OS services                                                                                                  |

| $s_i$           | A generic OS service                                                                                                |

| $\mathcal{S}^*$ | Subset of $\mathcal{S}$ representing the OS services that will undergo a reconfiguration                            |

| $s_i^*$         | A generic OS service that will undergo a reconfiguration                                                            |

| $\mathcal{S}^s$ | Set of software services that will be changed by another software service ( $\mathcal{S}^s \subset \mathcal{S}^*$ ) |

| $\mathcal{S}^h$ | Set of hardware services that will be changed by another hardware service ( $\mathcal{S}^h \subset \mathcal{S}^*$ ) |

| $\mathcal{S}^w$ | Set of services that will change the execution domain ( $\mathcal{S}^w \subset \mathcal{S}^*$ )                     |

| $\mathcal{T}_s$ | Set of services located in software                                                                                 |

| $\mathcal{T}_h$ | Set of services located in hardware                                                                                 |

| $\mathbf{C}_1$  | Cost set of software services                                                                                       |

| $\mathbf{C}_2$  | Cost set of hardware services                                                                                       |

| $\mathbf{C}$    | Cost set of all OS services                                                                                         |

| $c_{i,j}$       | Cost of a service $s_i$ assigned to execution domain $j$ ( $j = 1$ : CPU; $j = 2$ : FPGA)                           |

| $A_i$           | Cost used by service $s_i$ when assigned to FPGA ( $c_{i,2} = A_i$ )                                                |

---

|                |                                                                                      |

|----------------|--------------------------------------------------------------------------------------|

| $U_i$          | Cost used by service $s_i$ when assigned to CPU ( $c_{i,1} = U_i$ )                  |

| $c_i$          | Hardware and software costs of a service $s_i$ ( $c_i = \{U_i, A_i\}$ )              |

| $l_i$          | Sum of $U_i$ and $A_i$ ( $l_i = c_{i,1} + c_{i,2}$ )                                 |

| $A$            | Total cost of OS services assigned to FPGA                                           |

| $U$            | Total cost of OS services assigned to CPU                                            |

| $B$            | Balance between FPGA and CPU costs                                                   |

| $w_1$          | Tendency of application resource utilization in CPU                                  |

| $w_2$          | Tendency of application resource utilization in FPGA                                 |

| $A_{max}$      | Maximum FPGA area cost available for OS services                                     |

| $U_{max}$      | Maximum CPU workload cost available for OS services                                  |

| $\delta$       | Balancing constraint: maximum allowed unbalance                                      |

| $\mathbf{X}_1$ | Assignment solution for software services                                            |

| $\mathbf{X}_2$ | Assignment solution for hardware services                                            |

| $\mathbf{X}$   | Assignment solution for all OS services                                              |

| $x_{i,j}$      | Assignment solution of a service $s_i$ at execution domain $j$                       |

| $x_i$          | Assignment solution for a service $s_i$ ( $x_i = \{x_{i,1}, x_{i,2}\}$ )             |

| $R$            | Complete system reconfiguration cost                                                 |

| $\mathbf{R}_i$ | Relocation matrix cost (3 x 3) of a component $s_i$                                  |

| $r_{i,j}$      | Cost to relocate a service from domain $i$ to domain $j$                             |

| $z_i$          | Assignment difference of a service $s_i$ between two different assignment solutions  |

| $\mathbf{Z}$   | Assignment difference set of services between two different assignment set solutions |

| $C^\alpha$     | Communication cost between two OS services, both located in software                 |

| $C^\beta$      | Communication cost between two OS services, both located in hardware                 |

---

|                          |                                                                                                         |

|--------------------------|---------------------------------------------------------------------------------------------------------|

| $C^\gamma$               | Communication cost between two OS services, each one located in a different execution domain            |

| $\kappa(u, v)$           | Communication costs between two OS services, $u$ and $v$ ( $\kappa = \{C^\alpha, C^\beta, C^\gamma\}$ ) |

| $(\lambda_1, \lambda_2)$ | Maximum resulted component cost that is allowed when clustering two OS services                         |

| $\mathcal{J}$            | Set of jobs needed to perform a system reconfiguration                                                  |

| $J_i$                    | A generic reconfiguration job associated to service $s_i$                                               |

| $J_i^a$                  | Configuration phase of a reconfiguration job $J_i$                                                      |

| $J_i^b$                  | Migration phase of a reconfiguration job $J_i$                                                          |

| $M^s$                    | “Migration” time of a component when changed by another component version at CPU                        |

| $M^h$                    | “Migration” time of a component when changed by another component version at FPGA                       |

| $M^w$                    | Migration time of a component when relocated between CPU and FPGA                                       |

| $Q^s$                    | Configuration (programming) time of a component at CPU                                                  |

| $Q^h$                    | Configuration (programming) time of a component at FPGA                                                 |

| $E^s$                    | Execution time of a component at CPU                                                                    |

| $E^h$                    | Execution time of a component at FPGA                                                                   |

| $P_i$                    | Period of service $s_i$                                                                                 |

| $D_i$                    | Relative deadline of service $s_i$                                                                      |

| $d_{i,k}$                | Absolute deadline of the $k$ th instance of service $s_i$                                               |

| $\hat{d}_i$              | Absolute deadline of migration job $J_i^b$                                                              |

| $a_{i,k}$                | Arrival time of the $k$ th instance of service $s_i$                                                    |

| $\hat{a}_i$              | Arrival time of migration job $J_i^b$                                                                   |

| $b_{i,k}$                | Starting (beginning) time of the $k$ th instance of service $s_i$                                       |

| $\hat{b}_i$              | Starting (beginning) time of migration job $J_i^b$                                                      |

$f_{i,k}$  Finishing time of the  $k$ th instance of service  $s_i$

$\hat{f}_i$  Finishing time of migration job  $J_i^b$

$\eta$  Computation ratio ( $0 \leq \eta \leq 1$ ) of a migration job

$\sigma$  Time distance between arrival times of a service and its related migration job  $J^b$

# CHAPTER 1

---

## Introduction

---

The presence of embedded systems is massive in our lives. It is possible to identify its usage in a great variety of products: cellular phones, Personal Digital Assistance devices (PDAs), household appliances (e.g., washing machines, microwave ovens, DVD players), vehicles, airplanes, missiles, medical equipments, etc.; only to cite some of them. Some numbers show that more than 99% of the microprocessors produced nowadays are devoted to embedded system platforms [1].

The design of embedded systems is complex and involves many interdisciplinary research areas, from high level modeling and simulation, through software, hardware and platform design to the hardware and software synthesis and testing [2]. Unlike a general-purpose computer, such as a Personal Computer (PC), the design of an embedded system is considerably more complex. Usually, when designing such system one needs to take into account requirements such as memory and power consumption, real-time behavior, short time to market, etc.

On the other hand, with technology advances, most of embedded system components can be incorporated into a single chip, leading to the so called System-on-Chip (SoC) [3]. One SoC may contain one or more CPUs, memory, peripherals and dedicated hardware components (e.g., coprocessors) specifically developed for a target application in order to meet the performance required by the application. These solutions, however, are usually static, meaning that adaptations and/or modifications due to application changes are not adequately supported.

A side effect of this integration is that contemporary embedded systems are increas-

ingly incorporating more and more functionalities, requiring thereby higher computation performance. Moreover, these systems are becoming multipurpose, since they need to support more than one application which may be different in their nature. For instance, modern PDA or mobile phones are capable to play movies, connect to the internet and make telephone calls among other activities. In addition, the algorithm complexity tends to increase in many application domains such as signal, image and processing control. Therefore, modern embedded systems are increasingly requiring more computational performance and flexibility due to the growing complexity and dynamics of the application domain.

In order to be able to handle this tradeoff between flexibility and high performance, an execution platform combining reconfigurable hardware and SoC becomes an attractive solution. This new platform is usually referred as Reconfigurable System-on-Chip (RSoC). A single RSoC based platform may provide different facilities. For instance, a product can change or upgrade its functionality by e.g., at initialization phase, loading different configuration data. This enables, further, to upgrade a product that has been already assembled, or even to correct some error identified in this product after delivering it to the market. Additionally, a RSoC based system may support run-time reconfiguration. This may even allow the creation of more complex systems, with capability to dynamically adapt to system changes.

## 1.1. Motivation

The duty of an Operating System (OS) is to provide the necessary abstraction of the hardware platform and provide services to the application, like for instance, message passing, shared resources management, etc. Given that the computational power and size (in terms of components integration) of nowadays SoC are rapidly increasing, the utilization of an OS is also gaining in importance. An OS eases programming activities by providing well defined interfaces to the underlying execution platform, hiding thereby low level details from programmers. Furthermore, it enables the portability, reusability and protection among applications. Actually, the reasons of using an OS for a SoC are not different from those for running an OS on any system [4].

The demand of an OS is more emphasized in the case of platforms based on RSoC. Due to the aggregated overhead caused by the reconfiguration activities, and management of the shared reconfigurable hardware (dynamic reconfiguration), the support given by an OS is highly desired. The OS executing on such platforms needs to provide suitable methods and infrastructure for managing and using the resources in an efficient manner.

The design of a SoC architecture is application dependent. Due to the necessity to reduce costs, power consumption, etc, it is required to provide an architecture only with those components that a specific application will require. Since an OS also uses resources from the execution platform, it is also desirable to have a modular OS. Thus, the software

designer may tailor the OS to provide only the required services that an application needs. These solutions, however, are usually static.

Since applications of modern embedded systems do present dynamic behavior (e.g., the PDA example mentioned above), imposing thereby dynamic requirements to the OS, those static solutions are no longer efficient. For such scenarios, the presence of an OS capable to be dynamically reconfigured is highly desirable, in order to provide only the current facilities required by the application and, thereby, using the resources in an efficient manner.

## 1.2. Thesis Goals

A typical RSoC architecture includes a CPU and reconfigurable hardware as main computational resources, which are shared between application and OS activities. Towards an optimal usage of the available resources, the RTOS should be able to reconfigure itself over the underlying hybrid architecture.

In this direction, this thesis aims to provide methodologies, strategies, mechanisms, as well as hardware and design support, which aggregates self-reconfiguration capabilities to an embedded operating system. By this means, the used operating system can configure itself over the hybrid architecture in order to use the computational resources that are currently not being used by application programs, and similarly, freeing resources currently demanded.

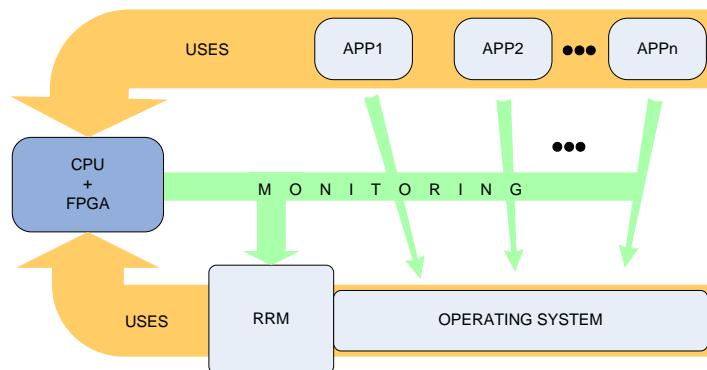

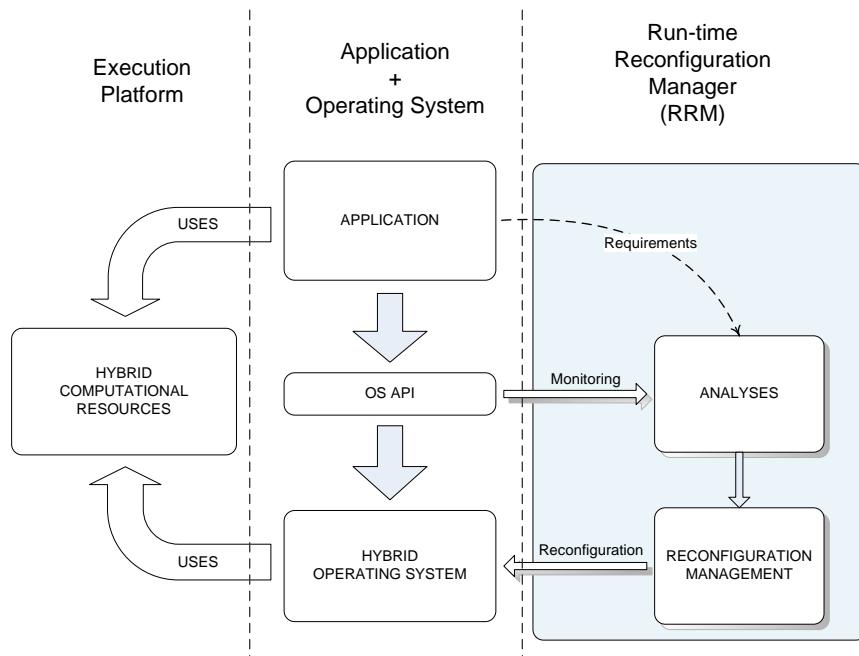

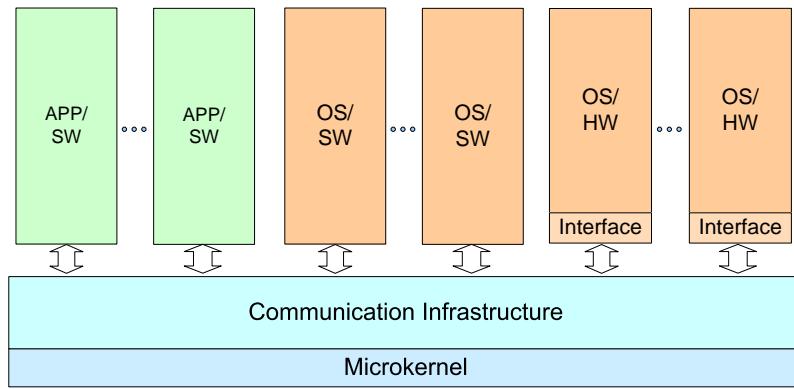

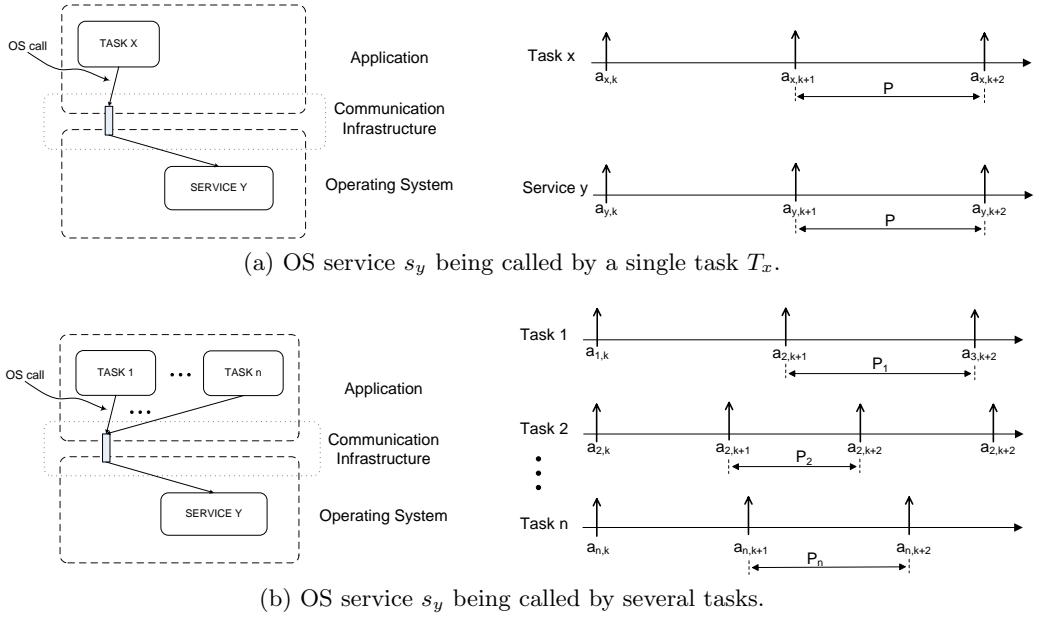

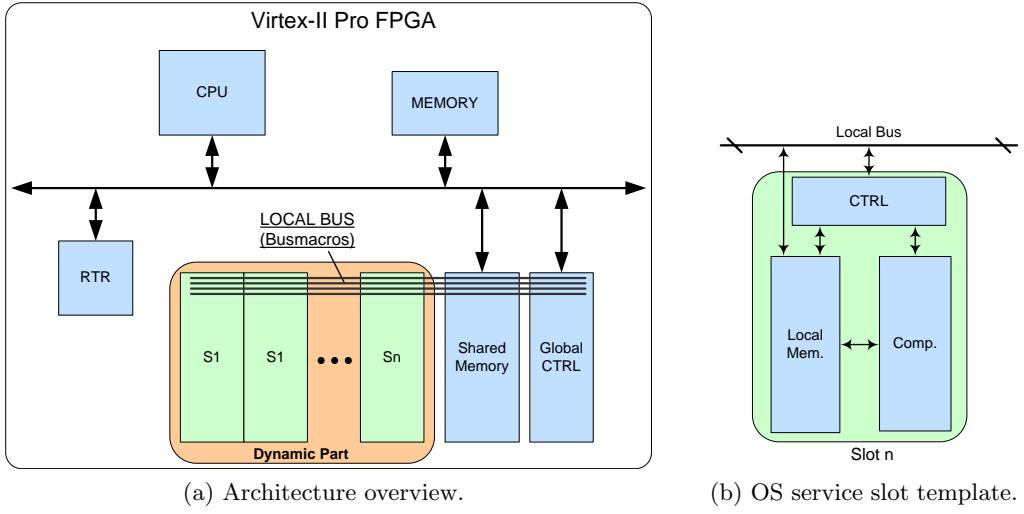

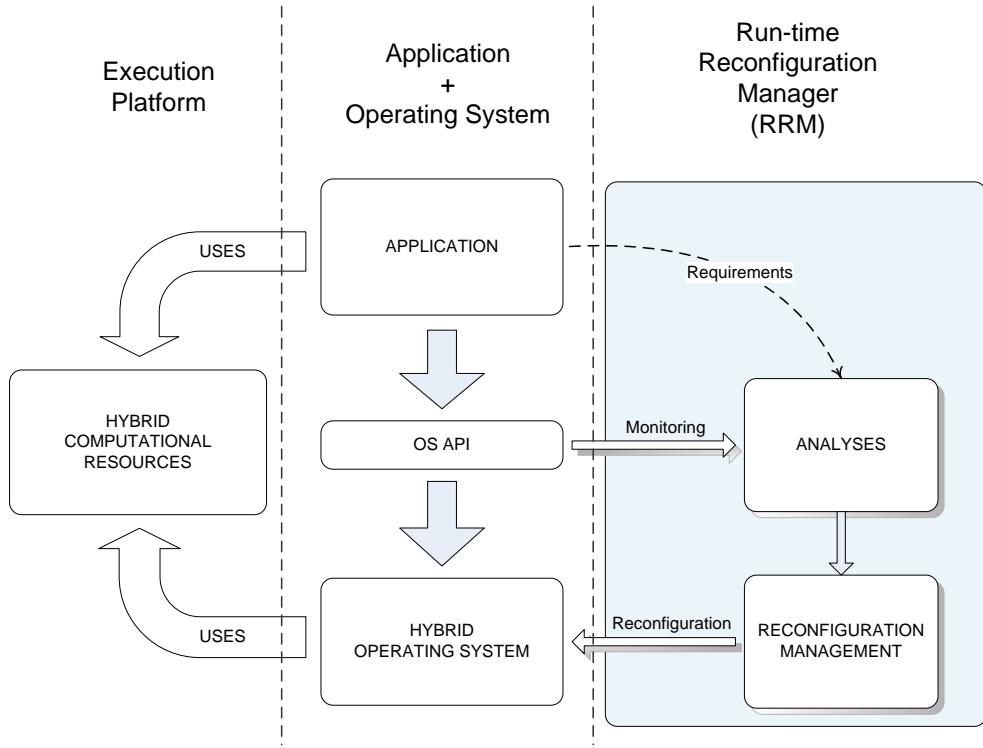

Figure 1.1 summarizes the idea of this thesis. An extra component in the system, called RRM (Run-time Reconfiguration Manager), monitors application requirements along with the current occupation of the execution platform. So, by continuously analyzing the overall resource utilization it coordinates the configuration of the OS services over the hybrid architecture.

Figure 1.1.: Reconfigurable OS for RSoC: Overview.

### 1.3. Thesis Contributions

The main contribution of this thesis is the development of strategies and methodologies comprising an OS extension that can be aggregated to a real-time operating system running under a hybrid execution platform enabling, thereby, an effective usage of the computational resources by application tasks as well as by OS services. Such OS is well adequate for given support to the modern and future embedded systems, relying on execution platforms with high flexibility and performance.

All main parts of this thesis have been published in several conferences, which demonstrate the recognition of this work by the research community. Moreover, it indicates the relevance of the investigations carried out in the scope of this thesis research.

The raw proposal and concept of a reconfigurable OS for RSoC has been published in [5]. Then, in [6] a more sound proposal for an execution platform is presented along with heuristic algorithms for allocation of OS services over this hybrid platform. Later on, in [7, 8] those algorithms were improved in order to decrease the reconfiguration overhead. A further extension to the allocation algorithms, in order to take into account the communication costs of OS components depending on their allocations, has been presented in [9].

Appropriated model and strategies used to assure a deterministic reconfiguration of OS services on the hybrid platform were firstly presented in [10] and then extended to cover all aspects of this thesis in [11]. In addition, a framework and additional infrastructure to support the design of relocatable components was presented in [12], [13] and [14].

The use of the proposed OS adaptation mechanisms and strategies in self-optimizing systems is presented in [15, 16]. Furthermore, an overview of the overall proposal was published in [17] and recently accepted for journal publication [18].

### 1.4. Thesis Outline

This thesis is organized as follows:

**Chapter 2** provides theoretical background information, necessary for a clear understanding of the topics discussed in the subsequent chapters.

**Chapter 3** summarizes relevant related work. It includes a survey on (re)configurable operating systems based solely in software, filtering those ones intended for embedded systems domain. Then, several aspects related to reconfigurable computing and the proper and adequate support of an operating system for such systems is largely discussed. Comparisons between those works and the subject of this thesis are left to the end of the chapter.

**Chapter 4** discusses in more details the ideas briefly introduced in Section 1.2. Herein,

target applications are carefully specified. In addition, the target OS, which will be used in the validation phase of this work, as well as the reasons for choosing it, are presented. Furthermore, the execution platform is introduced in this chapter along with the related design assistance requirements.

**Chapter 5** presents the models adopted for the execution platform, the OS components, and the reconfiguration activities. Additionally, the main problems that the Runtime Reconfiguration Management (RRM) needs to solve are here formulated.

**Chapter 6** introduces the methodologies and strategies adopted by the RRM to deterministically manage the allocation and reconfiguration of the OS services over the hybrid architecture. These strategies are mainly based on low complexity heuristic algorithms proposed to solve NP-Hard problems faced by RRM, which further need to be executed concurrently with the normal system operation.

**Chapter 7** evaluates each heuristic algorithm presented in the previous chapter. For that purpose, the MATLAB tool was used. Results are analyzed according to algorithm efficiency, pointing out where further research need to be spent to solve some open questions.

**Chapter 8** describes the support made available to the programmer to enable the usage of the proposed system, covering thereby two aspects. First, the automatic generation of hardware-software interface using the IFS [19] (Interface Synthesis) tool is explained. Second, a framework for generation of hybrid services/tasks that enables their run-time relocation between CPU and FPGA is presented.

**Chapter 9** shows a case study used to validate the proposed reconfiguration strategies, the design support proposed, and to analyze the effectiveness of the underlying architecture in carrying out the reconfiguration activities. As a target OS service, an encryption algorithm was selected, which is an OS service (for both, embedded and non embedded systems) increasingly demanded by safety and security applications.

**Chapter 10** gives a synopsis of the work presented in this thesis. Furthermore, it signals directions on which further work can be conducted.

# CHAPTER 2

---

## Background

---

This chapter gives the reader the necessary background information for a complete understanding of the technical discussions in the following chapters. Fundamentals of Reconfigurable Computing and the mainly used hardware technologies are presented.

### 2.1. Embedded System Design

Traditional embedded systems, those existing until middle of nineties, could be specified as a system comprising a microcontroller, memory, analog devices and some I/O signals. Nowadays, due to technology advances and also with the increasingly requirements from applications supported by contemporary embedded systems, they became more complex, which have a direct impact on the design of such systems.

Unlike a general-purpose computer, such as a Personal Computer (PC), the design of an embedded system is considerably more complex. It is an interdisciplinary activity, involving many research areas. It goes from abstract level modeling and simulation, through software, hardware and platform design to the hardware and software synthesis and testing [2].

Besides low cost and tight time to market, other constraints, like for instance the limited amount of memory available, low power consumption requirement, etc, make the design of such a system a challenge. Furthermore, the fact that a single “standard” execution platform for an embedded system does not exists (differently, for instance, from the situation of PC market) increases even more the degrees of freedom by searching complete

solution for an embedded system.

Contemporary embedded systems are further integrating more and more functionalities and requiring, therefore, higher computation performance. With technological advances most of system components can be incorporated into a single silicon die leading to a so called System-on-Chip (SoC) [3]. One SoC may contain one or more CPUs, memory, peripherals and dedicated hardware components (e.g., coprocessors) specifically developed for a target application. A SoC offers more advantages and benefits to system designers such as for instance, higher performance, lower power consumption, and higher reliability, if compared with the case where a system is build by assembling various chips and components on a circuit board.

Another trend in the development of execution platforms for embedded system is towards multiprocessor architectures. Due to constraints in power consumption and increasing demand in performance, some solutions in integrating multiple processors in a single die are being currently investigated. Examples are Multi-Processors System-on-Chip (MPSoC) and Network-on-Chip (NOC) systems [3].

Even for normal PCs this trend is observed (for instance, the Dual Core processor from Intel [20]), or even in graphic cards used inside such architectures. Recently, NVIDIA company released the G8 graphic chips where multithreading is used as based environment for the application design (for more details see [21] and [22]).

Another example is the Cell Multiprocessor [23], which was developed to attend the demands of the game/multimedia industry. The Cell multiprocessor combines in a single die one 64bit based microprocessor with eight cooperative processors, all connected together through a high bandwidth on-chip coherent bus.

## **Hardware/Software Codesign**

A typical SoC architecture is based on hardware and software components, and the decision of which parts will be developed in hardware and which in software is one of the most important parts by designing an embedded system execution platform [24]. Hardware/Software codesign defines some methodologies and strategies for designing heterogeneous (hardware and software) systems. The goal is to find an efficient solution for a system which meets the specified requirements and constraints. In this process, it is important to have a unified model environment, which allows the co-simulation and co-verification of hardware and software parts together. A considerable amount of work has been done in this area: [25], [26], [27] and [28].

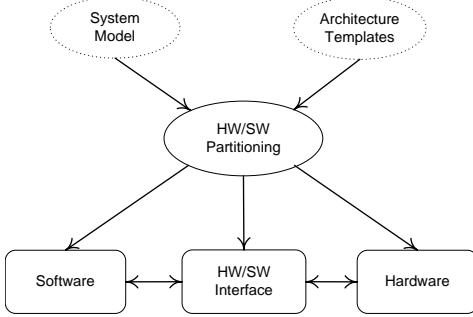

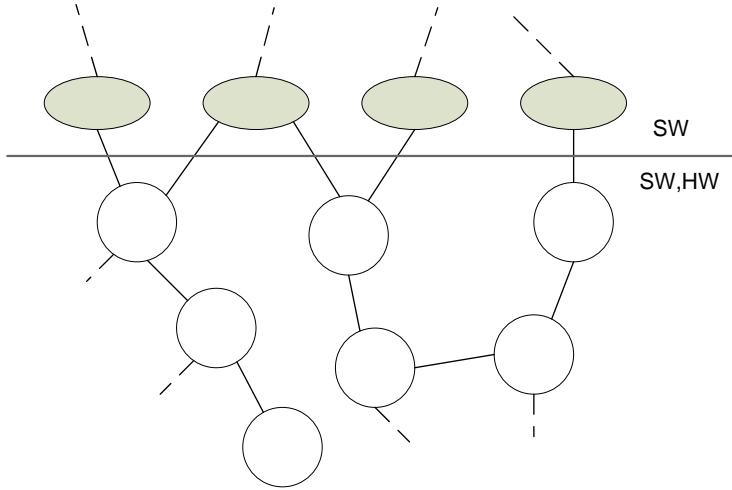

One key part of the hardware-software codesign, shown in Figure 2.1, is the hardware-software partition and the correspondent interface synthesis. The partition phase is not a trivial task. Even though there are some tools which do this in an automatic way, this activity is done also manually [29]. Nowadays, the partition of the system in hardware and software is influenced mainly by the designer experience and also by the availability

of previously designed and used architectures (also known as architecture templates). Moreover, due to the market pressure, there is a need to deliver a product as soon as possible, which also decreases the development costs. This short time-to-market also emphasizes the reusability of hardware and software components in the design of new embedded system architectures.

Figure 2.1.: HW/SW partitioning scheme.

Another important aspect of hardware/software codesign is the generation of an interface between hardware and software components. This phase is commonly left to the end part of the design flow, mostly due to the lack of properly abstraction of HW/SW interfaces, which makes difficult the dialog between software and hardware design teams. This problem is highlighted even more in new architectures that are becoming multiple and heterogeneous multiprocesssing. Therefore, a hardware/software interface codesign [30] is necessary in order to tackle the complexity of designing SoC architectures in the near feature.

## 2.2. Reconfigurable Computing Overview

As previously mentioned, the required application performance is achieved by implementing the computational intensive functionalities in a dedicated device, usually referenced as a hardware accelerator. If, for instance, a hard-wired technology is used then an Application Specific Integrated Circuit (ASIC) is designed and fabricated specially for the purpose of this specific application.

Although an ASIC could perform very well when executing the exact computation for which it was designed, it does not provide flexibility. In order to change the computation performed inside an ASIC, re-design and re-fabrication are necessary. A microprocessor, in an opposite way, offers great flexibility, since its functionalities are determined by the software instructions stored in the memory. In terms of efficiency, however, a microprocessor is by far inferior to an ASIC, since the computation is executed sequentially.

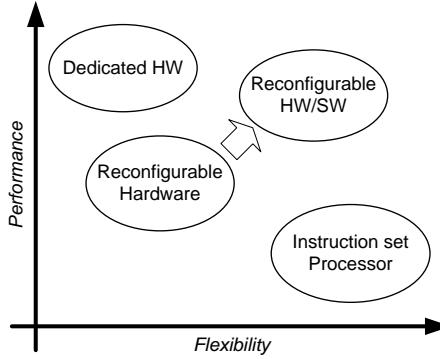

Reconfigurable systems may fill the gap between application-specific platforms based on custom hardware functions, and software programmable systems based on traditional

microprocessors [31]. The resulting system is one which can provide higher performance by implementing custom hardware functions in reconfigurable units, and still be flexible by reprogramming the hardware and/or a microprocessor (hybrid architectures). Figure 2.2 shows the trade off between performance and flexibility related to software, hardware and reconfigurable computing.

Figure 2.2.: Performance versus Flexibility tradeoff.

A reconfigurable hardware (RH) is very attractive for designing execution platforms for modern embedded systems. One motivation is the reduction of the Non-Recurring Engineering (NRE) costs, since the same hardware architecture may be used for more than one product. Even the same product can be provided by a company with several variations by reprogramming the hardware and software. Furthermore, the post-manufacturing programmability allows upgrades or corrections of problems when the product has been already finished.

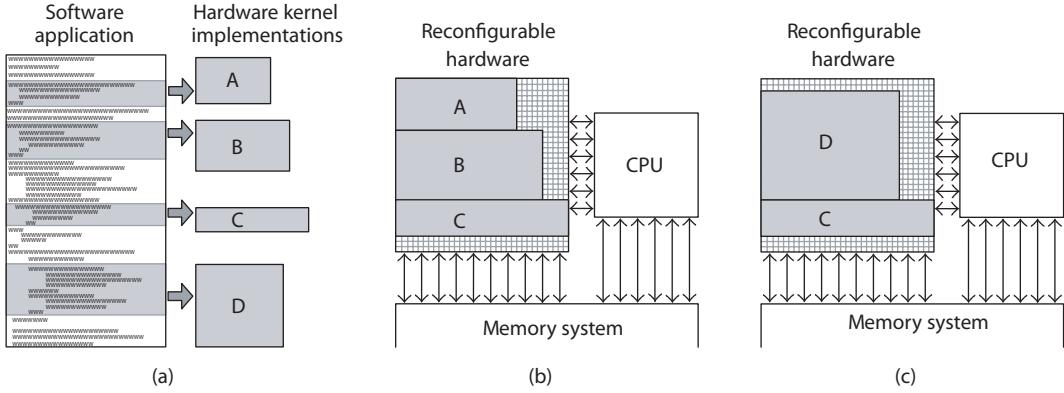

Execution platforms based on RH may also be dynamically reconfigured, allowing the dynamic adaptation of the system to the run-time environments [32]. Flexibility can be added to the architecture by dynamically allocating different and dedicated processing operators within the reconfigurable device. It also allows a configuration larger than the available RH to be used (virtual hardware concept). This improves the resource utilization by sharing the hardware between various applications.

The Figure 2.3 illustrates an example scenario where computations A, B, C and D are accelerated by the RH [33]. After finishing the execution of A and B, the computation D can replace them in the RH. Depending on the hardware support, computation C may be kept running while the reconfiguration happens. Such platforms require, however, more attention on the management and control.

There are two main challenges by following this approach. First, the kernel candidates to be implemented in hardware need to be mutual exclusive in their execution (no concurrency). This is also true for hardware devices that comport more than one kernel. However, in this cases the mutual exclusivity need to be assured among the kernel sets. To find a solution for these problems, techniques known as temporal and

Figure 2.3.: Example of dynamic reconfiguration usage [33].

spatial partitioning [34, 35] are used. The second challenge is to provide a well designed infrastructure, which needs to provide efficient methods to, e.g., swap in and out the configurations on the RH, keep track of data exchanged between configurations, schedule the configurations, etc.

### 2.2.1. Coupling CPU and Reconfigurable Hardware

A reconfigurable architecture appears normally in form of a CPU connected with a RH. The coupling type has a strong influence in the communication costs between CPU and RH. Furthermore, certain connection types require that the CPU is specially designed to be connected with the RH (non standardization).

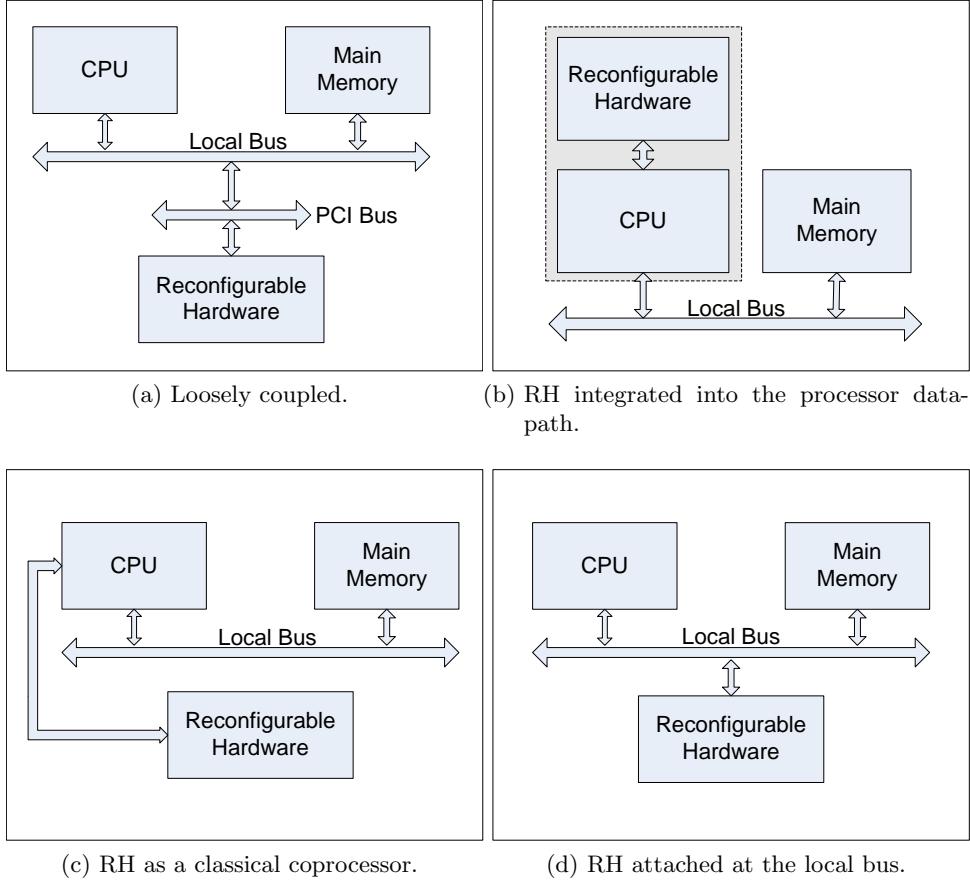

Figure 2.4 shows four different types of connections. In a really tightly coupled architecture (Figure 2.4b) the RH is deeply integrated with the CPU, so that it belongs to the processor data-path. The RH may also be connected with the CPU in the form of a classical coprocessor as presented in Figure 2.4c. In a middle connected architecture, the RH is plugged to the CPU through a local bus, as in Figure 2.4d. This can be seen also as an extended version of a coprocessor, since the RH may be accessed by the CPU using memory mapped technique. However, such architecture may also be used as an execution platform for a multiprocessing system. In loosely coupled architectures (Figure 2.4a) the RH is attached to the CPU through an external bus (like PCI) which is also an usual solution for a system architecture.

### 2.2.2. Reconfigurable System Design

Event though the usage of reconfigurable hardware in embedded systems is increasing [33], there is no standard method to design such system yet. Instead, there are proposals which are based on the extension of the traditional hardware/software codesign methods

Figure 2.4.: CPU and RH: Coupling types.

[36, 37], and their differences concentrate on the hardware-software partition phase.

However, the design of such system is even more complex than the traditional one due to the necessity to evaluate the temporal and spatial utilization of the reconfigurable hardware (which is considered as a shared resource), configuration overhead, communication infrastructure, etc. Moreover, the new approaches rely on the usage of modeling languages, which allows the consideration of the reconfigurability aspects since the beginning of the design phase.

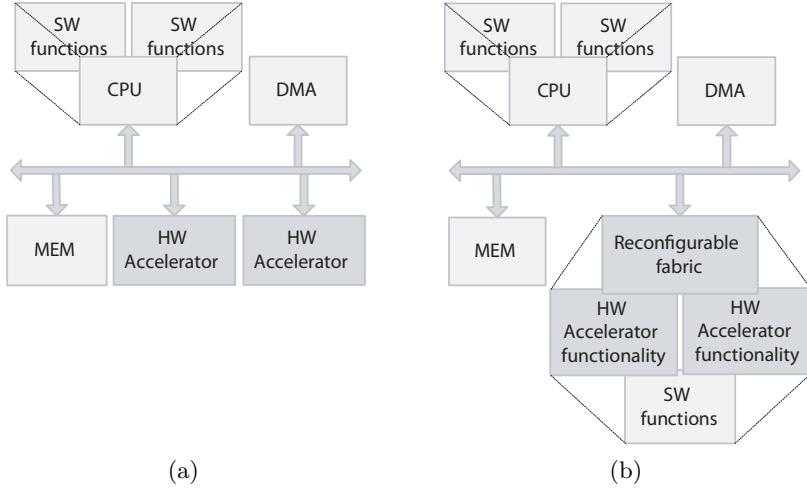

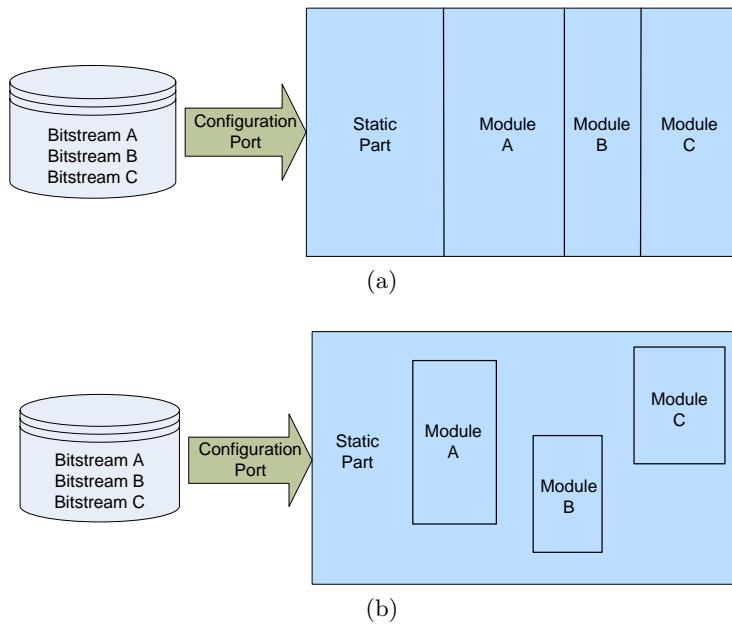

Figure 2.5 gives an idea about the differences at execution platform between SoC and RSoC. In Figure 2.5a HW accelerators are static components and in Figure 2.5b they are placed in the reconfigurable fabric according to its usage.

Figure 2.5.: Typical SoC architecture (a) and a RSoC architecture (b) [38].

## 2.3. Reconfigurable Hardware Technology

An execution platform for a reconfigurable computing application is based typically on a Field Programmable Gate Array (FPGA), which is a two-dimensional grid of configurable logic cells, called Configuration Logic Blocks (CLBs). These blocks are embedded in a general routing structure (also configurable) which allows their interconnections (inputs and outputs of each CLB). This architecture, shown in Figure 2.6a, supports a construction of a relatively arbitrary interconnection scheme between the logic blocks in the system.

Figure 2.6.: FPGA comprises a set of CLBs.

Each CLB can implement a distinct and limited logic function. A very simplified structure of a CLB is shown in Figure 2.6b which contains a 4-input Look-Up Table (LUT)<sup>1</sup>, a Multiplexer (MUX) and a storage element (flip-flop). A real CLB available in the modern FPGAs usually comprises more than one of such logic blocks and more signals for controlling, allowing the implementation of complex logic circuits.

FPGAs currently represent the most popular and mature segment of RH technologies. Of special interest are the SRAM-based FPGAs, which are the state-of-the-art in FPGA technology. The configuration (CLBs and interconnect resources) are stored internally on a static RAM. Changing the content of the configuration RAM will also change the resulting circuit running on the FPGA.

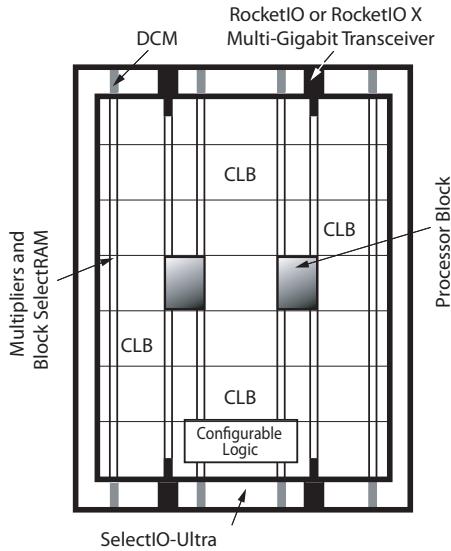

### 2.3.1. Hybrid Architecture

Meanwhile there are FPGA fabrics which incorporate a processor core. Figure 2.7 shows the structure of a Virtex-II Pro FPGA used in this work. This FPGA (as well as Virtex4, from the same company) is equipped with up to four hardcores PPC405 processors, signifying also that RH and CPU are located in the same device. With these devices, it is possible to design sophisticated architectures, where even more than one RH component may be connected with the CPU. This provides more flexibility when designing Reconfigurable SoC (RSoC) execution platforms.

Figure 2.7.: Virtex-II Pro architecture overview [40].

If a processor core is needed and not available in a FPGA, like the Virtex and Spartan3 FPGA families, one can use a softcore processor. An example available from Xilinx

<sup>1</sup>A LUT implements a combinatorial logic by storing a function truth table.

company is the so called MicroBlaze, which is a softcore processor based on RISC architecture. This processor even allows the integration of accelerators, designed inside the FPGA, to the processor data-path [41].

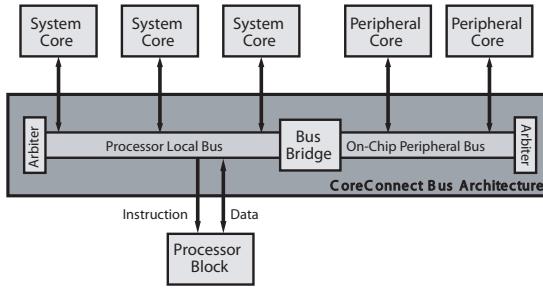

In order to help the design of embedded systems based on such hybrid devices, a design tool called EDK (Embedded Development Kit) is made available by the FPGA Company. The architecture advised and supported by this tool, when using the hardcore PPC405, is shown in Figure 2.8. The processor block is connected to the other components through the CoreConnect™ bus architecture, composed by two main buses: Processor Local Bus (PLB) and On-chip Peripheral Bus (OPB). Slow peripherals should be attached to the OPB bus in order to offload the PLB bus, which provides low latency access to peripherals requiring high performance.

Figure 2.8.: CoreConnect block diagram [40].

Other FPGA manufactures provide similar solutions in their products as well. For instance, Altera offers the Stratix II<sup>2</sup> and Cyclone II<sup>3</sup> devices, which allow the usage of NIOS softcore processors. Also ATMEL have an architecture for dynamically reconfigurable SoC, called FPLSLIC (AVR processor and FPGA) [42]. Nonetheless, the background information given in this work is concentrated on FPGAs manufactured by Xilinx Company. This device was chosen for implementation purpose, since not all FPGAs support a specific feature called dynamic partial reconfiguration (discussed in Section 2.3.3).

### 2.3.2. Configuration Techniques

A FPGA configuration is performed by downloading a bitstream<sup>4</sup> through a specific configuration port. This can be done offchip assisted by an extra component connected to the FPGA configuration port (for details please refer to [40]). Alternatively, the configuration data can be downloaded by an internal FPGA entity (not available in all FPGAs), called ICAP (Internal Configuration Access Port), which is mainly used for partial reconfiguration approaches (Section 2.3.3).

<sup>2</sup>Available at: <http://www.altera.com/products/devices/stratix2/st2-index.jsp>

<sup>3</sup>Available at: <http://www.altera.com/products/devices/cyclone2/cy2-index.jsp>

<sup>4</sup>A bitstream is a configuration data used to program the FPGA in a serial manner.

Furthermore, through the same port the present configuration on the FPGA can be read. This technique, called *Readback* operation, is used to verify the configuration on the FPGA and it is also used as a main technique to provide basic support for multitasking on FPGA (more details about this subject is given in Section 3.2.7).

### 2.3.3. Partial Reconfiguration Feature

Some FPGAs support partial reconfiguration. In these fabrics, part of the device can be reconfigured whilst the remaining part keeps its execution normally. This feature allows the implementation of multitasking systems based on reconfigurable devices. The FPGA is partially configured by downloading the related partial bitstream on the FPGA through the same port used for the case of a complete configuration. If the system wants to configure itself, the internal ICAP entity must be used.

Additionally, partial reconfiguration is a device dependent feature. Xilinx FPGAs are the few ones on the market with support to partial reconfiguration. Xilinx FPGAs with this feature goes from Virtex-4 devices to Spartan-3/E family. However, usually on these devices the partial reconfiguration is possible in a column-wise manner [43]. In these cases the device is divided into a number of columns. Each column spans vertically the chip (1D partition model) and it can be independently reconfigured without affecting the other columns (Figure 2.9a). Meanwhile, the release of new guidelines and design flows, like *Early Access Partial Reconfiguration* [44, 45] and other techniques from Xilinx shall allow a more flexible rectangle sizing (2D partition model) to be partial reconfigured on a device (Figure 2.9b).

An architecture designed to support partial reconfiguration is similar to the one presented in Figure 2.9. Usually, the FPGA device is divided in different parts. A static one related to the management of configuration data and the input/output data, and one or more parts which are reconfigured on-the-fly. The connections between the static and dynamic parts of the FPGA must be implemented by specific interconnect device resources. A known technique used is the so called *Busmacros* [43]. Therefore, all circuits implemented inside the dynamically reconfigurable parts of the FPGA must use the *Busmacros* wires to connect with other entities in the system.

The technical realization of such architectures are difficult due to the poor tool support and strong restrictiveness of the design guidelines [43]. Therefore, the partial reconfiguration feature is mostly used in academic research works. However, by recently improvement in the design support (like the [44] and [45] guidelines) and recently introduced design tools, which explicitly support a modular design approach (PlanAhead [46]), this feature is going to be used commercially as well. One evidence for that is the recently usage of partially reconfigurable FPGA based platforms for Software Defined Radio (SDR) SoC modems [47].

Figure 2.9.: Example of device partition for 1D (a) and 2D (b) partition models.

## 2.4. Chapter Conclusions

This chapter highlights the main features of reconfigurable computing and how it can contribute in improving the flexibility and performance for modern embedded system execution platforms. Additionally, the FPGA device has been introduced as being the mainstream technology in reconfigurable computing systems, keeping the focus on those FPGAs with support for partial reconfiguration. The investigations carried out in the scope of this work rely on this specific feature, which is still being improved by the FPGA vendors. Evidence for that are the availability of new tools and design flow guidelines (introduced in Section 2.3.3), which are intended to decrease the current difficult practicability of partial reconfigurable based platforms.

# CHAPTER 3

---

## Related Work Survey

---

This chapter starts giving a survey on reconfigurable operating systems conceived for software-only based architectures, concentrating on those ones envisioned for embedded systems domain. The intention thereby, is to figure out what are the trends and results already achieved in this research field.

In the sequence, important and relevant results related to operating system support *for* reconfigurable computing architectures, operating systems running *on* this architectures, and some new further approaches are presented. Along that, different aspects related to reconfigurable computing and the support required by an OS are covered, which concentrate on the interaction between CPU and reconfigurable hardware. Such a support may represent a simple driver as well as more sophisticated services that are required for managing the reconfigurable hardware in an abstract manner.

### 3.1. (Re)Configurable Operating Systems

An operating system with the ability to be reconfigured is not new and most OSs support it in one form or in another. The motivation for reconfiguration of an operating system is that by configuring it one can achieve customization of the OS to the application requirements, allowing system upgrade, etc. Moreover, dynamic reconfiguration can allow run-time adaptation of the OS to the current application requirements, and so achieving a better execution environment for this application.

Such operating systems can be in a first level classified into two categories, static and

dynamic. Beside that, reconfigurable OS can be classified in respect to the initiator of the reconfiguration [48], which could be triggered by:

**Human** This is often the case when the designer decides which components of an OS is going to be used for the target application and this feature is supported by most operating systems. Dynamic reconfiguration is also usual for those systems, even at boot time (by passing some parameters to the kernel) or at run-time by loading or unloading modules (e.g., Linux OS).

**Application** A reconfiguration that is triggered by an application appears only in dynamic case and this has received strong attention in the OS research community. Several proposals therefore have been proposed and in the following subsection some representative OSs of this category will be presented and discussed.

**Operating System** Also called Automatic or Self-Adaptation, OSs belonging to this category are those which the reconfiguration is initiated by the OS itself. Portability of the OS to different platforms at compile time may be seen as a feature of this kind of OS which does not represent a significant innovation, since most of the OSs provide this feature. The interesting approach is in dynamic scenarios, which require more intelligence from the OS.

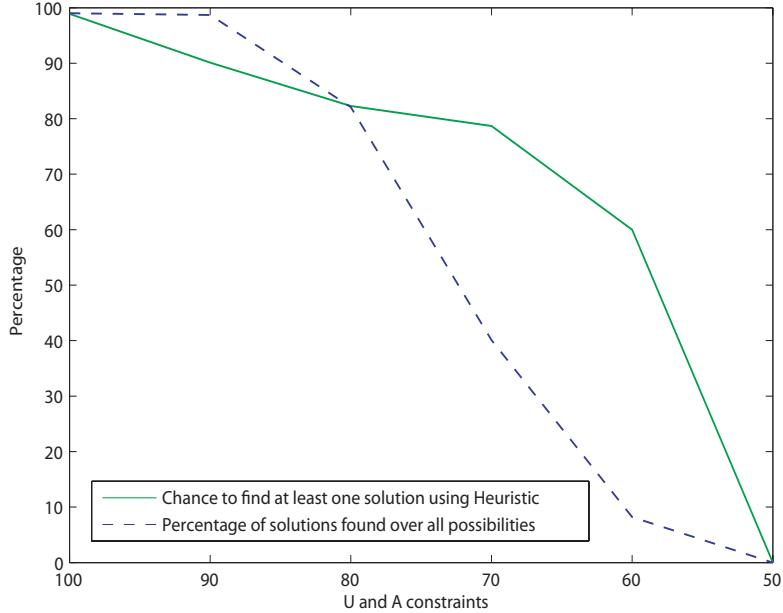

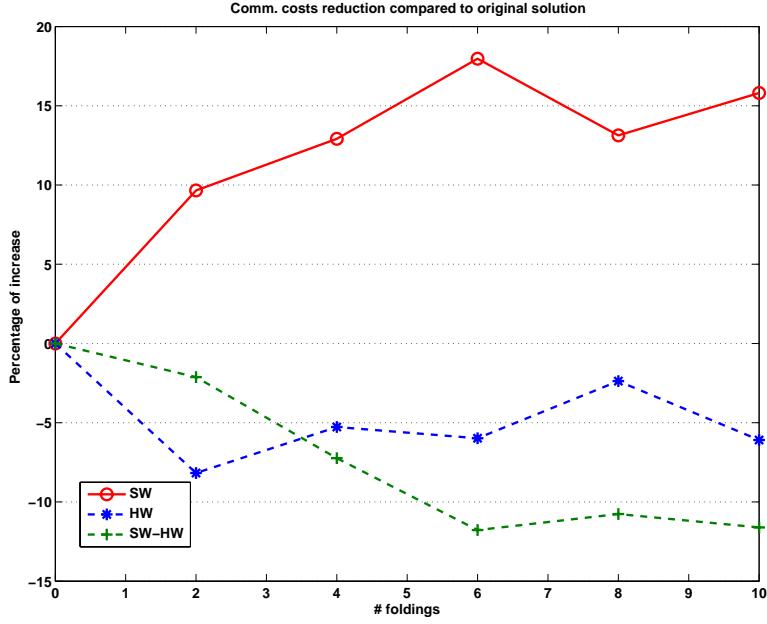

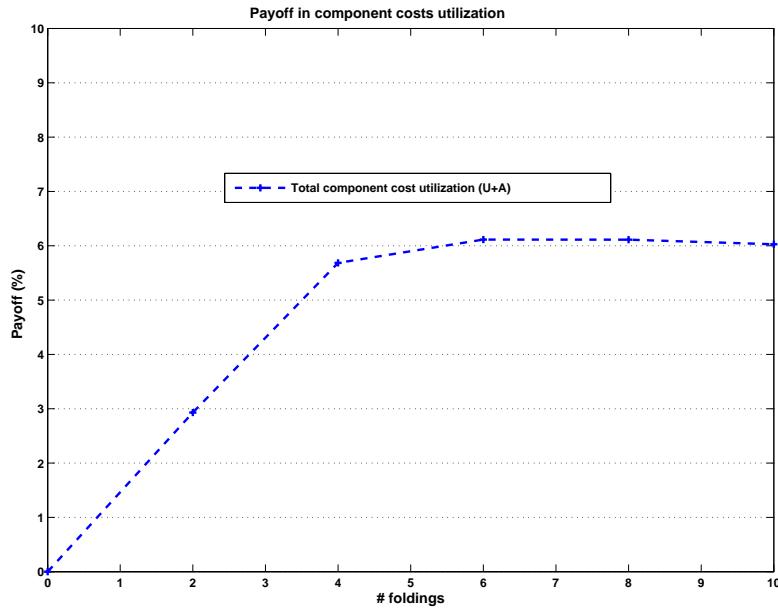

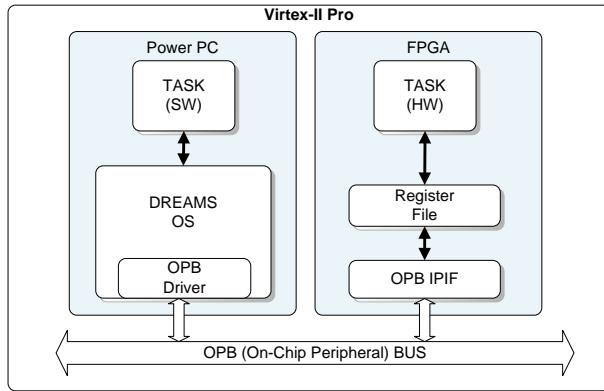

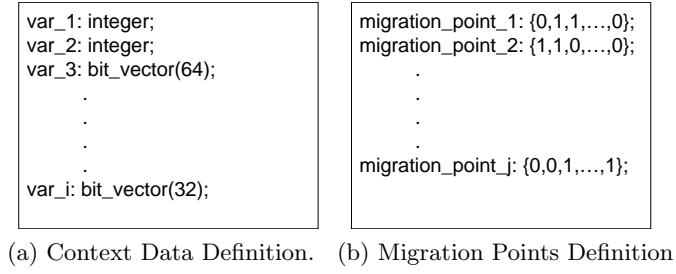

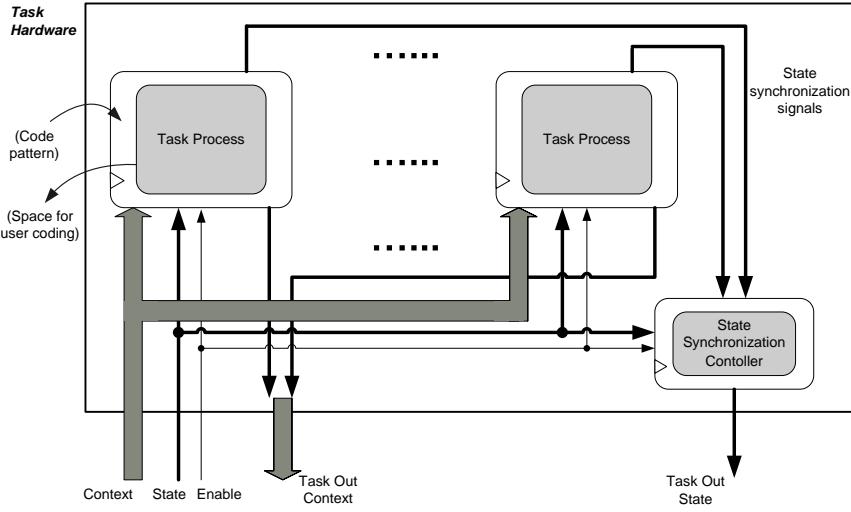

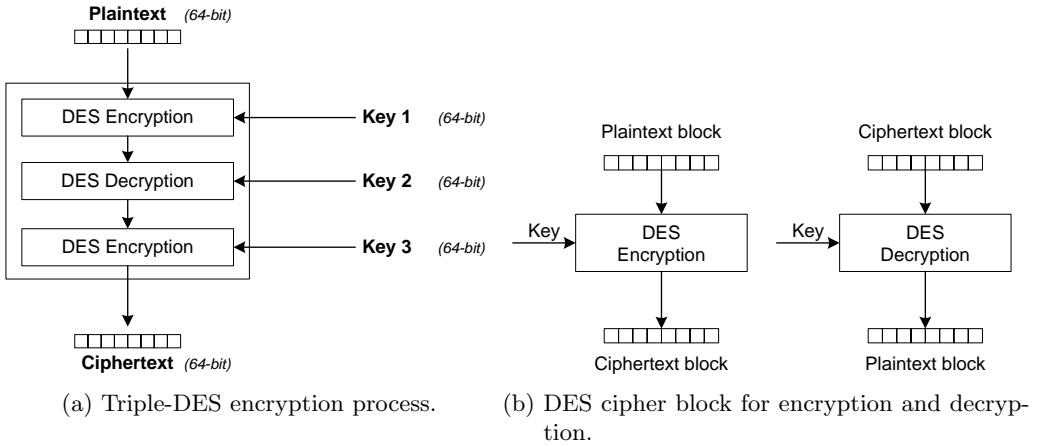

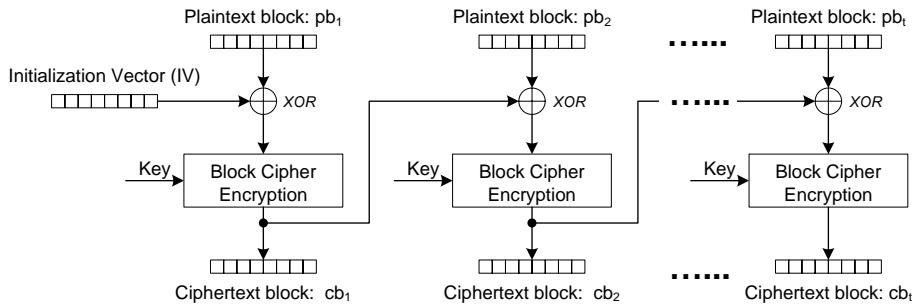

Most of the investigations done for dynamic reconfigurable OS are concentrated on the cases where reconfiguration is triggered by the application, and in the majority, those approaches accept the idea that applications know better than the OS what their needs and requirements are. Therefore, usually the application makes requests to the OS to change its policies on its behalf. A self-reconfiguring OS, on the other hand, needs to have enough intelligence in order to gather sufficient and appropriated information from the running applications. Such information is needed to make a decision regarding what and when to reconfigure itself, in such a way to provide an optimal execution environment for each of the applications.