Dissertation

**Versatility of Bulk Synchronous Parallel Computing:

From the Heterogeneous Cluster to the System on Chip**

Olaf Bonorden

**UNIVERSITÄT PADERBORN**

*Die Universität der Informationsgesellschaft*

FAKULTÄT FÜR ELEKTROTECHNIK, INFORMATIK UND MATHEMATIK

INSTITUT FÜR INFORMATIK UND HEINZ NIXDORF INSTITUT

February 2008

## Zusammenfassung

Der Bedarf an Rechenleistung in den Wissenschaften und der Industrie steigt ständig an. Bei der Entwicklung schnellerer Prozessoren gelangt man allerdings an physikalische Grenzen, so dass zur weiteren Leistungssteigerung sehr viele Prozessoren zusammen als Parallelcomputer benutzt werden müssen. Zur Nutzung dieser Supercomputer ist es wichtig, allgemeine Modelle und Werkzeuge zu haben, die es erlauben, unabhängig von der speziellen Hardware effiziente Algorithmen zu entwickeln und zu implementieren.

In dieser Dissertation werden Modelle für parallele Systeme vorgestellt, ein Überblick über Algorithmen für diese Modelle gegeben und effiziente Implementierungen für verschiedene Architekturen entwickelt. Der Schwerpunkt liegt dabei auf der Familie der *Bulk Synchronous Parallel* Modelle, da diese die Entwicklung portabler, aber trotzdem effizienter paralleler Programme erlauben.

Für die Implementierungen werden zwei Architekturen betrachtet: ein On-Chip-Parallelcomputer und Workstation-Cluster. Im Bereich des On-Chip-Systems zeigt die Arbeit, wie das benutzte Modell die Entwicklung applikationsunabhängiger, effizienter, paralleler Systeme unterstützen kann.

Die Workstation-Cluster, auf denen nur freie Rechenkapazitäten genutzt werden dürfen, stehen auf der anderen Seite des Spektrums paralleler Systeme. Sie unterscheiden sich vom On-Chip-System nicht nur durch viel größere Latenzen, geringere Kommunikationsbandbreite und größeren Arbeitsspeicher, sie können auch heterogen sein, d. h., verschiedene Computertypen enthalten. Hierdurch und durch die variable, sich ständig ändernde, nutzbare Rechenkapazität der einzelnen Knoten ergeben sich besondere Herausforderungen, z. B. Lastbalancierung. Hierfür stellt die Arbeit eine Implementierung vor, welche mittels virtueller Prozessoren und deren Migration die Last gleichmäßig im Netzwerk verteilt.

Exemplarische Implementierungen zeigen, dass die Idee eines allgemeinen Modells funktioniert, d. h., dass ein Algorithmus für dieses Modell, sogar ein Programmquelltext, zu effizienten Implementierungen auf unterschiedlichen Systemen führen kann.

Reviewers: Prof. Dr. Friedhelm Meyer auf der Heide, University of Paderborn

Prof. Dr.-Ing. Ulrich Rückert, University of Paderborn

# Acknowledgements

First and foremost, I wish to thank my advisor, Prof. Dr. Friedhelm Meyer auf der Heide, for his great support over all the years. I had a pretty good time and a very nice atmosphere in his research group Algorithms and Complexity. I always had the freedom to choose the topics and direction of my research.

Furthermore, I would like to thank all (former) members of the research group Algorithms and Complexity and all participants of the projects DFG-Sonderforschungsbereich 376 and GigaNetIC, especially the persons with whom I closely collaborated in research, teaching, or just in daily conversations. I am grateful to Ingo Rieping, who introduced me to bulk synchronous parallel computing.

For the technical support, my thanks go to the members of the IRB, especially Ulrich Ahlers and Heinz-Georg Wassing, who always tried to satisfy my needs concerning hardware and software, and to the Paderborn Center for Parallel Computing (PC<sup>2</sup>), namely Axel Keller, who always reanimated nodes of the system killed by my experiments.

Special thanks I owe to Bastian Degener and Marc Rautenhaus, who proof-read parts of this thesis.

Last but not least, I would like to thank Stefanie for her patience, empathy, love, and all the other things that make it so worthwhile to know her. She turned even the most stressful days into a wonderful time, nowadays assisted by Emely's and Nele's enthusiastic welcome each day after work.

*Olaf Bonorden*

To those who cannot read these lines anymore:

Heide Bonorden

# Contents

|          |                                                          |           |

|----------|----------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                      | <b>1</b>  |

| 1.1      | High Performance Computing . . . . .                     | 1         |

| 1.2      | Contributions of this Thesis . . . . .                   | 3         |

| 1.3      | Related Work . . . . .                                   | 4         |

| 1.4      | Organization . . . . .                                   | 5         |

| <b>2</b> | <b>Parallel Models</b>                                   | <b>7</b>  |

| 2.1      | Parallel Random Access Machine models . . . . .          | 8         |

| 2.2      | Bulk Synchronous Parallel Models . . . . .               | 10        |

| 2.3      | Other Parallel Models . . . . .                          | 15        |

| 2.4      | Conclusion . . . . .                                     | 16        |

| <b>3</b> | <b>Algorithms</b>                                        | <b>19</b> |

| 3.1      | BSP-Algorithms . . . . .                                 | 19        |

| 3.2      | Composition of Efficient Nested BSP Algorithms . . . . . | 26        |

| <b>4</b> | <b>Implementations</b>                                   | <b>35</b> |

| 4.1      | BSP Environments . . . . .                               | 35        |

| 4.2      | Implementations of BSP Algorithms . . . . .              | 43        |

| <b>5</b> | <b>BSP for Parallel System on Chip</b>                   | <b>49</b> |

| 5.1      | Project GigaNetIC . . . . .                              | 49        |

| 5.2      | Related Work . . . . .                                   | 50        |

| 5.3      | Design of the Architecture . . . . .                     | 51        |

| 5.4      | Toolchain . . . . .                                      | 56        |

| 5.5      | Evaluation . . . . .                                     | 62        |

| 5.6      | Conclusions . . . . .                                    | 71        |

| <b>6</b> | <b>BSP for Heterogeneous Workstation Clusters</b>        | <b>73</b> |

| 6.1      | Heterogeneous Workstation Cluster . . . . .              | 73        |

| 6.2      | Related Work . . . . .                                   | 74        |

|          |                                               |            |

|----------|-----------------------------------------------|------------|

| 6.3      | Migration of Virtual Processors . . . . .     | 76         |

| 6.4      | Load Balancing . . . . .                      | 82         |

| 6.5      | Conclusions . . . . .                         | 94         |

| <b>7</b> | <b>Summary and Outlook</b>                    | <b>95</b>  |

| 7.1      | Summary . . . . .                             | 95         |

| 7.2      | Open Questions and Further Research . . . . . | 96         |

|          | <b>Bibliography</b>                           | <b>99</b>  |

|          | <b>Nomenclature</b>                           | <b>111</b> |

|          | <b>Index</b>                                  | <b>113</b> |

# Chapter 1

## Introduction

### 1.1 High Performance Computing

High performance computing has become an ubiquitous component of scientific work in natural and engineering sciences. Due to the well-known physical limitations of increasing the computational power of individual processing elements, parallel systems have become particularly important in recent years.

#### 1.1.1 Technological Progress

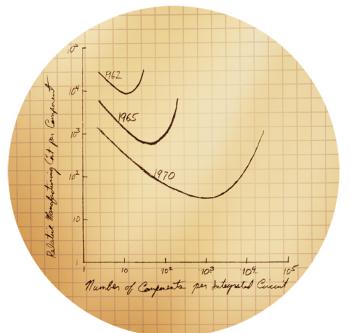

Processing elements are becoming increasingly faster. *Moore's Law* [Moo65, Moo98] is well-known for its statement that the complexity of microprocessors doubles every two years, a time interval nowadays adapted to 18 months. In the early days of processor design performance of a system could easily be improved by either increasing the clock frequency or by using more transistors. Since 1971 the number of transistors of the central processing unit (CPU<sup>2</sup>) has been increased from 2,250 to more than 299 millions in 2006 (Table 1.1). During the same time, arithmetic units were enlarged from 8 bits to 64 bits word size and support for the direct execution of increasingly complex instructions (e. g., multiplication) and floating point numbers was added. Later, sophisticated techniques were introduced to

Copyright © 2005 Intel Corporation.<sup>1</sup>

Figure 1.1: Moore's Law

<sup>1</sup>“In 1965, Gordon Moore sketched out his prediction of the pace of silicon technology. Decades later, Moore's Law remains true, driven largely by Intel's unparalleled silicon expertise.”[Int06]

<sup>2</sup>In this thesis we will denote CPU by processor because we are not dealing with other processing units like e. g. graphic processing units (GPU).

Table 1.1: Die Sizes

| Year | Processor                    | Transistors   |

|------|------------------------------|---------------|

| 1971 | Intel 4004                   | 2,250         |

| 1978 | Intel 8086                   | 29,000        |

| 1979 | Motorola 68000               | 68,000        |

| 1989 | Intel 80486                  | 1,180,000     |

| 2001 | IBM-Motorola Power4          | 174,000,000   |

| 2002 | Intel Itanium II (McKinley)  | 410,000,000   |

| 2005 | AMD Athlon 64                | 200,000,000   |

| 2006 | Intel Pentium Xeon           | 291,000,000   |

| 2007 | Intel Itanium II (Montecito) | 1,720,000,000 |

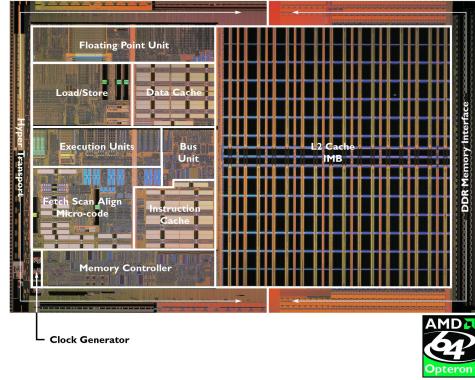

Figure 1.2: AMD Opteron

further increase the clock speed and to hide latencies. Examples are out-of-order execution, branch prediction, or speculative execution.

Another approach to utilize transistors is caching. Indeed, most transistors of modern processors are used for caches, for instance, the Intel Itanium II *Montecito* uses  $1.55 \cdot 10^9$  of its  $1.72 \cdot 10^9$  transistors for caches (24 MB). Figure 1.2 shows the die of an Opteron processor, although it has only 1 MB cache, the caches occupy more than half of the chip area.

### 1.1.2 Parallelism

The demand of computational power grows even faster than the increase in processor speed. To accommodate this demand, many processing units are combined to build large parallel machines. Parallel computers have been on the market for more than 20 years now, and much experience has been gained in designing such systems. Various design ideas have led to a wide range of parallel architectures, which differ in the type of the processing unit (standard CPUs, vector processors, et cetera) and use quite different communication structures like shared memory or various network topologies.

Although parallel systems are widely used in high performance computing, for instance, for complex simulations in science and engineering (e. g., fluid mechanics or crash tests). Modern office computers often have multicore processors, i. e., they have two or more processor cores inside the CPU. They are thus parallel computers, but the number of processing elements is very small and most standard software does not utilize the parallelism.

Software is the major reason why massive parallel systems are not widely used, although such systems could be made available at low cost. In the beginning of parallel computing, most algorithms were developed and analyzed for specific parallel computers, for example, sorting algorithms for computers with a hypercube network topology

[CP93]. When a new topology was developed, one had to adapt all algorithms and rewrite the software. In contrast, for sequential machines widely used model of the system (von-Neumann-model [BGvN89]) and architecture independent programming languages (e. g., ISO-C99 [ISO05]) exists, so it is easy to develop software that runs efficiently on all computers that follow the model.

Several parallel computer models try to play a similar role for parallel systems. Some are mainly used for theoretical analysis, but others are supported by libraries for the efficient implementation of algorithms on different target architectures.

For the success of parallelism on the market, a general parallel model is needed that is easy to use and allows the development of portable but yet efficient algorithms. Furthermore, a toolchain supporting the implementation is needed, including languages, compilers, libraries, and development tools like parallel debuggers and profilers.

## 1.2 Contributions of this Thesis

Skillicorn and Talia conclude their survey of parallel algorithms by the following perspective:

“Thus we can hope that, within a few years, there will be models that are easy to program, providing at least moderate abstraction, that can be used with a wide range of parallel computers, making portability a standard feature of parallel programming, that are easy to understand, and that can be executed with predictably good performance.”

*Skillicorn and Talia, 1998[ST98]*

In our view models which have these properties already exist. The main objective of this thesis is to demonstrate that the bulk synchronous parallel (BSP) models are flexible enough to allow portable, yet efficient parallel programs for a wide range of machines: from tightly coupled parallel computers on a single chip to workstation clusters using traditional local area networks.

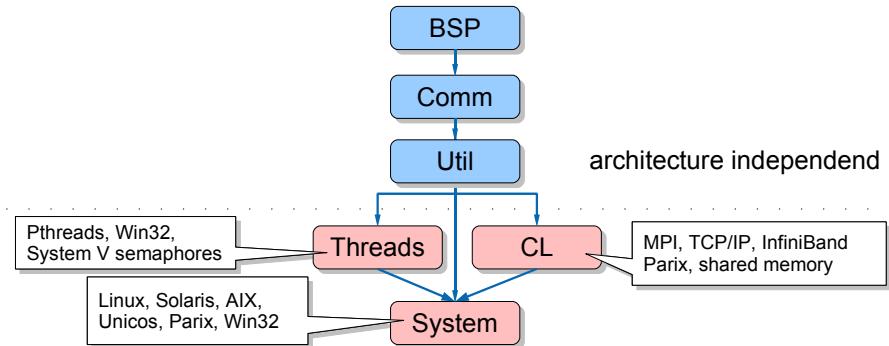

This thesis covers the entire work flow: parallel computation models, algorithms, and implementations on different parallel architectures. We first explore several of the existing models to find candidates for a general parallel model. We then concentrate on the family of bulk synchronous models, as we think they are good candidates for parallel models for general use like the von-Neumann model for sequential computers. Next, we investigate algorithms for the BSP model. The models should be in use, i. e., there should be a lot of algorithms in the literature for them. Furthermore, we want practical usable models, so we investigate universal implementations for them.

Our main contributions are the design of a configurable, efficient parallel system on a chip suitable for BSP — demonstrating how the model can guide the development of efficient hardware for general use — and an efficient implementation of the BSP model

for workstation clusters providing only unpredictable usable idle times. Our contributions demonstrate that the BSP model can be used for a wide range of parallel systems. It is thus well suited as a candidate for a commonly used parallel model.

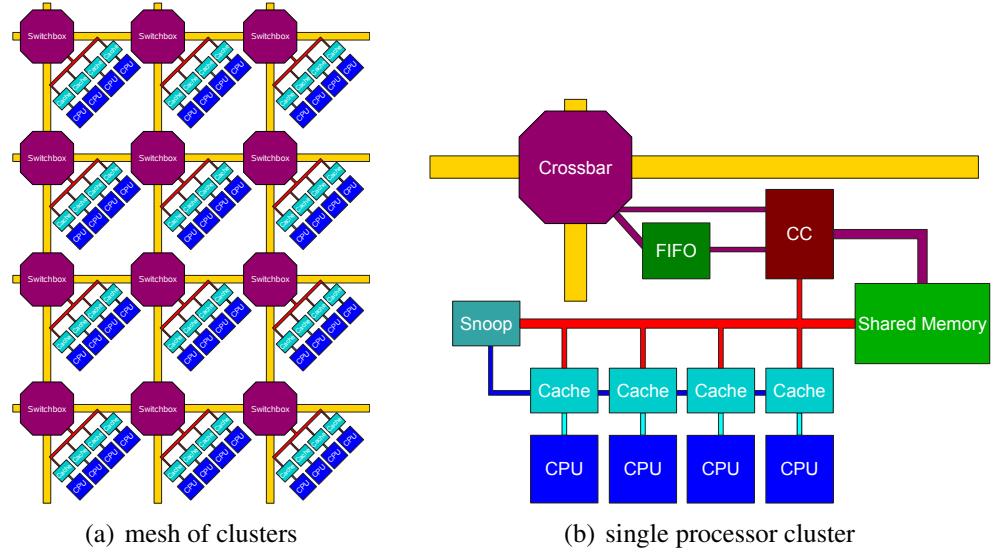

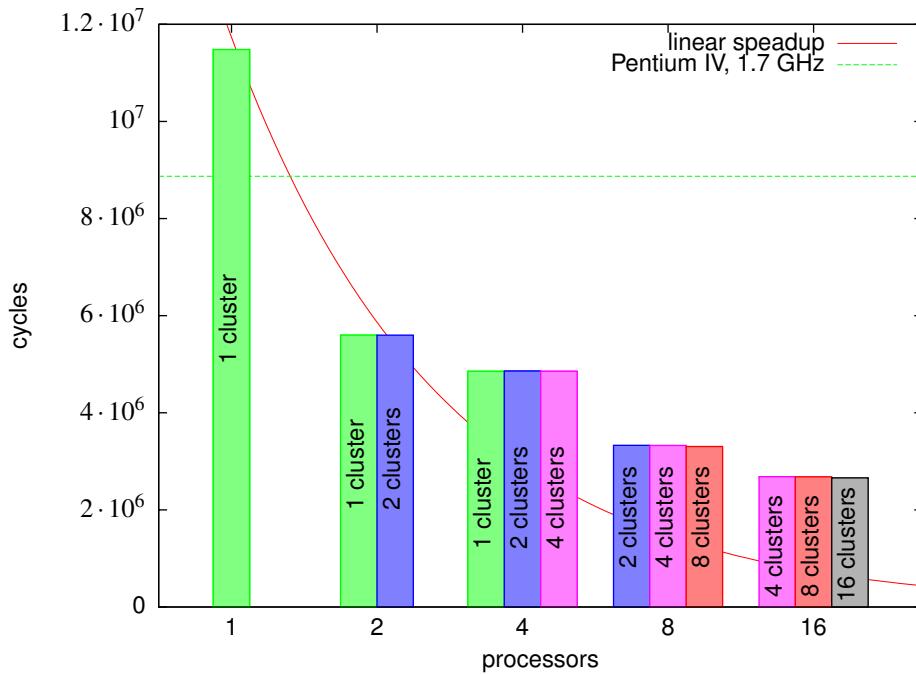

**BSP for Parallel System on Chip.** We design a hierarchical parallel architecture, with clusters of processors using shared memory and an on-chip interconnection network between the clusters. We develop communication protocols, a BSP library, and a set of simulators to evaluate the system and the influence of different parameters like cache sizes, organizations, et cetera. We evaluate the system using different benchmarks, from simple communication benchmarks to applications like sorting and solving 3-satisfiability, covering a wide range of limiting factors for parallel programs.

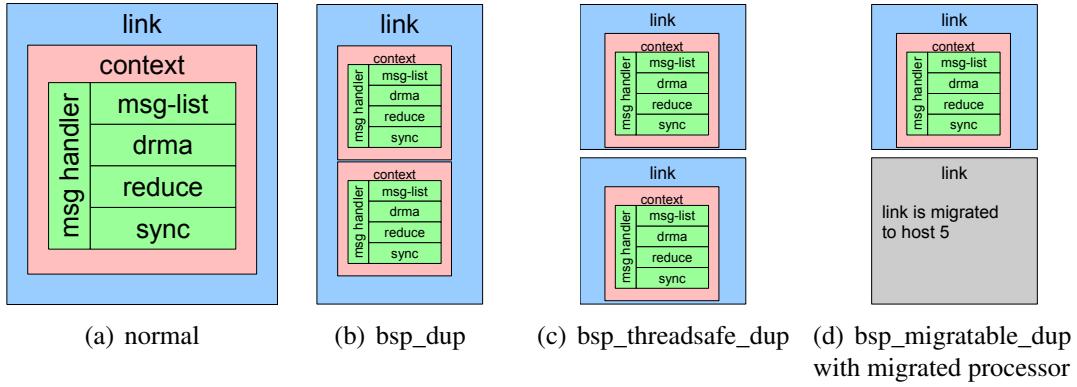

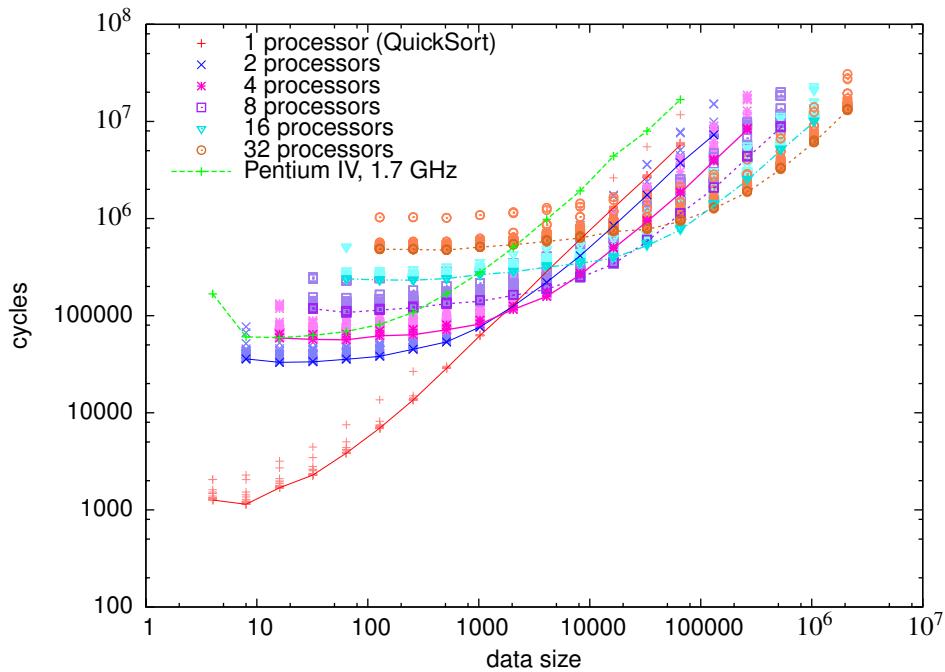

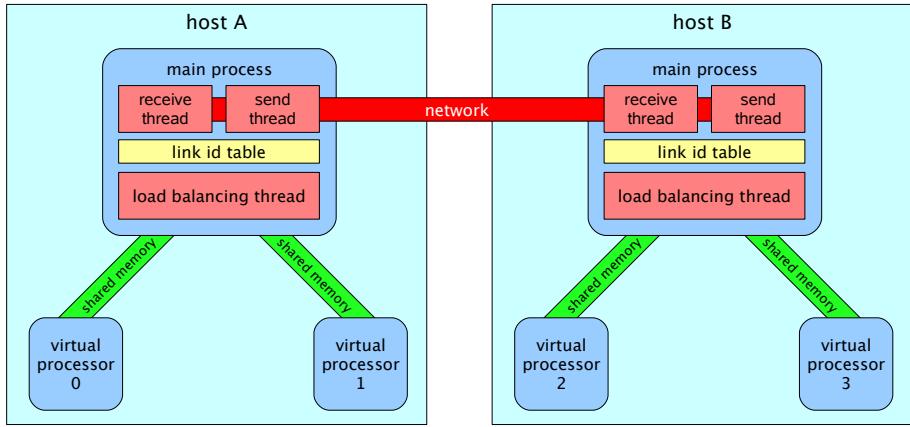

**BSP for Heterogenous Workstation Cluster.** We implement and evaluate a library for efficient execution of BSP programs for heterogenous workstation cluster. As we are allowed to use only the idle times of the computers, and the behavior of other users is not known in advance, we have to adapt to changes of the free capacity online.

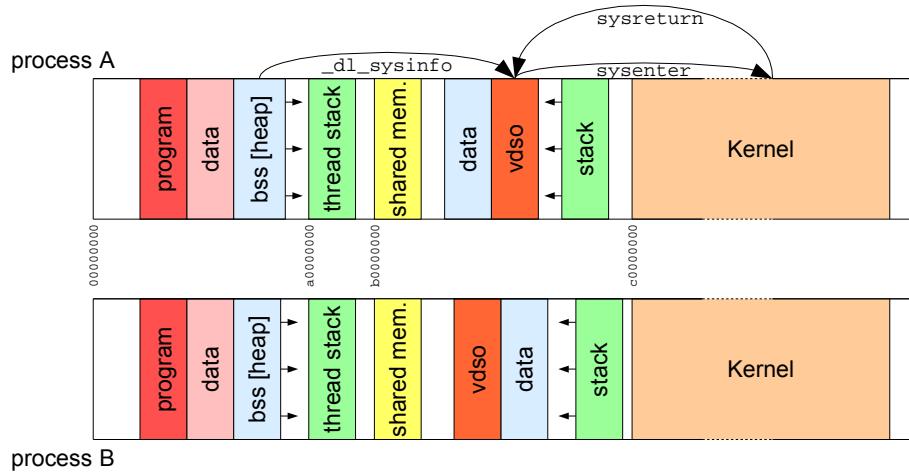

For this purpose we implement virtual processors, which can be migrated to idle nodes in the network. To the best of our knowledge, this is the first realization of migrating Linux processes in the userspace, without modifications of the operation system. This is very important, because normally users are not allowed to change the systems of other users. Furthermore, patching the Linux needs updates to the software for every new Linux version. These migration technique is also of independent interest.

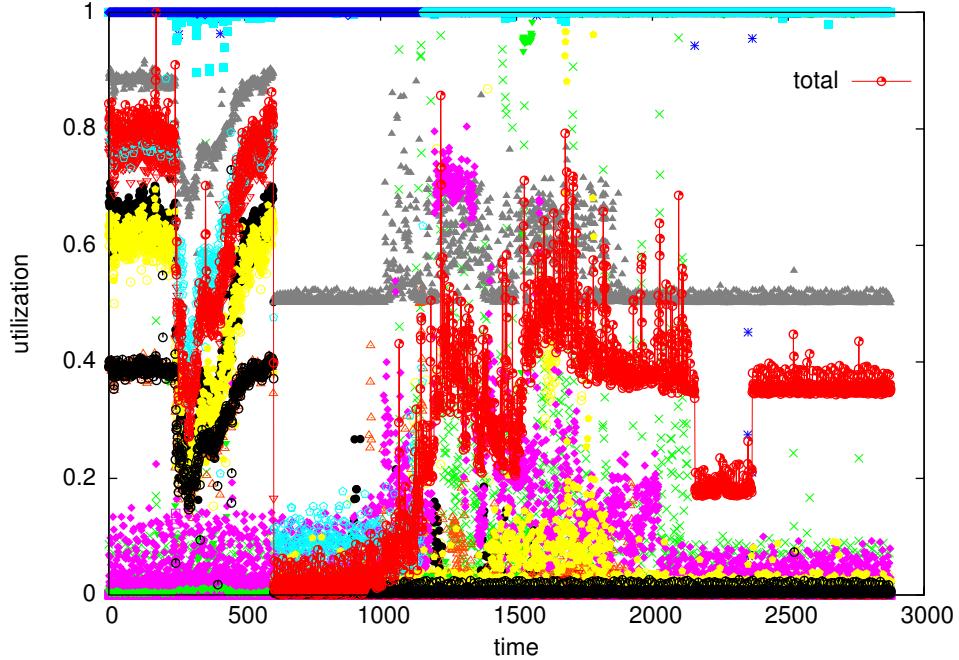

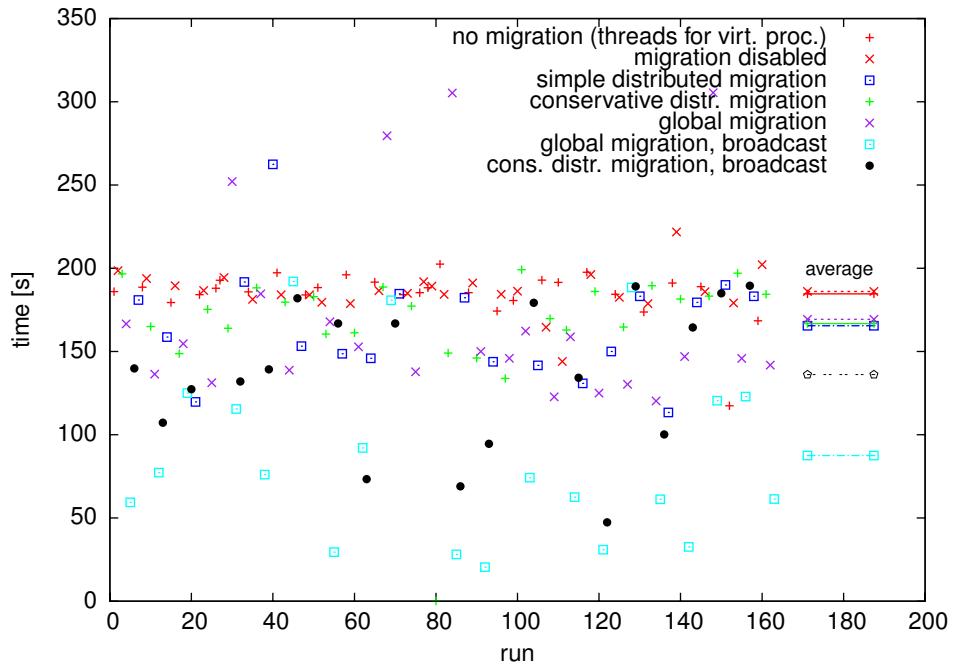

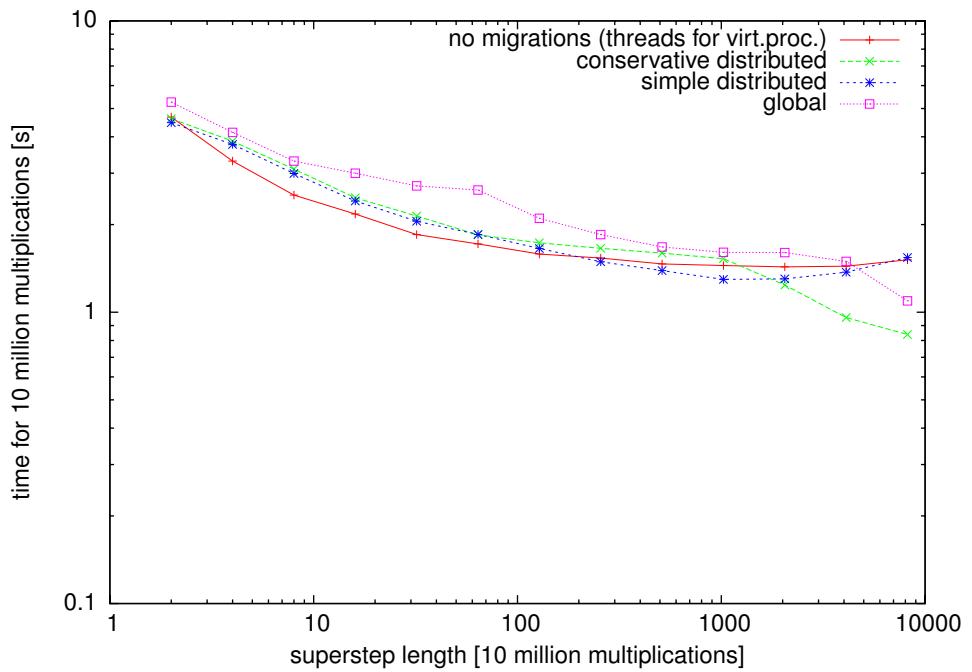

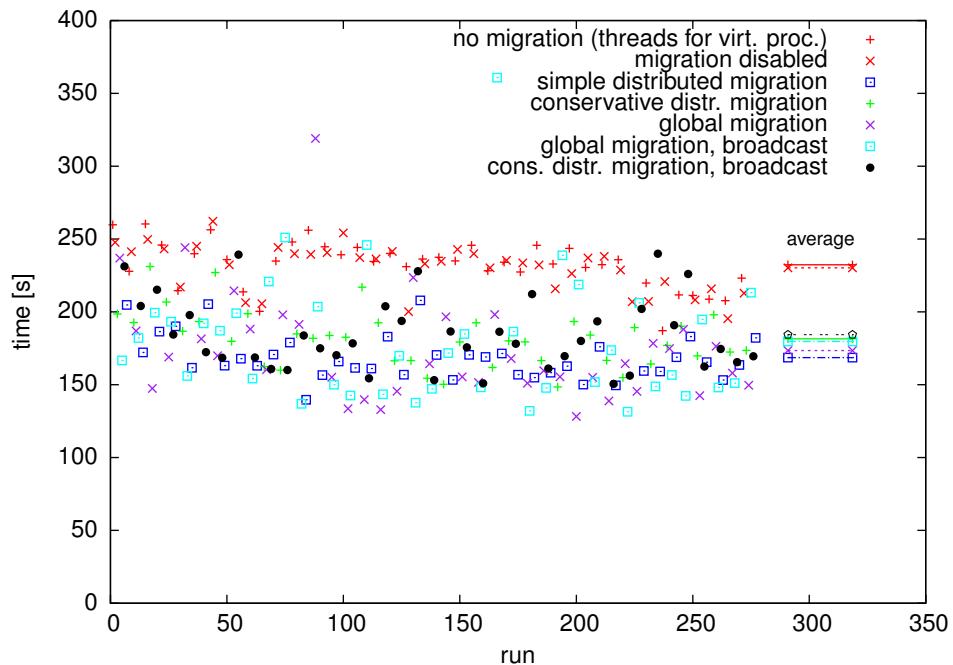

We examine the usage of a typical Linux workstation to create models for the load and the idle times of workstation clusters. Based on the load models we implement and evaluate load balancing strategies.

### 1.3 Related Work

Much research has been done in the field of parallel models and algorithms. We give a survey of some models that are related to the BSP model, and a survey of algorithms and implementations in the following chapters.

In the field of implementations there are different related publications: other BSP implementations (e. g., Oxford BSPlib), other systems for process migration and load balancing, and other approaches for parallel systems on a single chip. We discuss this work in the corresponding chapters.

## 1.4 Organization

In **Chapter 2** we describe parallel models in the field of bulk synchronous parallel computing. We start with the famous PRAM model and show the development to the bulk synchronous parallel model and its extenstions.

**Chapter 3** gives a survey over algorithms for the bulk synchronous model to show that it is widely used for algorithm design. The algorithms described in the literature are mostly analyzed using the  $\mathcal{O}$  notation (Landau notation), which shows the asymptotic behavior for very large input sizes.

In **Chapter 4** we show implementations, i. e., practical usable software, to confirm that the model is not only useful for analyzing algorithms in the  $\mathcal{O}$  notation but also leads to fast algorithms in practice. Furthermore, we give a survey of libraries for implementation of BSP algorithms. There are many more algorithms than implementations, mainly because the model is widely used in theory but still unknown to many programmers, which will hopefully change in the future. The last section in that chapter introduces our system to build libraries of algorithms, and shows a way to automatically configure optimal algorithms for a given machine and a given problem size using a collection of annotated algorithm implementations.

The next two chapters deal with our implementation of libraries for BSP computing for two very different architectures: **Chapter 5** describes a parallel system on a single chip, with low latencies, high bandwidth, but small local on-chip memories. It shows the flexibility of the model, as the same algorithms, in our implementations even nearly with the same source can be used for quite different systems. It also demonstrate how BSP can support the development of hardware architectures, e. g. designing communication protocols suitable for BSP.

In **Chapter 6** we propose an efficient implementation for a parallel architecture at the other end of the range of parallel systems: a lossly coupled workstation cluster with some external load, where we can only use unpredictable idle times. We show how the migration of virtual processors can help to cope with load changes and faulty machines.

### Publications

Parts of this work have been published on conferences and in journals. A fast BSP algorithm for factorization of polynoms is evaluated in [BvzGG<sup>+</sup>01]. The combination of algorithms and implementation and its automatical configuration is introduced in [BMW02]. Some issues of the design and implementation of our BSP implementation (PUB library) are described in [BJvR03], the migration and load balancing functionality for heterogenous workstation clusters in [Bon07]. A model for the utilization of workstations (constant-usage-interval load model) is published in [BGM05, BGM06]. An introduction to the System-On-Chip architecture is [BSR<sup>+</sup>03].

# Chapter 2

## Parallel Models

In this chapter we will give a survey of parallel computing models. We will start by introducing a family of parallel random access machine models [SS63], which are natural extensions to the sequential random access machine. Next bulk synchronous models will be described, and we conclude by reviewing some other related models. We concentrate on these models, because we think they can act as general parallel models, which are suitable for theoretical analysis as well as for portable and efficient implementations.

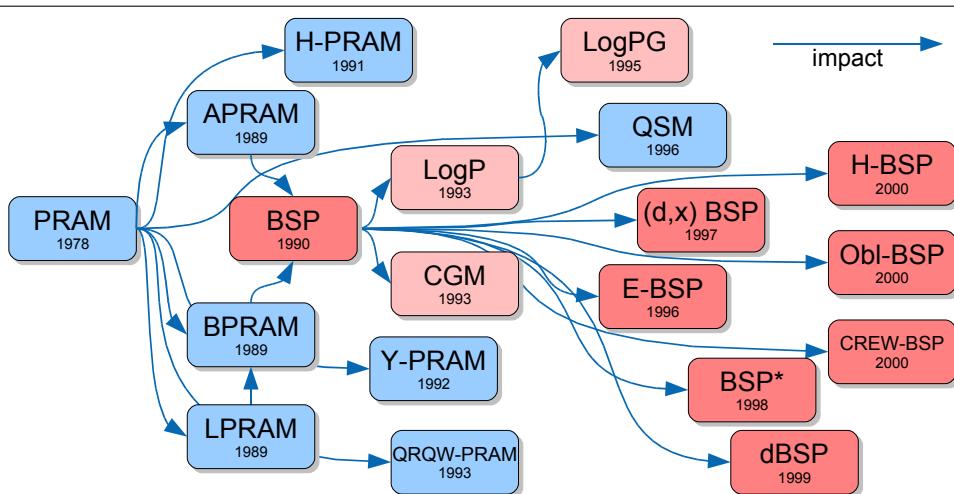

Figure 2.1 gives an overview of the parallel models described in the following paragraphs and their relations. In [LMR95], Li, Mills, and Reif present a framework of using resource metrics to characterize models of parallel computation. They concentrate on the resources that are accounted for by the model, for example, memory organization, latency, or block transfers. The paper describes a number of parallel models and classifies them with respect to their resources.

Figure 2.1: A Map of some Models for Parallel Computing

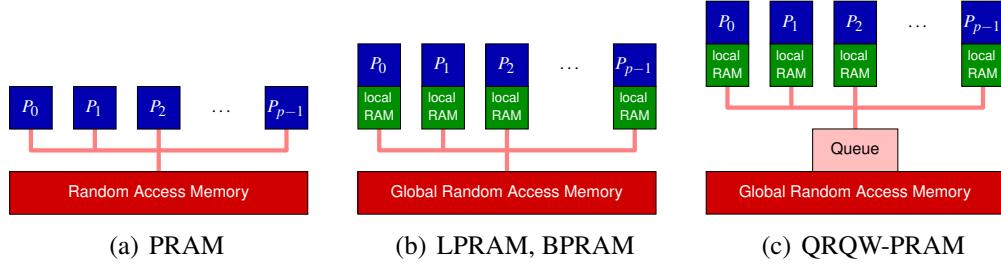

Figure 2.2: Parallel Random Access Machine

Another survey including parallel languages and systems with implicit parallelism as well, has been written by Skillicorn and Talia [ST98]. The authors use a set of six criteria that in their view an ideal model should satisfy. Four criteria are related to the needs of software developers, two address the needs for actual execution of the models on real parallel machines. The main focus of the paper is the classification of the models in categories based on these criteria.

## 2.1 Parallel Random Access Machine models

In this section we will describe a family of parallel computing models that use a global shared memory. We will start by introducing the standard Parallel Random Access Machine (PRAM) model, then continue by adding a number of extensions including additional local memory and block transfers.

### 2.1.1 Parallel random access machine (PRAM) model

The *parallel random access machine* [FW78] is an extension of the sequential random-access-machine (RAM). A RAM consists of one processing element (CPU) and a random access memory. The CPU can read and write to arbitrary cells of the memory.

In a PRAM, there are  $p$  processors that can read and write arbitrary cells of a global shared memory. The processors have a central clock and execute each instruction of a given program synchronously. All communication between the processors is done by writing to and reading from the memory (Figure 2.2). Many variants of PRAMs exist in the literature. They differ in how simultaneous accesses of different processors to the same memory cell are handled: *Exclusive* read and write (EREW) does not allow any conflicts. *Concurrent* read/write (CRCW), as the most powerful version, can handle such accesses. For CRCW PRAMs, there are different rules for resolving write conflicts, including *common* (all processors have to write the same), *priority* (processor with lowest id writes), and *arbitrary* (the winning processor is not defined).

Communication costs are not accounted for by the model. Thus, it is suited to analyze the maximal degree of parallelism which is possible for a given problem while neglecting problems occurring in practical applications, for instance, limited bandwidth or congestion.

### 2.1.2 Local-Memory PRAM (LPRAM)

The *Local Memory PRAM* introduced by Alok Aggarwal, Ashok K. Chandra and Marc Snir [ACS90] includes local memory. In addition to the global memory, each processor has its own unlimited private local memory. At each time step, a processor can either read or write a word to the global memory, or perform a local computation step. The access to the global memory is modelled by concurrent read, exclusive write.

The authors provide proves for upper and lower bounds for the LPRAM model for three problems: matrix multiplication, sorting, and computing an  $n$ -point FFT graph.

### 2.1.3 Block-PRAM (BPRAM)

The *Block-PRAM* model [ACS89] is an extension of the LPRAM, it includes block by block transfers. All accesses to the shared global memory are blockwise. This means that a processor can transfer a block of consecutive memory cells from the global memory to the local memory. The same is possible in the opposite direction. Copying of data is charged by costs of  $b + l$ , where  $b$  is the size of the block and  $l$  is the latency (a parameter of the machine). In the BPRAM model, different accesses are not allowed to overlap, i.e., the shared memory is modelled by exclusive read, exclusive write (EREW). Minimal running time and the total work performed by the processors are important measures of the algorithm performance in this model.

The authors demonstrate the capabilities of their model by analyzing sorting, global sum, matrix transposition and multiplication, rational permutations, and Fast Fourier Transformation. Furthermore, they summarize the relationship of execution time of standard PRAM and BPRAM with the following equation, since one step of a EREW-PRAM can be simulated with  $l$  steps of the Block-PRAM:

$$T_{\text{EREW-PRAM}} \leq T_{\text{BPRAM}} \leq l \cdot T_{\text{EREW-PRAM}}$$

### 2.1.4 Queue-Read Queue-Write PRAM

The *Queue-Read Queue-Write (QRQW) PRAM* was introduced by Gibbons, Matias, and Ramachandran [GMR98] and is a model situated between the EREW- and the CRCW PRAM. Similar to the LPRAM, each processor has its own local memory in addition to the global memory. Concurrent access to the global memory is allowed, but the cost

of a step is increased by the number of processors that access the global memory. The motivation of this cost function is that all requests are stored in a queue and processed sequentially. In [GMR98] the relationship to other models is also discussed: a  $p$  processor QRQW-PRAM can be simulated on a  $p/\log p$  processor BSP computer (cf. Section 2.2) with slowdown  $\mathcal{O}(\log p)$  with high probability.

### 2.1.5 Asynchronous PRAM (APRAM)

The *Asynchronous PRAM* by Phillip B. Gibbons [Gib89] is a PRAM that also incorporates both local and global memory. However, in contrast to the other PRAM models, each processor of the APRAM has its own local clock and executes instructions of its own program independently of the timing of other processors. In addition to the global and local read and write operations, there is an instruction to synchronize arbitrary subgroups of the processors. All processors in the subgroup stop until the last has reached a synchronization barrier.

To prevent race conditions, i. e., the output is depended on the order of events, processors are prevented from reading a global memory cell that has been modified by another processor until a synchronization event has occurred. The cost model assumes a global clock, i. e., all instructions on all processors are equally expensive. However, an algorithm for the APRAM model is considered correct only if it works regardless of any delay that may occur.

## 2.2 Bulk Synchronous Parallel Models

In this section we will describe the Bulk Synchronous Parallel Model and its extensions, as we think they are the right candidates for a general parallel model, which is usable for theoretical analysis as well as for portable and efficient implementations.

The models are more restrictive concerning communication patterns than the PRAM models in the previous section, but this simplifies the analysis of algorithms as well as the implementation of the model in real hardware systems.

### 2.2.1 The Bulk Synchronous Parallel Model

The *Bulk Synchronous Parallel Model* (BSP) was introduced by Leslie G. Valiant as a bridge between the hardware and the software to simplify the development of parallel algorithms.

“A major purpose of such a model is simply to act as a standard on which people can agree.”

*Leslie Valiant, 1990 [Val90]*

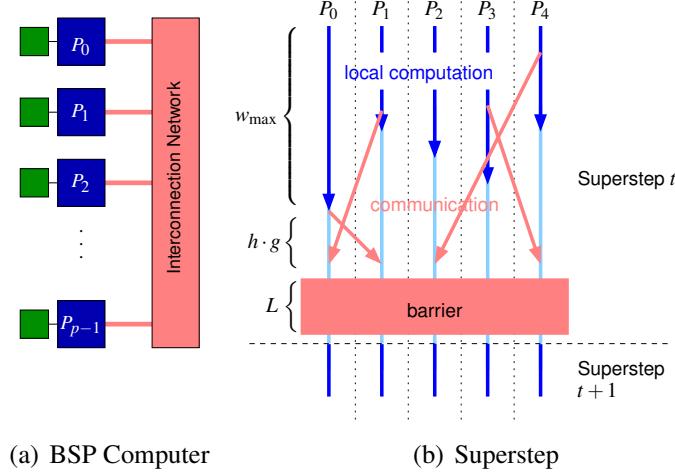

Figure 2.3: BSP Model

On the one hand it provides an abstract view of the technical structure and the communication features of the hardware to use (e. g., a parallel computer, a cluster of workstations, or a set of personal computers (PCs) interconnected by the internet) for the developer. On the other hand it helps hardware designer to build efficient parallel machines without knowing the applications running on it in advance. There are three different parts of the model: a *machine model*, a *programming model* and a *cost model*. There are several views of this model with slightly different descriptions, but they are all equivalent up to constant factors in the cost model. We start with our view, based on our experiences with implementations. Afterwards, we describe the differences.

**Machine model.** A *BSP computer* is defined as a set of processors with local memory and an arbitrary communication mechanism (e. g., a network or shared memory) that supports point-to-point communication between the processors, and barrier synchronization. The model does not assume a specific topology or exploit locality (cf. Figure 2.3(a)).

**Programming Model.** A *BSP program* consists of a set of *BSP processes* and a sequence of *supersteps* – time intervals bounded by the barrier synchronization. Within a superstep each process performs local computations and sends messages to other processes; afterwards it indicates by calling the synchronization method that it is ready for the barrier synchronization. When all processes have invoked the synchronization method and all messages are delivered, the next superstep begins. Then the messages sent during the previous superstep can be accessed by its recipients.

**Cost Model.** The cost of a superstep is the sum of  $w_{\max}$ , the maximal local work of a processor,  $h$ , the maximal amount of data that is sent or received by one processor multiplied with the *gap*  $g$  of the network, and the time  $L$  (*latency*) for one barrier synchronization (Figure 2.3(b)):

$$\text{Cost of a superstep} = w_{\max} + hg + L$$

A communication pattern where each processor sends or receives at most  $h$  bytes is called *h-relation*.

In the original description of Valiant [Val90] the synchronization hardware checks every  $L$  time steps whether all processors have finished the superstep. Thus, the length of a superstep is always a multiple of  $L$ . The difference in the cost function compared to our definition is at most  $L$  times the number of supersteps, thus at most a factor of 2.

**Computational power.** The computational power of BSP is analyzed by Martin Beran in [Ber98]. He assumes an unlimited number of processors, and functions  $g(p)$  and  $L(p)$  describing the bandwidth and the latency with respect to the number of active processors. If  $g(p)$  and  $L(p)$  are polylogarithmic in  $p$ , a BSP computer is asymptotically as powerful as a PRAM. They both belong to a class  $C_2$ , which are all machine models that are polynomial-time equivalent to the space complexity of Deterministic Turing Machines (DTM). All machines in  $C_2$  can solve all problems of the class  $\mathcal{PSPACE}$  in polynomial time (with unbounded number of processors).

For  $g(p) = \Omega(p^a)$ , or  $L(p) = \Omega(p^a)$ ,  $a > 0$ , or  $p$  constant, a BSP-Computer belongs to the Class  $C_1$  (all machines that are polynomial-time equivalent and linearly space equivalent to DTM).

More details on the complexity classes  $C_1$  and  $C_2$  can be found in the Handbook of Theoretical Computer Science [vL90].

**Extensions to BSP.** A lot of extensions to the standard BSP model have been proposed since 1990, for example, E-BSP,  $\text{BSP}^*$ , dBSP, Obl-BSP, or H-BSP. Some of them try to improve the accuracy of running time predictions by using more parameters to describe the machine, for example by introducing a minimal block size for efficient communication in the  $\text{BSP}^*$  model. Others improve the power of the machine by introducing new features, an example is oblivious synchronization.

### 2.2.2 $\text{BSP}^*$

Most real machines need some time to prepare messages, for example, for creating message headers or starting the transmission. So the achieved bandwidth for the communication depends on the size of the messages. In the BSP model the cost depends only on the sum of all transmitted data (*h relation*), not on the size of the messages. The  $\text{BSP}^*$  model

by Armin Bäumker, Wolfgang Dittrich, and Friedhelm Meyer auf der Heide [BDM98] introduces an additional machine parameter  $B$ . Informally,  $B$  is the minimal size a message must have to achieve a “good” network bandwidth. More formally, the communication cost of a superstep is  $h \cdot g$ , where  $h$  is the maximal amount of data  $h_i$ ,  $i = 0, \dots, p - 1$  send or received by a processor. In opposite to the normal BSP model, these  $h_i$  are the sum of all message sizes where each message smaller than  $B$  bytes is charged for  $B$ .

The authors use multisearch as an example to show the improvement over BSP.

### 2.2.3 Oblivious BSP

One often noted objection to the use of BSP is the global synchronization. Especially for large parallel machines having many processors, the cost of a global synchronization seems to be quite big (although in most implementations it is of order  $\mathcal{O}(\log p)$  for  $p$  processors). So there are some proposals to reduce this cost. The Oblivious-BSP model by Jesus A. Gonzalez, Coromoto Leon, Fabiana Piccoli, Marcela Printista, José Luis Roda, Casiano Rodríguez, and Francisco de Sande [GLP<sup>+</sup>00] formalized *Oblivious Synchronization*, which was first implemented in the BSPk system (s. Section 4.1.1).

In the BSP model all processors are in the same superstep, guaranteed by the barrier synchronizations between supersteps. But for a correct execution it is only needed that messages are received at the right time, i. e., two processors that do not communicate with each other do not have to synchronize. In the Oblivious BSP model processors may be in different supersteps, the only limitation is that a processor is not allowed to enter a new superstep until all messages for it have been received. As it is not possible for the system to know in advance if other processors, which are still in earlier supersteps, will send messages, the user has to specify the number of messages each processor will receive.

The processor waits until the messages have been received and continues with the next superstep. This can reduce the idle time waiting for other processors in barrier synchronizations, especially if the amount of work in a superstep is not equal on all processors. Furthermore, the time for the barrier synchronization is saved.

The authors demonstrate the accuracy of running time predictions in their model by evaluating a nested parallel Discrete Fast Fourier Transform algorithm with the PUB library (Section 4.1.2) on a Cray T3E supercomputer. The performance gain of the oblivious synchronizations in practice can be seen in [BJvR03], where the running time of a multi search program is evaluated using different advanced features of the PUB library.

### 2.2.4 E-BSP

In 1996 Ben H. H. Juurlink and Harry A. G. Wijshoff proposed the *Extended BSP (E-BSP) model* [JW96]. It includes unbalanced communication and locality. The authors extend the cost model by replacing the term  $h$ -relation in the BSP cost model by an

$(M, k_1, k_2)$ -relation, where  $M$  is the total number of messages,  $k_1, k_2$  is the maximal number of message a single processor sends respectively receives, thus a (full)  $k$ -relation is a  $(kp, k, k)$ -relation in the E-BSP model.

The locality of a superstep is defined as the maximal difference of the identifiers of any sender/receiver pair. The implementation should use a numbering of the processors, such that two processors with a small difference in their identifiers have a short distance in the underlying physical network, for instance, using a peano embedding for a mesh of dimension two. The PUB library uses such embeddings for some mesh architectures, for instance, the Parix GCel/GCPP.

A comparison with other models can be found in Ben Juurlink's PhD thesis [Juu97], including comparisons of communication times of sorting algorithms for the E-BSP and for the standard BSP model.

### 2.2.5 Decomposable BSP (dBSP)

The *Decomposable BSP model* by Martin Beran [Ber99] is another approach to include locality. A dBSP computer can dynamically partition itself into smaller parts which behave as dBSP computers with smaller  $p$ . Communication between processors of different partitions is impossible. The parameters  $g$  and  $L$  of the original BSP model are replaced by functions of  $p$ . In most implementations,  $g(p)$  and  $L(p)$  increase with  $p$ . If the synchronization is implemented using message passing and a tree as communication structure,  $L(p)$  is usually of order  $\mathcal{O}(\log p)$ .

The paper shows a slowdown of  $\mathcal{O}(\max\{g(p), L(p)\})$  for a superstep of a dBSP computer simulated on a BSP computer, and an additional cost of  $\mathcal{O}((1+L(p)+g(p)) \cdot \log p)$  for the partition and join operations.

Besides the performance advantage, the model is useful in practice, if different algorithms should run simultaneously on parts of a parallel computer. The PUB library supports this model: it is possible to partition the machine into independent BSP computers; furthermore, BSP parameters of the machine are given for the actual size of the partition.

### 2.2.6 H-BSP

The *Heterogeneous Bulk Synchronous Parallel (HBSP) model* by Tiffani L. Williams and Rebecca J. Parsons [WP00] is a generalization of the BSP model. The gap  $g$  is substituted by the gap  $g_i$ ,  $i = 0, \dots, p - 1$  of each processor. The parameter  $g_i$  describes the rate at which a processor can send data to the network. Additional parameters  $c_i$ ,  $i = 0, \dots, p - 1$ , define the computation power of the processors, relative to the slowest one.

The cost function is adapted, such that the local work is weighted by the  $c_i$ s. The term  $g \cdot h = g \cdot \max_{0 \leq i < p} \{h_i\}$  for the communication cost is replaced by  $\max_{0 \leq i < p} \{g_i h_i\}$ ,

where  $h_i$  is the amount of data sent to the network by processor  $i$ .

How to use the model for designing algorithms is shown by some examples: prefix sums, matrix multiplication, and randomized sample sort.

### 2.2.7 (d,x)-BSP

The *(d,x)-BSP model* by Guy E. Blelloch et al. [BGMZ97] is an extension of the BSP model designed for high performance parallel computer with global shared memory. The additional parameters  $d$  (delay) and  $x$  (expansion) describe the timing of the memory, i. e., the time for an access (typically in the order of 10 clock cycles for machines in 1996) and the ratio of the number of processors and the number of parallel accessible memory banks. The cost functions is expanded by a term for the maximal number of accesses to a memory bank, scaled with the delay  $d$ .

Typical example machines for this model were NEC SX3 ( $p = 4, x = 256$ ), Cray C90 ( $p = 16, x = 64, d = 6$ ), or Cray J90 ( $p = 16, x = 64, d = 14$ ).

### 2.2.8 CREW-BSP

The standard BSP model allows point-to-point messages and barrier synchronizations only. Sometimes the hardware supports other communication patterns, for example, broadcasts are easy to realize if the communication medium is shared, for example a bus.

The *CREW-BSP-model* (concurrent read exclusive write) by Michael T. Goodrich [Goo00] extends the standard BSP-model by arbitrary multicast operations, i. e., the destination of a message is a set of processors. The same paper defines also a CRCW-BSP computer, which is able to combine data from more than one processor using an arbitrary relation. This computer is more powerful than a standard BSP-computer, for instance, it can compute the maximum of  $p$  numbers in constant time.

## 2.3 Other Parallel Models

In this section we describe two parallel models, which are similar to the BSP model, but does not divide the time into supersteps, thus, they are not synchronous models.

### 2.3.1 Coarse grained multicomputer (CGM)

The *Coarse Grained Multicomputer (CGM)* was introduced 1993 by Dehne, Fabri, and Rau-Chaplin [DFRC93, DFRC96]. It is the first model of a family of parallel computation models called coarse grained parallel computing (CGP) and is similar to the LogP model (which we will describe in the next section) and the BSP model. A CGM( $n, p$ )

consists of  $p$  processors with  $\mathcal{O}(\frac{n}{p})$  local memory each, and an arbitrary interconnection network. It is said to be “coarse grained” because the size of the memory is defined to be “considerably larger than  $\mathcal{O}(1)$ ”. Dehne et al. assume that  $\frac{n}{p} \geq p$ .

The basic idea behind this model is the following: The algorithms partition the given problem into  $p$  subproblems of size  $\mathcal{O}(\frac{n}{p})$ . These subproblems are solved sequentially by the processors; afterwards the results are combined using a global communication operation. This scheme is iterated; for many problems a constant number of iterations is sufficient. For the global operation sorting is used. Many parallel architectures have global sorting as a system call, or a highly optimized implementation can be obtained as public domain software. Other communication operations, for example, broadcast (segmented, multinode), total exchange, or partial sum (scan) can be implemented using a constant number of global sort operations. So in the CGM sorting is the only way to communicate, and the cost for an algorithm is based on  $T_S(n, p)$ , the time needed to sort  $n$  data items on  $p$  processors.

### 2.3.2 LogP

The *LogP model* was introduced by Culler, Karp, Patterson, Sahay, Schausser, Santos, Subramonian, and von Eicken [CKP<sup>+</sup>93] in 1993 and tries to model a processor network by four parameters:  $L$  is the *latency*, i. e., the delay for sending a very small message from a source to a destination,  $o$  is the *overhead*, the time a processor is busy starting a transmission or reception of a message, including the time needed for computing message headers. Parameter  $g$  is the *gap*, the minimal time interval between consecutive message transmissions or consecutive message receptions, the reciprocal is the per processor bandwidth.  $P$  is the number of processors. Thus, LogP does not consider the topology of the network, similar to the CGP model. Furthermore, the capacity of the network is limited, i. e., at most  $\lceil L/g \rceil$  data can be in the network at the same time.

On the one hand this model is more general than CGM or BSP as it allows arbitrary asynchronous communication and does not restrict the algorithms to global communications or supersteps, on the other hand proofs of correctness or running time analysis of algorithms may be much complexer.

## 2.4 Conclusion

We described parallel models, from the PRAM to BSP and its extensions. We think that the BSP model and its extensions are a good way to model parallel systems such that algorithm engineers can develop parallel algorithms that run fast on a wide area of parallel systems, because: On the one hand the PRAM model is hard to realize, because multiple accesses to a global shared memory require an expensive cross bar system. On the other hand the plain BSP model is too restricted, i. e., there are algorithms that does

not fit into BSP very well, but some relaxations, for instance, oblivious synchronization or a decomposable machine increase the number of possible applications.

In some areas it may even be needed to soften the model a little, to allow asynchronous messages in some parts, but at the cost of loosing some nice features of the synchronous model, for example, simplicity of verification. Our implementation, the PUB library, which is described in Section 4.1.2, follows that direction.

# Chapter 3

## Algorithms

A suitable model for parallel computing should support the development of efficient algorithms. This chapter starts with an overview of algorithms for the bulk synchronous setting. In the second part we will propose a system which can be used to build libraries of algorithms for more complex problems by combining basic algorithms. It configures an optimal algorithm based on information of the input (e. g., the size of the input), and the architecture, i. e., the BSP parameters, using a library of BSP algorithms and their running time descriptions.

### 3.1 BSP-Algorithms

In this section we will give a short overview of algorithms for the BSP model to show that it is widely used in algorithm design. Here we focus on algorithms and their theoretical analysis in the BSP model. In Section 4.2 we will show some implementations of BSP algorithms.

There are many BSP algorithms for various different application areas. Simple examples are basic communication functions (e. g., broadcast or parallel prefix operations, which are already mentioned in the paper introducing the BSP model [Val90]) and sorting. Examples for more complex applications are graph algorithms, optimizations, simulations, and algebra.

#### 3.1.1 Basic Communication Algorithms

The BSP model supports point-to-point messages and synchronizations only. All other communication patterns, for instance *broadcast* (one processor sends a message to all others), *multicast* (one message to a set of destination), *total exchange* (every processor has data for all other processors), or the parallel prefix operations *scan* and *reduce* have to be realized on top of these point-to-point messages.

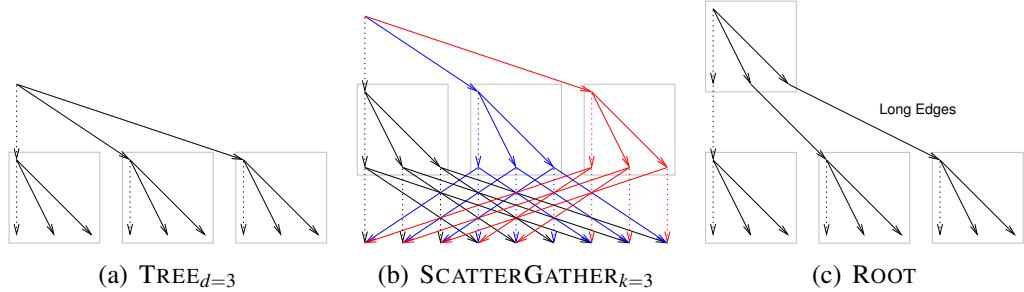

Figure 3.1: Broadcast Algorithms

Some implementations of BSP are more powerful and support such advanced communication functions directly, for example, the PUB library (Section 4.1.2), which is sometimes more efficient [Rie00], and more comfortable for the user. There are also models that allow this, like CREW-BSP (Section 2.2.8), but they are not as widely used as other BSP models.

## Broadcast

In the *Broadcast* problem one processor has one message of size  $m$  that has to be sent to all other processors. A basic algorithm TREE is given by the author of the BSP model [Val90]: in  $\log_d p$  supersteps each processor that knows the message sends it to  $d$  others. As  $d$  messages of size  $m$  are sent in each superstep, a superstep takes time  $\mathcal{O}(dm \cdot g + L)$ , thus the total time is  $\mathcal{O}((dm \cdot g + L) \log_d p)$ .

Other broadcast algorithms can benefit from locality, for example in the dBSP model. An example for such an algorithm is ROOT [JKMR03]: the message is sent to  $\sqrt{p}$  subgroups in the first step, and distributed inside these groups by a recursive broadcast call.

In [Rie00] other broadcast algorithms are analyzed: PTREE (pipelined version of the standard algorithm TREE), and SCATTERGATHER, an algorithm that splits the message in  $k$  parts, broadcasts the parts to subgroups, and then sends the parts from a subgroup to all other nodes (similar to an all-to-all communication). These algorithms are illustrated in Figure 3.1, their running time in the dBSP model can be found in Table 3.1.

### 3.1.2 Parallel Prefix Operations

In the *Parallel Prefix* problem every processor  $i$  has some data  $x_i$ , and for a given associative operation  $\otimes$  one needs to compute  $x_0 \otimes x_1 \otimes \dots \otimes x_i$  for all  $i = 0, \dots, p-1$ . This problem is sometimes referred to as *scan*. A simpler problem is called *reduce*: instead of computing the results for all  $i$ , only  $\bigotimes_{i=0}^{p-1} x_i$  is needed. A simple tree based algorithm with

Table 3.1: Running Times of Broadcast Algorithms in the dBSP Model [Rie00]

| Algorithm     | Result                                                                                                                                                                                        |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tree          | $\sum_{i=0}^{\lceil \log_d p \rceil - 1} \left( (d-1) \cdot (m \cdot g(\lceil \frac{p}{d^i} \rceil) + L(\lceil \frac{p}{d^i} \rceil)) \right)$                                                |

| PTree         | $k \cdot (L(p) + 2 \lceil \frac{n}{k} \rceil \cdot g(p)) + \sum_{i=1}^{\lceil \log p \rceil - 1} L\left(\frac{p}{2^i}\right) + 2 \lceil \frac{m}{k} \rceil \cdot g\left(\frac{p}{2^i}\right)$ |

| ScatterGather | $2(m \cdot g(p) + L(p)) + \text{time for broadcast of } \frac{m}{k} \text{ to } \frac{p}{k} \text{ processors}$                                                                               |

| Root          | $\sum_{i=0}^{\lceil \log \log p \rceil} 2^i \left( m \cdot g(\lceil p^{1/2^i} \rceil) + L(\lceil p^{1/2^i} \rceil) \right)$                                                                   |

Table 3.2: Running Times of Sorting Algorithms

| Algorithm              | Result                                                                                                                        | Reference |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------|

| CommunEfficientParSort | $\mathcal{O}\left(\frac{n \log n}{p} + \frac{\log n}{\log(n/p)} \left(\frac{n}{p} \cdot g + L\right)\right)$                  | [Goo00]   |

| Randomized SampleSort  | $\mathcal{O}\left(\frac{n \log n}{p} + (p^\epsilon + \frac{n}{p}) \cdot g + L\right)$ w. h. p.                                | [GV94]    |

| Regular Sampling       | $\mathcal{O}\left(\frac{n \log n}{p} + \frac{n}{p} \cdot g + L\right)$ for $n \geq p^3$                                       | [SS92]    |

| XY-Sort                | $n = \sqrt{p}$ , $\mathcal{O}(\sqrt{p} \cdot g + L) + T_{\text{red}}$<br>$T_{\text{red}}$ time for reduce on $\sqrt{p}$ proc. | [Rie00]   |

a tree of degree  $d$  archives the same order of running time than the broadcast algorithm TREE.

### 3.1.3 Sorting Algorithms

Sorting is one of the basic problems in computer science. It is well understood and there are sorting algorithms for almost all parallel computing models. Some results for BSP sorting algorithms are summarized in Table 3.2.

**Sample Sort.** Parallel SAMPLESORT is an extention of the sequential QUICKSORT algorithm. QUICKSORT splits the input into two parts, elements smaller than a splitting element and those that are greater. Next these two groups are sorted recursively. In SAMPLESORT, the data is partitioned into  $p$  groups according to  $p-1$  *splitters*. Each processor sends the keys to the right destination, next the received keys are sorted locally. The main problem is to find good splitters such that the sizes of the partitions are nearly equal. For this purpose samples of the input are selected, sorted, and used as splitting elements. The main part of the analysis is about the number of samples. An algorithm based

Table 3.3: All-pairs Shortest Paths Algorithms [Tis01]

| Algorithm                | Result                                                                                                                           |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Dijkstra / Path Doubling | $\mathcal{O}\left(\frac{n^3}{p} + \frac{n^2}{p^{2/3}} + (\log p)L\right)$ ,<br>$\mathcal{O}\left(\frac{n^3}{p} + n^2 + L\right)$ |

| Floyd-Warshall-algorithm | $\mathcal{O}\left(\frac{n^3}{p} + \frac{n^2}{p^\alpha} g + p^\alpha L\right)$ , $\frac{1}{2} \leq \alpha \leq \frac{2}{3}$       |

on this approach, proposed by Gerbessiotis and Valiant [GV94], needs a running time of  $\mathcal{O}\left(\frac{n \log n}{p} + (p^\varepsilon + \frac{n}{p}) \cdot g + L\right)$  for sorting  $n$  keys, with high probability for any constant  $0 < \varepsilon < 1$ , if  $p \leq n^{1-\delta(\varepsilon)}$  where  $\delta(\varepsilon)$  is a small constant depending only upon  $\varepsilon$ .

The randomized sampling can be replaced by regular sampling. This technique is described by Hanmao Shi and Jonathan Schaeffer [SS92].

**XY-Sort.** XY-SORT is a sorting algorithm used as an example in [Rie00]. It sorts  $\sqrt{p}$  keys on  $p$  processors with a constant number of communication operations: the keys are distributed using two multicast operation, compared in constant time, and the total rank of each key is calculated with  $\sqrt{p}$  parallel reduce operations, each on a subgroup of size  $\sqrt{p}$ .

### 3.1.4 Graphalgorithms

There are many algorithms for problems based on graphs in the literature. The challenge for the algorithm designer is that the input is not as regular as in other application areas like matrix multiplication, thus the algorithms are almost not oblivious, i. e., the communication pattern is dependent on the input.

**Shortest Path.** There are two main sequential algorithms for shortest path problems: Dijkstra's algorithm and the algorithm of Floyd-Warshall. For the *All-Pairs-shortest Paths problem* one can execute DIJKSTRA algorithm in parallel for all sources, or use a parallel variant of FLOYDWARSHALL, which is based on matrix potentialization. This algorithm is more communication efficient, but needs more than a constant number of supersteps. Table 3.3 summarizes the results of Alexandre Tiskin [Tis01].

**Minimal Spanning Tree.** We give a formal definition of the problem in Section 3.2.2. There are various parallel algorithms for the calculation of a minimal spanning tree. A communication lower bound and an overview of BSP algorithms can be found in the PhD thesis of Ingo Rieping [Rie00]. The algorithms are made up of some modules: BSP-MERGE, which merges two minimal spanning trees, and BSPBORUVKA, which executes

Table 3.4: Running Times of MST Algorithms

| Algorithm | Result                                                                                                                                                                                                                            | Reference             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| MSTMerge  | $\mathcal{O}\left(T_{\text{seq}}(n, \frac{m}{p}) + \frac{m}{p^{1+\varepsilon/2}} + L\right)$ for $p^{1+\varepsilon} \leq m/n$                                                                                                     | [Rie00]               |

| MSTDense  | $\mathcal{O}\left(n \log \log p + \frac{m}{p} + n \cdot g + \log p \cdot L\right)$ for $p \leq \frac{m}{n}$ ,<br>1-optimal if $p \log \log p = o(\frac{m}{n})$                                                                    | [ADJ <sup>+</sup> 98] |

| MSTSparse | $\mathcal{O}\left(\frac{n \log p + m}{p} + \frac{m}{p} \cdot g + \frac{(\log p)^2}{\log((m+n)/p)} L\right)$ with prob. $\geq 1 - n^{-c}$<br>for any $c > 0$ , $p \leq m+n$ , $\log p \leq \frac{m}{n} \leq p$ , $m \geq n \log n$ | [ADJ <sup>+</sup> 98] |

| BSP-AS    | $\mathcal{O}\left(\frac{m+n}{p} \log p + \frac{m+n}{p} \log p \cdot g + \frac{(\log p)^2}{\log((m+n)/p)} L\right)$ for $n+m \geq p$                                                                                               | [ADJ <sup>+</sup> 98] |

so-called Borůvka steps. In each step a (super-)vertex selects a cheapest outgoing edge and joins the two (super-)vertices to a new supervertex. A third module is BSP-AS, a BSP version of the algorithm due to Awerbuch and Shiloach, which was originally developed for a CRCW-PRAM. By combining these modules one get efficient algorithms for sparse as well as for dense graphs.

The minimal spanning tree problem is also used as an example for combining several BSP algorithms together to an optimal algorithm, adaptive to the BSP computer and to the input size. The modules BSPMERGE and BSPBORUVKA and their combinations are described in more details in Section 3.2.2.

### 3.1.5 Optimization

One kind of optimization is searching for an optimal solution in a given space of feasible solutions. Starting from a solution the algorithms perform small legal changes to the instance and try to improve it concerning a given cost function. As the changes are usually chosen by an algorithm with some random choices, a natural parallelization is to start the search in parallel on different processors. After some time the processors exchange their locally best solutions and start searching at the globally best solution found so far. This scheme fits perfect to the BSP model: in each superstep the local search is done, at the end of the superstep the best solution is computed by a parallel prefix operation using max (or min) as combine function. This approach is used by Klaus Brockmann and Ingo Rieping for a parallel tabu search algorithm (unpublished), based on parallel tabu search implementations from Stefan Bock and Otto Rosenberg [BR00].

### 3.1.6 Simulations

**Discrete Event Simulation.** In a *discrete event simulation* there are events at certain points of time. These events have to be processed in non decreasing time order. Each

event can change the state of the simulation, and introduce new events.

One approach for a parallel algorithm is to distribute parts of the simulation to the processors and send events concerning parts simulated on other processors by messages. This is implemented by an event queue locally on each processor. For high efficiency these queues cannot be synchronized with each other, i. e., the events processed in parallel may not be in the right order concerning global time. One solution is called *Optimistic Discrete Event Simulation*. Each processor has its own local virtual time (*lvt*) and processes events in its local queue in non decreasing time order. If it receives an event with a timestamp earlier than the own *lvt*, it rollbacks the simulation (time warp) and restart it at that time, sending *anti-messages* for each wrong message it has sent in the past.

Several bulk synchronous parallel algorithms for optimistic discrete event simulation are proposed by Radu Calinescu [Cal96].

**N-Body.** The *N-body problem* is the problem of simulating the movement of a set of bodies (or particles) under the influence of some type of force, for example gravitational or electrostatic. A basic approach is to simulate the system by advancing the bodies in discrete time steps. In each time step, the algorithm computes (or approximates) the force exerted on each body due to all other bodies; this determines the acceleration and speed of that body during the next time step.

Efficient parallel implementation of  $\mathcal{O}(N)$  adaptive tree codes for the BSP model are given by David Blackston and Torsten Suel [BS97].

### 3.1.7 Algebraic Problems

Algebraic problems have been addressed by parallel algorithm designers since long ago. Operations on matrices, for instance, multiplication of two matrices, are often used as an introduction to parallel algorithms. Many algorithms are oblivious, they have a static communication behavior that simplifies things like load balancing. The results for the following algorithms are summarized in Table 3.5.

**Matrix Multiplication.** There are different algorithms for *matrix multiplication*. A BSP version of the standard algorithm is given as a simple example of a tightly synchronized algorithm by Valiant [Val90], a faster algorithm using the idea of Strassen to reduce the work is given by William F. McColl [McC95a].

McColl and Tiskin propose other algorithms optimizing the memory use. In [MT99] they analyse memory efficient BSP algorithms for both the standard and the fast matrix multiplication.

**Solving Linear Equations.** A system of linear equations over a domain  $\mathcal{D}$  is given by a matrix  $A \in \mathcal{D}^{n \times m}$  and a vector  $b \in \mathcal{D}^n$ . The problem is to find one or all solutions  $x \in \mathcal{D}^n$

Table 3.5: Algebraic BSP algorithms

| Problem                                     | Algorithm              | Result                                                                                                                       | Reference               |

|---------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Matrix Multiplication                       | naive                  | $\mathcal{O}\left(\frac{n^3}{p} + \frac{n^2}{\sqrt{p}} \cdot g + L\right)$                                                   | [Val90]                 |

|                                             | standard               | $\mathcal{O}\left(\frac{n^3}{p} + \frac{n^2}{p^{2/3}} g + L\right), p \leq n^2$                                              | [McC95b]                |

|                                             | Strassen               | $\mathcal{O}\left(\frac{n^{\log_2 7}}{p} + \frac{n^2}{p^{2/\log_2 7}} \cdot g + L\right), p \leq n^{2\log_2 7/(2+\log_2 7)}$ | [McC95a]                |

| Dense Matr. $\times$ Vec.                   | standard               | $\mathcal{O}\left(\frac{n^2}{p} + \frac{n}{\sqrt{p}} g + L\right), p \leq n$                                                 | [McC95b]                |

| Sparse Matr. $\times$ Vec. <sup>1</sup>     |                        | $\mathcal{O}\left(\frac{cn}{p} + n + \left(1 - \frac{1}{p}\right) n \cdot g + L\right)$                                      | [Bis04]                 |

| Gaussian Elimination<br>with pairwise elem. | block rec.             | $\mathcal{O}\left(\frac{n^3}{p} + \frac{n^2}{p^\alpha} g + p^\alpha L\right), \frac{1}{2} \leq \alpha \leq \frac{2}{3}$      | [Tis07]                 |

|                                             |                        | $\mathcal{O}\left(\frac{n^3}{p} + \frac{n^2}{p^\alpha} g + p^\alpha L\right), \frac{1}{2} \leq \alpha \leq \frac{2}{3}$      | [Tis07]                 |

| LU Decomposition                            |                        | $\mathcal{O}\left(\frac{n^3}{p} + \frac{n^2}{\sqrt{p}} \cdot g + n \cdot L\right)$                                           | [Bis04]                 |

|                                             |                        | $\mathcal{O}\left(\frac{n^3}{p} + \frac{n^2}{\sqrt{p}} \cdot g + \sqrt{p} \cdot L\right)$                                    | [McC95b]                |

|                                             |                        | $\mathcal{O}\left(\frac{n^3}{p} + \frac{n^2}{p^{5/8}} \cdot g + n \frac{\log p}{\log(L/g)} \cdot L\right), p \leq n^{8/5}$   | [Juu97]                 |

| Solution Triangular<br>Lin. System          | back sub-<br>stitution | $\mathcal{O}\left(\frac{n^2}{p} + n \cdot g + p \cdot L\right)$                                                              | [McC95b]                |

| Fourier Transform.                          | FFT                    | $\mathcal{O}\left(\frac{n \log n}{p} + \frac{n}{p} \cdot g + L\right), n \geq p^2$                                           | [Bis04]                 |

| Exponentiation in<br>Finite Fields          | addition<br>chains     | $\mathcal{O}(\log p \cdot (g + L))$                                                                                          | [Nöc01]                 |

| Poly. Factorization                         |                        |                                                                                                                              | [BvzGG <sup>+</sup> 01] |

<sup>1</sup> $c$  denotes the number of non-zero elements of the matrix

that satisfy the equation  $A \times x = b$ . There are different algorithms for solving this equations with different objectives: A parallel version of the standard gaussian elimination is analyzed by Alexandre Tiskin [Tis03, Tis07]. If there is more than one such system with the same matrix  $A$ , one could split  $A$  into a product of two triangle matrices  $A = L \times U$ . Knowing  $L$  and  $U$ , the solution can be computed efficiently for various instances of  $b$ . This so called LU-decomposition is one of the examples in [Bis04].

**Other Computer Algebraic Problems.** Michael Nöcker analyses the problem of exponentiation in finite fields in his PhD thesis [Nöc01] and propose data structures for fast algorithms. As a computation model for the parallel algorithms he uses amongst others

the BSP model. Together with others he also uses BSP for fast factorization of large polynomials [BvzGG<sup>+</sup>01].

## 3.2 Composition of Efficient Nested BSP Algorithms

The results in this section are based on work done for my diploma thesis [Bon02]. The actual running time of implementations of parallel algorithms depends on two groups of parameters, namely “software” parameters, for example, the number of memory accesses or the degree of a broadcast tree, and “hardware” parameters, for instance, the time necessary to set up a communication or the number of available processors. This leads to the observation that for different parameter constellations different “plain” algorithms are the fastest ones. Furthermore, sophisticated parallel algorithms often introduce subproblems or make recursive calls. For example, efficient parallel algorithms for minimum spanning tree computation use parallel sorting algorithms, broadcast methods, and make recursive calls. For each subproblem, one can choose between different algorithms.

Hence, in order to have efficient parallel programs for an actual machine, they have to be *configured*. This means that one has to decide which parallel algorithm has to be taken and which subroutines have to be used on what portion of the parallel machine depending on hardware parameters as well as on the input instance for the algorithm.

For the BSP model and its extensions, a large variety of efficient parallel algorithms for many problems has been developed and quite accurately analyzed (see Section 3.1).

This enables the programmer to choose from a pool of available algorithms for the composition of the final program on his or her parallel machine. However, configuring a parallel program becomes quickly very complex due to the various parameters and (possibly mutually influencing) dependencies. Therefore, it should be done automatically by a program we call *configurator* [BMW02].

### 3.2.1 The Configurator: Input/Output Specification and Algorithm

In what follows, we define how to describe algorithms and introduce the term *schedule* for a given problem. This is the necessary adaptation of the BSP model. A schedule fixes the algorithms and all free parameters to be used to solve a problem and all occurring subproblems. The input of the configurator is the problem  $\Pi$ , the BSP computer (i. e., which BSP parameters apply), and a specification of the input of  $\Pi$ . The configurator works on a library of algorithm descriptions and outputs the schedule. This schedule is used during the execution to determine the real (sub-)program that will be executed. It is the equivalent to the actual parallel program.

**Algorithm Description.** An *algorithm description*  $A$  consists of the following five components:

---

BinTreeBroadcast:=(*Broadcast*, $p_{count}$ , $v_{count}$ , $t$ , $s_{count}$ , $s$ )

- $p_{count}(n, p, p_{max}) := \{p\}$ , use all processors

- $v_{count}(n, p, c) := 1$ , only one variant

- $t(n, p, c, v) := \lceil \log_2 p \rceil (2 \cdot \max(n, B(p)) \cdot g(p) + L(p))$ ,

one superstep per tree level,  $n$  bytes data send to each of the 2 children

- $s_{count}(n, p, c, v) := 0$ , no subproblems

- $s$  undefined function

---

Figure 3.2: Example for an Algorithm Description for BINARYTREE Broadcast

---

1. The problem  $\Pi$  that the algorithm solves.

2. The set  $p_{count}$  of feasible machine sizes, i. e., the machine sizes for which the algorithm  $A$  can work depending on the input for  $A$ .

3. The number  $v_{count}$  of different possible choices for fixing the free algorithmic parameters of  $A$ . For example, in a broadcast algorithm this might be the number of feasible tree degrees.

4. The function  $t$  that computes, for a given variant of the algorithm, the running time of  $A$  without the time  $A$  will spend in subcalls. Note that in the algorithm description, it is not known in advance which algorithms for the subproblems will be used in the schedule.

5. The function  $s$  that computes a list of subproblems for all possible variants of  $A$ . Each list item contains the subproblem, the description of the input of the subproblem, and the processors involved.

Figure 3.3 shows an example for the Broadcast algorithm TREE. A more formal specification of the components and a more detailed description can be found in [Bon02]. We say that  $A$  solves problem  $\Pi$ .

**Schedule.** Given a set  $\mathcal{P}$  of problems and a set  $\mathcal{A}$  of algorithm descriptions, a *valid schedule*  $S$  for a problem  $\Pi \in \mathcal{P}$  and its input description is defined recursively. An algorithm  $A \in \mathcal{A}$  solving  $\Pi \in \mathcal{P}$  is fixed, as well as all free parameters, and there are valid schedules for all occurring subproblems  $\Pi'_i \in \mathcal{P}$ . The recursion terminates when there are

Let  $d_v \geq 2$  be the  $v$ -th integer number, s. t.  $d_v|p$  ( $d_v$  is the tree degree of variant  $v$ ).

TreeBroadcast: = ( $Broadcast, p_{count}, v_{count}, t, s_{count}, s$ )

- $p_{count}(n, p, p_{max}) := \{p\}$ , use all processors

- $v_{count}(n, p, c) := |\{d \in \{2, \dots, p\}; d|p\}|$ ,

variants are all possible tree degrees  $d$ ,  $d$  is valid tree degree  $\Leftrightarrow d$  divides  $p$

- $t(n, p, c, v) := \max(n, B(p)) \cdot (d - 1) \cdot g(p) + L(p)$ ,

time for the first level of the tree

- $s_{count}(n, p, c, v) := \begin{cases} 0 & \text{if } p = d_v \\ d_v & \text{otherwise} \end{cases}$

If the degree  $d_v$  is smaller than  $p$ , there is one subproblem (Broadcast)

- $s(n, p, c, j, v) := (Broadcast, n, p/d_v, 1, d_v)$ ,

input for subproblem Broadcast has input size  $n$  for  $p/d_v$  processors, and is executed  $d_v$  times in parallel

Figure 3.3: Example for an Algorithm Description for TREE Broadcast

no further subproblems. So a valid schedule  $S$  can be viewed as a *schedule tree* directed from the root to the leaves.

Let  $S$  be a valid schedule for a problem  $\Pi$  that has to be executed on a  $p$  processor BSP machine given by its machine parameters. The *cost* of  $S$ , i. e., its predicted running time on the BSP machine, is defined along the schedule tree. The cost of the root is the running time of algorithm  $A$  (without the time spent in solving subproblems) given by the function  $t$  (see point (4) above) plus the sum of the cost of all children of the root.

**Configurator.** We have implemented a prototypical configurator that computes a schedule tree (in a bottom-up way) and, hence, a valid schedule with minimum cost by a brute force search testing all possible valid schedules. Note that this computation is offline, i. e., it is done only once before the schedule is used for many same-sized inputs. The configurator works for arbitrary problems  $\Pi$  and algorithm descriptions  $A$ . Although the execution time of the configurator may be exponential in the number of algorithms, for our MST experiments the configuration was finished in less than five minutes.

### 3.2.2 An Example: Parallel Minimum Spanning Tree Algorithms

As example for a complex problem with a rich combinatorial structure, a usually irregular communication pattern, and a variety of sophisticated algorithms that in turn use clever

subalgorithms, we use the problem of computing a minimum spanning tree (MST) for an undirected weighted graph. For the algorithmic background of the MST problem, see [CLR90, Chap. 24].

**Minimal Spanning Tree (MST).** Given an undirected graph  $G = (V, E)$  with edge weights  $w : E \rightarrow \mathbb{Q}$  a tree  $T = (V, F)$  with  $F \subseteq E$  and  $|F| = |V| - 1$  is called a *spanning tree*. The weight  $w(T)$  of a spanning tree is  $w(T) := \sum_{e \in F} w(e)$ .  $T$  is a *minimal spanning tree*, if and only if  $w(T) \leq w(T')$  for all spanning trees  $T'$  of  $G$ .

### 3.2.3 Algorithms for the MST problem

Each of our implemented algorithms is based on the following three basic operations:

1. Algorithm KRUSKAL: Kruskal's sequential algorithm ([CLR90, Sec. 24.2]) tests for every edge, in order of increasing weights, whether it can be included in the minimum spanning tree, i. e., whether it connects two connected components (called *supervertices*) created by the edges chosen so far.

2. Operation “Borůvka step”: In a Borůvka step (for a nice and detailed description, see [Göt98]) each supervertex selects its cheapest outgoing edge. These edges are added to the MST edges, avoiding cycles (by construction, these cycles are not longer than 2). After that, the new supervertices, i. e., the connected components, are calculated, the edges are relabeled according to the new supervertices, and all edges belonging to the same supervertex are removed. This step reduces the number of vertices at least by a factor of two.

We have implemented two different algorithms for this problem, namely DENSE-BORUVKASTEP which is step (2) of algorithm MST-DENSE in [ADJ<sup>+</sup>98], and BORUVKASTEP which is in essence from [DG98, Göt98].

DENSEBORUVKASTEP is specially designed for dense graphs. It calculates the lightest edge of all locally stored edges and then executes a parallel prefix operation to determine the edges with global minimum weights, for every supervertex.

BORUVKASTEP creates adjacency lists for all vertices by grouping edges of the same vertices by integer sorting. Then the minima of each group are calculated by a parallel segmented prefix operation (see [Göt98], Section 4.1.4). Our implementation uses a sequential algorithm for computing the connected components.

3. Operation “MSTMERGE”: This operation (Step (2) of MSTMERGE in [ADJ<sup>+</sup>98]) merges local MSTs. It uses a  $d$ -ary communication tree.  $d$  is a free parameter to be set by the configurator. Each tree node sends its MST to its predecessor, the

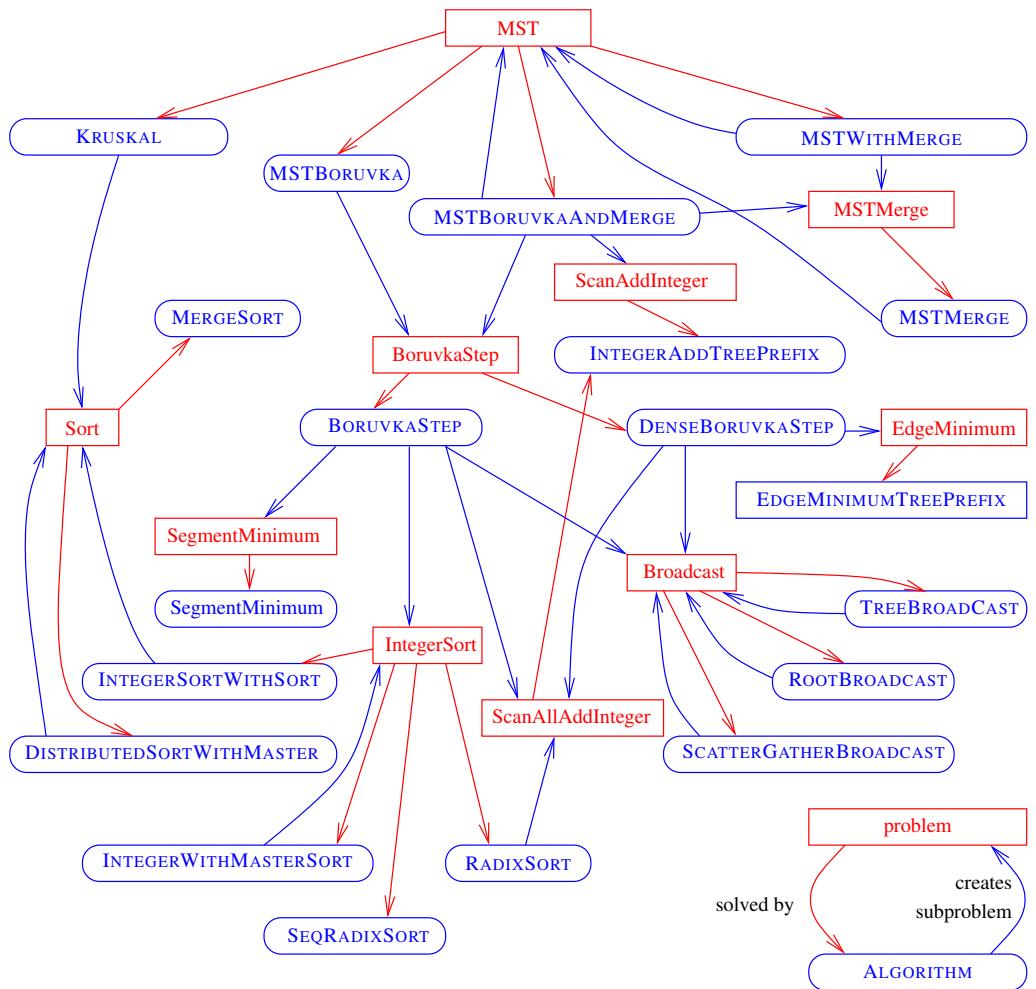

Figure 3.4: Map of Algorithms used for Configurator Test

predecessors merge the MSTs by calculating an MST of all edges received. In the end, the root of the communication tree knows the global minimum spanning tree.

Figure 3.4 shows a full map of all used algorithms, the subproblems, and their relationships. Note that the map even contains cycles that are caused by recursive calls. Of course, the configuration terminates because the parameters usually decrease.

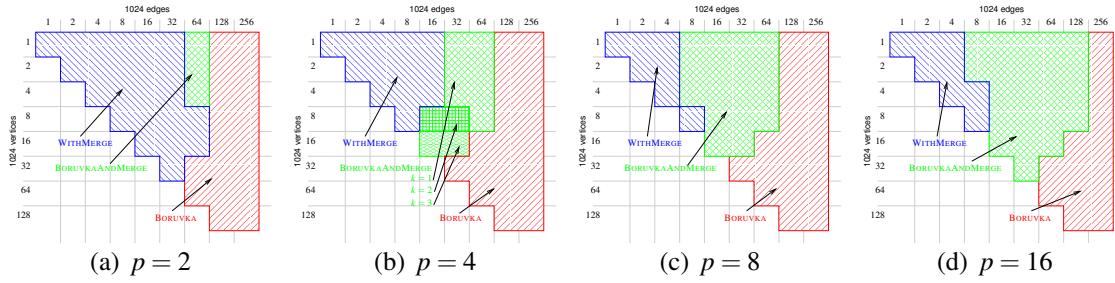

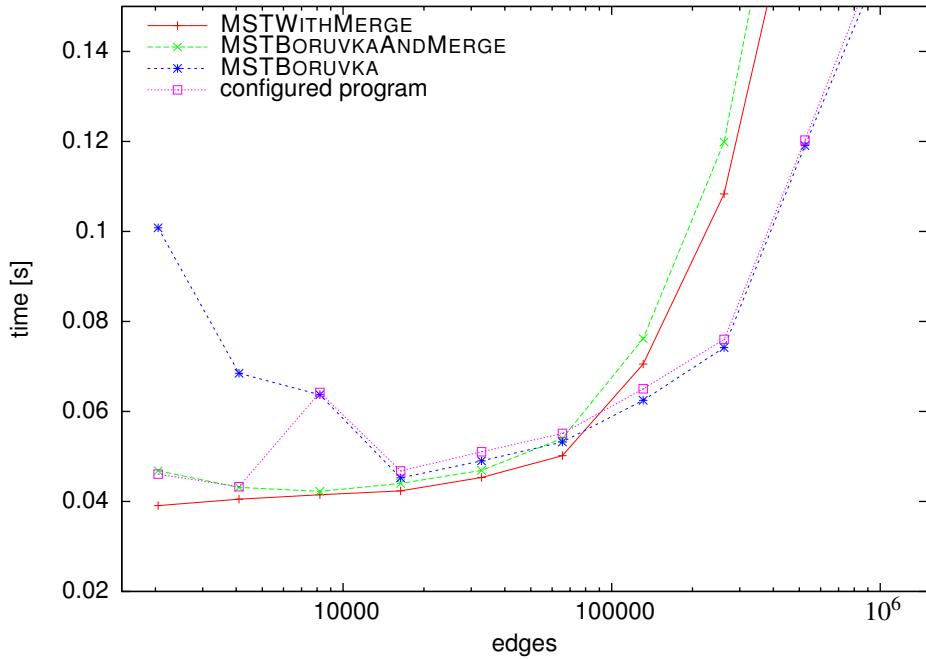

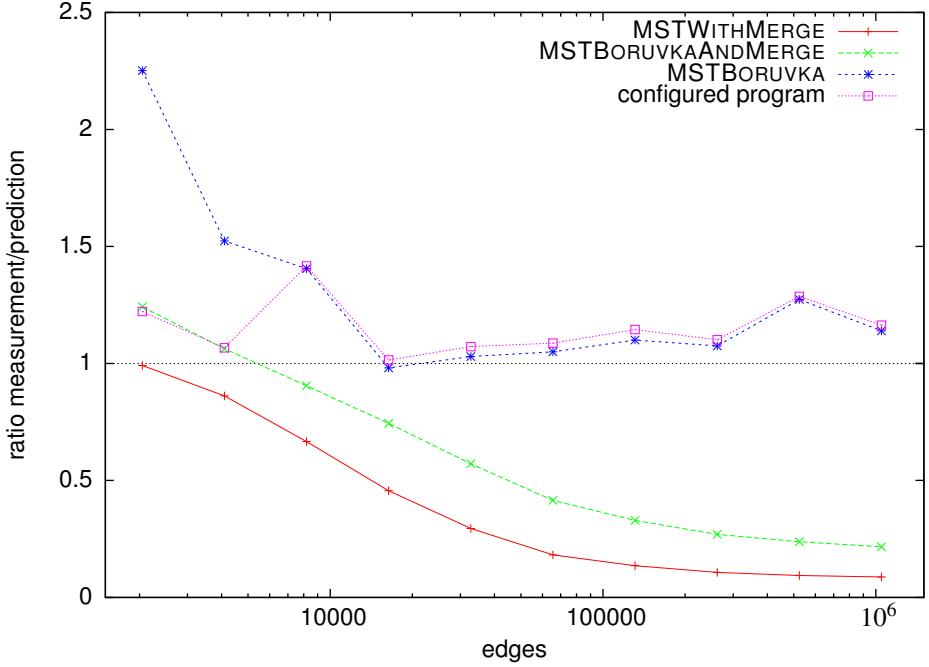

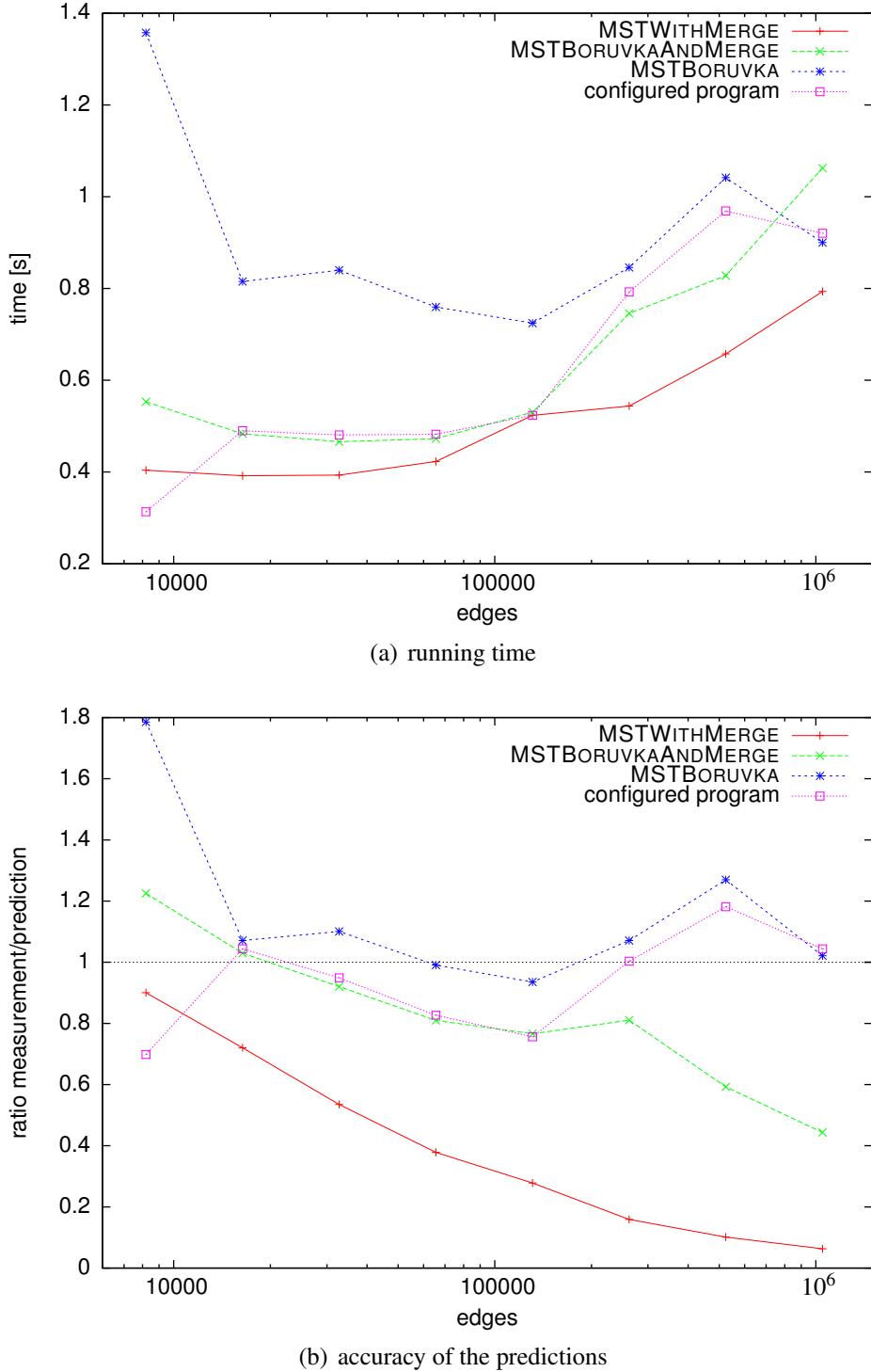

In the following, we give short remarks on the three parallel MST algorithms that can be found in the map. The algorithmic description of our general solution of the MST problem has three main variants: **MSTWITHMERGE**, **MSTBORUVKA**, and **MSTBORUVKAANDMERGE**.

**MSTWITHMERGE**: This algorithm solves the MST problem by calculating the local

Figure 3.5: Results of the Configuration on a Pentium III Workstation Cluster with SCI

spanning tree and merges all these trees with operation MSTMERGE. Then the result is distributed from the root to all nodes.

**MSTBORUVKA:** This algorithm executes Boruvka steps until the number of supervertices is 1. Since each step reduces the number of supervertices by at least a factor of 2, at most  $\lceil \log_2 n \rceil$  of these steps have to be executed ( $n$  denotes the number of vertices).

**MSTBORUVKAANDMERGE:** This algorithm combines Boruvka steps and merging. At the beginning it executes some number  $k$  of Boruvka steps in order to reduce the number of vertices, and then it calculates the minimum spanning tree using MSTMERGE. The number  $k$  of Boruvka steps is a free parameter of the algorithm and has to be set by the configurator.

### 3.2.4 Experimental Evaluation of the MST Implementations

#### Configured Programs: the Schedules

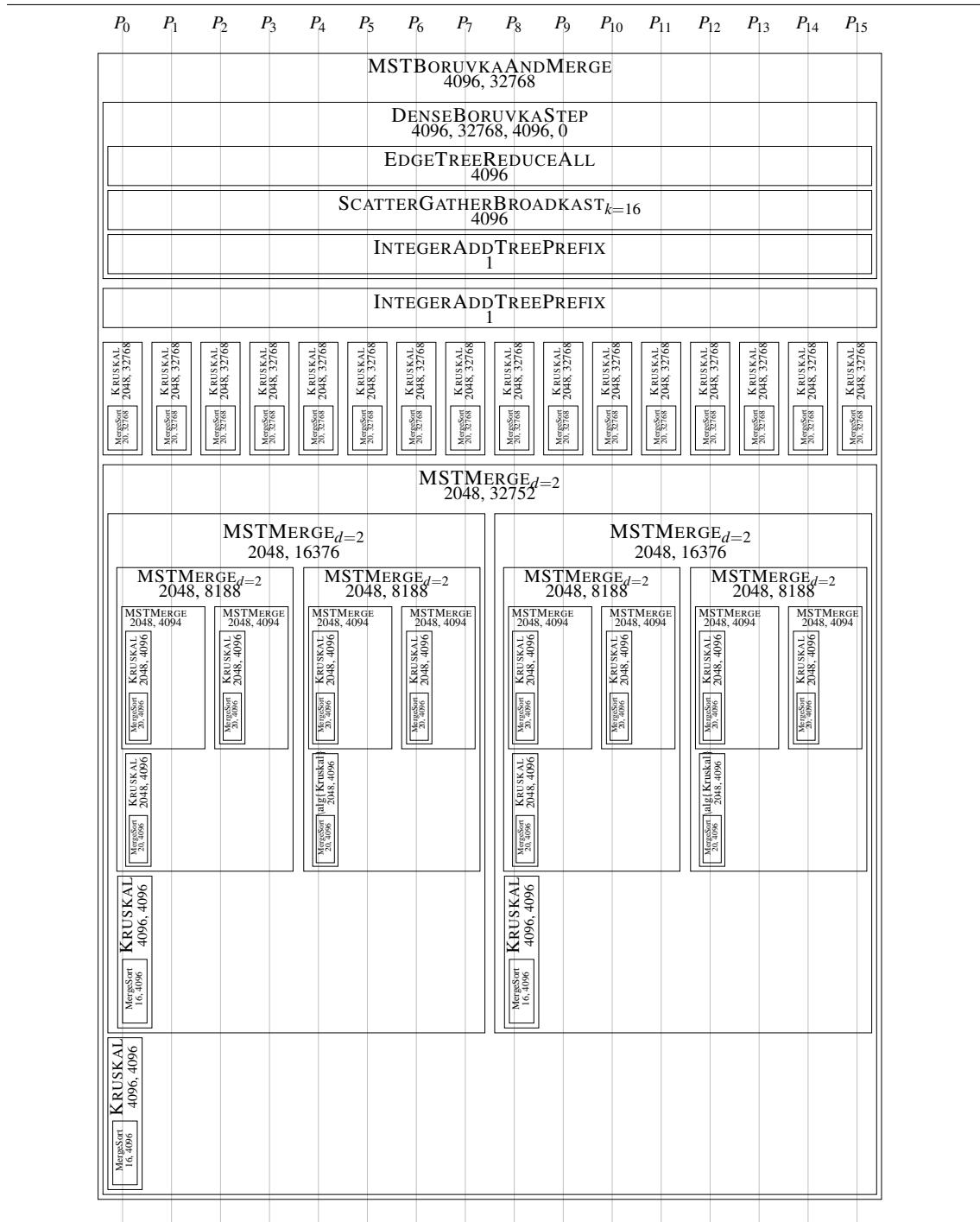

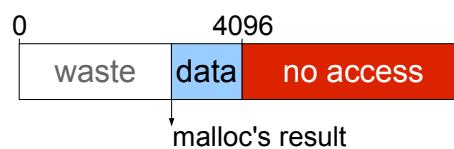

The output of the configurator is a schedule that defines for the problem and each occurred subproblem which algorithm on which processors should be used. Figure 3.6 shows an example of a schedule for the minimal spanning tree problem on a graph with 4096 vertices and 32768 edges. Horizontal there are the processors, whereas the vertical direction marks the time. Each box denotes an algorithm and the needed resources.

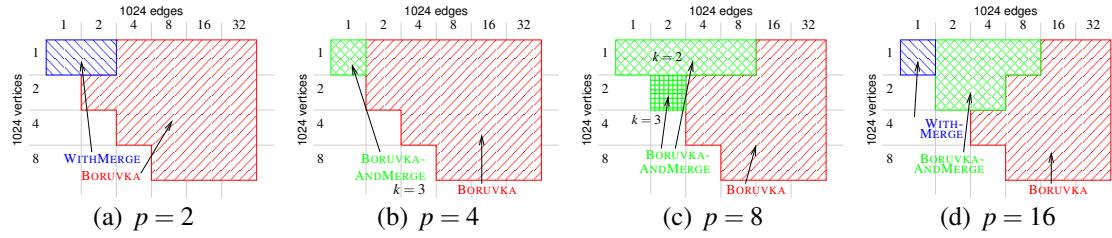

Figure 3.5 shows as the result of the configurator the selected algorithms and the fixing of the free parameters for different sizes of the input graphs and different number of processors for the parallel machine interconnected as a 2-dimensional torus of SCI links.

On a computer with a fast network, the algorithm MSTWITHMERGE is chosen on small graphs only. This algorithm has a small number of supersteps, namely  $\log_d p$ , but calculates a minimum spanning tree sequentially on  $(n-1)d$  edges for  $n$  vertices in every node of the  $d$ -ary communication tree. Also, most of the processors ( $p - p/d^{i-1}$ ) are idle

Figure 3.6: Schedule for the Minimal Spanning Tree Problem of a Graph with 4096 Vertices, 32768 Edges, for a 16 Processor BSP Computer

Figure 3.7: Results of the Configuration on a Pentium III Workstation Cluster with Fast Ethernet

in round  $i$ . If the network is slow (as it is the case with Fast Ethernet), the change from one chosen algorithm to another occurs for larger graph sizes, as can be seen in Figure 3.7 that presents the results of the automatic configuration for the cluster with Fast Ethernet.

An evaluation of the schedules, i.e., measurements of the running time of configured algorithms, and more details of the used computers and their BSP parameters are presented in Section 4.2.1 in the next chapter.

# Chapter 4

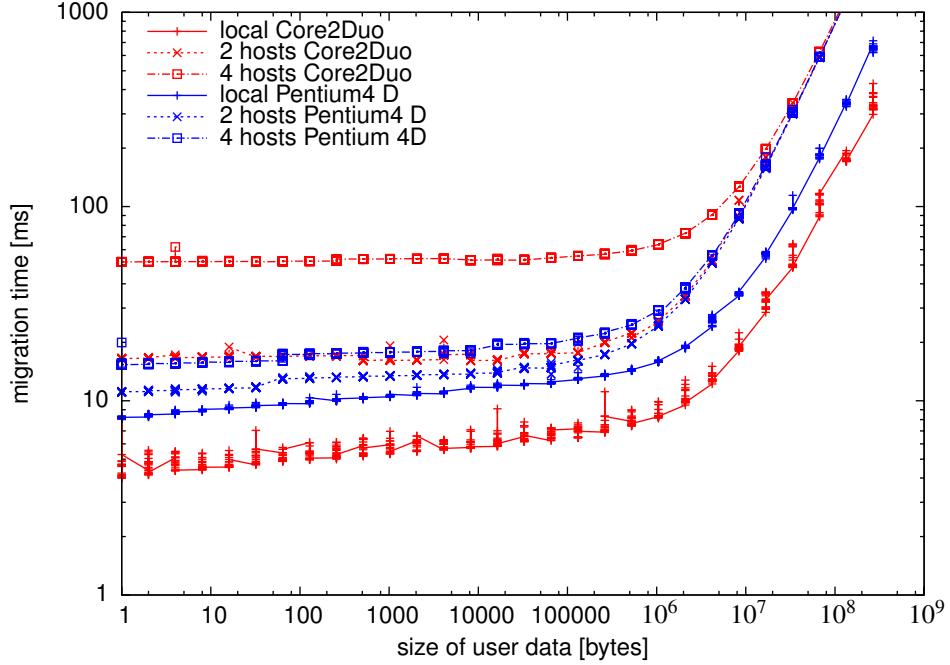

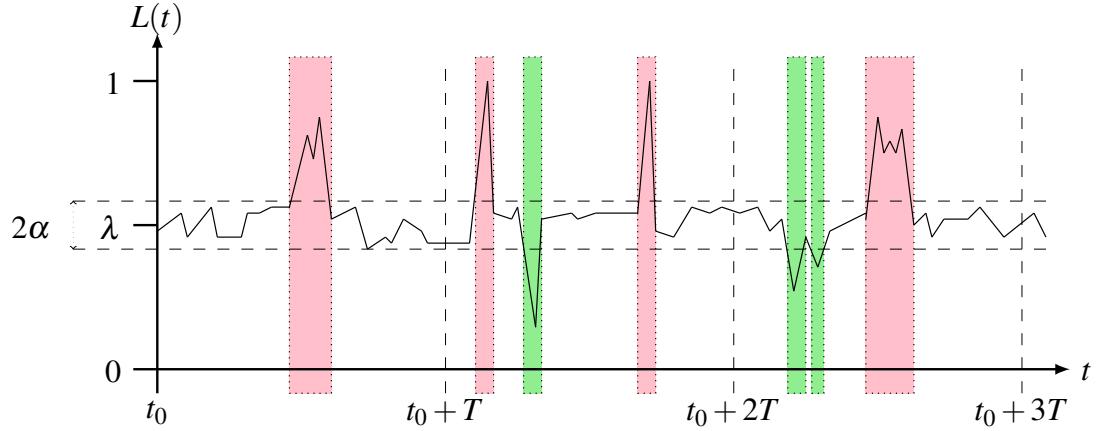

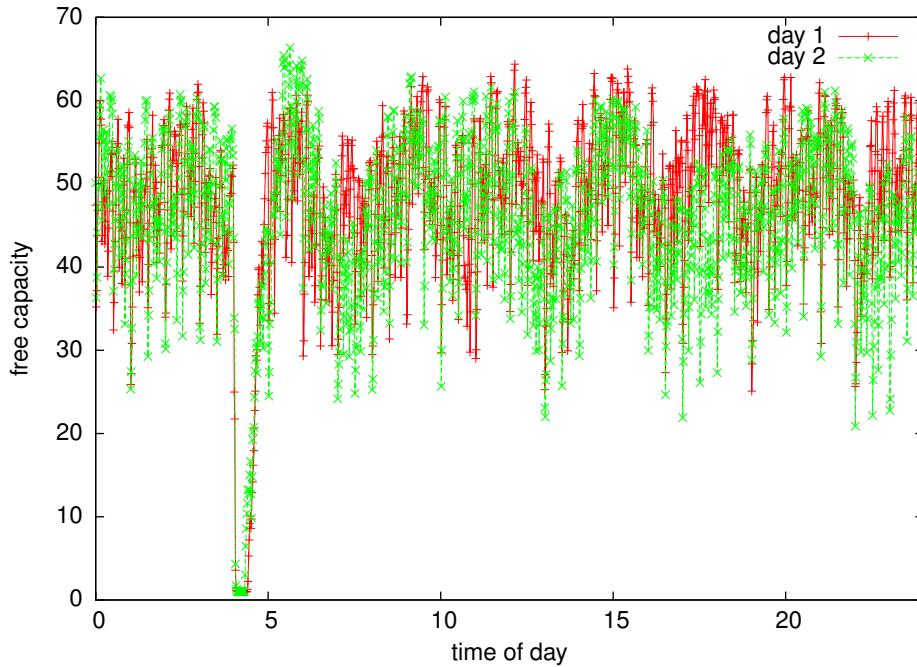

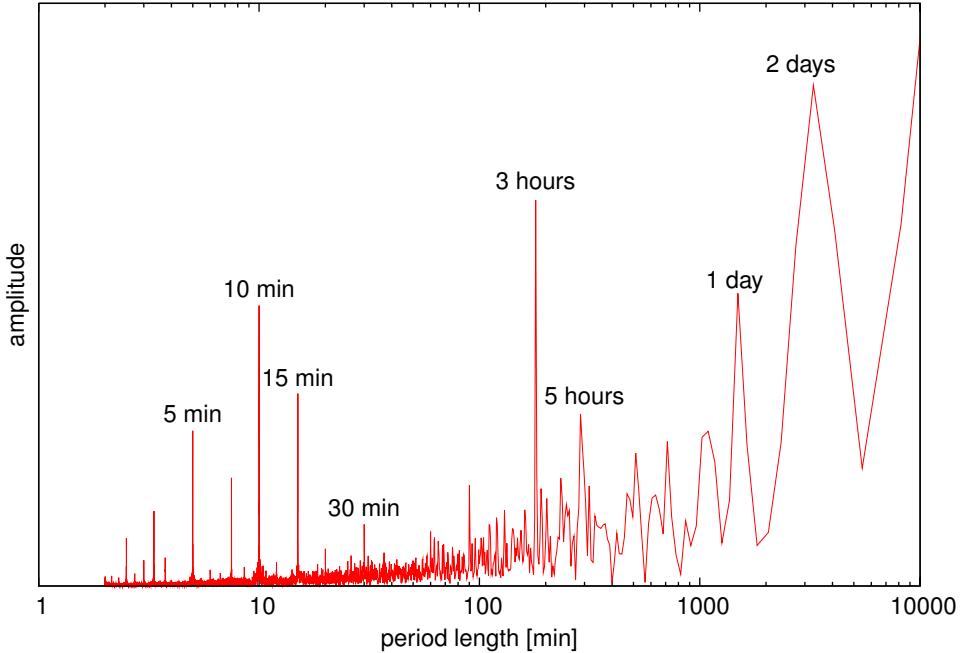

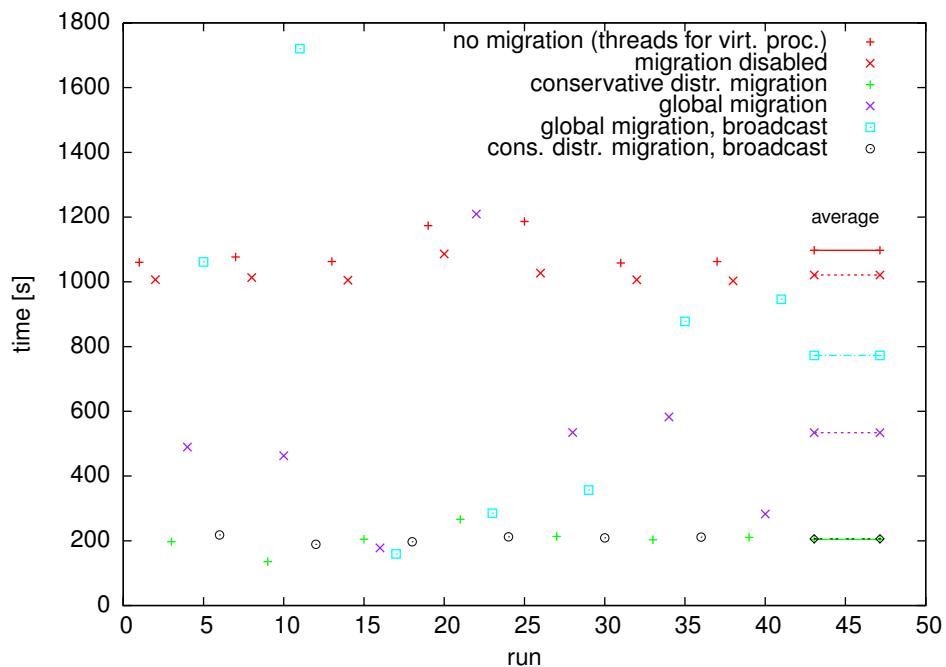

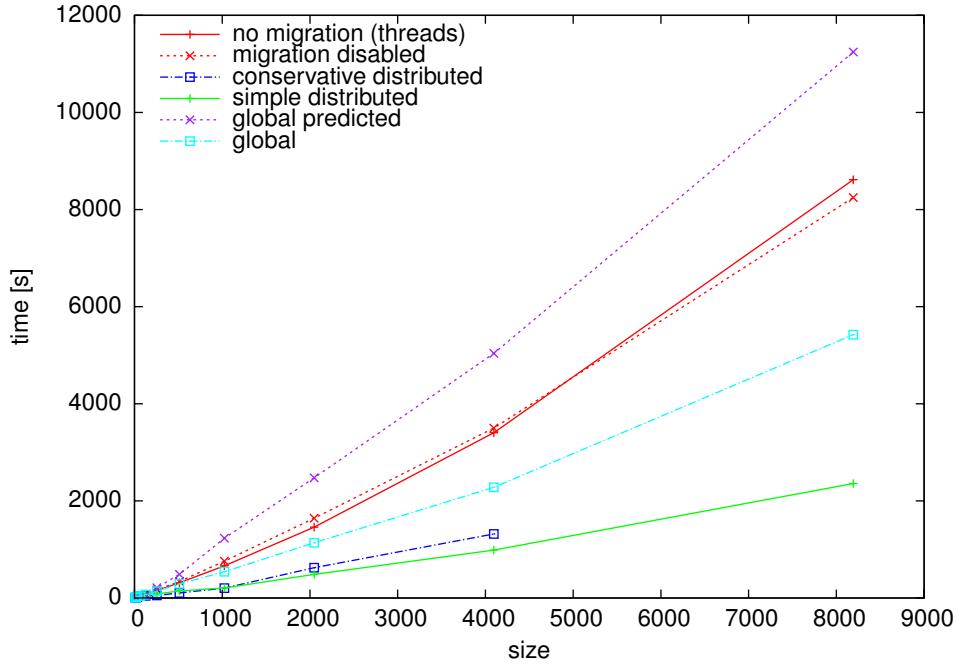

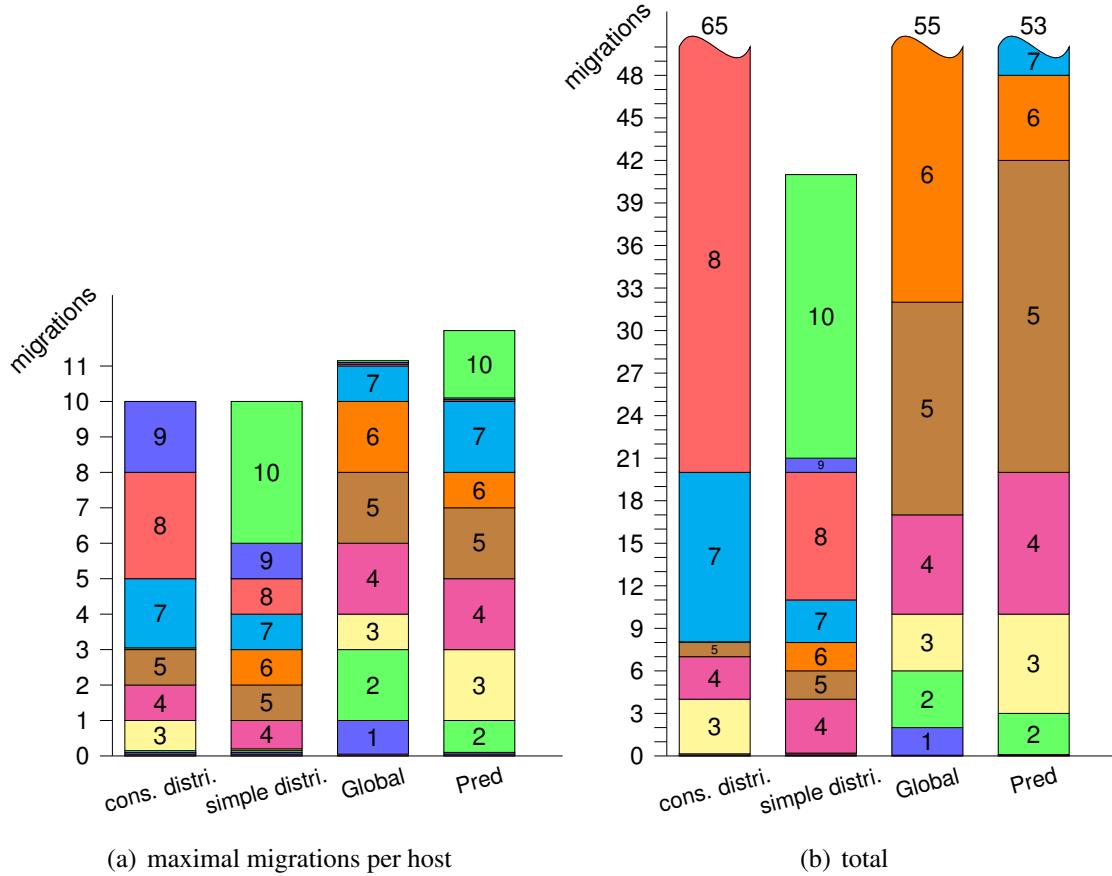

## Implementations