**UNIVERSITÄT PADERBORN**

*Die Universität der Informationsgesellschaft*

---

# **Towards the Design of Fault-Tolerant Distributed Real-Time Systems**

---

## **Dissertation**

A thesis submitted to the Faculty of Computer Science,

Electrical Engineering and Mathematics of the University of Paderborn

in partial fulfillment of the requirements for the degree of Dr. rer. nat.

by

**Kay Klobedanz**

Paderborn, 2014

**Supervisors:**

**Prof. Dr. Franz-Josef Rammig, University of Paderborn**

**Prof. Dr. Achim Rettberg, CvO University Oldenburg**

**Date of public examination: March 13., 2014.**

# Abstract

The number and complexity of embedded computer systems is rapidly increasing. Many of these embedded systems are real-time systems, i.e. the functional correctness depends not only on the provided results but also on their timeliness. Moreover, most embedded real-time systems are distributed systems that are composed of multiple networked processing nodes cooperating on a common function or set of functions. In the design of such systems, the given software functions have to be deployed to the different processing nodes in the network topology. This implies a task mapping and message mapping resulting in corresponding schedules which strongly influence each other. Especially for large systems, the determination of a feasible deployment is a complex and time-consuming task for the designer which cannot be performed without tool support. Therefore, in this thesis we present a design approach for distributed real-time systems that supports the designer to determine an appropriate deployment.

Distributed systems with hard real-time constraints are so-called safety-critical systems. In safety-critical systems, missing a hard deadline may cause catastrophic consequences on the environment or even humans. But beside safety, the system must also reliably provide its intended functionality. Fault tolerance enables a system to continue with safe and reliable operation even in presence of a fault. In this thesis, we focus on the compensation of hardware faults during system runtime resulting in network failures and processor failures. All fault-tolerant techniques require additional redundant elements integrated into the system to detect and compensate faults. Hardware redundancy is perhaps the most common form of redundancy and can be categorized into static and dynamic redundancy. In this thesis, we apply dynamic redundancy by means of reconfiguration to realize fault tolerance. For this purpose, we present concepts for a reconfigurable network topology and for an efficient coordination of the required reconfigurations. Based on these concepts, we extend our approach towards the design of fault-tolerant distributed real-time systems. Moreover, we describe the application of our approach to the de facto standard for automotive system design and approve its feasibility for realistic systems by means of a real-world case study.

# Kurzzusammenfassung

Die Anzahl und Komplexität eingebetteter Systeme nimmt stetig zu. Viele dieser Systeme sind Echtzeitsysteme, deren funktionale Korrektheit nicht nur von gelieferten Ergebnissen sondern auch von deren Pünktlichkeit abhängt. Außerdem sind eingebettete Echtzeitsysteme oftmals verteilte Systeme aus mehreren vernetzten Mikroprozessoren, die für eine oder mehrere Funktionalitäten kooperieren. Beim Entwurf solcher Systeme muss die Softwarefunktionalität auf die Prozessoren im Netzwerk verteilt werden. Dies beinhaltet Task- und Nachrichtenzuordnungen sowie die daraus resultierenden Ablaufplanungen, die sich gegenseitig stark beeinflussen. Insbesondere bei großen Systemen ist die Ermittlung einer passenden Verteilung eine komplexe und zeitaufwändige Aufgabe für den Entwickler, die nicht ohne Werkzeugunterstützung durchführbar ist. Daher präsentieren wir in dieser Arbeit einen Ansatz zum Entwurf eingebetteter Echtzeitsysteme, der den Systementwickler bei der Ermittlung einer geeigneten Lösung unterstützt.

Verteilte Systeme mit strikten Echtzeitanforderungen sind sogenannte sicherheitskritische Systeme, bei denen die Verletzung einer harten Zeitschranke der Umgebung oder sogar Menschen Schaden zufügen kann. Neben der nötigen Sicherheit muss ein solches System aber auch zuverlässig die vorgesehene Funktionalität liefern. Fehlertoleranz ermöglicht eine sichere und zuverlässige Fortsetzung des Systembetriebs im Fehlerfall. In dieser Arbeit betrachten wir die Kompensation von Hardwarefehlern zur Systemlaufzeit, die zu einem Netzwerk- oder Prozessorausfall führen können. Alle Ansätze zur Fehlertoleranz benötigen dabei redundante Systemkomponenten zur Erkennung und Kompensation von Fehlern. Hardwareredundanz ist der wohl am weitesten verbreitete Ansatz und kann in statische und dynamische Redundanz unterteilt werden. Zur Realisierung einer dynamischen Fehlerredundanz im Rahmen dieser Arbeit präsentieren wir Konzepte für eine rekonfigurierbare Netzwerkarchitektur und zur effizienten Koordination der notwendigen Rekonfigurationen. Basierend auf diesen Konzepten erweitern wir unseren Ansatz zum Entwurf fehlertoleranter verteilter Echtzeitsysteme. Zusätzlich beschreiben wir die Verwendung des hier vorgestellten Ansatzes im Quasi-Standard zum Entwurf automobiler Systeme und bestätigen dabei die praktische Anwendbarkeit anhand eines realistischen Fallbeispiels.

# Acknowledgements

This dissertation is the result of research at C-Lab and the University of Paderborn. Here I would like to express my gratitude to many people, who supported me with their comments, suggestions, criticism, and patience during my work. Without them, this thesis would not have been possible.

First of all, I would like to thank my supervisor Prof. Dr. Franz J. Rammig for his invaluable guidance and constructive feedback on my work. I also thank Prof. Dr. Achim Rettberg for vice-supervising and strongly influencing my dissertation. Furthermore, I would like to thank Prof. Dr. Sybille Hellebrand, Prof. Dr. Marco Platzner, and Prof. Dr. Christian Plessl for taking part in my examination board.

I also would like to thank my C-LAB group leaders Dr. Lisa Kleinjohann, Dr. Bernd Kleinjohann, and especially Dr. Wolfgang Müller for their advice and support on my daily work and research topics.

This work would not have been possible without the fruitful discussions I had with my good colleagues. Therefore, my sincere thanks go to all of them. In this regard, I would like to express my particular gratitude to my colleagues Markus Becker and Jan Jatzkowski who supported me throughout the development of this thesis with their comments, suggestions, and corrections.

Last but not least, I would like to thank my family for their strong support during my education and studies. In particular, my thoughts are with my parents and grandparents who unfortunately could not experience the completion of this dissertation. I am very grateful to my family, my many close friends, and especially to my girlfriend Claudia who guided me through difficult and good times in the last several years.

Paderborn, April 2014

---

# Contents

|          |                                                                         |           |

|----------|-------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                                     | <b>1</b>  |

| 1.1      | Motivation . . . . .                                                    | 1         |

| 1.2      | Objectives of the Thesis . . . . .                                      | 4         |

| 1.3      | Structure of the Thesis . . . . .                                       | 6         |

| 1.4      | Summary . . . . .                                                       | 7         |

| <b>2</b> | <b>Fundamentals and Basic Terms</b>                                     | <b>9</b>  |

| 2.1      | Real-Time Systems . . . . .                                             | 9         |

| 2.1.1    | Properties of Real-Time Tasks . . . . .                                 | 11        |

| 2.1.2    | Real-Time Scheduling . . . . .                                          | 16        |

| 2.2      | Distributed Real-Time Systems . . . . .                                 | 24        |

| 2.2.1    | Task Scheduling in Distributed Real-Time Systems . . . . .              | 26        |

| 2.2.2    | Communication in Distributed Real-Time Systems . . . . .                | 27        |

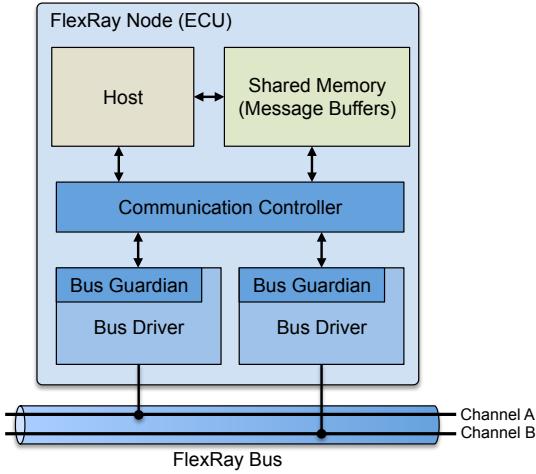

| 2.2.3    | FlexRay Communication Protocol . . . . .                                | 31        |

| 2.2.4    | Timing Constraints for Distributed Real-Time Systems . . . . .          | 39        |

| 2.3      | Fault-Tolerant System Design . . . . .                                  | 42        |

| 2.3.1    | Main Attributes of Dependable Systems . . . . .                         | 42        |

| 2.3.2    | Fault Types . . . . .                                                   | 43        |

| 2.3.3    | Means for Dependable Systems . . . . .                                  | 44        |

| 2.4      | Summary . . . . .                                                       | 47        |

| <b>3</b> | <b>Related Work</b>                                                     | <b>49</b> |

| 3.1      | Design of Distributed Real-Time Systems . . . . .                       | 49        |

| 3.2      | Scheduling in Distributed Real-Time Systems . . . . .                   | 51        |

| 3.3      | Fault Tolerance in Distributed Real-Time Systems . . . . .              | 56        |

| 3.4      | Summary . . . . .                                                       | 60        |

| <b>4</b> | <b>Design Approach for Fault-Tolerant Distributed Real-Time Systems</b> | <b>61</b> |

| 4.1      | Overview . . . . .                                                      | 61        |

| 4.2      | Objectives and Properties . . . . .                                     | 63        |

| 4.2.1    | Reconfigurable Distributed System Topology . . . . .                    | 68        |

| 4.2.2    | Distributed Coordinator Concept . . . . .                               | 70        |

| 4.2.3    | Specification of Timing Properties for the SW Architecture . . . . .    | 75        |

| 4.2.4    | Task Scheduling Strategy . . . . .                                      | 79        |

| 4.2.5    | Configuration of Hardware Architecture . . . . .                        | 83        |

---

|                                                  |                                                                         |            |

|--------------------------------------------------|-------------------------------------------------------------------------|------------|

| 4.2.6                                            | Protocol Data Unit Concept & Frame Packing . . . . .                    | 90         |

| 4.3                                              | Modeling of System Properties . . . . .                                 | 92         |

| 4.3.1                                            | Software Architecture and Hardware Topology . . . . .                   | 92         |

| 4.3.2                                            | Timing Constraints and Communication Properties . . . . .               | 97         |

| 4.4                                              | Deployment . . . . .                                                    | 107        |

| 4.4.1                                            | Task Mapping . . . . .                                                  | 107        |

| 4.4.2                                            | Bus Mapping . . . . .                                                   | 120        |

| 4.5                                              | Design Result and Feedback . . . . .                                    | 125        |

| 4.6                                              | Summary . . . . .                                                       | 129        |

| <b>5</b>                                         | <b>Application to the Design of Automotive Real-Time Systems</b>        | <b>131</b> |

| 5.1                                              | Introduction to AUTOSAR . . . . .                                       | 131        |

| 5.1.1                                            | AUTOSAR Software Architecture . . . . .                                 | 132        |

| 5.1.2                                            | AUTOSAR Software Components . . . . .                                   | 135        |

| 5.1.3                                            | AUTOSAR Methodology . . . . .                                           | 138        |

| 5.1.4                                            | AUTOSAR Communication . . . . .                                         | 142        |

| 5.1.5                                            | AUTOSAR OS . . . . .                                                    | 142        |

| 5.1.6                                            | AUTOSAR Timing Extensions . . . . .                                     | 143        |

| 5.2                                              | Fault-Tolerant Deployment of Real-Time Software in AUTOSAR Networks . . | 146        |

| 5.2.1                                            | Modeling of Application Software . . . . .                              | 147        |

| 5.2.2                                            | Modelling and Setup of Hardware Architecture . . . . .                  | 153        |

| 5.2.3                                            | Runnable and Task Mapping . . . . .                                     | 156        |

| 5.2.4                                            | Bus Mapping . . . . .                                                   | 167        |

| 5.2.5                                            | Reconfiguration with AUTOSAR . . . . .                                  | 171        |

| 5.3                                              | Summary . . . . .                                                       | 173        |

| <b>6</b>                                         | <b>Conclusion and Outlook</b>                                           | <b>175</b> |

| 6.1                                              | Conclusion . . . . .                                                    | 175        |

| 6.2                                              | Outlook . . . . .                                                       | 178        |

| <b>A</b>                                         | <b>Additional Figures from Chapter 4</b>                                | <b>179</b> |

| <b>List of Acronyms</b>                          |                                                                         | <b>183</b> |

| <b>List of Notations</b>                         |                                                                         | <b>185</b> |

| <b>List of Figures</b>                           |                                                                         | <b>189</b> |

| <b>List of Tables</b>                            |                                                                         | <b>191</b> |

| <b>List of Algorithms</b>                        |                                                                         | <b>193</b> |

| <b>List of Listings</b>                          |                                                                         | <b>195</b> |

| <b>List of Own Publications and Bibliography</b> |                                                                         | <b>197</b> |

---

# Chapter 1

## Introduction

This thesis presents a novel approach towards the design of fault-tolerant distributed real-time systems. Initially, this chapter introduces into the field of distributed real-time systems and motivates the necessity for a fault-tolerant design. Based on this motivation it presents the objectives of the thesis with the resulting main requirements and contributions. Finally, it provides the structure of the thesis by giving a brief description of each chapter.

### 1.1 Motivation

Nowadays, the number and complexity of embedded computer systems is rapidly increasing. In contrast to a classical general-purpose PC, an embedded system is a microprocessor-based system that is built into a device or environment and is designed to control a specific function or set of functions [Hea02]. Embedded systems range from small and simple systems like the microprocessor within a digital TV set-top box to very large and complex systems like control systems embedded in process plants. Also the controllers for the ABS system of a car or the operation of its engine as well as the automatic pilot system of an aircraft are embedded systems. In general, by now hardware and software systems are embedded within everyday products and places. Today, already 90% of computing devices are in embedded systems and not in general purpose PCs. The growth rate in embedded systems is more than 10% per year and it is predicted that there will be over 40 billion devices worldwide by 2020. Today, 20% of the value and cost of each car results from embedded electronics and this will increase to an average of 35-50% by 2020 [3TU10].

Many of the embedded systems are real-time systems, i.e. the correctness of the intended functionality depends not only on the provided results but also on the timeliness of the result provisioning by the system. This means the

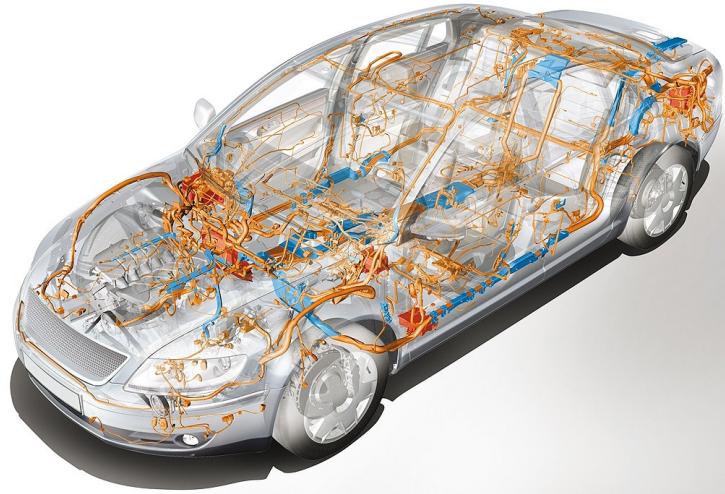

correct result must be available at a specified deadline. Moreover, nowadays most embedded real-time systems are distributed systems [Kop11]. In contrast to a embedded system with a single processing unit, a distributed system is composed of multiple networked processing nodes cooperating on a common function or set of functions [BW09]. A typical example for a large and complex distributed real-time system is the vehicle network of a modern car as depicted in Figure 1.1.

Figure 1.1: Vehicle network of a modern car [Eng12].

Today's modern automotive vehicles contain up to 100 or even more distributed and networked processors which execute thousands of software functions [VBK10]. The functions in a car network are associated to the subsystems powertrain, chassis, body, and multimedia with their corresponding subnetworks [SZ06]. In the design of such a distributed system, the given software functions respectively their corresponding tasks have to be deployed to the different processing nodes in the network topology. Consequently, the deployed tasks on the different distributed processing nodes have to exchange data messages over the network infrastructure, e.g. a communication bus. As described above in a distributed real-time system the timeliness of the task executions and the data transmissions have to be ensured to guarantee a correct system behavior.

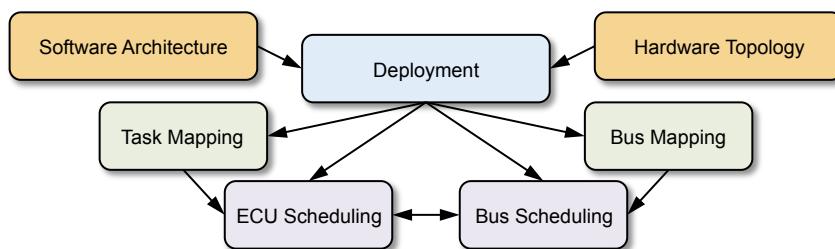

Figure 1.2: Design flow steps for distributed systems [SR08].

Figure 1.2 illustrates the resulting design flow steps for distributed systems. It shows, that the deployment implies a task mapping and message mapping resulting in corresponding schedules which strongly influence each other. This problem of mapping and scheduling tasks and messages in a distributed system is NP-hard [Bur91]. Especially for large systems, the determination of a feasible deployment is a complex and time-consuming task for the designer which cannot be performed without tool support. Therefore, in this thesis we present a design approach for distributed real-time systems that supports the designer to determine an appropriate deployment.

Distributed systems with hard real-time constraints are also called safety-critical systems. In a safety-critical system, missing a specified deadline may cause catastrophic consequences on the environment or even humans. Two of the major domains where safety and reliability are of high importance are the avionic and the automotive domain. In a car typical safety-critical functions are member of the powertrain, chassis, or partly the body subsystem, e.g. engine control, ABS, and airbag control [ZS07]. Obviously, in safety-critical systems the main requirement is to avoid conditions that can cause the catastrophic consequences mentioned before. However, the system must also reliably provide its intended functionality to be useful, as Burns and Wellings illustrate by the following example [BW09]:

*“In many ways, the only safe airplane is one that never takes off, however, it is not very reliable.”*

Hence, beside hard real-time constraints, a safety-critical system has to consider further requirements and safety concepts to also ensure its reliability. A common concept to improve reliability and safety is fault tolerance [LA90]. Fault tolerance enables a system to continue with a safe and reliable operation even in presence of a fault. This is important since due to the rising size and complexity of embedded systems defects caused by this electronic systems are increasing rapidly [EJ09]. In this thesis we focus on hardware faults during system runtime. In a distributed system these faults may result in two types of component failures: network failures and processor respectively node failures [CJ97]. All fault-tolerant techniques require additional redundant elements integrated into the system to detect and recover from faults. Hardware redundancy is perhaps the most common form of redundancy applied in systems [Pra96]. It can be distinguished between static and dynamic redundancy. Static redundancy typically requires multiple redundant instances of the hardware components, e.g. processors, whereas dynamic redundancy applies reconfiguration to realize fault tolerance.

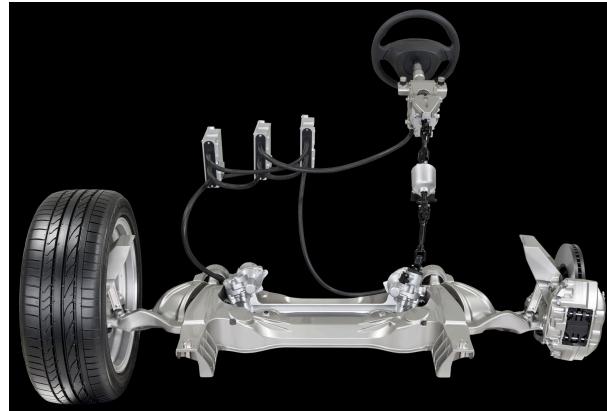

Figure 1.3 illustrates a CAD model of the Steer-By-Wire system which Nissan installed in their current luxury car model Infiniti Q50. It shows three redundant processing nodes and a mechanical steering column as an additional

Figure 1.3: CAD model of upcoming Steer-By-Wire system from Nissan (Image: Nissan).

mechanical backup to realize fault tolerance by means of static redundancy [Spe12]. The drawback of this kind of redundancy is that especially, in huge distributed systems with many components the hardware overhead may result in an inappropriate rise of cost and weight. Thus, the aim of fault tolerance is to minimize redundancy while maximizing the reliability [BW09]. Therefore, in this thesis we apply dynamic redundancy by means of reconfiguration to realize fault tolerance. For dynamic redundancy, in case of a detected error the corresponding faulty component must be detected. The faulty component has to be removed and its functionality has to be resumed by another to regain the operational status of the system, i.e. a reconfiguration has to be performed. To offer the required redundancy, we perform task replication, i.e. allocation of redundant task instances on the nodes. Task replication is a fundamental method for improving the reliability of a distributed system [Kim+11]. To enable a flexible task replication and reconfiguration for distributed real-time systems which interact with the environment, this thesis presents concepts for a reconfigurable network topology and for an efficient coordination of the required reconfigurations. Considering these concepts, we extend our approach for the design of fault-tolerant distributed real-time systems. In this way it determines the initial deployment for normal system mode and based on that for all required reconfigurations to compensate possible component faults.

The next section briefly summarizes the objectives and contributions of the thesis to address the challenges described above.

## 1.2 Objectives of the Thesis

The main objective of this thesis is to develop an approach for the design of fault-tolerant distributed real-time systems that supports the system designer by determining feasible solutions for the required deployments. For

for this purpose we extend and refine the design flow steps for distributed systems depicted in Figure 1.2 and present further concepts to enable dynamic redundancy by means of reconfiguration. In the following we shortly present the resulting objectives and requirements for this thesis.

**Compensation of arbitrary operational hardware faults** During system runtime, different possible operational hardware faults can be distinguished by means of their occurrence and duration and result in different behaviors of the faulty component. In a distributed system these faults may result in either network or node failures. We describe that the compensation of one arbitrary component fault is sufficient in most cases to ensure fault tolerance. Hence, in this thesis we provide means to compensate one arbitrary component fault.

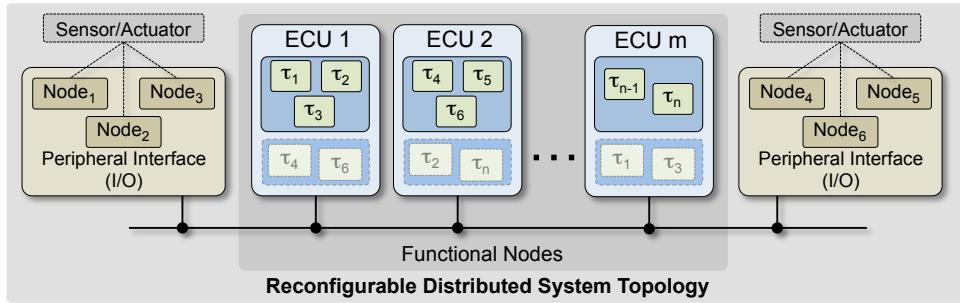

**Reconfigurable distributed system topology** Current distributed systems exchange data with the environment via hardwired sensors and actuators. This results in placement constraints for tasks which have to exchange data with these sensors or actuators. A failure of such a hardwired processing node cannot be compensated with dynamic redundancy by means of reconfiguration because the required connections get lost. Therefore, we propose a reconfigurable distributed system topology which avoids these placements constraints and offers the necessary flexibility for our fault-tolerant design approach.

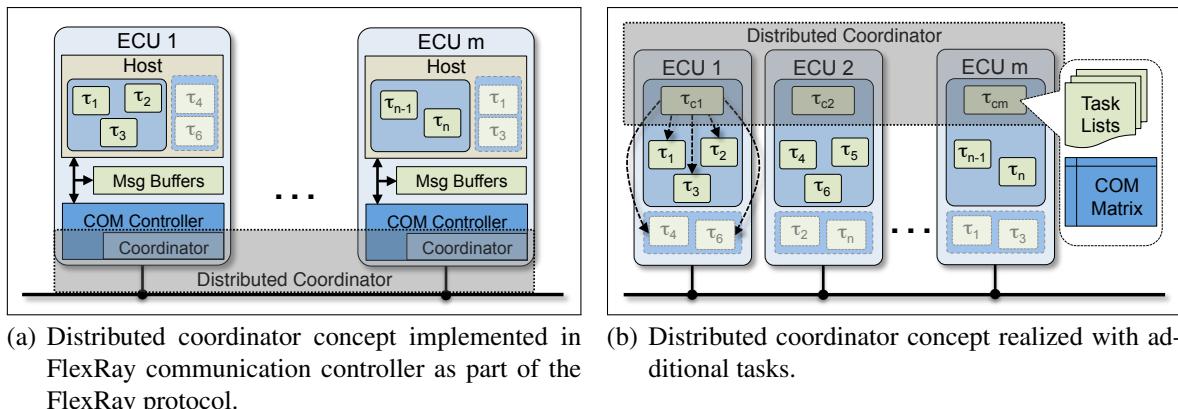

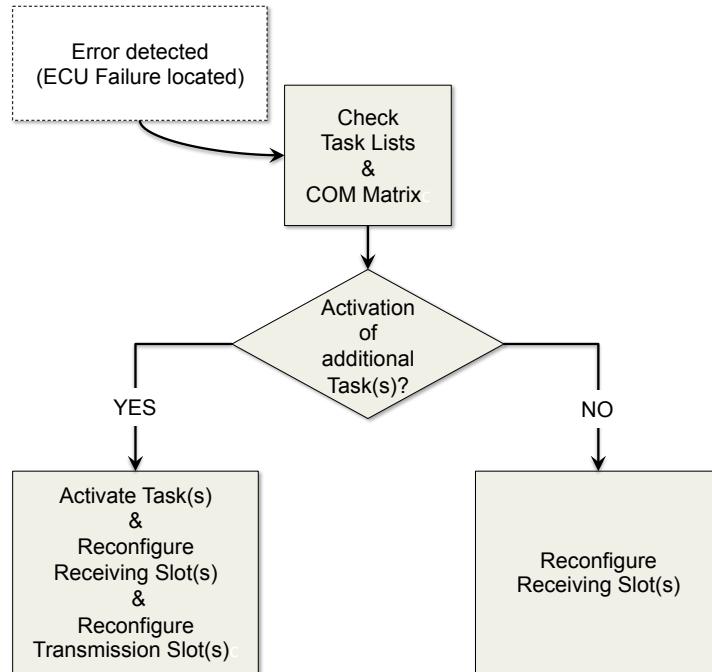

**Coordination of reconfiguration** To realize fault tolerance through dynamic redundancy, a component which coordinates and performs the required reconfiguration steps has to be integrated in the system. Thus, we discuss several methods how to realize this coordination and propose a novel distributed coordinator concept which allows the self-reconfiguration of the system by detecting faulty components and activating redundant task instances on other nodes to resume the functionality and regain the operational status of the system.

**Extended schedulability tests** Task scheduling in distributed systems has to cover the local level of each processor and the global scheduling, i.e. the mapping of tasks to nodes. For local scheduling we consider RM/DM scheduling which is still most frequently applied in many important real-time domains and EDF scheduling which has some significant advantages over RM/DM scheduling. To determine feasible candidates for the task mapping, the corresponding schedulability tests for the local scheduling have to be performed. To consider possibly resulting communication delays in a distributed system, we propose extended versions of the existing strategies.

**Modeling of system properties** To perform an appropriate system design, our approach requires information about the properties of the given software architecture and hardware topology as well as the resulting real-time constraints and communication properties. Thus, we define and present a graph-based modeling of the system properties as input for our approach. These models are annotated with the corresponding timing properties and constraints.

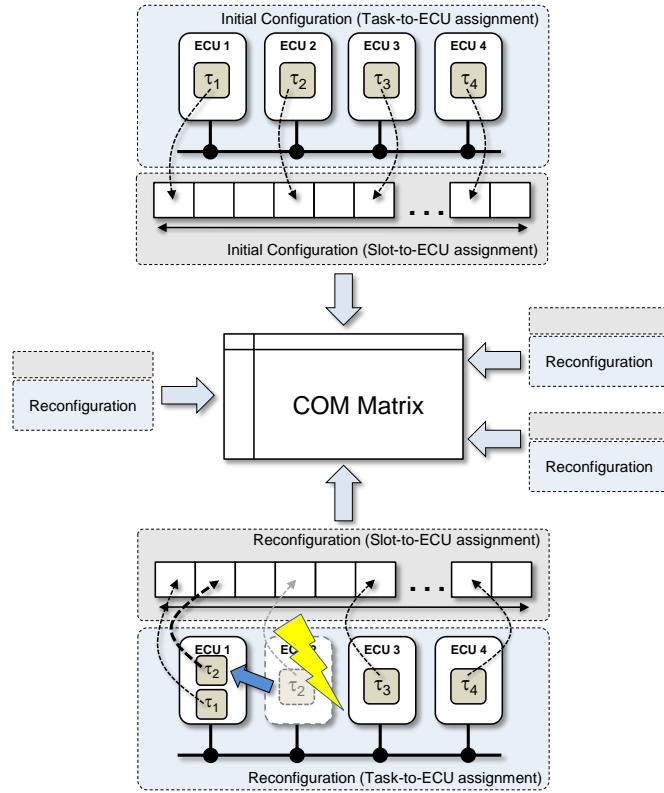

**Deployment and design result** Fault-tolerant system deployment is an essential part of our approach and shall provide a feasible design result. Hence, we present different algorithms for the determination of feasible task and bus mappings for the initial configuration and based on that for all necessary reconfigurations to design a fault-tolerant system. Finally, our approach returns the resulting design as feedback for the designer. Depending on the given input, our deployment approach is able to return a complete feasible solution for all possible configurations or for a subset. Based on this feedback, the designer can design the system according to the determined solution or perform a further iteration of the design approach.

**Application to the design of automotive systems** Modern automotive vehicles are a major area of application for large and complex distributed real-time systems. AUTOSAR is the established de facto standard for the development of automotive systems. Hence, we describe the application of our approach to the fault-tolerant design of automotive systems and the deployment of real-time software based on AUTOSAR. Additionally, we propose a further concept to coordinate and realize the required reconfigurations that is based on existing AUTOSAR components.

## 1.3 Structure of the Thesis

This thesis is structured as follows. Chapter 2 provides the essential fundamentals and basic terms for the work presented in this thesis. This includes general properties of real-time systems, an introduction to task scheduling and communication in distributed real-time systems as well as basic concepts for modeling and specification of timing constraints for such systems. The Chapter is completed by an introduction to fault-tolerant system design.

Chapter 3 gives an overview of related work relevant for the work in this thesis. This includes work and publications dealing with the design and configuration of distributed real-time systems, an overview of publications and techniques regarding the scheduling of real-time tasks and messages in distributed systems, and the presentation of existing concepts and approaches for reconfigurable and fault-tolerant distributed real-time systems.

In Chapter 4 our design approach for fault-tolerant distributed real-time systems is described in detail. Its main objective is the determination of feasible and flexible fault-tolerant system designs with compensation of different usual fault types and a simultaneous reduction of required redundancy based on a reconfigurable distributed system topology with an additional concept for fault tolerance. Applying the presented graph-based input model of system properties, this chapter describes the system deployment and its design result as essential part of the approach.

In Chapter 5 we present how to utilize our approach for the design of fault-tolerant automotive real-time systems. Therefore, this chapter describes the application of our approach to the modeling and deployment of automotive real-time software based on AUTOSAR, a well-defined and standardized methodology for the development of automotive systems.

Chapter 6 concludes the thesis by summarizing the main contributions and providing an outlook for future work. Finally, the publications which have been published in the context of this thesis as basis for the presented work are listed on page 197.

## 1.4 Summary

This chapter provided an introduction to the work presented in this thesis. It motivated the necessity to develop our approach for the design of fault-tolerant distributed real-time systems. Based on this motivation, the objectives of the thesis were presented. The last section of this chapter described the structure of this thesis and provided a brief description of each following chapter.

---

# Chapter 2

## Fundamentals and Basic Terms

This chapter provides a detailed description of fundamental and basic terms essential for the work presented in this thesis. It starts with properties of real-time systems, tasks, and their scheduling. This is proceeded by an introduction to task scheduling and communication in distributed real-time systems. Moreover, basic concepts for modeling and specification of timing constraints for distributed real-time systems are presented. The fundamentals are completed by an introduction to fault-tolerant system design.

### 2.1 Real-Time Systems

Today's number and complexity of *embedded* computer systems is rapidly increasing. In contrast to a classical general-purpose PC, an embedded system is a microprocessor-based system designed to control a specific function or range of functions [Hea02]. An embedded system is part of a self-contained product, e.g. an aircraft or an automobile, and generally bound to *real-time* constraints. Embedded real-time systems form the most important market segment for real-time technology and the computer industry in general [Kop11]. The term "real-time" means that the computer system is not longer controlling its own time domain. For a real-time system the progress of time of the environment (*external time*) defines how the *internal time* of the system has to progress. This external time may be the real physical time or also artificially generated by a surrounding environment. For the embedded system this makes no difference.

Summarized, Kopetz defines real-time systems as [Kop11]:

*"A real-time computer system is a computer system where the correctness of the system behavior depends not only on the logical results of the computations, but also on the physical instant (time) when these results are produced. By system behavior we mean the sequence of outputs in time of a system."*

This definition implies that in strict real-time systems a late result is also wrong. Here the meaning of "lateness" has to be defined dependent on the specific application. A real-time system must respond to stimuli from its environment in a certain way within time intervals dictated by its environment [Tan95]. The instant when a result must be produced is called *deadline*. Any given deadline has to be met under all circumstances – even the worst case. Thus, real-time also involves *predictability* and *determinism*. It is a wide spread myth that real-time systems have to be as fast as possible. In fact they just have to be fast enough to meet all given deadlines, but most of all they have to be predictable. Ensuring this determinism may even slow down a real-time system [Ram+09]. Therefore, real-time systems can be characterized by the strictness of their real-time restrictions [But11]:

- A *hard* real-time system – also called *safety-critical* real-time system – must meet at least one hard deadline. Missing this deadline may cause catastrophic consequences on the environment or people. Typical application areas are automotive systems, like air-bag control or steer-by-wire.

- In a *firm* real-time system the missing of a deadline makes the result useless, but does not cause severe consequences. Typical application areas are forecast systems for weather or stock exchange.

- For a *soft* real-time system the meeting of deadlines is desirable – e.g. for performance or quality reasons – but missing does not cause useless results. Here, typical areas are video and audio streaming or comfort and body electronics in automotive vehicles.

Because of the described strictness of real-time restrictions, the design of a hard real-time system is fundamentally different from the design of a soft real-time system. While a hard real-time system must sustain a guaranteed temporal behavior under all – even worst case – circumstances, it is permissible for a soft real-time computer system to miss a deadline occasionally. The focus of this thesis is on the more complex and demanding design of safety-critical systems with hard real-time constraints.

The process of executing a functionality or an algorithm by a processing unit is called *computation* or *task*. These computations are performed by

the *components* of the real-time system. A component is a self-contained hardware/software unit that interacts with its environment exclusively by the exchange of messages. To be aware of the progression of time, a real-time system contains a real-time clock. After power-up, a component enters a *ready-for-start* state to wait for a *triggering signal* that indicates the start of task execution. When started it reads input messages, updates its internal state and produces output messages, until the computation gets terminated. Afterwards, the component enters the ready-for-start state again to wait for the next triggering signal.

A triggering signal can be associated either with the occurrence of a significant *event* by an *event-triggered* control, or with a specified point in time by a *time-triggered* control [Kop11]. The significant events that form the basis of event-triggered control can be, for example, the arrival of a particular message, the completion of an activity inside a component, or the occurrence of an external interrupt. Time-triggered control signals are derived from the progression of the global time in the real-time system. Time-triggered control signals are typically cyclic. A *cycle* can be characterized by its *period*, i.e. the real-time interval between two successive *cycle starts*, and by its *phase*, which is the interval between the start of the period and the cycle start. We assume that a cycle is associated with each time-triggered activity. To guarantee the required predictability and determinism, safety-critical real-time systems generally utilize time-triggered control, e.g. for sensory data acquisition or control loops. Therefore, in this thesis we focus on cyclic and periodic tasks.

### 2.1.1 Properties of Real-Time Tasks

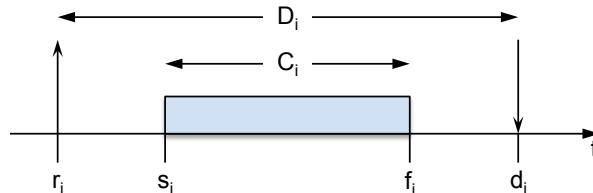

In contrast to other computational tasks, real-time tasks additionally consider the notion of *time*. This implies that the correctness of the system depends not only on logical results but also on the time when these results are produced. Concerning the timing restrictions defined above, a real-time task  $J_i$  can be characterized by the following properties depicted in Figure 2.1:

- **Release time  $r_i$ :** The *release time*  $r_i$  is the time at which  $J_i$  becomes ready for execution. It is also called *request time* or *arrival time*, denoted by  $a_i$ .

- **Computation time  $C_i$ :** The *computation time*  $C_i$  is the time necessary for the execution of  $J_i$  without interruption by other tasks. For this, we consider the *worst case execution time* (WCET), which has to be determined in advance for the task on the executing processor. The WCET is the upper bound on the execution times of a task on a specific hardware platform. Computing such a bound is undecidable in the general case [Mar03]. However, different techniques exist for estimating the

WCET. Those estimates are typically pessimistic, meaning that the estimated WCET is known to be higher than the real one. Consequently, much work on WCET analysis is on reducing the pessimism and computing tight bounds.<sup>1</sup> However, estimation of WCETs is not the focus of our work and we consider them as predetermined values.

- **Deadline  $d_i$  (absolute) and  $D_i$  (relative):** The deadline is the time at which a task has to be finished to avoid damage to the system or users. We distinguish between *absolute deadline*, denoted by  $d_i$  and *relative deadline*, denoted by  $D_i$ . Absolute deadline means related to the global time of the whole system while relative deadline means relative to the release time  $r_i$  of  $J_i$ .

- **Start time  $s_i$ :** The *start time*  $s_i$  is the time at which a task starts its execution. A task execution cannot be started before its release time. Furthermore, the execution can be delayed by other tasks. Therefore,  $r_i \leq s_i$  always holds.

- **Finishing time  $f_i$ :** The *finishing time*  $f_i$  is the time at which a task finishes its execution and can be calculated as  $f_i = s_i + C_i$ . The least possible value results for  $s_i = r_i$ . But due to delays and interruptions caused by other tasks the finishing time may be later. Nevertheless,  $f_i \leq d_i$  must always hold.

Figure 2.1: Parameters of a real-time task  $J_i$  [Ram+09].

### Task Dependencies and Precedence Constraints

The tasks of a given task set may be independent or dependent. In many real-time systems the tasks cannot be executed in arbitrary order but have to respect *precedence* relations resulting from task dependencies defined at system design.<sup>2</sup> Obviously task dependencies corresponding to synchronization or communication among tasks introduce additional *precedence constraints*. Therefore, we consider dependent task sets with precedence constraints in this thesis.

<sup>1</sup>For instance, AbsInt offers tools for WCET analysis [Abs12].

<sup>2</sup>”From a practical point of view, results on how to schedule tasks with precedence and mutual exclusion constraints are much more important than the analysis of the independent task model.” [Kop11].

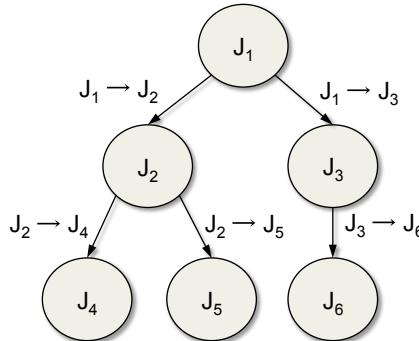

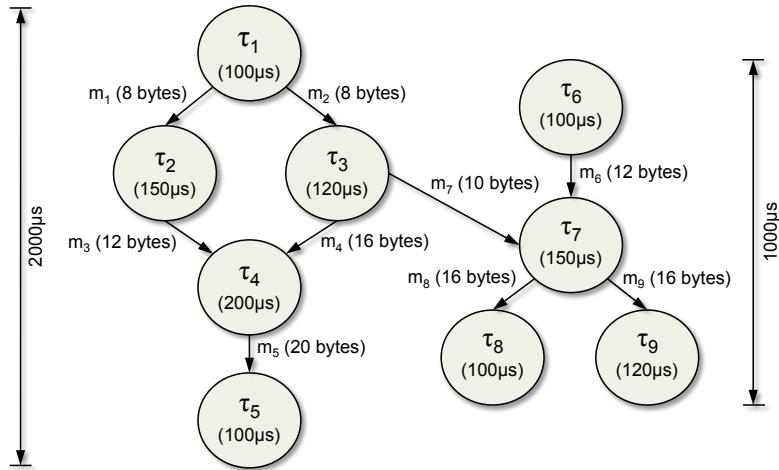

A task  $J_i$  depends on task  $J_k$ , if  $J_i$  cannot be started before  $J_k$  has been finished. Thus, the notion  $J_k \rightarrow J_i$  specifies that  $J_k$  is a *direct predecessor* of  $J_i$ . Dependencies between tasks can be defined by a *task dependency graph* (TDG), which is a directed acyclic graph (DAG). In a TDG:  $G_{\text{TDG}} = (V, E)$  the tasks are represented by a set of vertices  $V$  and precedence relations are represented by directed edges  $E$ . A TDG induces a partial order on the task set. Figure 2.2 depicts an exemplary TDG with its precedence constraints, e.g.  $J_1 \rightarrow J_2$  and  $J_3 \rightarrow J_6$ .

Figure 2.2: Example task dependency graph with precedence constraints.

### Periodic Tasks

Two main classes of tasks can be identified: *periodic* and *aperiodic* tasks. Both types are generic, i.e. a sequence of instances is generated over time. Usually such a task-instance is called *job*. Because all jobs share the same code they have the same WCET  $C_i$ . In case of a periodic task these instances arrive with a fixed period, denoted by  $T_i$ . The first arrival time, i.e. the release time of the first instance is usually called the phase  $\phi_i$  of this generic task. Periodic tasks directly reflect the "sense-execute-act" loop in control applications [Ram+09] and offer the required predictability and determinism for safety-critical real-time systems. These periodic tasks typically arise from sensory data acquisition or control loops which have to be executed time-triggered and cyclically at specific rates derived from the functional requirements of an application. Therefore, a real-time system may contain tasks with different rates resulting in a so-called *multirate system*.

Summarized, a set  $\Gamma$  of periodic real-time tasks can be characterized by the following set of parameters, which are commonly used in literature:

$\tau_i$ : A Generic task, where different instances of this task may exist over time.

$\tau_{i,j}$ : The  $j$ th-instance of  $\tau_i$ .

- $T_i$ : The period of  $\tau_i$  is the interval between two consecutive arrivals of  $\tau_i$ .

- $C_i$ : The computation time respectively WCET of  $\tau_i$  is identical for each instance.

- $r_{i,j}$ : The release time of  $\tau_{i,j}$  is an absolute value and specific for each instance  $j$ .

- $\phi_i$ : The phase of  $\tau_i$  is the release time of the first instance ( $\phi_i = r_{i,1}$ ).

- $D_i$ : The relative deadline of  $\tau_i$ . All instances of  $\tau_i$  have the same relative deadline. For independent tasks this is often equal to the period  $T_i$ . For dependent tasks the relative deadline may be less than  $T_i$ . Summarized,  $D_i \leq T_i$  always holds.

- $d_{i,j}$ : The absolute deadline is a specific property of each task instance  $\tau_{i,j}$ . It can be derived from the relative deadline by  $d_{i,j} = \phi_i + (j-1) \cdot T_i + D_i$ . The time interval  $\Psi_{i,j} = [r_{i,j}, d_{i,j}]$  defines the *available execution time interval* in which  $\tau_{i,j}$  must be executed.

- $s_{i,j}$ : The start time is an absolute value, which is specific for each task instance  $\tau_{i,j}$ . It holds  $s_{i,j} \geq r_{i,j}$  for all instances.

- $f_{i,j}$ : The finishing time is an absolute value, which is specific for each task instance  $\tau_{i,j}$ . It holds  $f_{i,j} \leq d_{i,j}$  for all instances.

Based on these parameters a set of  $n$  independent periodic tasks can be defined as [But11]:

$$\Gamma = \{\tau_i = (\phi_i, T_i, C_i) \mid i = 1, \dots, n\}. \quad (2.1)$$

The release time  $r_{i,j}$  and absolute deadline  $d_{i,j}$  of the  $j$ -th instance then can be calculated as:

$$\begin{aligned} r_{i,j} &= \phi_i + (j-1) \cdot T_i, \\ d_{i,j} &= r_{i,j} + T_i = \phi_i + j \cdot T_i. \end{aligned}$$

Due to the resulting precedence constraints for dependent tasks the release times and deadlines of task instances do not just depend on the periods, but also on the minimum finishing times and maximum start times of the direct

predecessors respectively successors. Consequently, these values have to be calculated as described above. Additionally, we can define a *response time*  $R_{i,j}$  for each task instance. This is the time – measured from the release time – at which an instance finishes execution, i.e. it responses to the task request:

$$R_{i,j} = f_{i,j} - r_{i,j}.$$

Obviously, the response time increases if the execution of a task instance is delayed or interrupted by other tasks. Therefore, Liu and Layland introduced the *critical instant* of a task. This is the time at which a release of this task will produce the largest response time [LL73]:

*"A critical instant for any task occurs whenever the task is requested simultaneously with requests for all higher priority tasks."*

In any case the release time for each instance must not be larger than the relative deadline, i.e.  $R_{i,j} \leq D_i \forall j$ . If all its instances fulfill this constraint and finish within their deadlines a periodic task  $\tau_i$  is called *feasible*. A task set  $\Gamma$  is called *schedulable* – or *feasible* – if all tasks in  $\Gamma$  are feasible.

### Precedence Constraints for Periodic Tasks

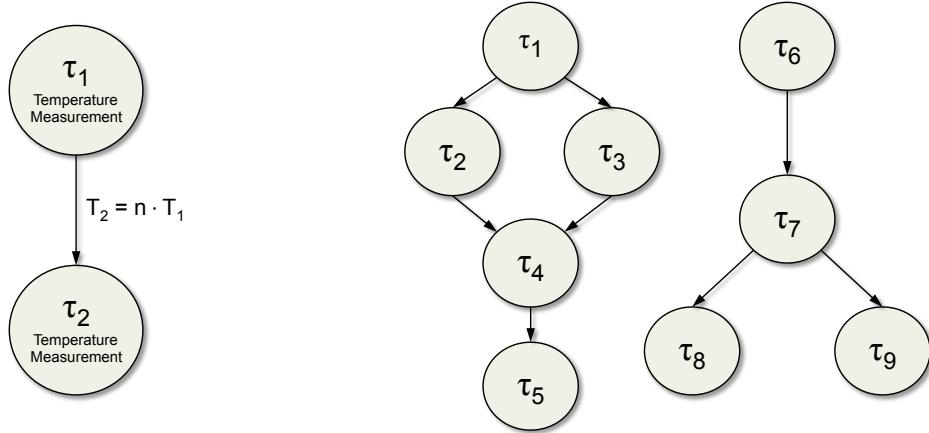

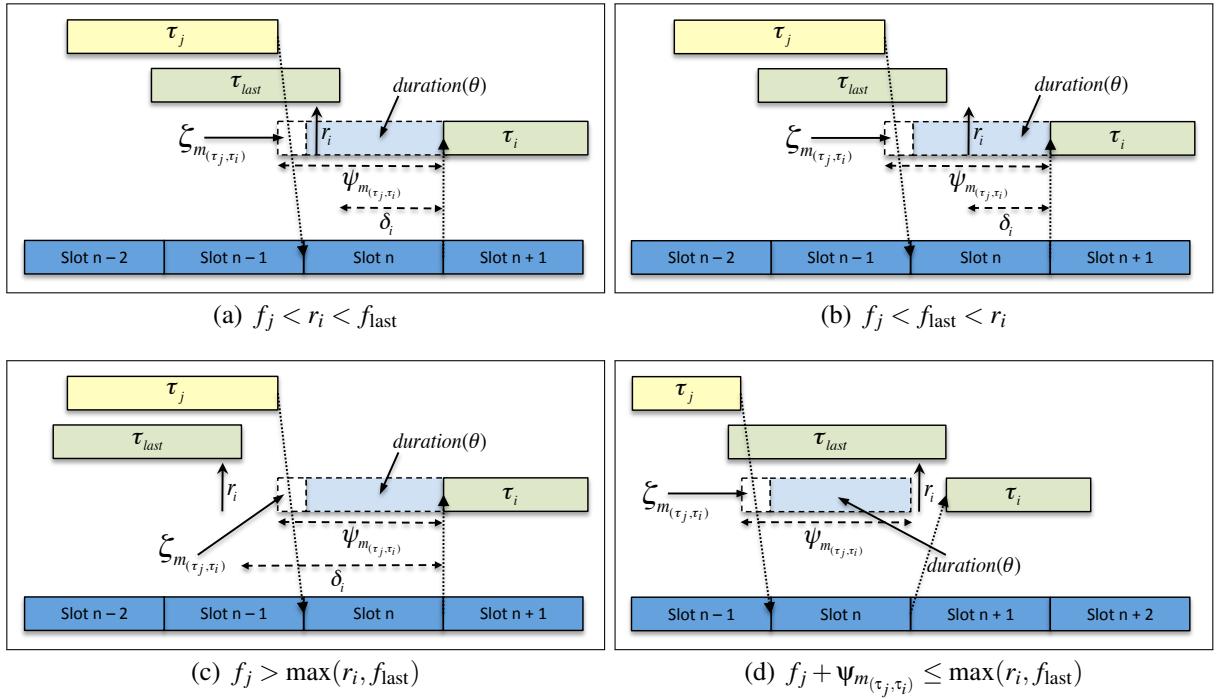

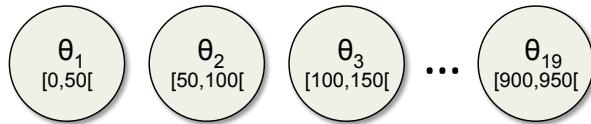

If we consider a multirate system with different task periods, complex precedence relationships may arise, where  $n$  successive instances of a task can precede one instance of another task, or one instance of a task precedes  $m$  instances of another task [Cot+02]. Figure 2.3(a) depicts an example for communicating tasks with different periods. Task  $\tau_2$  calculates the average value of the input data provided by task  $\tau_1$  over  $n$  samples and therefore has a period of  $T_2 = n \cdot T_1$ . To facilitate the description of the precedence constraint problem, in [Cot+02] Cottet et. al propose to consider only *simple precedence constraints*, i.e. if a task  $\tau_i$  has to communicate the result of its processing to another task  $\tau_j$ , these tasks have to be scheduled in such a way that the execution of the  $k$ -th instance of task  $\tau_i$  precedes the execution of the  $k$ -th instance of task  $\tau_j$ . Thus, these tasks have the same period ( $T_i = T_j$ ). This means, all tasks belonging to the same connected subgraph of the TDG must have the same period. For instance, on the TDG graph represented in Figure 2.3(b), tasks  $\tau_1$  to  $\tau_5$  must have the same period and tasks  $\tau_6$  to  $\tau_9$  also must have the same period. If the periods of connected tasks are different, these tasks will run at the lowest rate sooner or later. As a consequence the task with the shortest period will miss its deadline [Cot+02]. However, in real world systems often functions and tasks with different periods are executed and exchanging data resulting in *complex precedence constraints*. Therefore,

our approach also supports precedence between subgraphs with different periods (cf. Section 4.2.3).

(a) Example of a complex precedence relation of two tasks with different periods. (b) Example of a TDG composed of two subgraphs with simple precedence constraints.

Figure 2.3: Examples of complex (a) and simple (b) precedence relations in TDGs for periodic tasks [Cot+02].

In [Bla76] Blazewicz stated that if we have to ensure  $\tau_i \rightarrow \tau_j$ , the release times ( $r_i, r_j$ ) and the priorities ( $\text{Prio}_i, \text{Prio}_j$ ) of the tasks must fulfill the following rules:

- $r_j \geq r_i$ ,

- $\text{Prio}_i \geq \text{Prio}_j$  in accordance with the scheduling algorithm.

In the following section we will present commonly used basic real-time scheduling algorithms where a modification of task parameters shall lead to an execution order that respects the precedence constraints.

### 2.1.2 Real-Time Scheduling

In this thesis we focus on real-time systems where periodic tasks represent the main workload. A real-time system may contain tasks with different timing constraints. For instance, tasks with different periods have to be considered and dependent tasks additionally imply precedence constraints. Summarized, task executions have to be scheduled properly considering all given constraints, to guarantee that each periodic task instance is regularly activated according to its rate and finished within its deadline. Therefore, in this section we describe well-known and widely used basic algorithms for periodic task scheduling: *Rate Monotonic Priority Assignment* (RM) respectively *Deadline Monotonic Priority Assignment* (DM) and *Earliest Deadline*

First (EDF). The descriptions also provide a schedulability analysis for each algorithm to derive a priori guarantee tests for generic task sets.

Obviously, all these real-time scheduling algorithms strictly rely on priorities. Thus, analogous to the priority  $\text{Prio}_i$  of a generic task, the priority of a task instance is denoted by  $\text{Prio}_{i,j}$ . This means, that at any point in time the task instance  $\tau_{i,j}$  with the highest priority among all active instances is executed.

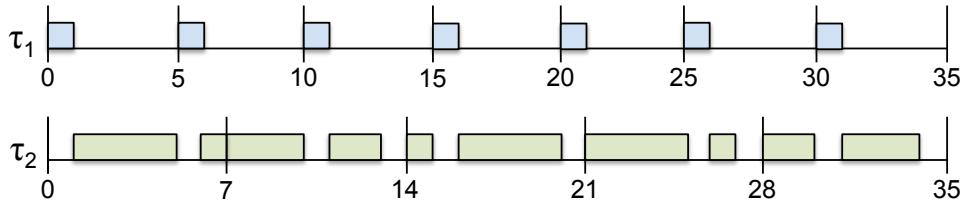

### Rate Monotonic and Deadline Monotonic Priority Assignment

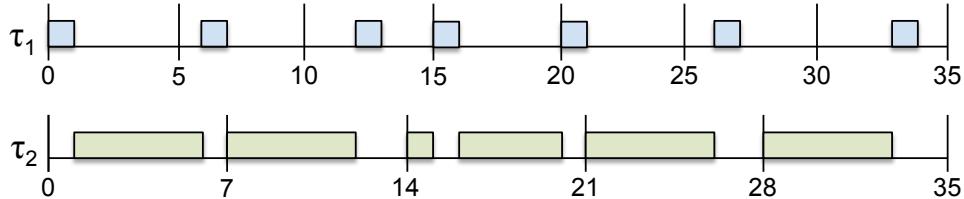

The Rate Monotonic Priority Assignment (RM) is a so-called *fixed-priority* scheduling algorithm presented by Liu and Layland in [LL73]. Fixed means, that priorities are statically assigned a priori and not modified dynamically during system runtime. RM defines a simple rule that assigns priorities to tasks according to their period, i.e. tasks with higher rates have higher priorities. Since periods are constant, RM is a fixed-priority assignment. Here, it is assumed that relative deadlines of tasks are identical to their periods ( $D_i = T_i$ ). Consequently, RM supports the handling of tasks with different rates in a multirate system. Since it may happen that a task instance is executed when a new instance of a task with higher priority arrives, RM is intrinsically preemptive. In this case the currently running task is preempted and the task with higher priority is executed. Figure 2.4 illustrates an example of a RM schedule in a *Gantt Chart*.<sup>3</sup>

Figure 2.4: Example of a RM schedule for two tasks.

It contains two tasks ( $\tau_1: T_1 = 5, C_1 = 1; \tau_2: T_2 = 7, C_2 = 5$ ) and shows how, by means of RM priority assignment, the instances of  $\tau_2$  are preempted by those of  $\tau_1$  with higher priority. The given task periods result in the *hyperperiod*  $H_\Gamma = 35$ . The hyperperiod is the minimum interval of time after which the schedule repeats itself. For such an interval with length  $H_\Gamma$ , the schedule in  $[0, H_\Gamma]$  is the same as that in  $[kH_\Gamma, (k+1)H_\Gamma]$  for any integer  $k > 0$ . Hence, for  $n$  periodic tasks synchronously released at time  $t = 0$ , the hyperperiod  $H_\Gamma$  is given by the least common multiple of the periods [But11]:

$$H_\Gamma = \text{lcm}(T_1, \dots, T_n).$$

<sup>3</sup>A Gantt Chart is a horizontal bar chart that represents a set of tasks. The Gantt chart displays time on the horizontal axis and arranges tasks on the vertical axis [SCR09].

RM is optimal among all fixed-priority scheduling algorithms [But11]. This means, that no other fixed-priority algorithm can schedule a task set that cannot be scheduled by RM. The schedulability test for RM compares the *utilization factor* of a given task set with the utilization factor of the worst possible task set which is still schedulable by RM. This results in the *least upper bound* of utilization ( $U_{\text{lub}}$ ) for all task sets that fully utilize the processor.

Given a set  $\Gamma$  of  $n$  periodic tasks, the utilization factor  $U$  is the fraction of processor time spent in execution of the task set [LL73]. Summing over the fractions of processor time ( $C_i/T_i$ ) spent for executing each task  $\tau_i$ , the utilization factor for  $n$  tasks is given by:

$$U = \sum_{i=1}^n \frac{C_i}{T_i}. \quad (2.2)$$

The utilization of the worst case task set is given by  $U_{\text{lub}} = n(2^{\frac{1}{n}} - 1)$  which converges towards  $U_{\text{lub}} = \ln(2) \approx 0.69$  with increasing  $n$  [But11]. Since the number  $n$  of tasks in the given task set  $\Gamma$  is known a priori, the schedulability test can be performed before system runtime by calculating  $U_{\text{lub}}$ . It is important to note that  $U_{\text{lub}} = n(2^{\frac{1}{n}} - 1)$  is sufficient but not necessary to guarantee the schedulability of a given task set. This means that for task sets with  $U_{\text{lub}} \leq U \leq 1$  nothing about the schedulability can be said.

RM allows a task to be executed anywhere within its period, i.e.  $D_i = T_i$ . However, in some cases a more tightened deadline is necessary. For instance, if a task has a constrained response time which is shorter than its period. Therefore, in [LW82] the *Deadline Monotonic Priority Assignment* (DM) was introduced as an extension of RM to enable scheduling of tasks with relative deadlines less or equal to their period ( $D_i \leq T_i$ ). A sufficient schedulability test for DM derived from RM is given by:

$$\sum_{i=1}^n \frac{C_i}{D_i} \leq n(2^{\frac{1}{n}} - 1). \quad (2.3)$$

Nevertheless this test is just sufficient and even more pessimistic for DM than for RM. Therefore, in [Aud+91], [Aud+93] Audsley et. al proposed an efficient method for a sufficient and necessary schedulability test for DM. This test is based on the so-called *Response Time Analysis* (RTA). At its critical instant, the response time  $R_i$  of a periodic task  $\tau_i$ , is given by the sum of its WCET and the interference ( $I_i$ ) resulting from preemption by higher-priority tasks, i.e.  $R_i = C_i + I_i$ . To calculate  $I_i$  for all higher priority tasks  $\tau_j$  ( $j < i$ ,  $\text{Prio}_j > \text{Prio}_i$ ) we have to determine the number of interferences given by  $\lceil R_i/T_j \rceil$  and the WCET of the respective interference  $C_j$ . Based on that,  $I_i$

can be calculated summing up over all interrupting tasks. Therefore,  $R_i$  is defined by:

$$R_i = C_i + \sum_{j=1}^{i-1} \left\lceil \frac{R_i}{T_j} \right\rceil C_j. \quad (2.4)$$

Since Equation 2.4 is not analytically solvable for  $R_i$ , no simple solution exists for this equation. However, by applying an iterative algorithm we can calculate the least fixpoint of the equation [But11]. If the calculated value is less or equal to the relative deadline, i.e.  $R_i \leq D_i$ , the feasibility of  $\tau_i$  can be guaranteed. The schedulability test for a task set  $\Gamma$  is positive if all tasks  $\tau_i$  are feasible. It can also be performed a priori before system runtime.

### RM and DM with Precedence Constraints

Considering precedence constraints for RM and DM the corresponding task parameters have to be modified to realize a proper task prioritization. The basic idea of these modifications is that a task cannot start before its predecessors and cannot preempt its successors. For RM this implies that for a precedence relation  $\tau_i \rightarrow \tau_j$  the release time and priority must be modified as [Cot+02]:

- $r_j^* \geq \max(r_j, r_i^*)$ , where  $r_i^*$  is the modified release time of  $\tau_i$ , and

- $\text{Prio}_i \geq \text{Prio}_j$  in accordance with RM algorithm.

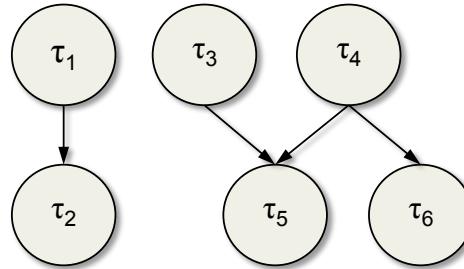

Figure 2.5: Example TDG with a set of six tasks in two subgraphs [Cot+02].

Here it is important to note that, if all tasks of the considered TDG have the same period, RM allows a free choice of priorities that we use to impose the precedence order [Cot+02]. Figure 2.5 shows a TDG for six tasks with simultaneous release times consisting of two subgraphs describing their precedence relations. Table 2.2 provides an exemplary corresponding priority

| Task     | $\tau_1$ | $\tau_2$ | $\tau_3$ | $\tau_4$ | $\tau_5$ | $\tau_6$ |

|----------|----------|----------|----------|----------|----------|----------|

| Priority | 6        | 3        | 5        | 4        | 2        | 1        |

Table 2.2: Example of a RM-based priority assignment for the TDG in Figure 2.5 considering precedence constraints.

mapping that considers the given precedence constraints and still schedulable with RM.

For DM scheduling additionally to the release times the relative deadlines have to be modified to respect the priority assignment. This means, that for a precedence relation  $\tau_i \rightarrow \tau_j$  the following parameters have to be modified [Cot+02]:

- $r_j^* \geq \max(r_j, r_i^*)$ , where  $r_i^*$  is the modified release time of  $\tau_i$ ,

- $D_j^* \geq \max(D_j, D_i^*)$ , where  $D_i^*$  is the modified relative deadline of  $\tau_i$ , and

- $\text{Prio}_i \geq \text{Prio}_j$  in accordance with DM algorithm.

Consequently, these modifications clearly ensure the preservation of the precedence relations between two tasks.

### Earliest Deadline First

In contrast to RM and DM, Earliest Deadline First (EDF) scheduling is a dynamic priority assignment approach presented by Horn [Hor74]. Here every task instance  $\tau_{i,j}$  gets a dynamically assigned priority inverse proportional to its absolute deadline  $d_{i,j}$ . This means, that tasks with shorter deadline will be executed with higher priorities. EDF is a dynamic priority assignment approach, because the absolute deadline of a periodic task  $\tau_i$  depends on the current  $j$ -th instance as:

$$d_{i,j} = \phi_i + (j-1) \cdot T_i + D_i.$$

Moreover, EDF is also intrinsically preemptive, i.e. a currently executed task is preempted if another periodic instance with shorter deadline and higher priority gets activated. This implies that the priorities have to be recalculated and reassigned at each task release. Consequently, the priority of a task may be changed dynamically during runtime. Since EDF does not make any specific assumption on the periodicity of the tasks it can also be applied for the scheduling of aperiodic tasks [But11]. Figure 2.6 depicts an example

EDF schedule for the same two tasks used for the RM example in Figure 2.4. It shows that in contrast to the RM schedule the instances of  $\tau_2$  are not preempted that often by  $\tau_1$ , because the scheduling depends on the absolute deadlines at the release times of the task. Furthermore, in case of equal absolute deadlines the currently running task keeps executing as illustrated by the last task instances of the hyperperiod.

Figure 2.6: Example of a EDF schedule for two tasks.

EDF is optimal among all periodic task scheduling approaches [But11]. This means, that if EDF cannot provide a feasible schedule no other periodic task scheduling algorithm can. A further advantage of EDF is the fact, that – for independent tasks – it guarantees feasible schedules for utilization factors up to 1, i.e. fully utilized processors. Therefore, the schedulability test for a task set scheduled by EDF is given by [LL73; Spu+95]:

$$\sum_{i=1}^n \frac{C_i}{T_i} \leq 1.$$

### EDF with Precedence Constraints

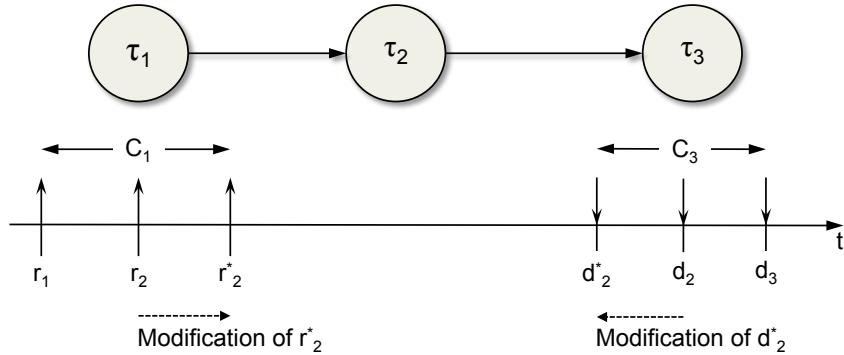

In case of EDF a modification of the release times and the absolute deadlines is necessary to handle precedence relations. This technique was originally only proposed for aperiodic tasks with deadline and precedence constraints in [CSB90]. It is optimal in the sense that a valid schedule can be found for the original task set if and only if a valid schedule can be found for the modified task set. Consequently, schedulability can be tested by applying an EDF schedulability test on the encoded task set. The modification technique directly applies to the case of periodic tasks with constrained deadlines and simple precedence constraints remaining optimal [For+10].

Summarized, for two dependent tasks  $\tau_i$  and  $\tau_j$  with  $\tau_i \rightarrow \tau_j$  the following modifications and conditions must be performed and satisfied to fulfill the given precedence constraints [But11]:

**Modification of release times:**

$s_j \geq r_j$ : Task  $\tau_j$  must start its execution not earlier than its release time.

$s_j \geq r_i + C_i$ : Furthermore, task  $\tau_j$  must start its execution not earlier than the minimum finishing time of  $\tau_i$ .

Therefore, the modified release time  $r_j^*$  can be set to the maximum of  $r_j$  and  $r_i + C_i$ :

$$r_j^* = \max(r_j, r_i + C_i).$$

**Modification of deadlines:**

$f_i \leq d_i$ : Task  $\tau_i$  must finish its execution within its deadline.

$f_i \leq d_j - C_j$ : Furthermore, task  $\tau_i$  must finish its execution not later than the maximum start time of  $\tau_j$ .

Therefore, the modified deadline  $d_i^*$  can be set to the minimum of  $d_i$  and  $d_j - C_j$ :

$$d_i^* = \min(d_i, d_j - C_j).$$

By means of these modifications of timing parameters a given set  $\Gamma$  of dependent tasks gets transformed to a corresponding independent task set  $\Gamma^*$  [CSB90]. Because of these modifications EDF with precedence constraints is also called EDF\*. Figure 2.7 provides an example for the modifications of task parameters. Here, the release time and the deadline of  $\tau_2$  have to be modified.

The modification of the absolute deadlines results in  $d_i \leq T_i$  for the tasks in  $\Gamma^*$ . Hence, similar to DM, the schedulability analysis becomes more complex for EDF\*. Therefore, Baruah, Rosier, and Howell introduced the *processor demand criterion* (PDC) [BHR90]. It says that if relative deadlines are no longer than periods and periodic tasks are simultaneously activated at time  $t = 0$  – i.e.,  $\phi_i = 0$  for all the tasks – then the number of instances  $\eta_i$  contributing to the demand in a time interval  $[0, L]$  is given by [But11]:

$$\eta_i(0, L) = \left\lfloor \frac{L + T_i - D_i}{T_i} \right\rfloor.$$

Figure 2.7: Modifications of task parameters for EDF with precedence constraints [Cot+02].

Thus, the processor demand  $g$  in the time interval  $[0, L]$  can be calculated as:

$$g(0, L) = \sum_{i=1}^n \left\lfloor \frac{L + T_i - D_i}{T_i} \right\rfloor \cdot C_i.$$

Consequently, the schedulability test for a synchronous periodic task set with relative deadlines less than or equal to task periods is given by:

$$\forall L > 0 \quad \sum_{i=1}^n \left\lfloor \frac{L + T_i - D_i}{T_i} \right\rfloor \cdot C_i \leq L. \quad (2.5)$$

For a reduced complexity, the number of intervals in which the schedulability test has to be checked can be decreased significantly. For this we make use of three observations:

1. Since the tasks are periodic and simultaneously activated at time  $t = 0$ , the schedule repeats itself after the hyperperiod  $H_\Gamma$  and the schedulability test needs to be checked only for intervals with  $L \leq H_\Gamma$ .

2. The processor demand  $g(0, L)$  is a step function which remains constant if  $L$  lies between two deadlines  $d_k$  and  $d_{k+1}$ . This implies, that if  $g(0, L) < L$  holds for  $L = d_k$ , then it also holds for all  $L$  with  $d_k \leq L < d_{k+1}$ . Consequently, the schedulability test needs to be checked only for values  $L = d_k$ .

3. Since in any case for the utilization factor  $U < 1$  holds, the demand is trivially satisfied after some time instant  $L^*$ . It can be shown that the value for  $L^*$  can be derived and calculated as [But11]:

$$L^* = \frac{\sum_{i=1}^n (T_i - D_i) U_i}{1 - U}.$$

Summarizing these observations and considering that it must be checked at least until the largest relative deadline  $D_{\max}$ , this results in the following schedulability test based on Equation 2.5:

$$\forall L \in \mathcal{D} \quad \sum_{i=1}^n \left\lfloor \frac{L+T_i-D_i}{T_i} \right\rfloor \cdot C_i \leq L, \quad (2.6)$$

with

$$\mathcal{D} = \{d_k | d_k \leq \min[H_{\Gamma}, \max(D_{\max}, L^*)]\}.$$

A comparison of EDF and RM respectively DM shows that EDF allows a higher processor utilization because RM can only guarantee feasibility for task sets with utilization  $U \leq 0.69$ . Moreover, in spite of the additional computation needed by EDF for updating the absolute deadline at each job activation, EDF introduces less runtime overhead than RM. Specifically, to enforce the fixed priority order, the number of preemptions utilizing RM is typically much higher than applying EDF. Despite this big advantages the fixed priority algorithms still are widely spread in many real-time systems [Ram+09]. Beside other arguments it is often argued that EDF is more complicated to implement because it dynamically assigns priorities during runtime. However, it has been shown that most of those arguments are not relevant in practical systems [But05].

## 2.2 Distributed Real-Time Systems

In the previous section we considered real-time systems consisting of a single processing unit. However, nowadays most embedded real-time systems are so-called *distributed real-time systems* [Kop11]. A distributed system is defined to be a system of multiple networked processing elements – generally referred to as *nodes* – cooperating on a common function or set of functions [BW09]. In general, distributed systems have a number of advantages over centralized systems [SZ06]:

**Spatial Distribution:** The functionality of a embedded system utilizes input data from and generates output data for the environment. This data exchange with the environment is realized through *sensors* and *actuators*. For instance, in the vehicle body of a car these sensors and actuators for common functions are often spread widely. In contrast to a centralized component, a spatial distribution of processing elements near to the involved sensors and actuators can reduce the cabling effort significantly.

**Extensibility and Scalability:** In a distributed system the extension with additional components and functions is much easier. This can be realized

by connecting additional processing elements instead of replacing a whole centralized system. As a result, this enables scalability and efficient composition of a overall system by combining modular subsystems which implement different functions.

**Fault Tolerance:** The availability of multiple processors enables the application to become tolerant to processor failures by avoiding a *Single-Point-of-Failure*<sup>4</sup> (SPOF). The system design should enable the implemented functionality to exploit this redundancy [BW09]. Fault tolerance is an important attribute for the reliability and safety of a (distributed) system. In Section 2.3.1 these aspects of system design are described in more detail.

There are two ways of viewing a distributed system: defined by the physical system components (*physical model*) and defined from the view of processing or computation (*logical model*) [Jal94]. The logical model defines the functionality whose correct behavior must be ensured. For a real-time system the correct behavior also depends on timing. The physical model describes the distributed components on which the computations are performed. Beside the advantages described above distributed systems also introduce new challenges. In the following we consider distributed real-time systems requiring a schedulability analysis which has to consider communication delays to fulfill timing constraints of communicating tasks. Moreover, fault tolerance gets more complex, which makes the problem of tolerating faults while respecting timing constraints even more difficult [Cot+02]. Although the availability of multiple processors enables the application to become tolerant of processor failures by avoiding a SPOF, it also introduces the possibility of more faults occurring in the system which would not occur in a centralized single-processor system. These faults are associated with partial system failure and the logical model must either be shielded from them, or be able to tolerate them [BW09]. Therefore, the goal of our work is a fault-tolerant design of distributed real-time systems preserving the correct behavior – including timing constraints – in the logical model despite the failure of components in the physical system.

It is useful to classify distributed systems as either *tightly coupled*, i.e. nodes, have access to a common memory, and *loosely coupled*, i.e. they do not [BW09]. In a tightly coupled system synchronization and communication can be realized by techniques based on the use of shared variables, whereas in a loosely coupled system some form of message communication is indispensable. In this thesis the term "distributed system" refers to a loosely coupled topology communicating over a network. Furthermore, we assume that each node has its own clock and that these clocks are synchronized for

---

<sup>4</sup>Any single component within a system whose failure will lead to a failure of the system is called a Single-Point-Of-Failure [Pra96].

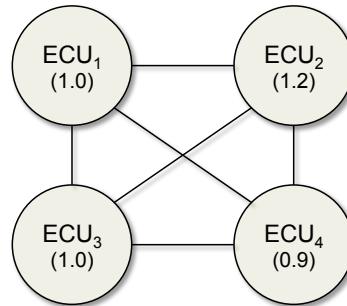

real-time issues. The manner in which the different nodes in a system are connected is called the *network topology* [Jal94]. A quite popular topology of distributed systems is a *bus*, to which all the different networks are connected, instead of a point-to-point communication network. An additional classification of a distributed system can be based on the variety of processors in the network topology. In a *homogeneous* system all processors are of the same type; a *heterogeneous* system contains processors of different types [BW09]. As we show in Chapter 4 our approach supports homogeneous as well as heterogeneous systems to a certain extent.

## 2.2.1 Task Scheduling in Distributed Real-Time Systems

Task scheduling in distributed systems has to deal with two levels. The *local scheduling* on the local level of each processor and the *global scheduling* on the level of the allocation of tasks to the processors [Cot+02]. Task allocation is often also called task mapping. Local scheduling means the assignment of the processor to tasks. For a real-time system this implies the fulfillment of timing constraints. Therefore, scheduling algorithms like the ones described in Section 2.1.2 can be utilized. Global scheduling means the allocation of tasks to the processors composing the distributed system. Obviously, the task mapping must be performed in such a way that the local scheduling can guarantee the fulfillment of the tasks timing constraints. In general, the problem of finding an optimal feasible allocation of  $n$  tasks to  $p$  processors is known to be NP-hard [Bur91]. Therefore, this problem is often addressed by searching for solutions which respect the initial constraints as much as possible, and then choosing the best solution, if several solutions are found [Cot+02].

Task mapping can be performed as *static allocation* or *dynamic allocation*. At static allocation, there cannot be any additional allocation or reallocation of tasks during system runtime, i.e. the initial allocation of tasks is fixed. At dynamic allocation the scheduling strategy assigns a node to a task guaranteeing the timing constraints when a task arrives. Dynamic allocation can increase the fault tolerance of a distributed system, e.g. in case of a node failure [Cot+02]. However, it can also lead to non-determinism or missing of timing constraints if the allocation is performed at runtime. For instance, the global scheduling algorithm finds no feasible solution because of its additionally required computation time. Our approach combines the advantages of both allocation concepts. On the one hand it keeps the determinism of the static allocation and guarantees the timing constraints; on the other hand it increases the fault tolerance by including possible reallocations in the predetermined solution to compensate node failures. Additionally, global scheduling may partition the computation of one task to different processors by utilizing *task migration*, i.e. a task can change node during its execution. Task migra-

tion consists of transferring its context<sup>5</sup>, which continuously changes during execution, and, if required, its code<sup>6</sup>, which does not change [Cot+02]. To minimize the migration time, the code of the tasks can be replicated on the nodes on which it shall be executed. Thus, in the case of migration, only the context must be transmitted.

### 2.2.2 Communication in Distributed Real-Time Systems

In addition to reliability and determinism, the timeliness of transmitted data has to be ensured for distributed real-time systems. This is the most important difference between a real-time communication system and a non-real-time communication system. Consequently, the real-time communication infrastructure utilized in such a system has to fulfill numerous requirements:

**Reliability:** To improve the communication reliability for distributed real-time systems several different techniques are utilized. For instance, the use of robust channel encoding, the use of error-correcting codes for forward error correction, or the transmission of replicated messages over redundant communication channels. In many non-real-time communication systems, reliability is achieved by time redundancy, i.e. retransmission of a lost message. However, this strategy is mostly inappropriate especially for hard real-time systems. If you consider a scenario, where a sensor component sends periodically, e.g. every millisecond, a message with sensory data to a control component. In case the message is corrupted or lost, it makes more sense to wait for the next message that contains a more recent observation than to retransmit the lost message with the outdated observation [Kop11].

**Determinism:** Determinism is a major property of a real-time system. Therefore the communication behavior must be deterministic, too. This means, that the order of messages must be the same on all communication channels and the arrival times of replicated messages over redundant channels are similar or at least close together.

**Short Transmission Latency:** A *distributed real-time transaction* generally starts with the reading of an input value via sensor and terminates with the output of the results to an actuator [Kop11]. The duration of such a distributed real-time transaction results from the time needed for the computations within the components and the time needed for the message transmission between the involved components. This duration is called *end-to-end delay* because it starts at one end of the system (source) and ends at the other end (destination) [Cot+02]. Since the

---

<sup>5</sup>Data, processor registers, etc.

<sup>6</sup>Instructions composing the task program

end-to-end delay should be as small as possible, the worst case transmission latency of a message should be small for real-time communication. The transmission latency is also called *transmission delay* or *communication delay*.

**Clock Synchronization:** In a distributed system, the temporal accuracy can only be checked if the duration between the time of the input value acquisition observed by the sensor node, and the data output determined by the actuator node, can be measured. This requires the availability of a global time base of proper precision among all involved nodes. Consequently, the communication system must establish such a global time and synchronize the nodes.

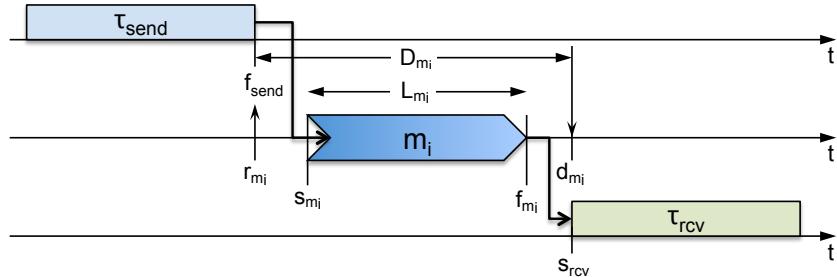

### Real-Time Messages

Similar to the definition of tasks two main classes of messages can be defined for real-time communication: periodic and aperiodic messages. An aperiodic, also called asynchronous message  $m_i$  is generated by an aperiodic task and is just characterized by its length  $L_i$  and its deadline  $D_i$ . Periodic, also called synchronous messages are generated and consumed by periodic tasks. Their characteristics are similar to the characteristics of their respective source tasks [Cot+02]. Hence, a set  $\mathcal{M}$  of periodic real-time messages can be characterized by the following set of parameters illustrated in Figure 2.8:

- $m_i$ : A generic message, where different instances of this message may exist over time. A message can also be notated as  $m_{(\tau_{tx}, \tau_{rx})}$ . This notation contains the sender task  $\tau_{tx}$  and the receiver task  $\tau_{rx}$  of a message  $m_i$ .

- $m_{i,j}$ : The  $j$ -instance of  $m_i$ .

- $T_{m_i}$ : The period of  $m_i$  at which instances of a message  $m_i$  are generated. Thereby, this period depends directly on the period of the sender task.

- $L_{m_i}$ : The *data length* of  $m_i$  which represents the original data of  $m_i$ . This means that additional overhead depending on the communication protocol has to be considered for the transmission time and the required *payload length* of  $m_i$ .

$r_{m_{i,j}}$ : The release time of  $m_{i,j}$  is an absolute value and specific for each instance. We define that a sender task  $\tau_{tx}$  must finish its computations before a message can be released. Consequently,  $r_{m_{i,j}} = f_{tx}$ , the finishing time of  $\tau_{tx}$ , always holds.

$d_{m_{i,j}}$ : The absolute deadline of  $m_{i,j}$  is a specific value for each instance. We define that  $m_i$  must be transmitted before the receiver task  $\tau_{rx}$  can start its execution. Therefore,  $d_{m_{i,j}} = s_{rx}$ , the start time of  $\tau_{rx}$ , always holds.

$D_{m_{i,j}}$ : The relative deadline of  $m_{i,j}$  represents the time interval  $\Upsilon_{m_{i,j}} = [r_{m_{i,j}}, d_{m_{i,j}}] = [f_{tx}, s_{rx}]$ , i.e. the *available transmission time interval* for  $m_{i,j}$ .

$s_{m_{i,j}}$ : The transmission start time of  $m_{i,j}$  with  $s_{m_{i,j}} \geq r_{m_{i,j}}$  is an absolute value, which is specific for each instance.

$f_{m_{i,j}}$ : The transmission finishing time of  $m_{i,j}$  with  $f_{m_{i,j}} \leq d_{m_{i,j}}$  is an absolute value, which is specific for each instance.

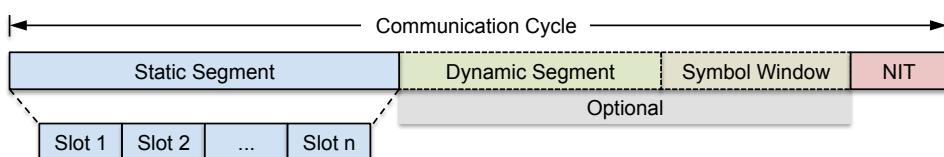

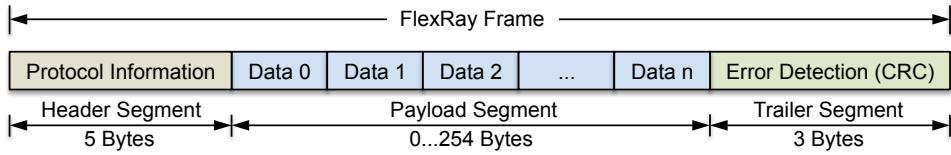

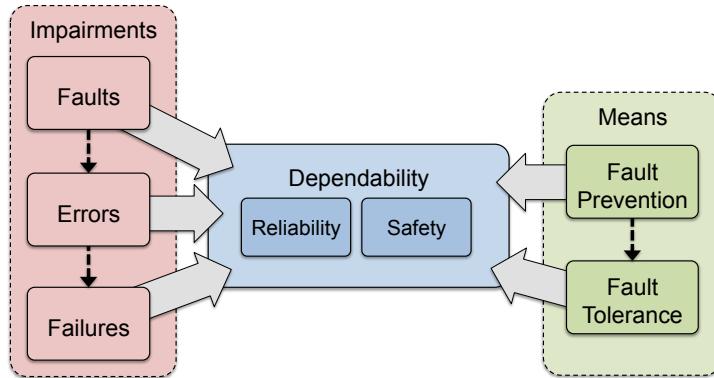

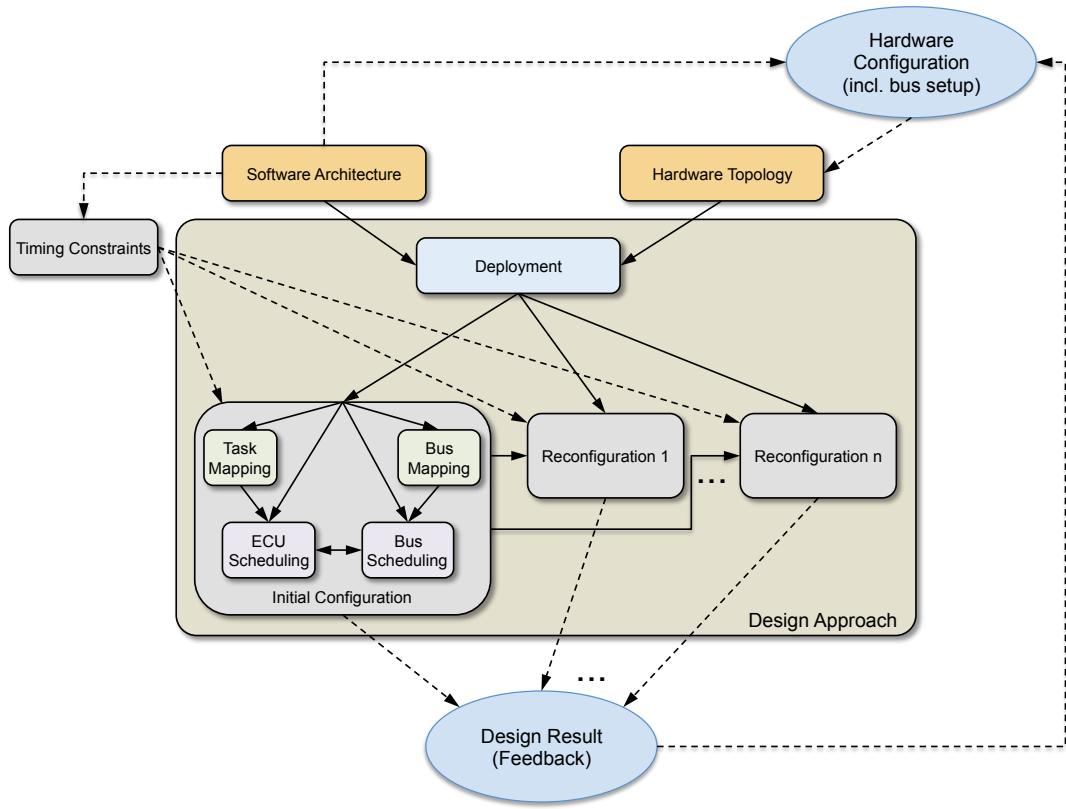

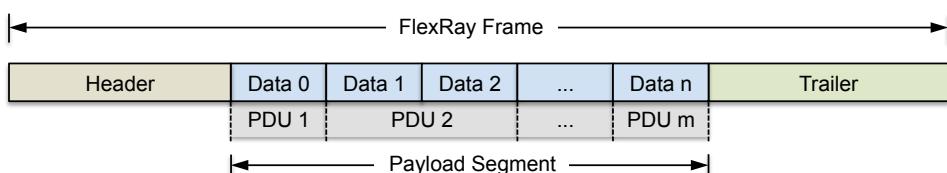

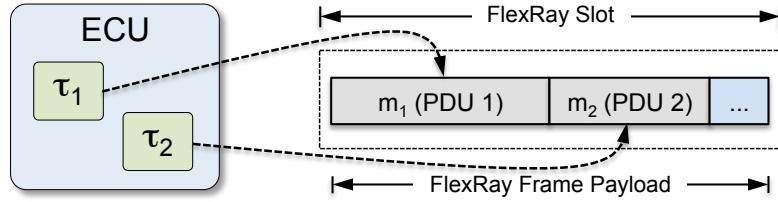

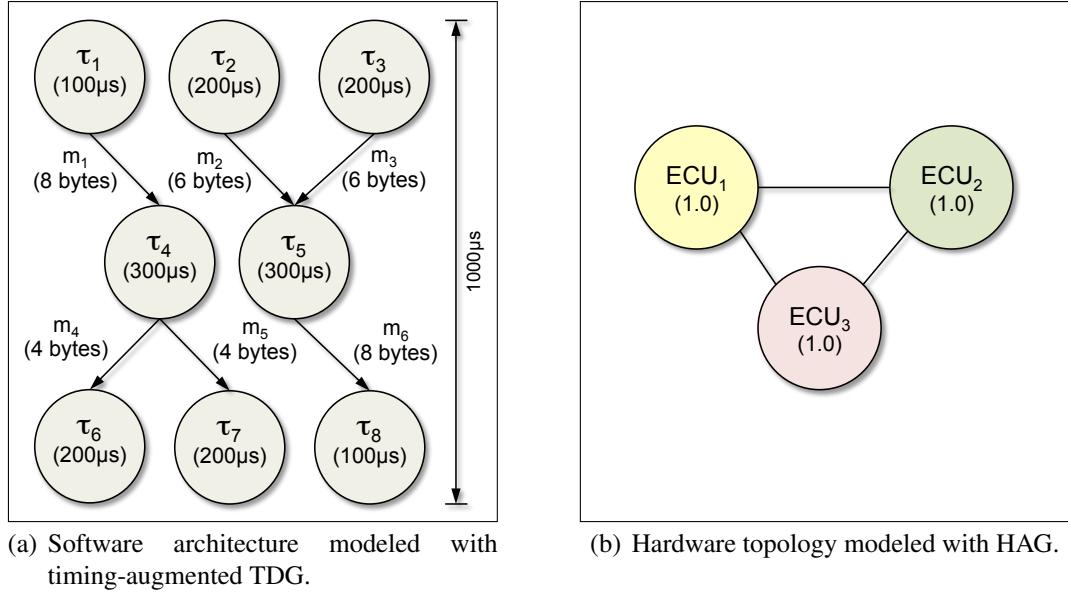

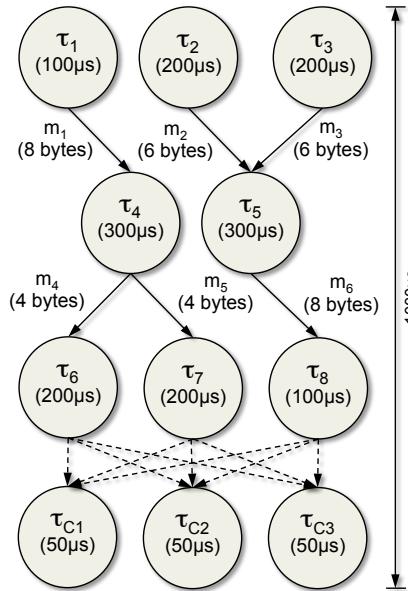

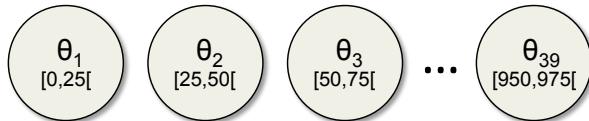

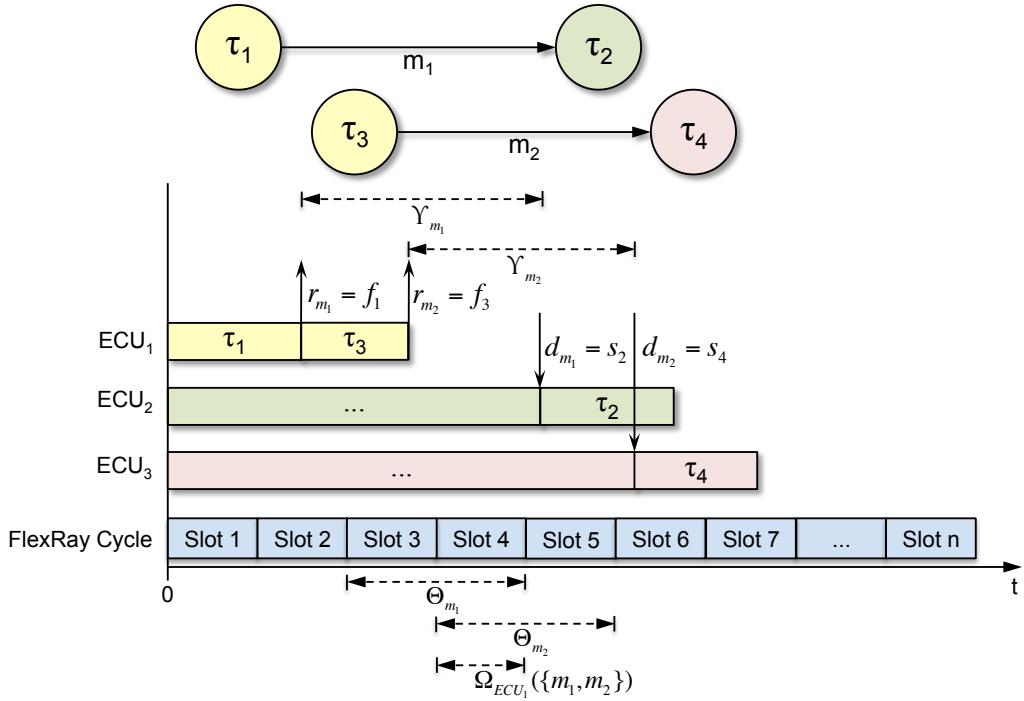

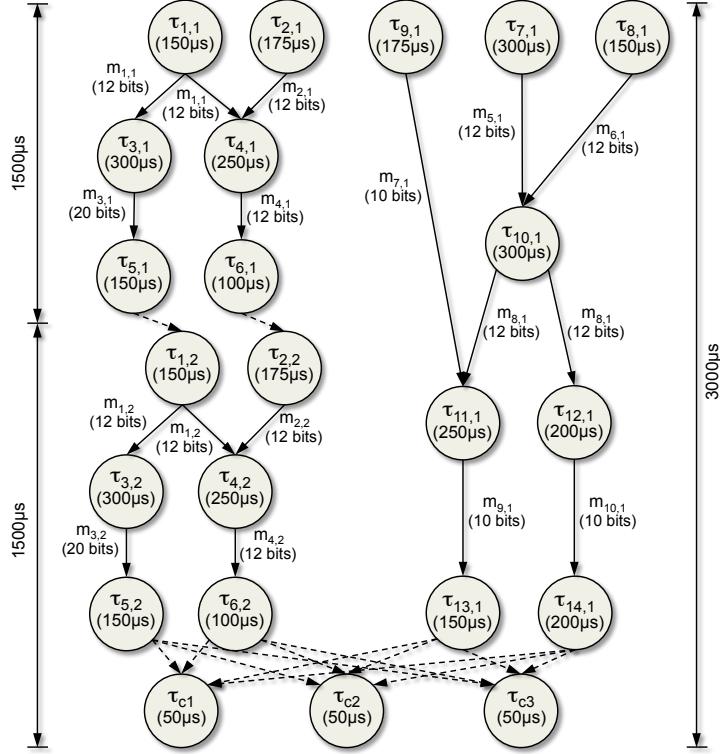

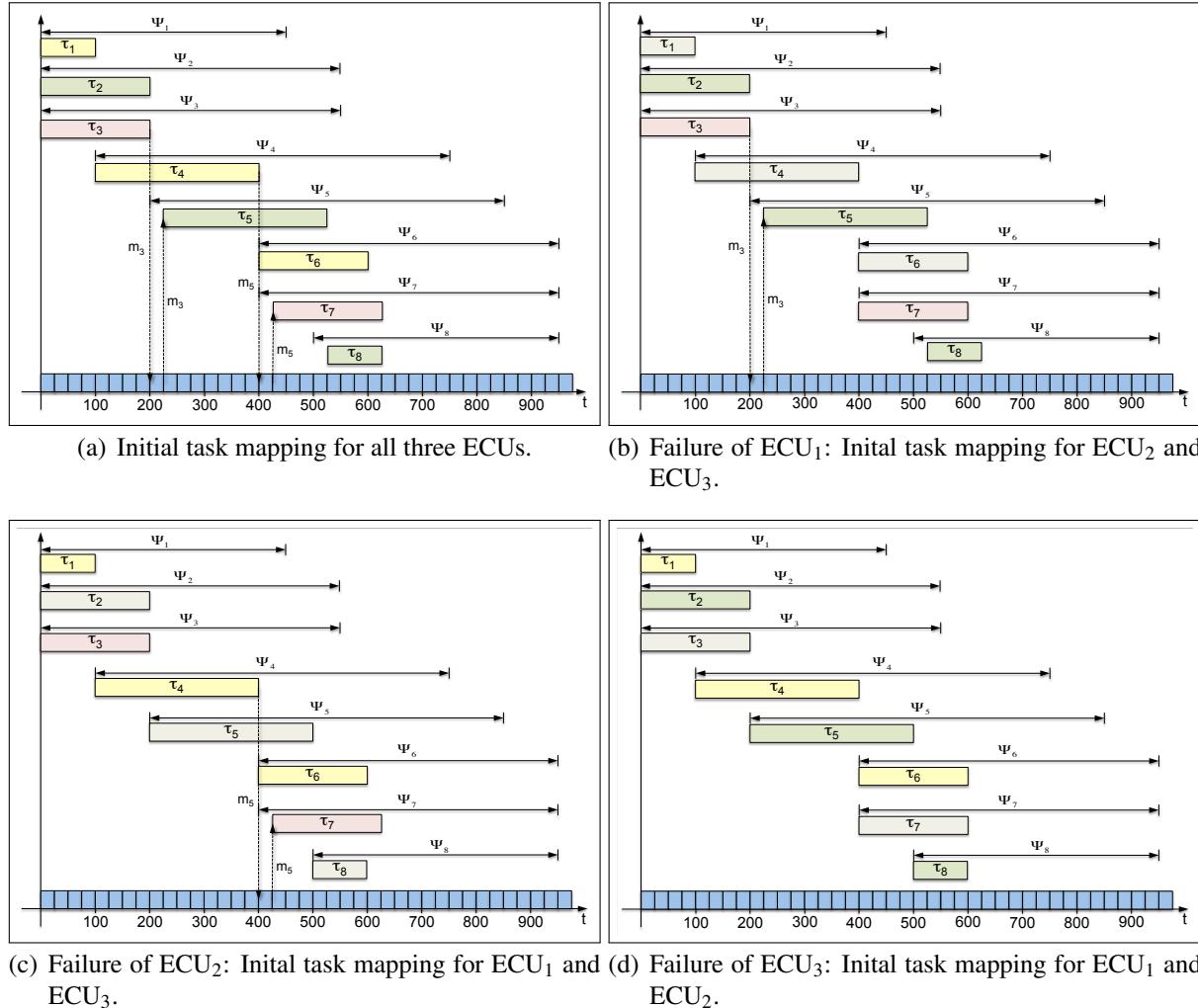

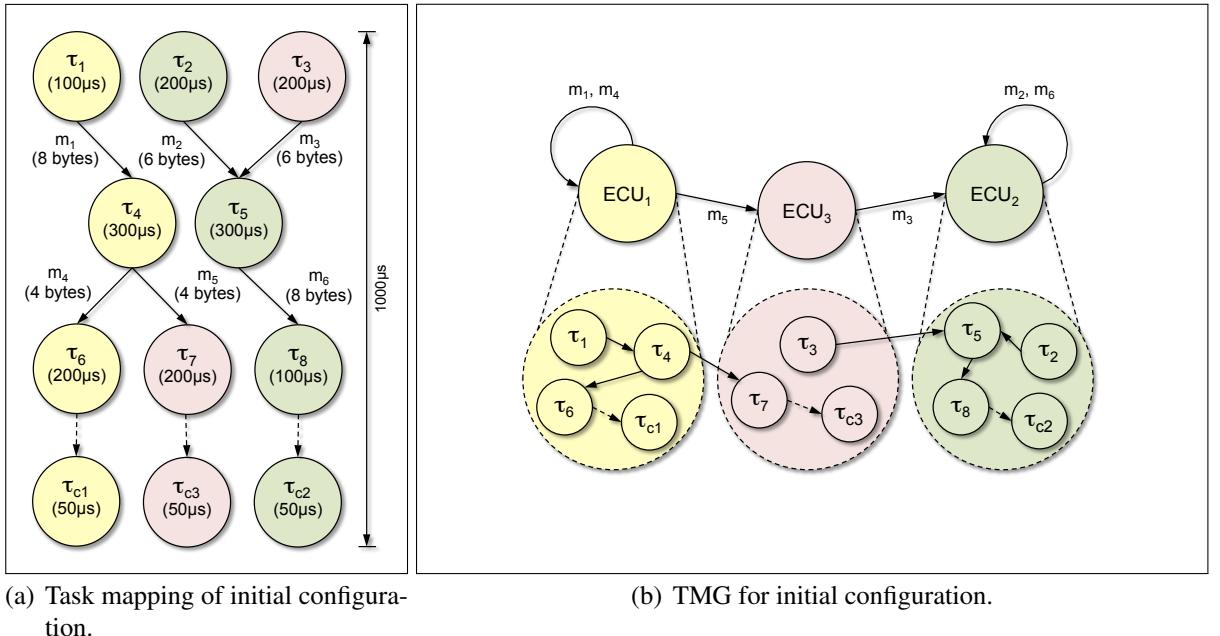

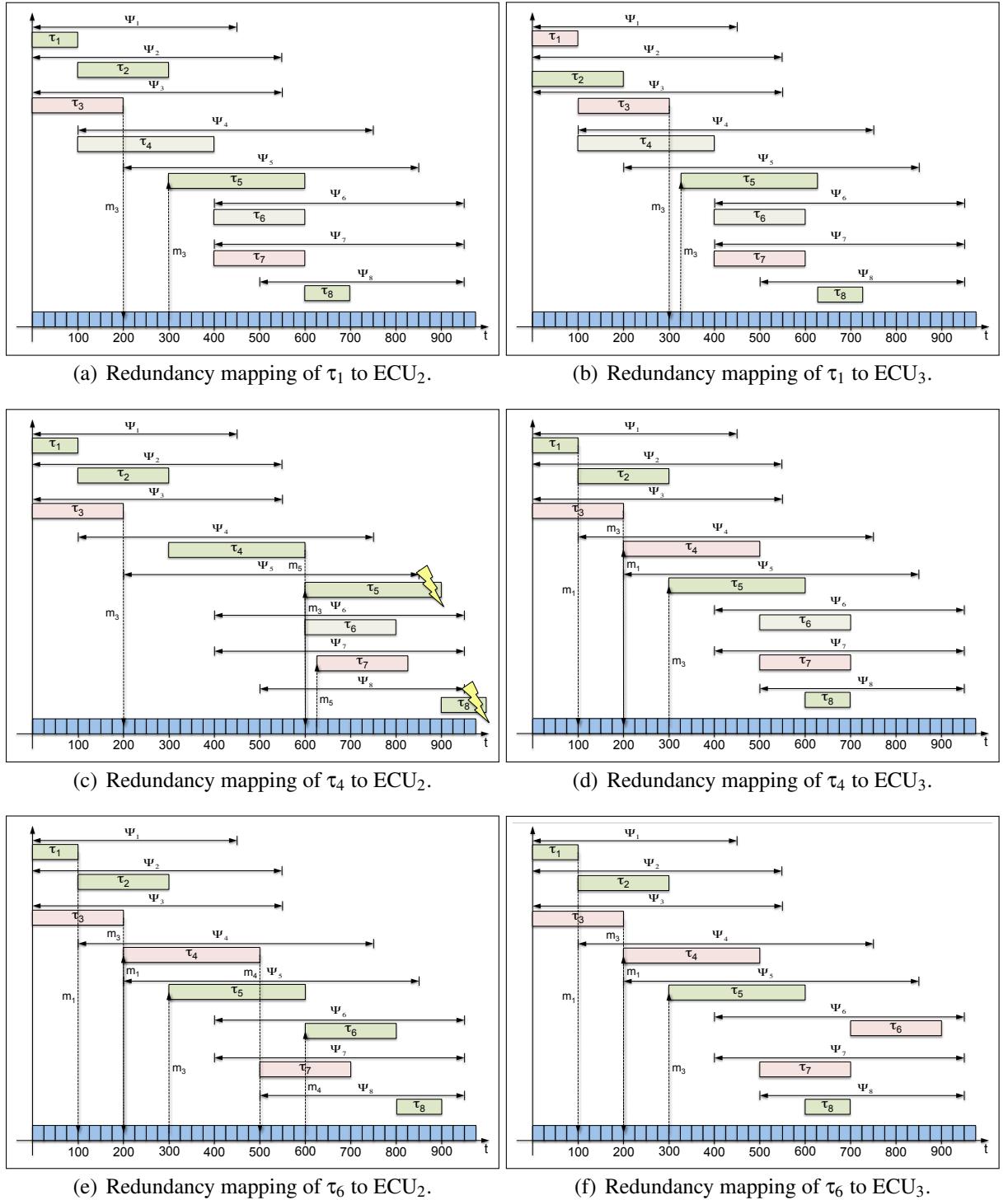

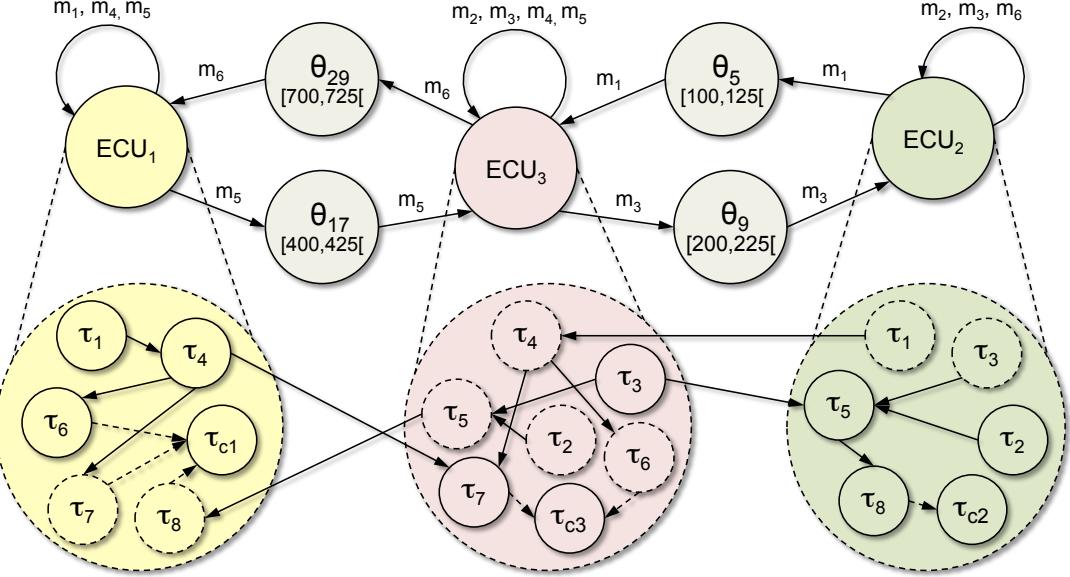

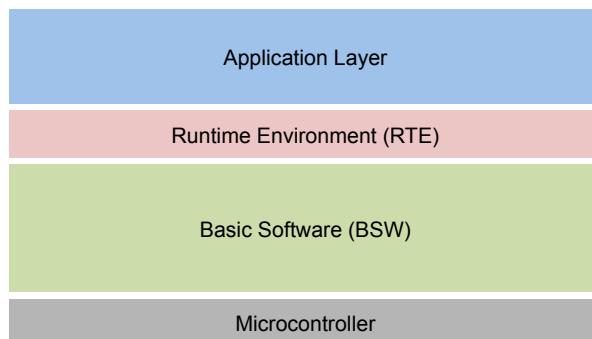

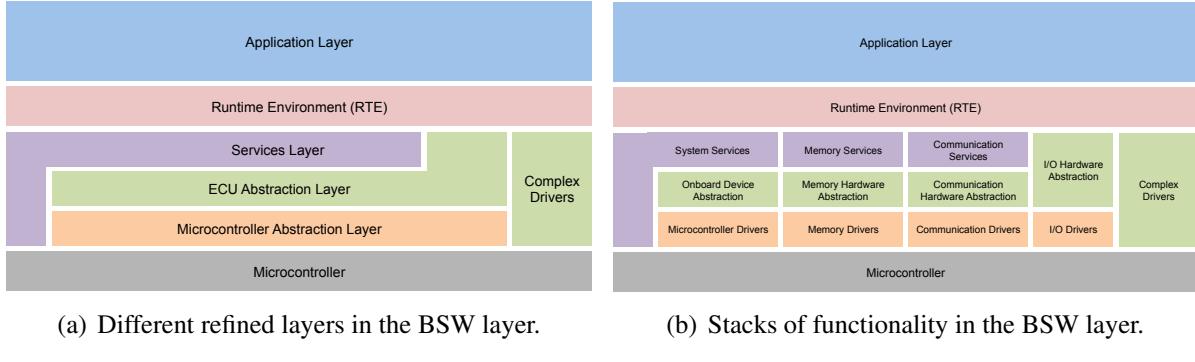

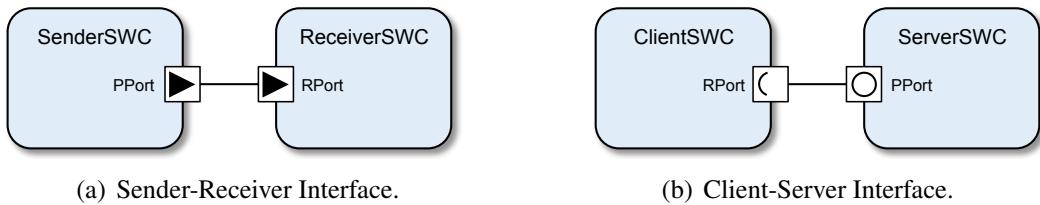

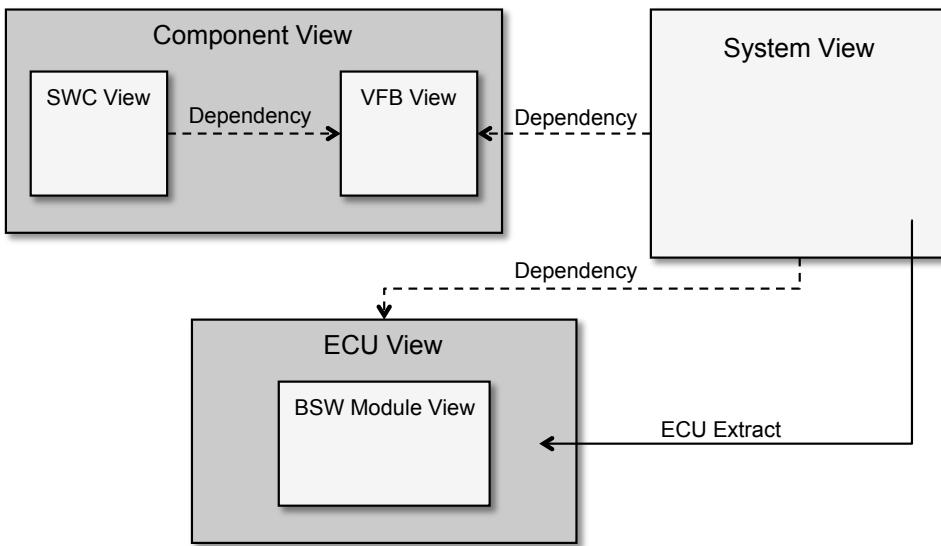

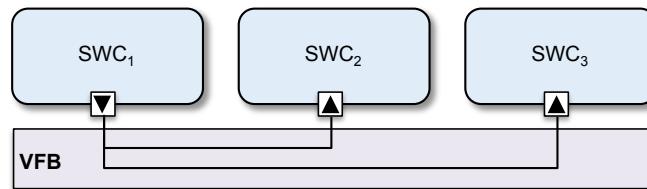

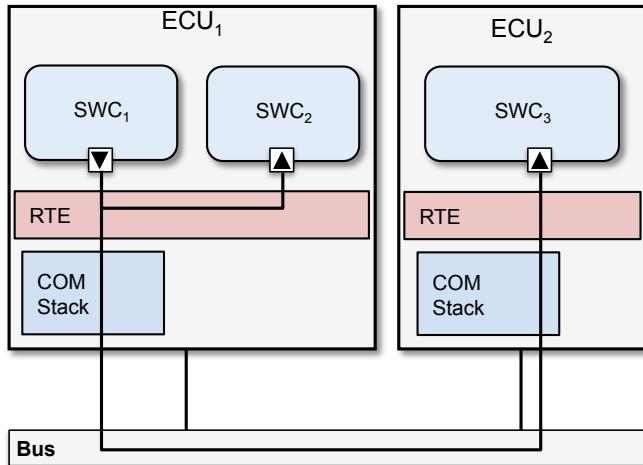

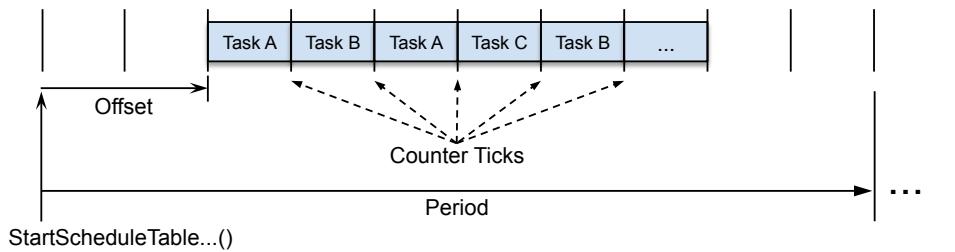

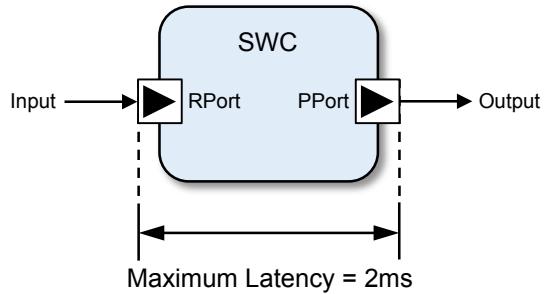

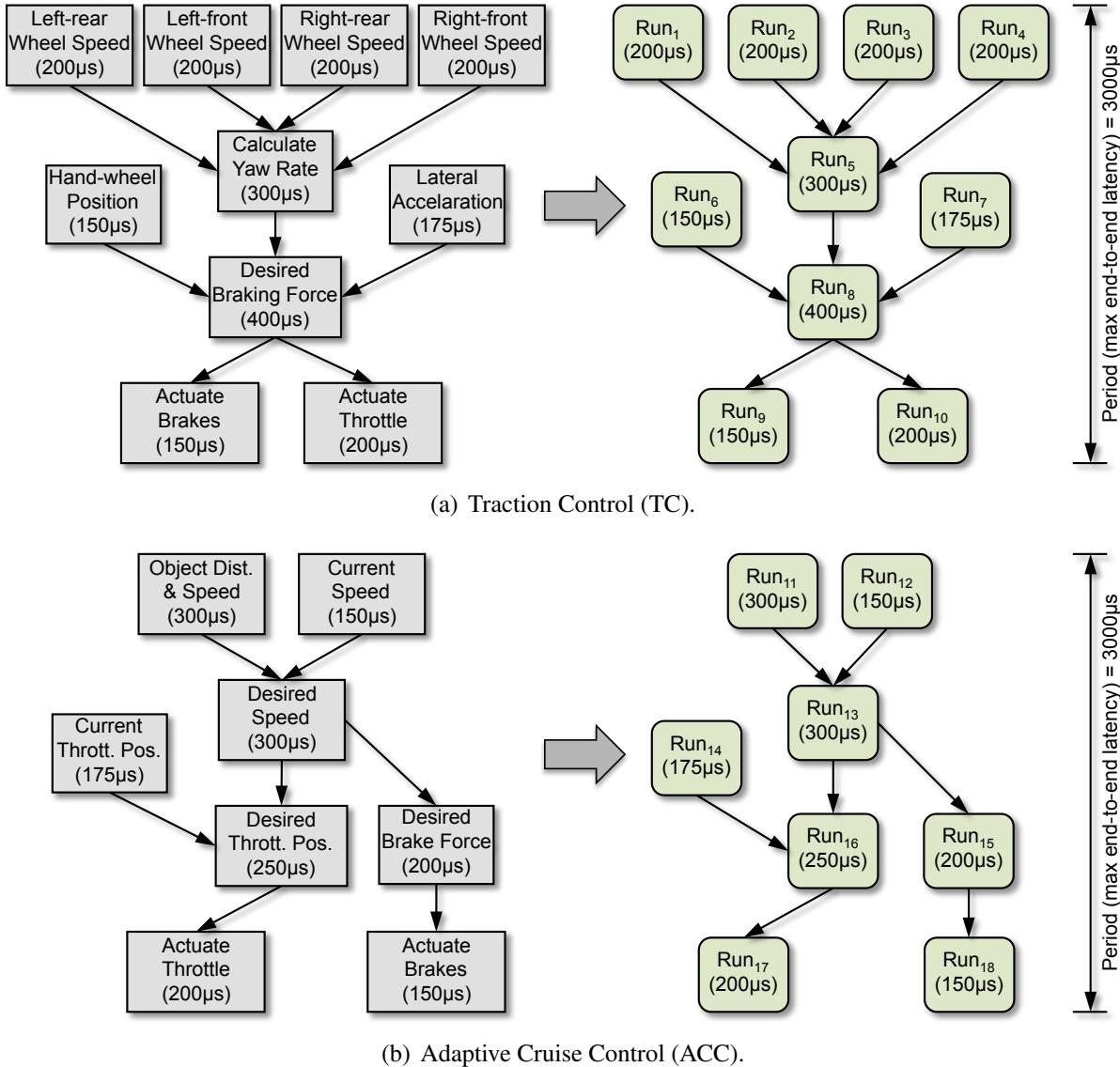

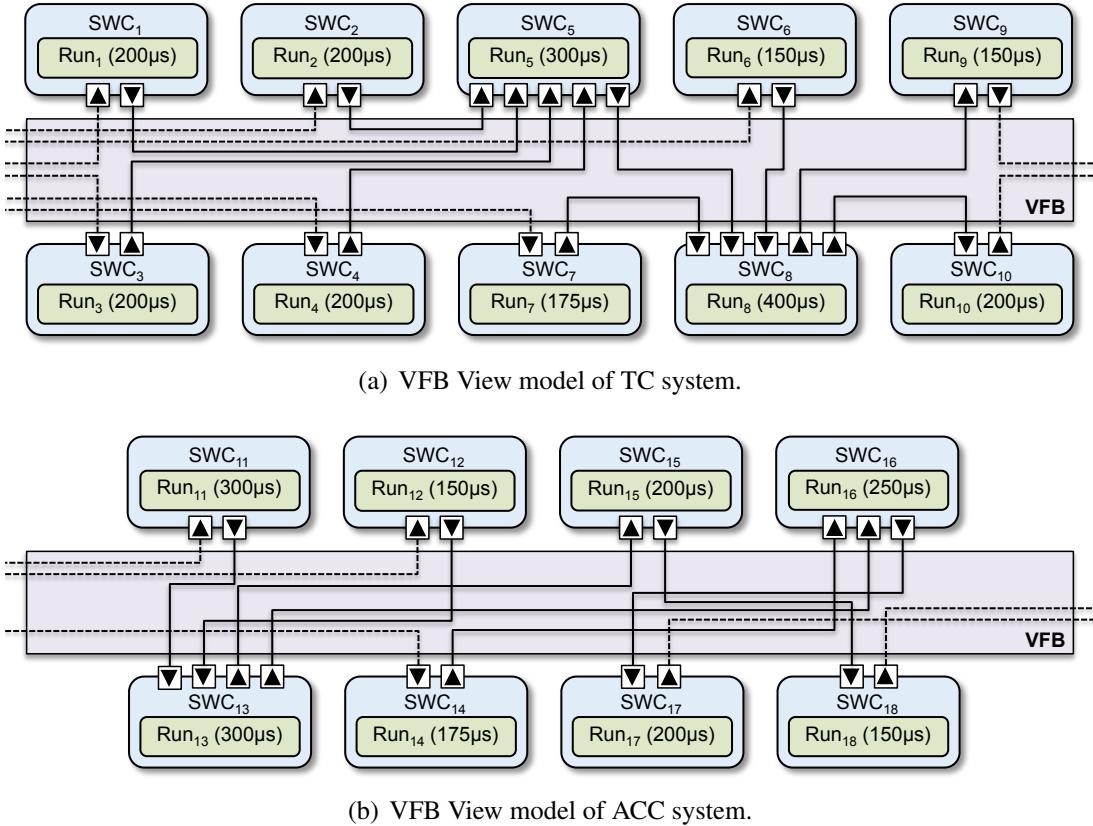

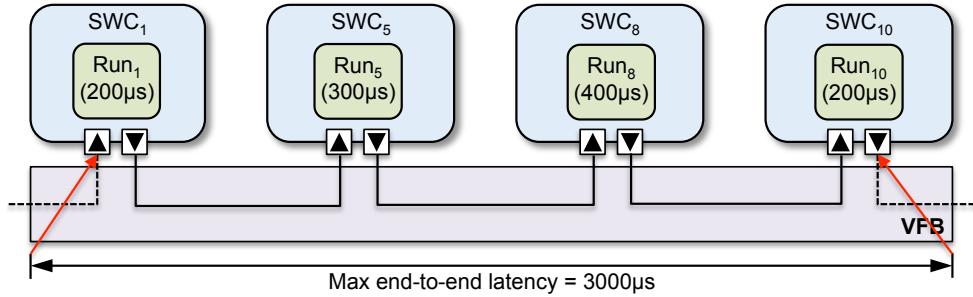

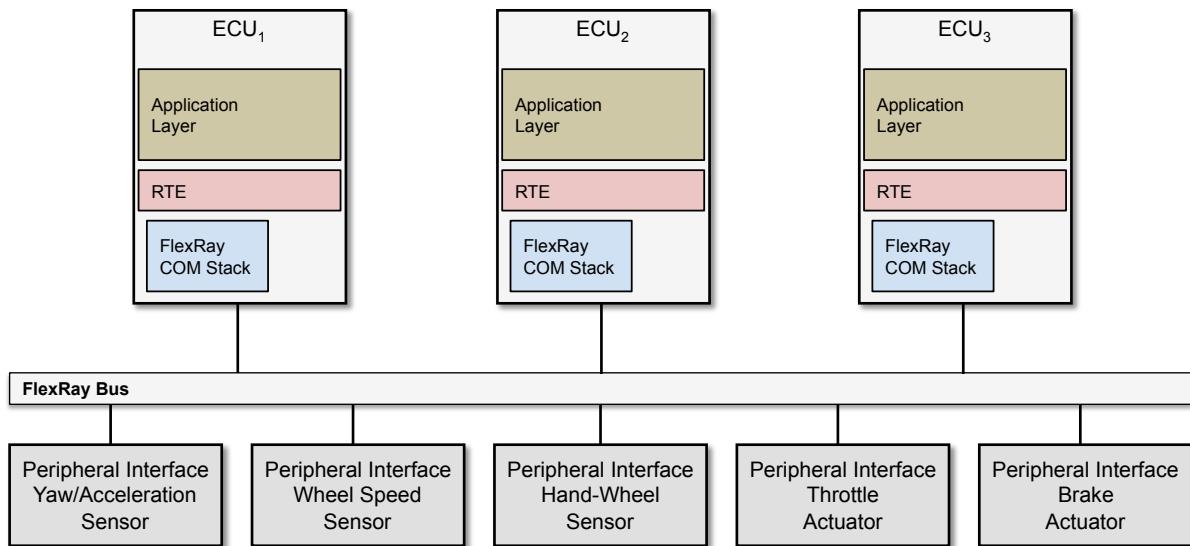

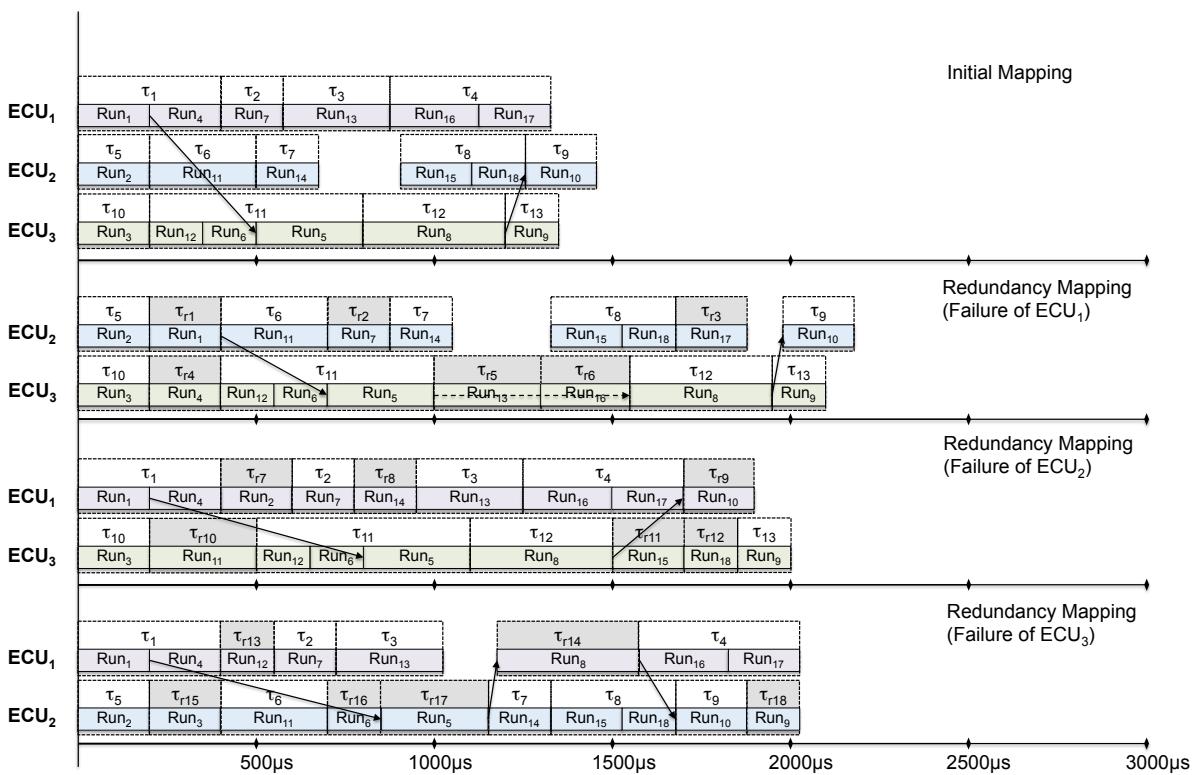

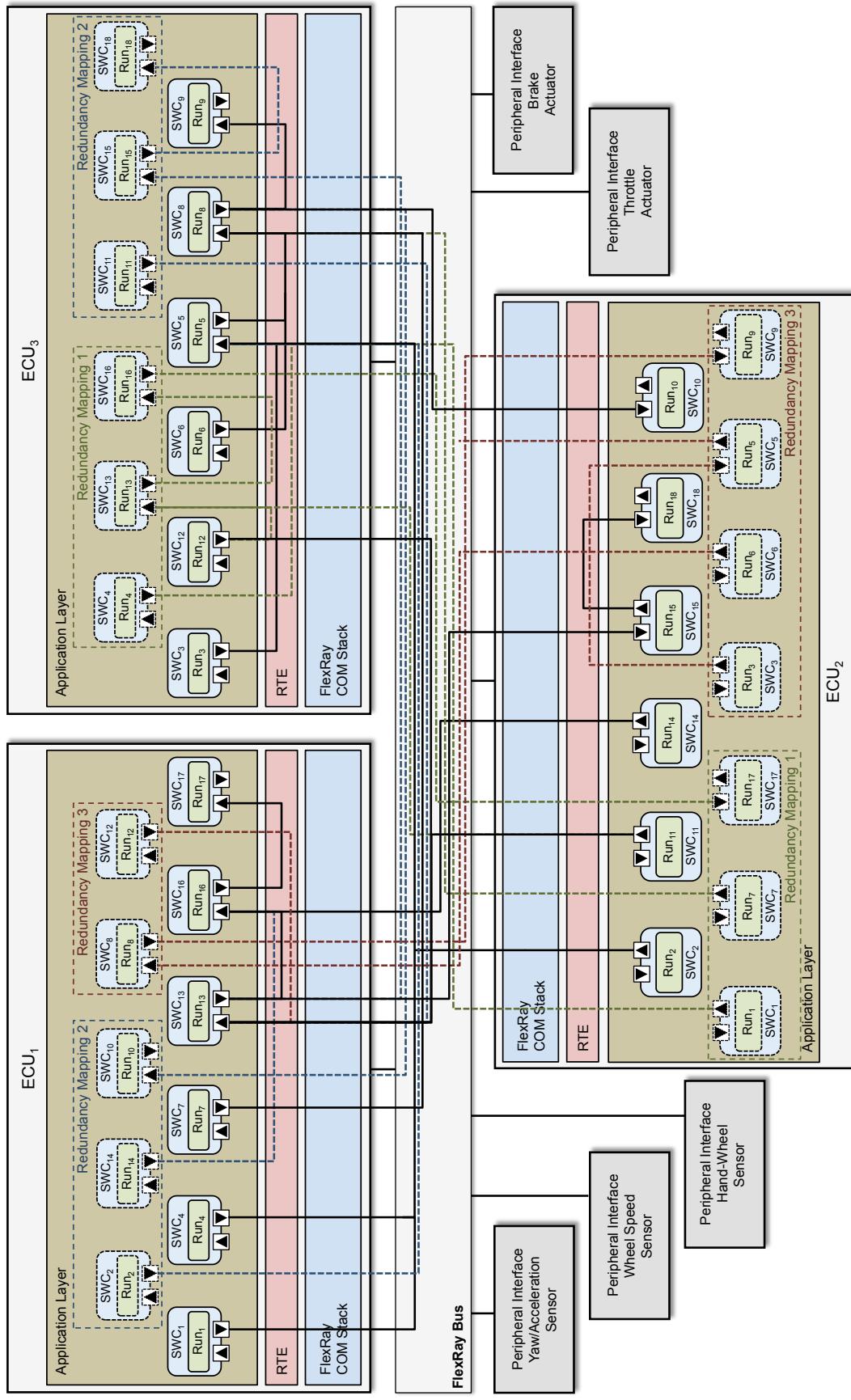

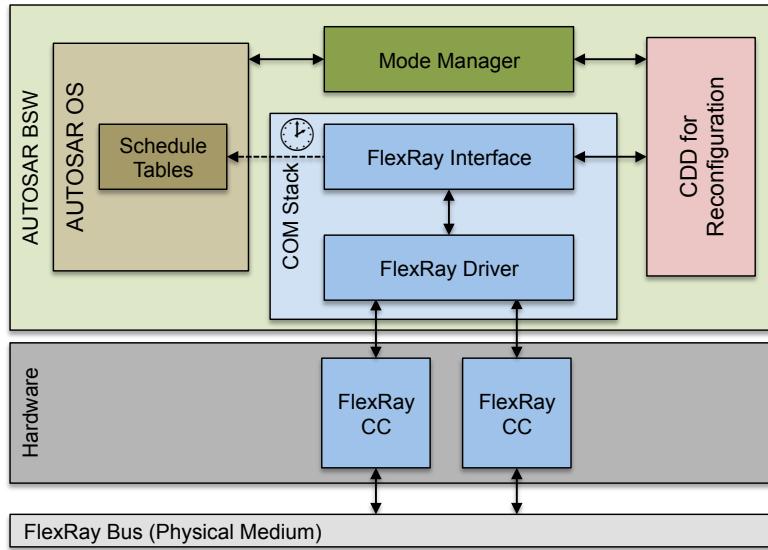

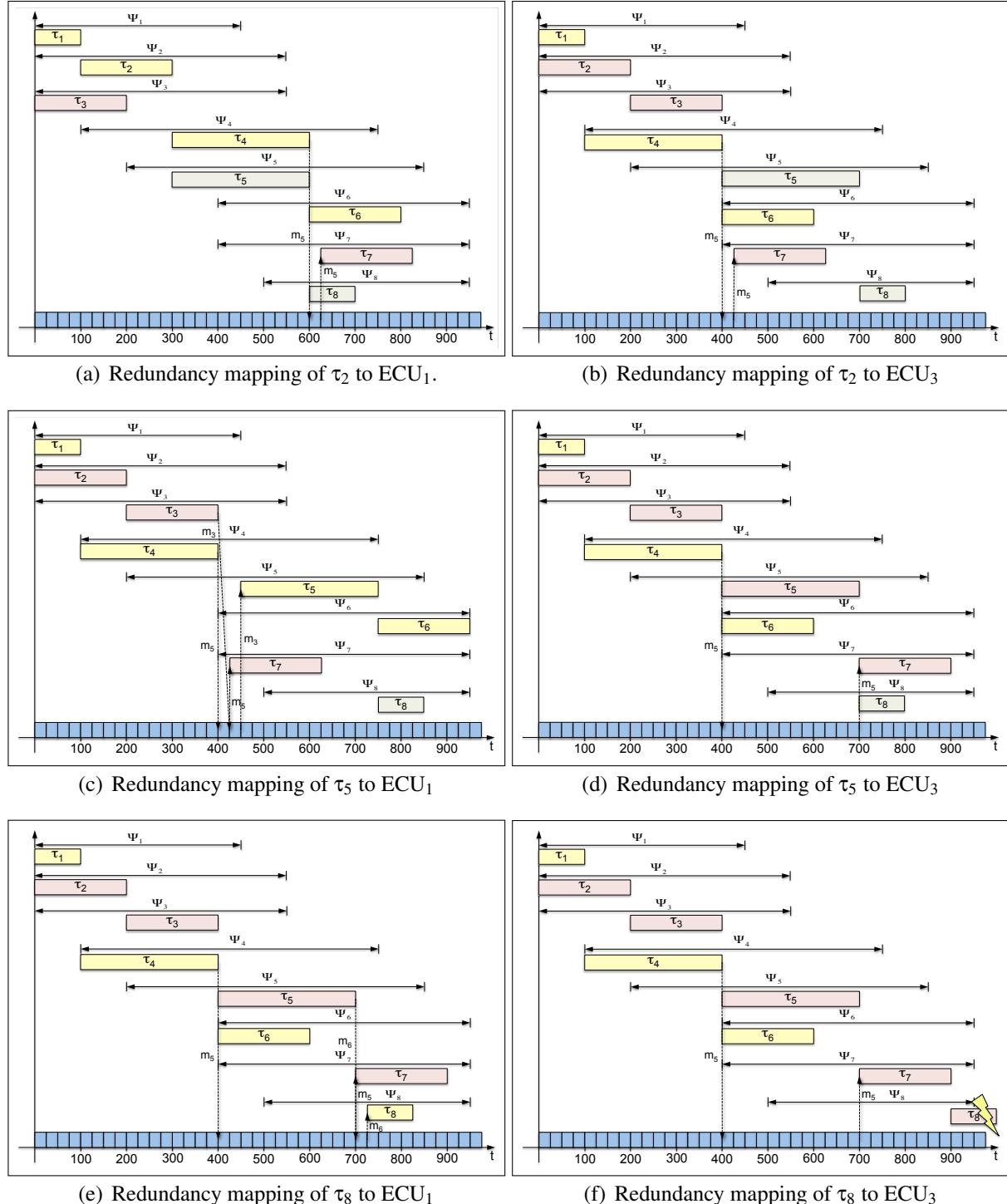

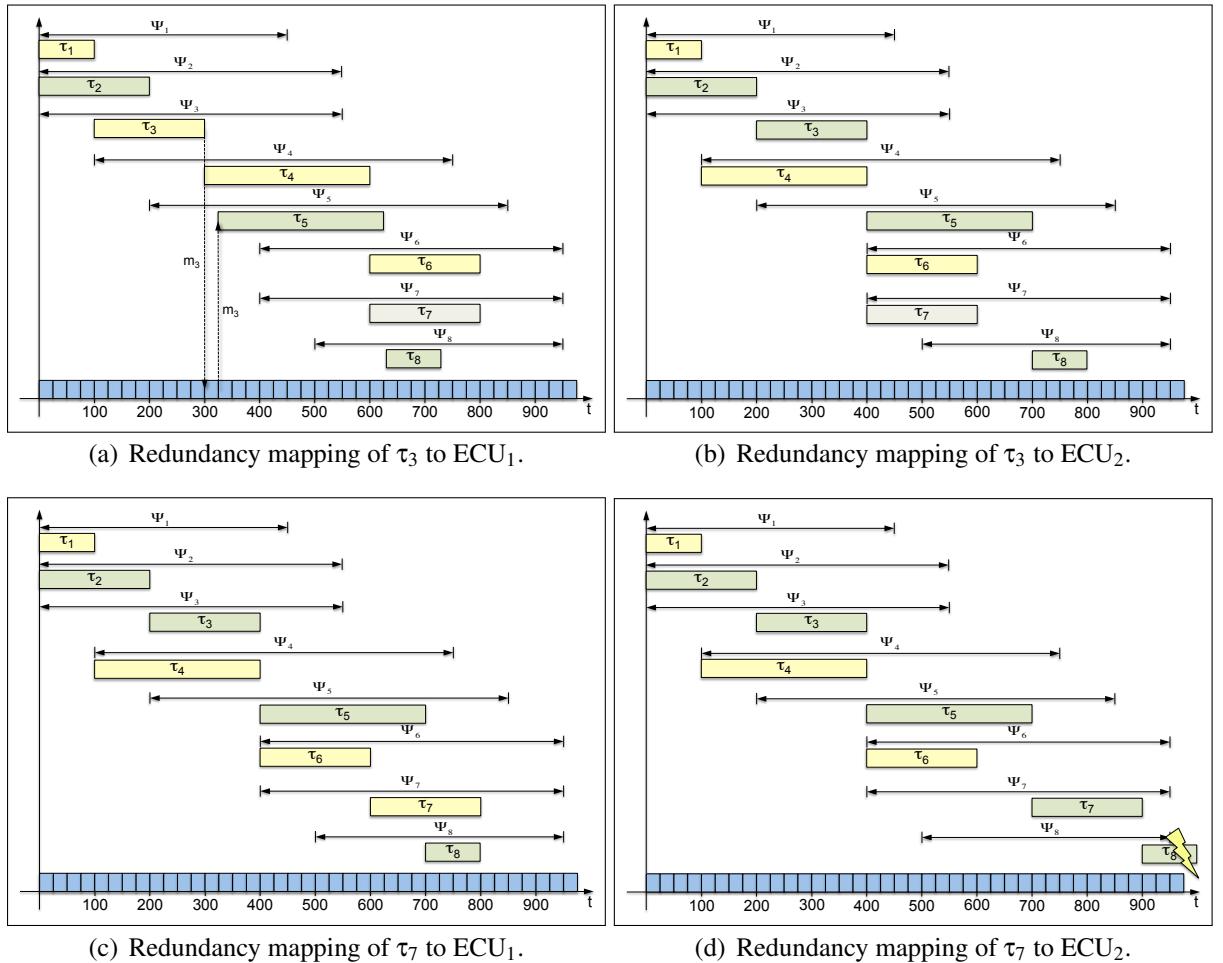

Figure 2.8: Parameters of a periodic real-time communication message.