A thesis submitted to the Faculty of Computer Science,

Electrical Engineering and Mathematics of the

University of Paderborn in partial fulfillment of the requirements for the degree of Dr. rer. nat.

submitted by

Dipl.-Inform. Timo Kerstan Paderborn, 21. März 2011

# TOWARDS FULL VIRTUALIZATION OF EMBEDDED REAL-TIME SYSTEMS

| Supervisor |                                                                              |

|------------|------------------------------------------------------------------------------|

| •          | Prof. Dr. rer. nat. Franz Josef Rammig                                       |

| Referees   |                                                                              |

|            | Prof. Dr. rer. nat. Franz Josef Rammig<br>Prof. Dr. rer. nat. Marco Platzner |

Timo Kerstan: *Towards full virtualization of embedded real-time systems*—© University of Paderborn, 21. März 2011

### **ABSTRACT**

The growing complexity and the need for high level functionality in embedded hard real-time systems lead to conflicting goals for the design of the underlying system software. Adding the required high level functionality endangers the properties of being small, robust, efficient, safe and secure typically stated for embedded real-time operating systems. On the other side, the capability of handling hard real-time loads in a general purpose OS is often not compatible due to strong non determinisms in general purpose OSes. Top of the line cars already house more than 70 interconnected embedded control units (ECUs). The question is how to cope with this additional complexity. Will the next generation of cars house even more ECUs or will there be powerful general purpose ECUs executing more than one dedicated task to reduce the number of ECUs, as the growing number of ECUs is not adequately manageable any more? When looking towards the direction of using more powerful ECUs, the conflicting goals of general purpose OSes and real-time OSes arise again. Is it suitable to apply the paradigm of virtualization to realize this integration, still ensuring the requirements for both types of OSes? What virtualization paradigm is suitable for the domain of embedded real-time systems? How to guarantee realtime properties when applying virtualization to a real-time system with other real-time system or general purpose systems? All these questions need to be answered when thinking of virtualization as an upcoming paradigm for designing complex distributed embedded hard real-time systems.

### ZUSAMMENFASSUNG

Die zunehmende Komplexität und die Forderung nach Schnittstellen auf höchster Ebene bei eingebetteten harten Echtzeitsystemen führt zu gegensätzlichen Zielen bei der Entwicklung der unterliegenden Systemsoftware. Das Hinzufügen weiterer Funktionalität auf höchster Ebene gefährdet die typischen Eigenschaften eingebetteter harter Echtzeitsysteme. Auf der anderen Seite ist die Implementierung von Funktionalität zum Ausführen von Systemen unter harter Echtzeit in nicht echtzeitfähigen Betriebssystemen nicht möglich, da diese aufgrund ihrer vorhandenen Implementierung oft nicht deterministisches Verhalten aufweisen. Heutige Oberklassenfahrzeuge enthalten allerdings mittlerweile mehr als 70 eingebettete Steuereinheiten (ECUs). Es stellt sich also die Frage, wie man dieser zunehmenden Komplexität Herr wird. Werden aus diesem Grund zukünftige Fahrzeuge noch mehr ECUs enthalten oder werden leistungsfähigere ECUs die Funktionalitäten mehrere ECUs in sich vereinen, weil die wachsende Zahl von ECUs nicht mehr adäquat handhabbar ist. Blickt man in Richtung des Einsatzes leistungsfähigerer ECUs, so tauchen die Konflikte der Designziele von eingebetteten harten Echtzeitsystemen und Betriebssystemen mit Funktionalität auf höchster Ebene wieder auf. Denkt man an den Einsatz von Virtualisierung, ergeben sich daraus interessante Fragestellungen. Ist der Einsatz von Virtualisierung in der Lage, die widersprüchlichen Ziele in ein System zu integrieren, wobei die Anforderungen beider Systeme noch immer erhalten bleiben? Eine weitere Frage ist, welches Paradigma der Virtualisierung am besten für eingebettete Echtzeitsysteme geeignet ist. Sämtliche Fragen bedürfen einer Antwort, wenn Virtualisierung als mögliches Lösungsparadigma in Betracht gezogen wird, um dem Design komplexer verteilter eingebetteter harter Echtzeitsysteme Herr zu werden.

## Auf der Familie ruht die Kunst, die Wissenschaft, der menschliche Fortschritt, der Staat.

—Adalbert Stifter \*23.10.1805 - †28.01.1868

To my children, my wife, my parents and my parents in law.

### OWN PUBLICATIONS

- [BK09] Baldin, Daniel and Timo Kerstan: *Proteus, a hybrid virtualization platform for embedded systems*. In Rettberg, Achim and Franz Josef Rammig (editors): *Analysis, Architectures and Modelling of Embedded Systems*. IFIP WG 10.5, Springer-Verlag, September 2009.

- [GKo8] Groesbrink, Stefan and Timo Kerstan: Modular paging with dynamic tlb partitioning for embedded real-time systems. In SIES '08. Third International Symposium on Industrial Embedded Systems, La Grande Motte, France, 2008.

- [KBG10] Kerstan, Timo, Daniel Baldin, and Stefan Groesbrink: Full virtualization of real-time systems by temporal partitioning. In Petters, Stefan M. and Peter Zijlstra (editors): Proceedings of the 6th International Workshop on Operating Systems Platforms for Embedded Real-Time Applications, pages 24–32. ArtistDesign Network of Excellence on Embedded Systems Design, ArtistDesign Network of Excellence on Embedded Systems Design, July 2010. in conjunction with the 22nd Euromicro Intl Conference on Real-Time Systems Brussels, Belgium, July 7-9, 2010.

- [KBS09] Kerstan, Timo, Daniel Baldin und Gunnar Schomaker: Formale Bestimmung von Systemparametern zum transparenten Scheduling virtueller Maschinen unter Echtzeitbedingungen. In: Informatik aktuell (Tagungsband Echtzeit 2009). Fachausschuß Echtzeitsysteme der Gesellschaft für Informatik und der VDI/VDE-Gesellschaft Mess- und Automatisierungstechnik (GMA), Springer-Verlag, November 2009.

- [KDMK10] Klobedanz, Kay, Bertrand Defo, Wolfgang Müller, and Timo Kerstan: Distributed coordination of task migration for fault-tolerant flexray networks. In Proceedings of the fifth IEEE Symposium on Industrial Embedded Systems (SIES2010). IEEE, IEEE, July 2010.

- [KO10] Kerstan, Timo and Markus Oertel: Design of a realtime optimized emulation method. In Proceedings of

- *DATE 2010*, Dresden, March 2010. IEEE Computer Society, IEEE Computer Society Press.

- [RDJ<sup>+</sup>09] Rammig, Franz Josef, Michael Ditze, Peter Janacik, Tales Heimfarth, Timo Kerstan, Simon Oberthür, and Katharina Stahl: *Hardware-dependent Software Principles and Practice*, chapter Basic Concepts of Real Time Operating Systems, pages 15–45. Springer, January 2009.

- [SBTKS09] Samara, Sufyan, Fahad Bin Tariq, Timo Kerstan, and Katharina Stahl: Applications adaptable execution path for operating system services on a distributed reconfigurable system on chip. In Proceedings of International Conference on Embedded Software and Systems, 2009. ICESS '09, May 2009.

- [SHK<sup>+</sup>10] Schäfer, Wilhelm, Christian Henke, Lydia Kaiser, Timo Kerstan, Matthias Tichy, Jan Rieke und Tobias Eckardt: *Der Softwareentwurf im Entwicklungsprozess mechatronischer Systeme*. In: Gausemeier, Jürgen, Franz Josef Rammig, Wilhelm Schäfer und Ansgar Trächtler (Herausgeber): 7. *Paderborner Workshop Entwurf mechatronischer Systeme*. Heinz Nixdorf Institut, HNI Verlagsschriftenreihe, Paderborn, März 2010.

## CONTENTS

| 1 | Intro | oduction                                      | 1   |

|---|-------|-----------------------------------------------|-----|

|   | 1.1   | Purpose of the Thesis                         | 3   |

|   | 1.2   | Current Status                                | 4   |

|   | 1.3   | Structure of the Thesis                       | 4   |

| 2 | Virt  | ualizing Embedded Real-Time Systems           | 7   |

|   | 2.1   | Real-Time Systems                             | 13  |

|   |       | 2.1.1 Task Models                             | 15  |

|   |       | 2.1.2 Periodic task scheduling                | 16  |

|   | 2.2   | The Architecture of VMs                       | 21  |

|   |       | 2.2.1 System Virtual Machines                 | 24  |

|   |       | 2.2.2 Processor Virtualization                | 26  |

|   |       | 2.2.3 Memory Virtualization                   | 34  |

|   |       | 2.2.4 Multiple independent layers of security | 40  |

|   | 2.3   | Emulation                                     | 41  |

|   |       | 2.3.1 Interpretation                          | 41  |

|   |       | •                                             | 43  |

|   | 2.4   | Summary                                       | 47  |

| 3 | ΑV    | irtual Machine Monitor for Embedded Real-Time |     |

|   | Sys   | tems                                          | 49  |

|   | 3.1   | Problem Statement                             | 54  |

|   | 3.2   | Related Work                                  | 57  |

|   |       | 3.2.1 Academia                                | 57  |

|   |       | 3.2.2 Industry                                | 60  |

|   |       | 3.2.3 Summary                                 | 70  |

|   | 3.3   | Design                                        | 71  |

|   |       | 3.3.1 Configurability                         | 73  |

|   |       | 3.3.2 Architecture                            | 73  |

|   |       | 3.3.3 Processor Virtualization                | 82  |

|   |       | 3.3.4 Timer Virtualization                    | 86  |

|   |       | 3.3.5 Scheduler                               | 92  |

|   |       | 3.3.6 Memory Virtualization                   | 92  |

|   |       | 3.3.7 I/O Virtualization                      | 97  |

|   |       | 3.3.8 Summary                                 | 99  |

|   | 3.4   | Evaluation                                    | 100 |

|   |       | 3.4.1 PPC405 ISA Analysis                     | 100 |

|   |       | 3.4.2 Worst Case Execution Times              | 102 |

|   |       | 3.4.3 Virtualization overhead                 | 110 |

BIBLIOGRAPHY

|   |     | 3.4.4 Footprint                                    |     |

|---|-----|----------------------------------------------------|-----|

|   |     |                                                    | 114 |

|   | 3.5 | Summary                                            | 115 |

| 4 | Sch | eduling of full virtualized hard real-time systems | 119 |

|   | 4.1 | Problem Statement                                  | 120 |

|   | 4.2 | Related Work                                       | 121 |

|   |     | 4.2.1 Academia                                     | 122 |

|   |     | 4.2.2 Industry                                     | 131 |

|   |     | 4.2.3 Classification                               | 133 |

|   |     | 4.2.4 Summary                                      | 135 |

|   | 4.3 | Model                                              | 135 |

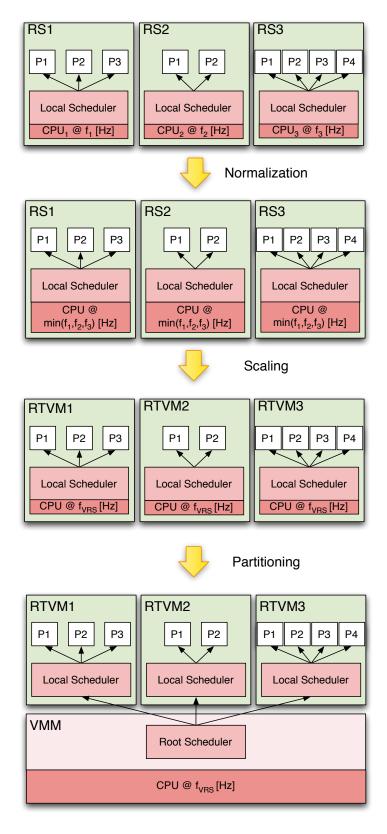

|   | 4.4 | Transformation of real-time systems into real-time |     |

|   |     | virtual machines                                   | 137 |

|   |     | 4.4.1 Normalization                                | 139 |

|   |     | 4.4.2 Scaling the virtual real-time system         | 140 |

|   |     | 4.4.3 Summary                                      | 142 |

|   | 4.5 | Partitioning Policy                                | 142 |

|   |     | 4.5.1 Activation slots                             | 143 |

|   |     | 4.5.2 Period of the static resource partitions     | 145 |

|   |     | 4.5.3 Schedule                                     | 149 |

|   |     | 4.5.4 Summary                                      | 153 |

|   | 4.6 | Evaluation                                         | 155 |

|   |     | 4.6.1 Algorithmic complexity                       | 156 |

|   |     | 4.6.2 Distribution of the GCD                      | 158 |

|   |     | 4.6.3 Experimental Setup                           | 159 |

|   |     | 4.6.4 Scheduling performance                       | 160 |

|   |     | 4.6.5 Context Switching                            | 164 |

|   |     | 4.6.6 Case Study                                   | 167 |

|   |     | 4.6.7 Summary                                      | 174 |

| 5 | Sur | nmary                                              | 177 |

|   |     | ,                                                  |     |

| A |     | luation                                            | 181 |

|   |     | Measurements                                       | 181 |

|   | A.2 | Scenario I: Electrical Drive Engineering - Linear  |     |

|   |     | Motor Control                                      | 185 |

|   | _   | Scenario II: Industrial - CNC Machine              | 186 |

|   | -   | Scenario III: Medical - X-ray Machine              | 187 |

|   | A.5 | Scenario IV: Automotive - Airbag Control and       |     |

|   |     | Driver Assistance                                  | 188 |

|   |     |                                                    |     |

189

# LIST OF FIGURES

| 1  | Operator Controller Module                               | 9  |

|----|----------------------------------------------------------|----|

| 2  | Use Cases for the application of virtualization to       |    |

|    | embedded systems[Heio8b]                                 | 11 |

| 3  | Classes of real-time systems. [Buto4]                    | 14 |

| 4  | Common parameters of real-time tasks [Buto4]             | 16 |

| 5  | Classes of real-time tasks [Buto4]                       | 17 |

| 6  | Example of timeline scheduling [Buto4]                   | 18 |

| 7  | Abstraction vs. Virtualization                           | 22 |

| 8  | Process and System VMs                                   | 23 |

| 9  | Different types of System VMs [SNo5b]                    | 24 |

| 10 | Virtual Machine Monitor Concept                          | 27 |

| 11 | Virtual Machine Map                                      | 32 |

| 12 | Memory Virtualization                                    | 35 |

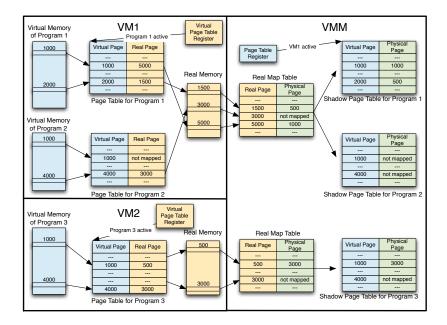

| 13 | Virtualizing architected page tables                     | 36 |

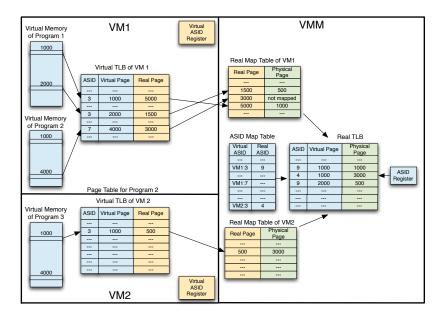

| 14 | Virtualizing architected TLBs                            | 38 |

| 15 | MILS architecture                                        | 39 |

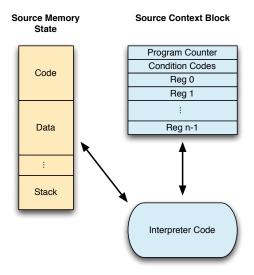

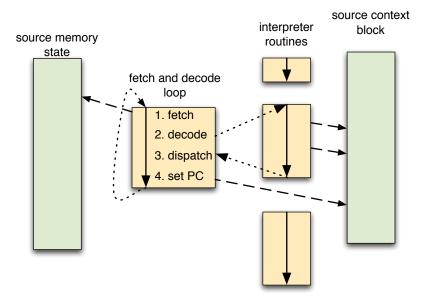

|    | Overview of an interpreter [SNo <sub>5</sub> b]          | 42 |

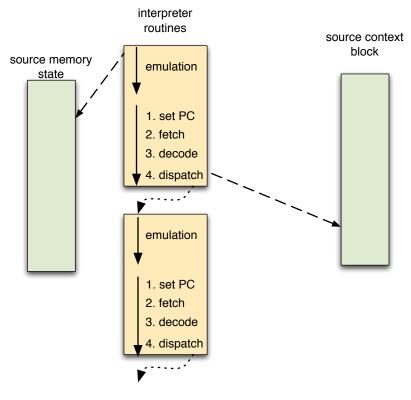

| 17 | Basic and threaded interpretation                        | 44 |

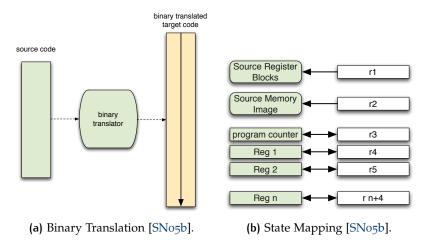

| 18 | Binary Translation                                       | 45 |

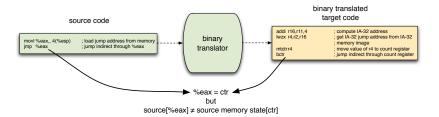

|    | Code Location Problem [SNo5b]                            | 45 |

|    | Code Discovery Problem                                   | 46 |

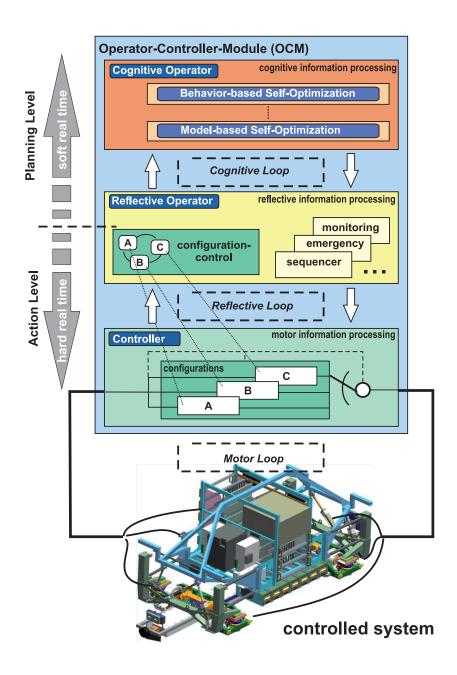

|    | Operator Controller Module                               | 50 |

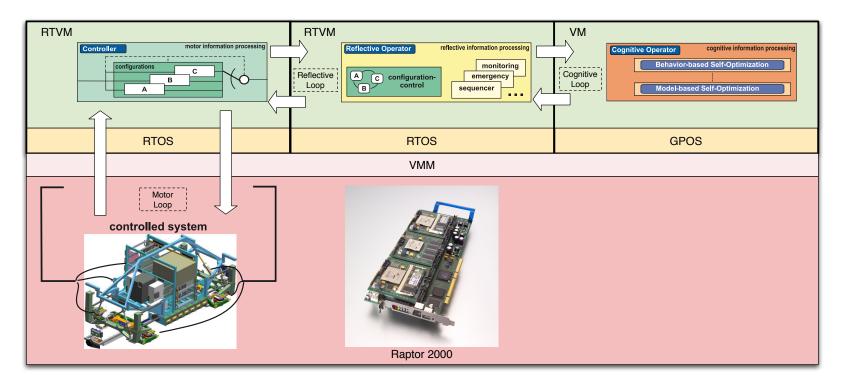

|    | OCM virtualized                                          | 53 |

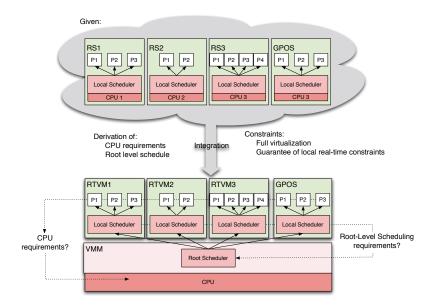

| 23 | Problem of integrating given real-time systems into an   |    |

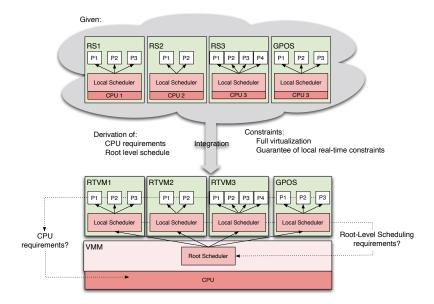

|    | virtual system hosting these real-time systems as RTVMs. | 55 |

| •  | Modular Page Tables                                      | 61 |

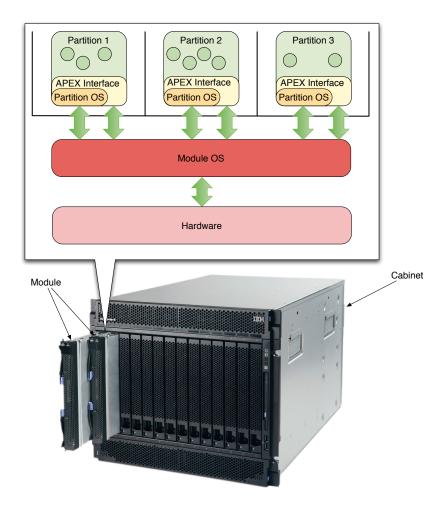

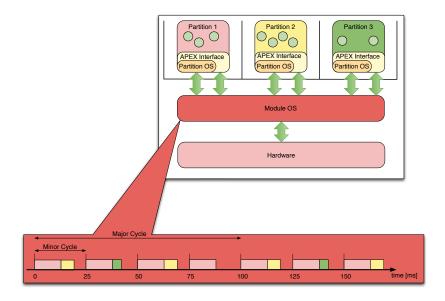

|    | Arinc653 architecture diagram                            | 63 |

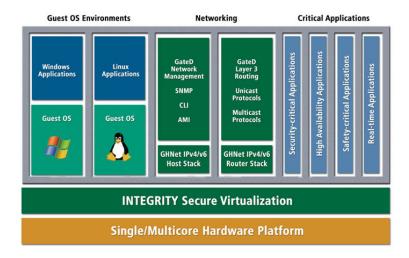

|    | Green Hills Secure Virtualization architecture diagram   | 64 |

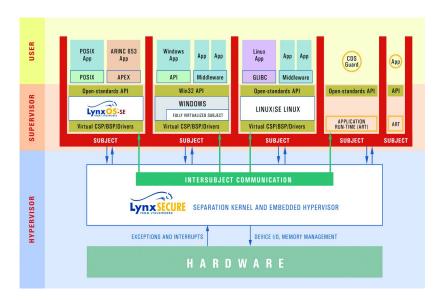

|    | Lynuxworks Lynxsecure architecture diagram               | 65 |

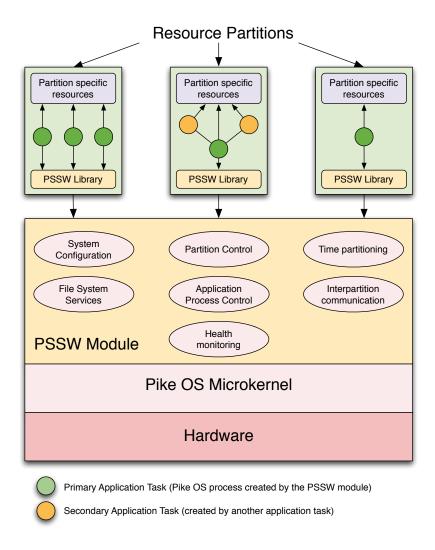

|    | PikeOS architecture diagram                              | 67 |

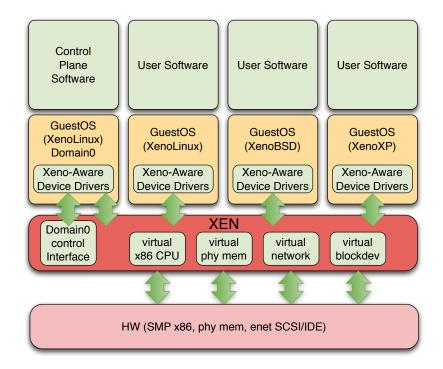

| _  | XEN Architecture                                         | 69 |

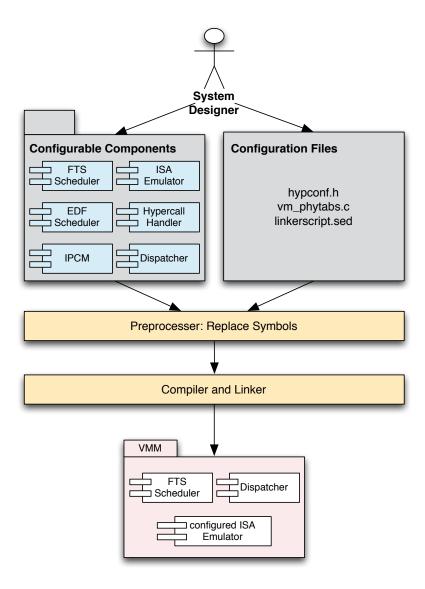

| 30 | Configuration flow of the virtualization platform        | 74 |

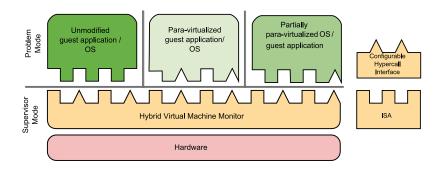

| 31 | The virtual machine monitor allows for the virtualized   |    |

|    | execution of any kind of guest application. Left: an     |    |

|    | unmodified application. Middle: a completely             |    |

|    | paravirtualized application. Right: a partially          |    |

|    | modified application                                     | 75 |

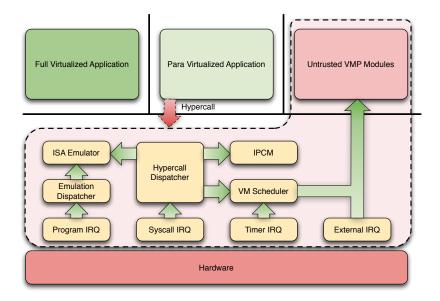

| 32 | Information and control flow of the components used          |     |

|----|--------------------------------------------------------------|-----|

|    | inside the virtualization platform                           | 76  |

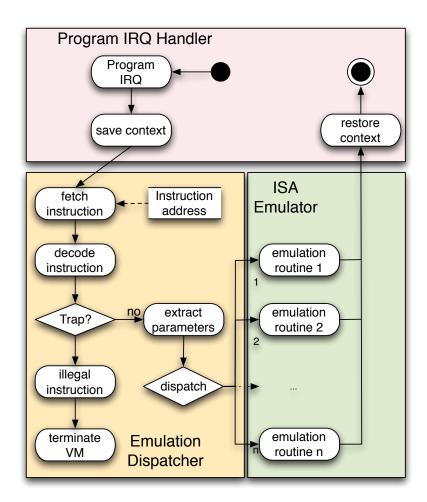

| 33 | Flow Chart of the Full Virtualization components             | 77  |

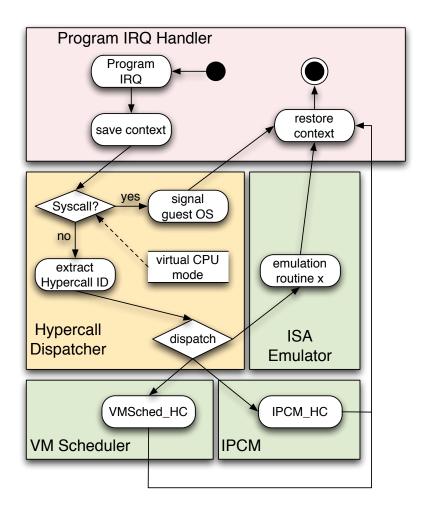

| 34 | Flow Chart of the Paravirtualization components              | 79  |

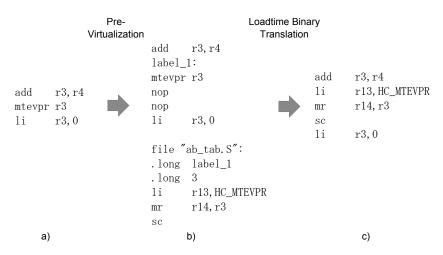

| 35 | Pre-Virtualization illustrated. a) Base source code. b)      |     |

|    | Pre-Virtualized source code and Pre-Virtualization           |     |

|    | table. c) The final paravirtualized code                     | 81  |

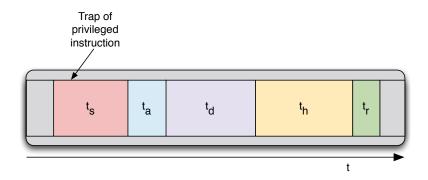

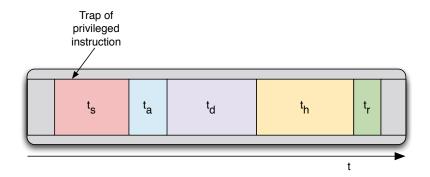

| 36 | Steps performed upon handling an IRQ [Balo9]                 | 83  |

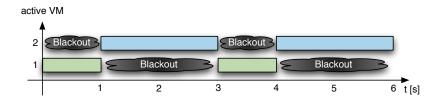

| 37 | When sharing the timer device, the VMs are suffering         |     |

|    | from blackouts during their phase of inactivity [Kaio8a].    | 85  |

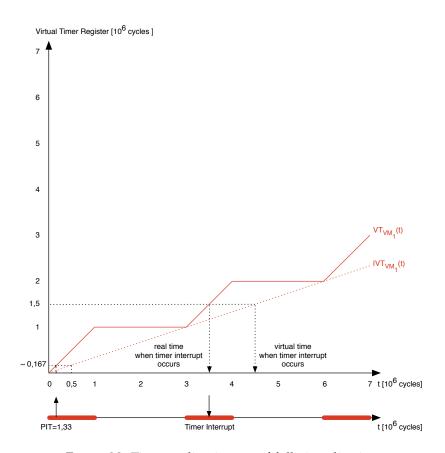

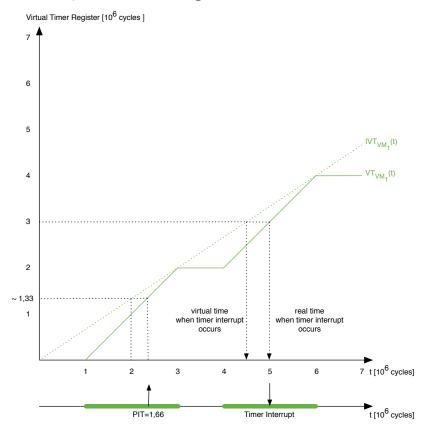

| 38 | Timer scaling in case of full virtualization                 | 87  |

| 39 | Timer scaling in case of full virtualization                 | 87  |

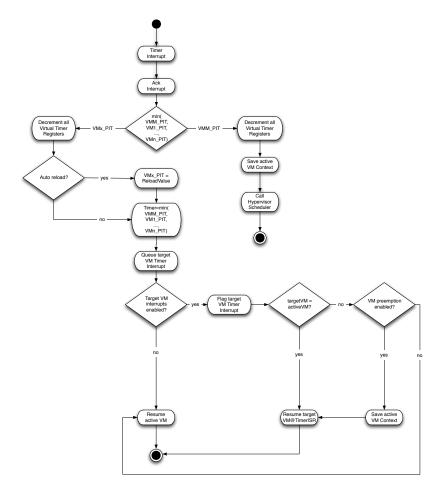

| 40 | Timer Virtualization Flow Chart                              | 91  |

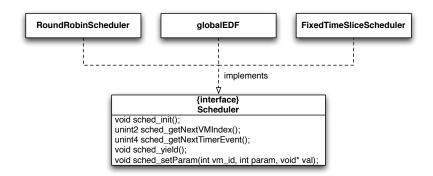

| 41 | Interface of the VMM Scheduler component [Balo9]             | 93  |

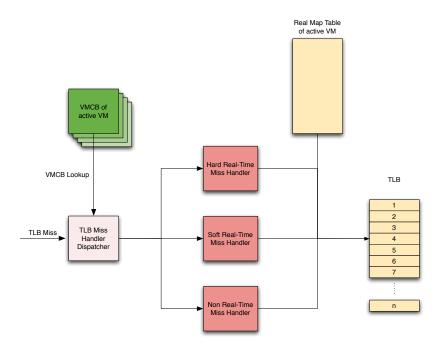

| 42 | Mixed Priority Paging with Dynamic TLB Partitioning .        | 94  |

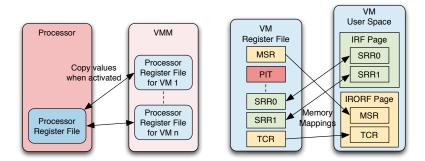

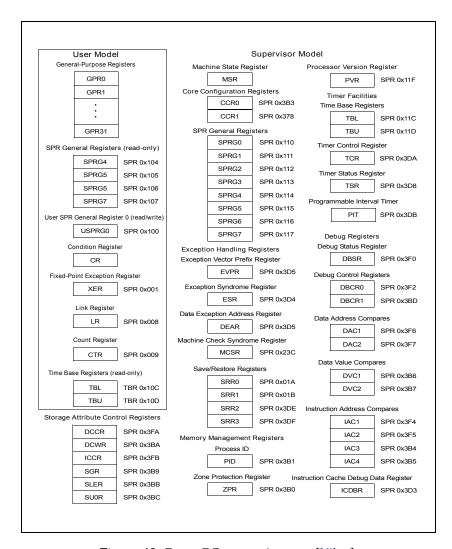

| 43 | PowerPC 405 register set [Xilo9]                             | 101 |

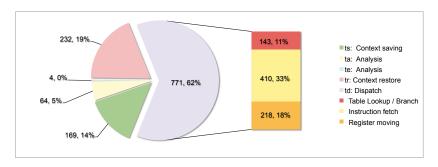

|    | Virtualization overhead                                      | 111 |

| 45 | Virtualization overhead of <i>mtevpr</i> in detail [Balo9]   | 111 |

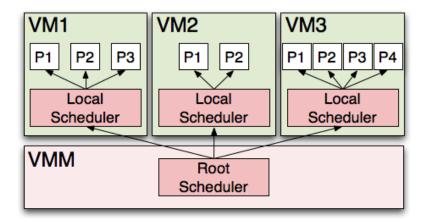

| 46 | Hierarchy of involved schedulers                             | 120 |

| 47 | Problem of integrating given real-time systems into an       |     |

|    | virtual system hosting these real-time systems as RTVMs.     | 121 |

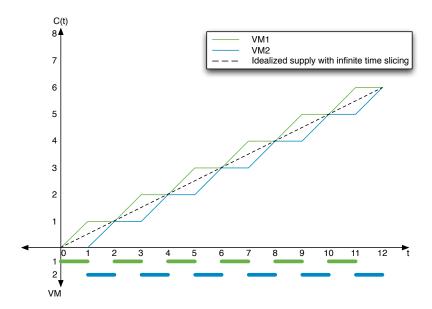

|    | VM supply function C(t) vs real time elapsed                 | 123 |

|    | Resource Partition Model                                     | 125 |

| -  | ARINC653 partition scheduling                                | 132 |

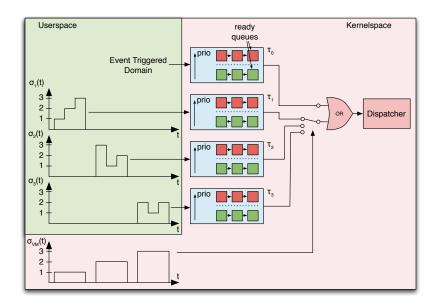

| 51 | PikeOS scheduling mechanism. The OR operator                 |     |

|    | realizes a preemptability of the time triggered              |     |

|    | partitions $\tau_i$ by the event triggered background        |     |

|    | partition $\tau_0$                                           | 133 |

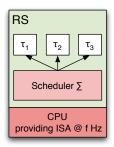

|    | Model of a real-time system                                  | 135 |

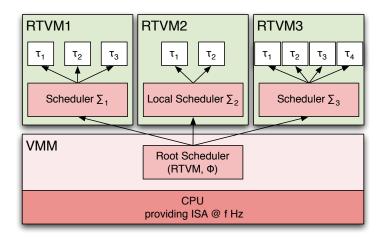

|    | Model of a virtual real-time system                          | 136 |

| 54 | Methodology to realize full virtualization of RTVMs          |     |

|    | by temporal partitioning                                     | 138 |

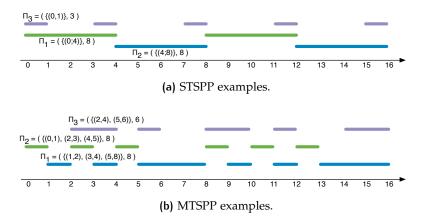

| 55 | Comparison of switching overhead of STSPPs and               |     |

|    | MTSPPs                                                       | 144 |

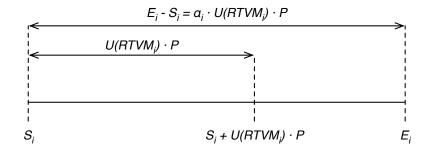

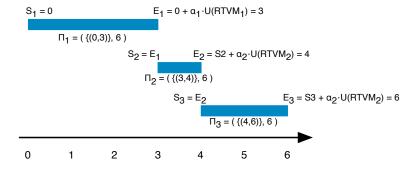

| 56 | Graphical illustration of the required computation           |     |

|    | time within the allocated interval $E_i - S_i$ of $\Pi_i$    | 145 |

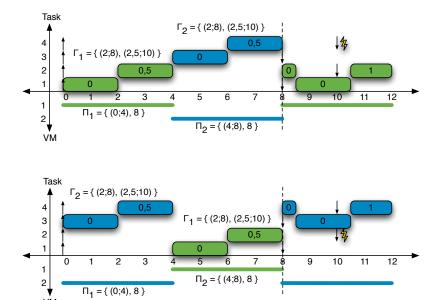

| 57 | Example for the choice of an incompatible period             |     |

|    | length for static resource partition                         | 146 |

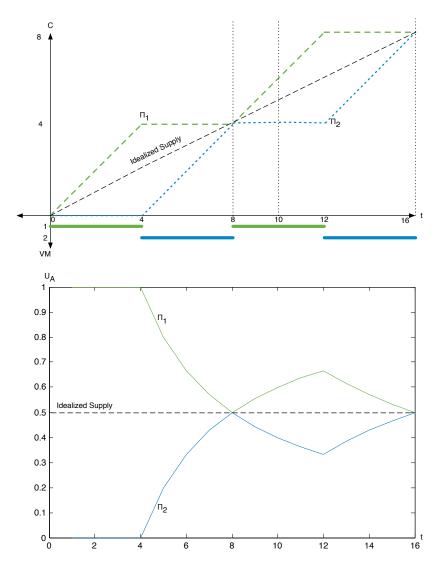

| 58 | Assigned computation time and utilization over the           |     |

|    | real time elapsed of schedule 1 of figure 57                 | 148 |

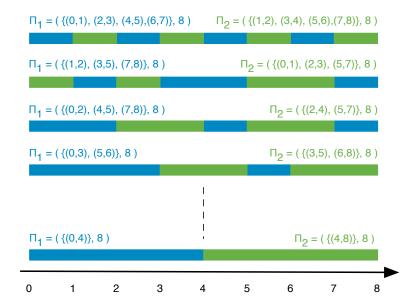

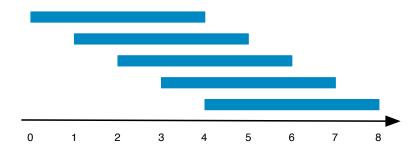

| 59 | Example for scheduling activation slots of a two             |     |

|    | periodic resource partitions $\Pi_1$ and $\Pi_2$ with period |     |

|    | $P_1 = P_2 = 8$ and $U_1 = U_2 = \frac{1}{2}$                | 149 |

|    | Example for placing the activation slots of a MTSPP          | 151 |

| 61 | Example for placing the activation slots of a STSPP          | 152 |

| 02                    | example for placing the activation slots of three                                                                                                |                                              |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|                       | STSPPs to ensure the schedulability of the whole system                                                                                          | 153                                          |

| 63                    | Example of a valid partitioned schedule with the                                                                                                 |                                              |

|                       | period being the GCD of all deadlines instead of                                                                                                 |                                              |

|                       | P = 8. The activation slots have been determined                                                                                                 |                                              |

|                       | according to equation 4.28                                                                                                                       | 154                                          |

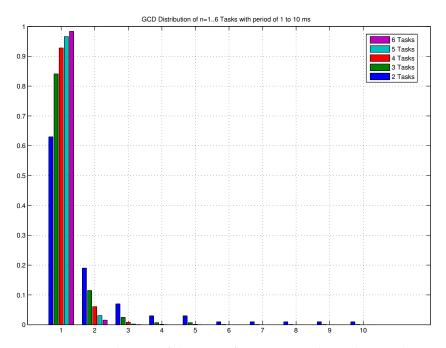

| 64                    | Distribution of the GCD for up to 6 tasks with periods                                                                                           |                                              |

|                       | up to 10ms                                                                                                                                       | 158                                          |

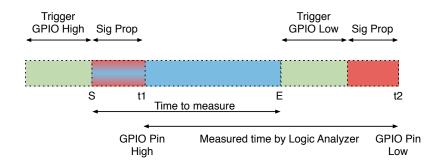

| 65                    | Possible measurement error due to signal propagating                                                                                             |                                              |

| _                     | time                                                                                                                                             | 159                                          |

| 66                    | Scaling behavior of sched_init. For measurement                                                                                                  |                                              |

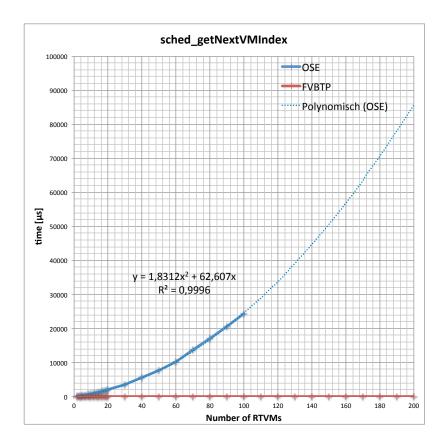

|                       | values see table 22, 23 and 26                                                                                                                   | 161                                          |

| 67                    | Scaling behavior of sched_getNextVMIndex                                                                                                         | 163                                          |

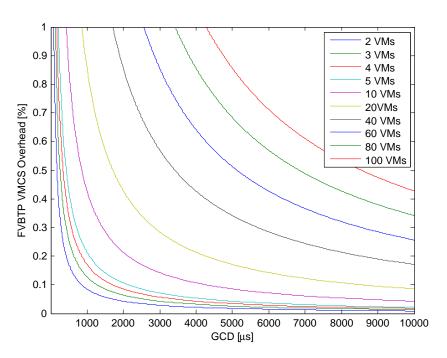

| _                     | VMCS overhead for periods from 1µs up to 10ms on                                                                                                 | 10)                                          |

| 00                    | PowerPC405 @ 300 MHz                                                                                                                             | 166                                          |

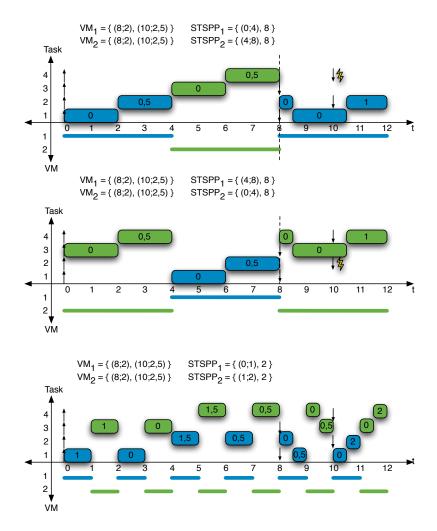

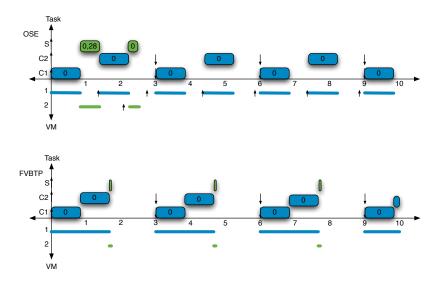

| 60                    | Schedules using OSE and FVBTP                                                                                                                    | 169                                          |

| 09                    | ochedules using Ool and I voll                                                                                                                   | 109                                          |

|                       |                                                                                                                                                  |                                              |

|                       |                                                                                                                                                  |                                              |

|                       |                                                                                                                                                  |                                              |

|                       | ST OF TABLES                                                                                                                                     |                                              |

| LI                    | ST OF TABLES                                                                                                                                     |                                              |

| LI                    | ST OF TABLES                                                                                                                                     | _                                            |

| LI                    | ST OF TABLES                                                                                                                                     |                                              |

|                       |                                                                                                                                                  |                                              |

| 1                     | Actions of the VMM on triggered page faults                                                                                                      | 36                                           |

| 1                     | Actions of the VMM on triggered page faults                                                                                                      | 36<br>39                                     |

| 1                     | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor      | 39                                           |

| 1<br>2<br>3           | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor mode |                                              |

| 1<br>2<br>3           | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor mode | 39                                           |

| 1<br>2<br>3           | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor mode | 39<br>103                                    |

| 1<br>2<br>3           | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor mode | 39                                           |

| 1<br>2<br>3           | Actions of the VMM on triggered page faults                                                                                                      | 39<br>103                                    |

| 1<br>2<br>3           | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor mode | 39<br>103                                    |

| 1<br>2<br>3           | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor mode | 39<br>103<br>106                             |

| 1<br>2<br>3           | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor mode | 39<br>103<br>106                             |

| 1<br>2<br>3<br>4      | Actions of the VMM on triggered page faults                                                                                                      | 39<br>103<br>106                             |

| 1<br>2<br>3<br>4      | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor mode | 39<br>103<br>106                             |

| 1<br>2<br>3<br>4      | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor mode | 39<br>103<br>106<br>107                      |

| 1<br>2<br>3<br>4      | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor mode | 39<br>103<br>106<br>107                      |

| 1<br>2<br>3<br>4      | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor mode | 39<br>103<br>106<br>107                      |

| 1<br>2<br>3<br>4      | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor mode | 39<br>103<br>106<br>107                      |

| 1<br>2<br>3<br>4<br>5 | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor mode | 39<br>103<br>106<br>107                      |

| 1<br>2<br>3<br>4      | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor mode | 39<br>103<br>106<br>107<br>108               |

| 1<br>2<br>3<br>4<br>5 | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor mode | 39<br>103<br>106<br>107<br>108<br>109<br>114 |

| 1<br>2<br>3<br>4      | Actions of the VMM on triggered page faults Actions of the VMM on triggered TLB misses Subset of PPC405FX registers available in supervisor mode | 39<br>103<br>106<br>107<br>108<br>109<br>114 |

| 10 | Comparison of the algorithmic complexity of the open   |     |

|----|--------------------------------------------------------|-----|

|    | system environment and FVBTP                           | 156 |

| 11 | Performance of scheduler interface routine             |     |

|    | sched_getNextTimerEvent [Grö10]                        | 162 |

| 12 | VMCS for Open System Environment for $n = 2$ . [Grö10] | 165 |

| 13 | VMCS Performance for FVBTP. [Grö10]                    | 166 |

| _  | Scenario IV: Electrical Drive Engineering - Linear     |     |

| •  | Motor Control. [Grö10]                                 | 168 |

| 15 | Electrical Drive Engineering Evaluation. [Grö10]       | 169 |

|    | Scenario I: Industrial - CNC Machine. [Grö10]          | 170 |

| 17 | Industrial - CNC Machine Evaluation. [Grö10]           |     |

| 18 | Scenario II: Medical - X-ray Machine. [Grö10]          |     |

| 19 | Medical Evaluation. [Grö10]                            | 172 |

| 20 | Scenario III: Automotive - Airbag Control and Driver   |     |

|    | Assistance. [Grö10]                                    | 173 |

| 21 | Automotive Scenario Evaluation. [Grö10]                | 174 |

| 22 | Performance of scheduler interface routine sched_init  |     |

|    | in case of FVBTP. [Grö10]                              | 181 |

| 23 | Performance of scheduler interface routine sched_init  |     |

|    | in case of FVBTP. [Grö10]                              | 182 |

| 24 | Performance of scheduler interface routine sched_init  |     |

|    | in case of OSE. [Grö10]                                | 183 |

| 25 | Performance of scheduler interface routine             |     |

|    | sched_getNextVMIndex in case of OSE. [Grö10]           | 184 |

| 26 | Performance of scheduler interface routine             |     |

|    | sched_getNextVMIndex in case of FVBTP. [Grö10]         | 184 |

### INTRODUCTION

### CONTENTS

- 1.1 Purpose of the Thesis 3

- 1.2 Current Status 4

- 1.3 Structure of the Thesis

Virtualization has been a key technology in the desktop and server market for a fairly long time. Numerous products offer hardware virtualization at the bare metal level or at the host level. They enable system administrators to consolidate whole server farms and end users to use different operating systems concurrently. In the case of server consolidation, virtualization helps to improve the utilization or load balance which facilitates a reduction of costs and energy consumption. Distributed embedded systems used in automotive and aeronautical systems consist of multitudinous microcontrollers, each executing a dedicated task to guarantee isolation and to prevent a fault from spreading over the whole network. In addition, the utilization of a single microcontroller may be very low. Applying virtualization to distributed embedded systems can help to increase the scalability while preserving the required isolation, safety, and reliability. It is not possible to apply the virtualization solutions for server and desktop systems one-to-one to embedded systems. The inherent timing constraints of embedded systems preclude this. These timing constraints add temporal isolation as a requirement to virtualized embedded real-time systems. Especially the classical approach of schedulability analysis [LL73] is no longer applicable to virtualized environments.

One of the main problems of building complex embedded systems is the integration of software components to a big integrated system. The automotive domain can be use as an example for a complex embedded system. When considering a top line

car, there are about 70 ECUs¹ installed with different tasks, from hard real-time tasks for actuating elements to soft real-time for multimedia devices to non real-time elements like the ECU for the window lifter. Those traditionally quit unrelated tasks start to interact in such complex embedded systems, and the problem of unintentional feature interaction becomes an extremely important issue to be handled safely as the verification of a complex integrated system is an extremely hard task. Thus, there is the trend to have much less ECUs in favor of more centralized multi-functional multipurpose hardware, less communication lines and less dedicated sensors and actuators. The trend towards more centralized multi-functional hardware boosts the problem of unintentional interaction of software components as they share the processor, memory and I/O devices in this case. Thus, the task of the system software is to prevent unintentional interactions which are not based on the communication between the components such as the domination of hardware resources like the processor or memory, faulty implementations allowing for buffer overflows, heap overflows, stack overflows, race conditions and so on, as these unintentional interactions endanger all components running on the same hardware. This is a typical task for system software and is normally covered by using virtual memory isolating the tasks from each other, but there is a new demand for high-level functionality in such complex embedded systems. Reconsidering the automotive domain, one can easily see that the modern multimedia, infotainment and other comfort functions require a lot of high-level APIs to like sophisticated GUI libraries. This is typically not a task of embedded RTOSs<sup>2</sup>. This is the point where virtualization can show its strength as virtualization allows to isolate the high-level tasks into a VM<sup>3</sup> together with a GPOS<sup>4</sup> providing all of the high-level functionality needed by the cognitive, while isolating the hard real-time tasks in RTVMs<sup>5</sup>, which are executing an RTOS. Thus, virtualization helps to simplify the integration process of compo-

<sup>1</sup> Electronic Control Unit (ECU) is a generic term for any embedded system that controls one or more of the electrical systems or subsystems in a motor vehicle.

<sup>2</sup> Real-Time Operating Systems (RTOS) are a class of operating systems being used in computing systems that must react within precise time constraints to events in the environment [Buto4]

<sup>3</sup> Virtual Machines (VMs) are containers that provide subsets of the underlying hardware to the guest operating systems executed in this container

<sup>4</sup> General Purpose Operating Systems (GPOSs) are the class of operating systems typically used on desktop computers

<sup>5</sup> Real-Time Virtual Machines

nents with different requirements to their operating systems as it allows to run multiple operating systems while spatially isolating them and preventing unintentional interactions like resource domination or attacks resulting from faulty implementations. A big advantage of virtualization against the use of a single operating system providing all functionality is that VMMs are by design very small and are easier to verify than a big operating system full of high-level functionality.

#### PURPOSE OF THE THESIS 1.1

The growing complexity of embedded real-time systems and their demand for high-level functionality typically provided by GPOSs like Linux, Windows and Mac OS X is the main motivation of this thesis. This growing complexity of distributed embedded real-time systems needs to be handled. Considering a top of the line car, one can observe that there are more than 70 ECUs used for the realization of safety and comfort functions. So will there be more ECUs used due to the growing complexity in future? Prof. Dr. Manfred Broy of the Technical University Munich, who is a leading scientist in the domain of software engineering, doubts this trend and formulated the following hypothesis:

"The car of the future will certainly have much less ECUs in favor of more centralized multi-functional multipurpose hardware, less communication lines and less dedicated sensors and actuators. Arriving today at more than 70 ECUs in a car, the further development will rather go back to a small number of ECUs by keeping only a few dedicated ECUs for highly critical functions and combining other functions into a small number of ECUs, which then would be rather not special purpose ECUs, but very close to general-purpose processors. Such a radically changed hardware would allow for quite different techniques and methodologies in software engineering." [Broo6]

The requirement for High-Level API functionality for comfort functions and hard real-time capabilities for safety functions is not addressed in state of the art real-time operating systems, as their focus is to be small and efficient while general purpose operating systems are not able to handle hard real-time loads, besides the demand for High-Level APIs. As both domains have different requirements virtualization is a promising approach for integrating both kinds of operating systems into a single virtualized system. The purpose of this thesis is to provide a virtualization environment being capable of handling multiple real-time guests together with multiple general purpose guests, while preventing the necessity of paravirtalization. The virtualization platform shall be able to support paravirtualization, but it shall not require it, as licensing restriction may eliminate the possibility of paravirtualizing a specific given operating system.

### 1.2 CURRENT STATUS

Up to the point in time where the work on this thesis started there, was no available virtualization platform providing the support for paravirtualization and full virtualization to address the problem of providing a hybrid virtualization interface being tailored to the applications needs. The trend towards virtualization has raised the interest of industry, and some products offering full virtualization for High-Level guests and paravirtualization for real-time guests have been released on the market in the meantime. Unfortunately, the support for multiple realtime VMs has been covered sparely in industry by restricting the execution of real-time virtual machines either to a dedicated cpu core or by restricting the number of real-time virtual machines to only one with an arbitrary number of non real-time virtual machines. Academia in contrast offers different hierarchical scheduling approaches especially suited for paravirtualization that allow for the presence of multiple real-time virtual machines, but there is also a lack of approaches using full virtualization.

### 1.3 STRUCTURE OF THE THESIS

To provide a general common understanding of the underlying real-time and virtualization techniques, chapter 2 will provide a short overview of basic real-time and virtualization terms and techniques. Chapter 3 will clearly define the problems being ad-

dressed in detail within this thesis. The problems being defined will be covered in chapter 3 and 4. The problem of providing a configurable hybrid virtualization interface will be covered in chapter 3, and an overview of the corresponding related work is given in the beginning of this chapter. Afterwards, the design of such a virtualization platform is presented and evaluated. In addition, the worst case execution times are determined in order to provide the possibility to determine the deterministic overhead induced by the virtualization. Finally, chapter 4 covers the problem of deriving the cpu requirements and feasible schedule of given real-time virtual machines in order to guarantee their execution in a full virtualized environment to eliminate the necessity of paravirtualization. Therefore, the related work relevant for this topic is presented in the beginning of this chapter, before these problems are modeled and a solution is presented. The final step of the thesis is an evaluation based on a real execution on a PowerPC hardware platform. Within this evaluation, the approach presented in this thesis will be compared to the state of the art approach and a final resume on the evaluation is given. To complete this thesis, a final conclusion is given summing up the reached goals and discussing the possible future work.

# VIRTUALIZING EMBEDDED REAL-TIME SYSTEMS

### CONTENTS

2.1 Real-Time Systems 13

2.2 The Architecture of VMs 21

2.3 Emulation 41

2.4 Summary 47

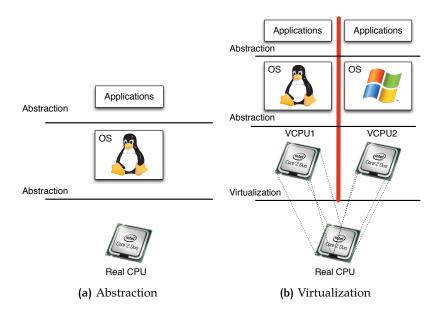

Today's computer systems are extremely complex and are designed as hierarchies with well-defined interfaces that separate levels of abstraction. This allows the independent development of subsystems by hardware and software design teams. Low-level implementation details are hidden by the simplifying abstractions. In contrast to abstraction, virtualization does not necessarily hide or simplify details. Instead, virtualization provides different resources at the same abstraction level. A simple example is providing two virtual network adapters while having only one physically available.

System virtualization has become a key technology in the enterprise and personal computing spaces and is recently gaining significant interest in the domain of embedded systems [Heio8b, Heio7]. After introducing the key characteristics of enterprise and embedded systems, the difference in motivation for the use of virtualization and the resulting differences in requirements will be presented. These requirements will be used to identify the flaws of current virtualization technologies in the context of embedded hard real-time systems under the assumption that the software of the embedded systems is not modified to support virtualization as this may be prohibited by licensing restrictions.

When looking at modern data centers today, virtualization is a hot topic. The decoupling of physical and virtual execution platforms by System VMs enables a variety of aspects which are of importance for enterprise data centers.

- Service consolidation: Services being executed on single machines can be integrated into a single virtualized system using system virtualization to reach a better utilization of the system.

- Load balancing: Through the decoupling of physical and virtual execution platform, it is possible to migrate VMs between different virtualization hosts depending on their load.

- Heterogeneity: The use of System VMs enables the execution of different operating systems (OSs) on a single machine. This is mostly relevant for personal desktops.

- Power management: This is closely related to load balancing, but with the optimization goal to minimize the power consumption of the data center.

- Spatial Isolation: The criticality of services may differ extremely, so in general it is necessary to isolate services from the rest of the system not allowing them to compromise the whole system when they are compromised or fail.

The main characteristic of these aspects is the fact that the VMs execute GPOSs, providing roughly the same kind of of capabilities and similar abstraction levels. Another characteristic of those scenarios is that VM communication is closely related to the communication of physical machines using network interfaces [Heio7, Heio8b, SNo5a, SNo5b].

The characteristics of embedded systems have changed dramatically over the last two decades. Especially the complexity of embedded systems has increased tremendously. They changed from relatively simple single purpose devices to extremely complex distributed systems with millions lines of code (Mloc). Top of the line cars consist of approximately 70 embedded control units (ECUs) and gigabytes of software. A funny rumor is that it takes longer to download the software than building the vehicle physically.

When taking a look at modern smart phones like the Apple iPhone, a new characteristic of modern embedded systems can be noticed. Increasingly, embedded systems run applications originally developed for GPOSs like Linux, Windows and Mac OS

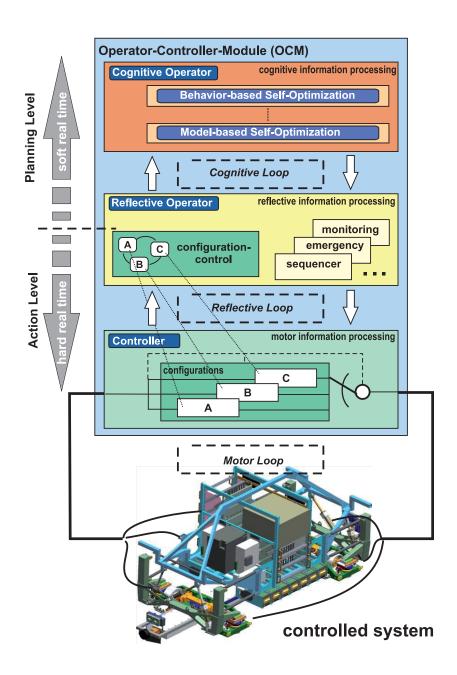

Figure 1: Operator Controller Module

X. There is also a trend that programers develop programs for embedded system platforms without any experience in this area. Furthermore there is a strong trend towards openness. The owners of a device want to load their own applications on the embedded systems and run them there. To enable such an openness, it is necessary to provide an open API introducing all the security challenges known from GPOSs. However, embedded systems are still subject to real-time and resource constraints. In addition they are often used in safety critical mechatronical systems like planes, cars and trains leading to very high requirements on safety, reliability and security. The OCM¹ structure (depicted in figure 1) of the CRC 614² is an example for such a safety critical system where the concurrent demands of safety critical systems and the need of High-Level APIs exist. [Buto6, Heio7, Heio8b]. The OCM is divided into 3 layers:

- Controller: A closed loop system that controls the sensors and actuators of the mechatronical system. The sensing, calculation of the control signals and the output of the control signal need to be performed in hard real-time.

- 2. Reflective operator: A monitoring and controlling layer above the controller. It has no direct access to the hardware, but modifies the controller by parameter or structure modifications. Typically, the reflective operator is time-critical in terms of soft real-time, but it may also operate in hard real-time.

- 3. Cognitive operator: The top layer of the OCM is responsible for using the information of the reflective operator as input for its cognition to perform self-optimization of the whole mechatronical system. This is realized by using a diversity of methods like machine learning, model based optimization or knowledge based systems. The application of these methods demand the use of High-Level APIs implementing those methods. The cognitive operator is not time critical and thus does not need to be executed under real-time constraints. Furthermore the programers at this layer do not need necessarily the knowledge of programing embedded systems.

<sup>1</sup> Operator Controller Module

<sup>2</sup> Collaborative Research Center for Self-Optimizing Mechatronical Systems

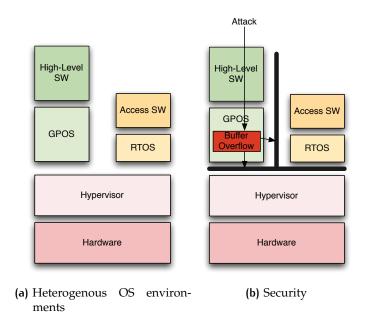

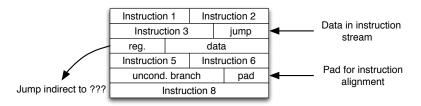

Figure 2: Use Cases for the application of virtualization to embedded systems[Heio8b]

The new trend for GPOS properties and the demands of complex embedded real-time systems like the self-optimizing mechatronical systems developed within the CRC 614 make virtualization a very promising technique in this area, as virtualization provides the following interesting aspects:

- Heterogeneity: The use of System VMs enables the execution of different operating systems (OSs) on a single embedded system, as depicted in figure 2a to address the conflicting requirements of high-level APIs, real-time support and legacy support.

- Spatial isolation: When building heterogenous OS environments on a single embedded system it is of indispensable importance to spatially isolate the different OSs from each other in a manner that it is not possible for a fault or an attack to spread to the other systems as depicted in figure 2b. Spatial isolation is typically realized by assigning different virtual address spaces to the different VMs. Virtualization fulfills this requirement and therefore increases the security and dependability significantly.

- Architectural abstraction: The decoupling of physical and virtual execution platform enables the possibility to abstract from the instruction set architecture (ISA). This results in the possibility to migrate VMs unchanged to hosts with the same ISA and to hosts with a different ISA using emulation. The same ISA migration covers especially the case of distributing VMs on multiple processor systems on chip (MPSoC) which are also an upcoming trend in embedded systems.

- Legacy software support: In contrast to personal desktops and enterprise systems, embedded systems are built on a broad diversity of different μCs<sup>3</sup>. This diversity implies the existence of different ISAs which makes it necessary to port embedded system software to run on a different ISA when changing the  $\mu$ C of an embedded system. This becomes problematic if the source code of this software is not available or accessible due to licensing restrictions. The advantage of virtualization now comes into play as virtualization allows the usage of emulation techniques to make this software run on a non supported ISA.

- Service consolidation: Services being executed on single ECUs can be integrated into a single virtualized system using system virtualization to lower the complexity of large distributed embedded systems.

These aspects are closely related to the aspects of enterprise system virtualization. However, the inherent timing requirements of embedded systems makes the application of existing virtualization techniques difficult as they have been developed for enterprise system architectures. Temporal isolation is an essential requirement of RTVMs. This means they must not be interfered by other VMs to respect their own timing behavior. Specifically, there is a temporal isolation among VMs whenever the ability for a VM to respect its own timing constraints (e.g. terminating a computation within a specified time, a.k.a. deadline) does not depend on the temporal behavior of other unrelated VMs running on the same system, thus sharing with it a set of resources (e.g. the CPU or such devices as disk, network, etc...). Understanding the issues of temporal isolation requires a fundamental understanding of real-time systems and their parameters. Sec-

<sup>3</sup> micro controllers

tion 2.1 clarifies the common notations and algorithms used for preserving the timing requirements of real-time systems.

The next essential requirement for virtualizing embedded realtime systems is the architecture of VMs enabling the spatial isolation being introduced in section 2.2. Especially the architecture of the software controlling virtual machine is addressed in this section. Besides the architecture of the VMs a brief introduction on common implementation methods for processor virtualization and memory virtualization will be given to show the issues of implementing VMs on a specific hardware.

#### **REAL-TIME SYSTEMS** 2.1

In the introduction of this chapter, the term "real-time" was already used without clearly defining it. Most people think of real-time systems being extremely fast and performing without any noticeable lags. This understanding of real-time systems does not conform to the definition of real-time systems given by Kopetz:

**Definition 2.1.** A real-time Computer system is a computer system in which the correctness of the system behavior depends not only on the logical results of the computation, but also on the physical instant at which these results are produced.

The definition implies that the value of a logical result depends on the time it is produced. Thus, a real-time operating system (RTOS) needs to be able to manage tasks with timing constraints. In addition, the RTOS may need to ensure the timing constraints of a task in the peak load (worst-case) situation. When this property is of indispensable importance, the real-time system needs to be entirely predictable to be able to determine the worst-case situation. Thus, a real-time system does not only need to be fast to fulfill the timing requirements, it especially has to be predictable to be able to determine whether it is possible to fulfill the timing constraints even in the worst-case situation. In a nutshell, a real-time system has to fulfill these properties:

### Timeliness

- OS has to provide kernel mechanisms for time management

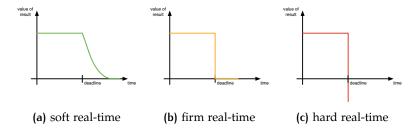

Figure 3: Classes of real-time systems. [Buto4]

- handling tasks with explicit time constraints

- Design for peak load

- Predictability

The value of the logical result in real-time decreases at the time the deadline is reached. Imagine a video decoder who has to decode the video frames in time to guarantee lag free video display. When the video decoder exceeds the deadline, the result is not completely useless. The decoded frame can still be displayed when the deadline is exceeded within a pre-defined time interval to prevent the frame from being dropped. This leads to video jitter, but the video may still be viewed at an acceptable quality. This application is an example for the class of soft real-time systems where the value of the computed result decreases smoothly after the deadline is exceeded (see figure 3a). The second class of real-time systems is called firm real-time systems. In a firm realtime system, the value of the computed result is zero when the deadline is exceeded (see figure 3b). Examples for such a systems are decision support and value prediction systems such as stock exchange systems and weather forecast systems. The third and final class of real-time systems is called hard real-time systems. In hard real-time systems, the value of the computed result is negative when the deadline is exceeded (see figure 3b), because missing the deadline causes catastrophic damage to the controlled system. Consider an ABS4 in a vehicle where the realtime task misses to compute the force control value of the brakes. Typical hard real-time activities are sensory data acquisition, actuator servoing and low-level control of critical system components. [Buto4]

<sup>4</sup> Anti Lock-Braking System

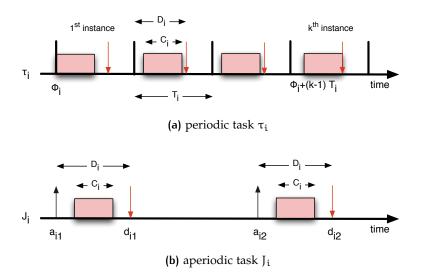

### Task Models

Real-time systems in general execute a set of so called real-time tasks under the constraint of fulfilling the time constraint of each real-time task. Tasks within a real-time system are characterized by computational activities within stringent timing constraints that must be met in order to achieve the desired behavior. A typical timing constraint on a task is the deadline. If a deadline is specified with respect to the arrival time, it is called a relative deadline, whereas if it is specified with respect to time zero, it is called an absolute deadline.

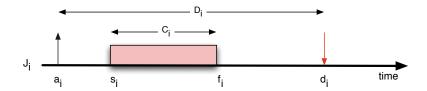

In general, a real-time task can be characterized by the following parameters (see figure 4 for a graphical description):

- Arrival time a<sub>i</sub>: is the time at which a task becomes ready for execution; it is also referred to as request time (or release time) and indicated by ri;

- Computation time C<sub>i</sub>: is the time necessary to the processor for executing the task without interruption;

- Absolute deadline d<sub>i</sub>: is the time before which a task should be completed to avoid damage (if hard) or performance degradation (if soft);

- Relative deadline D<sub>i</sub>: is the difference between the absolute deadline and the arrival time:  $D_i = d_i - r_i$ ;

- Start time s<sub>i</sub>: is the time at which a task starts activation;

- Finishing time f<sub>i</sub>: is the time at which the task finishes its execution;

- Response time R<sub>i</sub>: is the difference between finishing time and the arrival time:  $R_i = f_i - a_i$ ;

- Criticality: is a parameter related to the consequences of missing the deadline (typically, it can be hard or soft);

- Value  $v_i$ : represents the relative importance of the task with respect to other tasks in the system;

- Lateness  $L_i$ :  $L_i = f_i d_i$  represents the delay of a task completion with respect to its deadline;

- Tardiness or *Exceeding Time*  $E_i$ :  $E_i = max(0, L_i)$  is the time a task stays active after its deadline;

Figure 4: Common parameters of real-time tasks [Buto4].

• Laxity or *Slack time*  $X_i$ :  $X_i = d_i - a_i - C_i$  is the maximum time frame a task can be delayed on its activation to complete within its deadline;

In real-time systems there are different classes of real-time tasks, namely *periodic tasks* (see figure 5a), *aperiodic tasks* (see figure 5b) and *sporadic tasks*. The exact definition of these classes is now given to clearly distinguish them from each other:

**Definition 2.2.** A periodic task  $\tau_i$  has an infinite sequence of identical activities, called instances or jobs, and is regularly activated at a constant rate. The activation time of the first periodic instance is called phase  $\varphi_i$ . If  $\varphi_i$  is the phase of the periodic task  $\tau_i$ , the activation time of the k-th instance instance is given by  $\varphi_i + (k-1) \cdot T_i$ , where  $T_i$  is called period of the task. [But04]

**Definition 2.3.** An aperiodic task  $J_i$  has an infinite sequence of identical activities, called instances or jobs, and is not regularly activated at a constant rate [Buto4].

**Definition 2.4.** A sporadic task is an aperiodic task where consecutive jobs are seperated by a minimum interarrival time [Buto4].

### 2.1.2 Periodic task scheduling

In many real-time control applications, like the controller module of the OCM described in the introduction of this chapter (see 2), periodic activities represent the major computational demand in the system. When a control application consists of n concurrent periodic tasks, building the taskset

$$\Gamma = \{\tau_{i}(\Phi_{i}, T_{i}, C_{i}) | i = 1...n\}$$

(2.1)

with  $\tau_{i,j}$  being the j-th instance of task  $\tau_i$ , and  $\alpha_{i,j}$  or  $r_{i,j}$  being the release time of the j-th instance of task  $\tau_i$ , the operating

Figure 5: Classes of real-time tasks [Buto4].

system has to guarantee that each periodic instance is regularly activated at its proper rate and is completed within its deadline. Therefore, a brief introduction to timeline scheduling (TS) also known as cyclic scheduling (CS) or synchronous time division multiple access (TDMA), rate monotonic priority assignment (RM) and earliest deadline first scheduling policies are now given under the assumption of an independent taskset  $\Gamma$ and tasks  $\tau_i$  having relative deadlines  $D_i$  equal to their period T<sub>i</sub>.

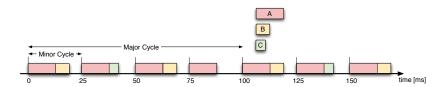

### Timeline scheduling

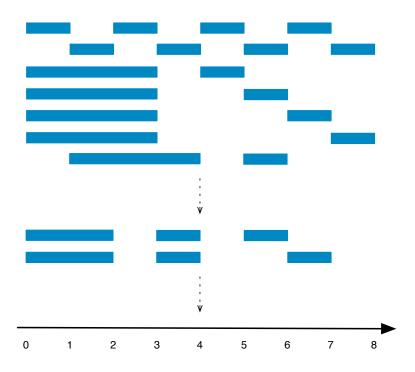

The main idea of timeline scheduling consists in dividing the temporal axis into slices of equal length in which one or more tasks can be allocated offline for execution, in such a way to respect the frequencies derived from application requirements. Figure 6 illustrates the timeline scheduling method for a taskset A, B and C with periods  $T_A = 25 \text{ms}$ ,  $T_B = 50 \text{ms}$  and  $T_C = 10 \text{ms}$ 100ms. To meet the required periods, the GCD<sup>5</sup> of the periods can be used to determine the time slice length which is also called *minor cycle*. The minimum period after which the schedule repeats itself is called a major cycle or hyperperiod being in general equal to the least common multiplier (LCM) of the tasks periods. In the example shown in figure 6, the minor cycle is 25ms and

<sup>5</sup> Greatest Common Divisor

Figure 6: Example of timeline scheduling [Buto4].

the major cycle is 100ms. Task A needs to be executed every minor cycle while Task B needs to be executed every two minor cycles and Task C needs to be executed every four minor cycles. A possible schedule is also depicted in figure 6.

Timeline scheduling is a very simplistic approach which can be easily implemented by programming a timer interrupt with a period equal to the minor cycle. Another advantage is that the tasks are not affected by jitter, because task start and response times are not subject to large variations. Nevertheless, timeline scheduling has some more drawbacks besides being an offline approach. Overhead condition handling is very problematic, because if a task does not terminate in time, it can either be aborted, leaving the system in an inconsistent state, or if the failing tasks continues execution, it can cause a domino effect on the other tasks, breaking the entire scheduler.

The timeline scheduling approach is similar to the *Time Division Multiple Access* multiplexing used in communications engineering.

## Rate Monotonic Scheduling

The RM<sup>6</sup> scheduling algorithm, or more precisely the rate monotonic fixed priority assignment algorithm, is a simple algorithm assigning priorities to real-time tasks proportional to their execution rates or equivalently anti-proportional to their period T. Thus, tasks with a higher rate (shorter period) will receive higher priorities. As periods are not subject to change at runtime, RM is a fixed priority scheduling algorithm where priorities are assigned offline to all tasks. The scheduling itself is priority-based and intrinsically preemptive.

In 1973, Liu and Layland showed in [LL73] that RM is optimal among all fixed-priority assignments, in the sense that there is

<sup>6</sup> Rate Monotonic

no other fixed priority algorithm that can schedule a taskset that cannot be scheduled by RM. Furthermore the least upper bound based on the processor utilization factor has been derived to test whether a taskset is schedulable by RM or not.

**Definition 2.5.** The processor utilization factor U is the fraction of processor time spent on executing the tasks of a given taskset  $\Gamma$ . The time spent within a task  $\tau_i$  is  $\frac{C_i}{T_i}$ . Thus the utilization factor U for ntasks is given by:

$$U = \sum_{i=0}^{n} \frac{C_i}{T_i}$$

To decide whether a real-time taskset  $\Gamma$  is being schedulable by an arbitrary scheduling algorithm A, it has to be checked whether the processor utilization U is less or equal than the upper bound  $U_{ub}(\Gamma, A)$ , which depends on the taskset and the applied scheduling algorithm. In the case  $U = U_{ub}(\Gamma, A)$  the processor is said to be fully utilized. To eliminate the dependency on the specific taskset to decide whether a taskset is schedulable by a scheduling algorithm A, the minimum of all upper bounds can be used as simplified schedulability check for a given taskset Γ. The minimum of all upper bounds is called *least upper bound* U<sub>lub</sub>:

$$U_{lub}(A) = \min_{\Gamma}(U_{ub}(\Gamma, A)) \tag{2.2}$$

In the case of RM, the least upper bound  $U_{lub}(n)^7$  of a taskset with n tasks can be calculated as:

$$U_{lub}(n) = n \cdot (2^{\frac{1}{n}} - 1)$$

(2.3)

$$\lim_{n\to\infty} U_{lub}(n) = ln(2) \approx 0.69 = U_{lub}(RM)$$

(2.4)

**Theorem 2.1.** Let  $\Gamma$  be an arbitrary set of periodic tasks with a processor utilization factor of  $U(\Gamma)$ . Then  $\Gamma$  is schedulable by RM if

$$U(\Gamma) \leq U_{lub}(RM)$$

.

<sup>7</sup> The derivation of  $U_{lub}(n)$  can be found in [LL73] or [But04]

**Theorem 2.2.** Let  $\Gamma$  be an arbitrary set of n periodic tasks with a processor utilization factor of  $U(\Gamma)$ . Then  $\Gamma$  is schedulable by RM if

$$U(\Gamma) \leqslant n \cdot (2^{\frac{1}{n}} - 1).$$

Another approach in the same complexity class of O(n) is the hyperbolic bound introduced by Bini et. al in [BBo1]. The hyperbolic bound is less pessimistic than the original Liu and Layland bound.

**Theorem 2.3.** Let  $\Gamma$  be an arbitrary set of  $\mathfrak n$  periodic tasks. Then  $\Gamma$  is schedulable by RM if

$$\prod_{i=1}^{n} \left(\frac{C_i}{T_i} + 1\right) \leqslant 2.$$

All these schedulability tests presented up to now are sufficient tests. Audsley et. al presented in [Aud91] a sufficient and necessary schedulability test with complexity  $O(\mathfrak{n}^2)$ . This test is called *Response Time Analysis*. As the name implies, the test determines for every task the response time at the critical instant as the sum of its computation and the interference due to preemption by higher priority tasks.

**Theorem 2.4.** Let  $\Gamma$  be an arbitrary set of  $\mathfrak n$  periodic tasks. Then  $\Gamma$  is schedulable by RM if and only if

$$\begin{split} \forall R_i \leqslant D_i: \\ \textit{with } R_i &= C_i + I_i, \\ \textit{where } I_i &= \sum_{j=1}^{i-1} \lceil \frac{R_j}{T_j} \rceil \cdot C_j \end{split}$$

As this is a recurrent equation, no simple solution exists. Thus, the test has to be performed by iteratively checking the equation for every task of the taskset  $\Gamma$ . The floor expression within the equation ensures the termination of the iteration when checking against the deadline of each task, as there is no asymptotic behavior.

### Earliest Deadline First Scheduling

In contrast to RM, the EDF<sup>8</sup> scheduling algorithm is a dynamic scheduling algorithm that selects the next task to execute according to the absolute deadlines. Thus, tasks with earlier absolute deadlines have higher priorities and as the absolute deadline of a periodic tasks depends on the current instance the priorities of the periodic task change during execution. As RM, EDF is intrinsically preemptive, as it preempts the current running task when a task arrives with a shorter absolute deadline. EDF is not only able to handle periodic tasks, but also aperiodic tasks and is optimal in minimizing the maximum lateness on a given taskset.

To check whether a given taskset is schedulable by EDF the processor utilization factor introduced in definition 2.5 is used to check it against the least upper bound of EDF. Fortunately, the least upper bound of EDF is one, enabling a very simple schedulability test and allowing tasks to fully utilize the processor up to 100%.

**Theorem 2.5.** Let  $\Gamma$  be an arbitrary set of periodic tasks, then  $\Gamma$  is schedulable by EDF if and only if

$$U(\Gamma) = \sum_{i=1}^{n} \frac{C_i}{T_i} \leqslant 1.$$

Buto<sub>4</sub>

### THE ARCHITECTURE OF VMS 2.2

Today's computer systems are extremely complex and are designed as hierarchies with well-defined interfaces that separate levels of abstraction. This allows the independent development of subsystems by hardware and software design teams. In addition low-level implementation details are hidden by the simplifying abstractions. In contrast to abstraction, virtualization does not necessarily hide or simplify details. This is depicted in figure 7. Figure 7a shows that the operating system is an abstraction of the hardware, in this case the CPU, and provides a simplified interface (Processes) to access the CPU, while figure 7b shows

<sup>8</sup> Earliest Deadline First

Figure 7: Abstraction vs. Virtualization

that virtualization provides different resources, in this case two virtual CPUs, at the same abstraction level.

Virtualization can be applied at different interface levels of a computer system architecture. The Instruction Set Architecture (ISA) is the interface between soft- and hardware and is divided into user and system instructions. The system instructions are privileged instructions that are only accessible by software running in system mode to prevent user mode software from unauthorized access to the hardware.

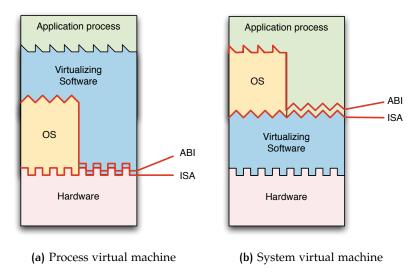

A process virtual machine is executed in general on top of the OS and provides a uniform view to application processes independent of the underlying OS and hardware. A good example for this is the Java Virtual Machine (JVM). A system virtual machine is located directly at the ISA level and creates virtual instances of the underlying hardware which it can assign to different guest OSs.

In case of process VMs depicted in figure 8a, the operating system runs in system mode and the virtualizing software runs in user mode while in case of System VMs the virtualizing software depicted in 8b runs in system mode. So in case of system virtualization, the virtualizing software is put directly at the ISA level and is therefore in full control of the hardware, while in

Figure 8: Process and System VMs

case of process VMs the virtualizing software is put in the ABI9 level where the OS is in full control of the hardware. The ABI gives a program access to the hardware by the system call interface of the OS and direct access to the user mode ISA. Thus the difference of System VMs and process VMs is that a process VM is a virtual platform that executes an individual process while a System VM provides a complete persistent system environment that supports an operating system along with its many user processes. In addition, it provides access to virtual hardware resources like networking, I/O, memory and processors [BDF<sup>+</sup>03, SN05a, SN05b].

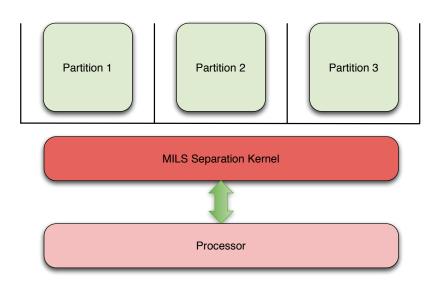

Due to the demands of GPOS properties, openness, High-Level APIs, real-time behavior and strict spatial and temporal isolation, system virtualization is the most interesting VM architecture for embedded real-time systems, because a system virtual machine is able to provide a complete persistent system environment to host multiple OSs fulfilling these demands. These properties inspired the development of the system multiple independent layers of security architecture (MILS [Objo8]) for embedded systems being used in mission critical systems.

<sup>9</sup> Application Binary Interface

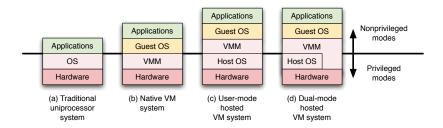

Figure 9: Different types of System VMs [SNo<sub>5</sub>b].

## 2.2.1 System Virtual Machines

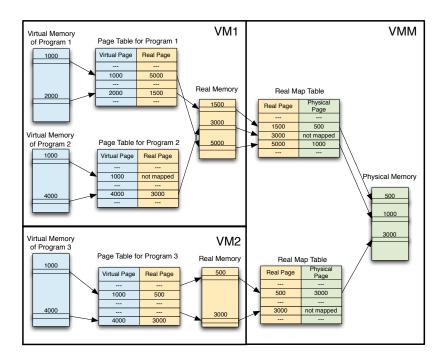

The VMM<sup>10</sup> is the core component in any System VM environment. It is responsible for scheduling and managing the allocation of hardware resources to various guest VMs. The VMM controls the physical resources and makes them available to the guest VMs by providing them as virtualized resources. The resources can be shared among the guest VMs, they can be partitioned with a partition being exclusively accessible to a guest VM or they can be exclusively assigned to a single guest VM. Such resources include the CPU registers, the real memory of the system and the various I/O devices attached to the system. To realize virtualization in an efficient manner, at least the VMM needs to be executed in an higher privileged "real CPU mode" than the code of the guest VMs. The real CPU mode denotes the CPU mode currently determined by the hardware. Usually, the hardware provides a system mode used by the OS and a user mode used by the applications. The real CPU mode can differ from the virtual CPU mode, as the CPU mode needs to be virtualized for the guest OS. Thus the guest OS executes virtually in a higher privileged CPU level than the guest applications, while the real CPU mode in hardware may not reflect this. With this knowledge, it is possible to distinguish between different types of System VMs.

**Definition 2.6.** A virtual machine system in which the VMM operates in a privileged level higher than the level of the guest VMs is called native VM system (see figure 9) [SNo5b].

In such a system, the VMM has to be installed first on the system. The guest OSs are installed on top of the VMM. Thus, the

<sup>10</sup> Virtual Machine Monitor

VMM always keeps full control over the hardware during the installation process. As the definition says the guest OS runs in a lower privilege level than the VMM, and thus the CPU privilege mode has to be emulated by the VMM. A well known example for native VM systems is XEN. Sometimes it is advantageous to run the VMM on top of a host OS for user convenience and implementation simplicity, as such a System VM can use the functionality provided by the host OS to implement the VMM functionality.

**Definition 2.7.** A virtual machine system in which the VMM is executed on top of an existing OS is called hosted VM system (see figure 9) [SNo5b].

A hosted VM system can be implemented with the VMM running at a lower privilege level than the guest OS only when it is possible to modify the host OS. This is not always possible, as the source code may be unavailable or licensing restrictions prohibit such modifications. In these cases, the VMM may be implemented at the same privilege level of the guest OS.

**Definition 2.8.** A virtual machine system in which the VMM is executed on top of an existing OS with a privilege level equal to the privilege level of its guests is called user-mode hosted VM system (see figure 9) [SNo5b].

User-mode System VMs suffer efficiency, because most of the code has to be scanned or emulated. To overcome these problems, an additional kind of hosted VM systems has been introduced.

**Definition 2.9.** A virtual machine system in which the VMM is executed on top of an existing OS with a privilege level lower or equal to the privilege level of its guests is called dual-mode hosted VM system (see figure 9) [SNo5b].

Those systems can be implemented using well defined interfaces of the OS such as kernel extensions or device drivers. A well known example for such a dual-mode hosted system is the classic VMWare for Desktops.

To make the physical resources available to the guest VMs the VMM assigns these resources to the guest VM. It is very important for the VMM to be able to get the control of the resources

back, so that they can be assigned to a different VM when the resource is shared between multiple VMs. Thus, the VMM must maintain the full control over all hardware resources, even in the case that they are temporarily assigned and used by the guest VM currently running. This problem already occurs in time-sharing system, where the OS needs to get the processor back to assign a new task to the processor. In this case, the resource controlled by the OS is the interval timer. It is not directly accessible for the tasks of the OS. Thus the OS can ensure its reactivation by setting a timer value equal to the time assigned to the task. After this time, the timer causes an interrupt guaranteeing that the OS gains back control of the processor. The situation is similar in a System VM environment. In this case the VMM controls the sharing of the resources between the different VMs. The VMM therefore emulates the access to privileged resources to prevent the VMs from directly accessing these resources. When considering interrupts as an example, the VMM would first handle the interrupt itself before it modifies the state of the guest VMs to emulate the incoming interrupt.

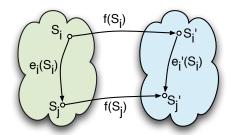

In the following section, the process of the control transfer from the guest VMs to the VMM will be formally derived to ensure virtualization with one of the main properties being to keep the VMM in full control of all system resources. Afterwards, the problems of virtualizing system memory will be introduced. [SNo5b]

### 2.2.2 Processor Virtualization

Already in the very early stage of third generation computers, virtualization came up as a technology to realize multiple subsystems on a large system like a mainframe computer. In 1974, G.J. Popek and R.P. Goldberg presented the formal definitions of VMs and a simple condition which can be tested to determine whether an architecture can efficiently support virtualization. After presenting this formal requirements in the following subsection the different control transfer approaches are shortly introduced to pass the control from a VM to the VMM.

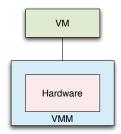

Figure 10: Virtual Machine Monitor Concept

## Formal Requirements of Virtualizability

In the following section, it will be shown that system virtualization software needs to fulfill the three properties efficiency, resource control and equivalency to provide a correct and efficient virtualization of the underlying ISA. This will be described at a quite formal level which allows the exact classification of ISAs into two classes. The first class contains all ISAs fulfilling the formal requirements and are thus virtualizable, while the second class contains the ISAs not fulfilling these requirements. These ISAs are called to be not efficiently virtualizable.

To realize a virtual machine on top of the real machine, the concept of the virtual machine monitor (VMM), depicted in figure 10, is introduced. The three essential characteristics of a VMM are:

- The VMM provides an essentially identical environment for programs as the original machine would.

- Programs running in this environment show only minor decreases in speed.

- The VMM is in complete control of the system resources.