# A framework for Assertion-Based Timing Verification and PC-Based Restbus Simulation of Automotive Systems

## **Dissertation**

A thesis submitted to the Faculty of Computer Science, Electrical Engineering and Mathematics of the University of Paderborn in partial fulfillment of the requirements for the degree of Dr. rer. nat.

by

**Gilles Bertrand Gnokam Defo**

Paderborn, 2015

### Supervisors:

Prof. Dr. Franz-Josef Rammig, University of Paderborn

Prof. Dr. Marco Platzner, University of Paderborn

Date of public examination: 11.09.2015

## **Abstract**

Automotive system innovation is mainly driven by software which can be distributed over a large number of functions typically deployed over several Electronic Control Units (ECUs). This growing design complexity makes the verification and validation process challenging and difficult. Therefore, the development of efficient and effective design methodologies is of great interest for automotive engineers.

A central concept in the development of automotive software is the component-based approach. Currently, the most prominent approach that supports this design paradigm is the AUTomotive Open System ARchitecture (AUTOSAR).

The System-Level Design Language (SLDL) SystemC provides means to simulate the behavior of AUTOSAR software components by means of a discrete-event simulation kernel. Additionally, SystemC comes with a set of libraries such as the SystemC Verification Library (SCV). Meanwhile, the interest of using SystemC has grown in the automotive software development community.

In this thesis we present a SystemC-based design methodology for early validation of time-critical automotive systems. The methodology spans from pure SystemC simulation to PC-based Restbus simulation. To deal with synchronization issues (oversampling and undersampling) that arise during Restbus simulation between the SystemC simulation model and the remaining bus network, we also present a new synchronization approach.

Finally, we make use IP-XACT for SystemC component integration. To capture timing constraints on the simulation model, we propose timing extensions for the IP-XACT standard. These timing constraints can then be used to verify the SystemC simulation model.

## Kurzfassung

Innovation in der Automobilindustrie wird durch Elektronik und vor allem durch Software ermöglicht. In der Regel wird eine Vielzahl von verteilten Funktionen realisiert. Typischerweise, wird diese Software über mehrere Steuergeräte verteilt.

Durch die Verteilung und die Vielzahl an Funktionen, ensteht eine immer wachsende Komplexität, die den Verifikations- und Validierungsprozess anspruchsvoller und schwieriger gestaltet. Daher ist für Ingenieure in der Automobilindustrie die Entwicklung von effizienten und effektiven Design-Methoden von großem Interesse.

Ein zentrales Element in der Entwicklung automobiler Software ist der komponentenbasierte Ansatz. Derzeit ist AUTOSAR der wichtigste Standard, der dieses Paradigma unterstützt. Die Systembeschreibungssprache SystemC ist ebenfalls ein Mittel, um AUTOSAR-Komponenten simulieren zu können. Desweiteren stellt SystemC einen Satz von Bibliotheken zur Verfügung wie zum Beispiel die "SystemC Verification Library" (SCV), und einen diskreten Event-Simulationskern. Inzwischen ist das Interesse an der Verwendung von SystemC in der automobile Softwareentwicklung stark gestiegen.

In dieser Arbeit stellen wir eine SystemC-basierte Entwurfsmethodik für eine frühe Validierung zeitkritischer automobile Systeme vor. Die Methodik reicht von einer reinen SystemC-Simulation bis zu einer PC-basierten Restbussimulation. Um die Synchronisation bezüglich Überabtastung und Unterabtastung zwischen dem SystemC-Simulationsmodell und dem Restbus während der Restbussimulation zu gewährleisten, präsentieren wir ein Synchronisationsverfahren.

Im Rahmen dieser Arbeit, wurde für die Integration von SystemC-Komponenten IP-XACT als Modelierungsstandard verwendet. Um eine Zeitanalyse ermöglichen zu können, stellen wir Erweiterungen für den IP-XACT Standard vor, mit deren Hilfe Zeitanforderungen an das Simulationsmodell erfasst werden können.

iii

## **Acknowledgements**

First and foremost, I would like to thank Prof. Dr. Franz-Josef Rammig for his guidance, his continuous support and valuable suggestions and ideas throughout the development of the concepts of this thesis. I also want to thank Prof. Dr. Marco Platzner for co-supervising this thesis.

Moreover, I would like to thank Jun. Prof. Christian Plessl, Dr. Wolfgang Müller, Dr. Stefan Sauer for being member of the examination board.

In C-LAB, I had the opportunity to contribute to several industrial research projects under the auspices of Dr. Wolfgang Müller in a great research environment. I thank him for his support and our numerous fruitful discussions. I would like to thank all my former colleagues at C-LAB and the University of Paderborn for the friendly and inspiring environment.

Furthermore, I would also like to thank Mr. Stefan Kuntz for the fruitful discussions and comments during the joint research projects, and for his support in the final phase of this thesis.

I am most indebted to my parents Prof. Dr. Edmond Gnokam and Elise Gnokam who have supported me not only during my studies but throughout my whole life in every imaginable way.

Last but not least, I would like to thank Dr. Anna Barát for being an on-going source of support and motivation during the time of this research and dedicate this thesis to my children.

Gilles Bertrand Gnokam Defo

٧

# **Contents**

| 1 | Intr | oduction 1                                                 |

|---|------|------------------------------------------------------------|

|   | 1.1  | Motivation                                                 |

|   |      | 1.1.1 Automotive system innovation                         |

|   |      | 1.1.2 Simulation                                           |

|   |      | 1.1.3 Modeling                                             |

|   | 1.2  | Problem statement                                          |

|   |      | 1.2.1 Restbus simulation for early functional validation   |

|   |      | 1.2.2 Data synchronization between simulator and hardware  |

|   |      | 1.2.3 Specification of timing constraints                  |

|   | 1.3  | Research contribution                                      |

|   | 1.4  | Structure of this thesis                                   |

| 2 | Fou  | ndation 9                                                  |

|   | 2.1  | Automotive Control Systems                                 |

|   |      | 2.1.1 Open-Loop Control                                    |

|   |      | 2.1.2 Closed-Loop Control                                  |

|   | 2.2  | Design of Automotive Control Systems                       |

|   |      | 2.2.1 Classification of Real-Time systems                  |

|   |      | 2.2.2 Design Methodology (AUTOSAR)                         |

|   |      | 2.2.3 Timing Modeling with TADL2                           |

|   |      | 2.2.4 Testing and Verification                             |

|   | 2.3  | Automotive Vehicle Netwoks                                 |

|   |      | 2.3.1 Controller Area Network (CAN)                        |

|   |      | 2.3.2 FlexRay                                              |

|   | 2.4  | Design of Electronic Systems                               |

|   |      | 2.4.1 Design Modeling with IP-XACT                         |

|   |      | 2.4.2 Design Modeling Language with SystemC                |

|   |      | 2.4.3 Formal Property Specification Language with PSL      |

| 3 | Rela | ated Work 49                                               |

|   | 3.1  | IP-XACT                                                    |

|   |      | 3.1.1 Extensions of the IP-XACT Schema                     |

|   | 3.2  | Modeling and simulation of embedded automotive software 50 |

|   |      | 3.2.1 Restbus Simulation                                   |

|   |      | 3.2.2 Modeling and simulation with SystemC                 |

|   | 3.3  | 3.2.3<br>3.2.4 | AUTOSAR Vs. SystemC                                                   | 52<br>52<br>53   |

|---|------|----------------|-----------------------------------------------------------------------|------------------|

|   | 3.3  | 3.3.1          | Verifying SystemC using an Intermediate Verification Language and     | 53<br>53         |

|   |      | 3.3.2          | ·                                                                     | 53               |

|   |      | 3.3.3          | • • •                                                                 | 54               |

|   |      | 3.3.4          |                                                                       | 54               |

|   |      | 3.3.5          | · ·                                                                   | 55               |

| 4 | Met  | hodolog        | ev .                                                                  | 57               |

|   | 4.1  | _              | ,                                                                     | 58               |

|   |      | 4.1.1          | Ç                                                                     | 59               |

|   |      | 4.1.2          | · · · · · · · · · · · · · · · · · · ·                                 | 59               |

|   |      | 4.1.3          |                                                                       | 63               |

|   |      | 4.1.4          |                                                                       | 64               |

|   |      | 4.1.5          | -                                                                     | 64               |

|   | 4.2  | Restbu         |                                                                       | 65               |

|   |      | 4.2.1          |                                                                       | 65               |

|   |      | 4.2.2          |                                                                       | 65               |

|   |      | 4.2.3          |                                                                       | 67               |

| 5 | Asse | ertion-B       | ased Timing Verification                                              | 71               |

|   | 5.1  |                | 8                                                                     | 72               |

|   | 0.1  | 5.1.1          |                                                                       | . –<br>72        |

|   |      | 5.1.2          |                                                                       | . <u>-</u><br>74 |

|   |      | 5.1.3          |                                                                       | 75               |

|   |      | 5.1.4          |                                                                       | 77               |

|   |      | 5.1.5          |                                                                       | 78               |

|   | 5.2  |                |                                                                       | 79               |

|   |      | 5.2.1          | Reason for using both TADL2 and Property Specification Language (PSL) |                  |

|   |      | 5.2.2          |                                                                       | 82               |

|   |      | 5.2.3          |                                                                       | 83               |

|   |      | 5.2.4          |                                                                       | 85               |

|   |      | 5.2.5          | •                                                                     | 87               |

|   |      | 5.2.6          |                                                                       | 89               |

|   |      | 5.2.7          | <u> 1</u>                                                             | 90               |

|   |      | 5.2.8          |                                                                       | 92               |

|   |      | 5.2.9          | •                                                                     | 95               |

|   | 5.3  |                |                                                                       | 96               |

|   | 5.4  |                |                                                                       | 97               |

| 6 | Vari | fication       | of timing properties: case study Brake-By-Wire                        | 99               |

| U | 6.1  |                | onal decomposition of the BBW model                                   |                  |

|   | 6.2  |                | nenting of the simulation model                                       |                  |

|   | J.2  | THOU MI        |                                                                       | ٠.               |

### CONTENTS

|   | 6.3   | Refere    | nce model                                                | 103 |

|---|-------|-----------|----------------------------------------------------------|-----|

|   | 6.4   | Specify   | ying the timing requirements                             | 104 |

|   | 6.5   | Evalua    | tion results                                             | 105 |

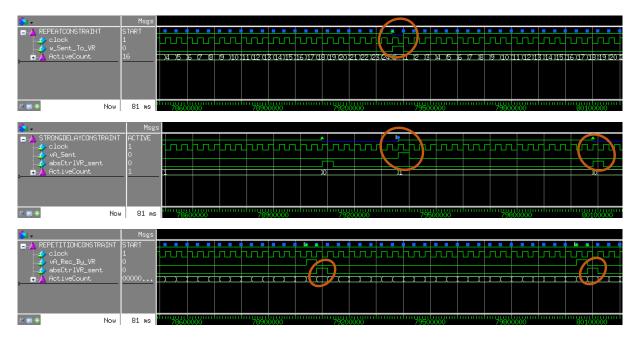

|   |       | 6.5.1     | Repeat, StrongDelay and Repetition timing constraints    | 105 |

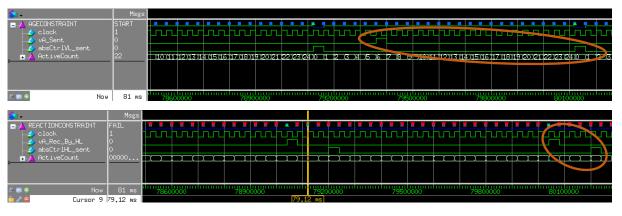

|   |       | 6.5.2     | Evaluation of the AgeConstraint and ReactionConstraint   |     |

|   |       | 6.5.3     | Evaluation of synchronization related timing Constraints | 108 |

|   | 6.6   | Summa     | ary and discussion                                       | 109 |

| 7 | Syno  | chroniza  | ation                                                    | 111 |

|   | 7.1   | Backgi    | round                                                    | 111 |

|   |       | 7.1.1     | Data smoothing: Robust LOWESS/LOESS                      | 111 |

|   |       | 7.1.2     | Multirate Systems                                        | 115 |

|   |       | 7.1.3     | Downsampling                                             | 117 |

|   | 7.2   | Our sy    | nchronization approach                                   | 121 |

|   | 7.3   | Upsam     | npling                                                   | 123 |

|   | 7.4   | Downs     | sampling                                                 | 124 |

|   |       | 7.4.1     | Main phase                                               | 125 |

|   |       | 7.4.2     | Initialization phase                                     |     |

|   |       | 7.4.3     | Downsampling with peak detection                         | 127 |

|   | 7.5   | Summa     | ary                                                      | 130 |

| 8 | Eval  | luation   | of Synchronization approach                              | 133 |

|   | 8.1   |           | tion platform                                            | 133 |

|   |       | 8.1.1     | System Overview                                          |     |

|   |       | 8.1.2     | Hardware architecture                                    |     |

|   |       | 8.1.3     | Software architecture                                    |     |

|   |       | 8.1.4     | Applied tools                                            |     |

|   | 8.2   | Evalua    | ation results                                            |     |

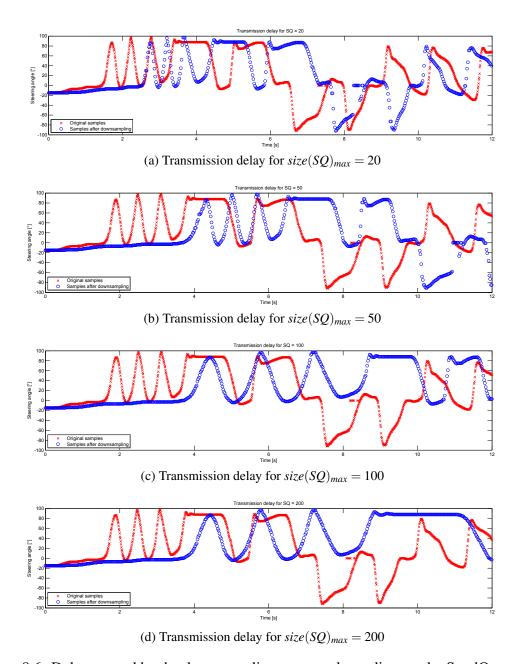

|   |       | 8.2.1     | Impact of the SendQueue-size on transmission delay       |     |

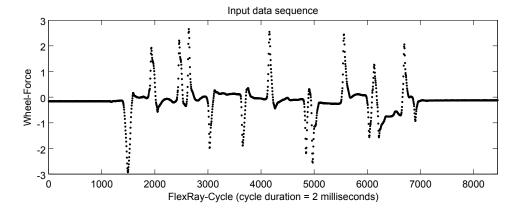

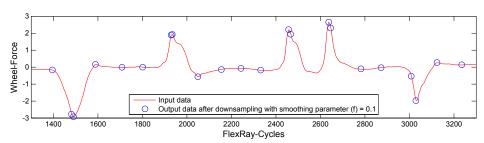

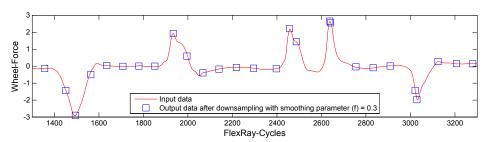

|   |       | 8.2.2     | Variation of the smoothing parameter of Robust LOWESS    |     |

|   |       | 8.2.3     | Impact of the SendQueue size on peak sequence detection  |     |

|   |       | 8.2.4     |                                                          |     |

|   |       | 8.2.5     | Summary                                                  |     |

| 9 | Con   | clusion   |                                                          | 147 |

|   | 9.1   | Summa     | ary                                                      | 147 |

|   | 9.2   |           | ok                                                       | 149 |

|   |       | 9.2.1     | Synchronization                                          | 149 |

|   |       | 9.2.2     | Timing verification                                      | 149 |

| A | Veri  | fication  | unit                                                     | 151 |

| В | Picto | orial rei | presentation of the IP-XACT Schema Extensions            | 155 |

| • | B.1   | _         | ims                                                      | 155 |

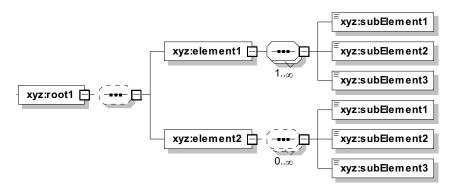

|   | ו.ע   | B.1.1     | Elements and sequences                                   | 155 |

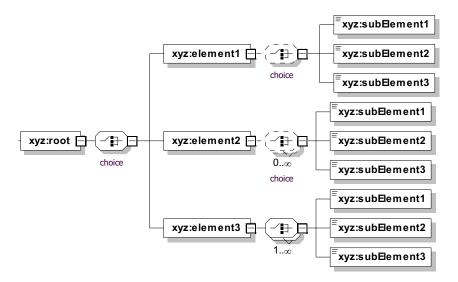

|   |       | B.1.1     | •                                                        |     |

|   |       | D.1.2     | Lientents and choices                                    | 150 |

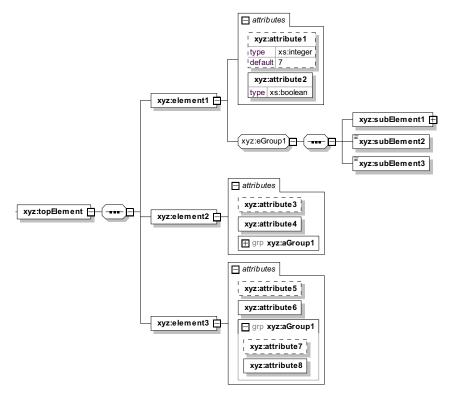

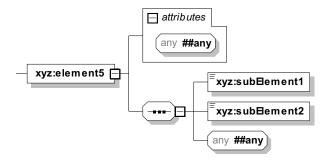

|                  |       | Elements, attributes, groups, and attributeGroups |     |

|------------------|-------|---------------------------------------------------|-----|

| List of Acronyms | 159   |                                                   |     |

| List of Figu     | ires  |                                                   | 165 |

| List of Tables   |       | 167                                               |     |

| List of Own      | ı Pub | olications and Bibliography                       | 169 |

# **Chapter 1**

## Introduction

### 1.1 Motivation

## 1.1.1 Automotive system innovation

Meanwhile safety, security, driving dynamics, and comfort features have significantly been improved in today's automobile. This was made possible by the availability of intelligent sensor and actuator technologies and powerful ECUs, whereby some of the ECUs are nowadays equipped with multi-core processors.

To keep up with the competition on the market, automotive Original Equipment Manufacturers (OEMs) try to shorten their development cycle, whilst keeping or enhancing their products quality.

Typically, these systems are complex real-time embedded systems composed of a large number of functions deployed over several ECUs, whereby the ECUs communicate among each other via network buses like FlexRay or CAN. This leads to an ever growing design complexity, which makes the test and validation process challenging.

Therefore, it is necessary to start the test and validation process as early as possible in the design process.

### 1.1.2 Simulation

#### System level simulation

Usually, a significant amount of time is spent during the system architecture design phase of the automotive development process. In this phase hardware- and software partitioning is done. Hereby, the hardware architecture comprises elements such as ECUs, bus systems, sensors and actuators and energy supply. The software infrastructure includes the operating system, bus drivers and additional services.

Simulation can be used to speed up the system architecture design exploration phase. It gives system designers the possibility to test their designs against predefined functional requirements and therewith analyze communication interactions and the overall system design in an early phase of the development process.

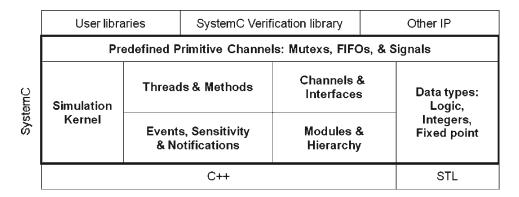

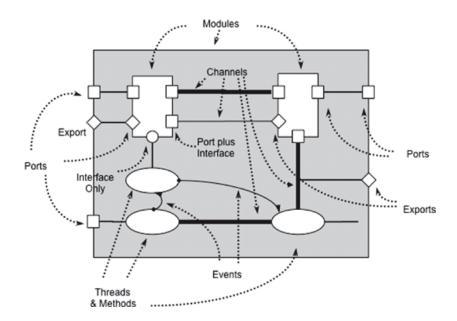

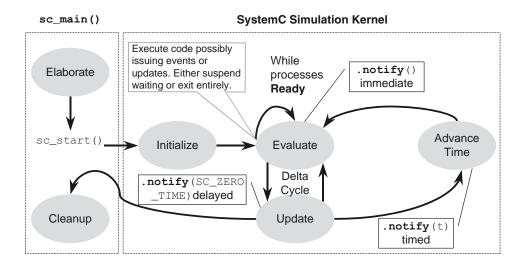

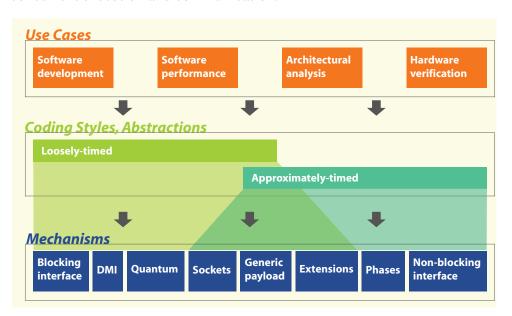

SystemC [53] is a well deployed System Level Description Language (SLDL) in the field of Embedded System level design. Strictly speaking, SystemC is not a language but rather a C++ based class library, which is coupled with an integrated verification library: the SystemC Verification Library (SCV) and a discrete-event simulation kernel. Furthermore, SystemC provides means to describe, analyze and verify both hardware and software models at various levels of abstraction (see Section 2.4.2).

#### Hardware-in-the-Loop simulation

Since in-vehicle driving tests are often time-consuming, expensive and not reproducible, Restbus simulation (RBS) and Hardware-In-the-Loop (HIL) are applied in later phases of the development cycle. RBS and HIL are widespread techniques. They allow developers to validate new hardware and software solutions within their target environment.

HIL simulation provides an effective platform by adding the complexity of the plant under control to the test platform. The complexity of the plant under control is included in the test and development by adding a mathematical representation of all related dynamics of the system. These mathematical representations are referred to as the plant simulation. The embedded system to be tested interacts with the plant during simulation.

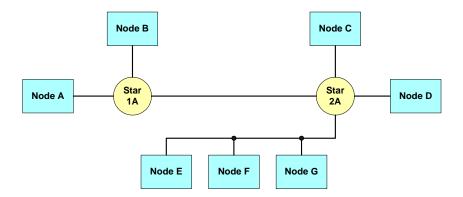

Restbus simulation on the other hand is a special HIL variant, whereby this method takes the bus network into account. A typical application for Restbus simulation is the integration of any developed functionality (features) into an existing bus network. To achieve this, the Restbus simulator has to pro-

vide messages from non-existing nodes to the rest of the system during the simulation. It also has to consume message from existing nodes and react accordingly.

## 1.1.3 Modeling

To benefit from the components-oriented approach when designing complex embedded systems, several modeling languages have been proposed in the literature. In the context of automotive system development there exists a variety of modeling standards, the most prominent ones are the AUTOSAR and the Systems Modeling Language (SysML). Another far but related modeling standard from the field of Electronic Design Automation (EDA) is IP-XACT.

SysML [43] is a general-purpose modeling language for system engineering applications. It supports the specification, analysis, design, verification and validation of a broad range of systems and systems-of-systems. SysML was originally developed by an open source specification project, and includes an open source license for distribution and use.

The AUTOSAR [27] initiative was founded in 2003 and is a union of well-known vehicle manufacturer and supplier of automotive systems with the goal of having a common framework for the development of software components. The AUTOSAR standard defines not only a comprehensive technical infrastructure for these systems, but also one that builds upon the methodology and description formats for the development of AUTOSAR-compliant systems. A further primary goal of AUTOSAR is the integration aspect.

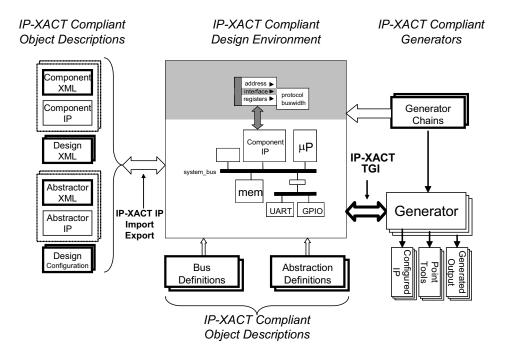

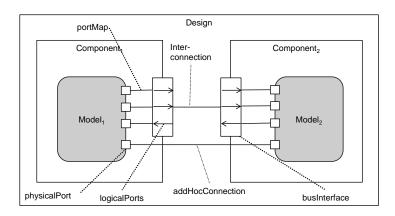

IP-XACT [48] is an XML standard format for IP packaging, reuse and integration. This standard was originally created by Mentor Graphics [45]. It defines a standard way for describing and handling multi-sourced electronic IP components, enabling an automated design integration and configuration within multi-vendor design flows.

### 1.2 Problem statement

## 1.2.1 Restbus simulation for early functional validation

SystemC has turned out to be suitable for the modeling and simulation of automotive networks systems [63]. As aforementioned, it provides means to describe both hardware and software and a simulation environment. Furthermore, several verification methodologies and libraries support the test and verification of SystemC models. The most popular ones are: UVM [54] (Uni-

versal Verification Methodology), OVM [20] (Open Verification Methodology) and PSL [52] (Properties Specification Language).

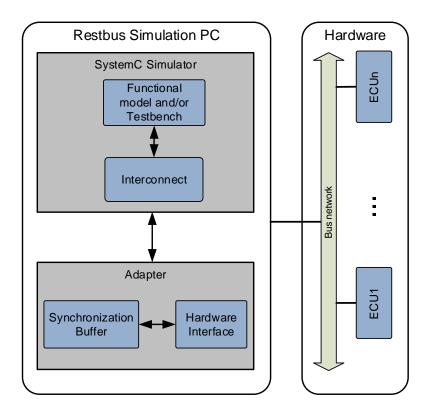

Several companies provide tools and hardware equipment for Hardware-inthe-Loop and Restbus simulation. They all require the use of dedicated hardware to run the design under test. In those simulation environments, the standard PC is only used to host the test automation software. Up to now there is no approach describing how to actually use the standard host PC as execution platform for the design under test.

The main contributions of this thesis consists of providing a framework and design methodology to support the use of a standard PC for the simulation of the design under test during Restbus simulation. Moreover, the Restbus simulator is implemented in SystemC.

# 1.2.2 Data synchronization between simulator and hardware

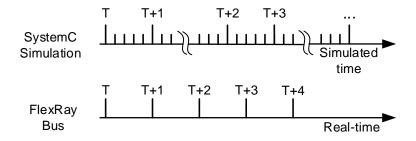

The notion of time is one of the key concepts of SystemC, which enables the simulation of concurrent processes. However, the standard SystemC simulation kernel does not provide real-time simulation support. Mechanisms such as preemption and priority based scheduling are not available. Therefore, it is not possible to model the complete software behavior of a real-time critical system.

There exist a wide range of SystemC-based Real-Time Operating System (RTOS) modeling concepts. These concepts consist of implementing the operating system features at a high abstraction level, and later during the refinement process, the RTOS model is typically replaced by a custom RTOS. The simulation overhead introduced by RTOS models has been proven to be negligible [77].

Nevertheless, none of those RTOS modeling concepts can be applied to Restbus simulation or Hardware-in-the-Loop, since they only target the simulation of a real-time environment and not simulation itself in real-time. Further, SystemC simulation time differs from the real network time.

As a consequence, during the simulation of complex models, not all the data generated by the real network nodes might be received and processed on time by the corresponding components in the SystemC simulation. Oversampling and Undersampling might be observed.

## 1.2.3 Specification of timing constraints

IP-XACT has been proven to be a well-defined standard for hardware design description. It provides a common language and vendor-neutral way to describe IPs. Thus, we opted for its use as an exchange format for the description of the individual Restbus and HIL components.

In this thesis we present a SystemC-based simulation approach, where the SystemC simulation model interacts with the real hardware infrastructure. In the context of the simulation of real-time critical systems, timing can be considered as a functional property. Therefore, the model should be analyzed in order to verify if it conforms to the specified timing requirements. This analysis has to be done before exercising the actual test process.

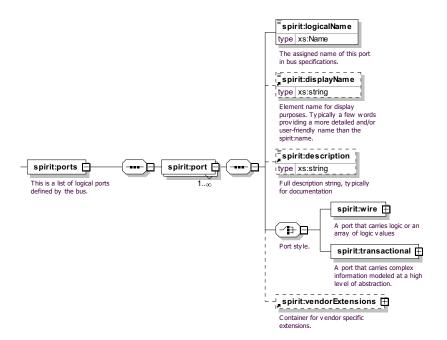

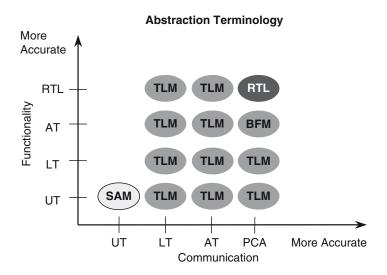

For component abstraction representation, the IP-XACT standard does not provide support for the entire range of abstraction levels usually considered in the literature. However, Transaction Level Modeling (TLM) and Register Transfer Level (RTL) are supported, which are the most important ones.

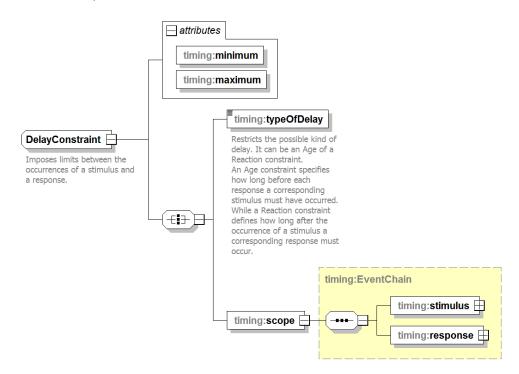

Further, the notion of timing constraints already exists in IP-XACT. Delay timing constraints can be specified for RTL models. But unfortunately the current standard does not provide similar elements for transactional models and the standard needs to be extended by additional timing constraints to enable a more detailed timing analysis of complex designs.

### 1.3 Research contribution

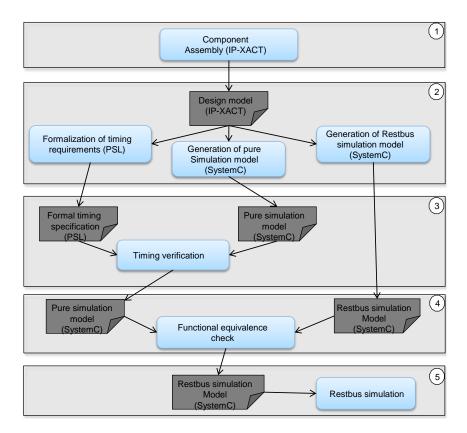

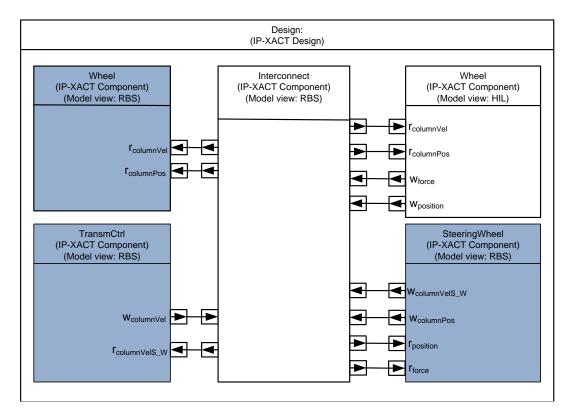

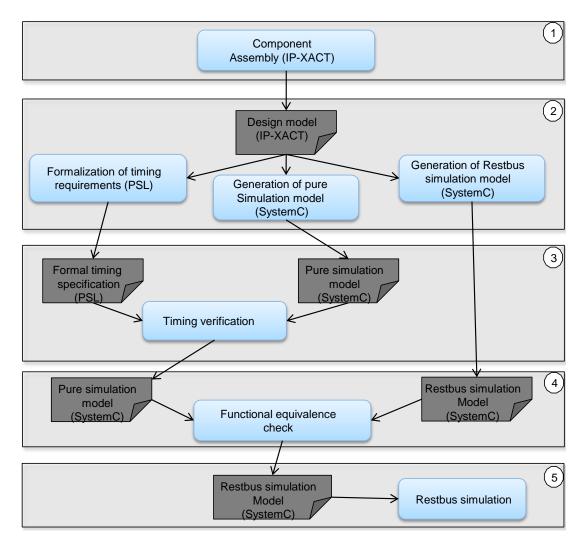

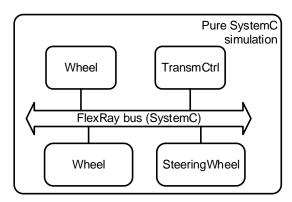

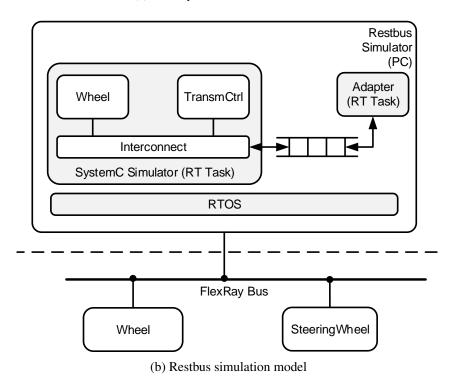

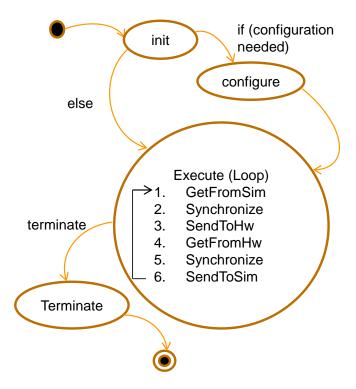

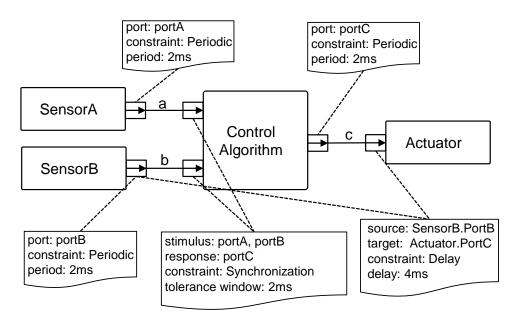

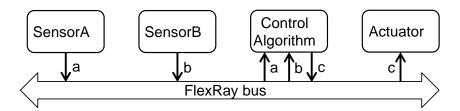

The aim of this thesis is to provide a framework for SystemC-based Restbus simulation of automotive systems for early validation. For this purpose we define a methodology for timing analysis of SystemC models in a pure SystemC simulation environment, before starting the actual Restbus simulation process. The defined methodology is depicted in Figure 1.1.

The research contributions in this dissertation can be defined as follows:

- 1. Proposal of additional timing constraints for the IP-XACT standard version IEEE 1685-2009 [48] to capture timing constraints.

- 2. Development of a property specification-based verification flow to verify and enhance the simulation models constructed. IEEE 1850 version of PSL [52] (Property Specification Language) was used.

- 3. Derivation of PSL formulas from specified IP-XACT-timing-extensions. This contribution consists of defining mapping rules from IP-XACT timing constraint specifications into executable PSL formulas.

Figure 1.1: Proposed design flow

4. Development of a synchronization algorithm to handle possible sampling rate issues between simulator running on the host PC and the real hardware. The synchronization approach depends on the possible kind of application that can be simulated on the host PC. We classified the applications into the following three categories: Open-loop control, Monitoring, and Closed-loop control.

## 1.4 Structure of this thesis

Chapter 2 introduces the theoretical background of the fields involved in this thesis. This includes the field of automotive control systems and the design of such systems. Additionally, the automotive vehicle network communication protocols FlexRay and CAN are discussed. At last but not least a brief introduction into the field of Electronic System Level design is given. Chapter 3 briefly discusses research results related to the simulation of automotive network and the design of electronic systems.

The chapters 4, 5 and 7 discuss the contributions of this thesis. Chapter 4 presents our methodology and simulation framework for functional verification of real-time critical automotive systems developed in this thesis. The

methodology includes a timing analysis of the model under investigation, that helps to verify that the model conforms to its timing requirements before starting the actual Restbus simulation process. Furthermore, the timing requirements are captured using IP-XACT.

In Chapter 5, timing extensions for IP-XACT needed to capture timing constraints on the design will be introduced. Chapter 7 is explicitly dedicated to one of the most important contributions of this thesis, which is the development of an approach needed for data synchronization between our Restbus simulator and the network bus.

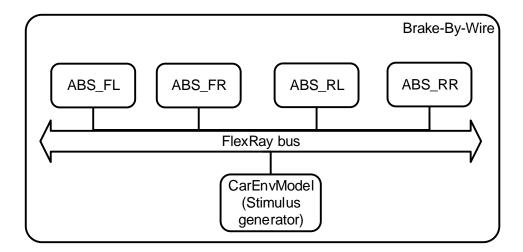

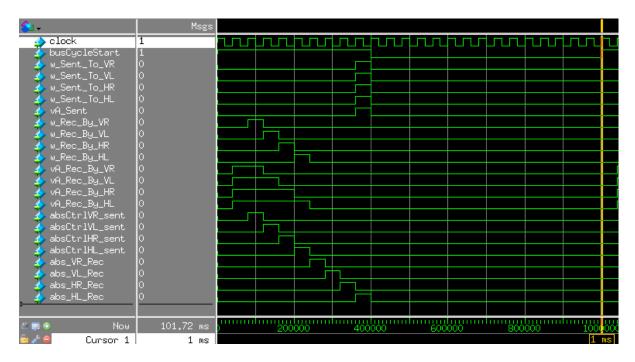

The chapters 6 and 8 are dedicated to the evaluation of both the timing verification and the synchronization approach. Chapter 6 evaluates the timing verification methodology. The system model used in this case study is a SystemC model of an automotive Brake-By-Wire (BBW) application. The application is distributed over a set of ECUs and includes Anti-lock Braking System (ABS) functionality. Chapter 8 evaluates the synchronization approach. The approach was validated on a HIL test environment consisting of a Steer-By-Wire system. This test environment has been used in several projects [90, 49].

## Chapter 2

## **Foundation**

This chapter introduces the theoretical background of the domains involved in this thesis. We will start by giving a brief introduction into the field of automotive control systems and the design of such systems. Following, the automotive vehicle network communication protocols FlexRay and CAN will be discussed, and finally a brief introduction into the field of Electronic System Level design will be given.

## 2.1 Automotive Control Systems

In today's automotive systems, control systems running on electronic control units (ECU) are used to regulate the operation of other systems. From the control application's perspective, the system being controlled is referred to as the *system plant*. In this sections we will describe the major types of automotive control systems. A control system is described by its fundamental elements, which are:

- Objectives of control

- System components

- Results/Outputs.

The objectives of a control system are the quantitative measures of the tasks to be performed by the system. These describe the desired values of one or more variables and are normally specified by the user [83].

The results are called outputs or controlled variables. Typically, the objective of a control system is to regulate the values of the outputs in a prescribed

9

manner based on the inputs of the control system. A control system should perform accurately, respond quickly, be stable and immune against noise.

The control system's accuracy specifies the deviation between the system's output and the desired system's output, with a constant-value input command. A quick response describes how fast the control system will track or follow changing input commands. A system's stability specifies how a system behaves, when a sudden change is made by the input signal.

The output of an unstable control system will diverge from its intended value based on its input. For any automotive application, a control system must be stable and controllable over the entire desired operating range.

A good controller design will minimize the chance of unstable operation even under extreme operating conditions. A system should maintain its accuracy by responding only to valid inputs. When noise or other disturbances threaten to change the system plant's output, good design will eliminate response to such inputs from system performance as much as possible [83].

A control system having small (ideally zero) response to noise inputs is said to have good noise immunity. Accuracy, quick response, stability and noise immunity are all determined by the control system configuration and parameters chosen for a particular plant. The purpose of a control system is to determine the output of the system (plant) being controlled in relation to the input and in accordance with the operating characteristics of the controller.

The relationship between the controller input and the desired plant output is called the control law for the system. The desired value for the plant output is often called the set point. The output of an electronic control system is an electrical signal that must be converted to some physical (or other) action in order to regulate the plant. A device that converts the electrical signal to the desired mechanical action is called an actuator.

Although electronic controllers can, in principle, be implemented with either analog or digital electronics, the trend in automotive control is digital. There are two major categories of control systems: open-loop (or feedforward) and closed-loop (or feedback) systems [83].

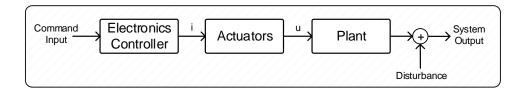

## 2.1.1 Open-Loop Control

Figure 2.1 depicts the generic structure of an open-loop control system. As shown in the figure, the components of an open-loop control system include an electronic controller, which has an output to an actuator. The actuator in turn, regulates the plant in accordance with the desired relationship between

the reference input (input command) and the value of the controlled variable (denoted by u) in the plant.

Figure 2.1: Block diagram of an open-loop control system

Many examples of open-loop control systems are encountered in automotive electronic systems, such as fuel control in certain operating modes [83]. As illustrated in Figure 2.1, the command input is sent to the electronic controller, which performs a control operation on the input to generate an intermediate electrical signal (denoted by i).

An open-loop control system is a system in which the computation of the controlled variables only depends on the current state and its system model. It does not use feedback to determine whether its output has achieved the expected goal or not. Thus, the operation of the plant is directly regulated by the actuator. The system's output may also be affected by external disturbances that are not an inherent part of the plant, but are the result of the operating environment.

One of the main drawbacks of the open-loop controller is its inability to compensate for external changes that might occur in the plant or for any disturbances.

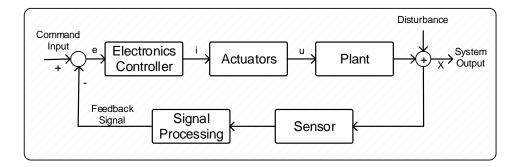

## 2.1.2 Closed-Loop Control

Closed-loop control systems are usually more robust than open-loop control systems. In a closed-loop control system, the actual system output is compared to the desired output value in accordance with the input. As shown in Figure 2.2, the measurements of the output variable being controlled is obtained via a sensor and feedback to the controller.

Each measured value of the controlled variable is compared with the desired value based on a reference input. A deviation signal based on the difference between desired and actual values of the output signal is created, and the controller generates an actuator signal (u) that tends to reduce the error to zero.

In addition to reducing this error to zero, feedback has other potential benefits in a control system. It can affect the control system performance by

Figure 2.2: Block diagram of a closed-loop control system

improving system stability and suppressing the effects of disturbances in the system.

The generic closed-loop control system illustrated in Figure 2.2 has some of the components shown in an open-loop control system, including the plant to be controlled, actuator(s), and control electronics. In addition, however, this system includes one or more sensors and some signal-conditioning electronics. The signal conditioning used in a closed-loop control system plays a role similar to that played by signal processing in measurement instrumentation.

That is, it transforms the sensor output as required to achieve the desired measurement of the plant output. Compensation for certain sensor defects (e.g. limited bandwidth) is possible, and in some cases necessary, to enable the comparison between the plant output and the desired value. Electronic control systems are classified by the way in which the error signal is processed to generate the control signal. The major control systems include proportional (P), proportional-integral (PI), and proportional-integral-differential (PID) controllers [83].

## 2.2 Design of Automotive Control Systems

### 2.2.1 Classification of Real-Time systems

A real-time computer system is a system, where the correctness of the system behavior depends not only on the logical results of the computations, but also on the physical time, when these results are produced [61]. By system behavior we mean the sequence of system's outputs over time.

The classification of real-time systems depends on the design perspectives. In [62] for instance, five different perspectives are defined and classified as follows:

- 1. Hard Real-Time Vs Soft Real-Time

- 2. Fail-Safe Vs Fail-Operational

- 3. Guaranteed-Response Vs Best effort

- 4. Resource-adequate Vs Resource-inadequate

- 5. Event-triggered Vs Time-triggered.

The first two classifications are influenced by the characteristics of the environment, that is, on the factors outside the computer system. The last three classifications are based on the tightness and strictness of the deadlines within the computer system, this means, on factors inside the computer system, such as peak load and the fault scenario [62].

Hard real-time systems describe the category of systems, where it is absolutely imperative for a system to provide its response within its required deadline. Missing the deadline would lead to useless results or even dangerous system state. In Soft real-time systems on the other hand, missing a deadline will only lead to a deterioration of the system's quality [62].

The classification Fail-safe Vs Fail-operational is related to the characteristics of the controlled object and not the computer system itself. Fail-safe systems are real-time systems, where one or more safe states can be reached in case of system failure. Therefore, fail-safe systems are required to have a high error-detection coverage. This high error-detection coverage is typically reached by means of a special external device called watchdog. In case of failure, the watchdog forces the controlled object into a safe state. Fail-operational systems however are systems where a safe state cannot be identified, e.g.: a flight control system on an airplane. In such systems, the computer must remain operational and provide a minimal level of service in case of failure to avoid a catastrophe [62].

Guaranteed-response systems are systems that make it possible to reason about the adequacy of the design independently of probabilistic arguments like peak loads and fault scenario. The probability of failure of a perfect system with guaranteed response is reduced to the probability that the assumptions about the peak load and the number and types of faults do not hold in reality. This probability is called assumption coverage [78]. Guaranteed response systems require careful planning and extensive analysis during the design phase. If such an analytic response guarantee cannot be given, we speak of a best-effort design. Moreover best-effort systems are typically only used for non safety-critical real-time systems. [62].

Guaranteed-response systems are based on the principle of resource adequacy, i.e., there are enough computing resources available to handle the

specified peak load and the fault scenario. Many non safety-critical real-time system designs are based on the principle of resource inadequacy. It is assumed that the provision of sufficient resources to handle every possible situation is not economically viable, and that a dynamic resource allocation strategy based on resource sharing and probabilistic arguments about the expected load and fault scenarios are acceptable. Hard real-time systems must be designed according to the guaranteed response paradigm that requires the availability of adequate resources [62].

Event-triggered (ET) and Time-triggered (TT) real-time systems differentiate themselves in the way they are internally triggered. They are not characterized by the behavior of their environment. A trigger hereby is a an event that causes the start of some activity in the computer, such as, the execution of a task (processing activity) or the transmission of a message (communication). In an ET control system, all communication and processing activities are initiated whenever a significant event other than the regular event of a clock tick occurs. In a TT system, all activities are initiated by the progression of time. Further, every observation of the controlled object is time-stamped with this global time [62].

## 2.2.2 Design Methodology (AUTOSAR)

The driving factors for the development of automotive systems are mainly related to customer requests and related to the regulation entities. On the one hand, customers express the need for more and more features whilst increasing safety and security aspects. On the other hand, environmental constraints have to be fulfilled from the regulation entity's perspective. This leads to an increasing design complexity.

Software is a driving factor for automotive innovation. A key concept in the development of automotive software is the component-based approach and the most prominent approach is AUTOSAR [27]. AUTOSAR is an initiative of a union of well-known vehicle manufacturers and suppliers of the automobile industry and was founded in 2003. AUTOSAR provides a common standard for the development of automobile software. Furthermore, the standard defines not only a comprehensive technical infrastructure for automotive systems, but it also builds upon a methodology and description formats for the development of AUTOSAR-compliant systems [73].

The development methodology is model-driven. The software architecture, as well as the ECU hardware and the network topology, are modeled in a formal way, which is defined by a metamodel that supports the software development process. All available modeling elements are specified by the AUTOSAR metamodel [27].

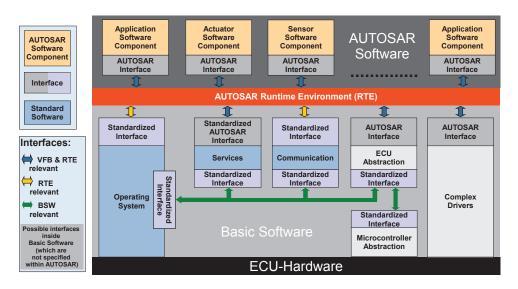

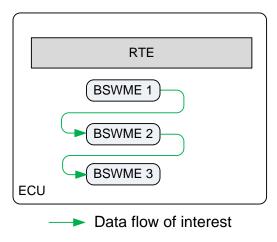

Figure 2.3 depicts the architecture of the AUTOSAR software layers. AUTOSAR distinguishes between three software layers, running on top of the ECU hardware. These layers are: the Application layer, the Runtime Environment (RTE) and the Basic Software (BSW).

Figure 2.3: AUTOSAR layered software architecture

### **Application Layer**

The AUTOSAR Software layer consists of Software Components (SW-Cs) that are mapped on to the ECU. A SW-C is the fundamental element in AUTOSAR. A SW-C can be either a *Composition* or *Atomic*.

While Atomic SW-C encapsulate the implementation of their functionality and behavior and expose well-defined connection points, the purpose of Composition SW-C is to allow the encapsulation of specific functionality by aggregating existing SW-C. Software components can be refined into Application-, Sensor/Actuator- and Service software component type [29].

### **Runtime Environment**

From a system design level perspective, the AUTOSAR RTE acts as a middleware for inter- and intra-ECU communication.

The RTE provides a communication abstraction to the AUTOSAR Software layer by providing standardized interfaces and services for both inter-ECU and intra-ECU communication. The software components running on top of the RTE are application dependent, therefore, the RTE layer is partly gener-

ated and partly configured. As a result, the RTE will differ from one ECU to another [30].

#### **Basic Software**

The AUTOSAR BSW is a standardized software layer, which provides services to the AUTOSAR SW-C and is required to run the functional part of the software. It does not fulfill any functional task itself and is situated below the AUTOSAR RTE (see Figure 2.3). The Basic Software contains standardized and ECU specific components. Furthermore, this layer provides System, Memory and Communication related services to the application software. Moreover, the BSW layer incorporates a Micro-controller- and ECU abstraction layer [28].

#### **AUTOSAR Timing Extensions**

The AUTOSAR timing extension specification [31] provides consolidated and consistent representation of relevant timing dependencies and corresponding timing constraints. For the specification of the timing requirements, the timing extension specification defines a timing model that can be used as specification basis for a contract based development process, in which the development can be carried out by different organizations at possibly distributed locations.

Basically, there are two different interpretation when dealing with timing information. It can either be a restriction for the timing behavior of the system (*TimingConstraint*) or a *TimingGuarantee* for the timing behavior of the system (*TimingDescription*). Minimum or maximum latency bound for a certain sequence of timing events can be taken as constraint, for instance during component integration. A component related timing event can be guaranteed to occur periodically within a certain bound.

In the timing extension specification two basic elements play a key role, namely the timing description event (*TimingDescriptionEvent*) and the timing description event chains (*TimingDescriptionEventChain*). In essence, a *TimingDescriptionEvent* is an abstract representation of a specific observable system behavior, which can be observed during the system's operation, while a *TimingDescriptionEventChain* describes a causal relationship between two timing events. Each event chain has a well-defined stimulus and response, where the stimulus and response elements describe the start and end point of the event chain. These elements can be hierarchically decomposed into an arbitrary number of chain segments.

Furthermore, by means of timing description event chains, the specification of the interrelation between the stimulus of a system and its corresponding response can be formalized and used to constrain the given system dynamic. The AUTOSAR timing extension model [31] distinguishes at the highest level between the following types of timing constraints:

EventTriggeringConstraints characterize a type of timing constraints that can be used to describe the occurrence of the referenced timing event. This constraint can be further refined into:

- PeriodicEventTriggering: specifies the characteristics of a timing description event which occurs periodically.

- SporadicEventTriggering: specifies the characteristics of a timing description event which occurs sporadically.

- BurstPatternEventTriggering: describes a burst of occurrences of a single event and its repetition.

- ConcretePatternEventTriggering: specifies the characteristics of a timing description event which occurs as a concrete pattern and its repetition.

LatencyTimingConstraints are used to specify the amount of time allowed to elapses between the occurrences of any two timing description events. It is always associated with a TimingDescriptionEventChain.

AgeConstraints are used to specify a minimum and maximum age that is tolerated when data is received.

SynchronizationTimingConstraints are used to specify a synchronicity constraint among the occurrences of two or more timing description events.

OffsetTimingConstraints are used to specify an offset between the occurrences of two timing description events.

ExecutionOrderConstraints are used to specify the order of execution of executable entities and ExecutionTimeConstraints are used to specify minimum and maximum execution time constraints of executable entities.

### **AUTOSAR Timing Views**

The AUTOSAR methodology is subdivided into well-defined process steps. Furthermore, the methodology defines all artifacts needed by and provided for each process step. The AUTOSAR timing extension specification groups

the timing related methodology steps by boundary in five views called *Vfb-Timing*, *SwcTiming*, *SystemTiming*, *BswTiming* and *EcuTiming*.

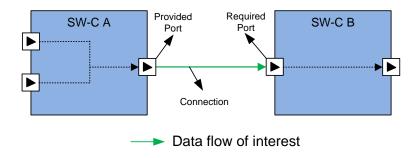

**VfbTiming**: A key concept of AUTOSAR is the Virtual Functional Bus (VFB). The VFB abstracts all communication layers encapsulating the underlying architecture of the ECUs and network topology. The concrete implementation of the VFB on an ECU is the RTE. At the modeling level, connections between the ports of the SW-Cs are modeled by means of the so-called connectors.

This view deals with timing information at a logical level, and is related to the interaction of the software components. End-to-end timing constraints can be captured in this view, allowing an early formalization of timing constraints.

The physical distribution of the software components is not considered in this view. A further restriction of the *VfbTiming* view is the fact that each component is treated as black-box, which means the internal behaviour is not considered. Thus, VFB timing description only refers to ports and connections of software components as depicted in Figure 2.4.

Figure 2.4: Virtual Functional Bus Timing

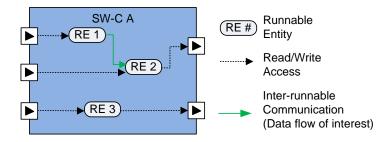

**SwcTiming:** The SwcTiming view is used to capture timing information related to the internal behavior (SwcInternalBehavior) of atomic software components. The internal behavior of an atomic software component is modeled

Figure 2.5: Software Component Timing

using the so-called Runnable Entities (RE) element as depicted in Figure 2.5.

Thus, this view is useful for specification engineers that are interested in the internal behavior of the atomic SW-C represented as black boxes in the Vf-bTiming view. This can be achieved by referring to the activation, start, and termination of the execution of runnable entities.

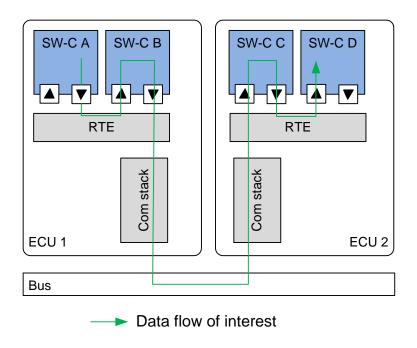

**SystemTiming:** In contrast to the VfbTiming and SwcTiming views, the SystemTiming view considers additional information, such as the system topology, software deployment and signal mapping. This additional information is used as system configuration input. Based on that configuration, software components can be mapped on to ECUs with corresponding communication matrices. After the mapping step, the communication between two SW-Cs might change. It can now be either local if both SW-Cs remain on the same ECU and remote if they are mapped to different ECUs. In the latter case the communication goes over the RTE, through the BSW communication stack and the network bus (see Figure 2.6).

Figure 2.6: System Timing

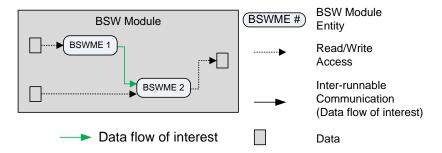

**BswTiming:** The BswTiming view addresses timing details related to the Basic software internal behavior of a single basic software module description. According to the AUTOSAR methodology, a BSW module description is generated for each BSW module during the ECU configuration phase. BswTiming is similar to SwcTiming (see Figure 2.7) except for the fact that it deals with the BSW module entities (BSWME) instead of dealing with SW-C internal behavior. Therefore analogously, BswTiming focuses on the activation, start and end of the execution of the BSW module entities.

Figure 2.7: Basic Software Timing

**EcuTiming:** The EcuTiming view addresses the timing description of all software component instances deployed on a specific ECU. Additionally, ECU related interaction is considered including bus communication and so forth. This view is comparable to the SystemTiming view except for that the focus lies on one specific ECU. The information is attached to the ECU configuration description, which comprises information containing ECU related extract from the system configuration. Figure 2.8 shows an example data flow in the ECUTiming view.

Figure 2.8: ECU Timing

## 2.2.3 Timing Modeling with TADL2

The Timing Augmented Description Language 2 (TADL2) [80] is an outcome of the ITEA2 <sup>1</sup> project TIMMO-2-USE [49]. TADL2 is an extension of Timing Augmented Description Language (TADL), which was defined in the TIMMO project [90].

<sup>&</sup>lt;sup>1</sup>ITEA is the EUREKA Cluster programme supporting innovative, industry-driven, pre-competitive R&D projects in the area of Software-intensive Systems & Services (SiSS). (https://itea3.org/)

The goal of these projects was to master different types of timing requirements, and deal with dynamic behavior of complex real-time automotive systems throughout the different phases of the design process. TADL2 differs from TADL in numerous ways: it introduces a clear semantic and adds new concepts for multiple time bases, symbolic time expression and probabilistic timing. In fact, the first version of the AUTOSAR timing model was defined based on TADL, and during TIMMO-2-USE, a harmonization took place between TADL2 and the AUTOSAR timing extensions.

Moreover, TADL2 defines a set of basic and derived timing constraints in hand with their syntax and semantic to avoid unambiguous interpretation. These syntax and semantic definitions are complemented with a metamodel. It introduces the notion of event occurrences in a running or simulated system to specify the timing properties. These events reference to discrete observable events or event chains of the system under investigation.

#### **Event Occurrences and Event-Chains**

Any form of state change in a running system that can be constrained with respect to time is represented as an event (*Event*). The event takes place at distinct points in time, and these points are called *occurrences* of the event. This means, a running system can be observed by identifying the forms of state changes that need to be monitored. The times when the changes occur can then be logged for each observation point.

An event chain (*EventChain*) is a container for a pair of events, that must be causally related.

This notion of observation also applies to a hypothetical predicted run of a system or a system model. From a timing perspective, the only information that needs to be in the output of such a prediction is a sequence of times for each observation point, indicating the times at which each event is predicted to occur.

In system models, events appear syntactically as names indicating the state changes of interest. Semantically, an event name is a variable standing for some statically unknown set of occurrences. Events represent state changes that can be observed when a system is executed, or simulated, or perhaps only mathematically predicted.

In the TADL2 semantics, an occurrence is a *timestamp* expressed using a real value. However, for more complex timing constraints, TADL2 also makes use of an additional information to specify an occurrence.

A color annotation can also be used. The color can be set by the producer of an event, and may be utilized during the verification process to identify

| TADL2 Notation        | Description                                           |

|-----------------------|-------------------------------------------------------|

| $a \wedge b$          | constraint a and constraint b are both true           |

| $a \Rightarrow b$     | a is false or a and b are both true                   |

| $a \Leftrightarrow b$ | a and b have the same truth value                     |

| $\forall x : c$       | c is true for all possible values of x                |

| $\exists x : c$       | c is true for at least one value of x                 |

| X                     | number of elements in set $X$                         |

| $X \subseteq Y$       | all elements in X are also in Y                       |

| $\forall x \in Y : c$ | for each x in Y, c is true                            |

| $\exists x \in Y : c$ | there is an x in Y such that c is true                |

| $X \leq Y$            | X is a subsequence of Y                               |

| $x \le y$             | x occurred earlier than y                             |

| x = Y(i)              | x is the element number $i$ in $Y$ counting from zero |

|                       | set of all occurrences between smallest and           |

|                       | greatest occurrences in X                             |

| $\lambda([X])$        | the length of the continuous intervals in $X$         |

| $\lambda(X)$          | the total length of all continuous intervals in $X$   |

Table 2.1: Notation used in the definition of the TADL2 semantics

related occurrences. Colors are drawn from some abstract, possibly infinite types whose only restriction is that it must support an equality test on its values. Thus, an event occurrence can also be semantically expressed using a (timestamp, color) pair, although in some contexts the color information might not be necessary.

Table 2.1 gives a list of operators used in the TADL2 notation. Syntactic and semantic objects like events, constraints and time are referenced by simple variable names such as "c" for constraint, "x" for an event occurrence, or "Y" for a set or sequence of event occurrences.

The TADL2 provides a large set of constructs that can be used to constrain time occurrence of events. These constructs basically specify the restrictions for:

- recurring delays between a pair of events,

- repetition of a single event,

- and synchronicity of a set of events.

### ArithmeticExpression and TimingExpression

An Arithmetic Expression, denoted by aexp, is a term built from literals, arithmetic variables and arithmetic operators. It stands for a value in a set of real

numbers extended with positive and negative infinity. The grammar notation used here is the standard BNF form, with keywords in boldface and non-terminal symbols written using lower-case names.

A *TimingExpression* is identical to an arithmetic expression. However, its grammar is extended to allow expressions to use alternative time bases and a variety of time units.

#### **TADL2** constraints

The concepts defined by TADL2 were taken as the basis for our approach for dynamic assertion-based verification defined in Chapter 5. This section will only highlight some of the timing constraints defined by the TADL2. A more detailed description of the timing constraints chosen for our approach will be given in Chapter 5.

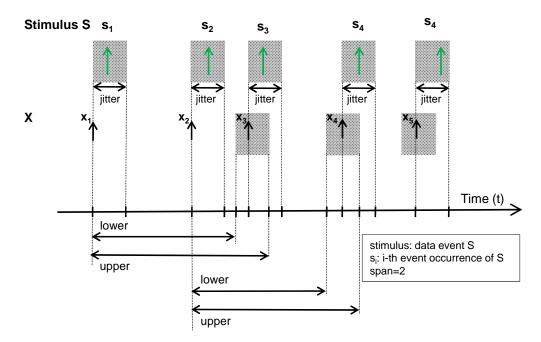

Basically, TADL2 defines a bunch of basic and complex forms of timing constraints. Some of the basic timing constraints are for instance the so-called *RepeatConstraints* and *DelayConstraints*. Most of the complex timing constraints can be expressed as a composition of other constraints. Examples of such complex timing constraints are the so-called *SynchronizationConstraint* and the *SporadicConstraint*.

Moreover, one basic attribute used for the definition of the timing constraints is the so-called *span* attribute. The *span* attribute is used to define the index of the correlated event occurrences.

The following descriptions of timing constraints are unchanged excerpts from [80]. Furthermore, the shaded areas in the respective figures highlight the event occurrences that are subject to the constraint specification.

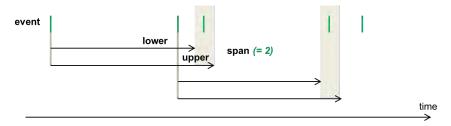

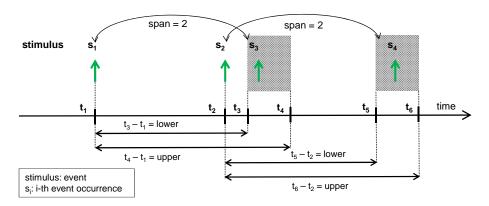

### The RepeatConstraint

A RepeatConstraint describes a repeated distribution of occurrences of a specific event. The semantic and attributes of this timing constraint are shown in Table 2.2: This constraint defines the basic notion of repeated occurrences. For a span attribute equal to 1 and for identical lower and upper attributes, the accepted behavior must be strictly periodic. Further, if the *span* value is 1 but the value of *lower* is strictly smaller than the value of *upper*, then the accepted behavior may deviate from a periodic one, making the time window within which each event occurrence may appear as wide as *upper – lower* time units. For a span value greater than 1 the constraint should be applied to each span+1 event occurrence, but places no restriction on the distances within shorter sequences [80].

|            | RepeatConstraint                                                                       |

|------------|----------------------------------------------------------------------------------------|

| Attributes | event: Event                                                                           |

|            | lower: TimingExpression                                                                |

|            | upper: TimingExpression                                                                |

|            | span: int                                                                              |

| Semantic   | $\forall X \leq event :  X  = span + 1 \Rightarrow lower \leq \lambda([X]) \leq upper$ |

Table 2.2: Semantic definition of the TADL2 RepeatConstraint.

Figure 2.9 depicts a set of event occurrences satisfying a RepeatConstraint with span of 2. The corresponding TADL2 formula can be expressed as follows:  $\forall X \leq event : |X| = 3 \Rightarrow lower \leq \lambda([X]) \leq upper$ , where the values of the attributes lower and upper are to be defined. |X| denotes the number of elements in the sub-sequence X of event occurrences and  $\lambda([X])$  denotes the length of the time interval in X. As it can be seen in the figure, only the

Figure 2.9: A set of event occurrences satisfying a RepeatConstraint with span of 2

last event occurrence in the sub-sequence X is constrained. Furthermore, the timing point of that occurrence can be referred to as  $\lambda[X]$ .

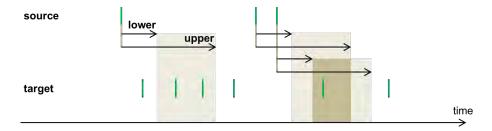

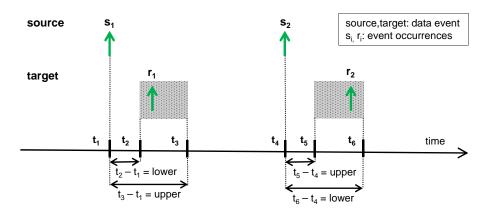

### The DelayConstraint

Looking at the communication between two components (a source and a target), a DelayConstraint specifies timing bounds between an event occurrence at the source and a corresponding event occurrence at the target, so that each event occurrences at the source must be matched by an event occurrence at the target [80].

|            | DelayConstraint                                                             |

|------------|-----------------------------------------------------------------------------|

| Attributes | source: Event                                                               |

|            | target: Event                                                               |

|            | lower: TimingExpression                                                     |

|            | upper: TimingExpression                                                     |

| Semantic   | $\forall x \in source : \exists y \in target : lower \leq y - x \leq upper$ |

Table 2.3: Semantic definition of the TADL2 DelayConstraint.

Figure 2.10: A set of event occurrences satisfying a DelayConstraint [80]

This notion of delay is entirely based on the duration between source and target occurrences. One-to-many and many-to-one source-target patterns are also possible. Figure 2.10 shows an example of a set of events satisfying a DelayConstraint. The formal definition on the DelayConstraint can be seen in Table 2.3.

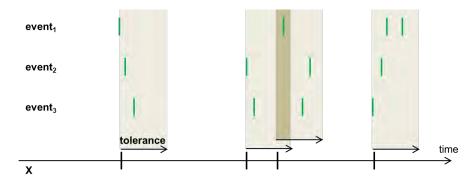

#### The SynchronizationConstraint

A SynchronizationConstraint describes how tightly the occurrences of a group of events shall follow each other. This form of timing constraint only speci-

|            | SynchronizationConstraint                                           |

|------------|---------------------------------------------------------------------|

| Attributes | event: Event[2*]                                                    |

|            | tolerance: TimingExpression = infinity                              |

| Semantic   | $\exists X : \forall i : DelayConstraint(X, event_i, 0, tolerance)$ |

|            | $\land DelayConstraint(event_i, X, -tolerance, 0)$                  |

Table 2.4: Semantic definition of the TADL2 SynchronizationConstraint. [80]

fies a time frame or tolerance window of each occurrence of a group of events. The length of the tolerance window is specified by the tolerance attribute.

Figure 2.11: A set of target event occurrences satisfying a SynchronizationConstraint. Overlapping tolerance windows and multiple event occurrences [80]

Figure 2.11 shows a generic example of a group of event occurrences which satisfy a SynchronizationConstraint. As shown in the figure, events may oc-

cur multiple times within the same tolerance window and the windows may also overlap and thus share event occurrences. [80]

The formal definition on the SynchronizationConstraint can be seen in Table 2.4. As it can be seen in the table, the SynchronizationConstraint is a variant of the DelayConstraint that adds a tolerance attribute and changes the target event link into a list of events. A system behavior satisfies a SynchronizationConstraint if and only if there is a set of times X such that for all events *event<sub>i</sub>*, the same system behavior concurrently satisfies

$DelayConstraint(X, event_i, 0, tolerance)$  and  $DelayConstraint(event_i, X, -tolerance, 0)$ .

## 2.2.4 Testing and Verification

The main purpose of a verification task is to check whether or not a model or system is consistent with respect to its specification or requirement. Furthermore, verification activities are performed several time during the design phase according to the verification plan.

In the context of the verification of electronic design, a multitude of approaches have been proposed and are being applied in the EDA industry. Basically, these approaches can be sorted in two main categories. Some of them are static and others are dynamic.

Static verification techniques perform a thorough analysis on a certain aspect of the design model. Static verification characterizes verification techniques, where the design model under verification is investigated in an analytical way by means of formal specifications. Theorem proving, Equivalence Checking and Model Checking [13, 59] belong to this category.

Dynamic verification is usually associated with the simulation of the design model at a certain abstraction level. Although simulation is not enough to prove consistency of formal entities, as it is the case for formal verification methods, it can be applied in situations where the model under investigation cannot be formalized in a way as requested by the respective formal method. Further, simulation-based based verification is typically performed using a testbench as simulation environment. There are several methodologies specifying how to build such a testbench [20, 74, 7, 8].

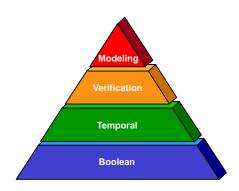

The thesis focuses on dynamic verification in the context of Model-Based Design (MBD). Throughout the different phases of MBD, several levels of modeling of both the plant and controller are required, in order for the functional behavior of the model to match that of the generated code [10].

To reduce development time and introduce technologies faster to the market, many companies have been turning more and more to MBD. In MBD, the development process centers around a system model, from requirements capture and design to implementation and test.

Traditional design paradigms in the automotive industry often delay control system design until late in the process. In some cases, control system design requires several costly hardware iterations. To reduce costs and improve time to market, emphasis is placed on modeling and simulation as early as possible in the development process [97].

Different steps are supported by a variety of approaches from Model-In-the-Loop (MIL), to Software-In-the-Loop (SIL), HIL, Rapid-Control-Prototyping (RCP), or Component-In-the-Loop (CIL). Each process is used to address different stages of the development process. The first step is the simulation, where neither the controller nor the plant operates in real-time. This step, usually used toward the beginning of the process, allows engineers to study the performance of the system and design the control algorithm(s) in a virtual environment, running computer simulations of the complete system, or subsystem.

RCP provides the engineer with the ability to quickly test and iterate their control strategies on a real-time computer with actual hardware. The control strategy is simulated in real-time on a processor that augments or replaces the real embedded controller, allowing the user to investigate and refine the control algorithms while operating with the real system under control. RCP is now a commonly used method to develop and test control strategies.

In the SIL phase, the actual Production Software Code is incorporated into a mathematical simulation that contains models of the Physical System. This is done to permit inclusion of software functionality for which no model(s) exists or to enable faster simulation runs.

HIL is a technique for running a mathematical simulation model of a system on a real-time computer, integrated with actual controller hardware and software, such that the controller acts as though it were integrated into the real system. This is used for testing and validation of embedded electronic controllers, prior to testing in a vehicle.

CIL is used to assess the impact of an entire system (e.g., engine plant and control) on other portions of the system (e.g., vehicle). The system to be analyzed is real hardware while the rest of the components are emulated from models.

### 2.3 Automotive Vehicle Netwoks

#### 2.3.1 Controller Area Network (CAN)

The Controller Area Network (CAN) [17, 73, 89] is an International Standardization Organization (ISO) standard. The CAN standard is a serial communications bus originally developed for the automotive industry to replace the complex wiring harness with a two-wire bus. Its domain of application ranges from high speed networks to low cost multiplex wiring. In automotive electronics, engine control units, sensors, anti-skid-systems, etc. are typically connected using a CAN bus with transmission rates ranging from 10 kbit/s up to 1 Mbit/s. The transmission rate depends on the bus segment. For instance, 1 Mbit/s can only be reached at a maximum bus length of 40 meters.

The CAN protocol has a high immunity to electrical interference, and includes sophisticated mechanisms for self-diagnosis, error-detection and error handling mechanism. These features have led to CAN's popularity in a variety of industries beyond the automotive industries, such as: marine, medical, manufacturing, and aerospace.

Furthermore, CAN is a multi-master bus with an open, linear structure with one logic bus line and equal nodes. The number of nodes is not limited by the protocol, and the bus nodes do not have a specific address. Instead, the address information is contained in the identifiers of the transmitted messages (CAN Frame), indicating the message content and the priority of the message.

Moreover, CAN supports multicasting and broadcasting. The error-detection and error handling mechanism basically consists of automatically retransmitting erroneous messages, that have been detected. Temporary errors are recovered. Permanent errors are followed by autonomous deactivation of the defect nodes. This approach therefore guarantees a system-wide data consistency.

The bus access is handled via the advanced serial communications protocol Carrier Sense Multiple Access/Collision Detection with Arbitration on Message Priority (CSMA/CD+AMP). CSMA means that each node on a bus must wait for a prescribed period of inactivity before attempting a message transmission.

In the CD+AMP communication protocol, collisions are resolved through a bit-wise arbitration, based upon a configured priority of each message in the identifier field of a CAN Frame. The higher priority identifier always wins bus access. In the following section, the structure of CAN frame will be described.

#### The CAN frame

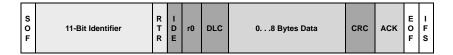

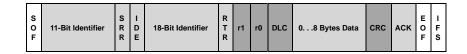

The first version of the CAN standards was the so-called Low-Speed CAN (ISO 11519). This version was intended for applications up to 125 kbit/s with a standard 11-bit identifier. The following version, ISO 11898 with the same indentifier length was later standardized in 1993. However, this version provides a transmission rate ranging from 125 kbit/s to 1 Mbit/s. The more recent amendment of the second version (ISO 11898) was published in 1995. This version introduces an extended 29-bit identifier. The ISO 11898 11-bit version is often referred to as Standard CAN Version 2.0A, while the ISO 11898 amendment is referred to as Extended CAN Version 2.0. The structure of the standard CAN frame format can be seen in Figure 2.12, while Figure 2.13 depicts the various part of the extended CAN frame format [17, 89].

Figure 2.12: Standard CAN frame with 11-Bit identifier

Figure 2.13: Extended CAN frame with 29-Bit identifier

#### **CAN Network Topology**

The CAN protocol operates on a broadcast bus. There is no built-in support for other topologies. However, third-party solutions with gateways or switches for star topologies exist [73]. In advanced applications, such as an automotive system, several CAN bus segments are interconnected using one or more gateways. A gateway is provided with software that knows which data should be forwarded between the different bus segments it is connected to.

## 2.3.2 FlexRay

FlexRay is a fast, deterministic and fault-tolerant vehicle network bus standard for automotive use. This standard was developed by a consortium of

well-known OEMs of the automotive industry. The consortium was disbanded in 2010 after the release of the actual protocol specification version 3.0. The core members of the consortium were: BMW, Bosch, Daimler-Chrysler, General Motors, Ford, NXP Semiconductors, Philips Semiconductor, and Volkswagen. In the scope of this thesis, the version 2.1 Revision A [41] was used for validation purposes.

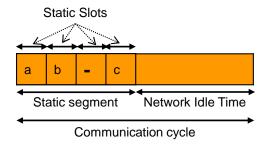

#### Communication schedule

The FlexRay protocol is based on a periodically recurring communication cycle. Within one communication cycle the standard offers the choice between two media access schemes, that is: a static Time Division Multiple Access (TDMA) scheme, and a dynamic mini-slotting based scheme referred to as Flexible Time Division Multiple Access (FTDMA). Furthermore, the configuration of a FlexRay network schedule has to be done at design time. Then, once configured the bus communication schedule cannot be changed at system run-time.

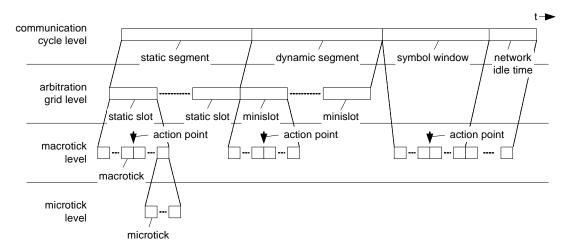

Figure 2.14: Timing hierarchy within the communication cycle [41]

The communication cycle is a fundamental notion for the media access scheme. As illustrated in Figure 2.14, the FlexRay communication cycle can be broken into four segments. The segments are the *static segment*, the *dynamic segment*, the *symbol window* and the *Network Idle Time*. Furthermore, the timing hierarchy can be decomposed in four timing hierarchy levels (see Figure 2.14).

Within the static segment, communication is arbitrated based on the TDMA scheme. Whereas FTDMA is applied in the dynamic segment to arbitrate transmission. The symbol window is a communication period within which special control information can be transmitted on the network. The network idle time is a communication-free period that concludes the communication

cycle. This period can be used by the nodes (ECUs) for synchronization or internal computation for instance.

The next lower level, the arbitration grid level, contains the arbitration grid that forms the backbone of FlexRay media arbitration. In the static segment the arbitration grid consists of consecutive time intervals, called static slots, in the dynamic segment the arbitration grid consists of consecutive time intervals, named minislots.

The arbitration grid level builds on the so-called *macrotick level* that is defined by the so-called *Macrotick*. Designated macrotick boundaries are called action points. These are specific instants at which transmissions shall start in all segments of the communication cycle. In the dynamic segment, the action point also specifies the instant at which a transmission shall end. For more detailed information about the remaining levels, please refer to [41].

#### FlexRay frame format

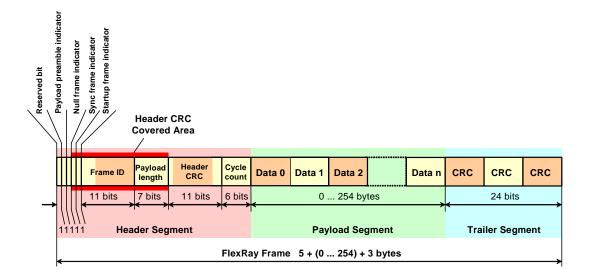

The FlexRay protocol supports a data transmission rate of up to 20 Mbit/s. Figure 2.15 depicts the structure of a FlexRay frame. As depicted in the figure, a FlexRay frame consists of three main parts. These parts are the header, the payload segment containing up to 254 bytes of data, and the Trailer segment containing CRC information of 24 bits.

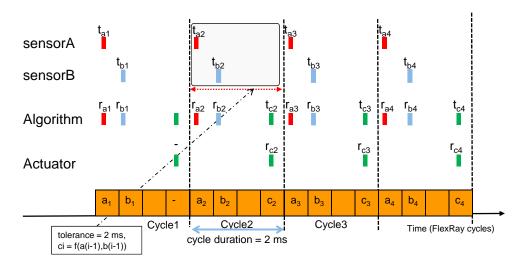

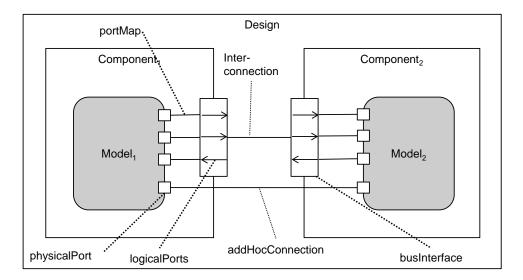

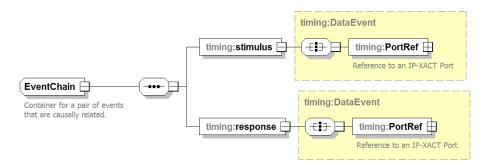

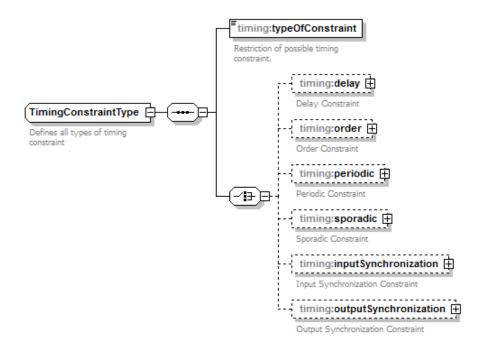

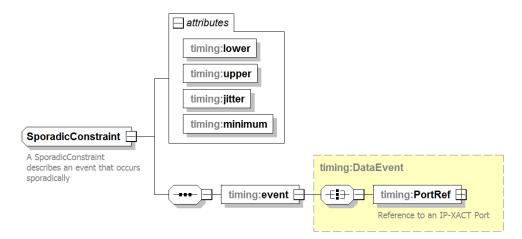

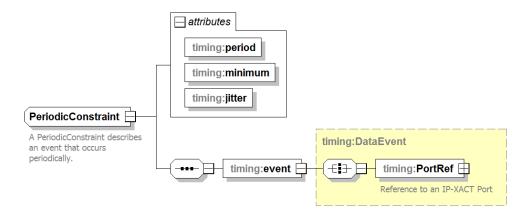

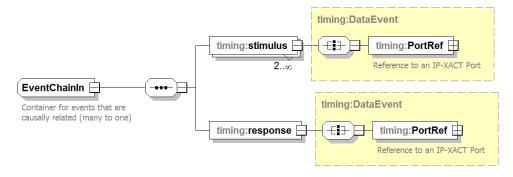

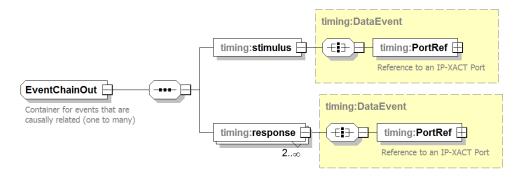

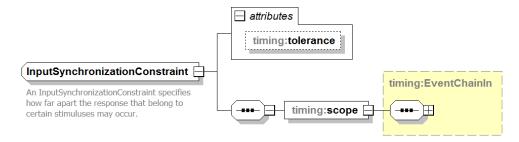

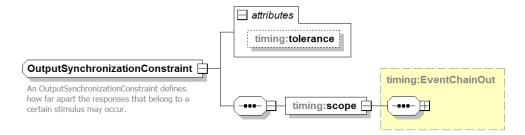

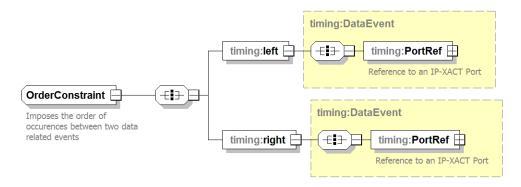

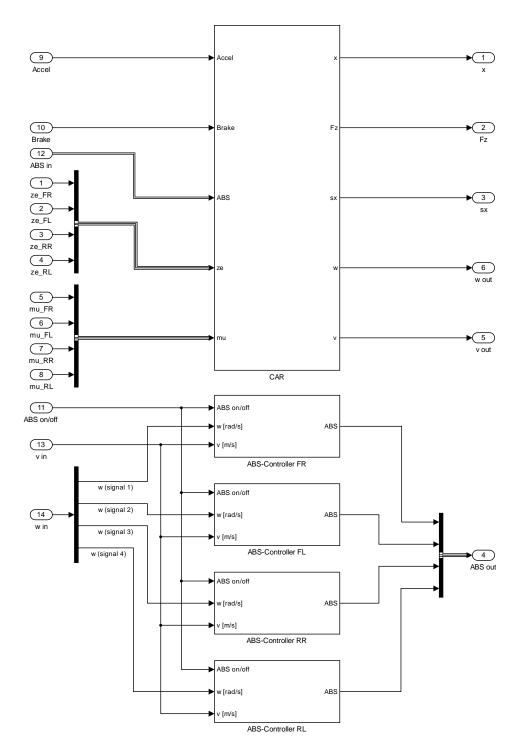

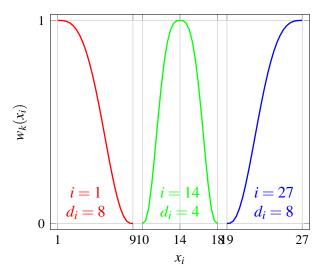

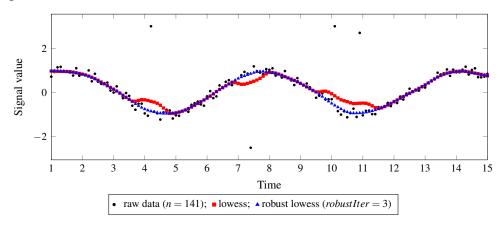

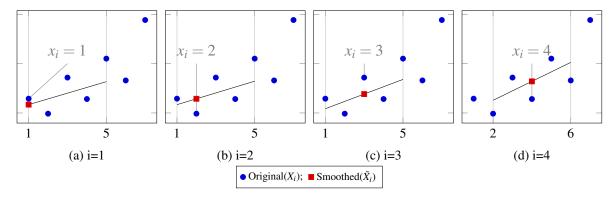

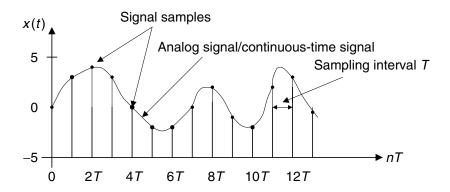

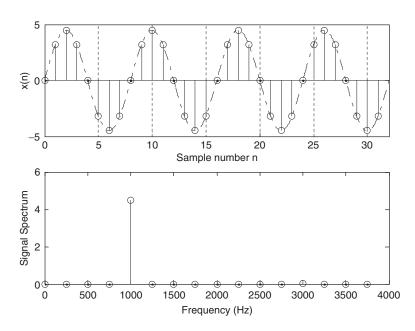

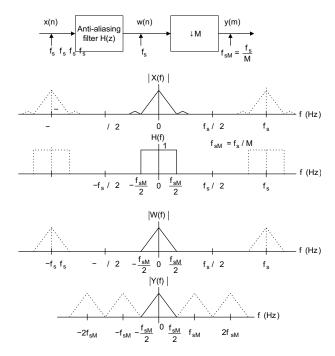

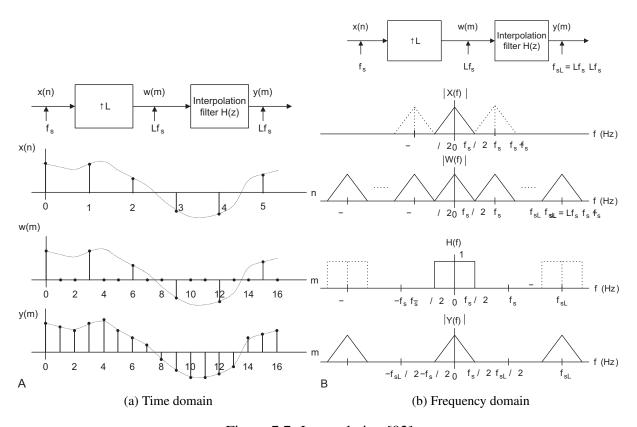

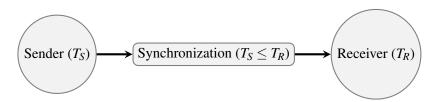

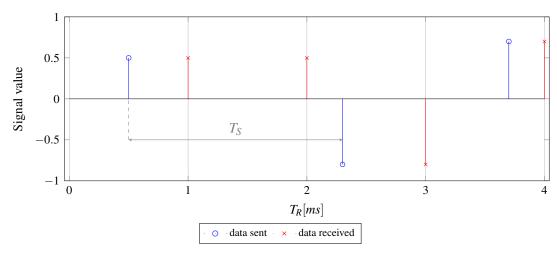

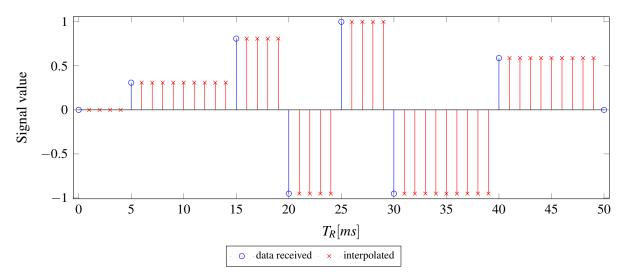

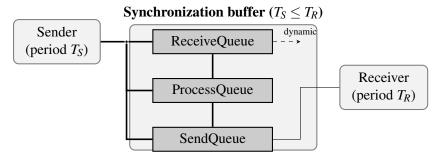

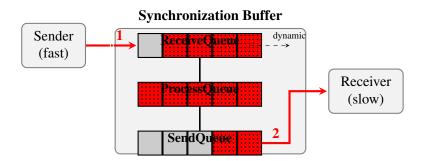

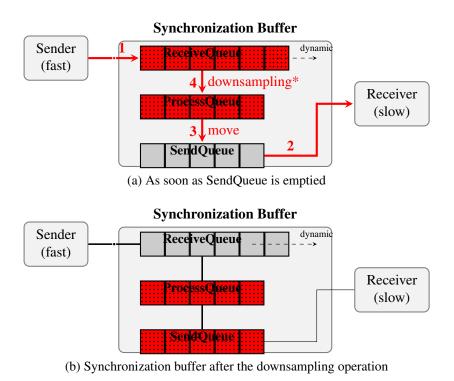

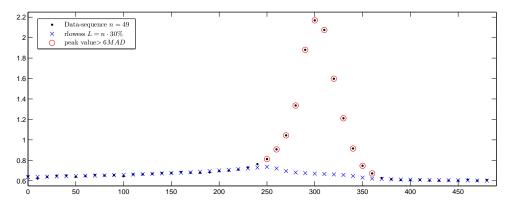

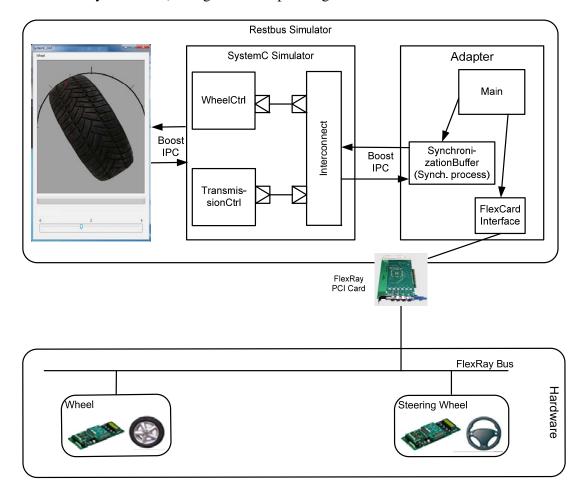

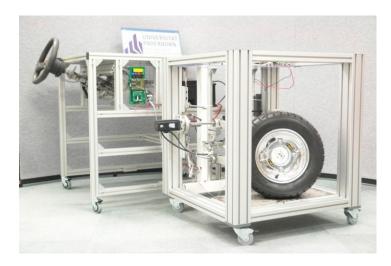

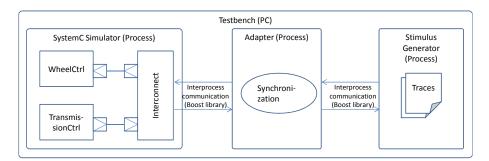

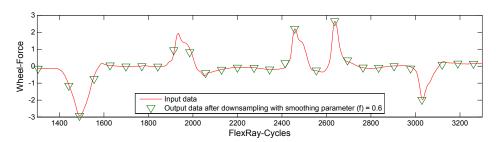

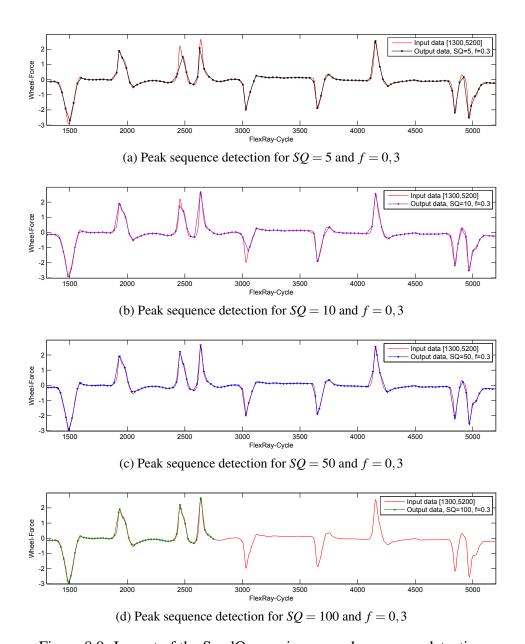

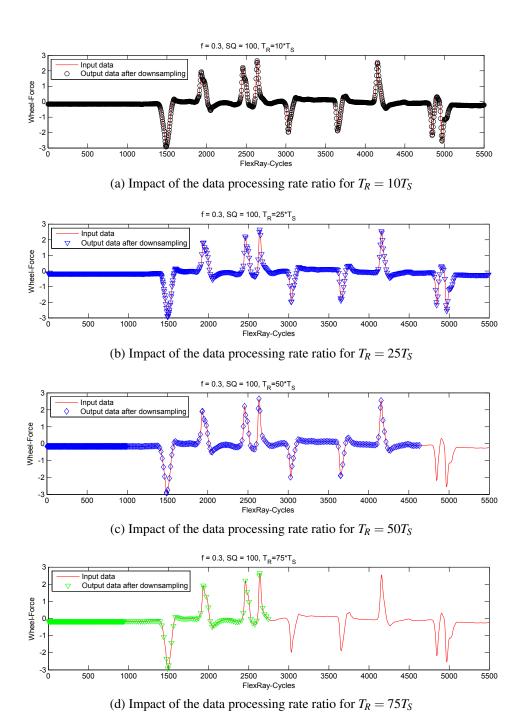

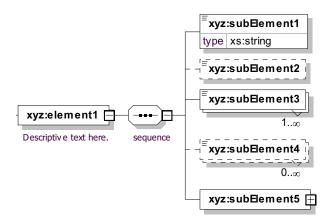

The header of 5 bytes includes the identifier of the frame and the length of the data payload. The use of the identifier field allows to move a functionality implemented by a software component, that generates a frame X, from one ECU to another ECU without having to change the configuration of the receiving ECU. The configuration of the sending node needs to be modified since frame are dedicated to specific communication slots.