# **Generating Processors from Specifications of Instruction Sets**

---

## **Dissertation**

A thesis submitted to the

**Faculty of Electrical Engineering, Computer Science, and Mathematics**

of the

**University of Paderborn**

in partial fulfillment of the requirements for the degree of

**Doctor rerum naturalium (Dr. rer. nat.)**

by

**Ralf Dreesen**

Paderborn, September 2011

**Supervisor:**

Prof. Dr. Uwe Kastens (University of Paderborn)

**Reviewer:**

Prof. Dr. Uwe Kastens (University of Paderborn)

Prof. Dr. Marco Platzner (University of Paderborn)

Prof. Dr.-Ing. Ulrich Rückert (University of Bielefeld)

**Additional members of committee:**

Prof. Dr. Franz Rammig (University of Paderborn)

Dr. Matthias Fischer (University of Paderborn)

**Submitted:** 15.09.2011

**Examination:** 6.12.2011

**Published:** 9.12.2011

# Acknowledgments

I would like to use this opportunity to show my gratitude to all people who supported me during this thesis.

First of all, I would like to thank my adviser Professor Uwe Kastens, for the support and guidance he gave me and which significantly contributed to the quality of this thesis. Professor Kastens allowed me great latitude in the design of the system and has shown me the right direction during numerous fruitful discussions. I want to thank Professor Ulrich Rückert and Professor Marco Platzner for their interest in my thesis and reviewing. In addition, I would like to thank Professor Rückert for the constructive cooperation with his research group.

I am obliged to many of my colleagues, who accompanied me in the past years. In particular, I owe earnest thankfulness to Dr. Michael Thies for many intensive discussions during coffee break. Special thanks go to Thorsten Jungeblut for helping me in the area of hardware design and giving me access to the respective infrastructure.

I would like to show my gratitude to Friederike Sudholt and Paul Jaessing for proof reading, in particular as the subject is far away from their profession. My personal thanks go to Johanna Sudholt, who has supported me throughout this thesis, as she has done for the past 12 years. I am thankful to my parents for giving me advice and virtues for my life.

Paderborn, 15.09.2011

Ralf Dreesen

# Abstract

Most digital systems include microprocessors, as they are very flexible. Some of these microprocessors are tailored to the respective area of application, to optimize execution time and power consumption. An efficient development of such processors necessitates convenient development tools.

This thesis contributes a *specification language* called ViDL and two *generators* for rapid development of application specific processors. A developer specifies an instruction set in ViDL, then generates an instruction set simulator as well as a microarchitectural processor implementation from that specification. ViDL provides powerful concepts to specify a wide range of instruction sets at a high level of abstraction. For instance, the pipeline and its control are not defined by the developer, but contributed automatically by the processor generator. To demonstrate the power of ViDL, real world instruction sets, such as MIPS, ARM, Power and CoreVA have been specified. A ViDL specification is very similar to instruction set manuals, which allows for rapid formalization (e.g. one day for MIPS).

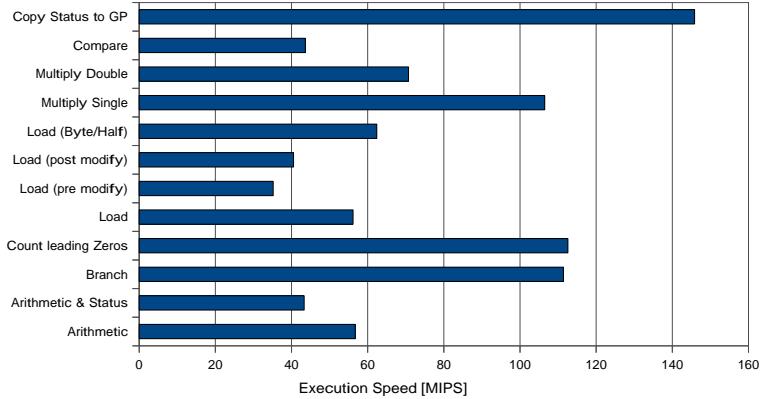

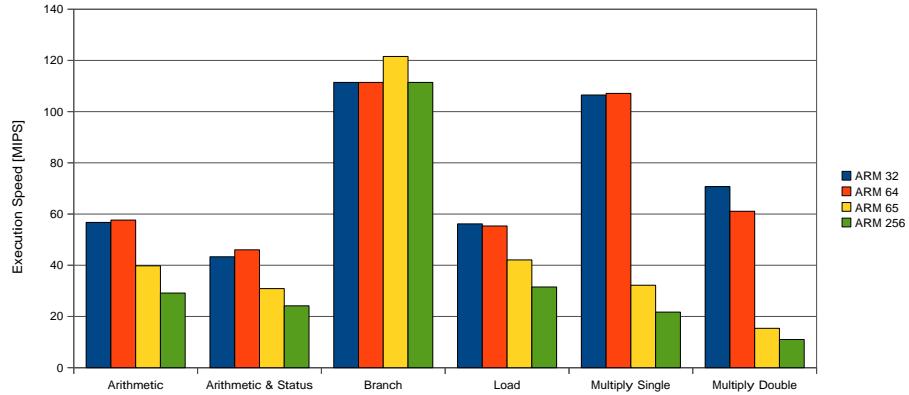

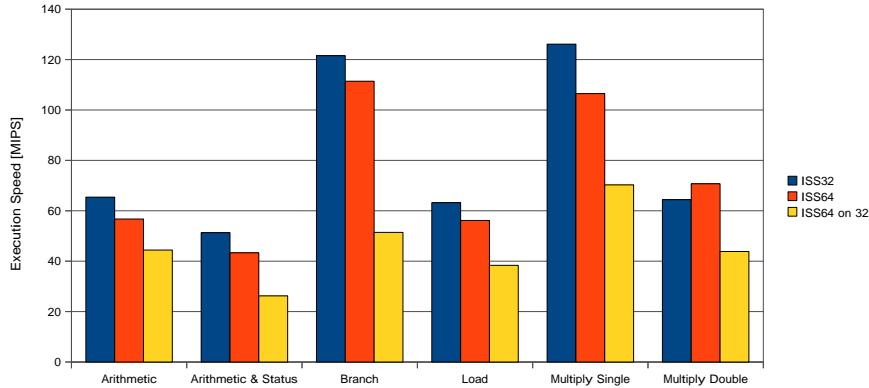

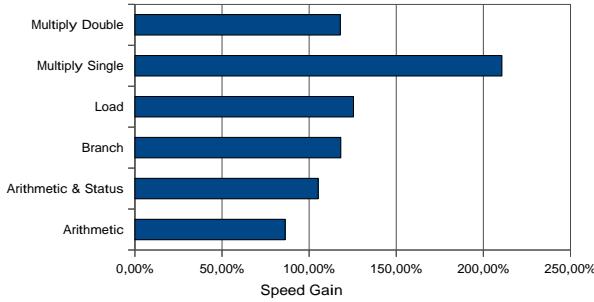

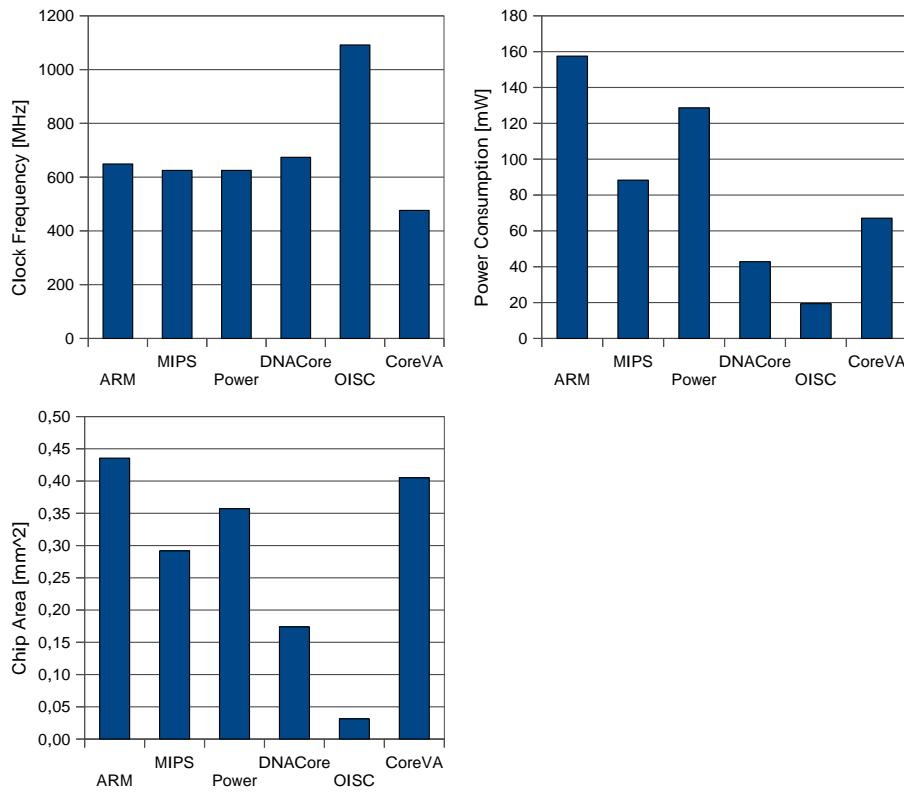

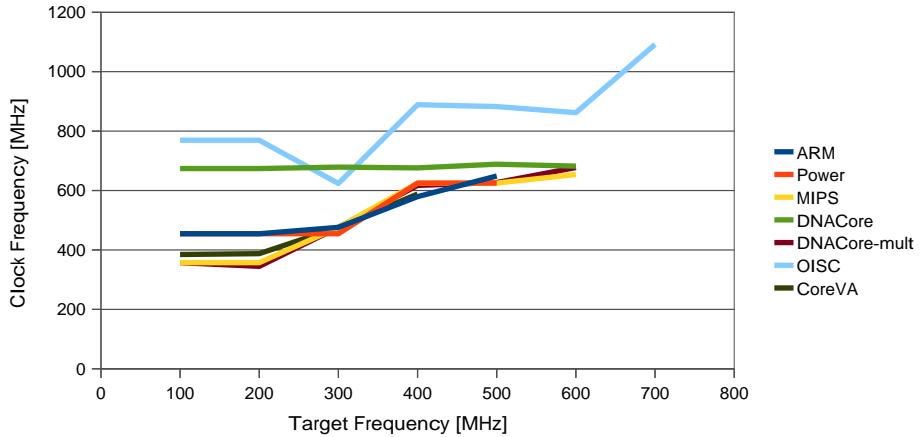

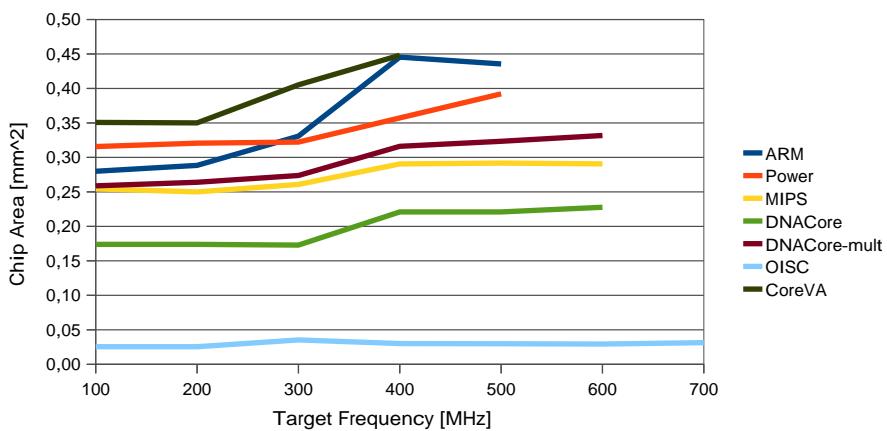

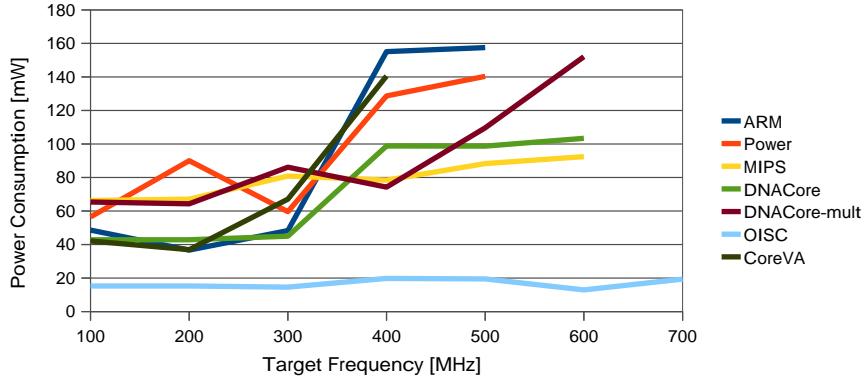

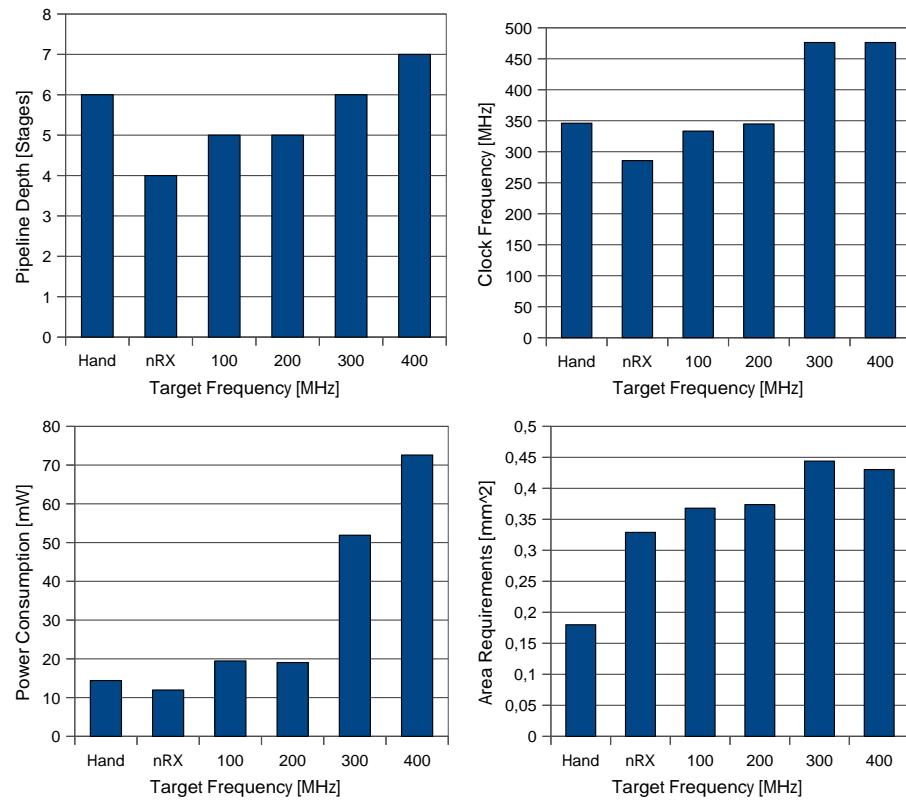

The generated high speed simulators execute 60 million instructions per second (Mips) on average with a peak performance of 140 Mips. The generated processor implementations yield a clock frequency of 600 MHz on a 65nm ST Microelectronics low power technology. The processor generator produces a pipelined  $n$ -stage microarchitecture, where  $n$  is automatically derived from a user defined target clock frequency (e.g. 600 MHz) and instruction semantics. As a result, different microarchitectural implementations (e.g. 2-stage and 6-stage) can be generated at no extra effort. All processors and the simulator are guaranteed to be consistent, as they are generated from the very same specification. There is no way that a ViDL user can break this consistency, neither by mistake nor by intention.

To prove the fitness of ViDL for *design space exploration (DSE)* and *instruction set extension (ISE)*, a new application specific processor has been developed as part of this thesis. The processor called DNACore is based on MIPS and includes a sophisticated SIMD instruction set extension to accelerate the Smith-Waterman algorithm. The algorithm is used in bioinformatics to align DNA, RNA and protein sequences. The generated processor is freely programmable and achieves a throughput of 2.6 billion cell updates per second (GCUPS) at an estimated power consumption of only 0.05 W.

# Zusammenfassung

Viele digitale Systeme beinhalten Mikroprozessoren, weil sie aufgrund ihrer Programmierbarkeit sehr flexibel einsetzbar sind. Einige dieser Mikroprozessoren sind auf den jeweiligen Anwendungsbereich zugeschnitten, um die Ausführungs geschwindigkeit von Programmen zu steigern und Energie zu sparen. Eine effiziente Entwicklung solcher anwendungsspezifischer Prozessoren bedarf geeigneter Entwicklungswerkzeuge.

Dazu trägt diese Arbeit, sowohl durch die Spezifikationssprache ViDL, als auch durch zwei Generatoren zur schnellen Entwicklung anwendungsspezifischer Prozessoren bei. Ein Entwickler spezifiziert einen Instruktionssatz in ViDL und generiert daraus einen Simulator, als auch eine mikroarchitektonische Implementierung eines Prozessors. ViDL verfügt über mächtige Konzepte, um eine Vielzahl an Instruktionssätzen auf einem hohen Abstraktionsniveau zu spezifizieren. So werden zum Beispiel die Pipeline und ihre Kontrolle nicht durch den Entwickler definiert, sondern automatisch durch den Generator aus dem Instruktionssatz hergeleitet. Um die praktische Anwendbarkeit von ViDL zu demonstrieren, wurden reale Instruktionssätze wie ARM, MIPS, Power und CoreVA spezifiziert und entsprechende Simulatoren und Prozessoren generiert. Eine ViDL Spezifikation ist der Notation in Instruktionssatz-Handbüchern sehr ähnlich und erlaubt deshalb eine schnelle Formalisierung (z.B. einen Tag für MIPS).

Der generierte Simulator führt durchschnittlich 60 Millionen Instruktionen pro Sekunde (Mips) aus, mit einer Spitzengeschwindigkeit von 140 Mips. Generierte Prozessoren erreichen eine Geschwindigkeit von ca. 600 MHz für eine 65 nm STMicroelectronics low power Technologie. Der Prozessorgenerator erzeugt eine  $n$ -stufige Pipeline, wobei  $n$  automatisch anhand einer vom Benutzer gegebenen Zielfrequenz ermittelt wird (z.B. 600MHz). Folglich können ohne zusätzlichen Aufwand verschiedenste mikroarchitektonische Implementierungen generiert werden. Alle Prozessoren und der Simulator sind garantiert konsistent, weil sie vollautomatisch aus derselben Spezifikation erzeugt werden. Ein ViDL Entwickler kann diese Konsistenz nicht verletzen, weder unbeabsichtigt noch vorsätzlich.

Die Eignung ViDLs zur Exploration von Entwurfsräumen und Erweiterung von Instruktionssätzen wurde durch die Entwicklung eines anwendungsspezifischen Prozessors im Rahmen dieser Arbeit nachgewiesen. Der Prozessor namens DNACore basiert auf MIPS und wurde durch einen Satz anspruchsvoller SIMD Instruktionen erweitert, die die Ausführung des Smith-Waterman Algorithmus erheblich beschleunigen. Der Algorithmus wird in der Bioinformatik eingesetzt,

um DNS-, RNA- und Proteinsequenzen zu analysieren. Der generierte Prozessor ist frei programmierbar und erreicht einen Durchsatz von 2.6 giga cell updates per second (GCUPS) bei einer Leistungsaufnahme von nur 0.05 W

# Contents

|          |                                                |           |

|----------|------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                            | <b>15</b> |

| 1.1      | Motivation . . . . .                           | 15        |

| 1.2      | Overview . . . . .                             | 17        |

| 1.3      | Processor aspects . . . . .                    | 18        |

| 1.4      | Scientific contributions . . . . .             | 19        |

| 1.4.1    | Language concepts . . . . .                    | 19        |

| 1.4.2    | Generation methods . . . . .                   | 20        |

| 1.5      | Processor implementations . . . . .            | 21        |

| 1.6      | System overview . . . . .                      | 22        |

| 1.7      | Evolution of ViDL and its generators . . . . . | 23        |

| 1.8      | Areas of expertise . . . . .                   | 24        |

| <b>2</b> | <b>Fundamentals</b>                            | <b>27</b> |

| 2.1      | Instruction set architectures . . . . .        | 27        |

| 2.1.1    | ARM . . . . .                                  | 28        |

| 2.1.2    | MIPS . . . . .                                 | 29        |

| 2.1.3    | OISC — One instruction set computer . . . . .  | 30        |

| 2.2      | Design scenarios . . . . .                     | 30        |

| 2.3      | Domain specific languages . . . . .            | 32        |

| 2.4      | Compilation methods . . . . .                  | 34        |

| 2.4.1    | Front-end . . . . .                            | 35        |

| 2.4.2    | Middle-end . . . . .                           | 36        |

| 2.4.3    | Back-end . . . . .                             | 36        |

| 2.4.4    | Compiler framework . . . . .                   | 37        |

| 2.5      | Type systems . . . . .                         | 37        |

| 2.5.1    | Subtyping . . . . .                            | 38        |

| 2.5.2    | Tuples . . . . .                               | 38        |

| 2.5.3    | Signatures . . . . .                           | 38        |

| 2.5.4    | Polymorphic types . . . . .                    | 39        |

| 2.5.5    | Polymorphic functions . . . . .                | 39        |

| 2.6      | Term rewriting systems . . . . .               | 39        |

| 2.6.1    | Term . . . . .                                 | 39        |

| 2.6.2    | Rewrite rules . . . . .                        | 40        |

| 2.6.3    | Termination and confluence . . . . .           | 40        |

|          |                                                   |           |

|----------|---------------------------------------------------|-----------|

| 2.7      | Microarchitecture . . . . .                       | 40        |

| 2.7.1    | Storages . . . . .                                | 41        |

| 2.7.2    | Datapath . . . . .                                | 42        |

| 2.7.3    | Pipeline . . . . .                                | 43        |

| 2.7.4    | Execution order . . . . .                         | 44        |

| 2.7.5    | Forwarding . . . . .                              | 44        |

| 2.7.6    | Interlocking . . . . .                            | 45        |

| 2.7.7    | Branch prediction . . . . .                       | 46        |

| <b>3</b> | <b>Related approaches</b>                         | <b>49</b> |

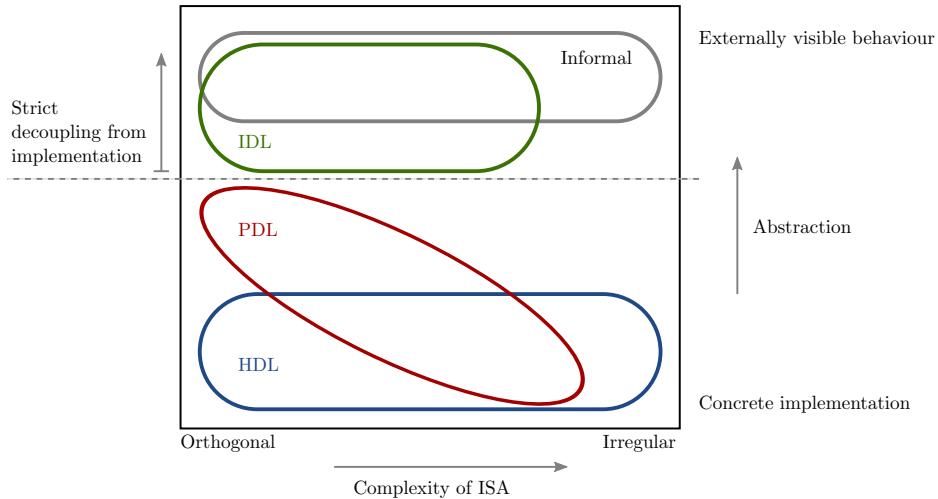

| 3.1      | Taxonomy of ISA specification languages . . . . . | 49        |

| 3.2      | Notation in ISA manuals . . . . .                 | 51        |

| 3.2.1    | ARM manual . . . . .                              | 52        |

| 3.2.2    | Review . . . . .                                  | 52        |

| 3.3      | ISP . . . . .                                     | 53        |

| 3.3.1    | State . . . . .                                   | 53        |

| 3.3.2    | Aliases . . . . .                                 | 53        |

| 3.3.3    | Instruction encoding . . . . .                    | 53        |

| 3.3.4    | Activations . . . . .                             | 54        |

| 3.3.5    | Actions . . . . .                                 | 54        |

| 3.3.6    | Data-types . . . . .                              | 55        |

| 3.3.7    | Review . . . . .                                  | 55        |

| 3.4      | nML . . . . .                                     | 56        |

| 3.4.1    | State . . . . .                                   | 57        |

| 3.4.2    | Instruction set . . . . .                         | 57        |

| 3.4.3    | Modeling of instruction sets . . . . .            | 59        |

| 3.4.4    | Review . . . . .                                  | 59        |

| 3.5      | ASIP Meister/PEAS-III . . . . .                   | 61        |

| 3.6      | Lisa . . . . .                                    | 62        |

| 3.6.1    | Storages . . . . .                                | 62        |

| 3.6.2    | Instruction set . . . . .                         | 63        |

| 3.6.3    | Hardware sharing . . . . .                        | 65        |

| 3.6.4    | Pipeline . . . . .                                | 66        |

| 3.6.5    | Complexity of language . . . . .                  | 67        |

| 3.6.6    | Practical application . . . . .                   | 67        |

| 3.7      | ISDL . . . . .                                    | 69        |

| 3.8      | Expression . . . . .                              | 70        |

| 3.9      | Tensilica instruction extension (TIE) . . . . .   | 70        |

| 3.9.1    | State . . . . .                                   | 71        |

| 3.9.2    | Instruction semantics . . . . .                   | 71        |

| 3.9.3    | Hardware sharing . . . . .                        | 72        |

| 3.9.4    | Datapath scheduling . . . . .                     | 73        |

| 3.10     | DPG — Datapath generator . . . . .                | 73        |

|                                                         |            |

|---------------------------------------------------------|------------|

| <b>4 ViDL — Versatile ISA description language</b>      | <b>75</b>  |

| 4.1 A ViDL example . . . . .                            | 76         |

| 4.2 Structure of a specification . . . . .              | 78         |

| 4.3 Abstraction from microarchitecture . . . . .        | 78         |

| 4.4 Instructions . . . . .                              | 80         |

| 4.4.1 Encoding . . . . .                                | 80         |

| 4.4.2 Semantics . . . . .                               | 80         |

| 4.5 Functional concepts . . . . .                       | 81         |

| 4.5.1 Functions . . . . .                               | 82         |

| 4.5.2 Polymorphism . . . . .                            | 82         |

| 4.5.3 Closures . . . . .                                | 82         |

| 4.5.4 Recursion . . . . .                               | 83         |

| 4.5.5 Name binding . . . . .                            | 83         |

| 4.5.6 Tuples . . . . .                                  | 84         |

| 4.5.7 Vectors . . . . .                                 | 84         |

| 4.5.8 Review of concepts . . . . .                      | 85         |

| 4.6 Epsilon logic . . . . .                             | 89         |

| 4.6.1 Operating on epsilon logic . . . . .              | 90         |

| 4.6.2 Review . . . . .                                  | 90         |

| 4.7 Delays . . . . .                                    | 92         |

| 4.7.1 Causality . . . . .                               | 93         |

| 4.7.2 Review . . . . .                                  | 94         |

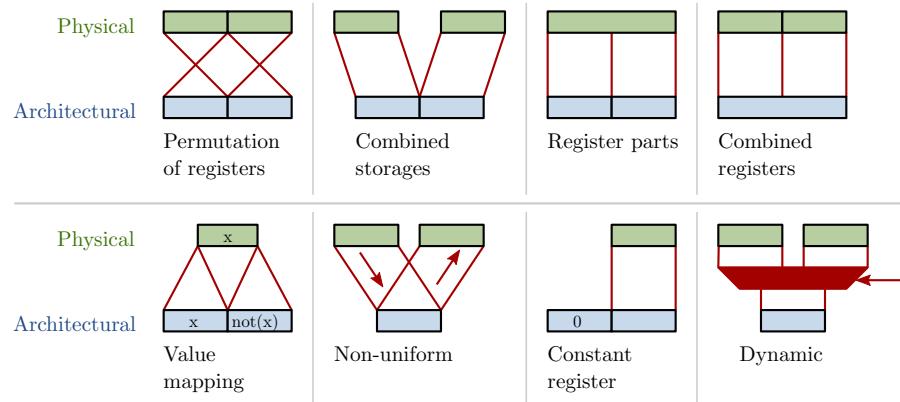

| 4.8 Architectural interfaces . . . . .                  | 95         |

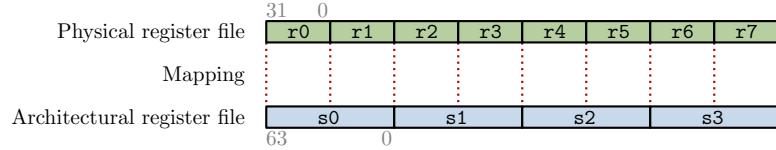

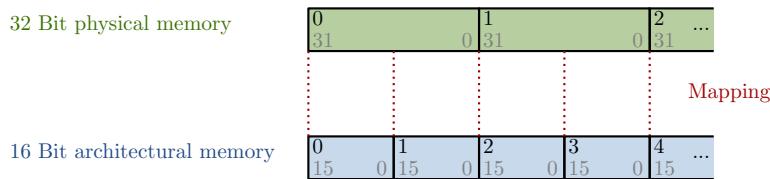

| 4.8.1 Mapping . . . . .                                 | 96         |

| 4.8.2 Review . . . . .                                  | 97         |

| 4.9 Type system . . . . .                               | 99         |

| 4.9.1 Types . . . . .                                   | 101        |

| 4.9.2 Type inference . . . . .                          | 107        |

| 4.9.3 Evaluation . . . . .                              | 111        |

| <b>5 Transfer primitives</b>                            | <b>117</b> |

| 5.1 Library . . . . .                                   | 118        |

| 5.2 Primitive . . . . .                                 | 118        |

| 5.3 Generic primitives . . . . .                        | 120        |

| 5.4 Review . . . . .                                    | 122        |

| <b>6 Design patterns</b>                                | <b>123</b> |

| 6.1 Partial memory accesses . . . . .                   | 123        |

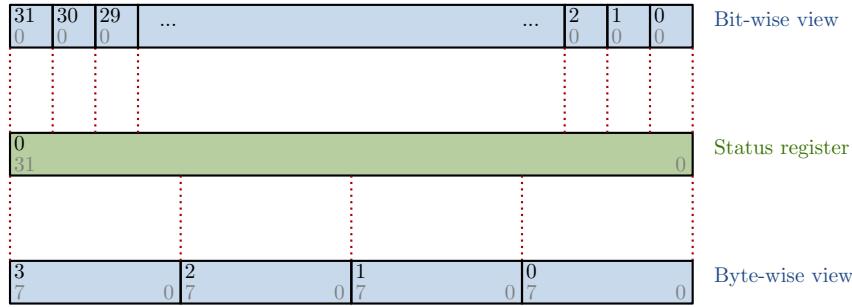

| 6.2 Status registers . . . . .                          | 125        |

| 6.3 Processor-mode sensitive registers . . . . .        | 126        |

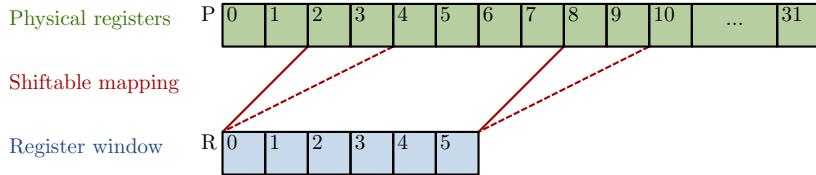

| 6.4 Register windowing . . . . .                        | 127        |

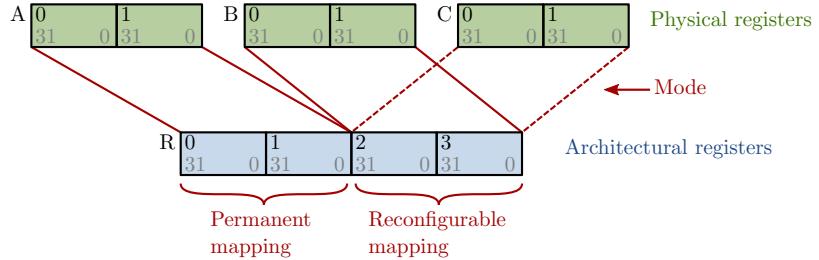

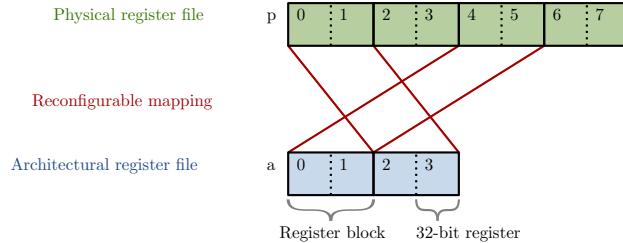

| 6.5 Dynamically reconfigurable register files . . . . . | 128        |

| 6.6 Register pairs . . . . .                            | 129        |

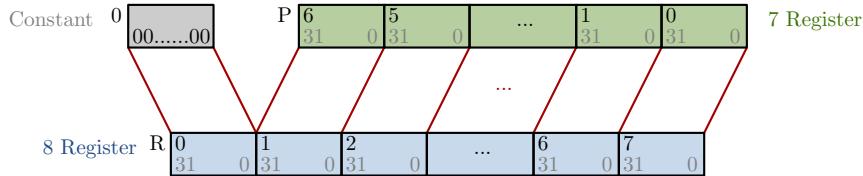

| 6.7 Constant register . . . . .                         | 130        |

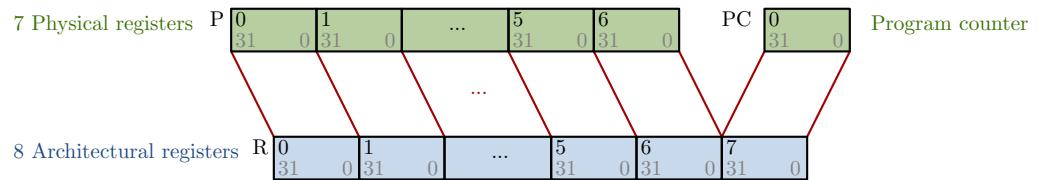

| 6.8 Embedded program counter . . . . .                  | 131        |

| 6.9 Branch . . . . .                                    | 133        |

|                                                         |            |

|---------------------------------------------------------|------------|

| 6.10 SIMD instructions . . . . .                        | 134        |

| 6.11 Conditional execution . . . . .                    | 135        |

| 6.12 Complex operand encodings . . . . .                | 136        |

| 6.13 Addressing modes . . . . .                         | 136        |

| <b>7 Generators</b>                                     | <b>139</b> |

| 7.1 Processing of ViDL . . . . .                        | 139        |

| 7.1.1 Name analysis . . . . .                           | 140        |

| 7.1.2 Optimizations . . . . .                           | 140        |

| 7.1.3 Translation of architectural interfaces . . . . . | 141        |

| 7.1.4 Analysis of instruction encoding . . . . .        | 142        |

| 7.2 Intermediate representation . . . . .               | 142        |

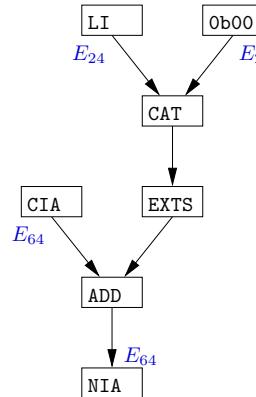

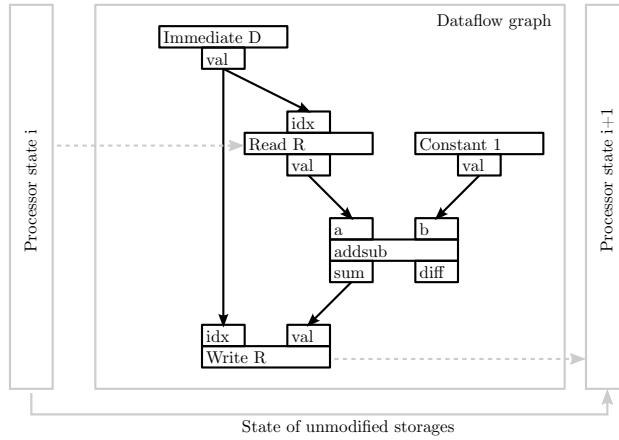

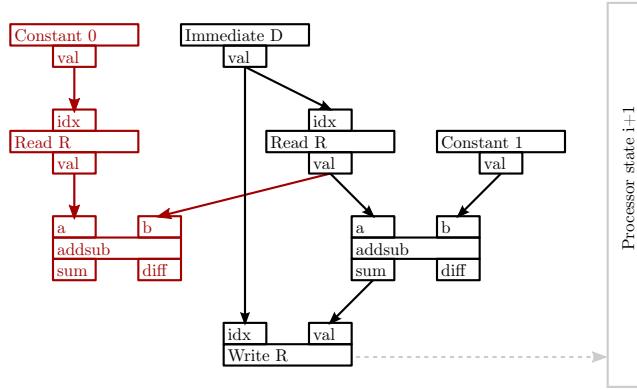

| 7.2.1 Instruction DFGs . . . . .                        | 144        |

| 7.2.2 DFG simplification . . . . .                      | 145        |

| 7.2.3 Origin information . . . . .                      | 145        |

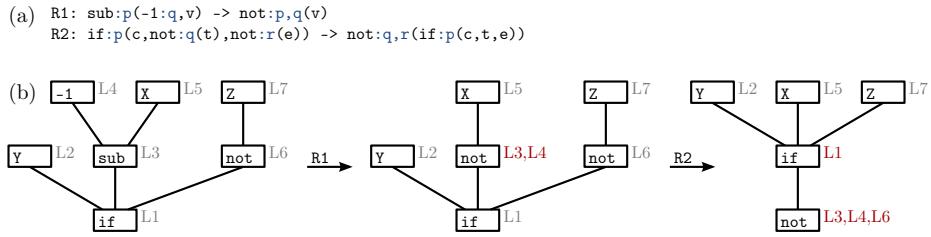

| 7.3 Term rewriting system . . . . .                     | 147        |

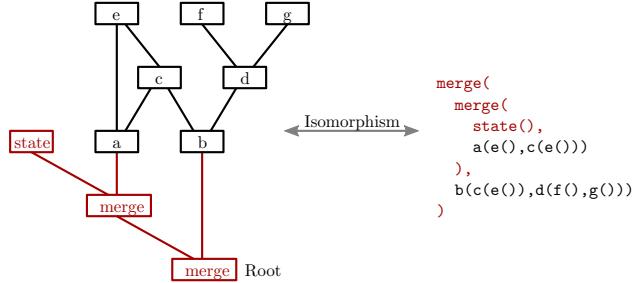

| 7.3.1 Isomorphism . . . . .                             | 148        |

| 7.3.2 Applications . . . . .                            | 149        |

| 7.3.3 Origin information . . . . .                      | 149        |

| 7.3.4 Integer arithmetic . . . . .                      | 150        |

| 7.3.5 Rule sets . . . . .                               | 151        |

| 7.3.6 Bit-widths . . . . .                              | 152        |

| 7.4 Transformations and optimizations . . . . .         | 152        |

| 7.4.1 Partial evaluation . . . . .                      | 152        |

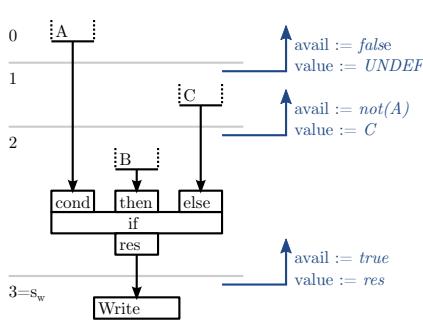

| 7.4.2 Epsilon transformation . . . . .                  | 153        |

| 7.5 Methods for generating simulators . . . . .         | 155        |

| 7.5.1 Structure of simulator . . . . .                  | 156        |

| 7.5.2 Bit-strings . . . . .                             | 157        |

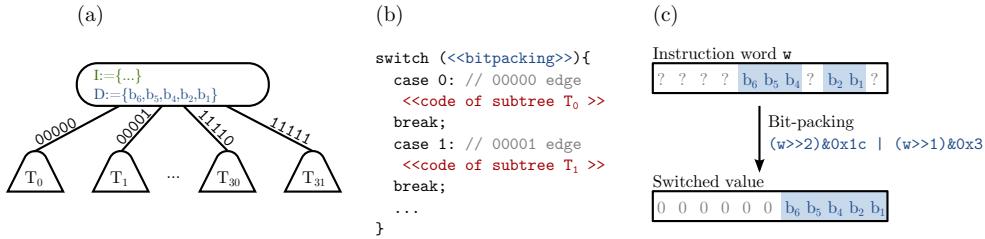

| 7.5.3 Decoding . . . . .                                | 158        |

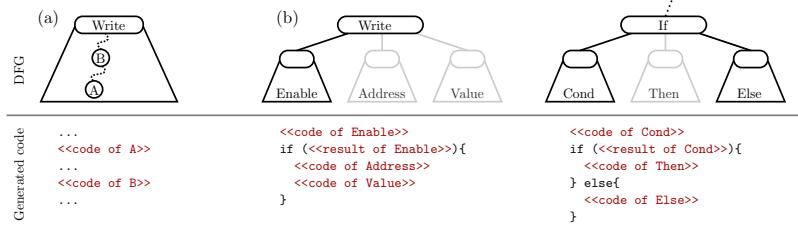

| 7.5.4 Implementing instruction semantics . . . . .      | 159        |

| 7.5.5 Transactions . . . . .                            | 161        |

| 7.6 Methods for generating processors . . . . .         | 162        |

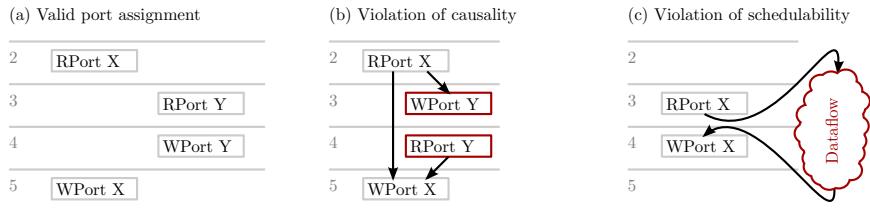

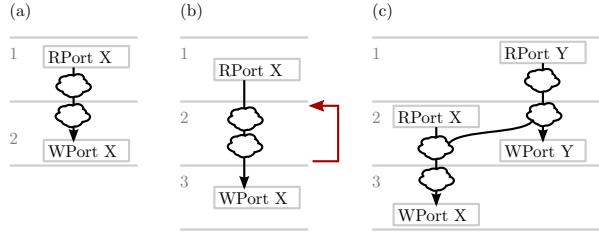

| 7.6.1 Register port allocation . . . . .                | 163        |

| 7.6.2 Operation pipelining . . . . .                    | 165        |

| 7.6.3 Timing . . . . .                                  | 165        |

| 7.6.4 Port scheduling . . . . .                         | 166        |

| 7.6.5 Operation scheduling . . . . .                    | 168        |

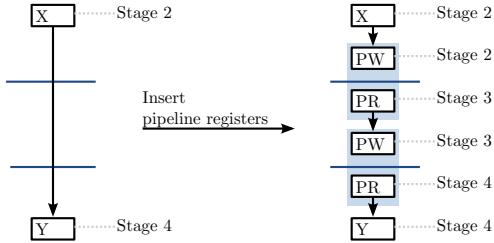

| 7.6.6 Pipeline registers . . . . .                      | 169        |

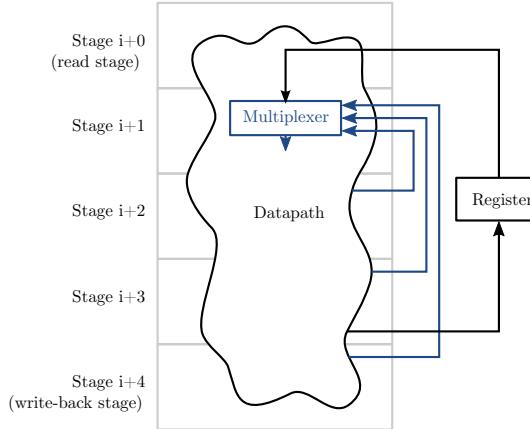

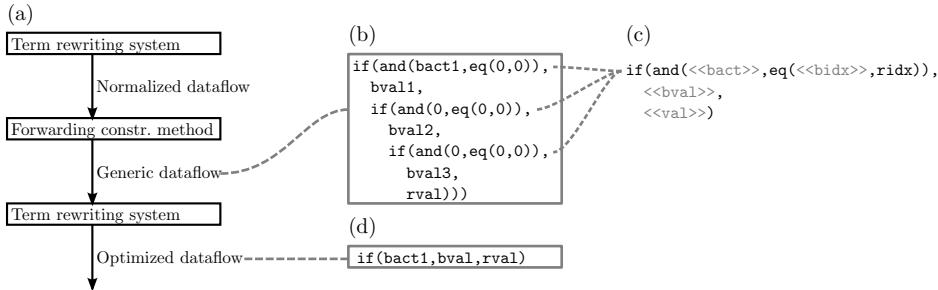

| 7.6.7 Forwarding circuit . . . . .                      | 169        |

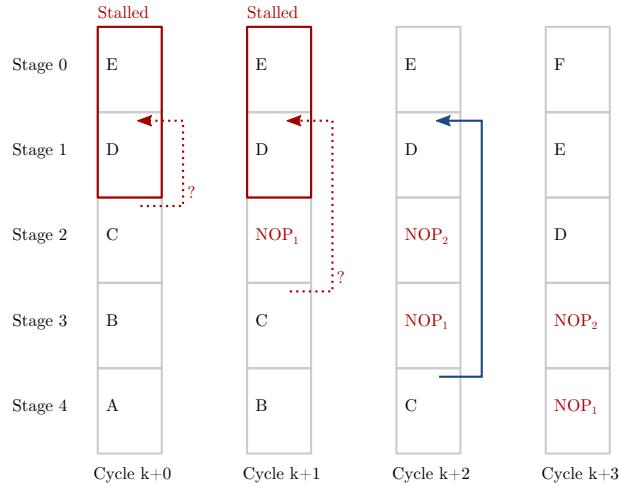

| 7.6.8 Interlocking . . . . .                            | 172        |

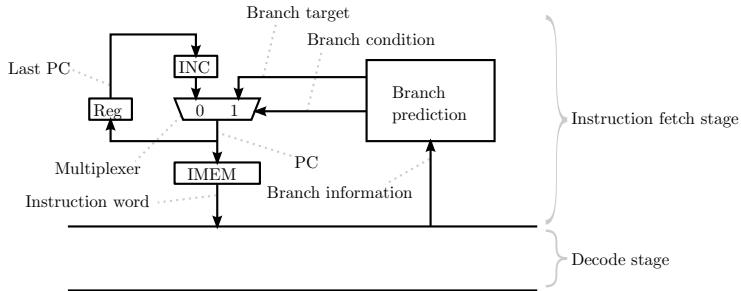

| 7.6.9 Branch prediction . . . . .                       | 173        |

|                                                               |            |

|---------------------------------------------------------------|------------|

| <b>8 Evaluation</b>                                           | <b>175</b> |

| 8.1 Evaluation process . . . . .                              | 175        |

| 8.2 ViDL . . . . .                                            | 177        |

| 8.2.1 Real world instruction sets . . . . .                   | 177        |

| 8.2.2 Efficient specification . . . . .                       | 178        |

| 8.2.3 Usability . . . . .                                     | 179        |

| 8.2.4 Rapid exploration of instruction sets . . . . .         | 180        |

| 8.2.5 Restrictions . . . . .                                  | 180        |

| 8.3 Generator speed . . . . .                                 | 182        |

| 8.4 Simulator generator . . . . .                             | 182        |

| 8.4.1 Setup . . . . .                                         | 183        |

| 8.4.2 Characteristic instructions . . . . .                   | 183        |

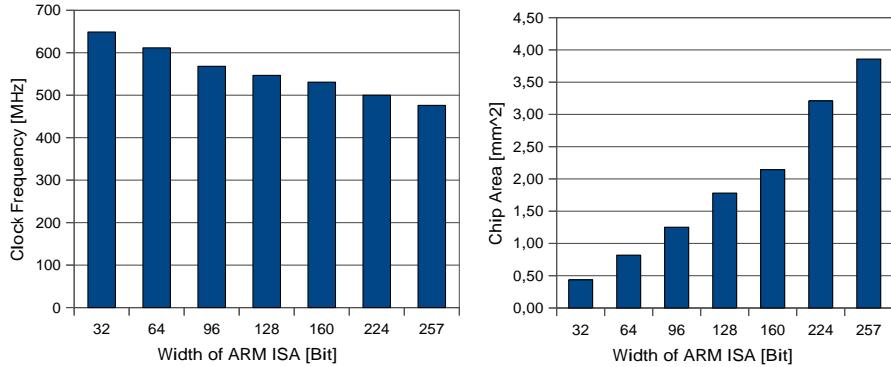

| 8.4.3 ISA width . . . . .                                     | 184        |

| 8.4.4 Width of simulator code . . . . .                       | 185        |

| 8.4.5 Generator optimizations . . . . .                       | 186        |

| 8.5 Processor generator . . . . .                             | 189        |

| 8.5.1 Setup . . . . .                                         | 189        |

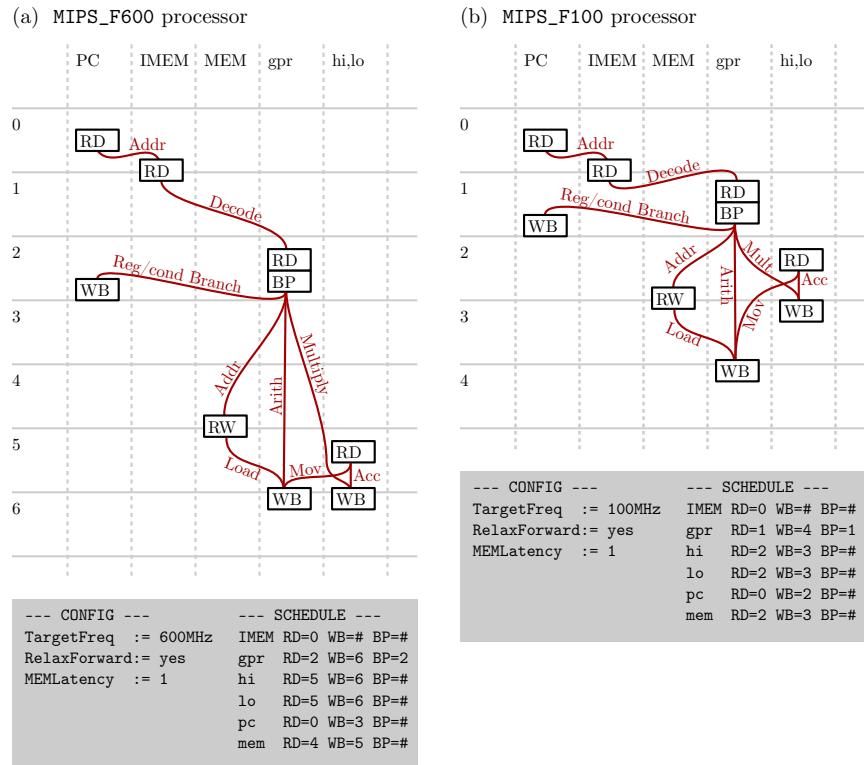

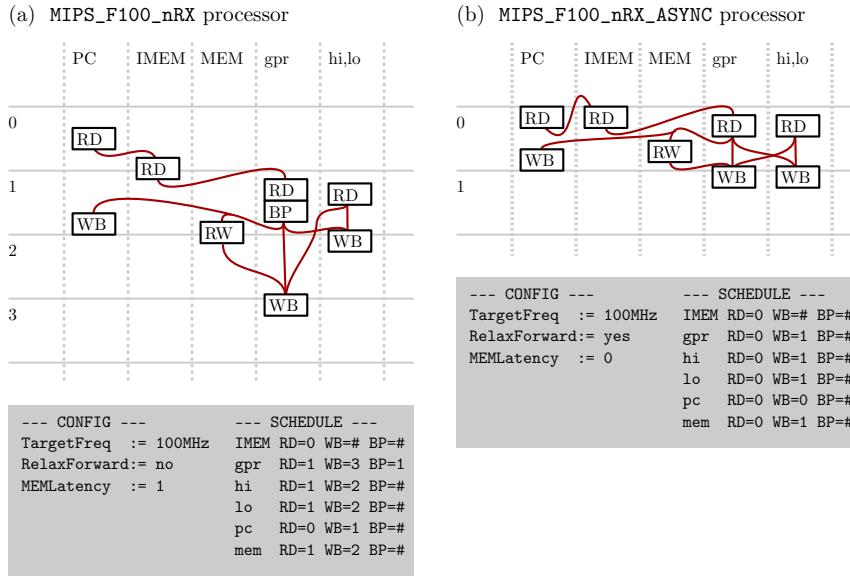

| 8.5.2 Overview of generated processors . . . . .              | 190        |

| 8.5.3 Exploration of microarchitecture . . . . .              | 192        |

| 8.5.4 Comparison to handcrafted processors . . . . .          | 194        |

| 8.5.5 OISC — A simple processor . . . . .                     | 197        |

| 8.5.6 Wide instruction sets . . . . .                         | 197        |

| 8.5.7 Register ports . . . . .                                | 198        |

| 8.5.8 Structure of generated pipeline . . . . .               | 199        |

| 8.5.9 Latencies and penalties . . . . .                       | 205        |

| 8.5.10 Resolution of hazards . . . . .                        | 207        |

| 8.5.11 Generating waveform definitions for ModelSim . . . . . | 213        |

| 8.6 DNACore — A case study on ISE . . . . .                   | 214        |

| 8.6.1 Development process . . . . .                           | 214        |

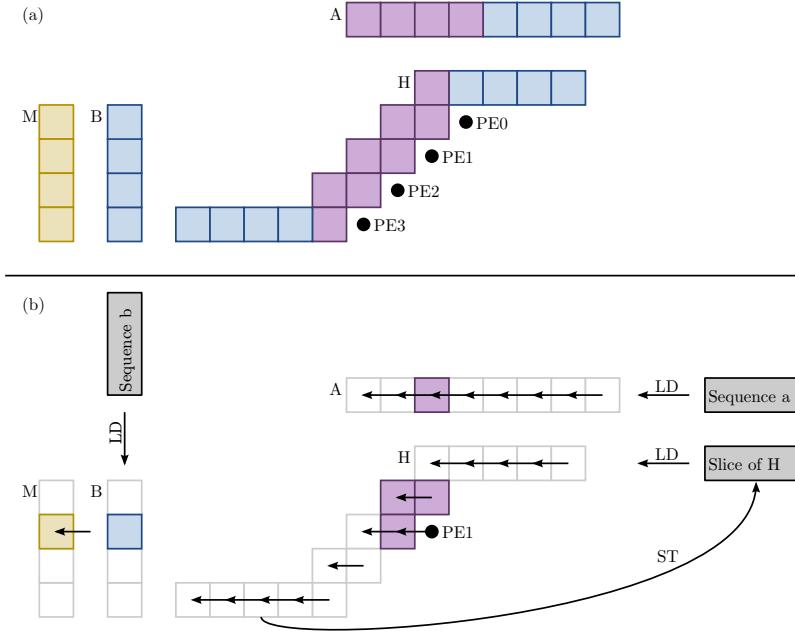

| 8.6.2 Algorithm . . . . .                                     | 215        |

| 8.6.3 Instruction set extension . . . . .                     | 216        |

| 8.6.4 Specification in ViDL . . . . .                         | 216        |

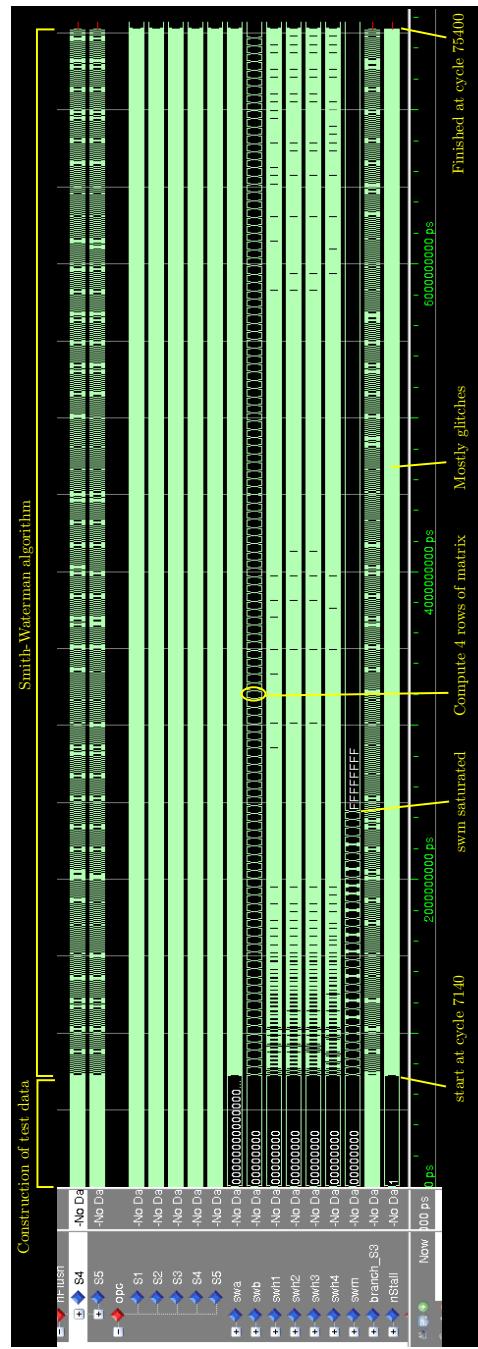

| 8.6.5 Dynamic behavior of processor . . . . .                 | 217        |

| 8.6.6 Results and remarks . . . . .                           | 219        |

| 8.7 Summary . . . . .                                         | 219        |

| <b>9 Conclusion</b>                                           | <b>223</b> |

# Chapter 1

## Introduction

## 1.1 Motivation

Digital systems are omnipresent in our today's life. They are for instance employed in personal computers, cell phones, cars, video game consoles and chip cards. Most of these digital systems include microprocessors, as they are flexible due to their programmability. The variety of different application areas raises the demand for customized processors. Processors in cell phones are supposed to consume low power, whereas desktop processors are optimized for high performance. A processor in a chip card includes special instructions to accelerate cryptographic algorithms, whereas processors in video game consoles use multimedia instructions for graphical operations. The application specific aspects of a processor are mainly encapsulated in its instruction set.

A multitude of such application specific processors is developed and increasingly employed in systems on a chip. Tools that support a rapid and reliable development of processors for a given instruction set are therefore essential. This

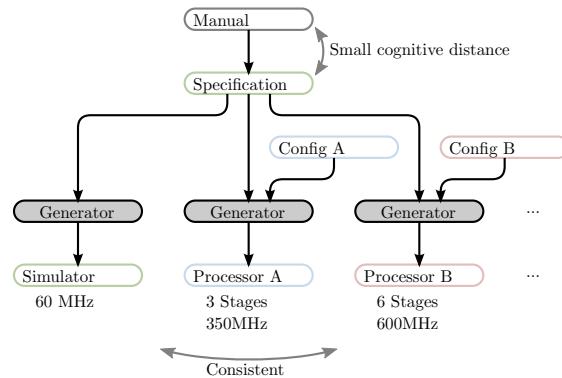

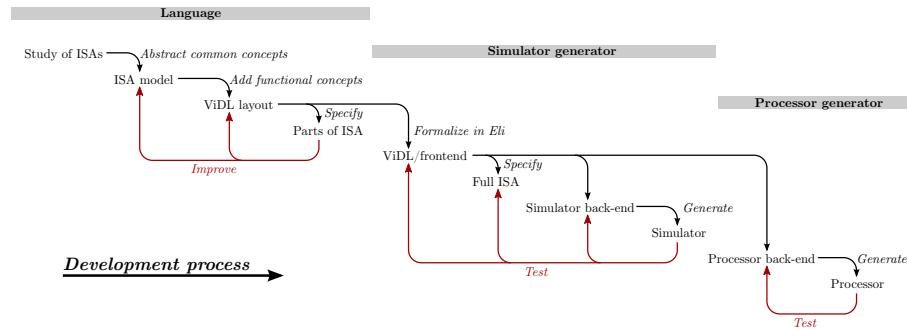

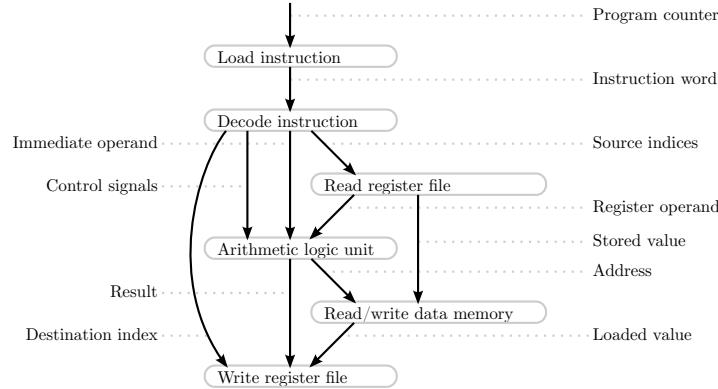

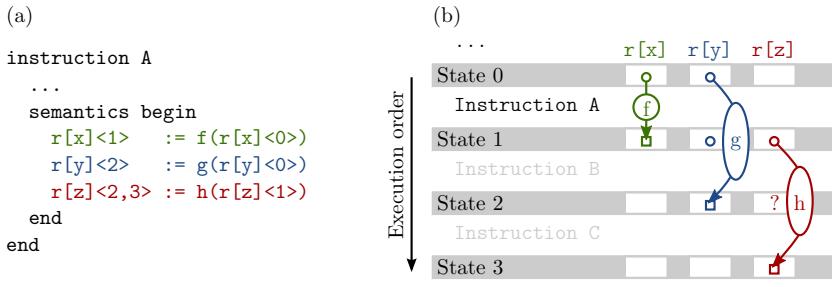

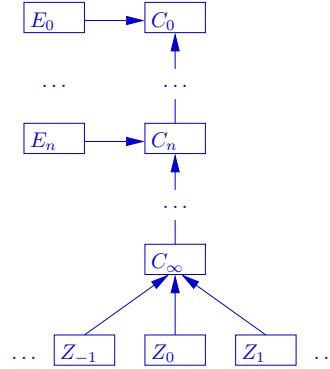

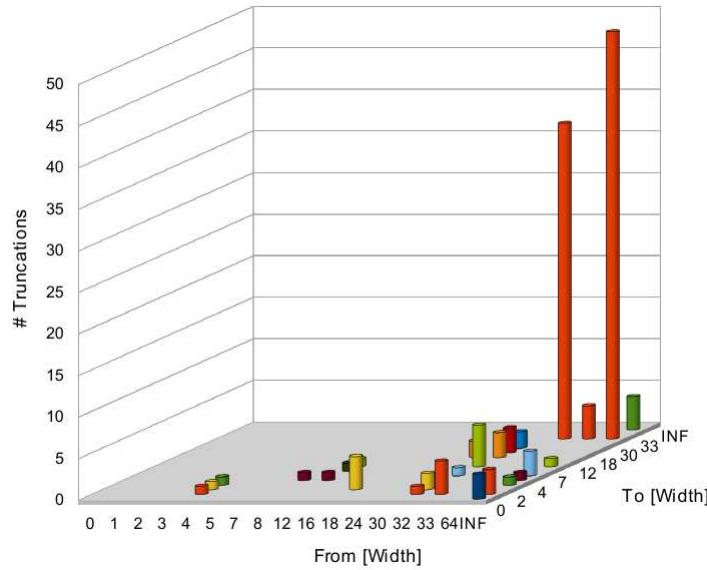

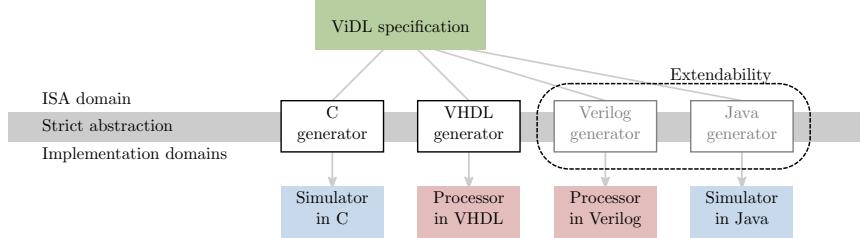

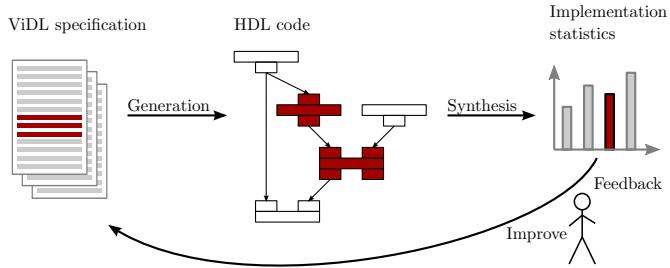

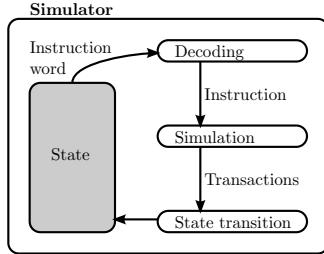

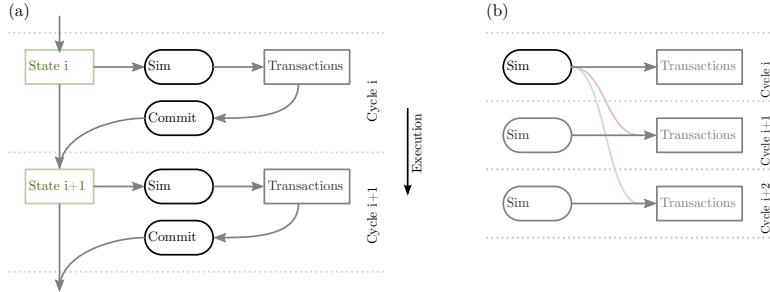

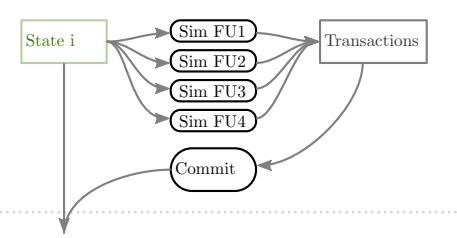

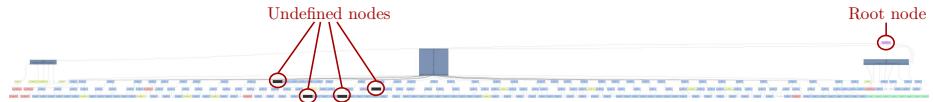

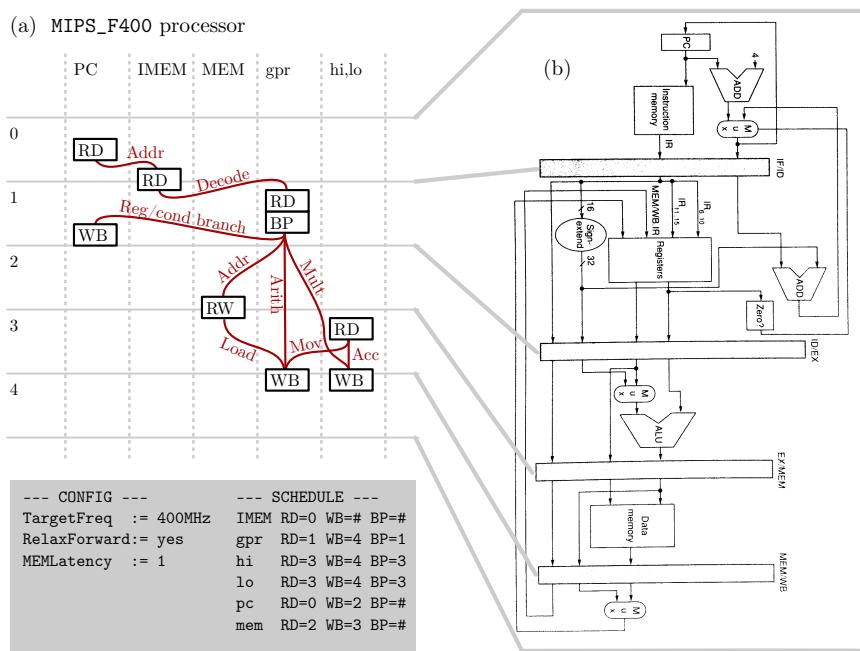

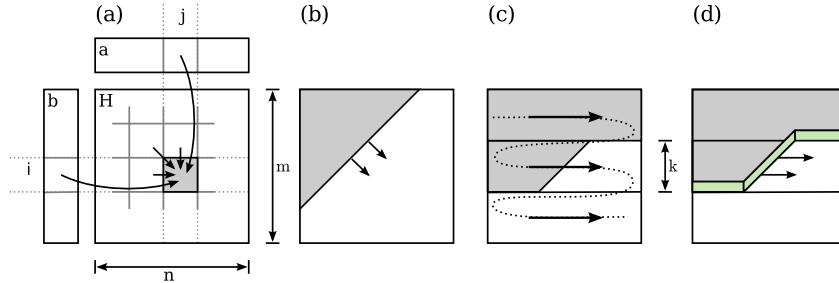

Figure 1.1: Overview of the proposed approach.

thesis proposes a system to generate a simulator and a processor implementation from a formal instruction set specification, as shown in Figure 1.1. The specification language enables rapid formalization of instruction set manuals, due to a small cognitive distance to descriptive manuals. The developer does not require particular knowledge of microarchitectures, since the specification language strictly abstracts from such aspects. The language excludes for instance all aspects of a pipeline and its control. This also eliminates a common source of faults. Thanks to this abstraction, processor implementations with different microarchitectures can be generated from the very same specification, as shown in Figure 1.1.

The generator automatically constructs an appropriate microarchitecture that suites the instruction set. The developer can control this derivation by an optional configuration. The configuration may for example constrain the clock frequency of the final processor. Based on such information and the specified instruction set, the generator determines for example the depth of the pipeline. Figure 1.1 shows the actual clock frequency and pipeline depth for two generated ARM processors.

As all generated implementations are based on the same instruction set specification, they are guaranteed to be compatible. Executing a program on each implementation will yields the same result. There is no way, a ViDL developer can break consistency of the generated implementations. The processor specification itself is always consistent and configurations have no effect on the processors execution semantics. As the generated implementations are consistent, extensive testing of processor implementations can be omitted.

**Processor design flow** In the first step of a classical design flow, the set of instructions is defined and evaluated using a simulator. The simulator basically emulates a real processor, but requires less development effort. It is typically programmed in C and runs on normal desktop computers. After the instruction set is fixed, a processor is defined in a hardware description language (HDL), such as VHDL. The description obeys a specific microarchitecture, which consists of structures and techniques to implement an instruction set. Note, that the same instruction set can be implemented with different microarchitectures. The resulting processors differ in power consumption, clock speed and chip costs, but can execute the same binary programs. Typically, a microarchitecture is selected that fits best the demands of the application area.

This design process has several disadvantages. The separate implementation of an instruction set in terms of a simulator and a hardware processor increases development costs and time to market. The instruction set or microarchitecture of the hardware implementation can hardly be changed in a late design stage. Decreasing for instance the length of the pipeline is laborious and error-prone. Functional units must be reassigned to stages, which affects pipeline registers and the pipeline bypass. As a result, the control unit must be adapted and even changes to branch prediction may be necessary.

In general, the development of pipelined implementations is complex due

to pipeline hazards. For this reason, processors need to be tested extensively. Development of test cases with a good coverage however is challenging. The microarchitecture must be considered to test instructions for all reachable pipeline states. In practice, testing has a major impact on development time and costs. Even the implementation of the simulator may be complex, due to the lack of bit-precise types and missing operations (e.g. “count leading zeros”) in C.

**Mixed level languages** To overcome these difficulties, mixed-level processor description languages are proposed. Such languages specify a processor on the level of microarchitecture and the instruction set level. On the microarchitectural level, a rough layout of the processor is specified. This typically includes pipeline stages, functional units and register ports. The specification of an instruction then refers to these elements. The instruction set level therefore builds on the microarchitectural level. As a result, the whole specification is bound to one specific microarchitecture. Once the instruction set is specified, the microarchitecture can not be changed without major changes to the instruction set. For instance, changing a 5-stage pipeline to a 3-stage pipeline is expected to be very complex.

In mixed-level languages, pipeline control is typically specified explicitly. This allows for the description of complex and exceptional pipeline behavior. However, its specification is typically very complex and error-prone, as all pipeline states must be considered. Some exceptional sequences of instructions are easily overlooked, which may result in unintended bypassing or branch behavior. As the developer is responsible for the correctness of pipeline control, extensive testing is required. Some languages require in-depth knowledge on microarchitectures, like VHDL and C++. A developer must therefore have respective skills. Some languages impose an orthogonal structure on the instruction set. Instructions are then defined according to this structure. To formalize an existing instruction set manual, the developer has to analyze the instruction set to reconstruct regular structures. Some languages offer or even require a separate specification of instruction semantics for the simulator and hardware implementation. The developer is responsible to specify equivalent semantics for both. This may introduce inconsistencies between simulator and hardware. Hence, sufficient testing is required, to exclude such faults with a certain probability. Besides, the redundant specification reduces maintainability and increases development effort.

The outlined problems of classical processor design flows and mixed level languages are solved by ViDL and its generators. The language and the generators therefore implement a variety of new concepts and methods, which are summarized in the next section.

## 1.2 Overview

This thesis is structured as follows: The remainder of this chapter gives a basic introduction to the *context* and the *contribution* of this thesis. Its *fundamentals*

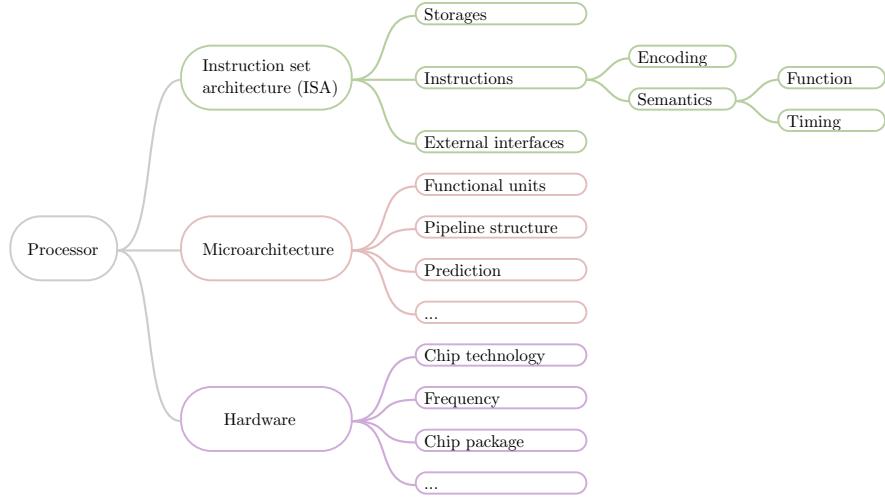

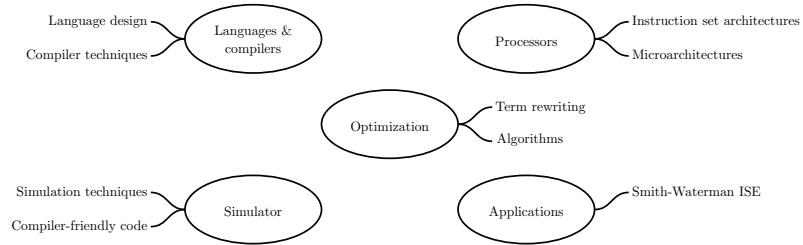

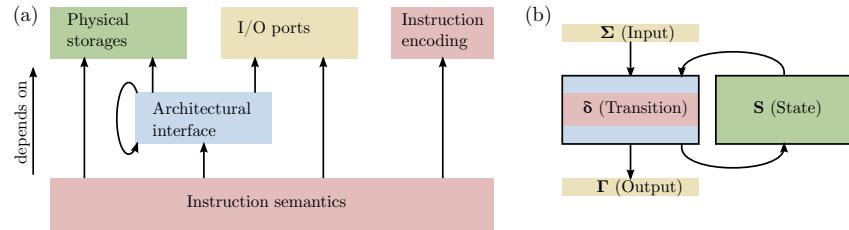

Figure 1.2: Structure of processor aspects.

by means of applied methods and concepts are briefly summarized, to introduce a common terminology and common definitions (Chapter 2). To give an overview of alternative approaches, *related specification languages* for instruction sets and processors are reviewed and classified (Chapter 3). Against this background, the *instruction set specification language ViDL* is proposed (Chapter 4). Explanations focus on ViDL’s concepts and their impact on the quality of instruction set specifications. Practical applications of ViDL are demonstrated, using design patterns for frequent concepts of instruction sets as example (Chapter 6). Besides ViDL, the simulator generator and the processor generator account for a great part of this thesis. Major concepts and methods of both generators are presented (Chapter 7), including the timing driven generation of pipelined processors (Section 7.6). Both generators are evaluated, by examining the generated products for multiple real world instruction sets (Chapter 8). The speed of the simulator is measured and physical characteristics of the processors are estimated by synthesis tools. As an all embracing proof of concept, an application specific processor is developed for the Smith-Waterman algorithm, using ViDL and its generators (Section 8.6).

### 1.3 Processor aspects

This section describes the aspects of a hardware processor implementation. The purpose of this section is to introduce a uniform terminology and classification of processor aspects. A processor is defined by its instruction set, microarchitecture and hardware properties, as shown in Figure 1.2.

An *instruction set architecture* defines the aspects of the processor that are visible to an assembly programmer or compiler. Basically, it defines a set of

storages and instructions that operate on these storages. The set of storages typically includes a general purpose register file, a status register and a data memory. An instruction is defined by its encoding and its semantics. The semantics define the effect of executing the instruction on the processor state. They are typically denoted on a register transfer level. The terms “instruction set architecture”, “instruction set” and ISA are used synonymously. Examples of popular instruction sets are Intel x86, Power, ARM and MIPS.

A *microarchitecture* comprises a set of techniques to implement an instruction set architecture. It has a major effect on the efficiency of a processor in terms of clock frequency, chip area and power consumption. A microarchitecture basically defines the structure of hardware units and their interaction. It defines for instance the structure of the pipeline and how branches are predicted. Hennessy and Patterson [24] use the term “Organization” as a synonym for “microarchitecture”. As the latter appears to be more common, it is used in this thesis. An example of a microarchitecture is a 5-stage pipeline with a dynamic branch prediction using a 4096-entry 2-bit prediction buffer.

The last term “*hardware*” covers physical aspects of a hardware processor. This includes the used chip technology, clock frequency and chip package. The three classes of ISA aspects (ISA, microarchitecture and hardware) are independent. One instruction set can for instance be implemented using different microarchitectures. A low power microarchitecture may be used for mobile applications, whereas a deeply pipelined microarchitecture is used for high-performance applications. On the other hand, the same microarchitecture may be used to implement different ISAs. Processors that share the same ISA and microarchitecture may differ in their actual hardware implementation. For instance may the chip technology and the chip package be different.

## 1.4 Scientific contributions

This thesis contributes a series of concepts and methods, which are integrated in the processor specification language ViDL, the simulator generator and the processor generator. They are briefly introduced in the following, to give an overview of this thesis.

### 1.4.1 Language concepts

In contrast to existing approaches, ViDL strictly *abstracts from microarchitecture* (Section 4.3). Thanks to this abstraction, the microarchitectural design space can automatically be explored, driven by the processor generator (Section 8.1). Small processors, as well as deeply pipelined processors are generated from the same specification. Besides, abstraction enables generation of a consistent high-performance simulator (Section 8.4), since microarchitectural aspects need not be simulated.

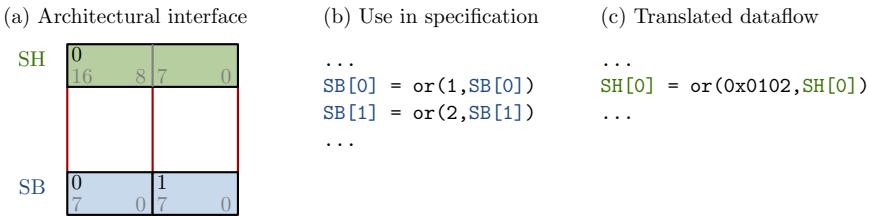

To specify timing behavior of instructions, while abstracting from their microarchitectural implementation, the concept of so called *delays* is proposed

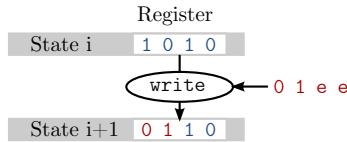

(Section 4.7). As a result, the number of delay slots of a branch can directly be denoted in ViDL, without considering the pipeline and its control. Views on storages and I/O ports can be defined using the concept of *architectural interfaces* (Section 4.8). It is a unified concept, which covers a variety of realistic register and storage structures, such as architectural registers and virtual address spaces (Chapter 6). The resulting abstraction improves clearness and maintainability of a specification. Architectural interfaces are based on equations and are translated into dataflow by the generator (Section 7.1.3). To efficiently define conditional and partial write accesses to storages, the unified concept of *epsilon logic* is proposed (Section 4.6). Epsilon logic is an instance of multi value logic, using three states, namely “zero”, “one” and “epsilon”, which means “don’t modify”. The concept integrates well in functional languages (such as ViDL) and improves clearness and reliability of specifications. Besides, a method is proposed, which translates epsilon logic into binary logic, as needed for implementations (Section 7.4.2).

As bit-widths need not be defined in ViDL, a type system and a respective type-analysis are proposed, to derive the widths of operations (Section 4.9). The type system is based on polymorphism and subtyping. In contrast to Verilog, bit-width rules on operations can concisely be specified in terms of signatures. Type analysis is based on type inference techniques. It statically checks for soundness and detects ambiguous semantics, as contained in the pseudo-code of the ARM manual (Section 4.9.3). Due to implicit typing, instruction set specifications are simplified and maintainability is increased. For instance, the widths of an entire instruction set can be changed, by simply redefining the width of registers (Section 8.2.4). ViDL integrates concepts of functional languages, such as tuples and higher order functions (Section 4.5). The language is free of side effects, which adds to reliability and clearness. Functionals can be defined, to encapsulate concepts of instruction sets, such as SIMD (Section 6.10).

#### 1.4.2 Generation methods

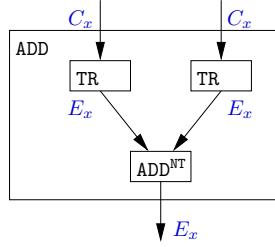

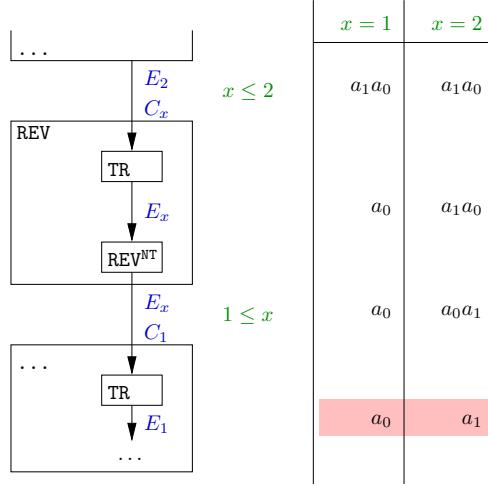

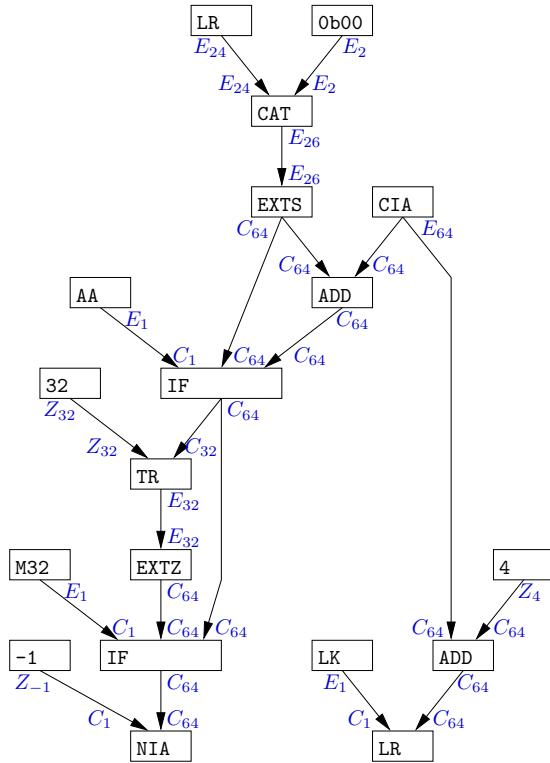

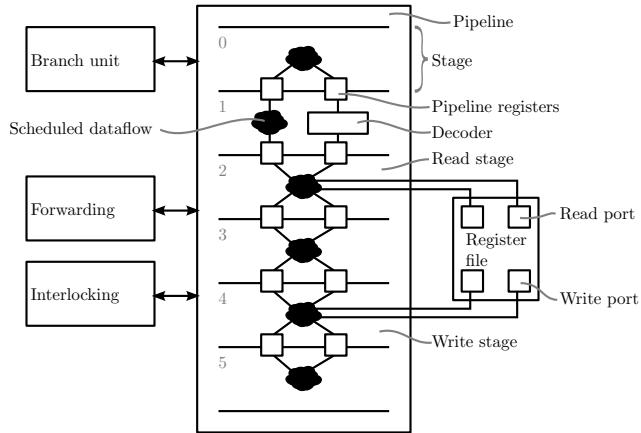

This thesis contributes methods to *generate pipelines* from specifications of instruction sets (Section 7.6). In contrast to related work, the approach is fully automated, i.e. no microarchitectural aspect of the pipeline needs to be specified by developers. Instead, the entire microarchitecture is contributed by the processor generator, based on a user-defined timing constraint (Section 7.6.3). The methods construct the entire pipeline, including forwarding circuits, interlocking, as well as control for branch instructions. All hazards are properly resolved in the resulting pipeline, while minimizing instruction latencies. The methods are based on scheduling techniques, term rewriting, as well as partial functions and their analysis. They are sensitive to instruction semantics and to the propagation delay of the targeted chip technology.

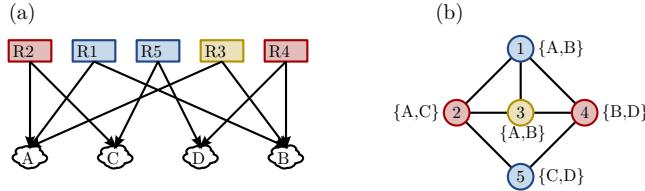

As ViDL abstracts from register ports, a *port allocation* method (Section 7.6.1) is proposed and integrated in the processor generator. The method assigns read and write accesses of instruction semantics to read and write ports of register files and memories. The number of ports is minimized, while excluding resource

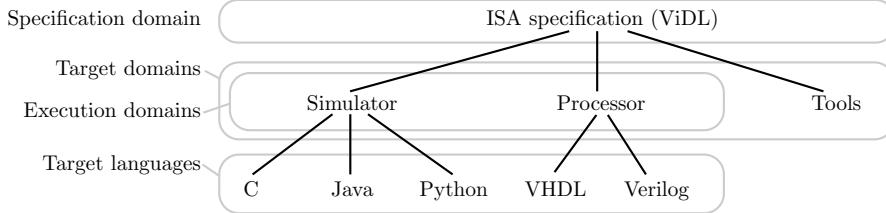

Figure 1.3: Domains and their relation.

conflicts. Besides, concurrent accesses are merged, if they refer to the same address. The allocation problem is reduced to graph coloring.

The thesis shows, how instruction semantics are systematically transformed and optimized using *term rewriting* on *dataflow graphs* (Section 7.3). A comprehensive set of rewrite rules has been defined, which encapsulates expert knowledge on semantic equivalences. The set is extensible and clear, which greatly adds to reliability of the generator. Partial evaluation of expressions is for instance solved using term rewriting (Section 7.4.1).

Code of the simulator is generated such, that it utilizes the principle of *lazy evaluation* (Section 7.5.4). Only those parts of instruction semantics are simulated that contribute to the result of an instruction. For instance, the target address of a branch is only computed, if the branch is actually taken.

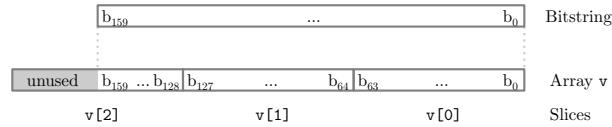

The thesis presents methods to process *arbitrary and ultra-wide* instruction semantics (e.g. 257 bit). All parts of the generation process are considered, including static evaluation and code generation for C. Static evaluation is implemented in the generator using an arbitrary precision library (Section 7.3.4). The generation of C-code is based on operation specific generator algorithms. The algorithms break ViDL operations of arbitrary width down to 32-bit or 64-bit integer arithmetic in C (Section 7.5.2).

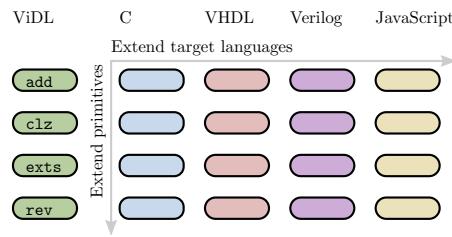

## 1.5 Processor implementations

In my approach, an ISA is defined in the *specification domain*, using the language ViDL. From this specification, products of different *target domains* are generated, as illustrated in Figure 1.3. In particular, this is the *simulator* domain, the (hardware) *processor* domain and the *tools* domain.

The simulator and processor domain are called *execution domains* in the following, as their products can actually execute ISA compliant programs. The simulator and processor domain are separated, as they significantly differ in structure. A simulator is described in terms of data structures and sequential algorithms. A processor in contrast is defined by inherently parallel units and their interconnection. The gap between both domains is further increased by complex processor microarchitectures, which are omitted in the simulator for the sake of efficiency.

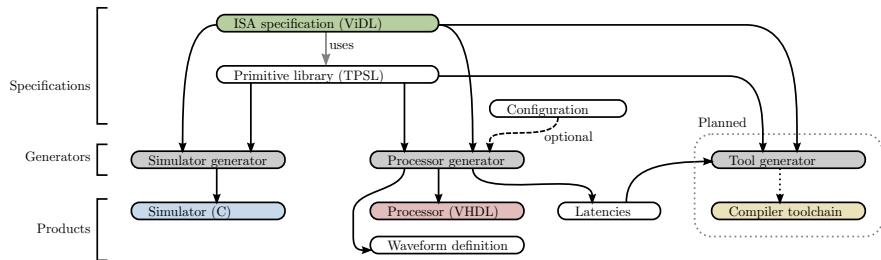

Figure 1.4: System of specifications, generators and products.

The tools domain covers ISA specific tools, which are used for software development. A classical toolchain for an ISA consists of a C-compiler, an assembler, a linker and a disassembler. This domain significantly differs from the former ones, as tools only consider certain properties of the ISA. An assembler for instance considers the encoding of instructions, but not their behavior.

The products of the execution domains can be implemented in different languages. A simulator is typically implemented in imperative programming languages, such as C, Java or Python. The structure of a processor is defined using hardware description languages, like VHDL or Verilog. For the tools domain, a target language corresponds to a specific retargetable toolchain. The generator may produce ISA descriptions that are specific for different toolchains.

Currently, generators are available for both execution domains and the most typical target languages C and VHDL. As ViDL is not bound in any way to these languages, generators for further target languages can be added. The effort for retargeting can be considered low, as only the code generation needs to be adapted. Domain specific concepts, such as pipelining or lazy evaluation, remain unchanged. The development of a generator for the third domain “tools” is not part of this thesis. It is discussed as future work in Chapter 9.

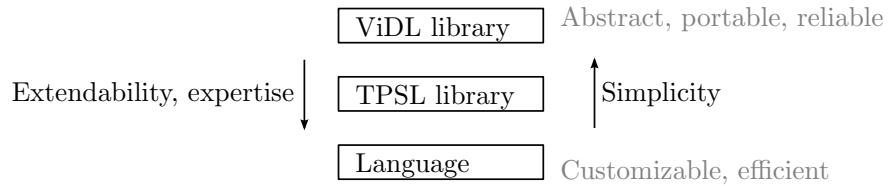

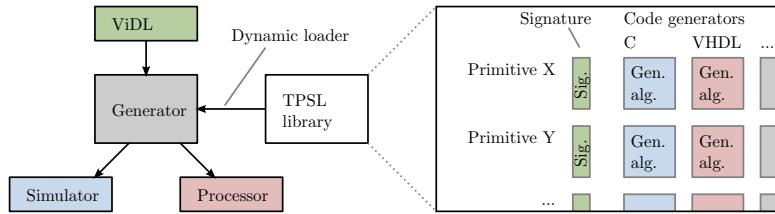

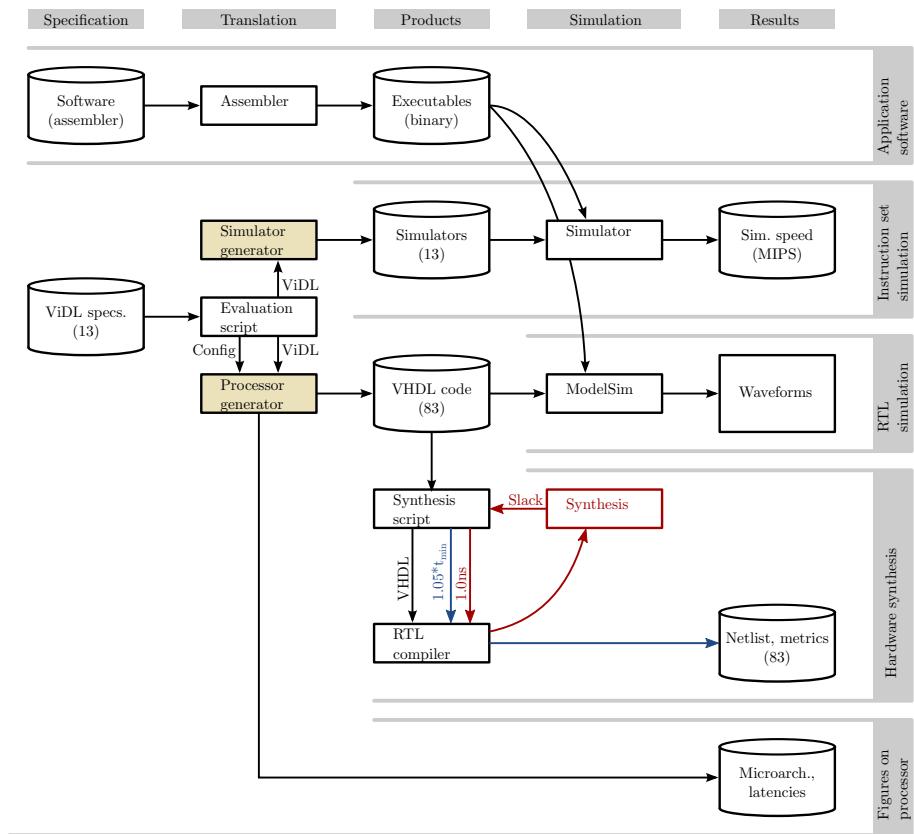

## 1.6 System overview

This section is intended to give a brief overview of the entire system of specifications, generators and their products on a high level. The in-depth discussion of its components is postponed to subsequent sections. The basic idea of the system is to generate different processor implementations from a central ISA specification, as illustrated in Figure 1.4.

An ISA is specified using the *Versatile ISA Description Language* (ViDL). The specification defines storages, instructions and external interfaces of the ISA. An important feature of ViDL is that *only* aspects of the ISA are specified. Microarchitectural aspects, such as pipeline stages and register ports are not defined. ViDL is described in detail in Chapter 4. For evaluation, the instruction sets of ARM, MIPS, Power, CoreVA, and SRC have been specified (Section 8.2.1). In addition, a one instruction set computer (OISC) and an

instruction set extension (ISE) for DNA sequence alignment have been defined.

ViDL uses primitives such as addition (`add`) or sign extension (`extz`), to define the semantics of instructions. The signatures and semantics of primitives are defined in the separate *primitive library*, which is specified using the *transfer primitive specification language* (TPSL, Chapter 5). It should be noted, that most ISA developers do not have to consider TPSL, as they can simply use the existing primitive library, which includes about 50 primitives. In rare cases, the developer may extend the library by additional special purpose primitives.

The ISA specification and primitive library are fed into generators. The *simulator generator* (Section 7.5) produces an efficient *instruction set simulators* (ISS) from this input. Simulation speeds of 60 Mips are likely on a Pentium 3 GHz workstation (Section 8.4).

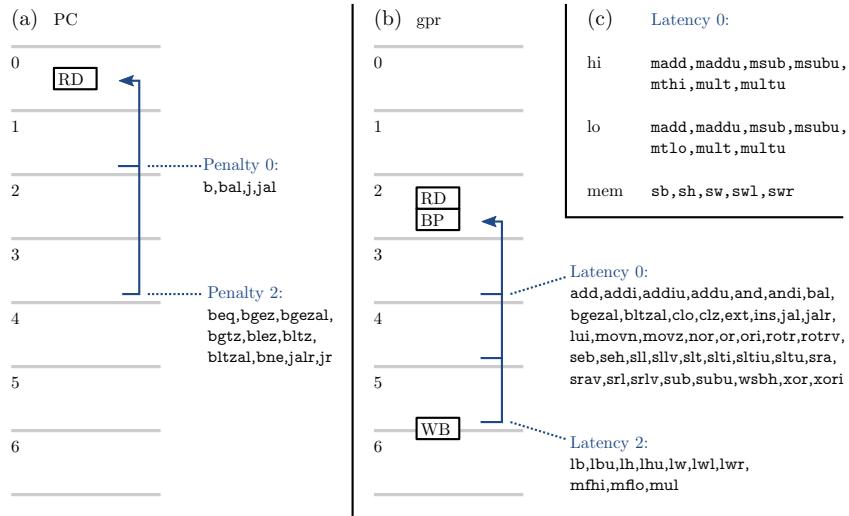

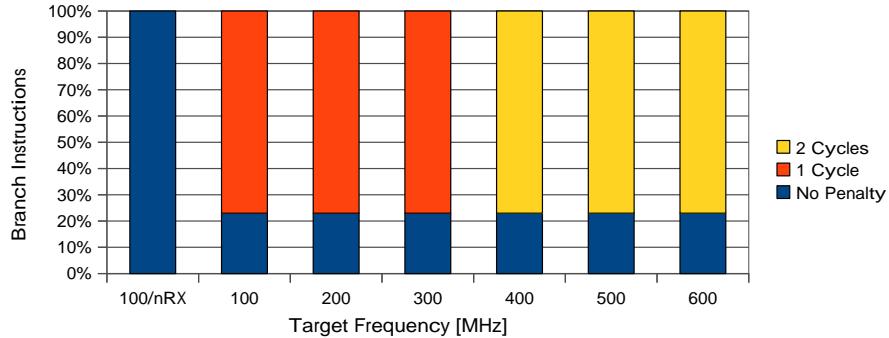

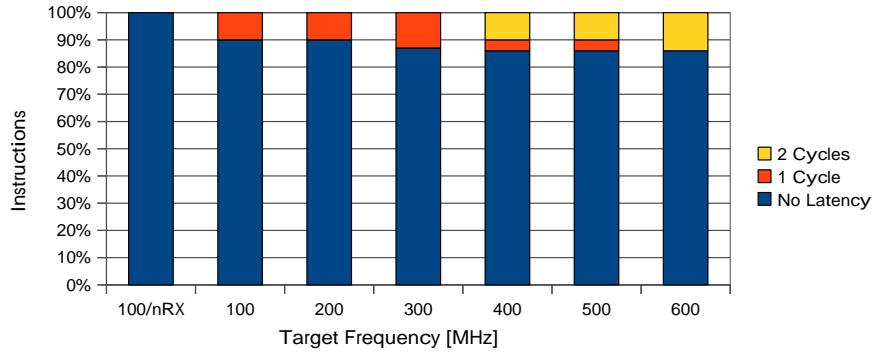

The *processor generator* (Section 7.6) produces a *processor*, i.e. a microarchitectural implementation of the ISA. The microarchitecture of the processor can be controlled using an optional *configuration*. The configuration typically defines the targeted clock frequency of the processor. The generator then estimates propagation delays and selects an appropriate pipeline depth to meet the targeted timing. The configuration enables the developer to generate multiple processors with different microarchitectures from the very same ISA specification. All processors and the simulator are guaranteed to be consistent. They can execute the same binary programs and yield the same results. The number of required execution cycles however may differ due to different dynamic behavior. The dynamic behavior is mainly affected by instruction *latencies*. Information on latencies is emitted by the processor generator and may be utilized by the scheduler of a generated processor to avoid interlocking. Another product of the processor generator is a waveform definition file for ModelSim. It contains the identifiers and structure of significant signals, which are then visualized in ModelSim.

## 1.7 Evolution of ViDL and its generators

The system described in the last section is the result of an extensive development process, which is illustrated in Figure 1.5. In particular ViDL is the outcome of a long process of ISA exploration and evaluation. It is based on the specification language UPSLA, from which it borrows the concept of encoding patterns and distinct specification of instructions.

To derive the underlying instruction set model of ViDL, a large set of representative instruction sets has been studied. Common concepts have been identified and generalized. High level concepts in instruction sets have been broken down to a combination of basic concepts. Conditional execution is for instance modeled as a combination of conditional expressions and epsilon logic. The development of the ISA model was probably one of the most complex tasks.

With the language in mind, representative sets of ISAs have been specified. This way, missing features and inadequate concepts have been identified in an early stage of development. For instance, the need to make the set of primitives

Figure 1.5: Development process of ViDL and its generators.

Figure 1.6: Involved problem areas.

extensible has been detected during this process.

After the model and the respective language had annealed to a sufficient degree, the generator has been developed. At first, the front-end and the simulator back-end have been developed, for three reasons.

- The simulator offers a convenient way to test the front-end and common optimizations of the generator.

- Existing experience in the area of simulator generation from UPSLA and the CoreVA architecture.

- The structure of the simulator is much simpler, as it does not involve the generation of a pipelined microarchitecture.

After a correct baseline simulator had been generated from an ARM specification, the processor back-end has been developed. Finally, the generated products were repeatedly evaluated and optimized.

## 1.8 Areas of expertise

The development of the generator system is an inter-disciplinary task. It requires expertise in very different problem areas, as illustrated in Figure 1.6.

The first major problem area covers processors and microarchitectures. A representative set of ISAs and their common structures and concepts has to be understood, to derive a simple, yet powerful ISA model. This domain specific knowledge is crucial for the design of ViDL. For code generation, expertise on state-of-the-art microarchitectures is required. Concepts such as pipelining, forwarding, interlocking and branch prediction must be implemented as generalized algorithms in the generator. This requires an in-depth understanding of these concepts, as correctness must be considered for any instruction set and not only for a specific one.

Language design mainly requires knowledge on language concepts and their benefits. A good selection of language concepts is a non-trivial task, as language qualities such as simplicity, reuse, maintainability and readability must be considered. In particular, concepts of functional languages and their implementation have to be understood, as ViDL inherits a large subset of SML. The language has to be formal and unambiguous, to be suited for generation. This implies a basic understanding of compilers and the target domains. To implement the generators, compiler development skills are required. This includes context free grammars, name analysis, type analysis and code generation. The grammar needs to obey the parser generator's grammar class, which is LALR(1) for ViDL. Name analysis in ViDL is a non-trivial task, as highly recursive scoping rules are inherited from SML. Type analysis requires expertise on type inference, polymorphism and subtyping. The type system also involves *formal proofs*, to ensure soundness. In general, the demand for correctness and generality makes compiler development hard.

To yield efficient products, the ViDL generators include sophisticated optimizations. The implementation of these optimizations involves the development of non-trivial algorithms and data structures. The pipeline scheduler 7.6.4 and the port allocator 7.6.1 are examples of such algorithms. The integrated term rewriting system requires knowledge on equivalent register transfer, and confluence.

To produce an efficient simulator, appropriate simulation techniques have to be applied. For example, the simulation speed is significantly increased by a decoder cache and a lazy evaluation strategy of instruction semantics. Besides, technical aspects of the generated C-code play an important role for efficiency. A basic understanding of C-compilers and their optimizations is required, to produce compiler-friendly C-code. For instance, the use of separate compilation units typically result in conservative estimates on data-dependencies, which finally limit the scheduler.

To evaluate ViDL's fitness for instruction set extension, the MIPS instruction set was extended by application specific instructions for the Smith-Waterman algorithm. To develop this extension, the structure of that algorithm had to be understood in depth. Besides, a basic idea of its application for sequence alignment of DNA, RNA and proteins is required.

In addition to expertise on concepts, methods and algorithms, an extensive technical knowledge is required to implement the generator system. For instance, 13 different languages were involved in the development of the whole

system. This includes declarative languages (ELI, Make and flex/bison), imperative languages (C and C++), scripting languages (Perl, Python and Bash), assembly languages (ARM, MIPS and Power), the functional language SML and the hardware description language VHDL.

# Chapter 2

# Fundamentals

This section outlines the fundamentals of this thesis and introduces a common terminology. The development of the language ViDL and its generators is founded on knowledge and techniques of several scientific disciplines. For instance, features of characteristic instruction sets (Section 2.1) and typical processor design scenarios (Section 2.2) have significantly guided the development of ViDL. Besides, ViDL obeys design guidelines of domain specific language (Section 2.3). The ViDL compilers implement classical compiler techniques (Section 2.4), sophisticated analyses (Section 2.5) and transformations (Section 2.6) to optimize the generated product. To derive a pipelined processor implementation, structures and principles of modern microarchitectures (Section 2.7) are utilized.

## 2.1 Instruction set architectures

To understand the design of ViDL, it is important to have a basic understanding of realistic instruction sets and their characteristics. This section therefore introduces two major instruction sets, namely ARM and MIPS, which have (among others) significantly influenced the development of ViDL. The instruction sets have inspired several concepts of ViDL. The goal has been to design the language such, that both real world instruction sets can precisely be specified, including irregularities and uncommon aspects. The evaluation in Chapter 8 presents the results for the formalization of both instruction sets.

In general, an instruction set architecture defines a set of instructions and storages. It thereby determines the execution semantics of binary programs. The description of an instruction set is for instance used by assembler programmers to write assembly programs. An instruction set can be regarded as an interface for the execution of binary programs. Processors that implement the same instruction are compatible. Executing a program on these processors will therefore yield the same results. However, the execution speed and the microarchitectural implementation of the processors may differ.

The purpose of this section is to give an impression of exceptional instruction set characteristics. In particular, the ARM, MIPS and an OISC instruction set is regarded. This section is not intended to discuss these instruction sets in detail, but only their interesting aspects. The presented aspects are considered to be complex in terms of instruction set specification. A specification language should be powerful enough to define these characteristics precisely and concisely.

### 2.1.1 ARM

The ARM instruction set [2] belongs to the class of RISC instruction sets. It has been chosen for evaluation, as it is a popular and state-of-the-art instruction set for mobile applications, which became more important in recent years. The instruction set is basically quite regular, but also includes some uncommon characteristics, which challenge ViDL and its generators. In the following, some of these irregularities of ARM are briefly described.

#### 2.1.1.1 Conditional execution

All instructions can be *executed conditionally*. Along with each instruction, a condition mode can be specified. The condition mode corresponds to a predicate on the status flags (Z,N,C,V) of the processor. If the predicate holds, the instruction is executed. Conditional execution is used to eliminate control flow in a program. The basic idea is that conditional execution of few instructions is more efficient than a branch, due to control-hazards. This is especially true for deeply pipelined microarchitectures and simple branch prediction.

#### 2.1.1.2 Shifter operand

Most ARM instructions have two operands. The second operand is the so called *shifter operand*. Each arm instruction can apply a shift operation on this operand. For instance, an add instruction on two operands  $x, y$  actually performs the computation  $x + \text{shift0operation}(y)$ . The operand  $y$  is either an immediate or a register value. The definition of the shift operation is surprisingly complex. It uses one of 5 shift modes, such as “logical shift left” or “arithmetic shift right”. The set of modes even includes an extended 33-bit rotate operation, which involves the carry flag. The shift distance is given by an even immediate value.

#### 2.1.1.3 Registers

The ARM instruction set defines a set of 16 general purpose registers, which are accessed by most instructions. The last register (**r15**) is defined to be the program counter. Write accesses to this register therefore result in branches. As a result, any instruction that writes to **r15** is actually a branch instruction. Some of the other general purpose registers are dynamically reconfigurable. Depending on the processor mode (e.g. user-mode, supervisor-mode, interrupt-mode), these general purpose registers are associated with different physical storage.

### 2.1.1.4 Exceptional instructions

The ARM instruction set defines usual 32-bit arithmetic and logical instructions. Besides, it defines some exceptional instructions, such as 64-bit multiplications, multi-cycle load/store-multiple instructions and atomic swap instructions.

## 2.1.2 MIPS

The MIPS instruction set [28] is a rather simple and regular RISC instruction set. It uses only few exceptional concepts, which are outlined in the following. The specification of MIPS has primarily served as a proof of concept, to show that regular instruction sets can efficiently be specified in ViDL. Actually, the MIPS instruction set has been specified in only one day, as described in Section 8.2.2.

### 2.1.2.1 Multiplications

Most instructions read parameters from general purpose registers and write their result to general purpose registers. However, 64-bit multiplications use a dedicated 64-bit wide special purpose register. This register can not be accessed by “normal” instructions. The instruction set therefore includes dedicated instructions to transfer values between the 64-bit register and the general purpose registers.

### 2.1.2.2 Branches

All branch instructions have one delay slot, i.e. the instruction following a branch is always executed. This behavior must precisely be modeled by an instruction set specification, as it affects program semantics. The set of branch instructions includes less common *section-relative* branches. The target of these branches is the sum of the branch’s section address and an offset.

### 2.1.2.3 Zero register

The first general purpose register ( $r[0]$ ) is always read as zero. The register can be used as any other register, but must not be written. As the state of the register is never changed, it does not have to be implemented by a hardware register. An instruction set specification language should provide concepts to define constant registers. Otherwise, the generated hardware may include unnecessary registers.

Besides, typical RISC instructions, the MIPS instruction set defines instructions to operate on bit-slices. These instructions are used to access an arbitrary sequence of bits in a register. The range of the sequence is given by immediates and is therefore not known statically.

### 2.1.3 OISC — One instruction set computer

The instruction set of a “one instruction set computer” consists of exactly one instruction. An OISC has been specified in ViDL to demonstrate, that small instruction set specifications lead to small generated processors. This section briefly outlines the idea of OISCs and discusses some of their characteristics.

Although an OISC consists of only one instruction, it is Turing complete which means that any program can be expressed in terms of an OISC instruction set. An OISC is exceptional in two ways: First, its definition is very short and second, the defined instruction combines behavior of different instruction classes, such as load, arithmetic and branch.

Several flavors of OISCs have been proposed [18], which differ in the semantics of their instruction. The most common OISC defines a “subtract and branch if negative” (SBN) instruction. It was first proposed by van der Poel [52]. The SBN instruction has three parameters A, B and C and is defined by the following imperative code.

```

SBN(A,B,C)

{

MEM[A] := MEM[A] - MEM[B]

if MEM[A] < 0 then PC := C

}

```

The instruction subtracts two values from memory and writes the difference back to the minuend. If the difference is negative, the instruction branches to an absolute target address. In terms of classical RISC instruction sets, the instruction combines a load instruction, a store instruction, a subtraction and an absolute conditional branch. It can directly be defined in ViDL to generate a respective simulator.

However, it can not efficiently be implemented as processor for two reasons. First, it does not utilize registers, which allow for fast accesses. Second, the instruction includes data dependent read and write accesses to the main memory. It can therefore not be implemented using synchronous memory.

To circumvent these restrictions, this thesis uses a modified OISC instruction set. It defines one instruction memory and one register file with two read ports and one write port. The SBN instruction only operates on the register file. Data and instructions are thereby separated, similar to a Harvard-architecture. To initialize the register file, a “load immediate” instruction is added. Alternatively, one may define the registers to contain the constant  $c = 1$  or  $c = -1$  on initialization.

## 2.2 Design scenarios

During this thesis, several different processor and ISA design scenarios have been identified. These use cases have been considered during the development of ViDL. A design goal of ViDL is to support the developer in these scenarios.

This section is therefore essential to understand the design of ViDL. It is also a foundation for the review of related specification languages in Chapter 3.

### **Instruction set extensions (ISE)**

Some classes of algorithms include specific computations, which can not efficiently be mapped to the usual set of general purpose instructions. To accelerate these algorithms, an existing instruction set is enriched by application specific instructions. The instructions should be generic to some extend, to accelerate not only one specific algorithm, but a class of applications. At its best, this also includes future algorithms of the specific area of application.

In the ISE scenario, an existing ISA is extended by instructions and may also be extended by special purpose registers. The resulting ISA has to be backward compatible, such that legacy software can be executed and existing compiler tool-chains can be used. To enable backward compatibility, additional instructions are embedded into unused regions of the instruction space. The behavior of existing instructions remains unchanged. To demonstrate, that ViDL is suited for this scenario, an existing MIPS specification has been extended by instructions and special purpose registers, yielding the DNACore instruction set (Section 8.6).

### **Design space exploration (DSE)**

A DSE is performed to tailor a processor to a specific area of application. Therefore, certain dimensions of the ISA as well as the microarchitecture are explored. Typical dimensions of the ISA include the number of registers, the size of storages, the width of the datapath, the set of instructions and the delay of instructions. Interesting dimensions of the microarchitecture include the pipeline depth, forwarding, branch prediction and the implementation of functional units (e.g. multi-cycle multiplier vs. pipelined multiplier). As part of evaluation, the ISA design space (Section 8.2.4) and the microarchitectural design space (Section 8.5.3) have been explored.

### **Implementation of legacy ISAs**

There are legacy processors, which are still in use, but no longer supported and commercially available (e.g. Zilog Z8000 [57]). The implementation is defined in an out-of-date language and its microarchitecture is superseded by modern approaches. In this design scenario, a compatible processor is developed using a state-of-the-art microarchitecture. The foundation of development is the existing ISA manual.

### **ISA design from scratch**

The ISA is developed from scratch, based on the intended area of application. The designer has a rough idea of the new ISA and the applied concepts. All design decisions are freely made without considering existing designs.

### Improvement of microarchitecture

To improve the efficiency of a processor implementation, it is desirable to incorporate novel approaches in microarchitecture design into existing processors. This scenario may range from a minor local modification, which can easily be integrated into an existing implementation, to a major change, which necessitates a complete reimplementation of the processor. The resulting implementation must be compatible with respect to the ISA.

## 2.3 Domain specific languages

This section gives a brief introduction to language design guidelines for domain specific languages. They are used in Chapter 3 to review related specification languages. Besides, they have significantly influenced the design of ViDL. The guidelines are based on the books by Watt [54] and Sebesta [45]. Watt and Sebesta mainly focus on programming languages, but their language design guidelines can also be applied to ISA specification languages to some extend. In the following, language aspects that are essential for ISA specification are briefly summarized.

### Simplicity

A language should be simple from the user's point of view. This should also hold for new users. A steep learning curve may discourage developers that are new to the language. The language should be readable, i.e. the meaning of a specification should immediately be clear. The language should also be writable, which means that it should be easy to express a thought in terms of the language. The semantic gap between the developer's imagination and the language should be small. A language should provide a small set of generic and orthogonal constructs, instead of an extensive set of specialized and similar constructs. The constructs should be regular, which means that they can be combined arbitrarily to specify complex aspects of an instruction set. Chapter 4 discusses the concepts of ViDL with respect to simplicity.

### Reusability

Reuse is a major objective of engineering. The reuse of existing and tested components saves time, avoids flaws, and increases maintainability. Typically, reuse involves some kind of abstraction.

In software engineering for instance, functions are used to abstract from expressions. A function can then be called in different contexts with different arguments. Further concepts for reuse in software engineering are procedures, ADTs, classes, libraries and frameworks. In hardware engineering, similar concepts have emerged, such as entities, libraries (e.g. Design Ware Components) and IP cores (e.g. complete processor cores). The concepts for reuse in ViDL are primarily discussed in Section 4.5.

### Portability

To enable portability, a language should abstract from the target domain. For instance, the programming language C abstracts from the instruction set of a processor. A standard C program can therefore be compiled for different targets, such as x86 or PowerPC. The abstraction is provided by the compiler, which translates a C program into processor dependent machine code. The C program is therefore portable. However, the C language also demonstrates how easily portability can be broken. Most C Compilers feature a way to bypass abstraction by means of inline assembly, which belongs to the target domain. Abstraction and portability are thereby broken, which means that the code is not platform independent.

To guarantee portability, an ISA specification language should strictly abstract from target specific aspects. For instance, a processor specification should not define microarchitectural aspects, to allow for generation of different microarchitectural implementations. Besides, the specification should not contain fragments of C or VHDL code that are literally copied into the generated code. This would prevent generation of implementations in different target languages, such as VHDL or Verilog. Section 4.3 describes how ViDL realizes a thorough-going abstraction, which guarantees portability.

### Completeness

Typical general purpose programming languages are Turing complete, which means that any program that can be expressed in programming language X can also be defined in programming language Y. Completeness needs typically not be considered for general purpose programming languages and is not covered by Watt and Sebesta.

Domain specific languages however use a higher level of abstraction and thereby typically restrict the area of application. An aspect that can be expressed in a DSL X may not be expressible in a DSL Y and vice versa. Of course, bypassing techniques may be used as a back door to widen the applicability of the DSL. However, bypassing breaks abstraction and portability, as described earlier.

For an ISA specification language, the completeness is determined by the underlying ISA model. A very general model covers a large set of ISAs, but may restrict portability and efficiency. The ISA model of ViDL is discussed in Section 4.2.

### Reliability

Reliability means, that errors and flaws are avoided by the design of the language or detected by analyses of a compiler (respectively generator). The generator should check the input for errors, including static semantics. An undefined aspect should be detected and reported along with a meaningful error message to allow for rapid debugging.

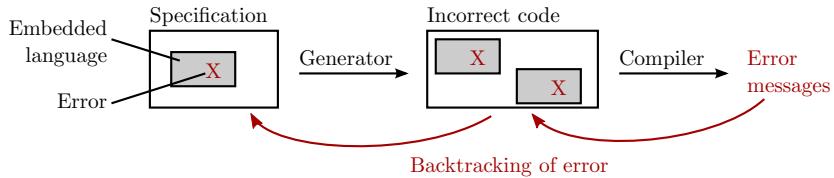

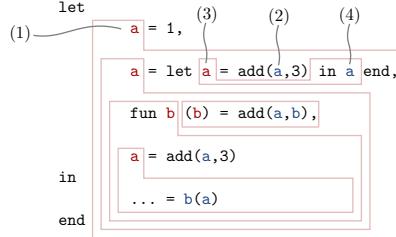

Figure 2.1: Tedious backtracking of errors as a result of embedded languages.

The ViDL generator for instance uses a powerful type-system to check the soundness of bit-widths (Section 4.9) as part of static semantics. In contrast, the embedding of target language code fragments makes such analyses virtually impossible. Figure 2.1 shows an example, where the code of an embedded language contains an error X. The embedded language is not under the generator’s control and therefore not checked. The generated code includes a copy of the embedded code, which is incorrect. Hence, the generated code is refused by subsequent tools and tedious backtracking is required to relate the reported error to its source.

### Consistency

In general, a source language may be translated into different implementations and different target languages. A C program may for instance be compiled for ARM and for Intel processors. To increase performance, the program may contain target specific blocks of inline assembly, one for ARM and one for Intel. These blocks are independent but are supposed to implement the same behavior. This bypassing of target specific code has two major disadvantages. First, the development effort is increased, as the same behavior is specified multiple times in different languages. Second, the developer is responsible to write semantically equivalent code.

In the context of an ISA specification, redundant C and VHDL code may lead to different behavior of the simulator and the microarchitectural processor implementations. Hence, excessive testing of the implementations is required, as described in [13]. Since ViDL does not require alternative specifications for different implementation domains, consistency is guaranteed.

## 2.4 Compilation methods

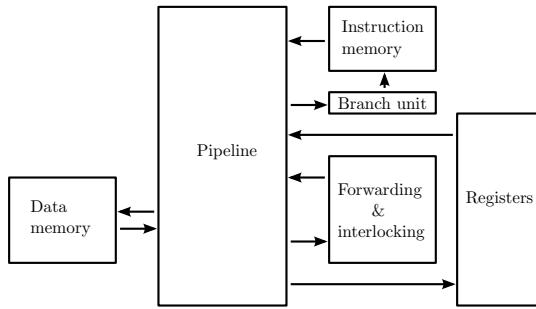

As part of this thesis, two generators have been developed — a simulator generator and a processor generator. The simulator generator translates a ViDL specification into a processor simulator, which is implemented in the imperative programming language C. The processor generator translates a ViDL specification into a hardware description of a pipelined processor. The structures of the target codes are very different from the source language. The generator therefore requires sophisticated compiler techniques for translation and optimization.

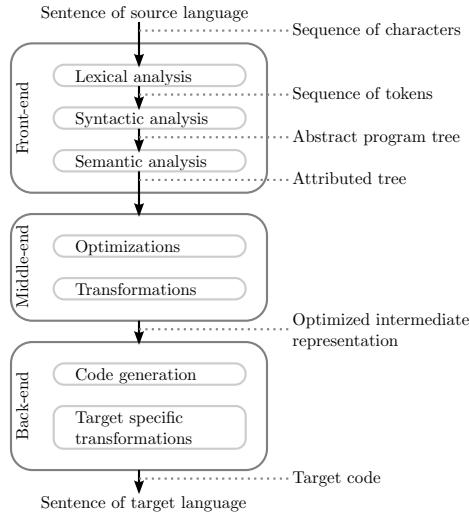

Figure 2.2: Generic structure of a compiler.

This section is intended to give a basic overview of these techniques. In-depth information can be found in literature [30, 32]

In general, a compiler translates a sentence of a *source language* into a semantically equivalent sentence of a *target language*. A C-compiler for instance may translate a sentence of the source language “C” into an equivalent sentence of the target language “Intel x86 Assembler”, where the sentence is a program. In the following it is assumed, that the source language is a programming language. However, the same applies to other formal languages.

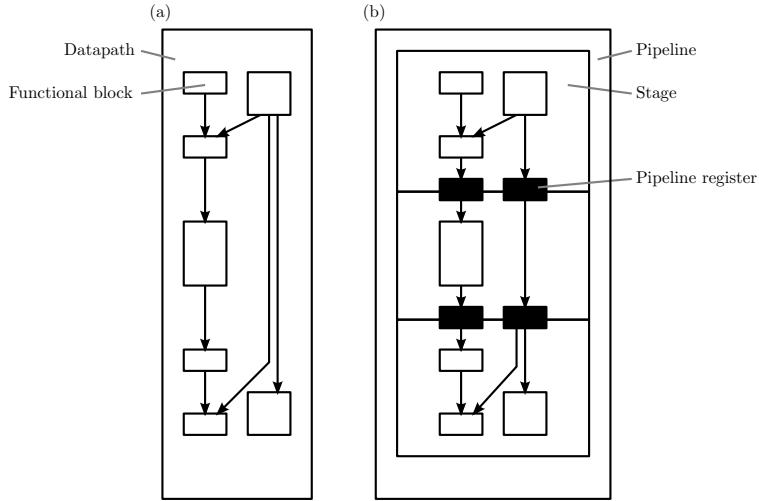

The generic structure of a compiler is shown in Figure 2.2. It consists of a front-end, a middle-end and a back-end. The *front-end analyzes* the sentence of the source language and yields an *intermediate representation (IR)* of the sentence. The *middle-end* optimizes the representations using sophisticated analyses and transformations. The *back-end* finally produces the target code. This step is also known as *code generation*. Before generating code, the back-end may also apply target specific optimizations on the intermediate representation.

### 2.4.1 Front-end

The front-end of a compiler can be further subdivided into the lexical, syntactic and semantic analysis. During *lexical analysis*, a *scanner* transforms the sentence of the source language (sequence of characters) into a sequence of *tokens*. A token represents an atomic element of the source language, such as a keyword, identifier or literal. The C-code “`return a+1`” is for instance divided into a sequence of 4 tokens. The tokens `return` and `+` are keywords, `a` is an identifier and `1` is a literal.

During *syntactic analysis*, a *parser* structures the sequence of tokens. The

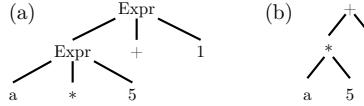

Figure 2.3: Example of (a) an abstract syntax tree and (b) a corresponding Kantorovich tree (b).

result is an *abstract syntax tree (AST)*, which reflects the structure of the sentence. For example, the abstract syntax tree of the C-expression  $a*5+1$  is shown in Figure 2.3a and is similar to its Kantorovich tree in 2.3b.

During *semantic analysis*, static properties of the abstract syntax tree are analyzed. The analysis uses a *tree walking algorithm* to annotate nodes of the AST with attributes. Semantic analysis typically includes *name analysis* and *type analysis*. Name analysis *binds* identifiers to so called *entities*. The uses of an identifier “a” are for instance bound to the respective variable. Note, that in most languages, different entities may share the same identifier. Name analysis therefore needs to consider the language’s *scope rules*.

The second major semantic analysis is that of types. For a *statically typed* language, type analysis determines the types of program entities, such as variables and functions. For simple *explicitly typed* languages, types may be determined by a tree walking algorithm. For *implicitly typed* languages like SML, types are determined by *type inference*. Basically, type inference solves a system of equations, where a variable represents the type of a program entity. Equations express type constraints between these entities. A solution of the system of equations is thereby a valid assignment of types to entities. Type analysis is explained in Section 2.5.

### 2.4.2 Middle-end

The middle-end implements *optimizations* on the intermediate representation. At its best, these optimizations are independent from source and target languages. An optimization transforms the intermediate representation such, that certain characteristics of the resulting target sentence are improved. For instance, a C-compiler includes optimizations to increase the execution speed of the resulting program. A valid optimization must preserve the semantics of the intermediate representation. Its interpretation before and after optimization must be the same. Examples of optimizations include *dead code elimination*, *evaluation of constant expressions* and *function inlining*.

### 2.4.3 Back-end

*Code generation* in the back-end translates the intermediate representation into code of the target language. In case of source to source translation, a *pattern based* code generator may be used. Such a generator uses text patterns of the

Figure 2.4: Generation of compiler components.

target language, which include insertion points for other fragments of target code.

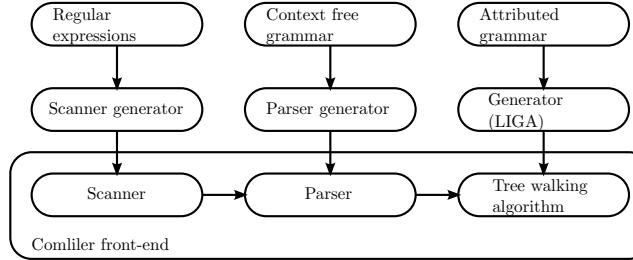

#### 2.4.4 Compiler framework

Compiler frameworks enable the efficient implementation of compilers [32]. Significant parts of the front-end can be generated, including the scanner, parser and tree walking algorithm. Figure 2.4 shows an overview of the front-end, its components, their specification and the involved generators. The *Eli compiler framework* [31] supports all three components shown in the figure. The generators are well integrated, i.e. a developer does not have to care about the interface between compiler stages. In contrast, the combination of *Flex and Bison* [9, 42] covers only the lexical and syntactic analysis. An advantage of Flex is, that different scanner modes can be defined, where each mode activates a certain set of tokens. During analysis, the mode can be changed to activate different subsets of tokens. This feature is required for embedding of languages, such as embedding C in a domain specific language.

## 2.5 Type systems

In ViDL, each value is a bit-string. The widths of such bit-strings needs to be known for code generation. However, it is not specified explicitly by the developer in ViDL. Instead, bit-widths are determined by the generator. Therefore, they are modeled by a type system and inferred by type-inference.

This section gives the foundation for ViDL’s type system, which is discussed in Section 4.9. In computer science, a *type* is defined by a *set of values* and *operations* on these values [45]. A 32-bit unsigned integer type represents for instance the set of integral numbers from 0 through  $2^{32} - 1$

$$\text{setOf(uint32)} = \{x \mid x \in \mathbb{Z} \wedge 0 \leq x < 2^{32}\}$$

Operations on this type include 32-bit addition, and multiplication.

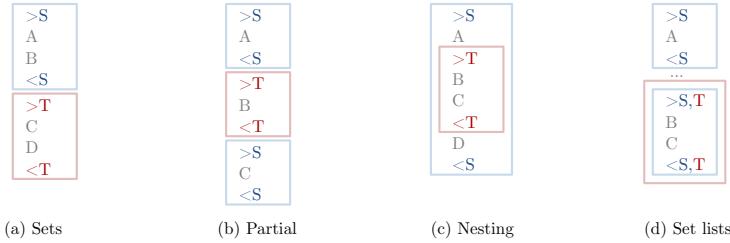

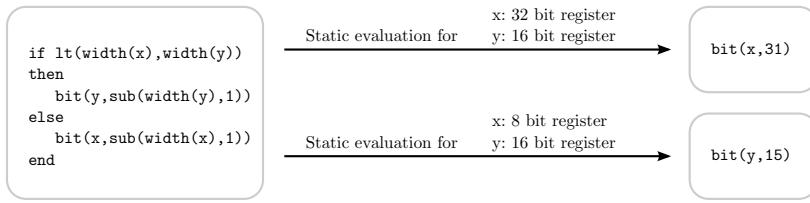

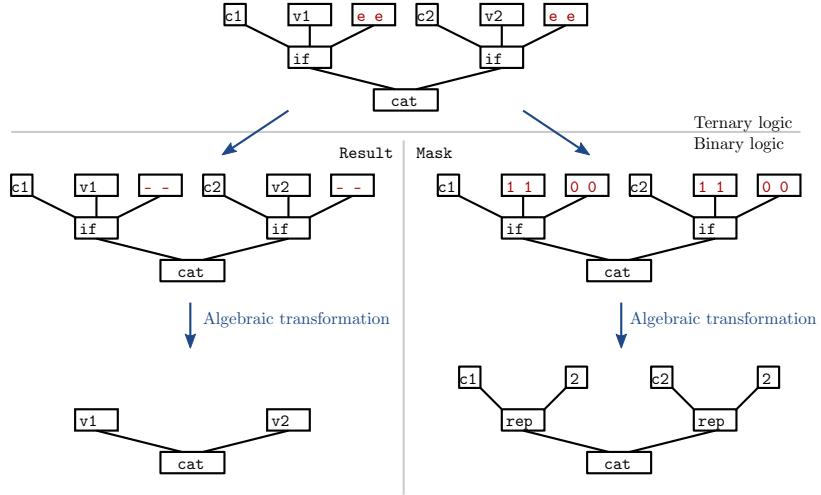

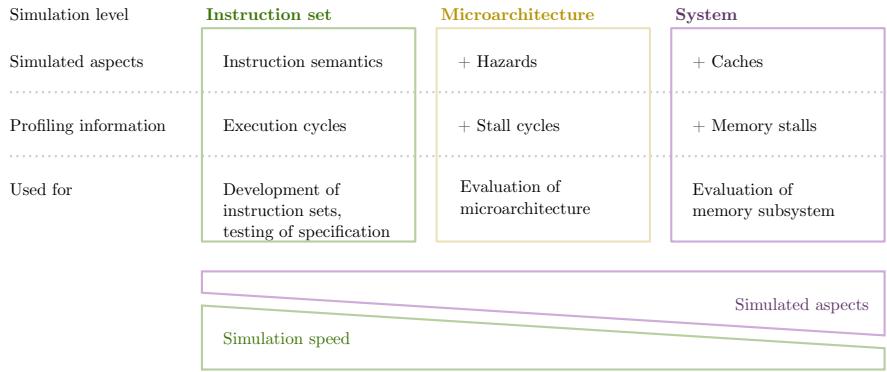

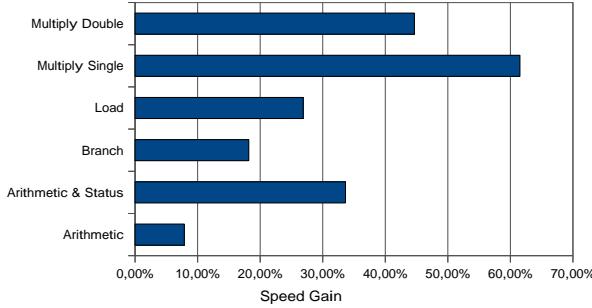

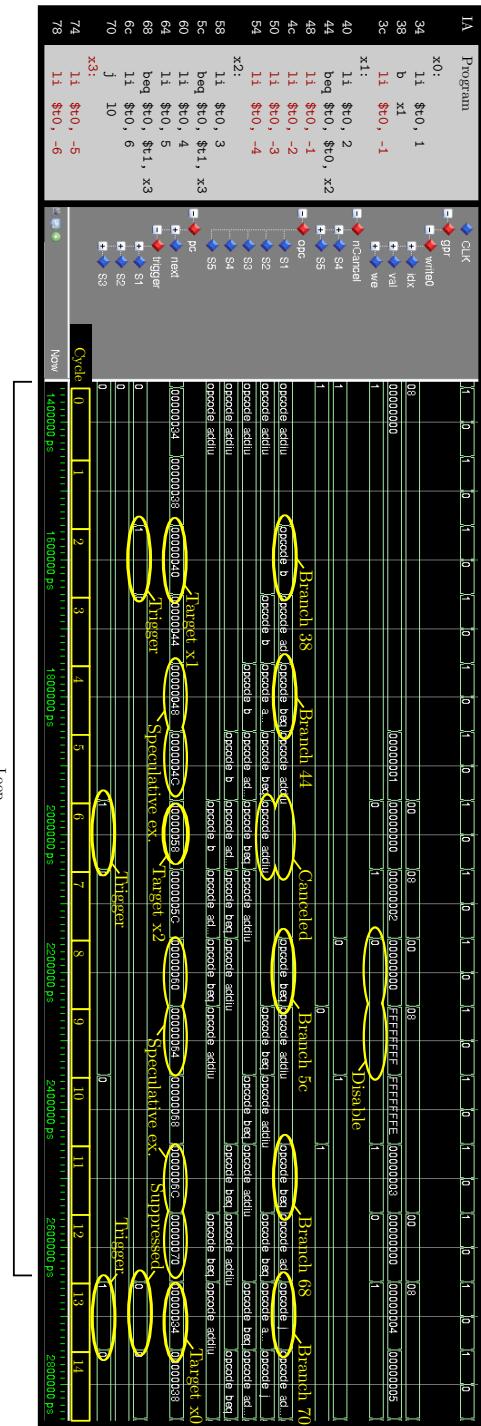

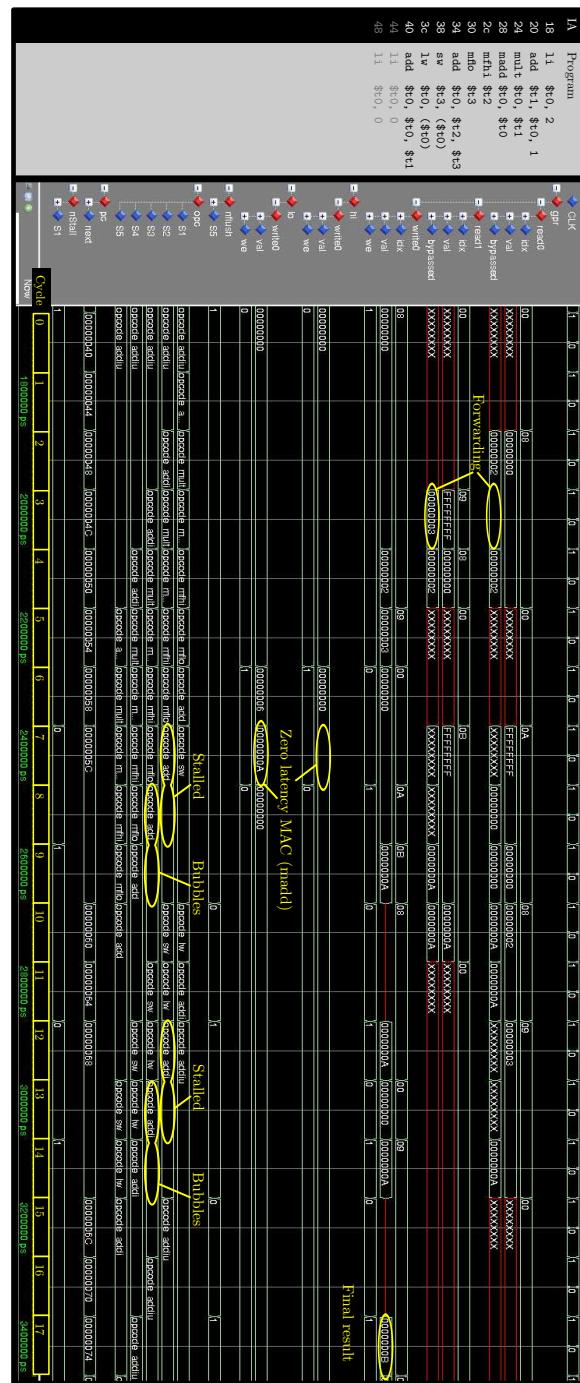

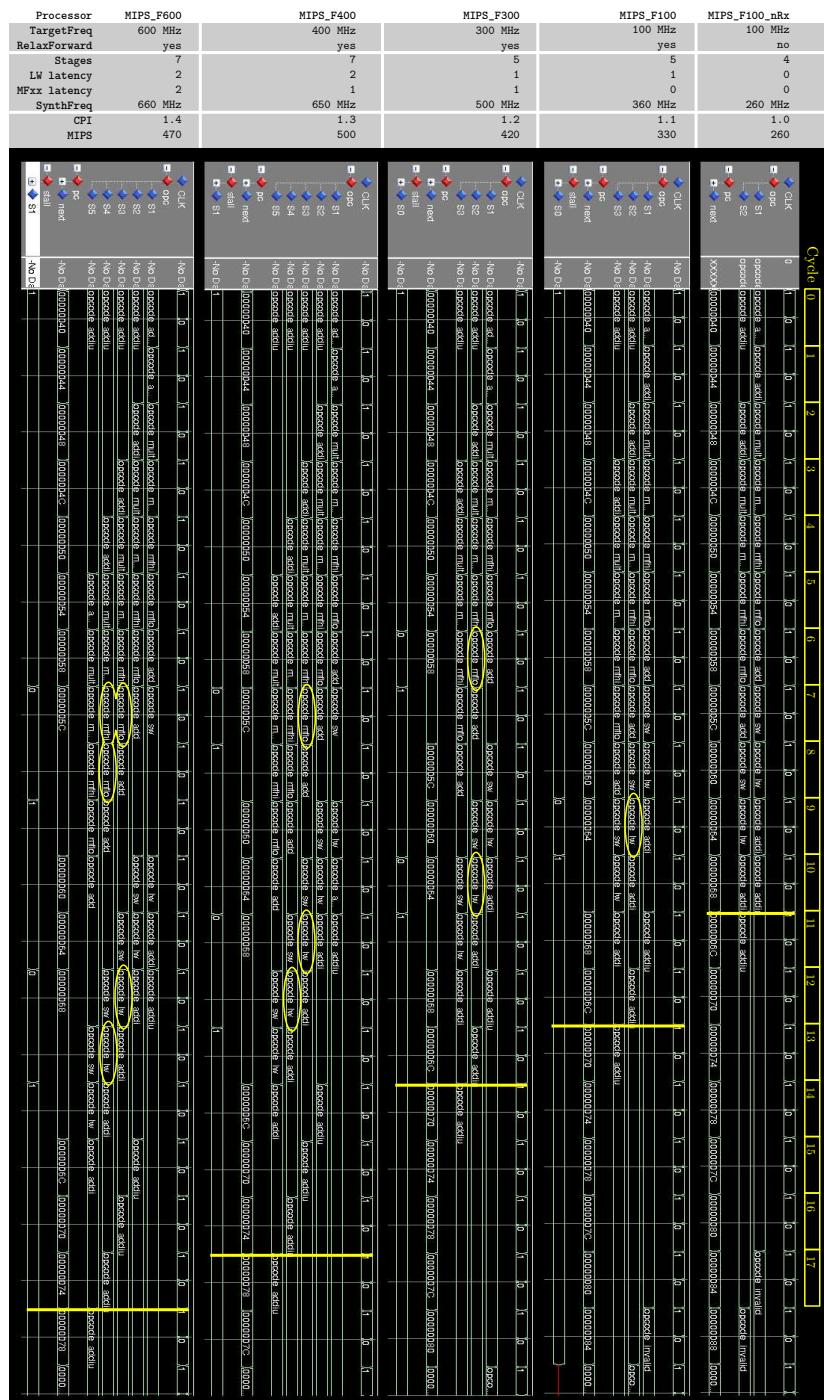

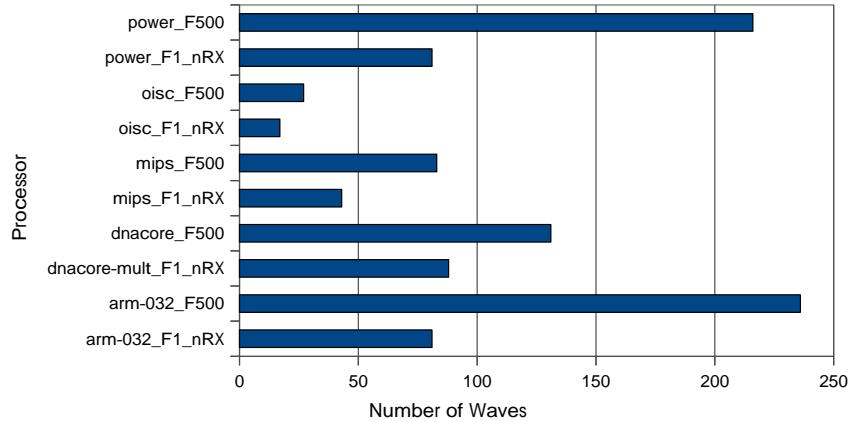

### 2.5.1 Subtyping