A CONCEPT FOR THE EDITING OF HARDWARE

RESULTING IN AN AUTOMATIC HARDWARE-EDITOR

Franz J. Rammig

University of Dortmund

Federal Republic of Germany

Abstract

It is the aim of this paper to investigate a system, which, with no manual or mechanical interference, permits the building, changing, processing and destruction of real (not simulated!) digital hardware.

It can be seen, that by the above nothing else than a hardware-editor is outlined. Therefore first a "mini-model" of a usual text-editor is given within this paper. Then this model is transferred to problems of the editing of hardware.

The main problem in particular, i.e. the problem of keeping the timing under control, will be discussed on the basis of an exact algebraic model of the time-behaviour of digital circuits.

The result of these discussions will be the concept of an automatic hardware-editor.

Finally a realization of this concept built by the author within the University of Dortmund, W. Germany, will be discussed.

A "Mini-Model" of a usual text-editor

A text-editor may be described by a triple  $(A, C, F)$  where:

$A$  is an alphabet (e.g. the set of representable ASCII-characters) and

$C$  is a finite, non-empty set of commands.

The semantics of a command is given by a function associated with each command:

$$\bigwedge_{c \in C} f_c : A^* \rightarrow A^*$$

which defines how a string  $s \in A^*$  is manipulated by the command  $c \in C$ .

Let  $F := \{f_c \mid c \in C\}$  be the set of all those semantic defining functions.

Given a string  $s \in A^*$  and a sequence of commands

$$\tilde{c} := c_n \dots c_0, \quad \bigwedge_{0 \leq j \leq n} c_j \in C$$

$f_{\tilde{c}}(s) := f_{c_n}(\dots(f_{c_0}(s))\dots)$  is called an editing of a string  $s$ .

Due to the fact that you have only a fixed finite memory available, strings may be represented as elements of  $A^n$  instead of  $A^*$  where  $n$  is the number of memory-cells available.

This may be done by introducing a special symbol "end of text" (EOT). Now, e.g., the string  $abcd \in A^*$  may be represented by any element of the set

$$\{abcdEOTx' \mid x' \in A^{n-4}\}.$$

A "Mini-Model" of a Hardware-Editor

Given an ordered set of modules  $M := \{m_1, m_2, \dots, m_k\}$ , each with an ordered set of inputs and outputs  $IO_{m_i} := \{i_{m_i, 1}, \dots, i_{m_i, r}, o_{m_i, 1}, \dots, o_{m_i, s}\}$ , an ordered set of pins

$P := \{p_1, \dots, p_n\}$  and a one to one mapping

$$b: \{io_{m_i, j} \mid io_{m_i, j} \in IO_{m_i} \wedge m_i \in M\} \rightarrow P,$$

a hardware-editor may be modelled in a similar manner: Let  $R$  be the maximal nonreflective antisymmetric relation on  $P$ , i.e.

$$R := \{(p_i, p_j) \in P \times P \mid i > j\} \text{ and } k := (n^2 - n)/2 = |R|.$$

Let  $HA := \{w, u\}$  ( $w$  stands for "wired",  $u$  for "unwired") be the alphabet,

$HC$  the finite non-empty set of commands, each with the semantic defining function

$$f_{hc} : HA^k + HA^k \text{ and } HF := \{f_{hc} \mid hc \in HC\}.$$

Then  $(HA, HC, HF)$  defines a hardware-editor.

Relative to the set of modules  $M$  and the mapping  $b$  any circuit is uniquely defined by a "string"  $c \in HA^k$ .

As module-outputs may not be connected together this may further be simplified:

Let  $(I, O)$  a partition on  $P$ ,  $I$  being the ordered set of module-inputs,  $I := \{i_1, \dots, i_k\}$ ,  $O$  the ordered set of module-outputs,  $O := \{o_1, \dots, o_e\}$  then  $HA$  can be replaced by  $HA' := \{1, 2, \dots, e\}$ ,  $HC$  by a set of commands  $HC'$  with a set of semantic describing functions  $HF'$  with:

$$\bigwedge_{h' \in HF'} h' : HA'^k + HA'^k.$$

$h' \in HF'$

Again, relative to a given set of modules and a mapping  $b$ , any circuit  $c$  is uniquely defined by a "string"  $c \in HA'^k$ .

From description to construction

From the above discussion one could imagine that the problem of building an automatic hardware-editor is a triviale one; the problem should be solved by providing  $k^k$  selectors "1 out of  $e$ ", connecting the outputs of the modules with the inputs of all selectors and the outputs of the selectors with the inputs of the modules. All editing would be done by manipulating the data on the address-lines of the selectors.

In fact, this will be the heart of our hardware-editor. But unfortunately some nontrivial problems arise:

- There is a severe distortion of the time-behaviour of the circuit because of the time-behaviour of the selectors and interfacing-logic. Thus the behaviour of a circuit built in this manner will be rather different from the behaviour of a hard-wired one.

- Even this irrelevant behaviour of the circuit cannot be readily observed because the timing is controlled by the circuit instead of being dictated by an observation mechanism.

Therefore in addition to an interconnection mechanism a time-controlling mechanism must also be provided.

To do this, one must have available an exact model of the time-behaviour of digital circuits.

#### Simplified Quasi Real Boolean Functions

Besides more global models  $1, 2, 3, 4$  such a model is given by the so called "Quasi Real Boolean Functions"<sup>5</sup>. Those functions allow a very precise description of the logic and the time-behaviour of digital circuits. In this paper a slightly modified approach will be presented. The modification has been done to allow an easier implementation of a hardware-editing-system based upon this model. On the other hand the modelling power is decreased very little by the modification.

As we want to describe the time-behaviour as well as the logic behaviour we must treat the set of functions

$$e := f: (\sigma_T)^n \rightarrow (\sigma_T)^m \quad n, m \in \mathbb{N}$$

mapping an  $n$ -tuple of signal-sets  $\sigma_T$  into an  $m$ -tuple

of these signal-sets, instead of treating Boolean

$$F: \{0,1\}^n \rightarrow \{0,1\}^m$$

By a signal-set we mean the set

$[0,1]^T$ , where  $T$  is the set  $\mathbb{R}$  of real numbers or a denumerable set with the ordering and metric adapted from  $\mathbb{R}$ .

In the following we restrict ourselves on signal-sets  $T$ , with

a)  $T$  denumerable

b)  $|t_{i+1} - t_i| = |t_i - t_{i-1}|$  for all  $i \in \mathbb{Z}$  (equidistancy)

c)  $a_{t_i} \in \{0,1\}$  for all  $i \in \mathbb{Z}$

and all functions mapping those sets.

Def 1 A function  $h: (\sigma_T)^n \rightarrow (\sigma_T)^m$  is called

Ideal Boolean Function iff

$$h': \{0,1\}^n \times \{0,1\}^m \xrightarrow{\sigma_T} \bigwedge_{t_o \in T} \bigwedge_{t_o \in T} \text{pr}_{t_o}(h(x)) = h'(\text{pr}_{t_o}(x))$$

where  $\text{pr}_{t_o}$  is the projection at the time  $t_o$ .

With  $h'_j$  we will denote the  $j$ -th image-component.

By an inertial-delay-specification we mean a triple of finite integers,  $ID := (up, dn, in)$ , "up" specifying the delay of an "up"-transition, "dn" of a "down"-transition and "in" specifying the minimum number of consecutive points of time for which a signal must have an identical constant value to be accepted (inertia). In addition "in" must be less than the minimum of "up" and "dn".

Def 2 Let  $ID := (up, dn, in)$  be an inertial-delay-specification,  $md := \max\{up, dn\}$ . With respect to  $ID$  we call  $idf: \sigma_T \rightarrow \sigma_T$ , inertial-delay-function iff

$$\bigvee_{idr': \{0,1\}^{md+in} \times \{0,1\}^n \xrightarrow{\sigma_T} \bigwedge_{t_o \in T} \bigwedge_{t_o \in T} \text{pr}_{t_o}(idr(x)) = idr'(\text{pr}_{t_o}(x), \dots, \text{pr}_{t_o-(md+in)}(x))$$

where

$$idr'(\text{pr}_{t_o}(x), \dots, \text{pr}_{t_o-(md+in)}(x)) =$$

$$\{ \text{pr}'_{t_o-up}(x) \text{ if } \text{pr}'_{t_o}(x) = 1$$

$$\text{pr}'_{t_o-dn}(x) \text{ if } \text{pr}'_{t_o}(x) = 0$$

$$\text{and } \text{pr}'_{t_o-up}(x) \neq \text{pr}'_{t_o-dn}(x) \Leftrightarrow$$

$$\bigvee_{t_o > t_k > t_{o-(up)}} \bigwedge_{t_o-(up) > t_j > t_{o-(dn)}} \bigvee_{t_o-(dn) > t_{o-(up)+in}}$$

with

$$\text{pr}_{t_k}(x) \neq \text{pr}_{t_{o-(up)}} \wedge \text{pr}_{t_o}(x) \neq \text{pr}_{t_{o-(dn)}}$$

An inertial-delay-specification is called pure-delay-specification if "in" has the value 0. An inertial-delay-function defined with respect to a pure-delay-specification is called pure-delay-function.

Def 3 Let  $ID_i = (up_i, dn_i, in_i)$ ,  $i = 1, \dots, n$ , be inertial-delay-specifications and

$$PD_j = (up_j, dn_j, 0)$$

,  $j = 1, \dots, m$ , be pure-delay-specifications.

Let be  $udi := \max\{up_i, dn_i\}$ ,

$$1 \leq i \leq n$$

$$udo := \max\{up_j, dn_j\}$$

$$1 \leq j \leq m$$

$$uin := \max\{in_i\}$$

$$1 \leq i \leq n$$

$$his := udi + udo + uin$$

A function  $q: (\sigma_T)^n \rightarrow (\sigma_T)^m$  is called a

Simplified Quasi Real Boolean Function (SQRBF) iff

$$\bigvee_{q': \{0,1\}^n \rightarrow \{0,1\}^m} \bigwedge_{x \in (\sigma_T)^n} \bigwedge_{t_o \in T} \text{pr}_{t_o}(q(x)) = q'(\text{pr}_{t_o}(x), \dots, \text{pr}_{t_o-his}(x))$$

$q'$  is defined by  $(q'_1, q'_2, \dots, q'_m)$  where

$$q'_j(\text{pr}_{t_o}(x), \dots, \text{pr}_{t_o-his}(x)) =$$

$$\text{odf}_j(h'_j(\text{idf}_1(\text{pr}_{t_o}(x), \dots, \text{pr}_{t_o-(up_i+in_i)}(x)), \dots, \text{idf}_n(\text{pr}_{t_o}(x),$$

$$\dots, \text{pr}_{t_o-(up_i+in_i)}(x)), \dots, h'_j(\text{idf}_1(\text{pr}_{t_o}(x), \dots, \text{pr}_{t_o-udo}(x)), \dots,$$

$$\text{idf}_n(\text{pr}_{t_o}(x), \dots, \text{pr}_{t_o-udo}(x)))$$

$$h'$$

with the image-components  $h'_1, \dots, h'_m$  being the

function used above to define Ideal Boolean Functions,

$\text{idf}_i$  being the inertial-delay-function defined with

respect to  $ID_i$  and  $\text{odf}_j$  being the pure-delay-function

defined with respect to  $PD_j$ .

If we want to describe the behaviour of a module relative only to the input-values at a single point of time we have to replace the function by an automaton.

It can easily be seen that the following automaton describes the behaviour of a SQRBF:

$A := (X, Y, S, \delta, \lambda)$  with

$$X := \{0,1\}^n$$

$$Y := \{0,1\}^m$$

$$S := s_{1,0}, s_{1,1}, \dots, s_{1,udi}, s_{2,0}, \dots, s_{1,n}, udi, \dots, s_{m,0}, \dots, s_{m,udo}$$

$\delta$  is defined by :

$$1) \bigwedge_{1 \leq j \leq m} \bigwedge_{0 \leq k \leq udo} \delta(s_{j,k}) = s_{j,k-1}$$

$$2) \bigwedge_{1 \leq i \leq n} \bigwedge_{0 \leq k \leq in_i} \delta(s_{i,k}) = s_{i,k-1}$$

$$3) \bigwedge_{1 \leq i \leq n} \delta(s_{i,in_i+1}) = \begin{cases} s_{i,in_i} & \text{if } \bigvee_{0 \leq k \leq in_i} s_{i,k} \neq s_{i,k-1} \\ s_{i,in_i} & \text{otherwise} \end{cases}$$

$$4) \bigwedge_{1 \leq i \leq n} \bigwedge_{in_i \leq k \leq udi} \delta(s_{i,k}) = s_{i,k-1}$$

$$5) \bigwedge_{1 \leq i \leq n} \delta(s_{i,0}) = x_i$$

$$6) \bigwedge_{1 \leq j \leq m} \delta(s_{j,1}) = f'_j(a_1, \dots, a_n) \text{ with } \bigwedge_{1 \leq i \leq n} a_i = \begin{cases} s_{i,up_i} & \text{if } x_i = 1 \\ s_{i,dm_i} & \text{if } x_i = 0 \end{cases}$$

$$\lambda \text{ is defined by}$$

$$\lambda | y_j = \begin{cases} s_{j,up} & \text{if } s_{j,1} = 1 \\ s_{j,dn} & \text{if } s_{j,1} = 0 \end{cases}$$

Note that the behaviour of this automaton is undefined with respect to word-prefixes of a certain length, as we allow each state to be an initial one. One sees immediately that this automaton has an extremely simple structure which can be realized with a set of shift-registers and very simple additional logic.

Now this simple automaton allows us to get the time under control.

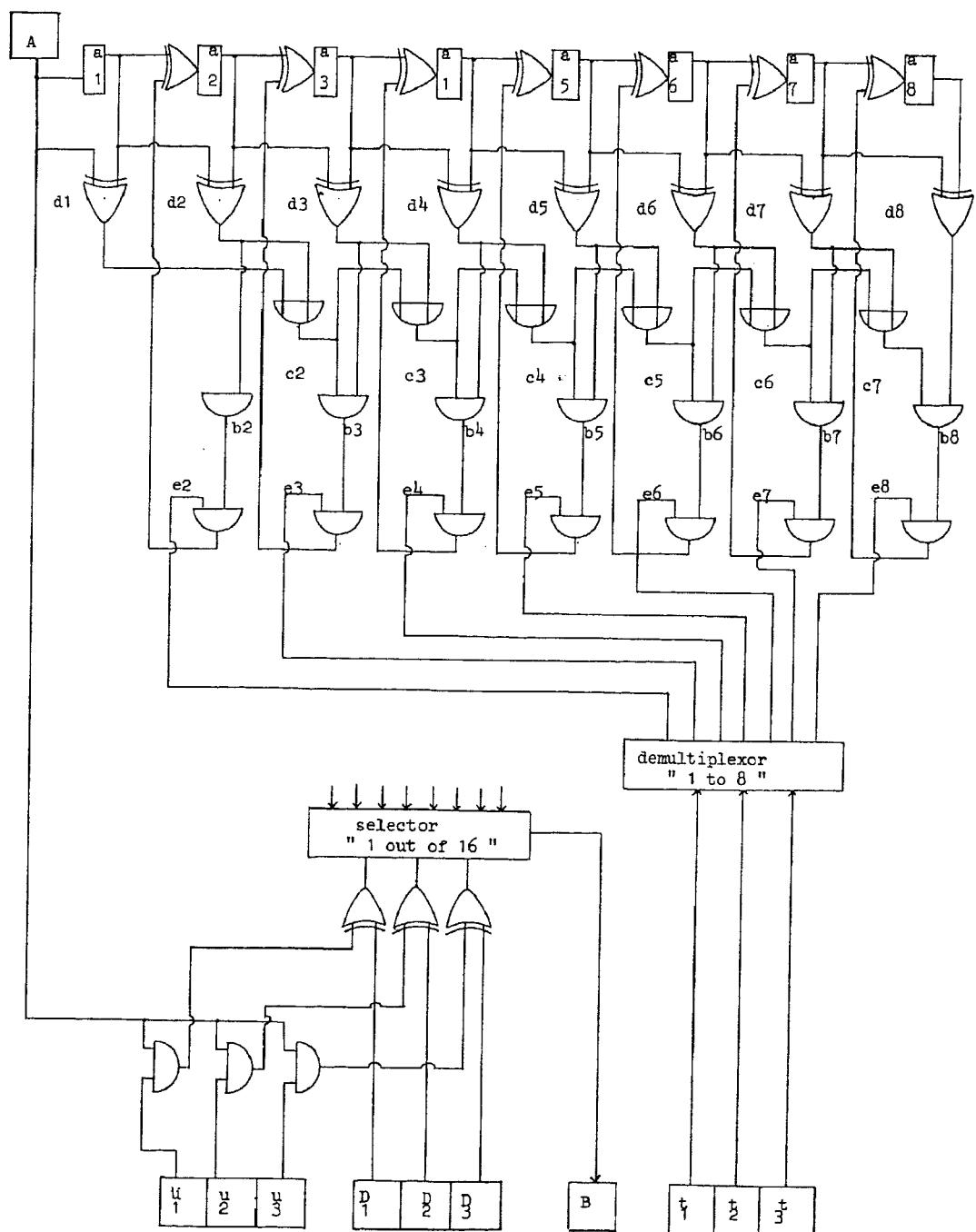

The basic idea is to represent only the logic behaviour of the modules by the modules themselves. The time-behaviour is represented by providing a circuit realizing a pure-delay-function for every module-output ("crossbar"-input) and an inertial-delay-function for every module-input ("crossbar"-output).

In this way time is under full control of the system, allowing us to stretch, distort and even to stop and restart time without any falsification of the modelling result.

Our system therefore is not only a hardware-editor but also includes an "All-channel State Analyser" without any time-limit.

#### The META-46 "GOLDLAC", a realization of the above concept

At the University of Dortmund, we decided to build a system realizing the above concepts in standard TTL-technology. We have restricted ourselves to a system allowing us to construct automatically a digital circuit from a given but changeable set of modules where the sum of module-outputs must not be greater than 128 and the sum of the module-inputs not greater than 192.

From the above discussion it follows that for the basic system we need

- a "crossbar" : "128 x 192" (simplified)

- 128 times a realization of a universal pure-delay-function

- 192 times a realization of a universal inertial-delay-function.

#### The "crossbar"

From the above discussion it follows, that the "crossbar" consists simply of 192 selectors "1 out of 128". Such a selector can be built very easily from standard TTL-chips using a two-level realization.

In addition, a 7-bit register is needed to store the address of the actual selected line. The actual data within these 192 7-bit registers specifies, relative to the set of modules plugged in at that moment, the circuit being built by the system.

From this it follows that, based on a given set of modules, up to  $2^{134}$  different circuits may be built without any manual interference.

Our "crossbar" consists of 24 PC-boards, each containing 8 selectors "1 out of 128" with their registers and some bus-interfacing logic.

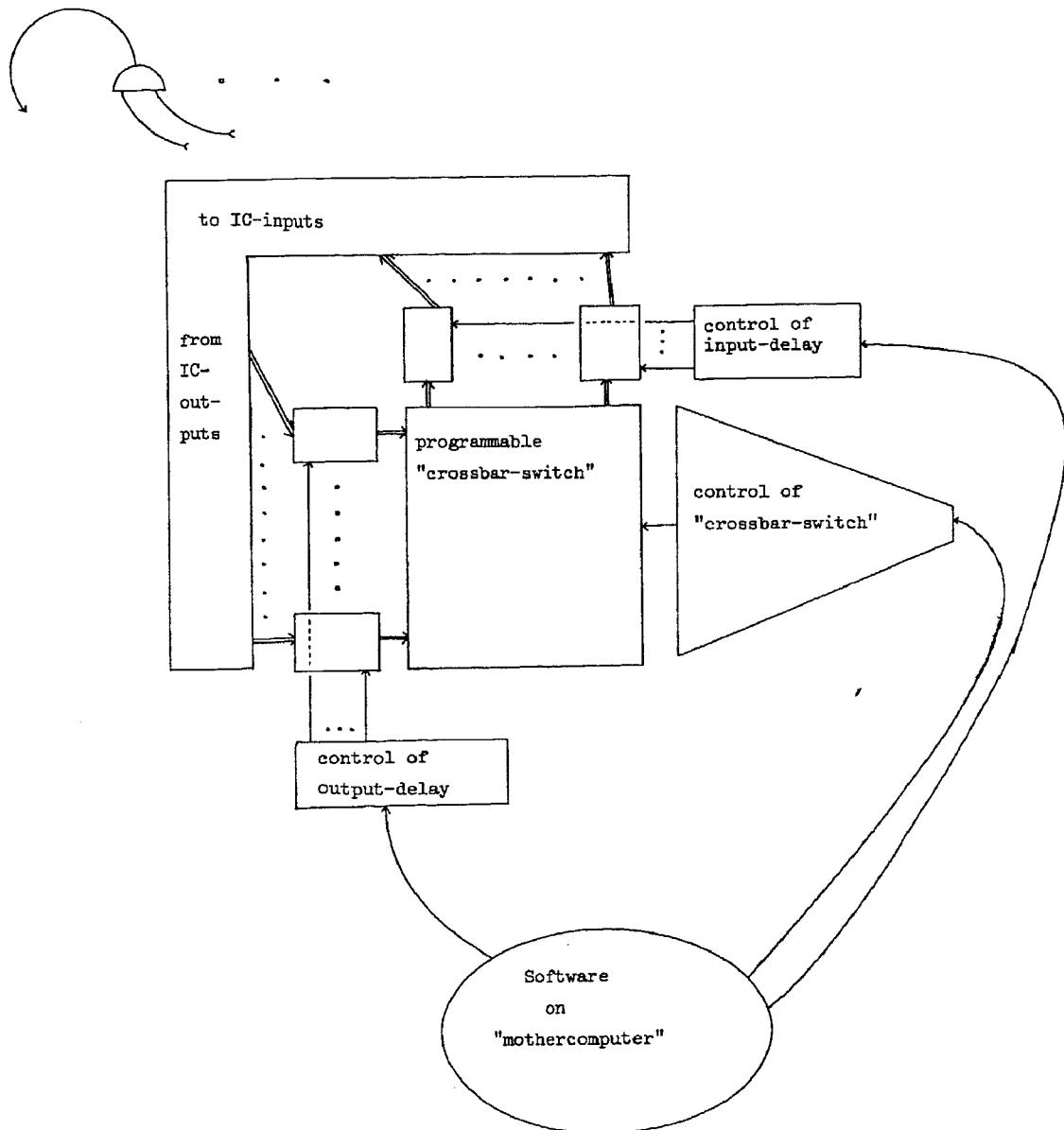

#### The realization of a universal pure delay function (see fig. 1)

We wanted to be able to assign a delay to every module-output with the aid of the system. The system should allow us to have different delays for up- and down-transitions.

We have restricted ourselves to a possible range of delay between 1 and 16 time-units. A time-unit may

stand for one nano-second (for example) and is represented by one clock-cycle within the system. Thus, a universal pure-delay-function can be built very easily out of a parallel readable 16-bit shift-register, a selector "1 out of 16", two 4-bit registers to store the actual "up"- and "down"-delay and some additional circuitry. (this circuitry consists only of 4 EXOR-gates and 4 AND-gates, as we store the bit-wise boolean difference between the "up"-delay and the "down"-delay in the register for the "up"-delay).

In our system the set of 128 pure-delay-functions is distributed on 8 PC-boards, each containing 16 pure-delay-functions.

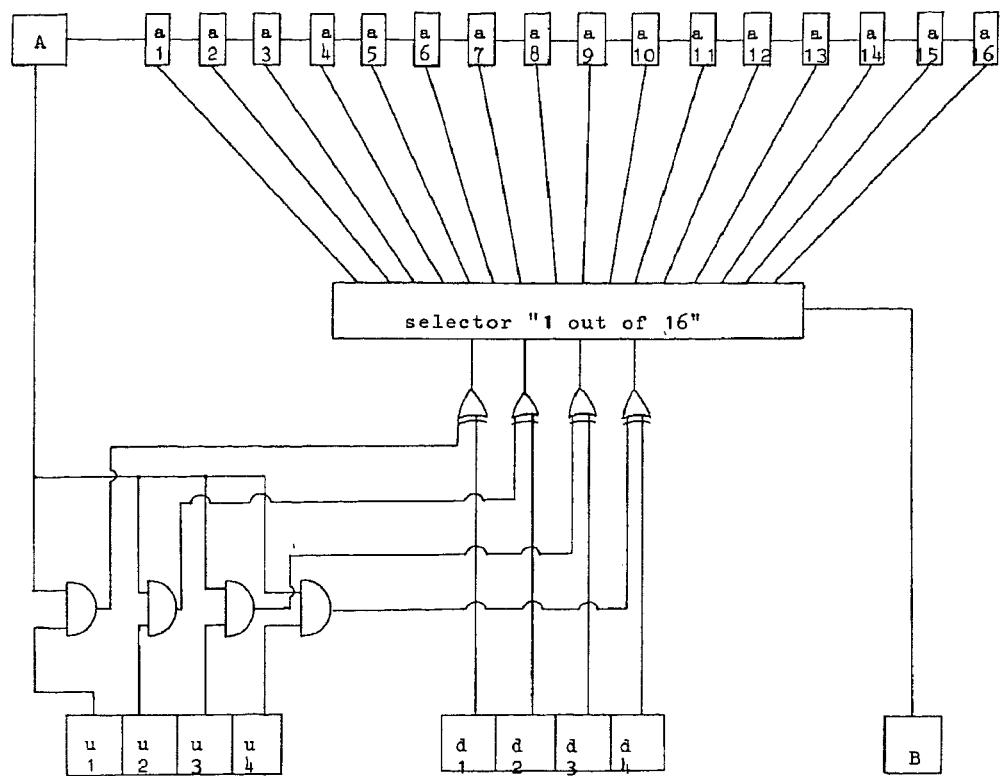

#### The realization of a universal inertial-delay-function (see fig. 2)

As we wanted to be able to assign an inertial-delay to each module-input, we had to construct a realization of a universal inertial-delay-function. This has been done by adding some circuitry for a universal inertia representation to the realization of a pure-delay-function. As this complicates the circuit, we restricted ourselves to a range for delay and inertia between 1 and 8 time-units.

The inertia is implemented by adding to a pure-delay-function the ability to store into the n-th cell of the shift-register not only the contents of the n-1-th cell but also the complemented value of this cell.

The latter is done iff

- 1) the n-th output of an inertia specifying demultiplexor carries a "high",

- 2) the n-th and the n-1-th cell carry different values,

- 3) any two other adjacent cells  $i, i-1$  with  $i < n-1$  carry different values.

In our system the set of 192 universal inertial-delay-functions is distributed on 24 PC-boards, each containing 8 such functions.

#### Additional components of the META-46 "GOLDLAC"

Since circuits of interest are generally not autonomous, the inputs into a circuit under test must be representable.

We do this with the aid of an additional 128-bit register. Each of the lines going into the "crossbar" may be connected with the corresponding cell of this register instead of being connected with a module-output. This is controlled by selectors "1 out of 2" which in turn are controlled by another 128-bit register.

Secondly, observation of the automatically built circuit must be possible, of course. For this purpose, an arbitrary subset of the 128 lines going into the "crossbar" can be selected as "signalset of interest". Any transition on one of these selected lines causes an interrupt signal that stops the machine, preserving its actual state. This state may then be read by a controlling mini-computer, which is also used to fill all the registers of the system.

For our system we use a PDP-11 as "mother-computer", coupled with the META-46 "GOLDLAC" by a parallel interface.

On this PDP-11 a small software-package that allows an interactive processing of the system is in operation.

Relative to a given set of modules the user defines a circuit by specifying the connections and assigning delays and inertias to lines. If he supplies his own set of modules, he first must describe it.

In addition he defines some circuit-inputs and a set of lines of interest. He may also change all his specifications interactively as in usual text-editors.

Having specified his circuit, he loads and starts the system by a simple command. At any time when one of his "signals of interest" changes its value, the values of all "signals of interest" are outputted on the user's terminal together with the system-time (simulated time). The user may now simply register the new values or react by changing the input-values or the circuit itself.

The complete dialogue is recorded on a log-file.

Future software-packages will immediately process circuit-descriptions in a Computer Hardware Description Language (DIGITEST<sup>6</sup>) and will allow single user time-sharing for the simulation of larger circuits as well as multi user time-sharing for a more economic use of the system.

#### References

- /1/ Beister, J.

A Unified approach to combinational hazards

IEEE ToC C-23 (1974), pp 566-575

- /2/ Brzozowski, J. A. & Yoely, M.

Digital Networks

(Prentice-Hall, 1976)

- /3/ Miller, R. E.

Switching Theory, Vol. II

(J. Wiley & Sons, New York, 1965)

- /4/ Noguchi, A. et al.

Mathematical Theory of asynchronous circuits I-III

(Waseda University Press, Tokyo 1963-1966)

- /5/ Rammig, F. J.

Quasi Reale Boolesche Funktionen: Ein Versuch,

zeitliche Effekte physikalisch realisierter

Bauteile zu algebraisieren

Digital Processes, 2 (1976) pp. 27-45

- /6/ Rammig, F. J.

Der Übersetzer DIGITEST (Version 2.1)

Bericht Nr. 8 der Abteilung Informatik der Universität Dortmund (1975)

Fig. 1 Draft of the realization of a pure delay function

Fig. 2 Draft of the realization of an inertial delay function

Fig. 3 Draft of the total system (only basic components)