# **Leitfäden und Monographien der Informatik**

Unter beratender Mitwirkung von

Prof. Dr. Hans-Jürgen Appelrath, Oldenburg

Dr. Hans-Werner Hein, St. Augustin

Prof. Dr. Rolf Pfeifer, Zürich

Dr. Johannes Retti, Wien

Prof. Dr. Michael M. Richter, Kaiserslautern

Herausgegeben von

Prof. Dr. Volker Claus, Oldenburg

Prof. Dr. Günter Hotz, Saarbrücken

Prof. Dr. Klaus Waldschmidt, Frankfurt

Die Leitfäden und Monographien behandeln Themen aus der Theoretischen, Praktischen und Technischen Informatik entsprechend dem aktuellen Stand der Wissenschaft. Besonderer Wert wird auf eine systematische und fundierte Darstellung des jeweiligen Gebietes gelegt. Die Bücher dieser Reihe sind einerseits als Grundlage und Ergänzung zu Vorlesungen der Informatik und andererseits als Standardwerke für die selbständige Einarbeitung in umfassende Themenbereiche der Informatik konzipiert. Sie sprechen vorwiegend Studierende und Lehrende in Informatik-Studiengängen an Hochschulen an, dienen aber auch in Wirtschaft, Industrie und Verwaltung tätigen Informatikern zur Fortbildung im Zuge der fortschreitenden Wissenschaft.

# **Systematischer Entwurf digitaler Systeme**

Von der System- bis zur Gatter-Ebene

Von Prof. Dr. rer. nat. Franz J. Rammig

Universität-Gesamthochschule Paderborn

Mit zahlreichen Abbildungen und Beispielen

**B. G. Teubner Stuttgart 1989**

Prof. Dr. rer. nat. Franz J. Rammig

Von 1969 bis 1973 Studium der Mathematik, Wirtschaftswissenschaften und Informatik an der Universität Bonn mit Abschluß als Diplommatematiker. Anschließend Wiss. Angestellter im Fachbereich Informatik der Universität Dortmund und 1977 Promotion bei Prof. Reusch. Seit 1983 Prof. für praktische Informatik an der Universität-GH Paderborn. Von 1985 bis 1987 Mitglied des Vorstandes von Cadlab, einem von der Universität-GH Paderborn und der Nixdorf Computer AG gemeinsam getragenen Forschungsinstitut.

89140169

CIP-Titelaufnahme der Deutschen Bibliothek

Rammig, Franz J.:

Systematischer Entwurf digitaler Systeme : von der System- bis zur Gatter-Ebene / von Franz J. Rammig. – Stuttgart : Teubner, 1989

(Leitfäden und Monographien der Informatik)

ISBN 3-519-02265-6

Das Werk einschließlich aller seiner Teile ist urheberrechtlich geschützt. Jede Verwertung außerhalb der engen Grenzen des Urheberrechtsgesetzes ist ohne Zustimmung des Verlages unzulässig und strafbar. Das gilt besonders für Vervielfältigungen, Übersetzungen, Mikroverfilmungen und die Einspeicherung und Verarbeitung in elektronischen Systemen.

© B. G. Teubner Stuttgart 1989

Printed in Germany

Gesamtherstellung: Zechnersche Buchdruckerei GmbH, Speyer

Umschlaggestaltung: M. Koch, Reutlingen

## Vorwort

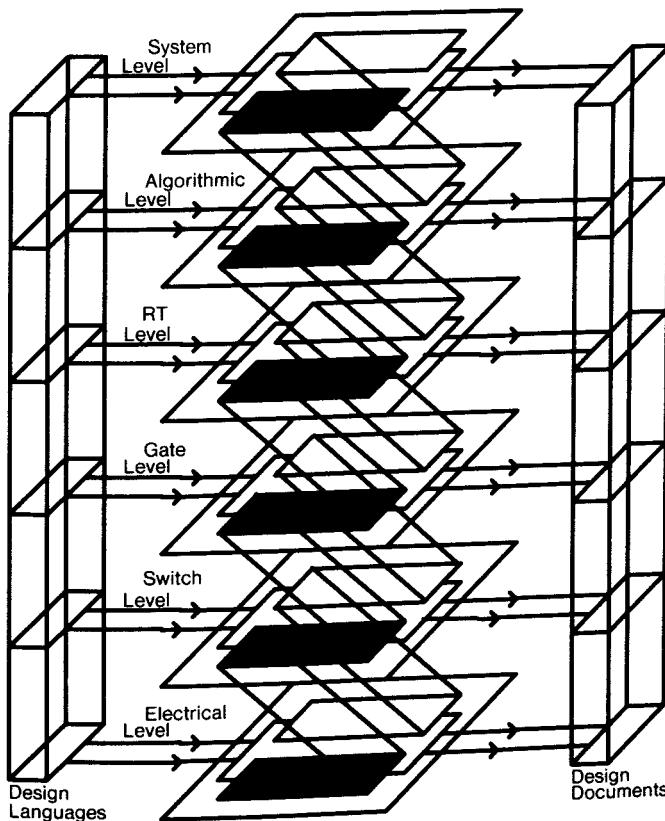

Dieses Buch versucht, eine durchgängige Systematik des Hardwareentwurfs über verschiedene Abstraktionsebenen hinweg darzustellen. Dabei wird von einem abstrakten Modell des Entwurfsvorgangs als über mehrere Abstraktionsebenen reichender rückgekoppelter Prozeß ausgegangen. Auf der Basis dieses Modells werden verschiedene Klassen von Entwurfsaktivitäten identifiziert. Es sind dies: Modellierung, Modifikation/Optimierung, Implementation und Verifikation. Die verschiedenen Abstraktionsebenen (Systemebene, algorithmische Ebene, Registertransfer-Ebene, Gatterebene, Schalterebene/ Ebene des symbolischen Layouts, elektrische/Layout-Ebene) werden in verschiedenen Sichten (Verhalten, Struktur, Geometrie, Test) charakterisiert. Dient das erste Kapitel dazu, eine allgemeine Systematik des Hardwareentwurfs zu entwickeln, so werden in den weiteren Kapiteln verschiedene Entwurfsaktivitäten beispielhaft diskutiert.

Das Kapitel 2 ist den verschiedenen Methoden der Hardwaremodellierung gewidmet. Nach einem allgemeinen Überblick wird darin exemplarisch die Breitband-Hardwarebeschreibungssprache DACAPO detaillierter eingeführt. Dies erlaubt, über verschiedene Aspekte des Hardwareentwurfs in einheitlicher Terminologie zu sprechen, und zwar nicht nur über Hardwarebeschreibungen auf unterschiedlichen Abstraktionsebenen, sondern auch über verschiedene Algorithmen des Entwurfsprozesses.

Im Kapitel 3 (Implementierungsaktivitäten) wird mit besonderem Augenmerk der Übergang von der algorithmischen auf die Registertransferebene behandelt. Aber auch verschiedene Methoden des Steuerwerksentwurfs und der Übergang auf die Gatterebene finden Berücksichtigung. Ein ausführliches Entwurfsbeispiel soll zur Illustration dienen. Optimierungsverfahren (Kapitel 4) werden hauptsächlich auf der Registertransferebene, aber auch auf der algorithmischen und Gatterebene diskutiert. Auch hier wird ein Beispiel exemplarisch durchgeführt. Das Kapitel 5 ist der Verifikation/Evaluation/Validierung gewidmet. Trotz ihrer in Zukunft sicherlich zentralen Bedeutung wird dabei die formale Verifikation relativ knapp und nur einführend behandelt. In diesem Buch sollte eine Konzentration auf heute praktisch und in Breite einsetzbare Hilfsmittel vorgenommen werden. Dies trifft für die "Ti-

mingverifikation” sicherlich zu, die aus diesem Grund auch etwas ausführlicher behandelt wird. Der Simulation als Hilfsaktivität für eine Verifikation wird breiter Raum eingeräumt. Hier werden verschiedene Simulationskonzepte verglichen, Simulationssszenarios behandelt und auf das Problem der Mehrebenensimulation eingegangen.

Das wichtige Thema der Testverfahren wird in dem abschließenden Kapitel 6 behandelt. Hier finden nach einer einleitenden Diskussion der Testproblematik Methoden der Testmustergenerierung, der Fehlersimulation, des testfreundlichen Entwurfs und der Selbsttestverfahren Erwähnung.

Alle Kapitel sind bewußt reich mit illustrierenden Beispielen versehen, wobei nach Möglichkeit auf eine einheitliche Notation geachtet wurde. Hier erwies sich die Abstützung auf die Breitband-Hardwarebeschreibungssprache DACAPO als sehr hilfreich.

Das Buch eignet sich sowohl für Informatiker in der Praxis als auch für Studenten der Informatik an Universitäten und Technischen Hochschulen.

Große Teile des Buches sind während meines Forschungsfreisemesters, das ich bei XEROX PARC, Palo Alto verbracht habe, entstanden. Die sehr anregende Atmosphäre dieses Forschungsinstitutes und die ausgezeichneten Arbeitsmöglichkeiten dort haben dieses Buch wesentlich beeinflußt. Ich möchte mich herzlich bei meiner Frau und Herrn Kollegen Waldschmidt für die kritische Durchsicht des Manuskriptes bedanken. Mein Dank gilt ganz besonders auch Frau S. Alejandro, deren Eifer dem Buch seine endgültige Form verliehen hat.

Paderborn, im Dezember 1988

Franz J. Rammig

# Inhaltsverzeichnis

|                                                                       |           |

|-----------------------------------------------------------------------|-----------|

| <b>1 Entwurfsprozeß</b>                                               | <b>11</b> |

| 1.1 Makroskopisches Modell des Entwurfsprozesses                      | 11        |

| 1.2 Abstraktionsebenen                                                | 13        |

| 1.3 Mikroskopisches Modell des Entwurfsprozesses                      | 32        |

| 1.4 Literatur                                                         | 37        |

| <b>2 Modellierungskonzepte und Entwurfssprachen</b>                   | <b>42</b> |

| 2.1 Modellierungskonzepte                                             | 42        |

| 2.1.1 Objektorientierte Modellierung                                  | 42        |

| 2.1.2 Imperative Sicht                                                | 46        |

| 2.1.2.1 Zeitbehaftete Interpretierte Petri-Netze                      | 47        |

| 2.1.2.2 Communicating Sequential Processes (CSP)                      | 50        |

| 2.1.3 Reaktive Sicht                                                  | 55        |

| 2.1.4 Stimulierte Gleichungen                                         | 57        |

| 2.1.5 Modellierungskonzepte und Abstraktionsebenen                    | 60        |

| 2.2 Sprachkonzepte                                                    | 60        |

| 2.2.1 Dedizierte Sprachen                                             | 61        |

| 2.2.1.1 Dedizierte Sprachen für die Systemebene                       | 61        |

| 2.2.1.2 Dedizierte Sprachen für die algorithmische Ebene              | 64        |

| 2.2.1.3 Dedizierte Sprachen für die Registertransferebene             | 66        |

| 2.2.1.4 Dedizierte Sprachen für die Gatterebene                       | 66        |

| 2.2.1.5 Dedizierte Sprachen für die Schalterebene/Symbolisches Layout | 67        |

| 2.2.1.6 Dedizierte Sprachen für die Elektrische/Layout-Ebene          | 69        |

| 2.2.2 Sprachfamilien                                                  | 71        |

| 2.2.3 Breitbandsprachen                                               | 74        |

| 2.3 Die Hardwarebeschreibungssprache DACAPO III                       | 75        |

| 2.3.1 DACAPO III Grundlagen                                           | 75        |

| 2.3.2 Beschreibungen in DACAPO III auf der algorithmischen Ebene      | 86        |

|                                                                            |            |

|----------------------------------------------------------------------------|------------|

| <b>2.3.3 Beschreibungen in DACAPO III auf der Systemebene</b>              | <b>97</b>  |

| <b>2.3.4 Beschreibungen in DACAPO III auf der Registertransferebene</b>    | <b>118</b> |

| <b>2.3.5 Beschreibungen in DACAPO III auf der Gatter/Schaltalebene</b>     | <b>125</b> |

| <b>2.3.6 "Behavioral"-Beschreibungen in DACAPO III</b>                     | <b>133</b> |

| <b>2.4 Literatur</b>                                                       | <b>135</b> |

| <br>                                                                       |            |

| <b>3 Implementationsaktivitäten</b>                                        | <b>142</b> |

| <b>3.1 Systemebene zur algorithmischen Ebene</b>                           | <b>142</b> |

| <b>3.2 Algorithmische Ebene zur Registertransferebene</b>                  | <b>143</b> |

| <b>3.2.1 Monolithische Dekomposition</b>                                   | <b>145</b> |

| <b>3.2.1.1 Ein vollständiges Beispiel zur monolithischen Dekomposition</b> | <b>161</b> |

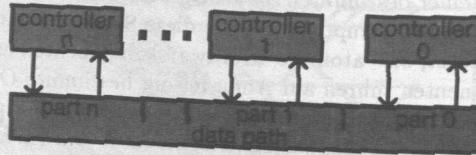

| <b>3.2.2 Parallele Dekomposition</b>                                       | <b>176</b> |

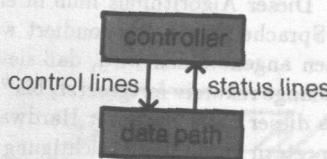

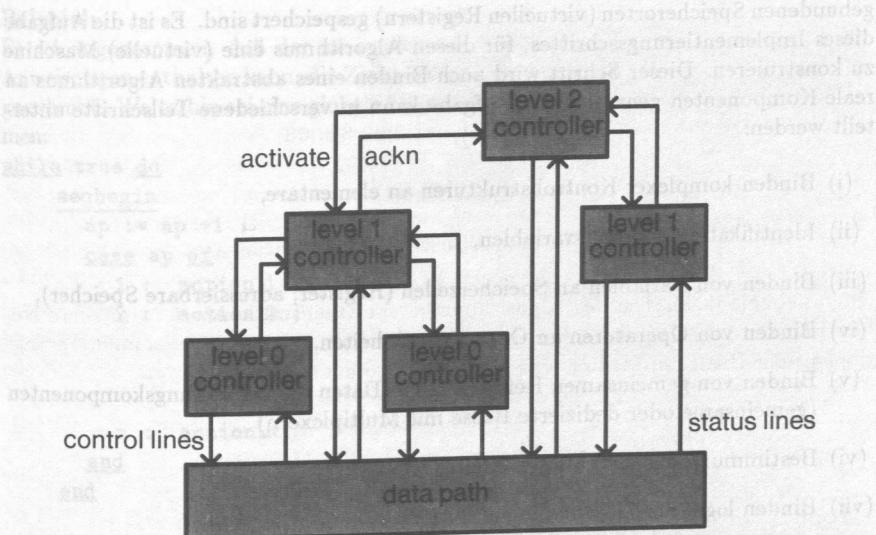

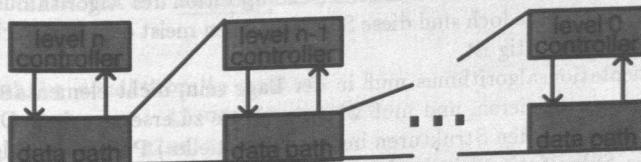

| <b>3.2.3 Hierarchische Steuerwerksdekomposition</b>                        | <b>177</b> |

| <b>3.3 Registertransferebene zur Gatterebene</b>                           | <b>180</b> |

| <b>3.3.1 Steuerwerksentwurf</b>                                            | <b>180</b> |

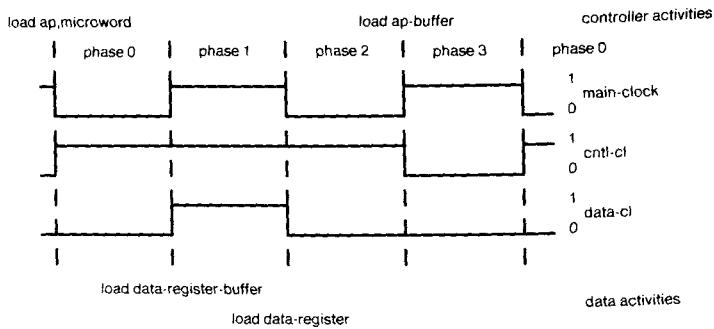

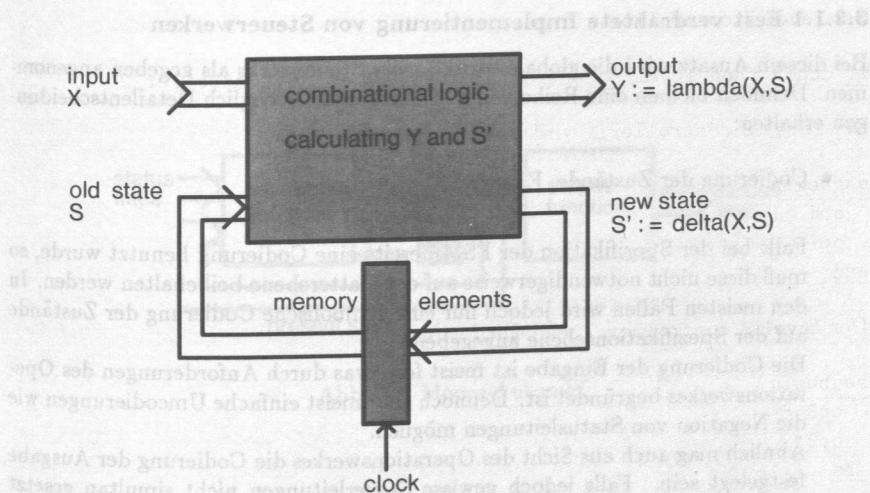

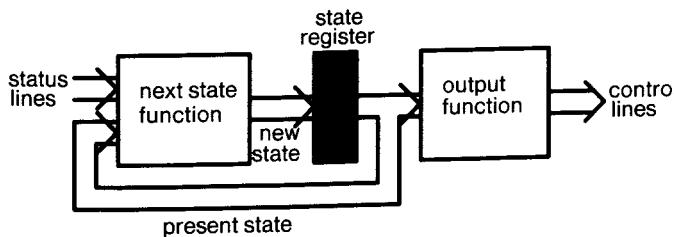

| <b>3.3.1.1 Fest verdrahtete Implementierung von Steuerwerken</b>           | <b>182</b> |

| <b>3.3.1.1.1 Implementierung in krauser Logik</b>                          | <b>185</b> |

| <b>3.3.1.1.2 Implementation durch Array-Logik</b>                          | <b>190</b> |

| <b>3.3.1.2 Mikroprogrammierte Steuerwerksimplementation</b>                | <b>194</b> |

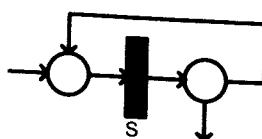

| <b>3.3.2 Datenpfadentwurf</b>                                              | <b>199</b> |

| <b>3.4 Literatur</b>                                                       | <b>199</b> |

| <br>                                                                       |            |

| <b>4 Optimierungsaktivitäten</b>                                           | <b>205</b> |

| <b>4.1 Optimierung auf der Systemebene</b>                                 | <b>205</b> |

| <b>4.2 Optimierung auf algorithmischer Ebene</b>                           | <b>206</b> |

| <b>4.2.1 Optimierung von Basisblöcken</b>                                  | <b>206</b> |

| <b>4.2.2 Optimierung von Schleifen</b>                                     | <b>208</b> |

| <b>4.3 Optimierung auf der Registertransferebene</b>                       | <b>209</b> |

| <b>4.3.1 Eine Heuristik zur Zustandsminimierung von Steuerwerken</b>       | <b>210</b> |

| <b>4.3.1.1 Beispiel einer Optimierung auf RT-Ebene</b>                     | <b>220</b> |

| <b>4.4 Optimierung auf der Gatterebene</b>                                 | <b>235</b> |

| <b>4.5 Literatur</b>                                                       | <b>252</b> |

|                                                                             |            |

|-----------------------------------------------------------------------------|------------|

| <b>5 Evaluierung, Validierung, Verifikation</b>                             | <b>255</b> |

| <b>5.1 Formale Verifikation</b>                                             | <b>255</b> |

| <b>5.1.1 Formale Verifikation von Verhaltenseigenschaften</b>               | <b>259</b> |

| <b>5.1.2 Verifikation des Zeitverhaltens getakteter Systeme</b>             | <b>261</b> |

| <b>5.2 Simulation</b>                                                       | <b>266</b> |

| <b>5.2.1 Generierung ausführbarer Objektmodelle und deren Ausführung</b>    | <b>268</b> |

| <b>5.2.1.1 Interne Modellierungskonzepte</b>                                | <b>268</b> |

| <b>5.2.1.1.1 Abbildung Algorithmischer Konstrukte von DACAPO III</b>        | <b>275</b> |

| <b>5.2.1.1.2 Abbildung von DACAPO III-Konstrukten der Systemebene</b>       | <b>277</b> |

| <b>5.2.1.1.3 Abbildung von DACAPO-Konstrukten auf Registertransferebene</b> | <b>280</b> |

| <b>5.2.1.1.4 Abbildung von DACAPO-Konstrukten auf Gatter/Schaltalebene</b>  | <b>280</b> |

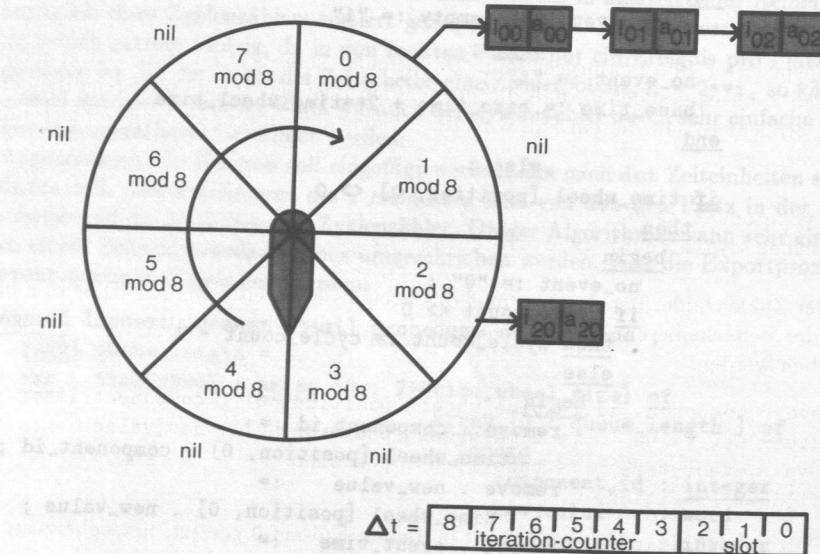

| <b>5.2.1.2 Simulationstechniken</b>                                         | <b>281</b> |

| <b>5.2.1.2.1 Streamline Code Simulation (SCS)</b>                           | <b>282</b> |

| <b>5.2.1.2.2 Äquitemporale Iteration (EI)</b>                               | <b>287</b> |

| <b>5.2.1.2.3 Critical Event Scheduling (CES)</b>                            | <b>293</b> |

| <b>5.2.2 Simulationsszenarios</b>                                           | <b>303</b> |

| <b>5.2.2.1 Modellierung der Umgebung</b>                                    | <b>304</b> |

| <b>5.2.2.2 Ergebnisanalyse</b>                                              | <b>306</b> |

| <b>5.2.3 Mehrebenensimulation</b>                                           | <b>308</b> |

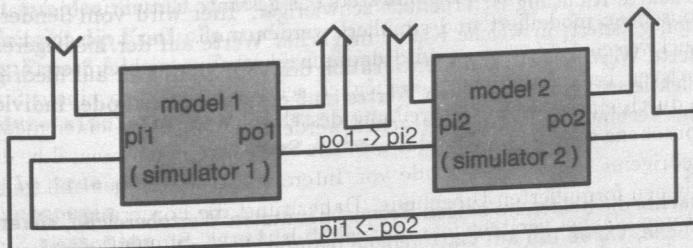

| <b>5.2.3.1 Multisimulatoransatz</b>                                         | <b>308</b> |

| <b>5.2.3.1.1 Datenaustausch</b>                                             | <b>309</b> |

| <b>5.2.3.1.2 Synchronisation</b>                                            | <b>311</b> |

| <b>5.2.3.1.3 Benutzerschnittstelle</b>                                      | <b>313</b> |

| <b>5.2.3.2 Breitbandsimulatoren</b>                                         | <b>314</b> |

| <b>5.3 Literatur</b>                                                        | <b>315</b> |

|                                                                  |            |

|------------------------------------------------------------------|------------|

| <b>6. Testmethoden</b>                                           | <b>320</b> |

| <b>6.1 Begriffsbestimmungen</b>                                  | <b>320</b> |

| <b>6.2 Strukturorientierte Testverfahren</b>                     | <b>321</b> |

| <b>6.2.1 Fehlermodelle</b>                                       | <b>321</b> |

| <b>6.2.2 Testmustererzeugung für das Haftfehlermodell</b>        | <b>323</b> |

| <b>6.2.3 Fehlersimulation</b>                                    | <b>331</b> |

| <b>6.2.3.1 Fehlersimulation mit dem SCS-Algorithmus</b>          | <b>331</b> |

| <b>6.2.3.2 Fehlersimulation mit dem CES-Algorithmus</b>          | <b>333</b> |

| <b>6.2.3.2.1 Parallele Fehlersimulation</b>                      | <b>333</b> |

| <b>6.2.3.2.2 Deduktive und Concurrent-Fehlersimulation</b>       | <b>333</b> |

| <b>6.3 Funktionsorientierte Testverfahren</b>                    | <b>335</b> |

| <b>6.4 Testfreundlicher Entwurf</b>                              | <b>336</b> |

| <b>6.4.1 Strukturelle Maßnahmen zur Erhöhung der Testbarkeit</b> | <b>336</b> |

| <b>6.4.2 Selbsttest</b>                                          | <b>340</b> |

| <b>6.5 Literatur</b>                                             | <b>347</b> |

| <b>Sachregister</b>                                              | <b>351</b> |

# 1 Entwurfsprozeß

Entwurfsaktivitäten sollten auf der Basis eines wohlverstandenen Modells des Entwurfsprozesses untersucht werden. Zusätzlich erlaubt es ein derartiges Modell, verschiedene Entwurfsmethoden zu klassifizieren und solche Unterstützungswerkzeuge für Entwurfsaktivitäten zu entwerfen und zu implementieren, die zusammenpassen. Aus diesen Grund soll zunächst der Entwurfsprozeß selbst untersucht werden.

## 1.1 Makroskopisches Modell des Entwurfsprozesses

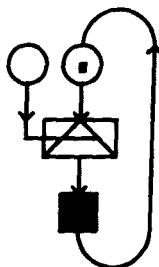

Eine naheliegende Idee, den Entwurfsprozeß zu modellieren, mag ein einfacher "Black Box"-Ansatz sein: Ein Entwurfsprozeß wird als "Black Box" gesehen, in die Entwurfsaufträge eingegeben werden. Immer wenn ein solcher Entwurfsauftrag in den Entwurfsprozeß eingegeben wird, reagiert dieser damit, daß er (hoffentlich) ein Entwurfsergebnis liefert. Somit kann ein Entwurfsprozeß, gegeben in einer Sprache  $L_{in}$ , als Transformationsabbildung interpretiert werden, die eine Objektbeschreibung abbildet in eine Objektbeschreibung, gegeben in einer Sprache  $L_{out}$ . Diese Abbildung ist in den meisten Fällen durch die Historie des Entwurfsprozesses parametrisiert. Sinnvollerweise partitioniert man die Eingabesprache  $L_{in}$  in zwei hauptsächliche Subsprachen. Die erste, genannt  $L_{in,d}$  dient als Eingabesprache, um die Entwurfsabsichten zu spezifizieren. Die zweite, genannt  $L_{in,c}$ , wird benutzt, um Restriktionen zu beschreiben. Derartige Restriktionen können spezifisch für ein spezielles Entwurfsobjekt sein, oder von globaler Gültigkeit. Diese Partition in zwei hauptsächliche Subsprachen impliziert unmittelbar eine Einteilung in zwei hauptsächliche Klassen von Entwurfsaktivitäten:

- Generierende Aktivitäten

- Überprüfende Aktivitäten (Verifikation, Validierung, Evaluierung).

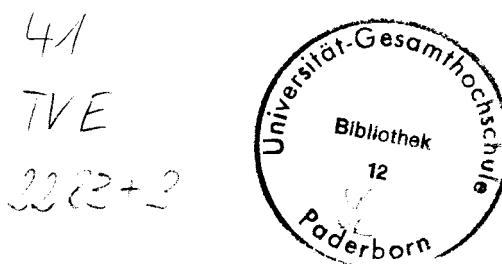

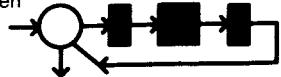

Die überprüfenden Aktivitäten werden durch die Sprache  $L_{in,c}$  gesteuert und operieren auf der Ausgabe der generierenden Aktivitäten. Diese haben  $L_{in,d}$  als primäre Eingabe. Wann immer jedoch die überprüfenden Aktivitäten eine Nichtübereinstimmung zwischen der Ausgabe der generierenden Aktivitäten und den gerade gültigen Restriktionen feststellen, wird Information darüber an die generierenden Aktivitäten zurück gesandt. Dadurch wird eine Modifizierung des aktuellen Entwurfsergebnisses angefordert. Bezeichne  $L_{check}$  die Sprache, die benutzt wird, um (vorläufige) Entwurfsergebnisse an die überprüfenden Aktivitäten zu senden und  $L_{correct}$  die Sprache, die benutzt wird, um Korrekturen anzufordern. Die generierenden und überprüfenden Aktivitäten zusammen mit den Sprachen (Kommunikationskanälen)  $L_{check}$  und  $L_{correct}$  bilden eine Rückkopplungsschleife, die von den beiden Sprachen  $L_{in,d}$  und  $L_{in,c}$  gesteuert wird. Damit ist ein kybernetisches Modell des Entwurfsprozesses entstanden (Abb. 1).

Abb. 1: Makroskopisches Modell des Entwurfsprozesses

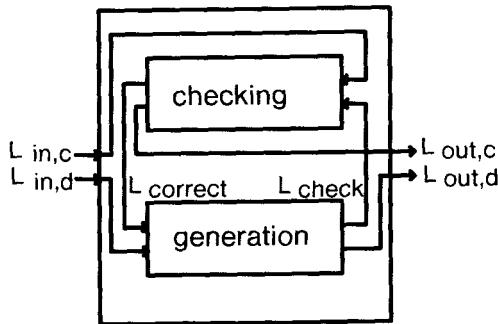

Üblicherweise wird die Beschreibung des Entwurfsergebnisses ebenfalls in Form eines Sprachpaars gegeben. Der Grund ist, daß ein entworfenes Objekt nicht nur gewisse Umgebungsrestriktionen zu respektieren hat, sondern in der Regel auch zusätzliche impliziert. Wir bezeichnen die beiden Ausgabesprachen mit  $L_{out,d}$  und  $L_{out,c}$ . Wenn man die überprüfenden Aktivitäten genauer betrachtet, so kann man drei hauptsächliche Subaktivitäten identifizieren: Zunächst muß das Ergebnis, das von den generierenden Aktivitäten erzeugt wird, auf Einhaltung der Restriktionen, die durch  $L_{in,c}$  formuliert werden, geprüft werden. Dies mag im engeren Sinne mit "Evaluierung" gekennzeichnet werden. Im Falle einer Nichtübereinstimmung (Normalfall) muß entschieden werden, durch welche eine Strategie dieser Defekt repariert werden soll. Diese Subaktivität mag mit "Entscheidungsfindung" bezeichnet werden. Schließlich muß die so gefundene Entscheidung ausgeführt werden. Dies bedeutet, daß sie in Information, ausgedrückt in der Sprache  $L_{correct}$ , überführt werden muß, sodaß sie von den generierenden Aktivitäten interpretiert werden kann. Diese Subaktivität mag mit "Steuerung" bezeichnet werden. Mit dieser Diskussion wurde ein verfeinertes Modell des Entwurfsprozesses erhalten, wie es in Abb. 2 angedeutet ist. Es sollte festgehalten werden, daß die beteiligten Aktivitäten interne Zustände haben können. In der Regel hat man es sogar mit lernfähigen Aktivitäten zu tun. Somit sind sie nicht nur von der aktuellen Eingabe, wie sie in den Sprachen  $L_{in,d}$  und  $L_{in,c}$  formuliert wird, abhängig, sondern auch von deren Geschichte. Zusätzlich kann in den meisten Fällen nicht davon ausgegangen werden, daß die Eingabebeschreibungen während des Entwurfsprozesses stabil bleiben. In jedem Fall jedoch erwartet die Umgebung des Entwurfsprozesses (das Management), daß er nach einer gewissen Zeit einen stabilen Zustand (Equilibrium) erreicht. Bis hier haben wir ein makroskopisches Modell der Klasse "Entwurfsprozeß" erhalten. Existierende oder gewünschte Entwurfsprozesse können instantiiert werden, wobei die geeigneten Attribute zum Parametrisieren der beteiligten Objekte gewählt werden müssen. Die

Abb. 2: Verfeinertes Modell des Entwurfsprozesses

erhaltene Struktur spiegelt nicht notwendigerweise die Arbeitsteilung des Entwurfsprozesses wieder (d.h. die beteiligten Abteilungen), sondern klassifiziert lediglich die verschiedenen Aktivitäten, die ausgeführt werden müssen. Diese makroskopische Sichtweise scheint allerdings nur für eine sehr grobe Analyse eines Entwurfsprozesses geeignet zu sein, oder für den Fall, daß der zu analysierende Prozeß eine sehr kleine Subaktivität eines komplexen Entwurfsprozesses ist. Um große Prozesse zu analysieren, müssen die beiden allgemeinen Paradigmen für diesen Zweck zur Beherrschung von Komplexität befolgt werden:

- Divide et impera (d.h. es wird ein Kompositions- / Dekompositionsmechanismus benötigt)

- Abstraktion

## 1.2 Abstraktionsebenen

Verschiedene Abstraktionsebenen haben eine lange Tradition beim Entwurf komplexer Systeme, insbesondere im Fall des Entwurfs digitaler Systeme. Unglücklicherweise gibt es keinen allgemein akzeptierten Standard für Abstraktionsebenen. Das nachfolgend beschriebene System scheint jedoch eine breite Vielfalt derartiger Schichten zu überdecken. Es umfaßt sechs Ebenen, wobei die Ebene 1 (Elektrische Ebene/Layout) die niedrigste ist und Ebene 6 (Systemebene) die höchste. Bevor diese Ebenen diskutiert werden sollen, muß zunächst das Konzept der Sichtweise

eingeführt werden. Es gibt vier hauptsächliche Sichten, unter denen ein zu entwertendes System betrachtet werden kann:

### **1) Die Verhaltenssicht**

In dieser Sicht ist man hauptsächlich daran interessiert, wie sich das System über die Zeit hinweg verhält. D. h. es kann beschrieben werden durch eine Menge "charakterisierender Variablen" und deren Werteverläufe über die Zeitachse. Diese "charakterisierenden Variablen" beschreiben sowohl die Werteverläufe an den Eingangsleitungen als auch die internen Zustandsfolgen des betrachteten Objekts.

### **2) Die Struktursicht**

In diesem Fall ist man mehr daran interessiert, wie das Objekt aus anderen Objekten zusammengesetzt ist. Die Subobjekte müssen dazu aufgelistet werden, wobei die Klasse, zu der sie gehören, und die notwendigen Parameter (falls es sich um generische Objekte handelt) angegeben werden müssen. Zusätzlich muß die Verbindungsstruktur spezifiziert werden.

### **3) Die Geometriesicht**

In dieser Sicht werden Objekte und ihre Subobjekte als mit geometrischen Eigenschaften behaftet betrachtet. Somit ist ihre relative Position zueinander ebenso von Interesse wie symbolische oder reale Dimensionen in einem n-dimensionalen Raum.

### **4) Die Testsicht**

Diese Sicht scheint zunächst der Verhaltenssicht zuzuordnen, da man entscheiden will, ob sich ein gefertigtes System so verhält wie intendiert. Jedoch ist Testen ein bisschen unterschiedlich, da in den meisten Fällen nur strukturorientiertes Testen möglich ist. Hier wird die Existenz oder Nichtexistenz angenommener struktureller Defekte (Fehlermodelle) überprüft.

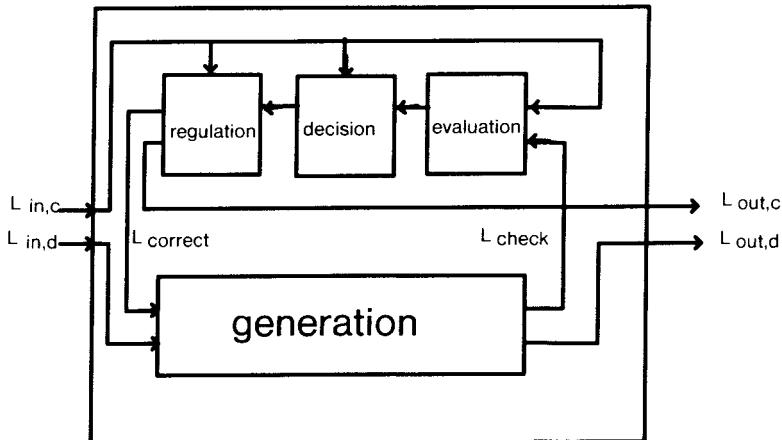

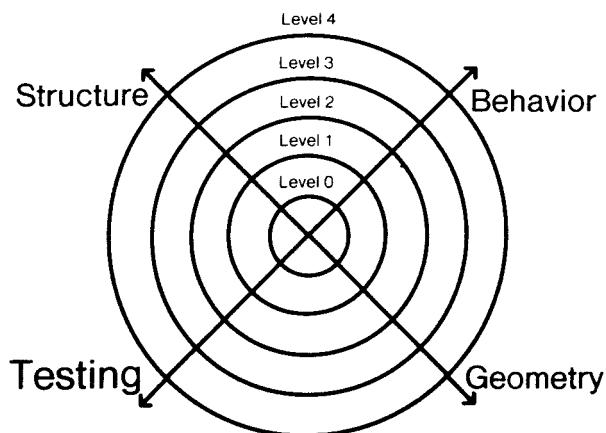

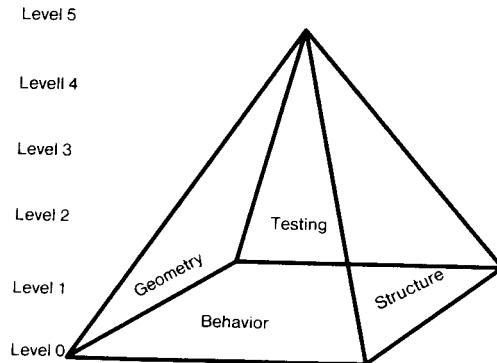

Falls man sich auf die Sichten 1 - 3 beschränkt, läßt sich dieser Multisichten-Ansatz graphisch sehr übersichtlich mittels Gajsky's Y-Diagramm (Abb.3) darstellen. Dieses Bild läßt sich sehr einfach zu einem X-Diagramm erweitern, das die Testsicht auch überdeckt (Abb. 4). Eine alternative Darstellung mit gleicher Aussagekraft ist durch eine vierseitige Pyramide (Abb. 5) gegeben. Diese Darstellung gibt sehr schön wieder, daß höhere Abstraktionsebenen in der Regel weniger Information als niedrigere beinhalten.

Nun sollen die verschiedenen Abstraktionsebenen detaillierter diskutiert werden:

#### **Ebene 6 : Systemebene**

##### **Verhalten:**

- Modellierungskonzept:

Abb. 3: Gajsky's Y-Diagramm

Abb. 4: X-Diagramm

Abb. 5: Entwurfs-Pyramide

System von semiautonomen Modulen wie Prozessoren, Kanäle, Steuerwerke, je charakterisiert durch :

- Funktionalität (d.h. den Instruktionssatz)

- Leistungskriterien

- Kommunikationsprotokolle

- Zeitmodell :

Kausalität

- Beobachtbare Werte :

Beliebige Werte in einem frei definierbaren Wertebereich.

#### Struktur:

- Statisch :

Auflistung von Komponenten und Angabe der Verbindungsstruktur

- Dynamisch :

Aufrufstruktur

#### Geometrie:

- Floorplanning im weiteren Sinn

#### Testkonzepte:

- Allgemeine globale Teststrategie.

### Erläuterungen:

Das Modellierungskonzept auf dieser Ebene für das Verhalten ist durch ein System semiautonomer kooperierender Module wie Prozessoren, Kanäle, etc. gegeben. All diese Komponenten werden als "Prozessoren" in einem weiteren Sinn betrachtet, d.h. als Objekte, die in wohldefinierter Weise auf Instruktionen reagieren. Damit sind aus einer theoretischen Sichtweise Abstrakte Datentypen (ADT) gut geeignet, als konzeptionelles Modell für diese Ebene zu dienen. Wenn man sich aus dem Bereich der Software nähert, so paßt das Konzept der objektorientierten Programmierung sehr gut. Drei hauptsächliche Eigenschaften müssen pro beteiligtem Modul (Objekt) spezifiziert werden:

- Für jedes Modul muß die grundlegende Funktionalität angegeben werden. Dies bedeutet nichts anderes, als Syntax und Semantik seines Instruktionssatzes zu definieren.

- Die grundlegenden Restriktionen auf dieser Ebene sind solche bezüglich der Leistung. Sie können global oder pro beteiligtem Modul spezifiziert sein.

- Schließlich müssen Syntax und Semantik der globalen Kommunikationsstruktur angegeben werden. Dies geschieht durch Definition von Protokollen für jede existierende Kommunikationsverbindung.

Die Struktur auf dieser Ebene ist durch einfaches Auflisten der beteiligten Komponenten (Typ und Instantiierung) und durch Angabe der Verbindungsstruktur gegeben. Diese Verbindungen können ebenfalls als Komponenten angesehen werden. Ihnen werden in der Verhaltenssicht die Kommunikationsprotokolle zugeordnet. Neben dieser statischen Struktur kann zusätzlich eine dynamische existieren. Sie gibt pro Modul an, von welchen anderen Modulen es Dienste anfordert und an welche es Dienste anbietet. Natürlich ist auch diese Information in Verbindung mit der Verhaltenssicht zu sehen.

Auf dieser Ebene existiert sehr wenig geometrische Information, falls man den logischen Entwurf betrachtet. Andererseits finden grundlegende mechanische Entscheidungen auf dieser Ebene statt. In den meisten Fällen durch externe Restriktionen gesteuert, wird auf dieser Ebene die dreidimensionale Plazierung der Komponenten durchgeführt.

Betrachtet man das Testen, so muß auf dieser Ebene eine globale Teststrategie festgelegt werden. Modulweise muß die Steuerbarkeit und Beobachtbarkeit betrachtet und die jeweilige Testmethode festgelegt werden. Besondere Beachtung muß auf die Kommunikationskanäle, d.h. auf die Protokolle gelegt werden.

### Beispiel:

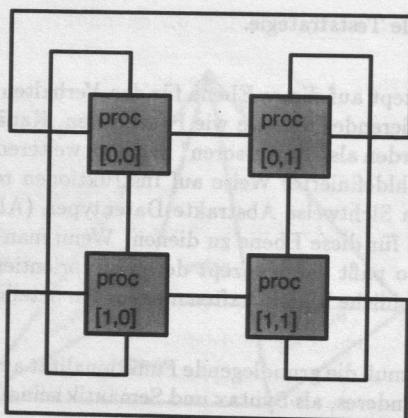

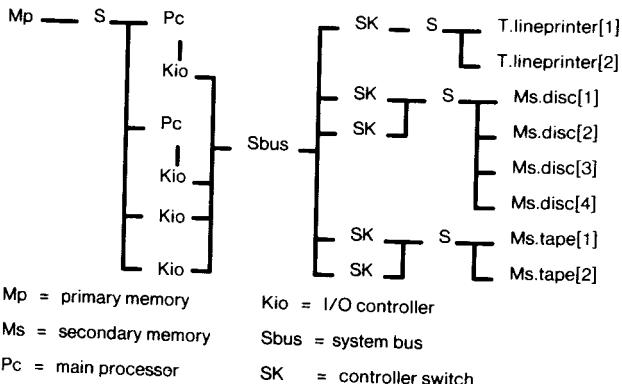

Es wird ein System angenommen, das aus vier Transputer-artigen Prozessoren besteht. Jeder dieser Prozessoren hat vier Kommunikationskanäle, wobei eine Verbindungsstruktur in Form eines Torus angenommen wird. Abb. 6 zeigt diese Struktur.

Abb. 6: Ein Prozessor-Torus

Ein derartiges System kann DACAPO-artig (siehe Abschnitt 2.3) wie folgt beschrieben werden:

```

definition module processor;

type processor =

export (operation_class_1,

operation_class_2,

operation_class_3) procedure processor;

processor.operation_class_1 =

procedure processor.operation_class_1;

processor.operation_class_2 =

procedure processor.operation_class_2;

processor.operation_class_3 =

procedure processor.operation_class_3;

channel

= procedure channel;

end processor.

module main;

from processor import processor,

processor.operation_class_1,

processor.operation_class_2,

processor.operation_class_3,

channel;

var processor_array : array [0:1,0:1] of processor;

```

```

link_array      : array [0:7]   of channel;

.

.{declaration of other (local) objects}

.

conbegin

.

.{description of the system's behavior}

.

end main.

```

Typische dedizierte Sprachen für diese Ebene sind:

- Um die Funktionalität zu beschreiben : DACAPO, VHDL, (OCCAM)

- Um die Leistung zu beschreiben : HIT

- Um Protokolle zu beschreiben : SDL, SLIDE, LASSO, (DACAPO)

#### **Ebene 5 : Algorithmische Ebene**

**Verhalten :**

- Modellierungskonzept:

Nebenläufige Algorithmen

- Zeitmodell :

Kausalität oder diskrete Realzeit

- Beobachtbare Werte :

Bitketten mit Interpretation.

**Struktur:**

- Keine spezifische Information.

**Geometrie :**

- Keine spezifische Information

**Test:**

- Softwareartiges Testen von Algorithmen (Tests auf niedrigeren Ebenen können möglicherweise davon abgeleitet werden).

### Erläuterungen :

Die Module auf der Systemebene sind Prozessoren im weiteren Sinn. Sie haben jeweils einen Instruktionssatz, der zu interpretieren ist. Auf der algorithmischen Ebene muß nun pro Modul der dazugehörige Interpretationsalgorithmus für den spezifischen Instruktionssatz definiert werden. Dieser Algorithmus ist üblicherweise hochgradig nebenläufig (z.B. falls Pipelining benutzt wird). Daher erscheinen Modellierungskonzepte wie Petri-Netze oder CSP für diesen Zweck gut geeignet zu sein. Sie werden an späterer Stelle detaillierter diskutiert werden. Diese Ebene wird oft auch Mikroprogrammierungsebene genannt. Tatsächlich kann man sich ein System als Hierarchie von Interpretern vorstellen, wobei jeder Interpreter ein Mikroprogramm ist, das den Instruktionssatz der nächsthöheren Mikroprogrammiersprache interpretiert. Bezuglich des Zeitmodells interessiert man sich auf dieser Ebene in den meisten Fällen weiterhin nur für Kausalitäten. Allerdings wird in manchen Fällen ein diskretes Zeitmodell angenommen, wobei man ein bestimmtes Taktschema im Auge hat. Die beobachtbaren Werte sind ein wenig konkreter als auf der Systemebene. Ihre Eigenschaft als Bitketten ist nun in den meisten Fällen sichtbar. Doch ist dies weiterhin von geringerem Interesse, man konzentriert sich mehr auf die typspezifische Interpretation (z.B. als Integer). Bezuglich der Struktur müssen wir zwischen der Komposition einer Kontrollstruktur aus Komponenten wie "While-Schleife" oder "Fork/Join" und der Struktur des Operationsteils des Algorithmus unterscheiden. Im letzteren Fall werden auf dieser Ebene bereits recht hardwarenahe Komponenten wie Register oder ALUs benutzt. Geometrische Information ist auf dieser Ebene nicht präsent. Es gibt eine Reihe von Testmethoden für Algorithmen. Sie alle stammen aus dem Bereich des Softwaretestens. Sie können entweder als Grundlage für funktionales Testen oder zur Ableitung von Testmustern auf niedrigeren Ebenen benutzt werden.

### Beispiel:

Angenommen wird ein gewöhnlicher Prozessor vom von-Neumann-Typ. Er habe einen Interpretationszyklus, bestehend aus "instruction fetch", "operand fetch" und "execute". Weiterhin wird angenommen, daß diese drei Aktivitäten im Pipelining ablaufen, also nebenläufig. Sie sollen mittels eines Taktes, genannt "main-clock", synchronisiert werden. Ein derartiges System kann auf algorithmischer Ebene in DACAPO-artiger Weise wie folgt beschrieben werden :

```

procedure alg_demo;

procedure instr_fetch (in inreg : bit(32); out outreg : bit(32));

{procedure body, defining how the instruction is fetched based

upon an address obtained from inreg, resulting in an instruction

stored in outreg}

procedure operand_fetch (in inreg : bit(32); out outreg : bit(32));

{procedure body, defining how the operand is fetched based

```

```

upon an address obtained from inreg, resulting in an operand

stored in outreg}

procedure execute (in instr, operand : bit(32); out status : bit(32));

{procedure body defining how the instruction obtained from

instr is executed using the operand obtained from operand,

resulting in a status information stored in status}

conbegin

while not halt do

at up (mainclock) do

conbegin

instr_fetch(memory_adr_register, instr_reg);

operand_fetch(instr_reg, operand_reg);

execute(instr_reg, operand_reg, status)

end

end

end

```

Man beachte, daß in dem Beispiel mehrere Details weggelassen wurden. So wurde keine der globalen Variablen wie `memory-adr-register` deklariert. Weiterhin wurden einige Seiteneffekte der Prozeduren angenommen. Man beachte, daß die Struktur des Algorithmus nicht unmittelbar die Struktur der zu implementierenden Hardware wiedergibt. Jedoch mag eine gewisse Hardwarestruktur impliziert werden, z.B. wegen der beschriebenen Pipeline-Struktur (`conbegin`).

Eine typische dedizierte Sprache für diese Ebene ist ISPS. DACAPO als Breitbandsprache überdeckt diese Ebene ebenfalls.

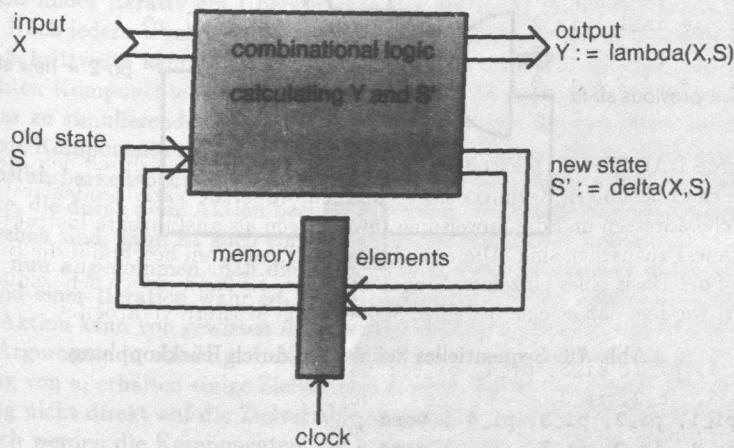

#### Ebene 4 : Registertransferebene

**Verhalten :**

- Modellierungskonzept :

Nicht geordnete Menge von Operationen, jede Operation ein "Guarded Command"

- Zeitmodell :

Diskrete Realzeit (Zählen von Taktzyklen)

- Beobachtbare Werte :

Bitketten (meist ohne Interpretation)

**Struktur :**

- Aufzählung von RT-Komponenten plus Verbindungsstruktur

**Geometrie :**

- Floorplanning

**Testkonzepte :**

- Spezielle Testmethoden für RT-Module (RAM, ROM, PLA, ALU, Schieberegister), C-Testbarkeit, Regelüberprüfer für "Design for Testability" auf RT-Ebene.

**Erläuterungen :**

Die Registertransferebene kann als das Inverse der algorithmischen Ebene charakterisiert werden. Auf der algorithmischen Ebene wird das System in einer imperativen Weise betrachtet. Das heißt, daß die Sichtweise die des Steuerwerkes ist. Dieses entscheidet, wann nach welchen vorhergehenden Aktionen eine bestimmte Aktion durchgeführt werden darf. Die strikt sequentielle Anordnung in üblichen imperativen Sprachen wird hier generalisiert, um auch Nebenläufigkeit zu erlauben. Auf der Registertransferebene wird eine reaktive Sichtweise eingenommen. Das System wird nun aus Sicht der gesteuerten Objekte betrachtet. Jedes derartige Objekt beobachtet kontinuierlich eine objektspezifische Bedingung. Wann immer diese Bedingung wahr wird, führt das Objekt seine Aktion durch. Dabei modifiziert es üblicherweise die Bedingungen innerhalb des Bedingungsraums. Dadurch mag es die Ausführung anderer Objekte (einschließlich seiner selbst) ermöglichen.

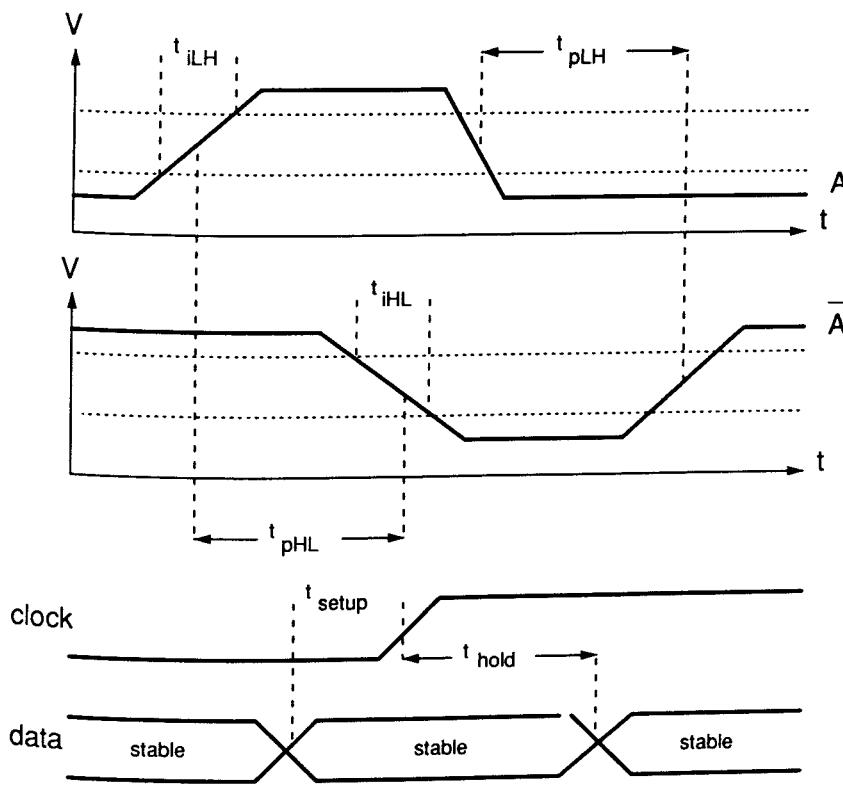

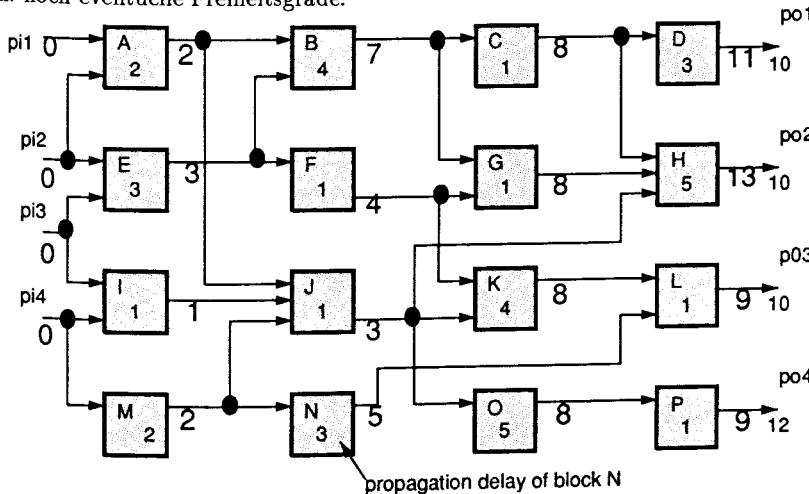

Auf dieser Ebene ist man üblicherweise an einem spezifischen synchronen Taktungsschema interessiert. Daher wird das Zeitschema auf dieser Ebene meist durch das Zählen von Taktzyklen gegeben. Bedingungen auf der Basis dieser Taktsignale sind Bestandteil der Ausführbarkeitsbedingungen der involvierten Module. Es hängt von dem jeweiligen Implementierungskonzept für das Zeitschema ab, ob Taktpegel, steigende, fallende oder beide Flanken, oder gar eine Mischung dieser Techniken benutzt werden. Die beobachtbaren Werte sind nun Bitketten. In den meisten Fällen wird ihnen nicht mehr eine feste Interpretation (Typ) zugeordnet. Vielmehr werden sie von verschiedenen Objekten unterschiedlich interpretiert. Auf der Registertransferebene wird die endgültige Hardwarestruktur sichtbar. Das System wird daher als Verschaltung von Registertransfermodulen beschrieben. Typische derartige Module sind Register, ALUs, Multiplexer, Kodierer, Dekodierer, Schiebebausteine, etc. So mit ist in dieser Sicht die Registertransferebene eine grobe Netzliste. Für einige der Komponententypen auf der Registertransferebene existieren spezielle semifunktionale Testmethoden. Sie können unabhängig von einer speziellen Implementierungstechnik ausgewählt und angewandt werden. Darüberhinaus werden auf dieser Ebene wichtige Entscheidungen in Bezug auf testbare Entwürfe getroffen. Als Beispiel diene die Entscheidung, ob ein Prüfbus eingeführt werden soll. Daher ist es sinnvoll, daß Regelüberprüfer, die auf Testbarkeit prüfen, Information auf dieser Ebene verarbeiten.

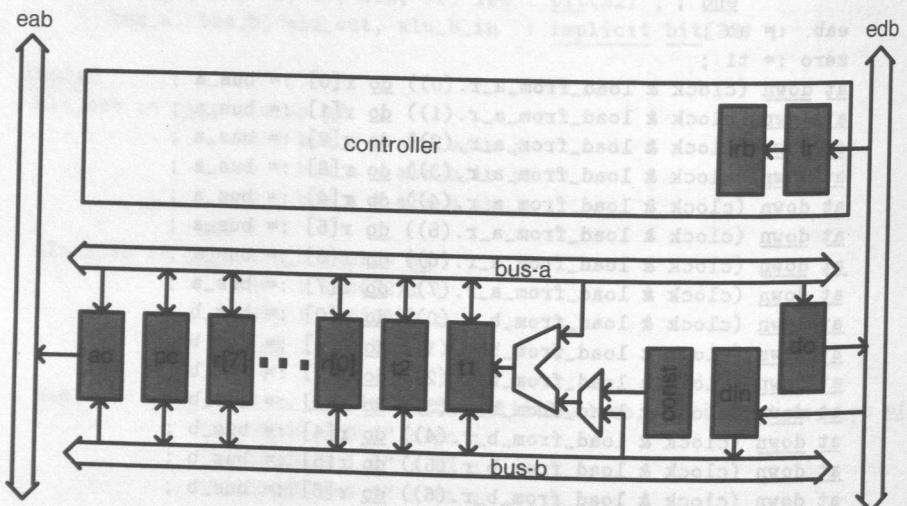

### Beispiel :

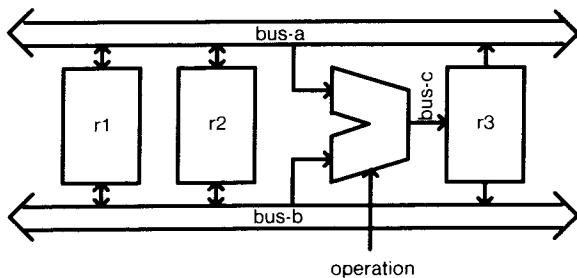

Es sei ein System angenommen, bestehend aus zwei Bussen, zwei Registern, die je mit beiden Bussen bidirektional verbunden sind, und einer ALU, die von beiden Bussen gleichzeitig gelesen werden kann und ihr Ergebnis über eine dedizierte Verbindung in ein drittes Register schreibt. Dieses dritte Register kann auf beide Busse schreiben. Abb. 7 zeigt dieses System.

Abb. 7: Beispiel eines Datenpfades

Auf Registertransferebene kann dieses System in DACAPO-artiger Weise wie folgt beschrieben werden :

```

procedure register_transfer_example:

{declarations}

impdef

at up (clk and r1_from_a) do r1 := bus_a;

at up (clk and r1_from_b) do r1 := bus_b;

at up (clk and r2_from_a) do r2 := bus_a;

at up (clk and r2_from_b) do r2 := bus_b;

at up (clk and r3) do r3 := bus_c;

bus_a := case sender_a of

r1_send_a : r1;

r2_send_a : r2;

r3_send_a : r3

end;

bus_b := case sender_b of

r1_send_b : r1;

r2_send_b : r2;

r3_send_b : r3

end;

```

```

bus_c := case operation of

add      : bus_a + bus_b;

sub      : bus_a - bus_b;

and      : bus_a and bus_b

end;

```

Man beachte, daß auch dieses Beispiel rudimentär ist. Es fehlen nicht nur die Deklarationen, sondern auch die Generierung der Steuersignale. Es läßt sich beobachten, daß zwei Klassen von Objekten beteiligt sind: Solche, die auf das Auftreten spezieller Ereignisse reagieren, in diesem Fall steigende Flanken von Booleschen Ausdrücken, und solche, die kontinuierlich aktiv sind, wie die Definition der Werteverläufe auf den Bussen. Typische dedizierte Sprachen auf dieser Ebene sind beispielsweise: CDL (die "klassische" RT-Sprache), DDL, CASSANDRE, RTS, ERES, KARL. DACAPO und VHDL als Breitbandsprachen überdecken diese Ebene ebenfalls.

### **Ebene 3 : Gatterebene**

#### **Verhalten :**

- Modellierungskonzept :

System "Boolescher" Gleichungen (in vielen Fällen wird eine mehrwertige Logik benutzt. Derartige Logiken sind meist nicht Boolesch.)

- Zeitmodell:

Kontinuierliche Realzeit

- Beobachtbare Werte :

"Bits" ( sie können mehrwertig sein).

#### **Struktur :**

- Auflistung von Komponenten und Angabe der Verbindungsstruktur (Netzliste)

#### **Geometrie :**

- Floorplanning

#### **Testkonzepte :**

- Strukturorientiertes Testen, Fehlermodelle wie Haftfehler oder Kurzschlußfehler, Testmustergeneratoren.

### Erläuterungen :

Beschreibungen auf der Gatterebene können als Expansion der Module auf der RT-Ebene angesehen werden. Allerdings geht die semantische Information über die Unterscheidung zwischen Daten- und Steuersignalen, wie sie auf der RT-Ebene noch vorhanden ist, vollständig verloren. Man hat nun lediglich ein Netz mit Gattern und Flipflops als Knoten und Einbit-Verbindungsleitungen als Kanten. Das Verhalten ergibt sich aus der Transformationsabbildung an den Knoten, die kontinuierlich ausgeführt wird, und durch das Werteverteilungsschema, wie es durch die Verbindungsstruktur gegeben ist. Auf dieser Ebene ist man in vielen Fällen an präzisen Informationen über das Zeitverhalten interessiert. Daher ist das übliche Zeitmodell auf dieser Ebene das der kontinuierlichen Realzeit. Allerdings werden verschiedene approximative Verzögerungskonzepte benutzt, die von simplen Konzepten wie feste Nominalverzögerung bis hin zu Modellen reichen, die fast das analoge Verhalten der beteiligten Module wiederspiegeln. Beobachtbare Werte sind "Bits" in einer mehrwertigen Logik, wobei bis zu 32 verschiedene Werte betrachtet werden. Die logische Struktur ist auf dieser Ebene sehr gut dokumentiert. Dabei müssen die Knoten nicht auf "Gatter" im engen Sinn beschränkt sein, sondern auf atomare Schaltungen, die durch einen Booleschen Ausdruck bzw. durch ein Bündel Boolescher Ausdrücke beschrieben werden können. Dadurch sind auch hierarchische Beschreibungen möglich. Testen ist lange Zeit nur auf der Gatterebene betrachtet worden. Daher gibt es auf dieser Ebene eingeführte Fehlermodelle, die ein strukturorientiertes Testen erlauben. Dabei handelt es sich um eine Testmethode, bei der man nicht funktionelles Fehlverhalten, sondern nur die Anwesenheit von irgendeinem als möglich erachteten Defekt ausschließen will. Die üblichen Fehlermodelle sind Haftfehler und Kurzschlußfehler. Für derartige Fehlermodelle existieren Testmustergeneratoren (ATPG), falls gewisse Restriktionen beachtet werden.

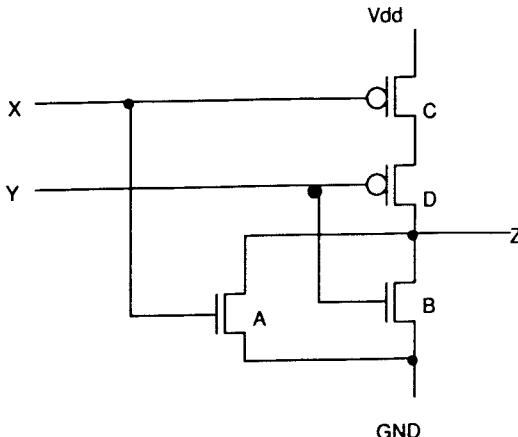

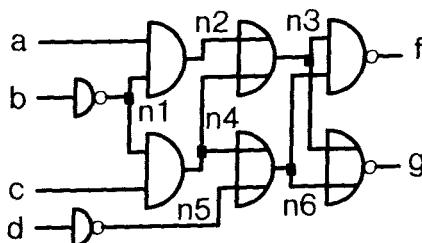

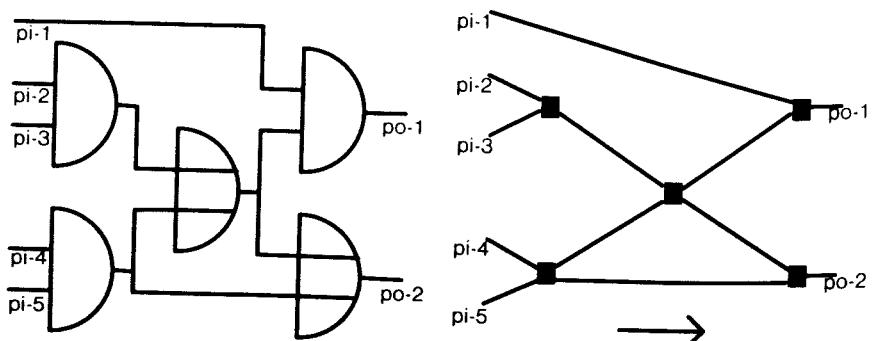

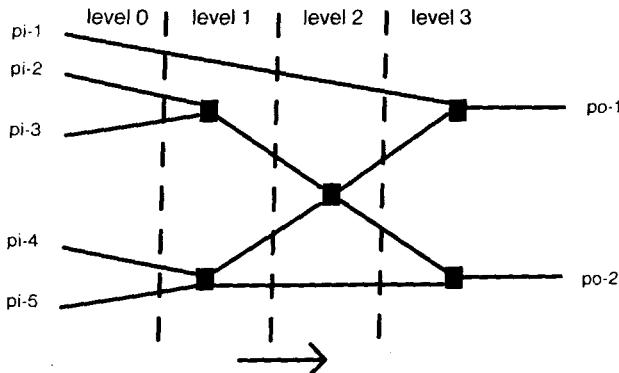

### Beispiel:

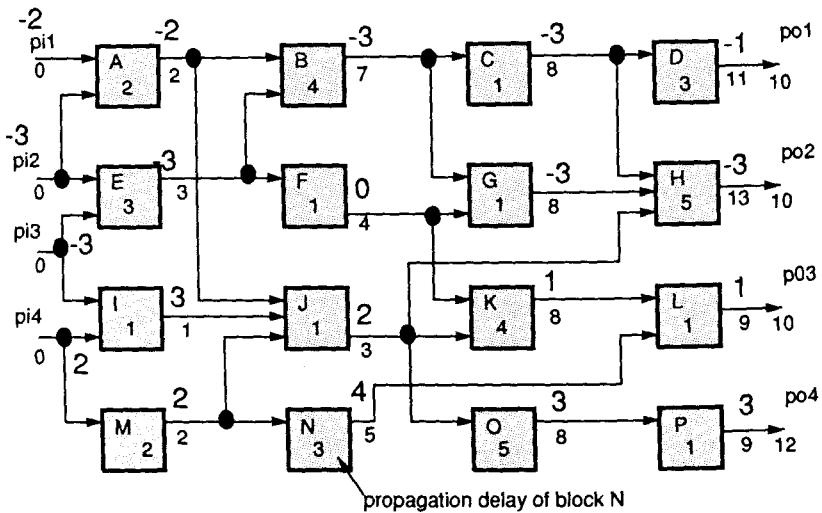

Es sei als Verzögerungsmodell eine einfache Durchlaufverzögerung angenommen, die jedem Gatterausgang zugeordnet wird.

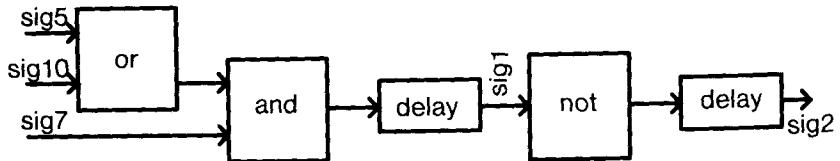

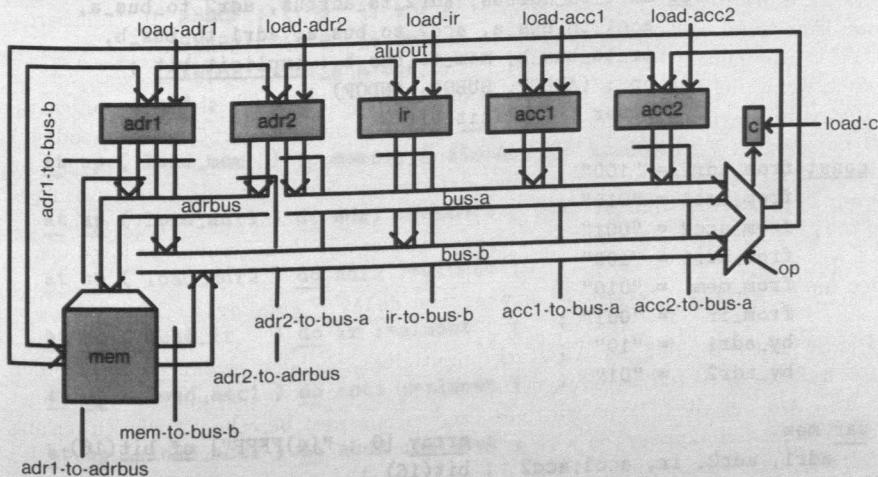

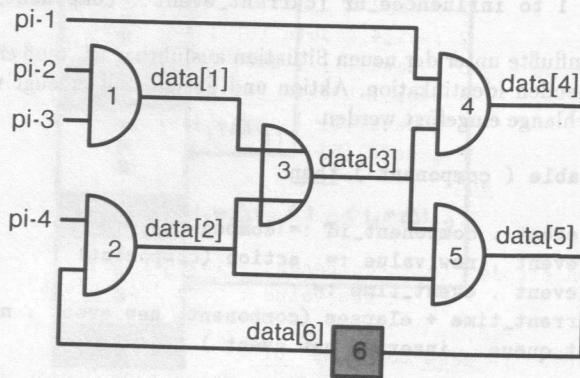

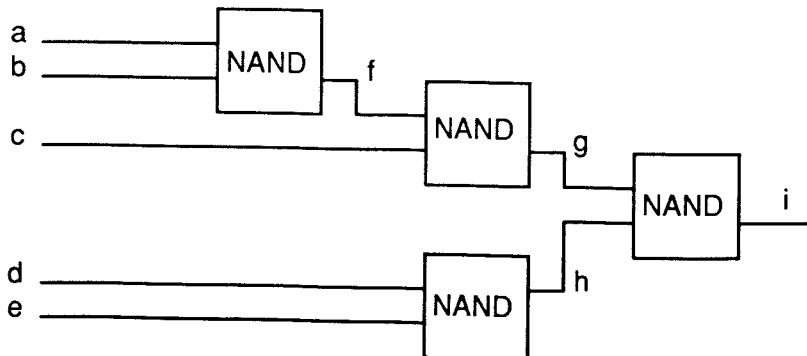

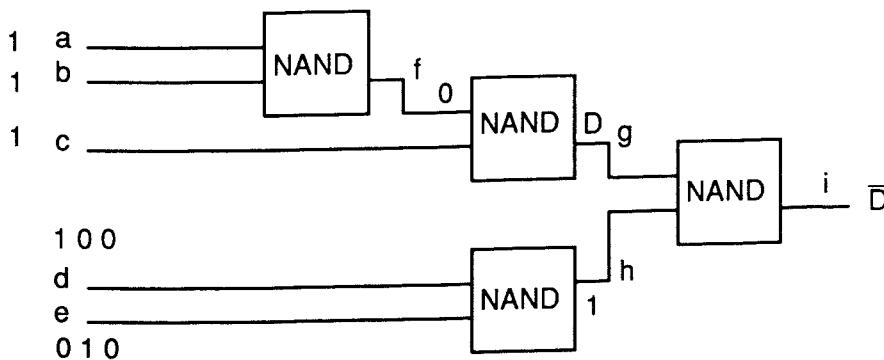

Gegeben sei die in Abb. 8 gezeigte Schaltung. Sie lässt sich auf Gatterebene in DACAPO-artiger Weise wie folgt beschreiben:

```

procedure gate_demo;

.

.

.

impdef

sig1 := sig7 and (sig5 or sig10) delay (up 5 to 7, down 3 to 6);

sig2 := not sig1 delay (3 to 8);

.

.

.

```

Abb. 8: Beispiel einer Gatterschaltung

In diesem Beispiel wurde angenommen, daß es für steigende und fallende Flanken unterschiedliche Verzögerungszeiten gibt. Weiterhin wurde mit Unsicherheitsintervallen bei der Verzögerungsbeschreibung gerechnet.

Typische dedizierte Sprachen für diese Ebene sind unter den Eingabesprachen von Gattersimulatoren wie TEGAS, DISIM, LSIM, DSIM, HILO, CADAT zu finden. Diese Ebene wird allerdings auch von gewissen RT-Sprachen, die eine hinreichend präzise Beschreibung des Zeitverhaltens erlauben (z.B. ERES), und natürlich durch Breitbandsprachen wie DACAPO und VHDL überdeckt. Darüber hinaus gibt es Bestrebungen, diesen Rahmen auf komplexere Module auszuweiten. Die grundlegende Idee ist es, das Ein-/Ausgabeverhalten von Modulen ("Supergatter") in einer bestimmten Sprache zu beschreiben und diese "Supergatter" in Beschreibungen auf der Gatterebene einzufügen. Dieser Ansatz sollte nicht mit der RT-Ebene verwechselt werden. Auf der RT-Ebene existiert ein wohldefinierter konzeptioneller Rahmen, während hier beliebige Module ohne vordefinierte Semantik verschaltet werden. Obwohl nur die Funktion der "Supergatter" beschrieben werden muß, werden für diesen Zweck meist algorithmische Sprachen benutzt. Als Beispiele für derartige "Verhaltenssprachen" ("Behavioral Languages"), wie sie meist genannt werden, mögen dienen: HELIX, DABL, QL, CAP/FBDL. ELLA fällt in dieselbe Klasse, folgt jedoch als konsequent funktionale Sprache einem saubereren Ansatz.

## Ebene 2 : Schalterebene / Symbolisches Layout

### Verhalten :

- Modellierungskonzept :

System mehrwertiger diskreter Gleichungen

- Zeitmodell :

Kontinuierliche Realzeit

- Beobachtbare Werte :

Paare der Art (logischer Wert, Stärke)

### **Struktur :**

- Auflistung von Transistoren (unterschiedlichen Typs) zusammen mit Angabe einer Verbindungsstruktur, wobei den Netzen Kapazitäten zugeordnet werden

### **Geometrie :**

- Stickdiagramme (d.h. nichtmetrisches Layout)

### **Testkonzepte :**

- Strukturorientiertes Testen mit modifizierten Fehlermodellen, Modifikationen zur Erhöhung der Testbarkeit, Ausnutzung topologischer Information zur Verringerung der Anzahl möglicher Kurzschlußfehler.

### **Erläuterungen :**

Beschreibungen auf der Schalterebene werden entweder dadurch erhalten, daß man solche auf der Gatterebene zu Netzwerken aus Schaltern und Kapazitäten expandiert, oder indem man solche Schaltwerke erzeugt, die keine Entsprechung auf der Gatterebene haben. Als Modellierungskonzept hat man ein System mehrwertiger diskreter Gleichungen. Eine andere mögliche Betrachtungsweise ist die des endlichen Automaten, wobei sich der Zustand aus der momentanen Ladungsverteilung in den Kapazitäten ergibt. Die Komponenten, die auf dieser Ebene benutzt werden, sind simplifizierte Transistoren (idealisierte Schalter, "switches") und "Knoten" (Kapazitäten). Beobachtbare Werte sind jeweils Paare bestehend aus einem logischen Wert und einer Signalstärke. Beide Werte haben üblicherweise einen endlichen Wertebereich. Das Zeitmodell ist wie im Fall der Gatterebene kontinuierliche Realzeit. Bezüglich der Strukturbeschreibung müssen die involvierten Transistoren aufgelistet und die Verbindungsstruktur angegeben werden. Jedem verbindenden Netz kann eine Kapazität zugeordnet werden. Die geometrische Information wird in Form von Stickdiagrammen gegeben. Über die reine Strukturinformation hinaus enthalten sie Information über die relative Lage der Komponenten zueinander und die Dotierungsebene der Verbindungsleitungen. Natürlicherweise versucht man die strukturellen Testmethoden der Gatterebene auf dieser Ebene auch anzuwenden. Allerdings müssen hierzu die Fehlermodelle leicht modifiziert werden. Die geometrische Information, die auf dieser Ebene vorhanden ist, kann sinnvoll für Testzwecke eingesetzt werden. Speziell im Fall von Kurzschlußfehlern können die möglichen Kurzschlüsse ignoriert werden, die zwischen entfernten Punkten stattfinden müßten (eine Information, die auf höheren Ebenen nicht vorliegt).

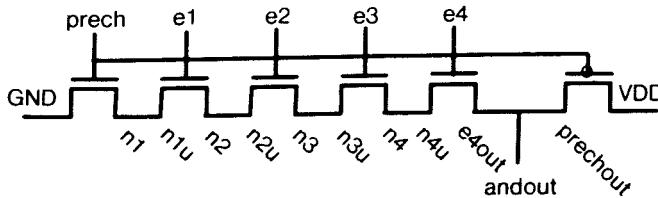

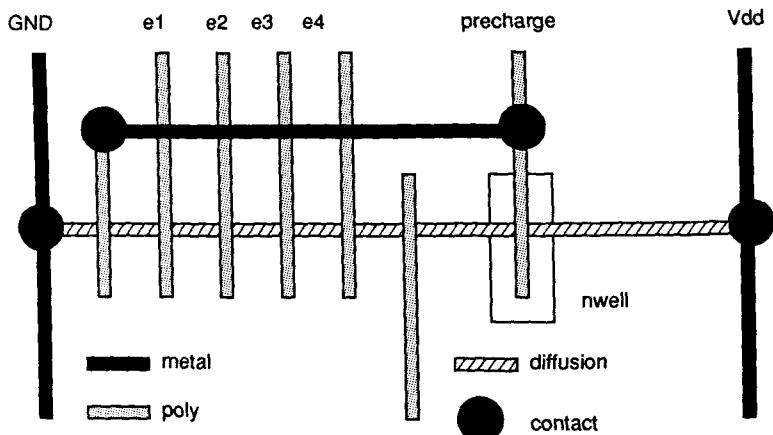

### **Beispiel :**

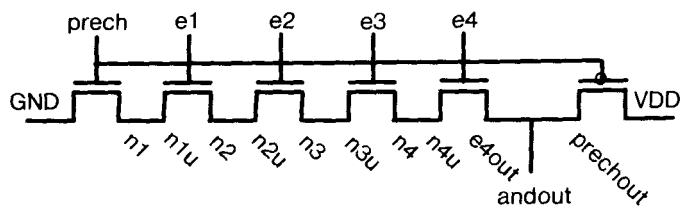

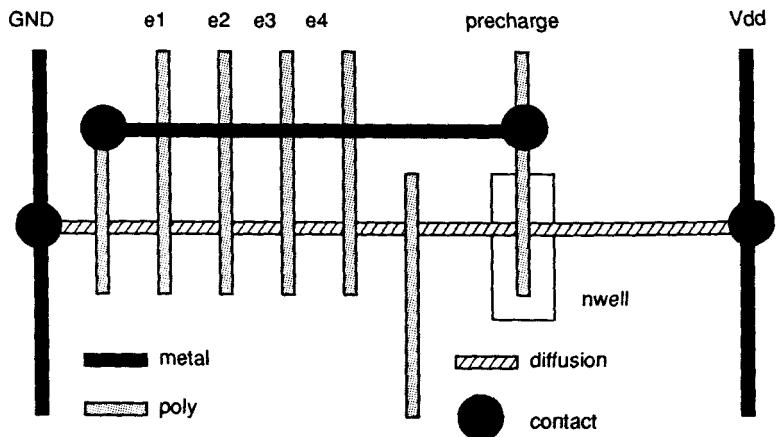

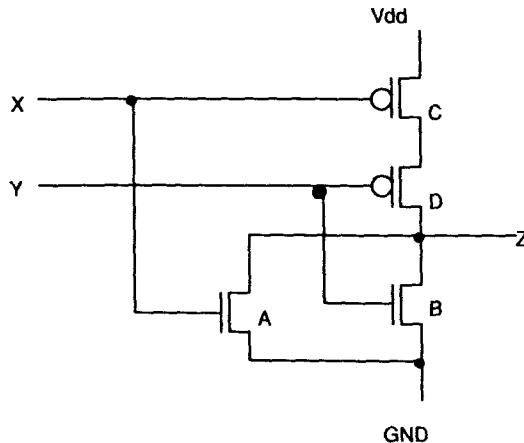

Abb. 9 zeigt die Struktur eines CMOS NAND-Gatters, Abb. 10 ein Stickdiagramm dazu.

Diese geometrische Information könnte alternativ auch in einer algorithmischen Layoutsprache gegeben werden. Nimmt man einen Prozedurtyp **collect (capacity,**

Abb. 9: Schematic eines CMOS NAND-Gatters

Abb. 10: Stickdiagramm eines CMOS NAND-Gatters

`port1, port2,...,portn)` zum Beschreiben von Netzen und einen Prozedurtyp `transfer (technology, gate, source, drain)` zur Beschreibung von Transistoren an, so kann diese Schaltung in DACAPO-artiger Weise wie folgt beschrieben werden :

```

procedure switch_level_example;

.

.

.

impdef

.

.

.

transfer (pmos, prech, vdd, prechout);

transfer (nmos, e4, n4u, e4out);

transfer (nmos, e3, n3u, n4);

transfer (nmos, e2, n2u, n3);

transfer (nmos, e1, niu, n2);

transfer (nmos, prech, gnd, n1);

collect (strength1, prechout, e4out, andout);

collect (strength2, n4u, n4);

collect (strength2, n3u, n3);

collect (strength2, n2u, n2);

collect (strength2, niu, n1);

```

Alle Knoten(Netze) außer dem ersten werden mit gleicher Kapazität angenommen. Vdd und GND werden als vordefinierte Konstanten angenommen.

Die klassische dedizierte Sprache auf dieser Ebene ist die Eingabesprache des Switch-Level-Simulators MOSSIM. Diese Ebene wird partiell auch von den derzeitigen Versionen der Breitbandsprachen DACAPO und VHDL überdeckt. Typische geometrische Sprachen auf dieser Ebene sind die verschiedenen Notationen für Stickdiagramm-Editoren. Ein Beispiel für eine algorithmische Layoutsprache für symbolisches Layout ist HILL.

## Ebene 1 : Elektrische Ebene / Layout

### Verhalten :

- Modellierungskonzept :

System von Differentialgleichungen

- Zeitmodell :

Kontinuierliche Realzeit

- Beobachtbare Werte :

Werte innerhalb eines kontinuierlichen Wertebereichs (Spannungen, Ströme,...)

**Struktur :**

- Auflistung elektrischer Elementarbausteine und Angabe der Verbindungsstruktur

**Geometrie :**

- Metrisches Layout

**Testkonzept :**

- Identifikation von Masken- oder Fabrikationsdefekten, funktionaler Vergleich zwischen intendiertem und beobachtetem Verhalten.

**Erläuterungen :**

Auf dieser Ebene wird die digitale Interpretation der Schaltung aufgegeben und das analoge Verhalten betrachtet. Das Modellierungskonzept ist durch ein System von Differentialgleichungen über kontinuierlichen Wertebereichen und in kontinuierlichen Zeitbereichen gegeben. Die benutzten Elementarbausteine sind Widerstände, Kapazitäten, etc.. Das Layout ist mit der elektrischen Beschreibung eng gekoppelt, da es wenig Sinn macht, ein metrisches Layout ohne Kenntnis des Herstellungsprozesses anzufertigen. Das metrische Layout unterscheidet sich vom symbolischen dadurch, daß jedes benutzte Objekt eine wohldefinierte Bemaßung hat. Zusätzlich muß auf dieser Ebene die Maskeninformation für jeden Herstellungsschritt bereitgestellt werden, während man auf der Ebene des symbolischen Layouts von gewissen Schritten abstrahieren kann. Für das Testen ist diese Ebene dann essentiell, wenn man den physikalischen Grund eines Fehlers identifizieren will. Dies ist besonders in der Phase der Stabilisierung eines noch instabilen Herstellungsprozesses wichtig.

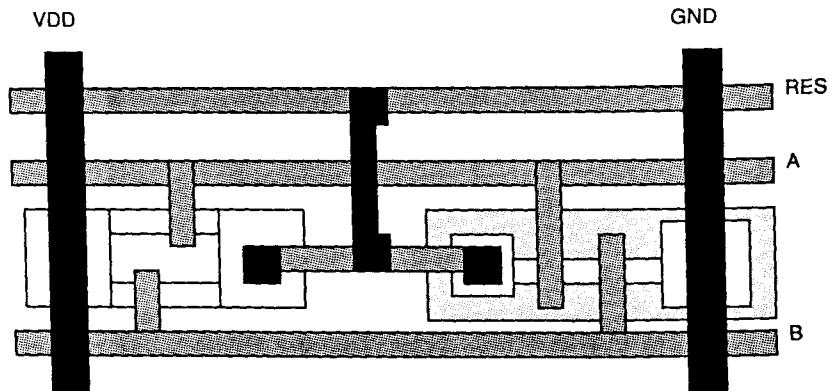

**Beispiel :**

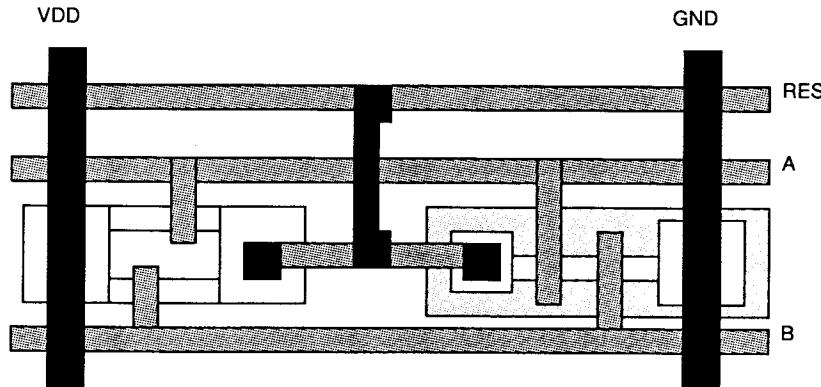

Abb. 11 zeigt ein metrisches Layout.

Als Beispiel für eine Beschreibung des elektrischen Verhaltens diene folgende Beschreibung eines statischen NOR mit 4 Eingängen in DOMOS :

TITLE NOR\$4

CIRCUIT

```

$NOR S4-1

$ 1. EINGANG

T1 P E2 N12 E1 8 1.5 110 110

```

Abb. 11: Beispiel eines Layouts

T2 N E2 NO N11 8 2.5 110 110

\$ 2. EINGANG

T3 P E3 N13 N12 8 1.5 110 110

T4 N E3 NO N11 8 2.5 110 110

\$ 3. EINGANG

T5 P E3 N14 N13 8 1.5 110 110

T6 N E3 NO N11 8 2.5 110 110

\$ 4. EINGANG

T7 P E3 N11 N14 8 1.5 110 110

T8 N E3 NO N11 8 2.5 110 110

\$ AUSGANGSBELASTUNG JE 1 GATE GEGEN MASSE UND VDD

C 1 N11 E1 0.017

C2 NO N11 0.010

TIMER 0 160

PARAMETERS

N CHANNEL N BODY NO NB 1.8E14 TOX 0.04 VT0 1.0 CGOX 0.85E-3 B0 0.045

N THETA 0.045 LOV 0.0 K1 0.3 CJ 0.46E-4 FL 0.2 F 2.0

P CHANNEL P BODY E1 NB 1.8E16 TOX 0.04 VT0 1.0 CGOX 0.85E-3 B0 0.014

P THETA 0.055 LOV 0.0 K1 0.8 CJ 0.46E-3 FL 0.2 F 2.0

WIDTH 100

Typische dedizierte Sprachen auf dieser Ebene:

Es gibt eine Vielzahl von Layouteditoren. Darüberhinaus gibt es verschiedene algorithmische Layoutsprachen. Hauptsächlich als Datenaustauschformate werden Sprachen wie CIF oder EDIF als textuelle Darstellung von Layouts benutzt. Das elektrische Verhalten kann in den Eingabesprachen elektrischer Simulatoren wie SPICE oder BONSAI (DOMOS) beschrieben werden.

### 1.3 Mikroskopisches Modell des Entwurfsprozesses

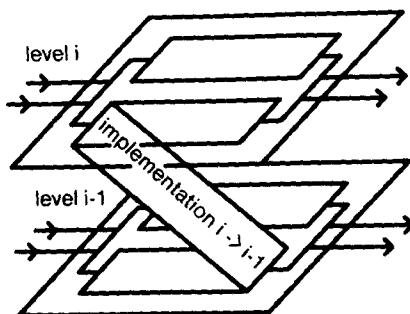

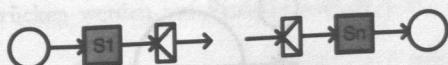

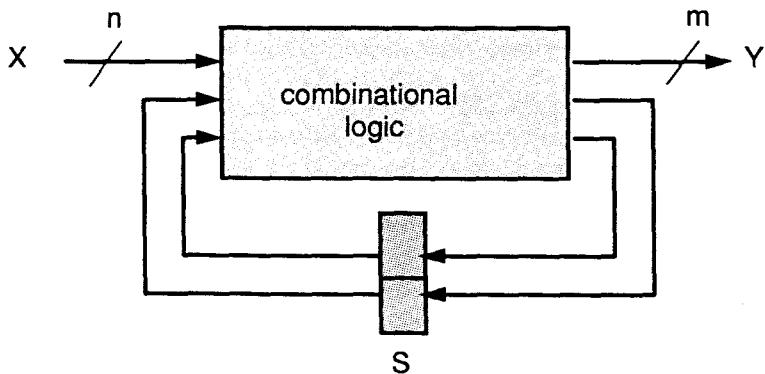

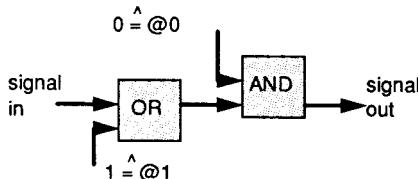

In Abschnitt 1.1 wurde ein adäquates makroskopisches Modell des Entwurfsprozesses entwickelt. Dieses Modell kann auf die sechs verschiedenen Abstraktionsebenen unabhängig angewandt werden, was zu sechs vollständig getrennten Entwurfsprozessen führen würde. Diese Prozesse können jedoch dadurch verbunden werden, daß prozeßinterne Aktivitäten durch solche ersetzt werden, die sich über mehrere Ebenen erstrecken. Ein erster Kandidat für eine derartige Aktivität ist die generierende. Innerhalb einer Abstraktionsebene wird eine derartige Aktivität Modifikation oder Optimierung genannt. Falls sie sich von einer höheren Ebene zu einer niedrigeren erstreckt, wird sie in der Regel Implementierung genannt. Sie ersetzt dann die generierende Aktivität auf der niedrigeren Ebene. Somit hat man ein Modell erhalten, wie es in Abb. 12 skizziert ist.

Abb. 12 Implementation im Entwurfsprozeß

Nun müssen die Ergebnisse der Implementations-Aktivität genauso behandelt werden wie die Ergebnisse der generierenden Aktivität, die dadurch substituiert werden. Dies bedeutet, daß sie dahingehend überprüft werden müssen, ob sie die aktuell auf der niedrigeren Ebene gültigen Restriktionen respektieren, oder nicht. Im Falle einer Verletzung wird man zunächst versuchen, das Problem auf der niedrigeren Ebene zu lösen, indem man Modifikationen und Optimierungen vornimmt. Ge-

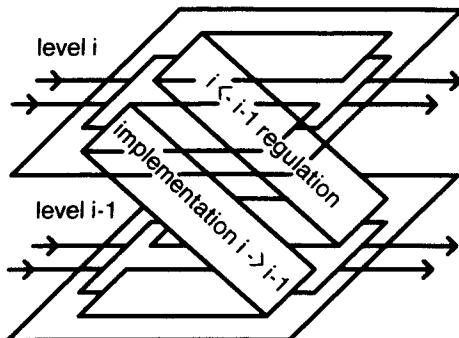

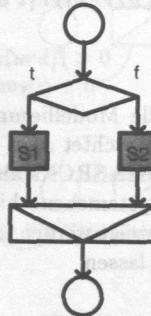

lingt dies nicht, bedeutet das, daß das auf der höheren Ebene entworfene Objekt mit den gewählten Implementationstechniken nicht unter Einhaltung der auf der niedrigen Ebene gültigen Restriktionen implementiert werden kann. Somit ist die einzige Chance, den Entwurf auf der höheren Ebene oder die Implementationsmethode zu ändern. Um eine derartige Maßnahme anzustoßen, muß die überprüfende Aktivität auf der niedrigeren Abstraktionsebene durch eine deabstrahierende substituiert werden. Diese deabstrahierende Steuerungsaktivität ersetzt die Intraebenen-Steueraktivität auf der höheren Ebene und dient dazu, die Probleme der niedrigeren Ebene zu übermitteln. Es ist zu beobachten, daß hiermit wieder eine Rückkopplungsschleife erhalten wurde, jedoch nun über mehrere Ebenen hinweg. Das so erhaltene Modell wird in Abb. 13 skizziert.

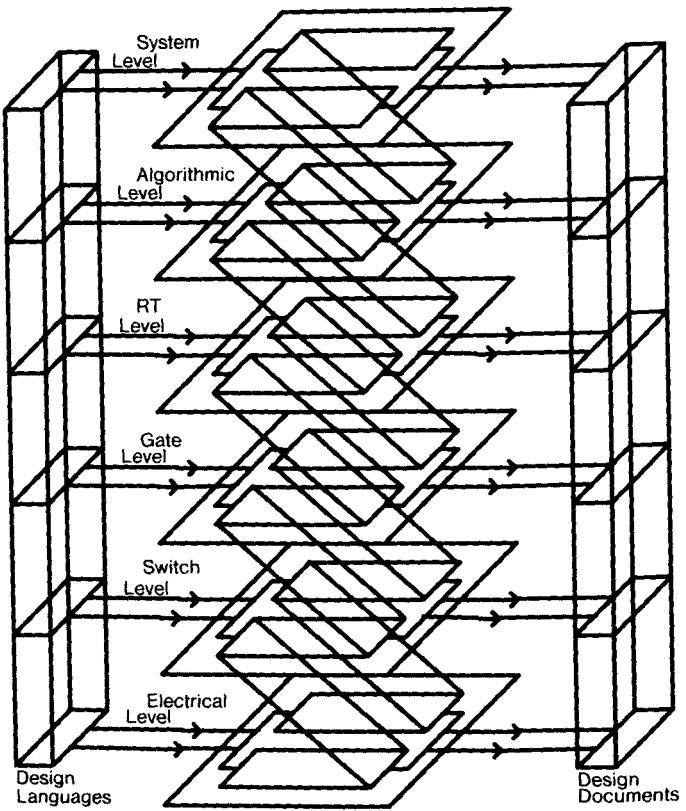

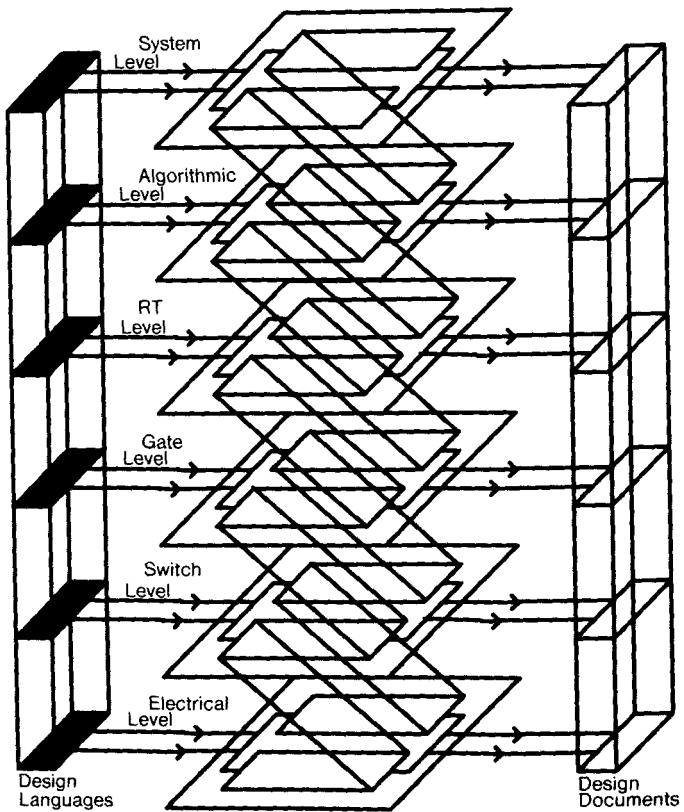

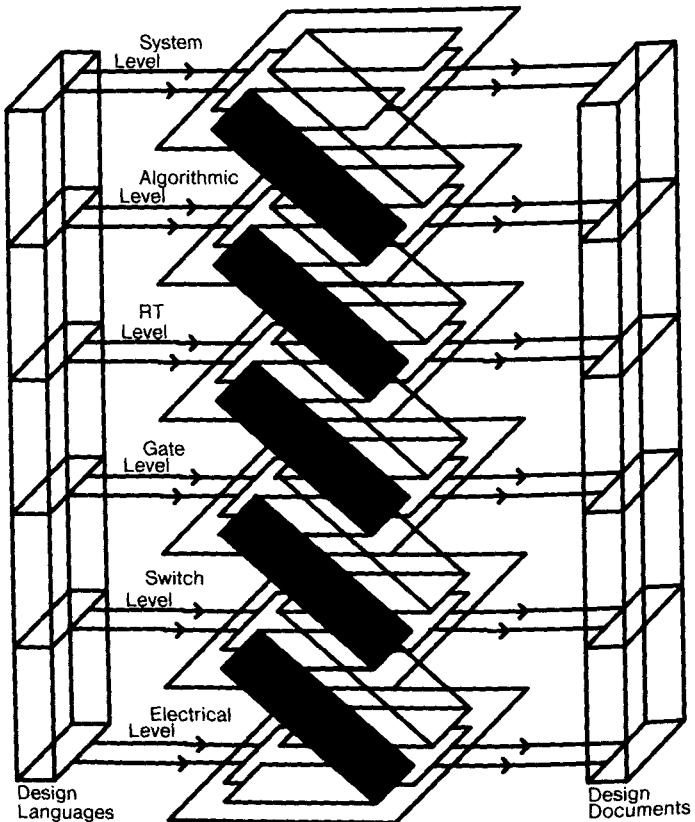

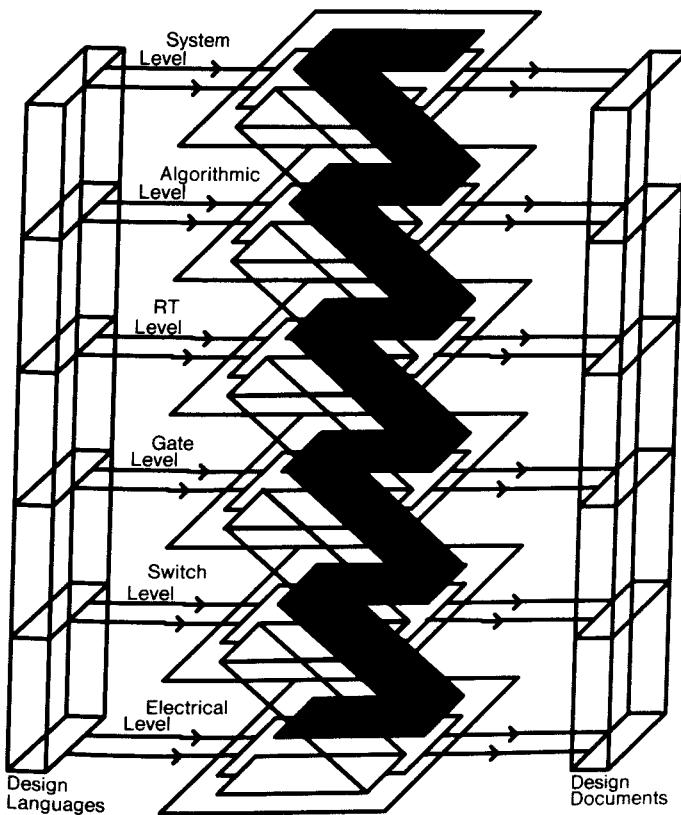

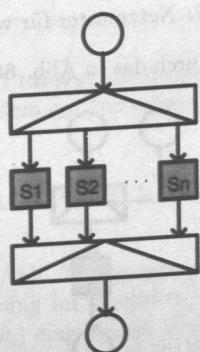

In Abb. 14 wird dieses Konzept über alle sechs Ebenen ausgedehnt, wobei der Übersichtlichkeit wegen von solchen Inter-Ebenen-Aktivitäten abgesehen wurde, die sich über mehr als zwei benachbarte Ebenen erstrecken. Grundsätzlich sind solche Aktivitäten natürlich nicht ausgeschlossen. Man kann sich sehr wohl eine Implementierungsaktivität vorstellen, die unmittelbar von der Systemebene auf die Layoutebene abbildet (idealer Silicon Compiler).

Abb. 13: Rückgekoppelter Entwurfsprozeß

Man kann sehen, wie der Aktivitätsfluß abwärts und aufwärts fließt, bis er auf der niedrigsten Ebene einen stabilen Zustand antrifft. Daher wird diese Entwurfsmethode "Yoyo"-Entwurfsstil genannt. In jedem Zustand des Entwurfsprozesses existieren Dokumentationen der aktuellen Version des Entwurfs auf verschiedenen Abstraktionsebenen. Diese Dokumente bereit zu stellen, ist die Hauptaufgabe der beteiligten Hardwarebeschreibungssprachen. Da diese Dokumente jedoch auch vom Entwerfer verändert werden können, dienen Hardwarebeschreibungssprachen auch als Eingabemittel in den Entwurfsprozeß.

Abb. 14: Entwurfsprozeß über 6 Abstraktionsebenen

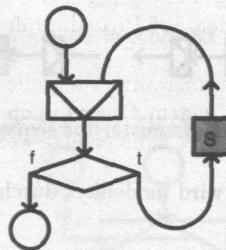

Aus dieser Diskussion folgt, daß die Skizze des Entwurfsprozesses durch zwei weitere wesentliche Komponenten komplettiert werden muß: Eine Aktivität, die über alle Abstraktionsebenen reicht, hat die verschiedenen Entwurfsdokumente auf den verschiedenen Abstraktionsebenen zu verwalten. Ein Entwurfsobjekt wird in verschiedenen Sichten (zumindest in den Sichten "Verhalten", "Struktur", "Geometrie" und "Testmethodik") auf verschiedenen Abstraktionsebenen dargestellt. Typischerweise sind diese Entwurfsdokumente hierarchisch organisiert. Hierarchie ist in diesem Kontext ein Konzept, das orthogonal zum Konzept der verschiedenen Abstraktionsebenen steht. Eine Abstraktionsebene ergibt sich durch ein spezielles Modellierungskonzept, das für die jeweilige Ebene spezifisch ist, während eine Hierarchie das Konzept der Komposition/Dekomposition wiedergibt. So sind typischerweise Dokumente über große Entwurfsobjekte auf jeder Abstraktionsebene hierarchisch. Auf der anderen Seite gibt es oft hierarchische Entwurfsdokumente, die mehrere Ebenen überspannen. Die andere Aktivität, die hinzugefügt werden muß, ist mit dem Management der Entwurfsdaten eng gekoppelt. Sie macht all diese Entwurfsdaten für den Entwerfer sichtbar und zugreifbar. Bei dieser Sichtweise wird diese Aktivität gerade ein bidirektionales Filter zwischen dem Benutzer Mensch und dem Entwurfsdatenverwalter. Dieselbe Aktivität sollte darüber hinaus benutzt werden, alle Information über Restriktionen und alle Steuerkommandos zum richtigen Empfänger zu leiten. So wird eine universelle Benutzerdialogkomponente daraus, die wiederum über alle Abstraktionsebenen reicht. Mit dieser Diskussion haben wir ein Modell des Entwurfsprozesses erhalten, wie es in Abb. 15 dargestellt ist.

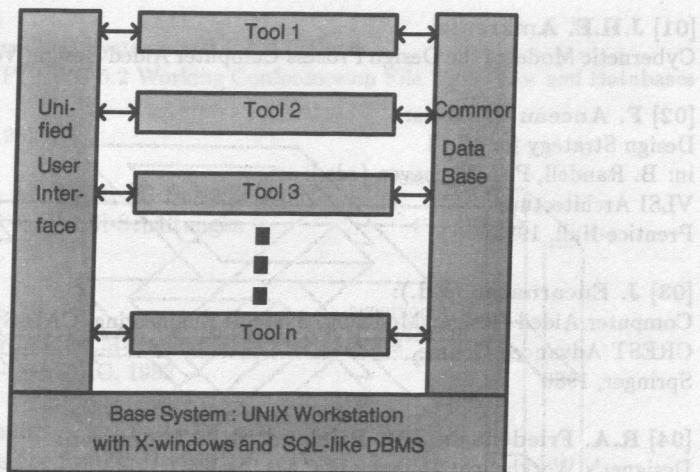

Entwurfssysteme sind dazu da, Entwurfsprozesse zu unterstützen. Ein Entwurfssystem stellt zunächst eine statische Entwurfsumgebung zur Verfügung. Sie besteht aus einer Reihe von Komponenten, wobei jede Komponente gewisse Entwurfsaktivitäten ausführen kann. Hat man solch ein Entwurfssystem, so kann man es für einen speziellen Entwurfsprozeß personalisieren, indem man die Aktivitäten und den Informationsfluß dieses Prozesses auf die Fähigkeiten der Komponenten der statischen Entwurfsumgebung abbildet. Somit wird der Entwurfsprozeß eine Aktivierungsfolge ("activation record") von Komponenten der Entwurfsumgebung zusammen mit dem geeigneten Kommunikationsfluß. Diese Abbildung eines Entwurfsprozesses ("dynamische Architektur") auf eine Entwurfsumgebung ("statische Architektur") ist nicht notwendigerweise immer möglich. Es können entweder notwendige Fähigkeiten von Aktivitäten nicht vorhanden sein, oder aber es gibt Kommunikationsrestriktionen, die zu weit reichen. Eine leistungsfähige Entwurfsumgebung, die verschiedene Entwurfsprozesse unterstützen kann, sollte eine einheitliche Benutzeroberflächenkomponente, eine universelle Datenverwaltungskomponente und eine Reihe von dedizierten Komponenten, die spezielle Entwurfsaktivitäten ausführen können, enthalten. Weiterhin sollte der Informationsfluß in uniformer Weise organisiert sein, basierend auf standardisierten Schnittstellen und mächtigen, einheitlichen konzeptionellen Datenschemata. Solch eine vereinheitlichte Entwurfsumgebung sieht typischerweise aus, wie in Abb. 16 dargestellt.

Abb. 15 Modell des Entwurfsprozesses

Abb. 16: Integrierte Entwurfsumgebung

## 1.4 Literatur

Zum Thema Entwurfsmethodik gibt es relativ wenig Literatur. Meist werden spezielle Fragestellungen oder eingeschränkte Anwendungsbereiche behandelt [02], [04], [09], [16], [19], [26], [27], [29], [32]. Koomen [12] versucht, den Entwurfsprozeß aus informationstheoretischer Sicht zu analysieren. Das in diesem Kapitel gewählte allgemeine Modell geht auf Amkreutz zurück [01]. In [23] wurde dieses Konzept auf verschiedene Abstraktionsebenen erweitert. Das Y-Diagramm geht auf Gajski zurück [05]. Der Datenbankspekt des Entwurfsprozesses wurde intensiver bearbeitet. Die Publikationen [07], [11], [20], [22], [25], [30] mögen als repräsentative Beispiele dienen. Eine besondere Rolle kommt dabei der Datenmodellierung und Schemaarbeit zu [07], [22]. Datenaustauschformate fallen auch in diese Kategorie. Hier kommt EDIF [33] eine zunehmende Bedeutung zu. Auch die Versionsverwaltung und andere Managementfunktionen spielen eine wichtige Rolle [13], [14], [17], [21]. Als Beispiel für eine einheitliche Benutzeroberfläche mag [08] dienen. In [18] werden allgemeine Fragen des Softwareengineering im CAD-Umfeld behandelt, während in [15] eine Anforderungsanalyse gewagt wird. Es gibt bereits eine Reihe von lauffähigen CAD-Umgebungen. In [06] wird eine allgemeine Umgebung vorgestellt, in [10] ein auf niedrigeren Abstraktionsebenen angesiedeltes vollständiges System und in [28], [31] werden Toolboxes dargestellt. Das wachsende Interesse an diesem Gebiet manifestiert sich in einschlägigen Konferenzen [03], [24], wobei letztere auf das Gebiet des Computerhardware-Entwurfs konzentriert war.

- [01] **J.H.E. Amkreutz:**

Cybernetic Model of the Design Process Computer Aided Design, Vol. 8, No. 3, 1976

- [02] **F. Anceau, R. Reis:**

Design Strategy for VLSI

in: B. Randell, P.C. Treleaven (eds.):

VLSI Architecture

Prentice-Hall, 1983

- [03] **J. Encarnacao (Ed.):**

Computer Aided Design: Modeling, Systems Engineering, CAD-Systems

CREST Advanced Course

Springer, 1980

- [04] **R.A. Friedenson, J.R. Brieland, R.J. Thompson:**

Designer's Workbench: Delivery of CAD Tools

in: Proceedings 19th DAC, 1982

- [05] **D.D. Gajski:**

The Structure of a Silicon Compiler

in: Proceedings of IEEE ICCD, pp 272-276, 1987

- [06] **G. Gottheil, G. Kachel, T. Kathöfer, H.J. Kaufmann, B. Kleinjohann, E. Kupitz, J. Miller, B. Nelke, F.J. Rammig, B. Steinmüller, C. White:**

The CADLAB Workstation CWS

in: F.J. Rammig(Ed.): "Tool Integration and Design Environments"

North Holland 1988

- [07] **H. Grabowski, M. Eigner:**

A Data Model for a Design Database

in: Proceedings IFIP WG 5.2 Working Conference on File Structures and Databases for CAD

North Holland, 1982

- [08] **K. Hammer, J. Hardin, T. Timmerman, D. Radin, T. Rhyne:**

Automating the Generation of interactive Interfaces

in: Proceedings of 23rd ACM/IEEE Design Automation Conference, 1986

**[09] D. Herrig:**

Design Theory for CAD Systems and CAD Objects

in: Proceedings IFIP WG 5.2 Working Conference on File Structures and Databases for CAD

North Holland, 1982

**[10] E. Hörbst, M. Nett, H. Schwärtzel:**

VENUS Entwurf von VLSI-Schaltungen

Springer 1986

**[11] R.H. Katz:**

A Database Approach for Managing VLSI Design Data

in: Proceedings 19th DAC, 1982

**[12] C.J. Koomen:**

Information Laws For System Design

in: Proceedings International Conference on Cybernetics and Society, Tokyo

Vol II, 1978

**[13] F.P. Mallman:**

The Management of Engineering Changes in the Primus System

in: Proceedings 17th DAC, 1980

**[14] R.M. Marshall, G. Bregnant:**

The Overseer: An Approach to Design Management

in: F.J. Rammig (ed.): Tool Integration and Design Environment

North Holland, 1987

**[15] C.R. McCaw et al.:**

Design Automation and VLSI in the 80's

in: Proceedings 17th DAC, 1980

**[16] M. Mills:**

A Totally Integrated Systems Approach to Design and Manufacturing at McDonnell

Douglas Corporation

in: Proceedings 18th DAC, 1981

**[17] J.A. Mölle, K.R. Dittrich, A.M. Kotz:**

Design Management Support by Advanced Databases Facilities

in: F.J. Rammig (ed.): Tool Integration and Design Environment

North Holland, 1987

- [18] **D. Nash, H. Willman:**

Software Engineering Applied to Computer-Aided Design (CAD) Software Development

in: Proceedings 18th DAC, 1981

- [19] **H. Nowacki:**

Modeling of Design Decisions for CAD

in: Proceedings CREST Advanced Course on Computer Aided Design:

Modeling, Systems Engineering, CAD Systems

Springer, 1981

- [20] **A.R. Newton, A.L. Sangiovanni-Vincentelli:**

Computer-Aided Design for VLSI Circuits

IEEE Computer, April, 1986

- [21] **A. Patrucco:**

The Monitor, a Design Manager for a Complex CAD System

in: F.J. Rammig(Ed.): "Tool Integration and Design Environments"

North Holland, 1988

- [22] **R. Piloty, B. Weber:**

IREEN - A Datamodel for Tool Integration in Open Microelectronic CAD-Systems

in: F.J. Rammig (ed.): Tool Integration and Design Environments

North Holland, 1987

- [23] **F.J. Rammig:**

A Multilevel Cybernetic Model of the Design Process

in: W.K. Giloi and B.D. Shriver(Eds.): "Methodologies for Computer System Design", North Holland, 1985

- [24] **F.J. Rammig (Ed.):**

Tool Integration and Design Environments

North Holland, 1988

- [25] **K.A. Roberts, T.E. Baker, D.H. Jerome:**

A Vertically Organized Computer-Aided Design Database

in: Proceedings 18th DAC, 1981

**[26] G. Rzevski:**

A Methodology and Associated CAD Tools for the Design of Real-Time Control Systems

in: Proceedings 2nd IFAC Symposium on Computer-Aided Design of Multivariable Technological Systems, Pergamon Press, 1983

**[27] E.G. Schlechtendahl:**

CAD Process and System Design

in: Proceedings CREST Advanced Course on Computer Aided Design: Modeling, Systems Engineering, CAD Systems, Springer, 1981

**[28] L. Spaanenburg:**

The Interconnection of Open CAD Systems

in: F.J. Rammig(Ed.): "Tool Integration and Design Environments"

North Holland, 1988

**[29] H.A. Tucker:**

Infrastructure Approach to Integrated CAD Systems

in: Proceedings CREST Advanced Course on Computer Aided Design:

Modeling, Systems Engineering, CAD Systems, Springer, 1981

**[30] P. Van der Wolf, N. Van der Meij, T.G.R. Van Leuken, I. Widyak, P. De Wilde:**

Data Management for VLSI Design: Conceptual Modeling, Tool Integration and User Interface

in: F.J. Rammig (ed.): Tool Integration and Design Environments

North Holland, 1987

**[31] F.R. Wagner, C.M.D.S. Freitas, L.G. Golendziner:**

The MPLO System - An Integrated Environment for Digital Systems Design

in: F.J. Rammig (ed.): Tool Integration and Design Environments

North Holland, 1987

**[32] H. Yoshikawa:**

General Design Theory and a CAD System

in: Proceedings IFIP WG 5.2-5.3 Working Conference on Man-Machine Communication in CAD/CAM, North Holland, 1981

**[33] --:**

EDIF - Electronic Design Interchange Format Version 2 0 0.

Electronic Industries Association

Washington D.C., 1987

## 2 Modellierungskonzepte und Entwurfssprachen

Abb. 17: Entwurfssprachen im Entwurfsprozeß

### 2.1 Modellierungskonzepte

In Kapitel 1 wurden verschiedene Modellierungskonzepte, wie sie auf verschiedenen Abstraktionsebenen geeignet sind, kurz besprochen. Sie sollen nun detaillierter diskutiert werden, da sie die Grundlage für den Entwurf von Beschreibungs- und Entwurfssprachen bilden.

#### 2.1.1 Objektorientierte Modellierung

Zunächst ist objektorientierte Modellierung ein struktureller Ansatz. Ein (zu beschreibendes) System wird als strukturierte Menge von Objekten angesehen. Diese Menge von Objekten ergibt sich durch die Instantiierung von Elementen spezifischer Objekttypen. Diese Typen können generisch sein mit unterschiedlichen Attributen für verschiedene Instantiierungen. Ein Objekttyp kann Information über verschiedene Aspekte eines solchen Objekts beinhalten wie Verhalten, Struktur, Geometrie, Testen. Damit wird die strukturelle Sichtweise des Ansatzes auf die anderen Sichten ausgedehnt. Verhalten scheint in diesem Zusammenhang die meisten Schwierigkeiten zu machen. Daher werden wir uns auf diesen Aspekt konzentrieren. Als Lösungsansatz bietet sich das Konzept des Abstrakten Datentyps (ADT) an. Ein ADT ist gegeben durch eine Signatur  $S$  und eine Menge von Gleichungen  $E$ . Die Signatur ist eine Menge von Sorten (Wertebereichsnamen) zusammen mit Operationen, die darauf definiert sind. Somit gibt die Signatur die Syntax eines Systems an, während die Gleichungen zur Definition der Semantik dienen.

### Beispiel :

Ein ADT zur Definition der Booleschen Algebra mag wie folgt aussehen:

```

type Boolean is

sorts Boolean

opns T,F : Boolean;{nullary operations, i.e. constants}

not : Boolean → Boolean; {unary operation}

and, or : Boolean, Boolean → Boolean; {binary operations}

eqns or(a,F) = a;

and(a,T) = a;

or(a,b) = or(b,a);

and(a,b) = and(b,a);

and(a,or(b,c)) = or(and(a,b),and(a,c));

or(a,and(b,c)) = and(or(a,b),or(a,c));

and(a,not(a)) = F;

or(a,not(a)) = T;

or(a,or(b,c)) = or(or(a,b),c);

and(a,and(b,c)) = and(and(a,b),c);

or(a,a) = a;

and(a,a) = a;

```

```

or(not(a),not(b)) = not(and(a,b));

and(not(a),not(b)) = not(or(a,b));

not(not(a)) = a;

endtype.

```

Dieses Beispiel illustriert auch die Bezeichnung "abstrakt" in ADT. Es wird vollständig vom Aussehen der Menge "Boolean" abstrahiert. Die einzige Forderung ist, daß es mindestens zwei Elemente geben muß, bezeichnet mit T und F. Die Sorte "Boolean" ist natürlich verschieden von dem Typ "Boolean". Die Sorte "Boolean" ist einfach eine Menge, während der Typ "Boolean" eine vollständige Algebra ist, mit Operationen definiert auf der gleichnamigen Menge, die alle genannten Gleichungen respektieren. Die Sorte "Boolean" ist von der Außenwelt nicht sichtbar. Die Algebra ist definiert auf der Basis der zwei Konstanten T und F, dem monadischen Operator **not** und den beiden dyadischen Operatoren **and** und **or**. Diese Operatoren haben die darunter angegebenen Gleichungen zu respektieren, nämlich Huntingtons Postulate. Bei Implementierten Abstrakten Datentypen (IADT) wird die Signatur durch Deklarationen gegeben, und die Gleichungen werden durch Implementationsbeschreibungen ersetzt, die definieren, wie die Operationen mittels bekannter IADTs (der sogenannten Trägerstruktur) ausgeführt werden können.

Somit ist ein IADT typischerweise definiert durch :

- Typidentifikation,

- Liste von Operationen,

- Referenz auf eine Trägerstruktur,

- Liste von Implementierungsbeschreibungen (eine pro Operation).

Dadurch wird anstelle einer reinen Spezifikation, wie im Falle des ADT, eine ausführbare Beschreibung erhalten. Sie beschreibt eine Hardwarestruktur, die als "Prozessor" charakterisiert werden kann, d.h. ein Objekt, das einen spezifischen Instruktionssatz hat (die Operationen), und in wohldefinierter Weise (wie in den Implementationsbeschreibungen angegeben) auf Anforderungen, derartige Instruktionen auszuführen, reagiert. Dies scheint eine sehr allgemeine Betrachtungsweise zu sein, die nicht auf Prozessoren im engeren Sinne eingeschränkt ist. Die DACAPO **export procedure** mag als Beispiel für dieses Konzept dienen. Dieses Sprachkonstrukt hat die allgemeine Form :

```

export <Liste von Operationen> procedure <Bezeichner> ;

<Deklarationen der Trägerstruktur>;

<Funktion oder Prozedur um Operation_1 zu implementieren>;

```

.

.

.

<Funktion oder Prozedur um Operationen zu implementieren>;

end;

Somit kann für den ADT zur Definition der Booleschen Algebra folgender IADT zur Implementierung benutzt werden :

```

export (true, false, own_not, own_and, own_or) procedure boolean;

const one = "1", zero = "0";

function true () : bit;

begin

true := one

end;

function false () : bit;

begin

false := zero

end;

function own_not (in arg : bit) : bit;

begin

own_not := not(arg)

end;

function own_and (in arg_1, arg_2 : bit) : bit;

begin

own_and := arg_1 and arg_2

end;

function own_or (in arg_1, arg_2 : bit) : bit;

begin

own_or := arg_1 or arg_2

end;

end;

```

Es sollte bemerkt werden, daß dieses Beispiel nur zur Illustration des Konzeptes gewählt wurde. In der Praxis wird sich niemand auf diese Weise seine eigene Boolesche Algebra definieren, da sie nichts weiter als die in DACAPO eingebaute Boole-

lesche Algebra zur Verfügung stellt. Tatsächlich ist dieser IADT nur deshalb eine korrekte Implementierung des obigen ADT, weil die Operationen `not`, `or`, `and` von DACAPO auf dem Datentyp `bit` in Übereinstimmung mit den Axiomen der Booleschen Algebra definiert sind. Brauchbarere Beispiele für IADTs werden im Abschnitt 2.3 gegeben werden. Der objektorientierte Ansatz hat seine Tradition im Bereich des Software Engineering mit den Sprachen SIMULA, SMALLTALK, MAINSAIL und CommonLoops als typische Vertreter. Auf der anderen Seite ist diese Art, Module zu betrachten, für Hardwareentwerfer sehr natürlich. Sie setzen Systeme aus Komponenten zusammen, die eine Menge von Operationen an die Umwelt anbieten. Allerdings paßt die Aktivierungsvorstellung der Softwarewelt nicht ohne Modifikationen in den Hardwarebereich. Auf niedrigeren Ebenen ist es nicht adäquat, anzunehmen, daß ein Modul eine Operation auf Anforderung ausführt, d.h. als Reaktion auf ein Paket, das ihm gesandt wird. So offeriert beispielsweise ein Und-Gatter kontinuierlich einen Wert, der abhängig ist von den aktuellen Werten an seinen Eingängen (u.U. unter Einbeziehung einer gewissen Verzögerung), ohne daß irgendeine Anforderung durch irgendein Paket stattfindet. Weiterhin sind die Module eines Hardwaresystems nebenläufig aktiv, während man in klassischen objektorientierten Sprachen ein sequentielles Verhalten annimmt. Daher wird im Bereich des Hardwareentwurfs der objektorientierte Ansatz hauptsächlich auf höheren Abstraktionsebenen benutzt. Auf diesen Ebenen ist es ein wesentliches Ziel des Entwurfsprozesses, das System in Module zu dekomponieren, wobei vor einem weiteren Implementationsprozeß für diese Module drei Aspekte pro Modul definiert werden müssen :

- Die Funktionalität des Moduls,

- die Kommunikationsprotokolle, wie sie von dem Modul erkannt und erzeugt werden,

- allgemeine Restriktionen z.B. bzgl. Leistung, Testbarkeit,...

Diese Eigenschaften können mittels des objektorientierten Ansatzes in adäquater Weise ausgedrückt werden.

### 2.1.2 Imperative Sicht

Die imperative Sicht hat ihre Tradition in algorithmischen Programmiersprachen für Prozessoren vom v.Neumann-Typ. Von seiner Natur ist es ein Verhaltenskonzept mit wenig Unterstützung für strukturelle oder geometrische Beschreibungen. Derartige Beschreibungen können trotzdem mittels algorithmischer Sprachen erzeugt werden. Aber dann ist eine derartige Sprache eine Art Meta-Sprache zur Generierung einer Beschreibung und nicht zur Beschreibung selbst. Die Schwächen von imperativen Sprachen auf dem Gebiet der Struktur und der Geometrie werden dadurch ausgeglichen, daß dieser Ansatz die beste Unterstützung für den Entwickler dafür bietet, seine Intentionen bezüglich des dynamischen Verhaltens über die

Zeitachse wiederzugeben. So wie die objektorientierte Sicht pro Modul spezifiziert, welches die Operationen sind, die das Modul ausführen kann, und was die Effekte dieser Operationen sind, so beschreibt die imperative Sicht, wie diese Effekte durch Ausführung eines interpretierenden Algorithmus erreicht werden. Daher überrascht es nicht, daß im Fall von IADTs die Implementation der Operationen üblicherweise im imperativen Stil gegeben werden (man beachte das obige DACAPO-Beispiel im Abschnitt 2.1.1).

Man könnte annehmen, daß jede imperative Sprache für diesen Anwendungsfall geeignet sei, vorausgesetzt die notwendigen Datentypen werden angeboten. Tatsächlich hat es verschiedene Ansätze gegeben, übliche Programmiersprachen mit nur sehr geringen Änderungen als algorithmische Hardwarebeschreibungssprachen zu benutzen. Derartige Versuche sind auf der Basis von PL/I und APL gemacht worden. Allerdings sind übliche Programmiersprachen entweder strikt sequentiell oder bieten einen sehr eingeschränkten Grad an Parallelität. Daher muß man sich nach leistungsfähigeren operationalen Konzepten umsehen. Hier sollen zeitbehaftete Interpretierte Petri-Netze und "Communicating Sequential Processes" diskutiert werden.

### 2.1.2.1 Zeitbehaftete Interpretierte Petri-Netze

Petri-Netze wurden von Carl Adam Petri als eine naheliegende Erweiterung endlicher Automaten entwickelt. Sie modellieren ein System als eine Menge von Aktionen (genannt Transitionen) die durch Bedingungen (genannt Stellen) gesteuert werden. Jede Transition entscheidet individuell, ob ihre lokale Ausführbarkeitsbedingung erfüllt ist oder nicht. Somit ist die Steuerung über das gesamte System verteilt. Petri-Netze lassen sich sehr einfach formal definieren und sind ebenso einfach zu verstehen.

#### Def. 2.1.2.1.1 (Petri-Netz-Graph)

$PG = (P, T, E)$  heißt Petri-Netz-Graph : $\Leftrightarrow$

$P$  endliche Menge (von "Stellen")

$T$  endliche Menge (von "Transitionen")

$E \subseteq (P \times T) \cup (T \times P)$

$P \cap T = \emptyset$

$\forall x \in (P \cup T) : \exists y \in (P \cup T) : (x, y) \in E \vee (y, x) \in E$

◇

#### Def. 2.1.2.1.2 (Petri-Netz)

$PN = (PG, m_0, R)$  heißt Petri-Netz : $\Leftrightarrow$

$PG = (P, T, E)$  Petri-Netz-Graph

$m_0 \in M = \{m \mid m : P \rightarrow \mathbb{N}_0\}$  (initiale Markierung)

$R \in \{r \mid r : T \rightarrow f_T\}$

mit  $f_T = \{f_t \mid t \in T\} \wedge \forall t \in T : (f_t : M \rightarrow M)$  (Schaltregel von  $T$ )

◇

In Petri-Netzen werden "Stellen" dazu benutzt, um Bedingungen zu modellieren. Falls eine Stelle  $p$  eine Marke enthält, d.h.  $m(p) > 0$ , wird angenommen, daß die zugeordnete Bedingung wahr ist. Somit modelliert eine Markierung einen globalen Zustand im globalen Bedingungsraum. Aktionen werden durch "Transitionen" modelliert. Eine Transition kann schalten, wenn bestimmte Bedingungen an ihren Eingangs- und Ausgangsstellen wahr sind (z.B. alle Eingangsstellen markiert sind). Durch das Schalten manipuliert eine Transition die Markierung ihrer Eingangs- und Ausgangsstellen (z. B. sie entfernt eine Marke von jeder Eingangsstelle und legt eine in jede Ausgangsstelle hinein). Somit modifiziert eine Transition lokal den globalen Zustand des Bedingungsraums.

Klassische Petri-Netze kennen genau eine Schaltregel:

#### Def. 2.1.2.1.3 (a-schaltbar, a-Schalten)

Sei  $PN = ((P, T, E), m_0, R)$  ein Petri-Netz.

Bezeichne  $\cdot t = \{p \in P \mid (p, t) \in E\}$  die Menge der Eingangsstellen von  $t$ ,  $t = \{p \in P \mid (t, p) \in E\}$  die Menge ihrer Ausgangsstellen.

Die Transition  $t$  heißt a-schaltbar unter der Markierung  $m$  : $\Leftrightarrow$

$$\forall p \in \cdot t : m(p) > 0.$$

$f_t : M \rightarrow M$  heißt a-Schalten der Transition  $t$  : $\Leftrightarrow$

$$f_t(m(p)) := m(p) - 1 : \Leftrightarrow p \in \cdot t$$

$$f_t(m(p)) := m(p) + 1 : \Leftrightarrow p \in t$$

$$f_t(m(p)) := m(p) \text{ else.}$$

◇

In Petri-Netzen mit einem heterogenen Satz von Schaltregeln kann  $f_t$  von Transition zu Transition verschieden sein. Üblicherweise gibt es einige wenige Klassen von Transitionen, wobei jede Klasse ihre eigene Schaltregel hat.

#### Def. 2.1.2.1.4 (Interpretiertes Petri-Netz)

$IPN = (PN, I, D)$  heißt Interpretiertes Petri-Netz : $\Leftrightarrow$

$PN = ((P, T, E), m_0, R)$  Petri-Netz

$I \in \{i \mid i : T \rightarrow \sigma \cup \{\lambda\}\}$  mit

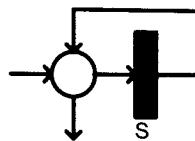

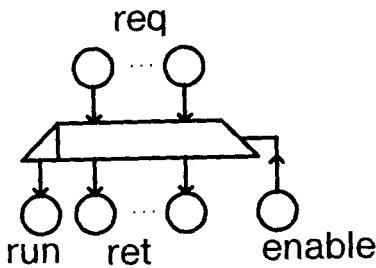

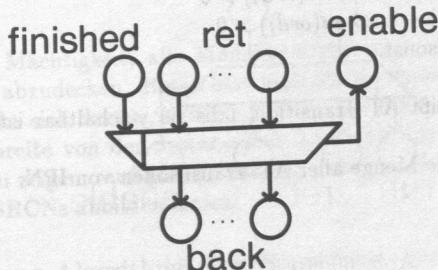

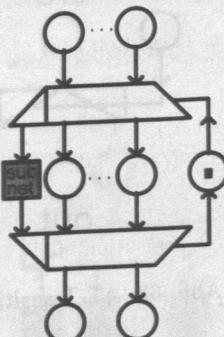

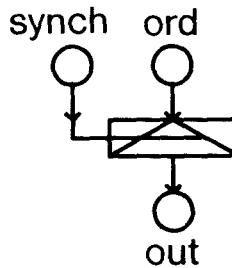

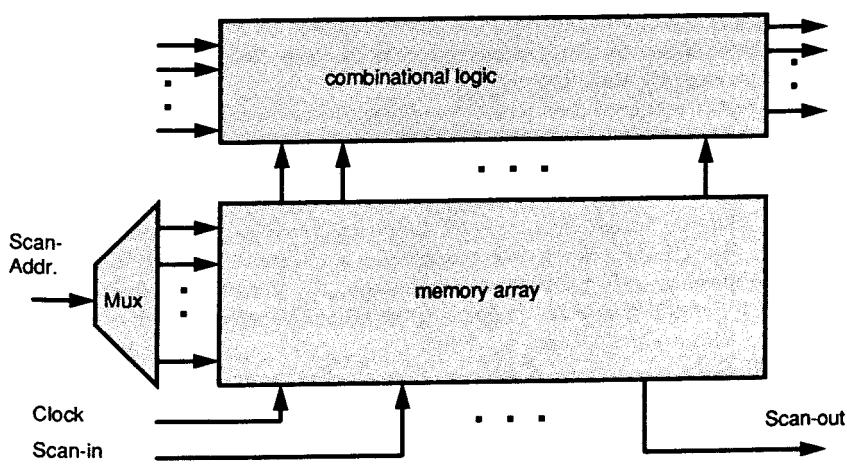

$\sigma = \{o \mid o : \text{dom}(o) \subseteq X(D) \rightarrow \text{codom}(o) \subseteq X(D)\}$