FORTSCHRITT-

BERICHTE

**VDI**

Dipl.-Inform. Ulrich Rückert, Dortmund

# **Integrationsgerechte Umsetzung von assoziativen Netzwerken mit verteilter Speicherung**

Reihe **10**: Informatik/

Kommunikationstechnik Nr. **130**

**VDI** VERLAG

Verlag des Vereins Deutscher Ingenieure · Düsseldorf

Rückert, Ulrich

## **Integrationsgerechte Umsetzung von assoziativen Netzwerken mit verteilter Speicherung**

Fortschr.-Ber. VDI Reihe 10 Nr. 130. Düsseldorf: VDI-Verlag 1990.

154 Seiten, 65 Bilder, 15 Tabellen.

**Für die Dokumentation:** Assoziative Netzwerke — Neuronale Netze — Assoziativspeicher — Integrationsgerechter Entwurf — Fehlertoleranz — Verteiltes Speicherprinzip — CMOS-Technologie

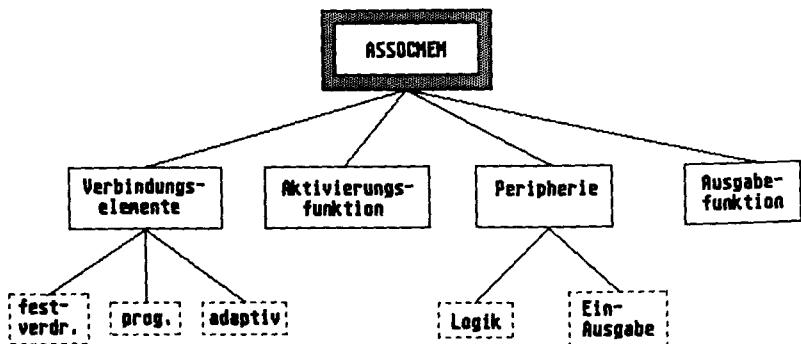

Assoziative Netzwerke mit verteilter Speicherung, deren grundlegende Aufgabe die Musterabbildung bzw. -vervollständigung ist, bilden eine Untermenge der derzeit viel diskutierten Neuronalen Netze. Für diese Untermenge wird eine einheitliche Beschreibungsform angegeben sowie die für die Anwendung wichtigen Eigenschaften der Speichereffektivität und Fehlertoleranz quantitativ erfaßt. Verschiedene integrationsgerechte Realisierungsalternativen ausgewählter Modelle werden diskutiert und mit Hilfe von integrierten Testschaltungen überprüft. Die erarbeiteten theoretischen und praktischen Ergebnisse bilden die Grundlage für zwei neue VLSI-Systemarchitekturen, die anhand von konkreten Bausteinrealisierungen in CMOS-Technologie analysiert werden. Beide Konzepte zeichnen sich durch einen modularen und regulären Systemaufbau, eine effiziente Informationsspeicherung und einen sehr schnellen assoziativen Datenzugriff aus.

### **Die Reihen der FORTSCHRITT-BERICHTE VDI:**

- |                                          |                                                                        |

|------------------------------------------|------------------------------------------------------------------------|

| 1 Konstruktionstechnik/Maschinenelemente | 12 Verkehrstechnik/Fahrzeugtechnik                                     |

| 2 Fertigungstechnik                      | 13 Fördertechnik                                                       |

| 3 Verfahrenstechnik                      | 14 Landtechnik/Lebensmitteltechnik                                     |

| 4 Bauingenieurwesen                      | 15 Umwelttechnik                                                       |

| 5 Grund- und Werkstoffe                  | 16 Technik und Wirtschaft                                              |

| 6 Energieerzeugung                       | 17 Biotechnik                                                          |

| 7 Strömungstechnik                       | 18 Mechanik/Bruchmechanik                                              |

| 8 Meß-, Steuerungs- und Regelungstechnik | 19 Wärmetechnik/Kältetechnik                                           |

| 9 Elektronik                             | 20 Rechnerunterstützte Verfahren<br>(CAD, CAM, CAE, CAP, CAQ, CIM,...) |

| 10 Informatik/Kommunikationstechnik      | 21 Elektrotechnik                                                      |

| 11 Schwingungstechnik                    |                                                                        |

© VDI-Verlag GmbH · Düsseldorf 1990

Alle Rechte, auch das des auszugsweisen Nachdruckes, der auszugsweisen oder vollständigen Wiedergabe (Photokopie, Mikrokopie), der Speicherung in Datenverarbeitungsanlagen und das der Übersetzung, vorbehalten.

Als Manuskript gedruckt. Printed in Germany.

ISSN 0178-9627

ISBN 3-18-143010-2

## **Danksagungen**

Die vorliegende Arbeit entstand während meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Lehrstuhl für Bauelemente der Elektrotechnik der Universität Dortmund.

Herr Prof. Dr.-Ing. Karl Goser, dem ich die Anregung zu diesem Thema verdanke, hat die Arbeit durch sein stetes Interesse und mit vielen wertvollen Diskussionen begleitet. Er hat stets für sehr gute Arbeitsbedingungen gesorgt und damit die Voraussetzungen geschaffen, unter denen die Arbeit gedeihen konnte. Dafür sei ihm an dieser Stelle herzlich gedankt.

Herrn Prof. Dr.-Ing. Heiner Klar danke ich für die anregenden und fördernden Hinweise sowie für die bereitwillige Übernahme des Koreferates.

Großen Anteil an der Durchführung dieser Arbeit haben Dr.-Ing. Hilleringmann und die Mitarbeiter der Technologielinie, die bei technologischen Problemen immer mit Rat und Tat zur Seite standen und die benötigten Testschaltungen stets mit Sorgfalt gefertigt haben.

Von meinen Kollegen erhielt ich in zahlreichen Gesprächen wertvolle Anregungen und Hinweise. Allen, die durch Diskussion und Kritik zum Gelingen dieser Arbeit beigetragen haben, möchte ich recht herzlich danken. Besonders möchte ich mich diesbezüglich bei Herrn Dipl.-Ing. Heite, Herrn Dipl. Phys. Kreuzer und Herrn Dipl.-Ing. Soennecken bedanken.

Für die ständige Hilfsbereitschaft und die Unterstützung während meiner Tätigkeit am Lehrstuhl Bauelemente bedanke ich mich bei Frau Menke und Herrn Prof. Dr.-Ing. Schumacher. Frau Schmidtbauer und Frau Lunte möchte ich für die schnelle Anfertigung von verschiedenen Fotos meinen Dank aussprechen.

Weiterhin möchte ich mich bei den Studien- und Diplomarbeitern Herrn Surmann, Herrn Stiebler, Herrn Groß und Herrn Kleerbaum für zahlreiche Simulationen, Messungen und Diskussionen bedanken.

Ein ganz besonderer Dank gilt meiner Frau Hannelore für ihre hilfreiche Unterstützung bei der Erstellung des Manuskriptes und ihre fürsorgliche Rücksichtnahme während der Entstehung dieser Arbeit.

## Inhaltsverzeichnis

|                                                                                 |    |

|---------------------------------------------------------------------------------|----|

| <b>1. Einleitung .....</b>                                                      | 3  |

| <b>1.1 Zielsetzung .....</b>                                                    | 6  |

| <br>                                                                            |    |

| <b>2. Grundlagen assoziativer Netzwerke .....</b>                               | 8  |

| <b>2.1 Neurophysiologische Motivation .....</b>                                 | 8  |

| <b>2.2 Eine allgemeine Modellbeschreibung .....</b>                             | 15 |

| <b>2.2.1 Definition einer Verarbeitungseinheit .....</b>                        | 16 |

| <b>2.2.2 Definition eines assoziativen Netzwerkes .....</b>                     | 19 |

| <b>2.3 Assoziative Informationsverarbeitung .....</b>                           | 22 |

| <b>2.3.1 Aufgabenstellung .....</b>                                             | 22 |

| <b>2.3.2 Die Pseudoinversen-Technik .....</b>                                   | 24 |

| <b>2.3.3 Die assoziative Matrix .....</b>                                       | 25 |

| <b>2.3.4 Das Hopfield-Netz .....</b>                                            | 28 |

| <b>2.4 Anwendungsbeispiele .....</b>                                            | 31 |

| <br>                                                                            |    |

| <b>3. Speichereigenschaften assoziativer Netzwerke .....</b>                    | 34 |

| <b>3.1 Speichereffektivität .....</b>                                           | 34 |

| <b>3.1.1 Speichereffektivität einer assoziativen Matrix.....</b>                | 34 |

| <b>3.1.2 Speichereffektivität eines Hopfield-Netzes .....</b>                   | 41 |

| <b>3.1.3 Speichereffektivität der<br/>         Pseudoinversen-Technik .....</b> | 42 |

| <b>3.2 Fehlertoleranz .....</b>                                                 | 45 |

| <b>3.2.1 Externe Fehler in der Eingabe .....</b>                                | 45 |

| <b>3.2.2 Defekte Komponenten im Netzwerk .....</b>                              | 50 |

| <b>3.2.3 Berechnungsgenauigkeiten .....</b>                                     | 53 |

| <b>3.3 Vergleich mit inhaltsorientierten Zugriffsmethoden .....</b>             | 58 |

|                                                                                   |     |

|-----------------------------------------------------------------------------------|-----|

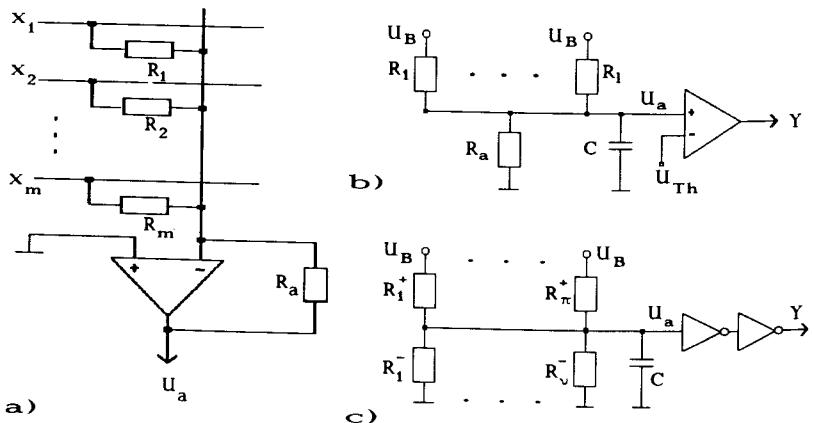

| <b>4. Grundschaltungen für eine Verarbeitungseinheit .....</b>                    | 61  |

| <b>4.1 Realisierung in digitaler Schaltungstechnik .....</b>                      | 61  |

| <b>4.2 Berechnung der Aktivierungsfunktion in analoger Schaltungstechnik.....</b> | 63  |

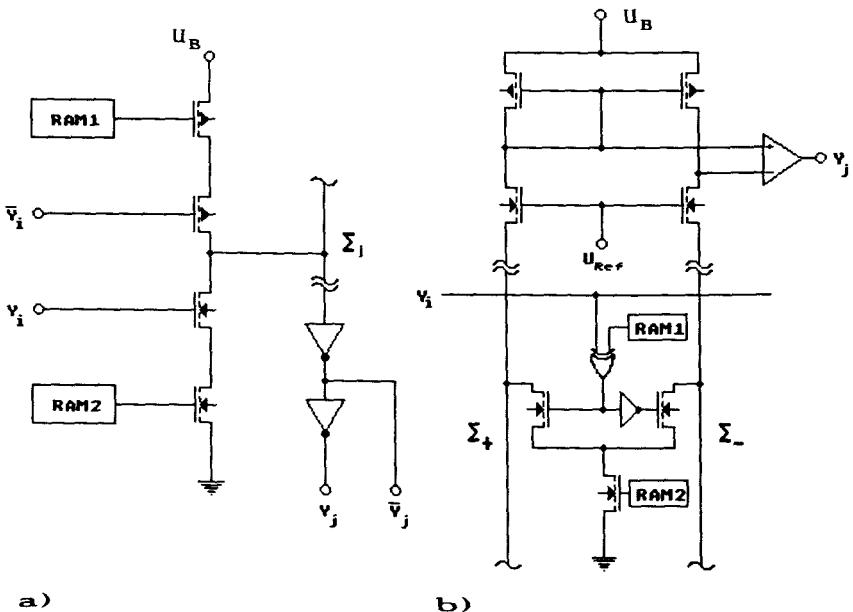

| <b>4.2.1 Stromsummation.....</b>                                                  | 63  |

| a) <i>Statisches Verhalten.....</i>                                               | 63  |

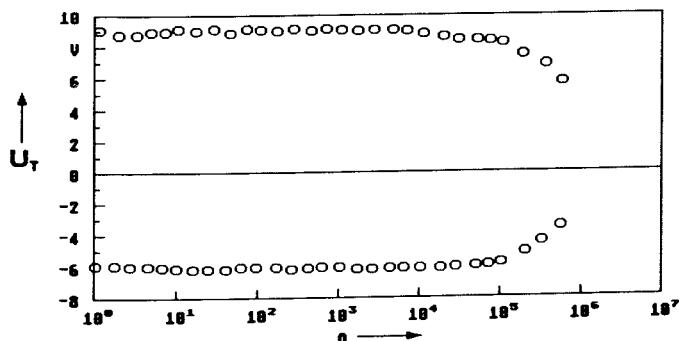

| b) <i>Dynamisches Verhalten .....</i>                                             | 72  |

| <b>4.2.2 Geschaltete Kapazitäten .....</b>                                        | 75  |

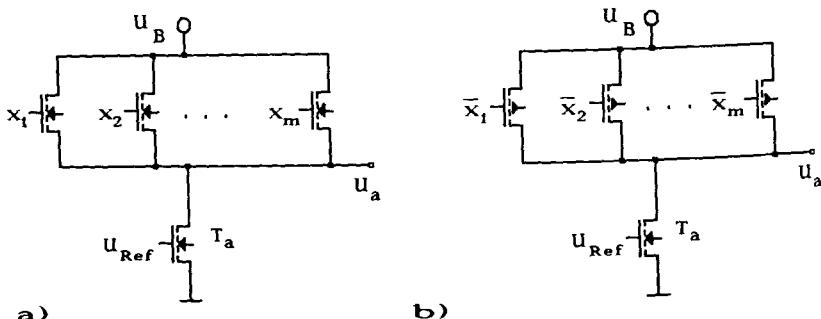

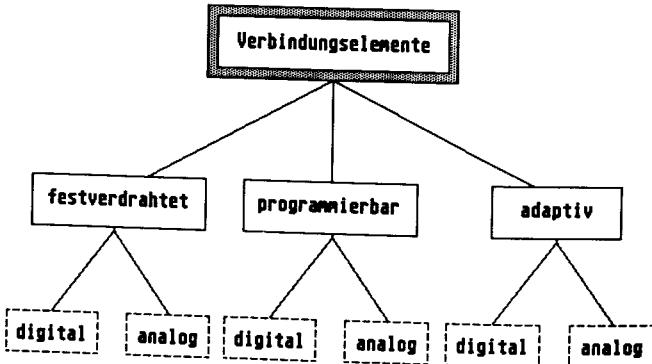

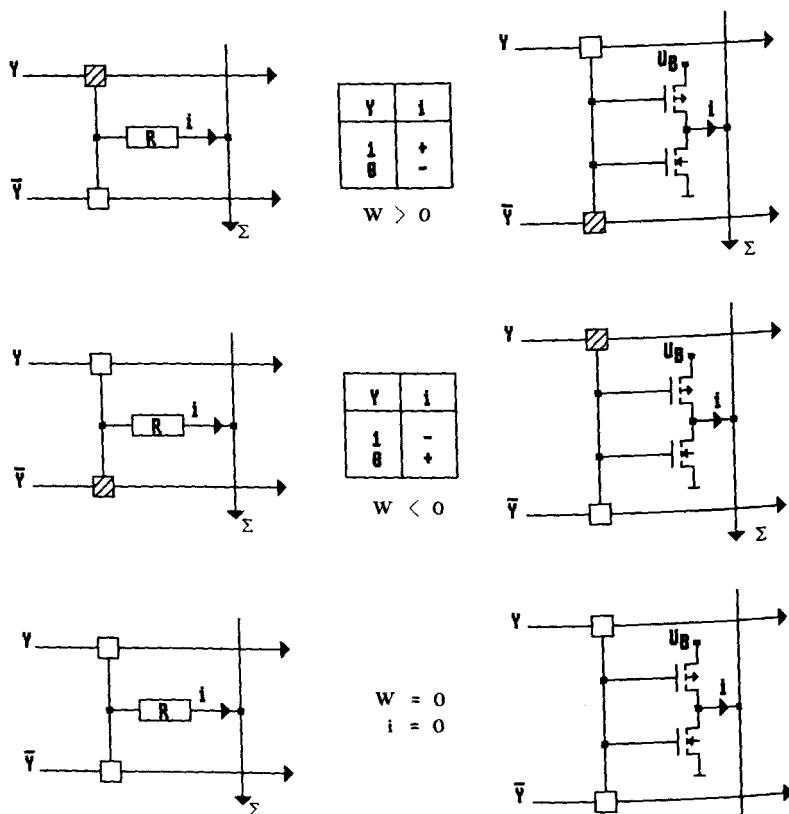

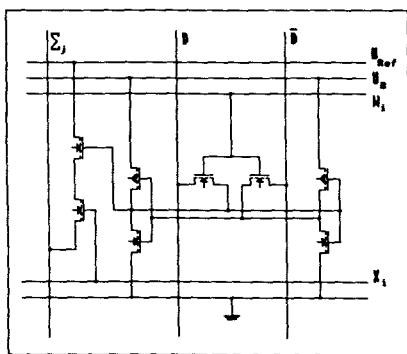

| <b>4.3 Realisierung der Verbindungselemente .....</b>                             | 77  |

| <b>4.3.1 Festverdrahtete Verbindungselemente .....</b>                            | 78  |

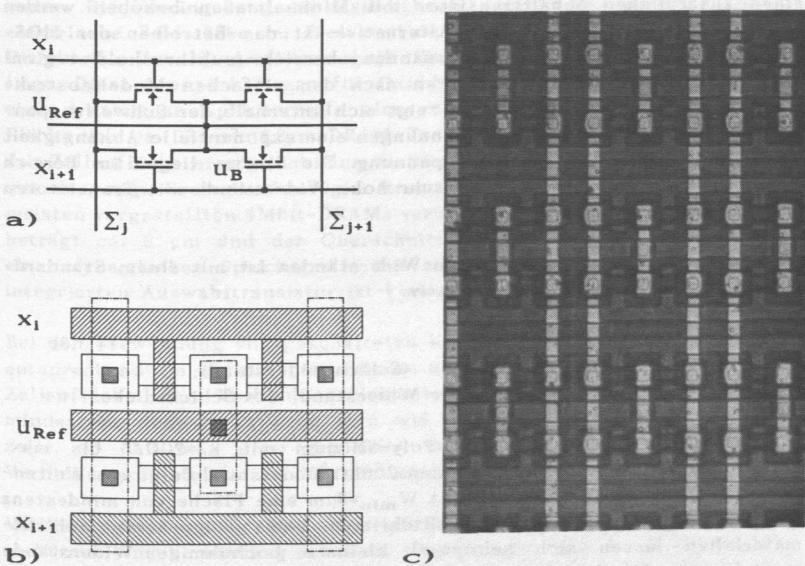

| <b>4.3.2 Programmierbare Verbindungselemente .....</b>                            | 83  |

| <b>4.3.3 Adaptive Verbindungselemente .....</b>                                   | 87  |

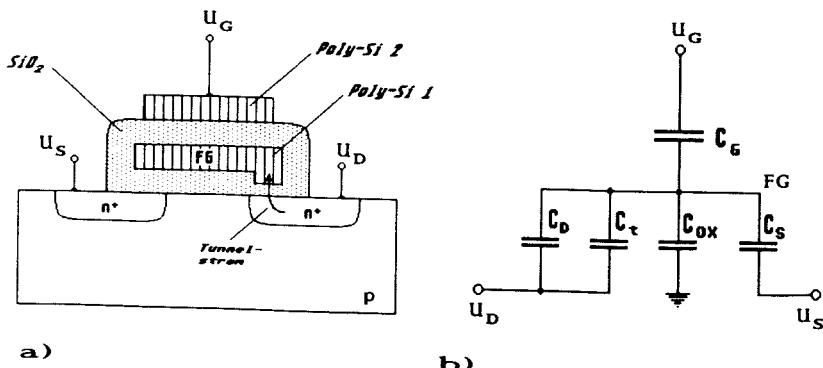

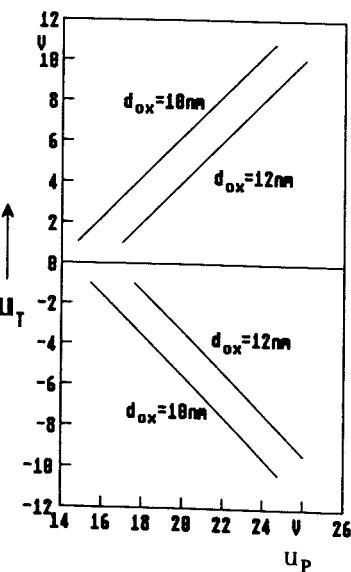

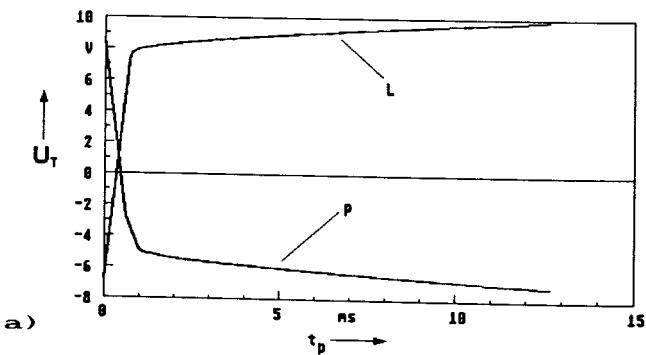

| a) <i>Pogrammierbare nichtflüchtige Speicherzellen.....</i>                       | 87  |

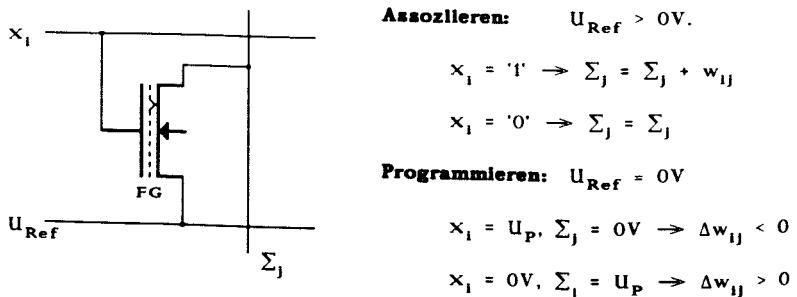

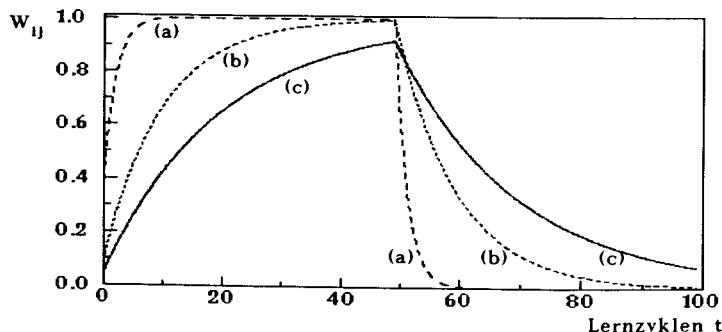

| b) <i>Ein adaptives Verbindungselement mit Floating-Gate-Transistor .....</i>     | 92  |

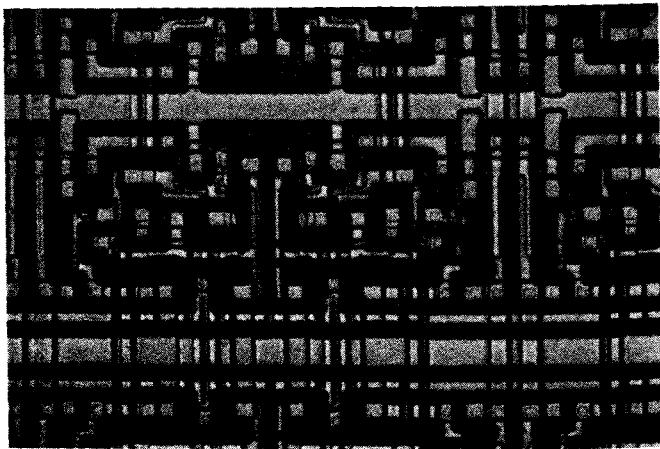

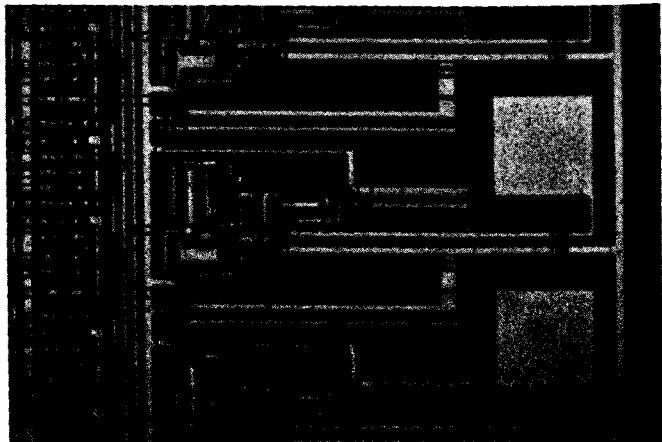

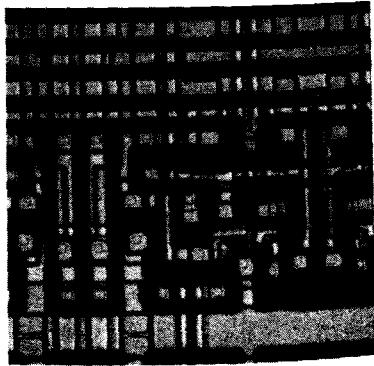

| <b>4.4 Integrierte Testschaltungen .....</b>                                      | 98  |

| <b>4.5 Diskussion .....</b>                                                       | 103 |

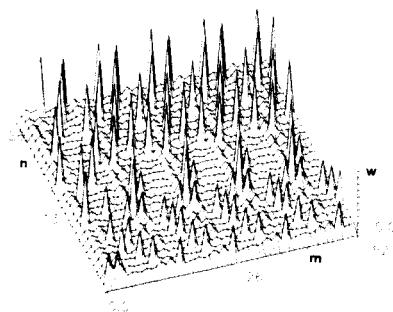

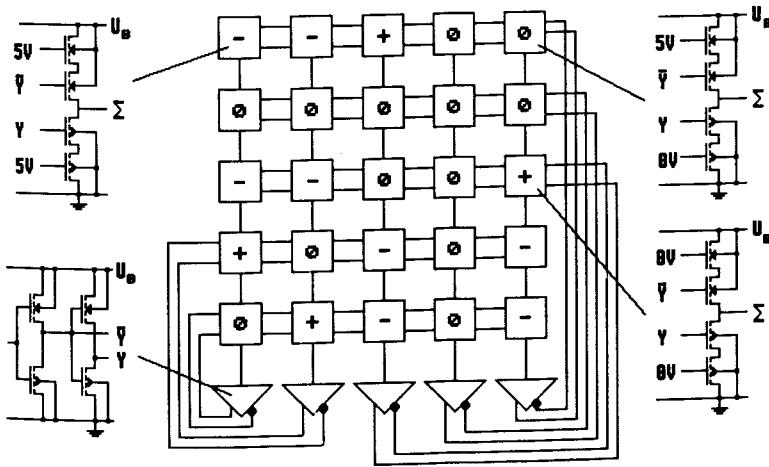

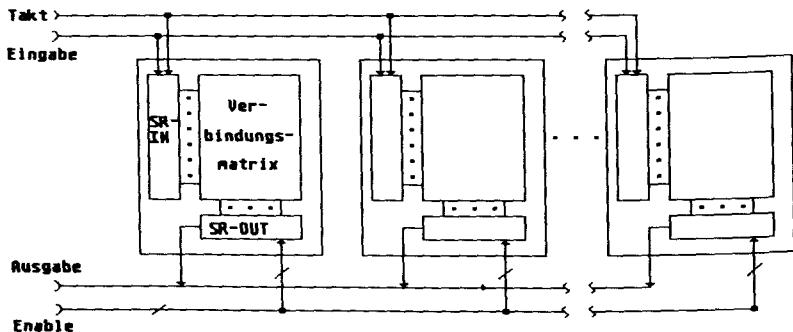

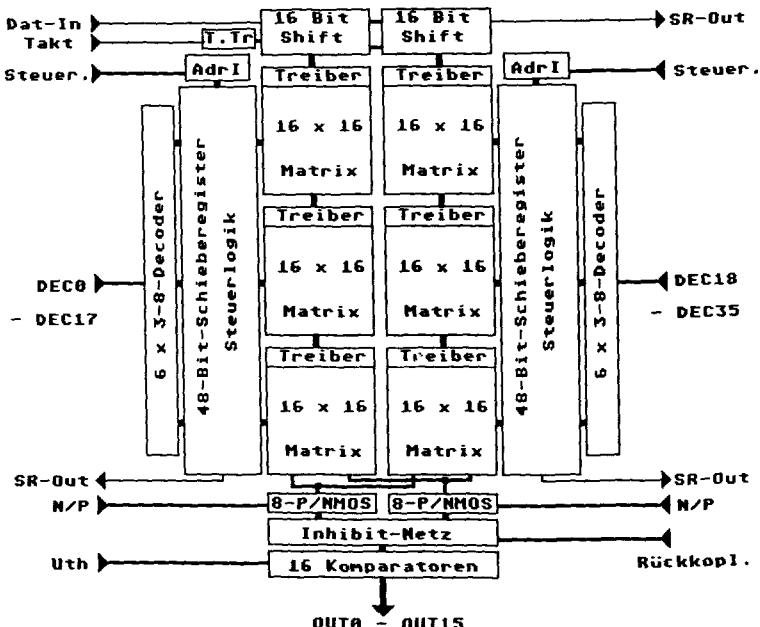

| <b>5. Systementwurf und Realisierung einer assoziativen Matrix ..</b>             | 105 |

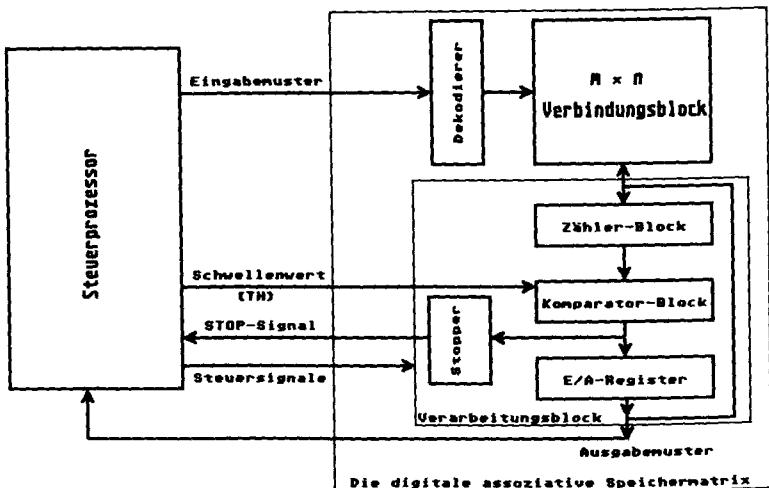

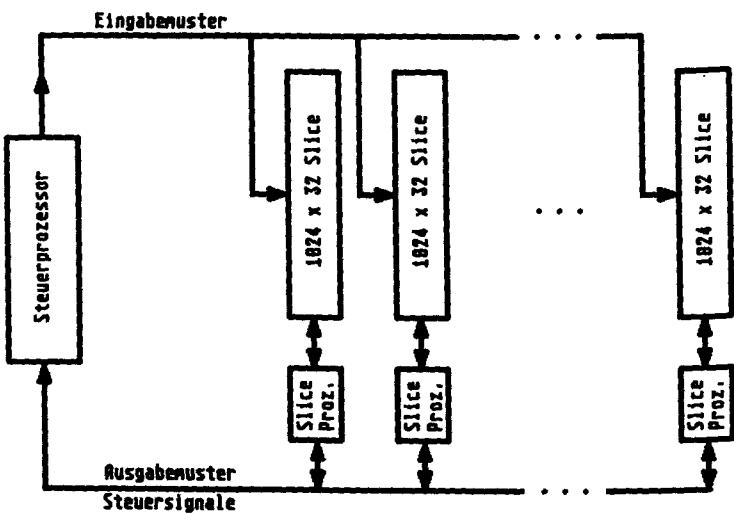

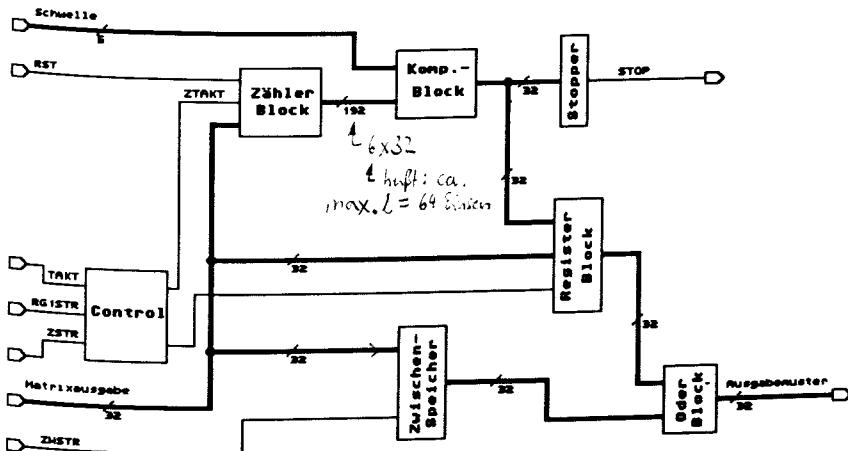

| <b>5.1 Digitale Implementierung einer assoziativen Matrix .....</b>               | 107 |

| <b>5.2 Digital-analoge Implementierung einer assoziativen Matrix.....</b>         | 115 |

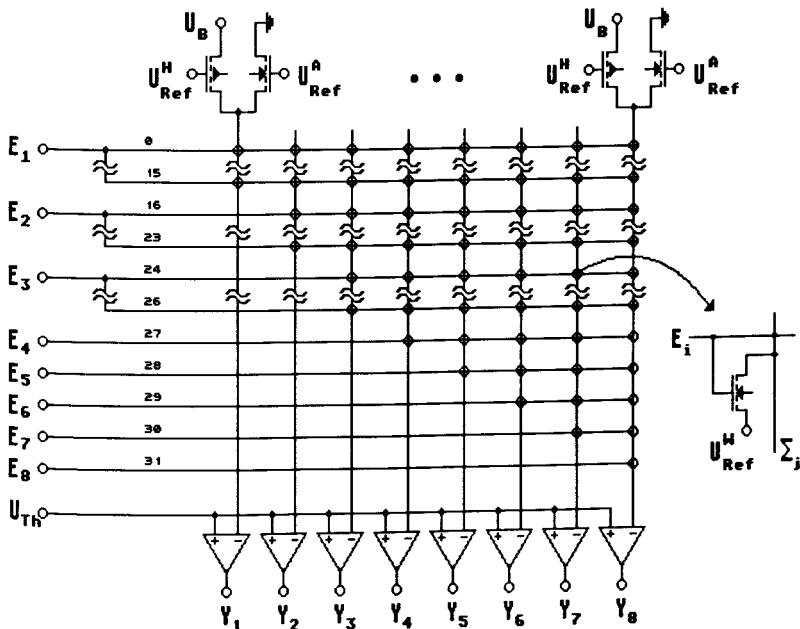

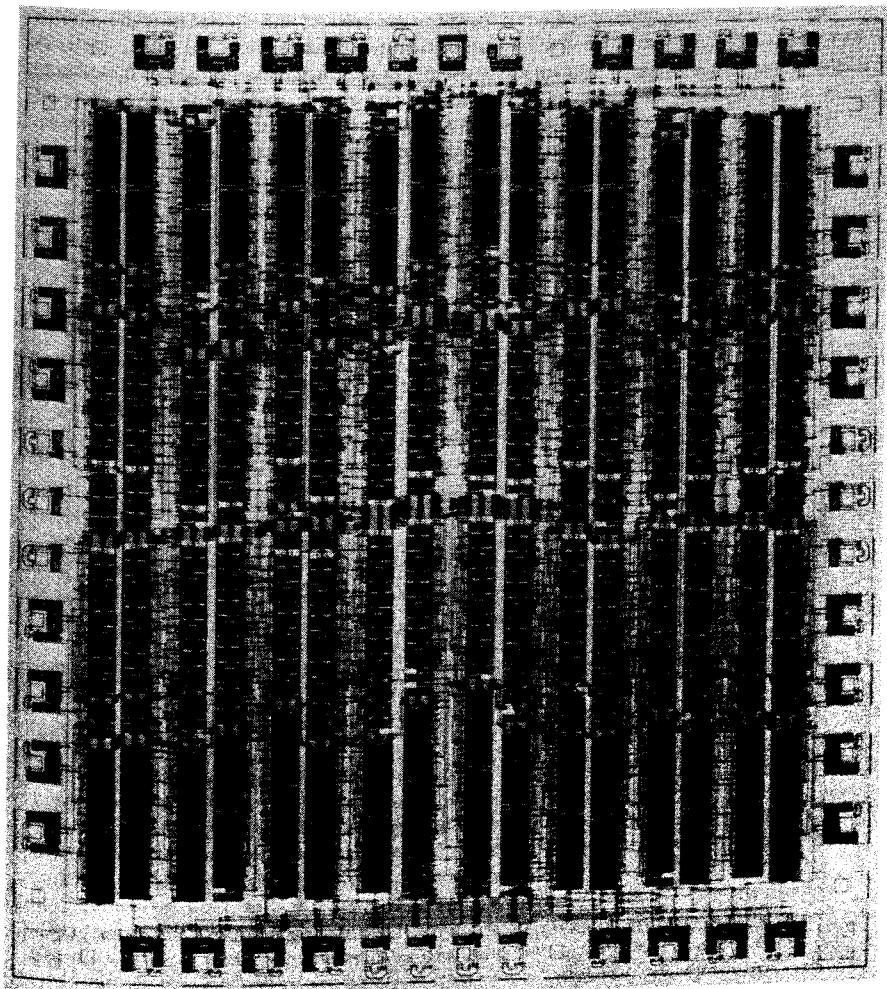

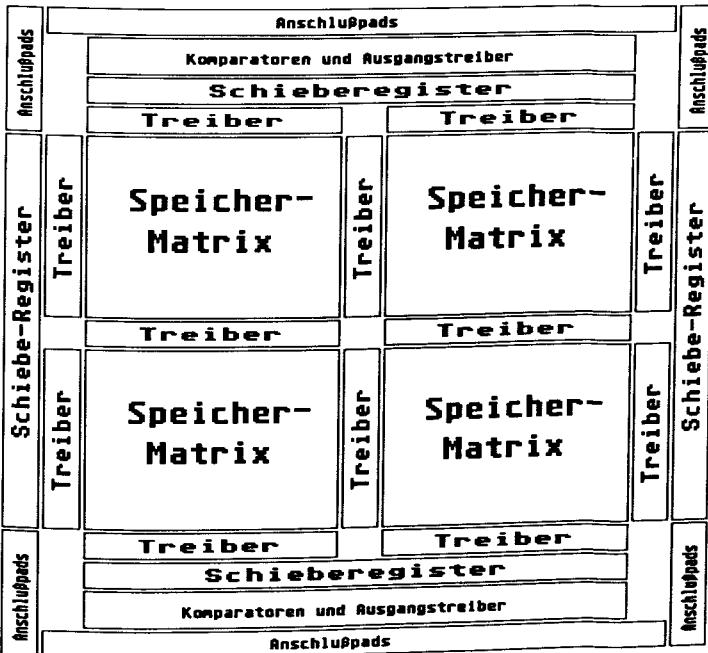

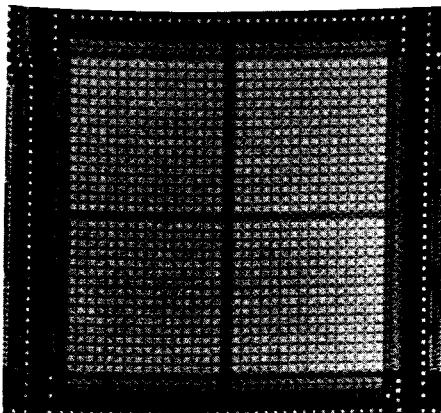

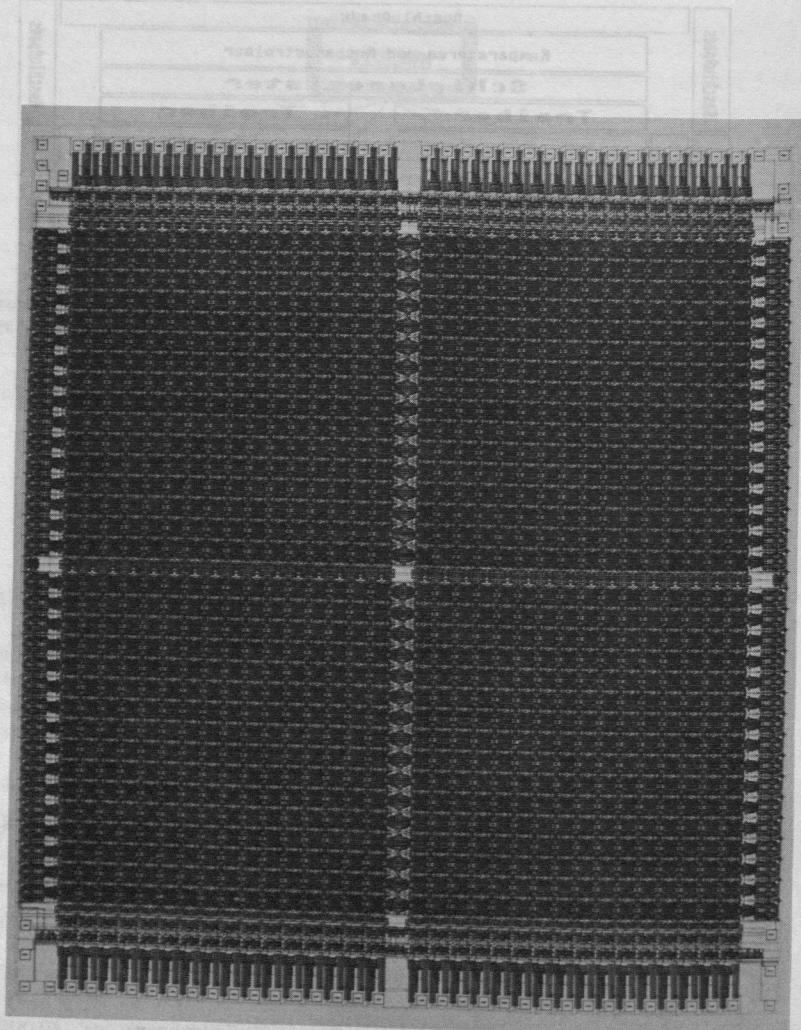

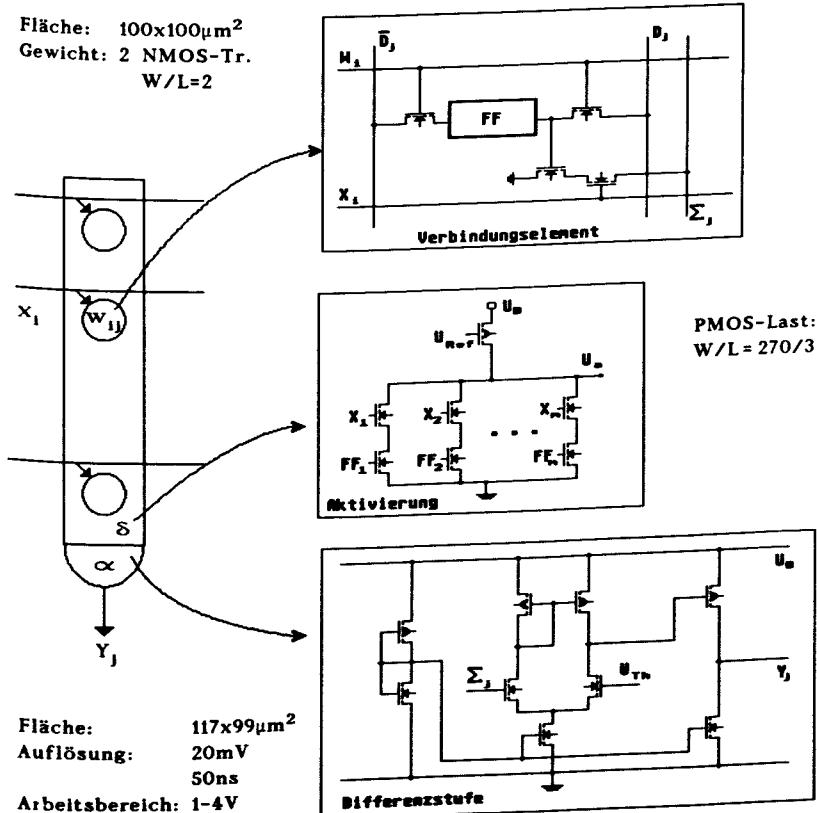

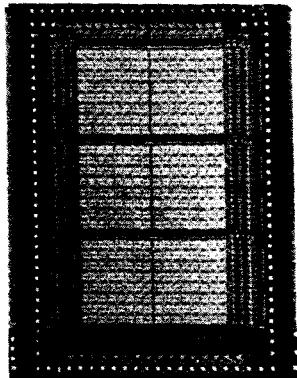

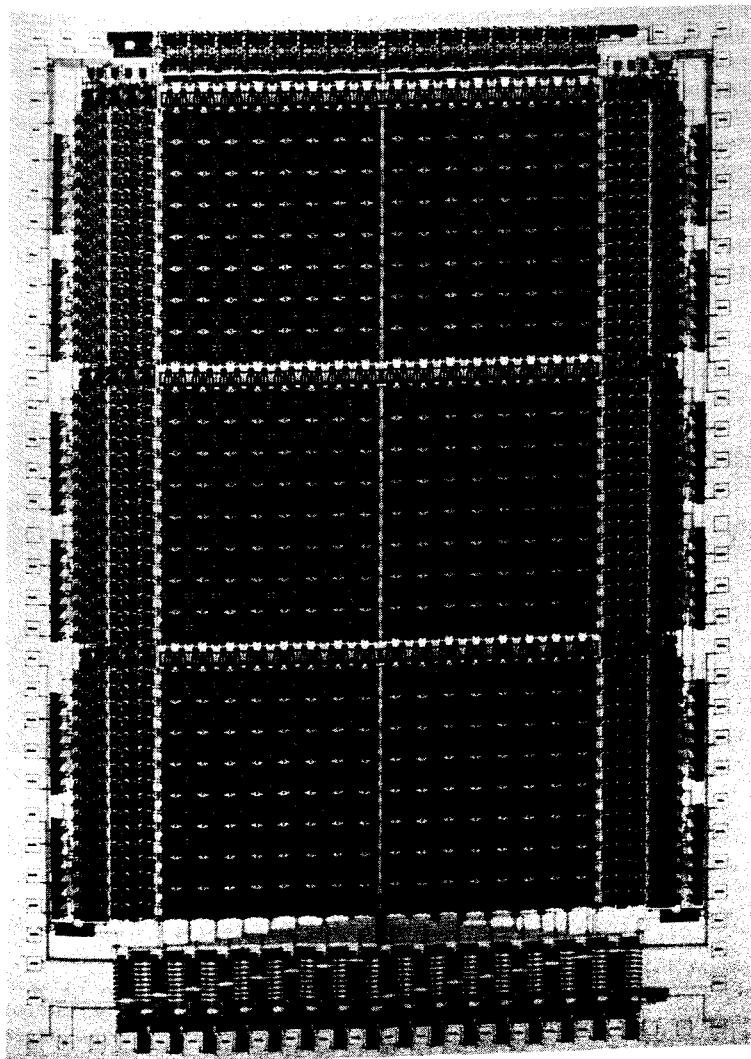

| <b>5.2.1 Ein Testbaustein für die assoziative Matrix .....</b>                    | 116 |

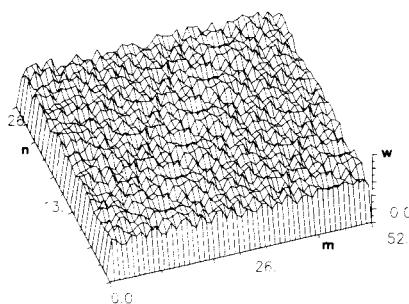

| <b>5.2.2 Realisierung einer 96x16-Slice einer assoziativen Matrix .....</b>       | 122 |

| <b>5.3 Diskussion .....</b>                                                       | 129 |

| <b>6. Zusammenfassung und Ausblick .....</b>                                      | 134 |

| <b>7. Verzeichnis der verwendeten Symbole .....</b>                               | 137 |

| <b>8. Literaturverzeichnis .....</b>                                              | 140 |

| <b>Danksagungen</b>                                                               |     |

## 1. Einleitung

Mit der Entwicklung integrierter Schaltungen zu immer höheren Integrationsgraden - derzeit stehen wir vor der Einführung der Mega-Logik und des 64-Megabit-Speicherbausteins - erhebt sich die Frage nach neuen, innovativen Schaltungs- und Systemkonzepten in der Großintegrations-technik. Die Grenzwerte der technologischen Möglichkeiten werden derzeit nur von Speicherbausteinen erreicht, bei denen aufgrund ihrer ausgesprochen regulären und modularen Architektur im wesentlichen "nur" schaltungstechnische und technologische Probleme zu lösen sind. Bei komplexen logischen Bausteinen, wie z. B. Mikrorechnern, ist das Problem der hohen Entwurfs- und Testkomplexität in den Vordergrund getreten. Gefordert sind daher Systemkonzepte, die einerseits die Möglichkeiten der Technologie weitestgehend ausschöpfen und andererseits die Entwurfs- und Testkomplexität auf ein beherrschbares Maß reduzieren.

Eine neue Herausforderung an die Großintegrationstechnik [1] stellt sich diesbezüglich durch die in jüngster Zeit viel diskutierten *neuronalen Netzwerkmodelle*. Diese Modelle basieren auf grundlegenden Kenntnissen bzw. Annahmen aus der Neurophysiologie. Mit ihnen versucht man die Eigenschaften und Leistungen biologischer Nervensysteme von Tieren und letztlich auch von Menschen zu ergründen. Die Natur dient hier einmal mehr als Wegweiser für die Erforschung neuer Prinzipien in der Informationsverarbeitung und für die Entwicklung neuer technischer Verarbeitungsstrukturen.

Neuronale Netzwerke sind sowohl von der Architektur als auch von den Eigenschaften her für die Großintegrationstechnik interessant. Die Netzwerke sind aus vielen ( $\geq 1000$ ) einfachen und gleichartigen Verarbeitungseinheiten aufgebaut, die über unidirektionale gewichtete Verbindungsleitungen hochgradig miteinander vernetzt sind. Die meisten Modelle gehen von einer regelmäßigen Verbindungsstruktur aus. Neuronale Netzwerkmodelle weisen daher die für einen integrationsgerechten Entwurf charakteristischen Eigenschaften der Regularität und Modularität auf.

Während konventionelle Rechnerarchitekturen eine Trennung in einen aktiven Prozessor und einen passiven Speicher vornehmen, verbinden neuronale Netzwerke die Speicherung und Verarbeitung von Informationen in ihrer Struktur. Die Informationsverarbeitung erfolgt kollektiv durch ein massives paralleles Zusammenwirken aller Verarbeitungseinheiten. Das wesentliche Verarbeitungsprinzip ist die Übertragung von einfachen Signalen zwischen diesen Einheiten. Ein neuronales Netzwerk wird daher nicht herkömmlich programmiert, sondern es muß eine Festlegung der Verbindungsstruktur erfolgen.

Das verteilte und kollektive Verarbeitungsprinzip lässt neuronale Netzwerke unempfindlich gegen den Ausfall einzelner Verarbeitungseinheiten oder Verbindungen werden. Derartige Ausfälle führen nicht zu einem Systemausfall, sondern werden bis zu einem gewissen Grad vollständig kompensiert. Weitere Ausfälle führen dann zu einem allmählichen Absinken der Leistungseigenschaften des Systems (graceful degradation). Die systeminhärente Fehlertoleranz macht neuronale Netzwerke attraktiv für ein integriertes Schaltungskonzept, denn bei den derzeitigen Integrationsgraden ist man auf fehlertolerante Systemkonzepte angewiesen.

Die Zielsetzung, ausgewählte Fähigkeiten biologischer Nervensysteme auf Maschinen mit neuronaler Architektur zu übertragen, ist keinesfalls neu. Sie ist seit den fünfziger Jahren durch die rasante und erfolgreiche Entwicklung der *von-Neumann-Architektur* moderner Digitalrechner in den Hintergrund getreten. Heute stoßen wir jedoch allmählich an die Grenzen dieses sequentiellen Rechnerprinzips. Trotz faszinierender Leistungen in vielen Bereichen der Informationsverarbeitung mangelt es den Systemen an Fähigkeiten, die selbst einfache Lebewesen anscheinend mühelos vollbringen. Beispiele sind die Wahrnehmung und Erkennung sowohl visueller als auch akustischer Eindrücke. Fähigkeiten, die auch mit den symbolisch arbeitenden Methoden der *Künstlichen Intelligenz* sowie den analytischen Methoden der Mustererkennung bisher nicht befriedigend gelöst werden konnten. Das hat in den letzten Jahren wieder zu einem verstärkten Interesse an neuronalen Netzwerken geführt.

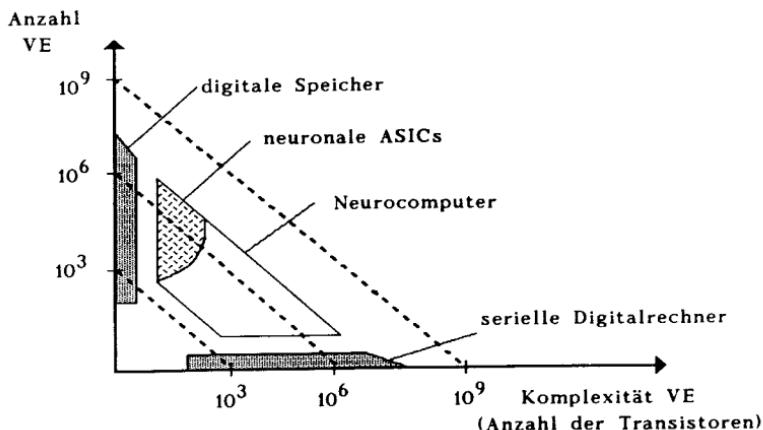

In der Literatur der letzten 5 Jahrzehnte finden sich viele verschiedene Modelle zu neuronalen Netzwerken, deren Funktionsweise und Anwendbarkeit theoretisch bzw. durch Simulationen auf seriellen Rechnern verifiziert wurden. Die Simulation von Netzwerken mit mehreren tausend Verarbeitungseinheiten, die für eine Anwendung interessant sind, führt aber zu hohen Simulationszeiten im Bereich von Stunden oder gar Tagen. Die vollständige Effizienz und Leistungsfähigkeit dieser hochgradig parallel arbeitenden Netzwerke kann somit nur durch eine geeignete Hardwarearchitektur erreicht werden. Es bieten sich hier zwei unterschiedliche Lösungswege an (Abb. 1.1): eine universell programmierbare Architektur oder eine modellspezifische Realisierung.

Die erste Gruppe, die *Neurocomputer*, sind weitestgehend Anpassungen bzw. Erweiterungen von bekannten parallelen Rechnerstrukturen an die Simulation von neuronalen Netzen. Das Spektrum erstreckt sich von Spezialprozessorkarten, die sich durch schnelle Gleitkommaverarbeitung und große Speicher auszeichnen [2], bis zu systolischen [3] und zellulären Parallelrechnerarchitekturen [4], die durch eine möglichst große Anzahl parallel arbeitender Prozessoren eine Beschleunigung erzielen. Neuronale Netzwerke werden von Neurocomputern nur *virtuell* implementiert, d.h. die Anzahl der parallel arbeitenden Prozessoren ist kleiner als die Anzahl der Verarbeitungseinheiten des neuronalen Netzes.

Die maximale Größe des Netzwerkes hängt nur von dem vorhandenen Speicherplatz ab. Das Hauptproblem beim Entwurf eines Neurocomputers ist der hohe Vernetzungsgrad neuronaler Netzwerke. Eine Aufteilung dieser feinkörnigen Netzwerke auf ein grobkörniges paralleles Mikrorechnernetzwerk führt oft zu einem Kommunikationsengpaß, der den Datendurchsatz eines parallelen Systems erheblich reduzieren kann.

Neurocomputer sind wichtige Hilfsmittel zur Modellierung und Analyse neuer Netzwerkmodelle. Sie sollten in der Lage sein, viele verschiedene theoretische Netzwerkmodelle zu unterstützen. Für diesen Freiheitsgrad wird eine Programmumgebung und eine angepaßte parallele Rechnerarchitektur benötigt. Ein leistungsfähiger Neurocomputer zeichnet sich somit durch eine sorgfältig aufeinander abgestimmte Soft- und Hardwarestruktur aus.

Abb. 1.1: Spektrum neuronaler Rechnerarchitekturen nach Recce / Treleaven [5] (VE = Verarbeitungseinheit).

Die zweite Gruppe, die *neuronalen ASICs* (application specific integrated circuits), bilden integrierte Bausteine, die auf ein bestimmtes Netzwerkmodell und eine spezielle Anwendung zugeschnitten sind. Diese können in rein digitaler, gemischt digital-analoger bzw. rein analoger Schaltungstechnik ausgeführt sein. Im Gegensatz zu Neurocomputern werden die Netzwerke nicht virtuell implementiert, sondern es werden alle Verarbeitungseinheiten des Netzwerkes physikalisch realisiert. Der zusätzliche Programmieraufwand beschränkt sich auf ein Minimum.

Neuronale ASICs sind für praktische Anwendungen von neuronalen Netzwerken wichtig. Hat man für eine bestimmte Anwendung die geeignete neuronale Struktur gefunden, dann ist der Freiheitsgrad der Modellierung nicht mehr notwendig. Es treten die Faktoren Zeit- und Platzbedarf in den Vordergrund, die im allgemeinen durch eine spezielle integrationsgerechte Implementierung optimiert werden können. Während Neurocomputer die systeminhärente Fehlertoleranz und die massive Parallelität neuronaler Netzwerke nur eingeschränkt ausnutzen können, lassen sich beide Eigenschaften direkt auf spezielle Schaltungimplementierungen übertragen.

## 1.1 Zielsetzung

Die vorliegende Arbeit leistet einen Beitrag zum Entwurf hochintegrierter neuronaler ASICs. Die Forschungs- und Entwicklungsarbeiten zu diesem Thema stehen derzeit erst am Anfang. Dementsprechend diffus stellt sich der Stand der Technik auf diesem Gebiet in der Literatur dar. Für den Vergleich verschiedenartiger Netzwerkmodelle und deren systematische Umsetzung in eine integrationsgerechte Architektur ist eine einheitliche Nomenklatur und Beschreibungsform notwendig. Aus diesem Grund besteht die erste Aufgabe darin, einen allgemeinen Beschreibungsformalismus anzugeben, mit dem sich viele der heute bekannten Modelle spezifizieren lassen. Im Mittelpunkt stehen assoziative Netzwerkmodelle, die eine Unterkategorie innerhalb der neuronalen Netzwerke bilden (Kapitel 2).

Zur Zeit gibt es noch keine allgemeingültigen Aussagen darüber, welches neuronale Netzwerkmodell für welche Anwendung eine effiziente Lösung bietet. Der Entwurfsaufwand für ein neuronales ASIC ist aber nur dann gerechtfertigt, wenn das ausgewählte Modell einen technischen Nutzen hat, d.h. einen Vorteil gegenüber alternativen Lösungen aufweist. Ein Vergleich verschiedener Lösungsansätze lässt sich anhand quantitativer Vergleichsmaße erreichen. Ein weiteres Ziel ist daher auf der Grundlage von Angaben aus der Literatur anwendbare Aussagen hinsichtlich der Speichereffektivität und Fehlertoleranz ausgewählter Modelle zu formulieren (Kapitel 3).

Ist die Entscheidung für ein bestimmtes neuronales Netzwerkmodell gefallen, stellt sich die Frage nach einer integrationsgerechten Realisierung. Die Mikroelektronik bietet verschiedene Realisierungsmöglichkeiten für neuronale ASICs, von denen die wichtigsten in dieser Arbeit aufgezeigt und die Eigenschaften ausgewählter Grundschaltungen mit Hilfe von integrierten Testschaltungen überprüft werden sollen.

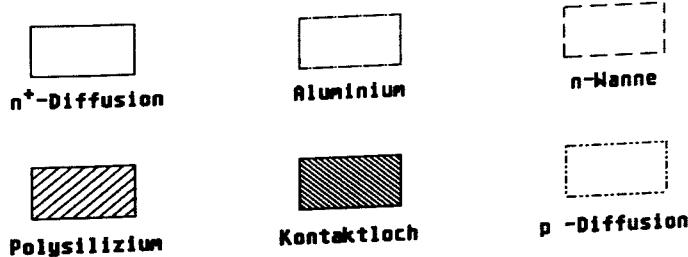

Grundlage für die Schaltungsrealisierungen ist der am Lehrstuhl Baulemente der Elektrotechnik der Universität Dortmund entwickelte 3 $\mu$ m-N-Wannen-CMOS-Prozeß mit Polysilizium-Gates und einer Aluminium Verdrahtungsebene [6]. Anhand dieser Untersuchungen soll eine Bewertung der verschiedenen Schaltungskonzepte hinsichtlich ihrer Auswirkungen auf die Speichereigenschaften assoziativer Netzwerke erfolgen, die für eine integrationsgerechte Umsetzung unerlässlich ist (Kapitel 4).

Auf der Grundlage der theoretischen und praktischen Ergebnisse gilt es abschliessend assoziative Netzwerkmodelle, deren technischer Nutzen nachgewiesen worden ist, in Form von neuen hochintegrierten Bausteinen zu realisieren. Im einzelnen sind verschiedene Realisierungsmöglichkeiten (digital/analog) und Lösungen für die wesentlichen Problemstellungen einer VLSI-Implementierung zu erarbeiten. Im Rahmen dieser Arbeit soll schließlich die integrationsgerechte Umsetzung eines assoziativen Netzwerkes in ein neues mikroelektronisches Bauelement durchgeführt und diskutiert werden (Kapitel 5).

## **2. Grundlagen assoziativer Netzwerke**

### **2.1 Neurophysiologische Motivation**

Die Erforschung biologischer Nervensysteme, besonders der Gehirne höherer Lebewesen, ist seit jeher im Interesse der Wissenschaften. Während die abstrakten, makroskopischen Fähigkeiten von Gehirnen, wie etwa das Denken, Planen oder Entscheiden, noch weitgehend unverstanden sind, hat die Erforschung der anatomischen Struktur und der Funktionsweise einzelner Grundelemente zu einer Fülle von mikroskopischen Fakten geführt. In diesem Abschnitt werden einige der grundlegenden Erkenntnisse und Annahmen aus der Neurobiologie zusammengefaßt, auf denen im wesentlichen die Modellannahmen für die neuronalen Netzwerkmodelle beruhen. Die Angaben stammen aus den Literaturquellen [7-9], in denen ausführliche Informationen zu diesem Thema zu finden sind.

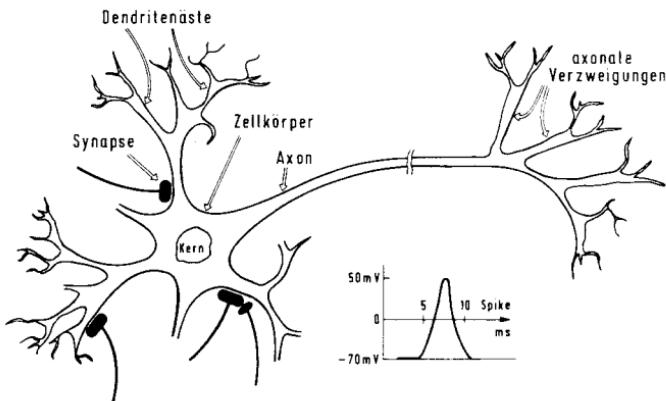

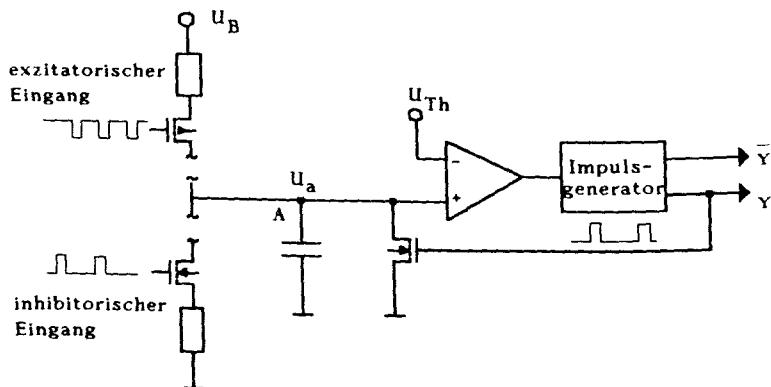

Biologische Nervensysteme bestehen aus einer sehr großen Anzahl von Nervenzellen (*Neuronen*), die intensiv untereinander vernetzt sind. Das menschliche Gehirn zum Beispiel enthält grob geschätzt 10 Milliarden Nervenzellen. Die Neuronen haben eine baumartige, weitverzweigte Erscheinungsform (Abb. 2.1.1) und sind mit bis zu  $10^4$  anderen Neuronen verbunden. Sie bestehen aus einem Zellkörper, vielen Eingabezweigen (*Dendriten*) und nur einem Ausgabezweig (*Axon*). Über die dendritischen Verzweigungen und den Zellkörper werden Eingabesignale von anderen Neuronen aufgenommen. Der Zustand eines Neurons wird durch das sogenannte *Membranpotential* bestimmt, das im Ruhezustand bei ca. - 70 mV liegt und durch die Eingangssignale verändert wird. Überschreitet das räumlich und zeitlich aufintegrierte Membranpotential einen Schwellenwert (ca. - 40 mV), so wird ein Ausgabesignal in Form eines Spannungsimpulses (*Spike*) generiert. Der Impuls hat eine Dauer von ca. 1 ms und eine Amplitude von ca. 120 mV bezüglich des Ruhepotentials. Nach der Aussendung eines Spikes folgt ein Zeitraum, in dem keine Erregung der Zelle möglich ist (*Refraktärzeit*). Die Refraktärzeit beträgt einige Millisekunden, so daß die maximale Impulsfrequenz bei ca. 100 Impulsen pro Sekunde liegt. Die Nervenzellen kommunizieren nach dem Prinzip der Impulsfrequenz-Kodierung. Die Information steckt in der Frequenz und Phase des Auftretens der Ausgangsimpulse.

Das Axon verzweigt sich sehr vielfältig und leitet die Ausgabeimpulse an viele tausend (ebenfalls ca. 10000) andere Nervenzellen weiter. An den Verzweigungsstellen wird der Impuls vervielfacht, d. h. es laufen identische Impulse weiter. Die Verbindungsstellen zwischen den Enden der Axonzweige und den nachfolgenden Nervenzellen heißen *Synapsen*. Synapsen werden nach ihrer Lage und Wirkung typisiert. Je nach Lage

spricht man von axo-dendritischen, axo-somatischen, axo-axonischen und dendro-dendritischen Synapsen. Synapsen der beiden erst genannten Gattungen treten am häufigsten auf. Die Wirkung der Synapsen kann entweder erregend (exzitatorisch), d.h. sie bewirken die Erhöhung des Membranpotentials oder hemmend (inhibitorisch) sein, also eine Erniedrigung des Membranpotentials bewirken. Es wird davon ausgegangen, daß Synapsen ihre Wirkung nicht umkehren können. Eine exzitatorische Synapse kann also nicht zu einer inhibitorischen werden und umgekehrt.

Abb. 2.1.1: Vereinfachtes Schema eines Neurons.

Es konnte ferner nachgewiesen werden, daß für bestimmte Synapsen die Stärke, mit der eine Nervenzelle auf eine andere wirkt, veränderbar ist. Demnach werden diejenigen Neuronen stärker miteinander verknüpft, die häufig gemeinsam erregt sind, d. h. etwa zur gleichen Zeit Spikes generieren. Diese Veränderung der Übertragungseigenschaft von Synapsen bereits 1949 von D. Hebb [10] als Hypothese formuliert worden. Sie wird heute als eine Grundlage für das Lernen betrachtet. Die Synapsen werden somit als die elementaren Einheiten des biologischen Gedächtnisses interpretiert, in denen unser Wissen "gespeichert" wird.

Die Signalübertragungseigenschaften von Neuronen und Synapsen sind im Detail recht kompliziert und noch nicht vollständig erforscht. Noch relativ unklar ist das Verrechnungsprinzip der ankommenden Signale. Untersuchungen deuten darauf hin [11], daß der Einfluß der Synapsen auf die Aktivität eines Neurons von der Lokalität der Synapsen abhängen kann. Somit sind eine Reihe von lokalen Operationen möglich, die die Geometrie

des Dendritenbaumes und die relative Lage der Synapsen zueinander ausnutzen. Auch der Einfluß der vielfältigen chemischen Wechselwirkungen auf die Informationsverarbeitung im Nervensystem ist noch nicht ausreichend verstanden. Es gilt aber als sicher, daß Neuronen zumindest die oben erwähnte Schwellenoperation ausführen. Ferner geht man davon aus, daß die Neuronen asynchron arbeiten, denn es gibt bisher keinen Hinweis auf einen zentralen Systemtakt.

Die Neuronen werden als die strukturellen und funktionellen Grundbausteine biologischer Nervensysteme angesehen. Aufgrund ihrer Erscheinungsformen unterscheidet man verschiedene Neuronentypen, wie z.B. Purkinjezellen, mit einem dichten weitverzweigten Dendritenbaum oder Pyramidenzellen, deren Zellkörper die Form einer Pyramide haben. Anatomische Untersuchungen zeigen, daß verschiedene Gehirnbereiche mit unterschiedlichen Neuronentypen aufgebaut sind. In der Großhirnrinde, die der größte ausgebildete Teil des menschlichen Gehirns ist und für die "höheren" geistigen Fähigkeiten verantwortlich gemacht wird, findet man z.B. vorwiegend zwei Neuronentypen: die Pyramidenzellen (ca. 70%) und die Sternzellen (ca. 30%). Die Sternzellen verzweigen sich überwiegend in ihrer unmittelbaren Umgebung und wirken in der Regel inhibitorisch. Die Pyramidenzellen haben weitreichende Axone mit meist exzitatorisch wirkenden Synapsen. Die verschiedenen Neuronentypen scheinen für bestimmte Aufgaben spezialisiert zu sein. Funktional unterschiedliche Gehirnbereiche sind daher auch architektonisch unterschiedlich.

Die von der Neurobiologie erforschten mikroskopischen Fakten, insbesondere die anatomischen Fakten, sind selbstverständlich viel detaillierter als es hier zum Ausdruck kommen kann. Das Verständnis der Informationsverarbeitung in Nervensystemen ist aber dennoch rudimentär. Es gilt hier die große Kluft zwischen den mikroskopischen Detailkenntnissen und den makroskopischen Fähigkeiten, wie zum Beispiel der Wahrnehmung, zu überbrücken. Dies motiviert Modellbildungen und -analysen, um Hinweise zu bekommen, inwieweit Konfigurationen einfacher Modellneuronen ausgewählte Eigenschaften hervorbringen können und einen naturgetreuen Nachbau notwendig machen.

Eine wichtige Frage zielt auf die interne Repräsentationsart der im Gehirn gespeicherten Informationen. Eine heute weitverbreitete Annahme ist, daß Daten im Gehirn nicht lokal, sondern verteilt gespeichert werden. In der Gehirntheorie spricht man von Zellverbänden (cell assemblies [10,12]). Konzepte werden im Gehirn nicht durch einzelne Neuronen, sondern durch einen Verband von miteinander verknüpften Neuronen repräsentiert. Die interne Informationsdarstellung ist somit ein Aktivitätsmuster gleichzeitig erregter Neuronen, deren synaptischen Verbindungen die Korrelationen zwischen gleichzeitig auftretenden Ereignissen speichern. Die Entstehung und Stabilität dieser Verbände sind so zu erklären, daß gleichzeitig akti-

vierte Neuronen aufgrund der erwähnten synaptischen Plastizität exzitatorische Verbindungen bilden. Ein Verband besteht daher aus sich gegenseitig erregenden Neuronen. Einzelne Neurone eines Verbandes haben immer das Bestreben, bei Aktivierung auch die mit ihnen verbundenen Neuronen zu erregen. Mit Zellverbänden lässt sich anschaulich die Fähigkeit von Gehirnen erklären, unvollständige oder verrauschte Sinnesindrücke, wie z.B. Bilder oder Tonfolgen, richtig zu erkennen. Der Sinnesindruck aktiviert einen genügend großen Teil des Zellverbandes, der diesen Sinnesindruck im Gehirn repräsentiert. Über die exzitatorischen Verbindungen erregen die aktivierte Neuronen die noch fehlenden Neuronen des Verbandes und vervollständigen somit den Sinnesindruck. Diese Annahmen haben insbesondere die Entwicklung assoziativer Speichermodelle motiviert, die sich einer verteilten Speicherung bedienen und im Mittelpunkt dieser Arbeit stehen.

Seit den vierziger Jahren gibt es viele Ansätze anhand von theoretischen Modellen die Informationsverarbeitung und -repräsentation in biologischen Nervensystemen zu ergründen. Erklärtes Ziel dieser Modelle ist es, ausgewählte makroskopische Fähigkeiten des zentralen Nervensystems vereinfacht nachzubilden. In den fünfziger und sechziger Jahren hatte dieses Bestreben im Rahmen der Kybernetik seinen ersten Höhepunkt. Beispielhaft genannte Vertreter dieser Zeit sind Rosenblatt (Perceptron, [13]), Uttely (Conditioned Probability Computer, [14]), Steinbuch (Lernmatrix, [15]) und Widrow (Adaline, [16]), deren Neuronenmodelle auf den grundlegenden Arbeiten von McCulloch und Pitts [17] sowie Hebb [10] basieren.

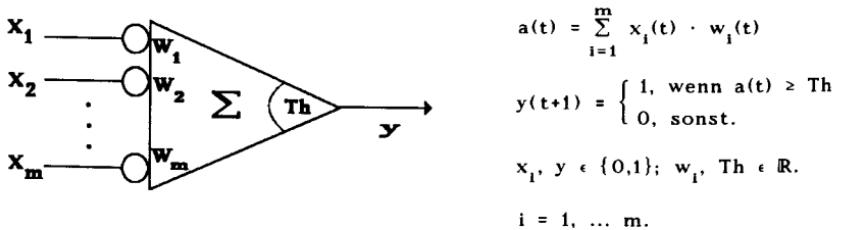

Das McCulloch/Pitts-Neuron (Schwellen neuron) ist ein sehr einfaches Modell eines biologischen Neurons (Abb. 2.1.2). Es empfängt  $m$  binäre Eingabewerte  $x_i$  und hat einen binären Ausgang  $y$ . Jeder Eingabe ist ein Gewichtswert  $w_i$  eindeutig zugeordnet. Wählt man die Refraktärzeit eines Neurons als einen diskreten Zeitschritt  $t \in \mathbb{N}$ , so erzeugt das Schwellen neuron einen Ausgabeimpuls zur Zeit  $t+1$ , wenn die Aktivierung des Schwellen neurons zur Zeit  $t$  den Schwellenwert  $\theta$  überschreitet. Die Aktivierung des Modellneurons ergibt sich aus der gewichteten Summe der Eingabewerte zur Zeit  $t$ . Die Gewichtswerte  $w_i$  modellieren die Übertragungsstärke der Synapsen. Sie können positiv, negativ oder null sein entsprechend erregenden, hemmenden oder nicht vorhandenen Synapsen.

Das Schwellen neuron nimmt nur die beiden binären Ausgangswerte 0 und 1 an, so daß man es als ein logisches Schaltelement (Schwellenwertgatter) betrachten kann. Im Sinne der Schaltwerktheorie ist ein Schwellenwertgatter ein vollständiges System logischer Operatoren, d.h. mit einem genügend großen und richtig zusammengeschalteten Netzwerk dieser Gatter kann man alle Booleschen Funktionen realisieren. Mit anderen Worten, ein solches Netz hat die Berechnungsmächtigkeit von Turingmaschinen [18].

Abb 2.1.2: Schema für ein einfaches Schwellenneuron.

Für die Programmierung einzelner Schwellenneurone hat man Lernregeln entwickelt, mit denen sich die Gewichte und der Schwellenwert iterativ einstellen lassen. Beispielhaft sei hier die Perzeptron-Lernregel aufgeführt [13]:

$$w_i(t+1) = w_i(t) + c \cdot (y_L - y(t)) \cdot x_i(t) \quad (2.1.1)$$

Entsprechend dieser Regel wird ein Gewicht verändert, wenn die erzeugte Ausgabe des Modellneurons  $y(t)$  von der geforderten Ausgabe  $y_L \in \{0,1\}$  (Lehrersignal) abweicht. Die Konstante  $c \in [0,1]$  bestimmt den Betrag der Gewichtskorrektur. Es ist auf verschiedene Weise gezeigt worden [13], daß das gewünschte Ein-/Ausgabeverhalten in einer endlichen Anzahl von Lernschritten erreicht wird, sofern dieses Verhalten von diesem Modellneuron überhaupt erzeugt werden kann.

Mit einem Schwellenneuron können nur linear trennbare Mustermengen erkannt werden. Für komplexere Probleme benötigt man eine Verschaltung von Schwellenneuronen zu einem komplexeren Netzwerk [19]. Eine Verallgemeinerung der Perzeptron-Lernregel auf komplexere, mehrschichtige Netzwerke, bei denen man nicht mehr für jedes Element das entsprechende Lehrersignal bereitstellen kann, ist in den sechziger Jahren nicht gelungen. Damit konnten sich diese Modelle gegenüber dem symbolverarbeitenden Ansatz der Künstlichen Intelligenz nicht durchsetzen. Die rasche Entwicklung der elektronischen Datenverarbeitung ermöglichte zunehmend komplexere Programmentwicklungen. Diese Entwicklung nährte die Hoffnungen der Wissenschaftler, die höheren geistigen Fähigkeiten in Form von "intelligenten" Programmen auf Rechenautomaten zu implementieren. Gegen Ende der sechziger Jahre sind die neuronalen Netzwerkmodelle aus dem Rampenlicht der Forschung verschwunden.

Die Forschungsarbeiten auf diesem Gebiet sind in den siebziger Jahren weitergeführt worden, wenn auch das öffentliche Interesse nicht sehr groß war. Das rudimentäre Wissen über Nervensysteme ist erweitert und

es sind neue modelltheoretische Erkenntnisse erlangt worden. Beispielsweise genannte europäische Vertreter dieser Zeit sind Caianiello, Willshaw, von der Malsburg, Kohonen und Braatenberg. Eine Zusammenstellung wichtiger Beiträge dieser Zeit findet sich z.B. in [20,21].

Anfang der achtziger Jahre bekam das ohnehin schon ausgesprochen interdisziplinäre Gebiet durch eine physikalische Betrachtungsweise einen neuen Akzent. Die Physik befaßte sich schon seit langem mit dem Verhalten von Vielteilchensystemen mit lokal wechselwirkenden Einzelementen. Die Eigenschaften von Materialien entstehen z.B. durch das Zusammenwirken von  $10^{23}$  Atomen oder Molekülen. Eine Reihe von Physikern versucht daher, die physikalischen Modelle von Vielteilchensystemen, wie z.B. Spinglas-Modelle [22], auf neuronale Netze zu übertragen. Zwei der bekanntesten Modelle sind das Hopfield-Netz [23] und die Boltzmann-Maschine [24].

Heute erleben wir eine Renaissance neuronaler Netze. Viele Faktoren haben dazu beigetragen, z.B. die sich abzeichnende Ernüchterung in der Künstlichen Intelligenz bezüglich bestimmter praktischer Anwendungen (z.B. sensorische Informationsverarbeitung), ein wachsendes Interesse an parallelen Rechnerstrukturen und nicht zuletzt die zunehmende Integrationsdichte in der Mikroelektronik. Insbesondere sind auch theoretische Grundlagen für mehrschichtige und selbstorganisierende Netzwerke [25-27] entwickelt worden.

Das enorme Interesse an neuronalen Netzwerken hat sich in jüngster Zeit auch auf die Großintegrationstechnik übertragen. Im Mittelpunkt steht die Frage, in welcher Form und inwieweit sich neuronale Netzwerkmodelle als mikroelektronische Bauelemente verwirklichen lassen [28]. Das Ziel ist dabei weniger ein naturgetreuer Nachbau biologischer Nervensysteme, sondern eher das Finden von alternativen Architekturen für die Informationsverarbeitung. Anhaltspunkte ergeben sich aus den wesentlichen strukturellen und funktionellen Unterschieden von biologischen Nervensystemen und heutigen Rechnersystemen, die qualitativ in Tabelle 2.1.1 zusammengefaßt sind.

Biologische Nervensysteme erreichen ihre Leistungsfähigkeit durch ein kollektives Zusammenwirken einer sehr großen Anzahl von gleichartigen und vermutlich einfachen Verarbeitungskomponenten. Durch die massiv parallele Arbeitsweise wird auch mit langsamen Verarbeitungseinheiten eine hohe Verarbeitungsgeschwindigkeit erreicht. Die Verarbeitungsgeschwindigkeit der Nervenzellen ist dabei um mehrere Größenordnungen kleiner als bei modernen Mikrorechnern. Die typische Zeitskala für Nervenzellen liegt im Millisekundenbereich, typische Speicherzugriffszeiten liegen im Nanosekundenbereich (50 - 100ns) und Prozessortaktraten bei einigen 10 MHz.

| Digitalrechner                                 | Eigenschaften                                                                                                      | Nervensystem                                  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| gering<br>gering<br>lokal<br>mäßig<br>synchron | <u>des Gesamtsystems:</u><br>Parallelität<br>Vernetzungsgrad<br>Speicherprinzip<br>Fehlertoleranz<br>Kommunikation | hoch<br>hoch<br>verteilt<br>hoch<br>asynchron |

| hoch<br>hoch<br>hoch                           | <u>der Komponenten:</u><br>Rechengeschwindigkeit<br>Rechengenauigkeit<br>Zuverlässigkeit                           | niedrig<br>niedrig<br>mäßig                   |

*Tabelle 2.1.1: Qualitative Gegenüberstellung der Eigenschaften eines biologischen Nervensystems und eines heutigen Digitalrechners.*

Der hohe Grad an Parallelität und Kollektivität wird durch eine einfache Kommunikation über unidirektionale Verbindungsleitungen erreicht. Gleichzeitig ergibt sich ein hohes Maß an Fehlertoleranz. Die Unzuverlässigkeit und Ungenauigkeit einzelner Verbindungen oder Verarbeitungseinheiten kann durch das verteilte und kollektive Arbeitsprinzip ausgeglichen werden.

Einen bremsenden Einfluß im Fortschritt der Informationstechnologie hat zunehmend die Entwicklung komplexer Programme übernommen. Da Nervensysteme z. B. akustische und visuelle Wahrnehmungen in Sekundenbruchteilen erledigen, können im Gehirn nur wenige hundert sequentielle Schritte ausgeführt werden. Die kognitiven Fähigkeiten können daher nur durch massive Parallelität ohne komplexe algorithmische Unterstützung erreicht werden.

Diese Eigenschaften biologischer Nervensysteme erklären das erneute wissenschaftliche und kommerzielle Interesse an dieser Thematik.

## **2.2 Eine allgemeine Modellbeschreibung**

Das Forschungsinteresse an neuronalen Netzwerken hat sich in den letzten Jahren rasch auf viele Wissenschaftsbereiche ausgeweitet. Die Begriffsbildung ist daher noch diffus und uneinheitlich. Für den Vergleich der Eigenschaften und Verwendungsmöglichkeiten unterschiedlicher Modelle ist aber eine einheitliche Beschreibungsform gefordert. Die Form der Beschreibung hängt im wesentlichen von der Zielsetzung ab. Für eine mathematische Analyse muß das Neuronenverhalten und die Netzwerkstruktur mit exakten mathematischen Strukturen, im allgemeinen Differentialgleichungen, beschrieben werden. Weitere geeignete mathematische Strukturen finden sich in der Automatentheorie [29], Graphentheorie [30] oder in der Physik [31]. Anhand von Axiomen und Theoremen werden dann die ausgewählten Modelleigenschaften bewiesen und neue Eigenschaften vorhergesagt.

Eine geschlossene mathematische Analyse ist nur für einfache Modelle möglich, die sich anhand weniger Gleichungen und Parameter beschreiben lassen. Im Grunde benötigt man für jedes Neuron im Netzwerk eine Gleichung zur Beschreibung der Übertragungseigenschaften, für jede Synapse eine Gleichung für die Änderung der Kopplungsstärke sowie Parameter, die z.B. die Anfangsverknüpfung im Netzwerk festlegen. Das Verhalten der meisten Modelle wird daher mit Rechnersimulationen untersucht. Eine Modellbeschreibung sollte in dieser Hinsicht viele Modellvarianten überdecken, so daß nicht für jede Variante Änderungen am Simulationsprogramm selbst vorgenommen werden müssen. Andererseits darf die erreichte Flexibilität nicht zu Lasten der Genauigkeit, der Simulationszeit oder des Speicherplatzbedarfs gehen. Hier gilt es einen geeigneten Kompromiß zu finden.

Für den Systementwickler integrierter Schaltungen kommen nur Modelle in Frage, deren Funktionalität und Anwendbarkeit bereits theoretisch bzw. mit Hilfe von Simulationen nachgewiesen worden sind. Im Rahmen dieser Arbeit wird daher eine Beschreibungsform gewählt, die den strukturellen Aufbau des Netzwerkes mit seiner Einbettung in eine gegebene Umwelt deutlicher zum Ausdruck bringt. Sie erhebt nicht den Anspruch auf Universalität, sondern beschränkt sich auf eine Untergruppe von neuronalen Netzwerken, die im folgenden mit "assoziative Netzwerke" bezeichnet wird.

Die Beschreibungsform orientiert sich bei der Verarbeitungseinheit an der Definition eines endlichen Automatens und beim Netzwerk an der Definition eines abstrakten Graphens. Sie eignet sich dadurch ebenfalls für die Implementierung eines modellunabhängigen Simulators für assoziative Netzwerke [32]. Die gewählte Beschreibungsform bildet somit eine geeignete Schnittstelle zwischen struktureller Beschreibung, Simulation und Theorie assoziativer Netzwerke.

### 2.2.1 Definition einer Verarbeitungseinheit

Grundlegendes Systemelement eines künstlichen neuronalen Netzwerkes ist ein Modellneuron, das im weiteren mit **Verarbeitungseinheit** bezeichnet wird:

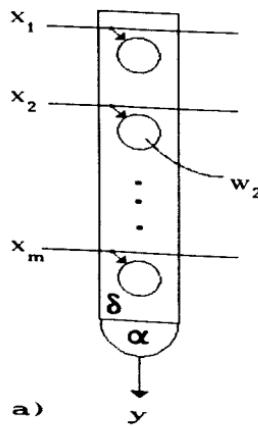

**Definition 1:** Eine **Verarbeitungseinheit** ist ein Tupel  $V = (m, X, A, Y, W, \delta, \alpha, \lambda)$  mit:

- $m$  : Anzahl der Eingabeleitungen;

- $X$  : Menge der Eingabewerte;

- $A$  : Menge der Aktivierungswerte;

- $Y$  : Menge der Ausgabewerte;

- $W$  : Menge der Gewichtswerte;

- $\delta$  : Aktivierungsfunktion;

$\delta : X^m \times W^m \times A \longrightarrow A$

- $\alpha$  : Ausgabefunktion;

$\alpha : A \longrightarrow Y$

- $\lambda$  : Adaptationsfunktion (Lernregel);

$\lambda : W^m \times X^m \times A \times Y \longrightarrow W^m$

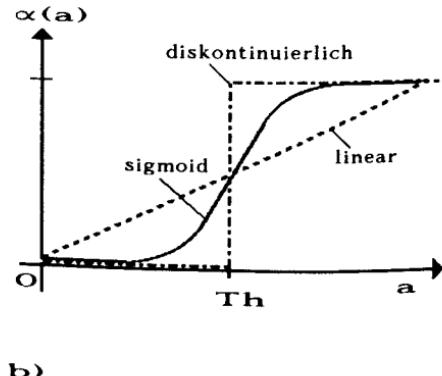

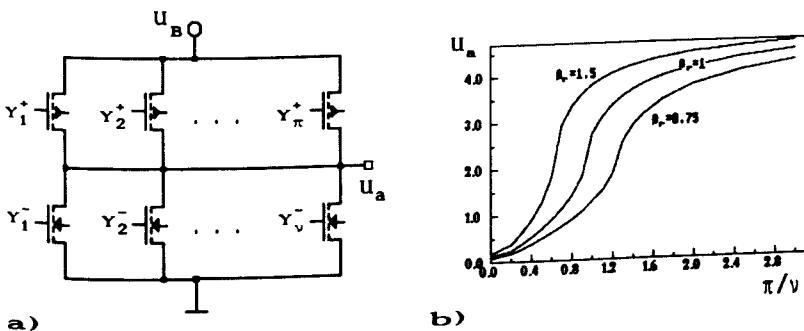

Abb. 2.2.1: Schematischer Aufbau einer Verarbeitungseinheit (a) und Beispiele gebräuchlicher Ausgabefunktionen (b).

Die Struktur einer Verarbeitungseinheit (Abb. 2.2.1) wird durch die  $m$  Eingangsleitungen, auf denen Eingabewerte  $x_i \in X$  übertragen werden können, einer Ausgabeleitung, auf der Ausgabewerte  $y \in Y$  übertragen werden können sowie den  $m$  Verbindungsgewichten  $w_i$ , die eineindeutig den Eingangsleitungen zugeordnet sind, bestimmt. Die Eingabe- und die Ausgabemenge werden häufig gleich gewählt ( $X=Y$ ) und die Eingabewerte sowie die Gewichtswerte zu einem  $m$ -dimensionalen Eingabevektor  $\underline{x}$  bzw. Gewichtsvektor  $\underline{w}$  zusammengefaßt.

Zur Vereinfachung wird im folgenden für eine Eingangsleitung die gleiche Bezeichnung  $x_i$  gewählt wie für die Eingabewerte auf dieser Leitung. Entsprechendes gilt für die Ausgangsleitung  $y$  und die Gewichte  $w_i$ . Formal gesehen ist das nicht ganz korrekt, aber für die hier angestellten Betrachtungen führt diese Vereinfachung nicht zu Konflikten.

Der Zustand einer Verarbeitungseinheit wird durch den Aktivierungswert  $a \in A$ , der neurophysiologisch mit dem Membranpotential vergleichbar ist, und durch den Gewichtsvektor  $\underline{w}$  ausgedrückt. Entsprechend der Wahl der Mengen  $X, Y, W, A$  (diskret-kontinuierlich, beschränkt-unbeschränkt) ergeben sich unterschiedliche Modelle für formale Neuronen, von denen viele bereits in der Literatur untersucht worden sind [25-27].

Die Dynamik einer Verarbeitungseinheit wird durch die drei Funktionen  $\delta, \alpha, \lambda$  bestimmt. Die Verarbeitungseinheiten können bezüglich einer kontinuierlichen oder diskreten Zeitskala arbeiten, entsprechend erhält man eine Beschreibung durch Differentialgleichungen oder Iterationsgleichungen. Der zeitdiskrete Fall ist immer dann zwingend, wenn man die Verarbeitungseinheiten auf einem Rechner simulieren will. Die meisten Modelle beziehen sich daher auf eine diskrete Zeitskala, so daß  $t \in \mathbb{N}$  gilt. Diese Betrachtungsweise wird für die weiteren Ausführungen übernommen.

Eine Verarbeitungseinheit arbeitet zu den diskreten Zeittakten  $t=0, 1, 2, \dots$ , an denen sie in Abhängigkeit von der aktuellen Eingabe  $\underline{x}(t)$  und dem aktuellen Zustand  $(\underline{w}(t), \underline{a}(t))$  eine neue Ausgabe  $y(t)$  erzeugt und einen Zustandswechsel durchführt. Sowohl die Ausgabe- als auch die Zustandsüberführungsfunktionen  $(\alpha, \lambda)$  sind zeitinvariant.

Für genaue Modellierungen der biologischen Vorbilder muß man eine entsprechend fein auflösende Zeitskala verwenden und relativ aufwendig die Impulsübertragungen modellieren (vgl. 2.1). Da die Analyse und Simulation dieser Systeme sehr viel Zeit in Anspruch nimmt, werden oft zeitlich gemittelte Größen, beispielsweise die der Impulsrate, oder nur binäre Zustände zur Approximation der Neuronenausgabe verwendet.

Die Aktivierungsfunktion bestimmt einen neuen Aktivierungswert in Abhängigkeit vom aktuellen Aktivierungszustand, den aktuellen Gewichten

$\underline{x}(t)$  und der aktuellen Eingabe  $\underline{x}(t)$ . Die meisten derzeit bekannten Aktivierungsfunktionen basieren auf der gewichteten Summe der Eingabewerte:

$$S(t) = \sum_{i=1}^m x_i(t) \cdot w_i(t) \quad (2.2.1)$$

$$a(t) = \delta(S(t)) \quad (2.2.2)$$

Die Aktivierung ergibt sich entweder direkt aus dieser Summe oder es wird noch eine nichtlineare Funktion auf diese Summe angewendet. Komplexere Aktivierungsfunktionen enthalten eine zeitliche Integration und komplexere mathematische Operationen als die Summenbildung [26].

Die Ausgabefunktion bestimmt den Ausgabewert in Abhängigkeit von der momentanen Aktivierung. Neben einfachen linearen Ausgabefunktionen findet man häufig sigmoide Ausgabefunktionen oder Schwellenwertfunktionen (Abb. 2.1.2, Abb. 2.2.1b).

Die Adaptationsfunktion verändert die Gewichtswerte und damit den Zustand der Verarbeitungseinheit. Entsprechend dem funktionalen Zusammenhang zwischen  $\underline{w}$ ,  $\underline{x}$ ,  $a$ ,  $y$  und der Änderung  $\Delta\underline{w}$ , lassen sich Adaptionsfunktionen in verschiedene Klassen einteilen, wie z. B. prinzipiell in überwachte oder nicht überwachte Lernregeln. Überwachte Lernregeln erfordern entweder eine "Lehrereingabe", die die geforderte Ausgabe einer Verarbeitungseinheit direkt vorgibt oder eine Bewertung, die die Richtigkeit der Ausgabe einer Verarbeitungseinheit beurteilt. Eine überwachte Lernregel mit Lehrereingabe ist z.B. die in Abschnitt 2.1 erwähnte Perzeptron-Lernregel.

Die interessanteren Lernregeln sind die nicht überwachten oder selbstorganisierenden Regeln. Sie befähigen ein Netzwerk von Modellneuronen zur selbstständigen Anpassung an eine gegebene Aufgabenstellung, indem das System eine zeitlang seine Umwelt "beobachten" muß. "Beobachten" meint hier die Auswertung von Eingaben aus der Umwelt. Ein Beispiel für ein Netzwerkmodell mit nicht überwachter Lernregel sind die selbstorganisierenden Karten von Kohonen [25].

Eine besondere Rolle spielen im Hinblick auf eine schaltungstechnische Realisierung die *lokalen Regeln*, bei denen es nur auf Größen ankommt, die lokal an jeder Verarbeitungseinheit zur Verfügung stehen. Eine einfache, aber sehr wirkungsvolle lokale Lernregel ist die *Hebb-Regel*, die von Hebb (vgl. 2.1) als grundlegend für das Lernen im Gehirn vorgeschlagen wurde:

$$\Delta w_i \sim x_i \cdot y \quad (2.2.3)$$

Entsprechend dieser Regel werden nur dann Gewichtswerte erhöht, wenn die Verarbeitungseinheit eine Ausgabe erzeugt (d.h. aktiv ist) und gleichzeitig die Eingabe  $x_i$  entsprechend hoch ist. Viele der bekannten Lernregeln basieren auf diesem Prinzip.

## 2.2.2 Definition eines assoziativen Netzwerkes

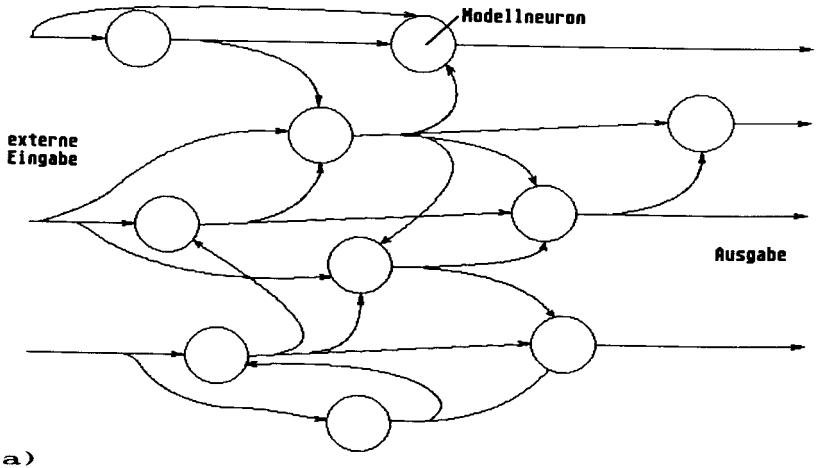

Ein assoziatives Netzwerk (Abb. 2.2.2) besteht aus einer möglichst großen Anzahl ( $\geq 1000$ ) von Verarbeitungseinheiten. Alle Verarbeitungseinheiten im Netz arbeiten parallel und kommunizieren untereinander sowie mit der Außenwelt über direkte Verbindungsleitungen. Die Verbindungsleitungen werden in externe, von der Außenwelt und interne, von den anderen Einheiten im Netz kommend unterschieden.

**Definition 2:** Ein **assoziatives Netzwerk** ist ein Tupel  $AN=(\mathfrak{B}, \mathfrak{E}, v, e, \mathfrak{z})$ , mit  $\mathfrak{B}$  einer endlichen Menge von Verarbeitungseinheiten,  $\mathfrak{E}$  einer endlichen Menge von externen Eingabeketten, und drei Abbildungen  $v : \mathfrak{B} \times \mathfrak{B} \rightarrow \{0,1\}$ ,  $e : \mathfrak{E} \times \mathfrak{B} \rightarrow \{0,1\}$  und  $\mathfrak{z} : \mathfrak{B} \rightarrow \{0,1\}$ . Für alle  $V_i, V_j \in \mathfrak{B}$  bestimmt  $v(V_i, V_j)$ , ob eine Verbindung von  $V_i$  nach  $V_j$  besteht. Für alle  $e_j \in \mathfrak{E}$  bestimmt die Abbildung  $e(e_j, V_i)$ , ob die Verarbeitungseinheit  $V_i$  mit der externen Eingabekette  $e_j$  verbunden ist. Die Abbildung  $\mathfrak{z}(V_i)$  bestimmt, ob die Ausgabe von  $V_i$  eine externe Ausgabe an die Umwelt ist.

Ein assoziatives Netzwerk besteht aus elementaren Verarbeitungseinheiten und einer Netzwerktopologie. Das zeitliche Verhalten des Netzwerkes wird von der Arbeitsweise der Verarbeitungseinheiten bestimmt. Im zeitdiskreten Fall unterscheidet man synchrone, d.h. ein globaler Systemtakt bestimmt die Zeitpunkte, an denen die Einheiten ihre Ausgabe neu berechnen und asynchrone Netzwerke, bei denen die Einheiten an zufälligen Zeitpunkten eine Ausgabe neu bestimmen. Die Ausgabe  $\mathfrak{z}$  des gesamten Netzwerkes ergibt sich aus einer von der Abbildung  $\mathfrak{z}$  festgelegten Teilmenge der Ausgabewerte  $y_j$ . In der Literatur sind häufig folgende Bezeichnungen zu finden [27]:

**Definition 3:** Eine Verarbeitungseinheit  $V \in \mathfrak{B}$  eines assoziativen Netzwerkes  $AN=(\mathfrak{B}, \mathfrak{E}, v, e, \mathfrak{z})$  mit  $|\mathfrak{E}|=m$  externen Eingabeketten heißt:

- 1) **Eingabeeinheit** :  $\exists j \in \{1, \dots, m\}$  mit  $e(e_j, V)=1$ ;

- 2) **Versteckte Einheit** :  $\forall j \in \{1, \dots, m\}$  gilt  $e(e_j, V)=0$  und  $\mathfrak{z}(V)=0$ ;

- 3) **Ausgabeeinheit** :  $\mathfrak{z}(V)=1$ ;

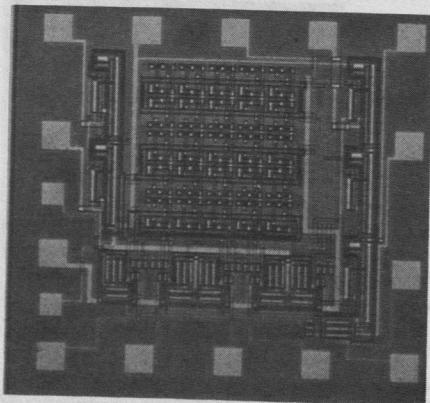

a)

b)

*Abb. 2.2.2: a) Assoziatives Netzwerk;

b) Reguläre Anordnung des Netzwerkes aus a).*

Die Netzwerktopologie wird durch die von den Abbildungen  $\epsilon$ ,  $\nu$  festgelegten Matrizen charakterisiert und kann, wie in Abb. 2.2.2a, beliebige Verbindungsstrukturen (z. B. Mehrebenen- oder Rückkopplungsstrukturen) annehmen. Neben der Wahl der geeigneten Verbindungsstruktur ist die Einstellung der Verbindungsgewichte  $w_{ij}$  festzulegen, die entweder explizit vorgegeben werden oder von einer Adaptationsregel bestimmt werden können. Diese Änderung ist im allgemeinen ein viel langsamerer Prozeß als die Aktivitätsänderung, das führt häufig zu einer Trennung in eine *Lernphase* und eine *Ausführungsphase*. Dem Netzwerk werden zunächst in der Lernphase die zu lernenden Muster eingegeben und die Verbindungsstruktur mittels der Adaptationsregel angepaßt. Eine Änderung der Kopplungsstärken bedeutet eine Änderung des Netzwerkverhaltens. Die Lernphase ist beendet, wenn das Netzwerk das geforderte Verhalten erlernt hat, bzw. sein Verhalten nicht mehr ändert. In der Ausführungsphase werden keine Änderungen der Gewichte mehr durchgeführt.

In diesen Spezifikationsrahmen für assoziative Netzwerke lassen sich viele der bisher bekannten Modelle durch eine entsprechende Wahl der Verarbeitungseinheit und der initialen Verbindungstopologie einordnen. Einschränkungen ergeben sich erstens dadurch, daß assoziative Netzwerke gemäß Definition 2 nur mit Verarbeitungseinheiten vom selben Typ aufgebaut sind. Zweitens wird die Wahl der Dynamikfunktionen durch die Vorgabe der Wertemengen eingeschränkt. Beide Einschränkungen lassen sich einfach beheben: die Erste, indem für  $\mathfrak{B}$  eine endliche Menge von endlichen Mengen von Verarbeitungseinheiten gewählt wird; die Zweite, indem beliebige Wertemengen zugelassen werden. Die Erweiterungen wirken sich aber negativ auf die Handhabbarkeit der Modellbeschreibung im Hinblick auf eine schaltungstechnische und programmtechnische Implementierung aus.

Für den Systementwickler integrierter Schaltungen ist der ausgesprochen modulare und reguläre Aufbau der Netzwerkbeschreibung wichtig. Es gibt nur einen Grundbaustein, der selbst wieder regulär und nur aus wenigen unterschiedlichen Baugruppen aufgebaut ist. Auch wenn die drei Funktionsgleichungen kompliziert ausfallen sollten, kann der Entwurf dieser Einheit vorerst ungeachtet der Netzwerkstruktur ausgeführt werden. Zudem lassen sich alle Netzwerktopologien in eine reguläre Matrixstruktur umwandeln (Abb. 2.2.2b). Dies ist sicherlich für große Netzwerke uneffektiv, denn es entspricht einer vollständigen Vernetzung aller Elemente eines Netzes. Für kleinere Teilnetze, die zu einem assoziativen Netzwerkmodul zusammengefaßt sind und sich zu komplexeren Systemen verschalten lassen, ist dieses Vorgehen angebracht.

## 2.3 Assoziative Informationsverarbeitung

Es stellt sich die Frage, für welche Aufgabenstellungen assoziative Netzwerke geeignet sind. In der Datenverarbeitung ergeben sich immer wieder Forderungen nach Systemlösungen, die große Datenmengen effizient speichern, einzelne Daten schnell wiederfinden sowie unerwünschte Nebeneffekte wie Rauschen und Unsicherheit unterdrücken können. Die Organisation und die effektive Nutzung von Daten ist eine wesentliche Voraussetzung für die Leistungsfähigkeit zukünftiger Informationssysteme.

Heutige Speichertechniken können große Datenmengen aufnehmen, aber nur schwer zugreifbar machen, wenn kein offensichtliches Ordnungsprinzip bekannt ist. Insbesondere ist es schwierig, das Datum herauszufinden, das unter allen gespeicherten Daten das geeignete in bezug auf eine gestörte oder unvollständige Eingabe ist. Gerade in diesem Bereich sind selbst "niedere" Nervensysteme, beispielsweise von Insekten, allen heutigen Rechnerarchitekturen deutlich überlegen.

### 2.3.1 Aufgabenstellung

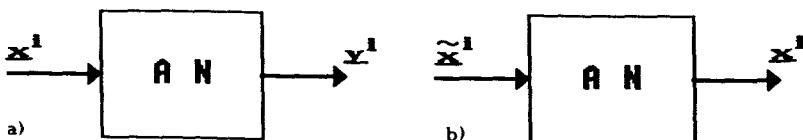

Formal läßt sich die Aufgabenstellung als eine Zuordnung von abstrakten Mustern beschreiben, wobei die Muster als Vektoren aufgefaßt werden. Die grundlegende Funktion eines assoziativen Netzwerkes ist eine Abbildung zwischen zwei endlichen Mustersätzen I und O (Abb. 2.3.1):

$$I = \{ \underline{x}^i : \underline{x}^i \in X^m, i = 1, \dots, z \}$$

$$O = \{ \underline{y}^i : \underline{y}^i \in Y^n, i = 1, \dots, z \}$$

Anschaulich kann man die Musterpaare  $(\underline{x}^i, \underline{y}^i)$  als Frage und Antwort oder Reiz und Reaktion auffassen. Damit wird auch die Begriffsbildung *assoziatives Netzwerk* verständlich, denn umgangssprachlich steht *Assoziation* für Verknüpfung oder Verbindung. Insbesondere steht sie für eine Verknüpfung von Gedanken, so daß der eine Gedanke den anderen ins Gedächtnis zurückruft. Bei der Anwendung assoziativer Netze unterscheidet man zwischen der Hetero- und der Autoassoziation:

Abb. 2.3.1: Grundlegende Aufgabenstellung assoziativer Netze (AN):

a) Musterabbildung (Heteroassoziation);

b) Mustervervollständigung (Autoassoziation).

- Definition 4:**

- a) **Heteroassoziation** (Musterabbildung):

Das assoziative Netzwerk AN speichert z Musterpaare  $(\underline{x}^i, \underline{y}^i)$ ,  $i=1, \dots, z$ . Bei Eingabe eines Musters  $\underline{x}^i$ , bzw. eines genügend großen Teils von  $\underline{x}^i$  bezüglich einer gegebenen Metrik, gibt AN das dazugehörige Muster  $\underline{y}^i$  aus.

- b) **Autoassoziation** (Mustervervollständigung):

Das assoziative Netzwerk AN speichert z Muster  $\underline{x}^i$ ,  $i=1, \dots, z$ . Bei Eingabe eines Musters  $\tilde{\underline{x}}^i$  gibt AN das Muster  $\underline{x}^i$  aus, das zu  $\tilde{\underline{x}}^i$  am ähnlichsten bezüglich einer gegebenen Metrik ist.

Die Autoassoziation kann als Sonderfall der Heteroassoziation angesehen werden ( $\underline{x}^i = \underline{y}^i$ ), bei der Bruchstücke eines gespeicherten Musters dazu dienen, das vollständige Muster abzurufen. Ein anschauliches Beispiel für die Autoassoziation von gespeicherten Gesichtern (Kohonen [25]) zeigt Abbildung 2.3.2. In einem assoziativen Netzwerk sind 100 Prototypen derartiger Gesichter eingespeichert worden. Jedes Bild hat  $54 \times 56 = 3024$  Bildpunkte mit jeweils acht Graustufen. Das assoziative Netzwerk kann sowohl ein unvollständiges (Abb. 2.3.2b oben) als auch ein gestörtes (Abb. 2.3.2b unten) Eingabemuster korrekt ergänzen.

**Abb. 2.3.2:** Demonstration der Mustervervollständigung (Kohonen [25]):

a) gespeicherte Prototypen; b) unvollständige bzw. gestörte

Eingabe; c) assoziierte Muster.

Die Musterabbildung bzw. -vervollständigung kann auch mit inhaltsorientierten Zugriffsverfahren der Digital- oder Softwaretechnik realisiert werden. Um die Eigenschaften der inhaltsadressierten Speicher oder der Hash-Kodierung mit assoziativen Netzwerken vergleichen zu können, werden im weiteren nur Anwendungen mit binären Ein- und Ausgabemustern ( $X=Y=\{0,1\}$ ) betrachtet.

### 2.3.2 Die Pseudoinversen-Technik

Das assoziative Modell von Kohonen erreicht seine Fähigkeiten (Abb. 2.3.2) durch die Verwendung der Pseudoinversen-Technik [25]. Kohonen fasst die Musterzuordnung als lineare Abbildung auf, für die das Abbildungsproblem als Matrix-Vektor-Multiplikation formuliert werden kann:

$$\underline{y}^i = \mathbf{W} \cdot \underline{x}^i, \text{ für alle } i = 1, \dots, z. \quad (2.3.1)$$

Faßt man die Vektoren  $\underline{x}^i$  und  $\underline{y}^i$  als Matrixspalten der entsprechenden Matrizen  $\mathbf{X}$  und  $\mathbf{Y}$  auf, so erhält man:

$$\mathbf{Y} = \mathbf{W} \cdot \mathbf{X} \quad (2.3.2)$$

Sind die Vektoren  $\underline{x}^i$  linear unabhängig, dann kann die Matrix  $\mathbf{X}$  invertiert und die Gleichung gelöst werden:

$$\mathbf{W} = \mathbf{Y} \cdot \mathbf{X}^{-1} \quad (2.3.3)$$

Es können mit  $\mathbf{W}$  alle  $z \leq m$  Musterpaare exakt bestimmt werden. Sind die Eingabevektoren linear abhängig, dann erhält man eine im Sinne der mittleren quadratischen Abweichung optimale Lösung mit der Pseudoinversen  $\mathbf{X}^*$  [25]:

$$\mathbf{W} = \mathbf{Y} \cdot \mathbf{X}^* \quad (2.3.4)$$

Eine Pseudoinverse  $\mathbf{X}^*$  existiert zu jeder Matrix  $\mathbf{X}$ . Für linear unabhängige Eingabevektoren entspricht  $\mathbf{X}^*$  der inversen Matrix  $\mathbf{X}^{-1}$ . Es gibt mehrere Verfahren zur Berechnung der Pseudoinversen [33], die aber keine "lokalen" Adaptationsregeln im Sinne von Abschnitt 2.2.1 darstellen. Eine approximative Lösung der Pseudoinversen bietet die folgende lokale, überwachte Adaptionsregel [25]:

$$\begin{aligned} \mathbf{W}^h &= \mathbf{W}^{h-1} + c \cdot (\underline{y}^i - \mathbf{W}^{h-1} \cdot \underline{x}^i) \underline{x}^i{}^T \\ \mathbf{W}^0 &= \mathbf{Q}, \text{ Nullmatrix, } i \in \{1, \dots, z\}, h \in \mathbb{N}. \end{aligned} \quad (2.3.5)$$

Die zu lernenden Vektorpaare müssen nacheinander und in der Regel mehrfach zur Berechnung der Matrix  $\mathbf{W}$  herangezogen werden. Die Lern-

regel ist vergleichbar mit der *Perzepron-Regel* (2.1.1) und wird allgemein mit *Delta-Regel* oder *Fehler-Korrektur-Regel* (error-correction rule [27]) bezeichnet.

Die Matrix  $\mathbf{W}$  speichert die Muster nicht lokal in einer bestimmten Spalte oder Zeile, sondern nur deren Korrelationen untereinander, verteilt über alle Matrixkomponenten. Jede Matrixkomponente  $w_{ij}$  kann zur Speicherung von mehreren Mustern beitragen, während bei einer *lokalen* Speicherung jede Komponente nur zur Speicherung eines Musters benutzt wird.

Die Pseudoinversen-Technik wird im allgemeinen für kontinuierliche Ein- und Ausgaben ( $X=Y=\mathbb{R}$ ) angewendet. Für linear unabhängige Eingabemuster ist die Musterabbildung bzw. -vervollständigung fehlerfrei, so daß maximal  $m$  Musterpaare  $(\underline{x}^i, X^m)$  fehlerfrei gespeichert werden können. Für linear abhängige Muster ist die Zuordnung bezüglich der mittleren quadratischen Abweichung  $\|\underline{y}^i - \mathbf{W} \cdot \underline{x}^i\|^2$  minimal. Der Berechnungsaufwand für die Matrix  $\mathbf{W}$  ist hoch, und die Matrixkomponenten  $w_{ij}$  können beliebige Werte annehmen. Im Hinblick auf eine schaltungstechnische Realisierung ist es sicherlich sinnvoll, vorerst von einfacheren Modellen auszugehen.

### 2.3.3 Die assoziative Matrix

Die einfachste und grundlegendste Struktur, die sich einer verteilten Speicherung bedient, ist die *assoziative Matrix* [34,35]:

**Definition 5:** Eine **assoziative Matrix** ist ein Netzwerk  $AM=(\mathfrak{B}, \mathfrak{C}, \mathfrak{v}, \epsilon, \delta)$  mit  $n$  Verarbeitungseinheiten  $AS=(m, X, Y, A, W, \delta, \alpha, \lambda)$ :

$$X = Y = W = \{0,1\}; \quad A = \mathbb{N};$$

$$\delta(\underline{x}(t), \underline{w}) = \underline{x}(t)^T \cdot \underline{w} =: a(t);$$

$$\alpha(a(t)) = \begin{cases} 1, & \text{wenn } a(t) \geq Th, \quad Th \in \mathbb{N}; \\ 0, & \text{sonst.} \end{cases}$$

$$\lambda(\underline{x}^h, \underline{w}^{h-1}, y^h) = \underline{w}^h, \quad \text{mit } w_i^h = w_i^{h-1} \vee (x_i^h \wedge y^h).$$

$\forall i \in \{1, \dots, m\}, \quad h=1, \dots, z;$

$\vee \equiv$  logisches "ODER"

$\wedge \equiv$  logisches "UND"

$\underline{w}^0 = \text{Nullvektor}; \quad \underline{w}^z = \underline{w}^z$

$$\mathfrak{B} = \{ AS_j : j = 1, \dots, n \}; \quad \mathfrak{C} = \{ e_i : i = 1, \dots, m \};$$

$$v(AS_k, AS_1) = 0, \quad \forall k, l \in \{1, \dots, n\};$$

$$\epsilon(e_i, AS_j) = 1, \quad \forall j \in \{1, \dots, n\} \text{ und } i \in \{1, \dots, m\};$$

$$\delta(AS_j) = 1, \quad \forall j \in \{1, \dots, n\}.$$

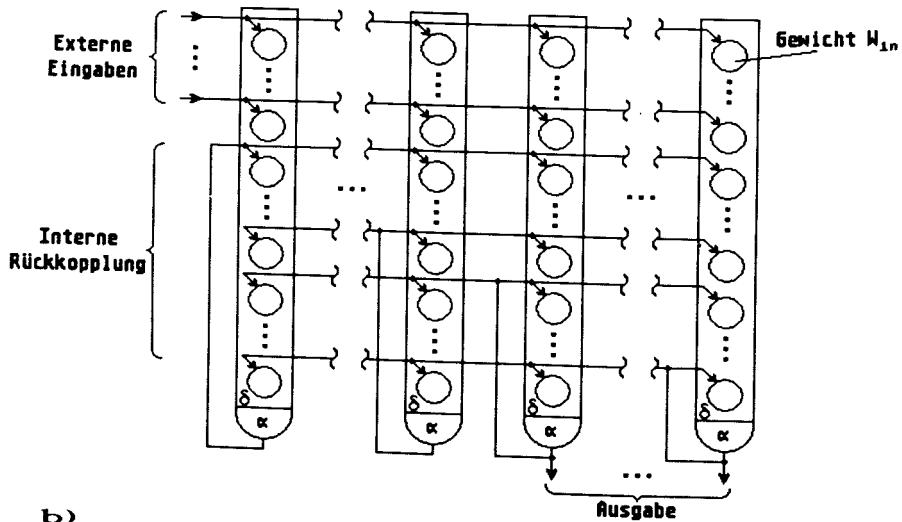

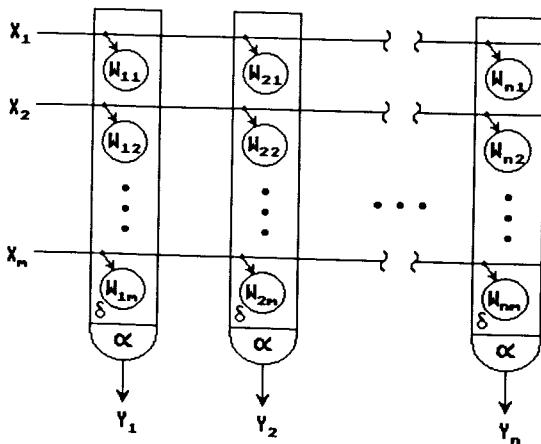

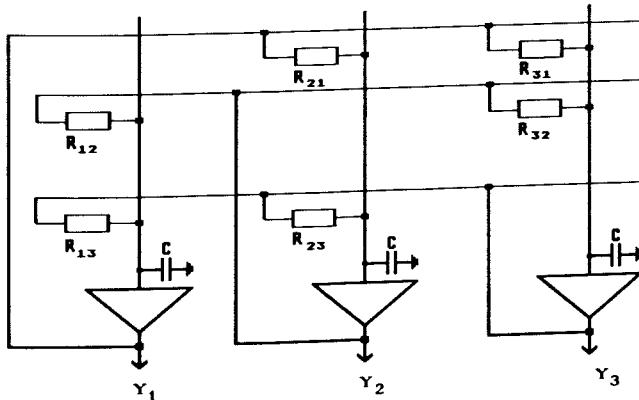

Abb. 2.3.3: Die assoziative Matrix.

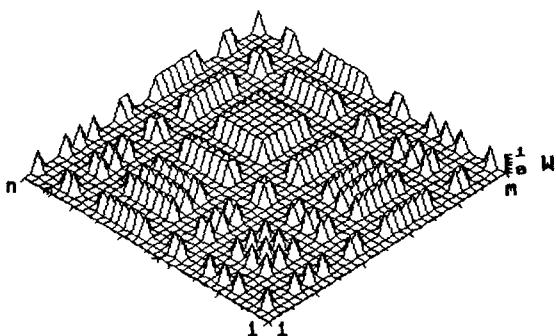

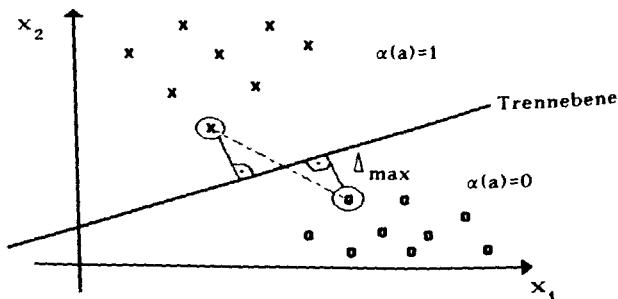

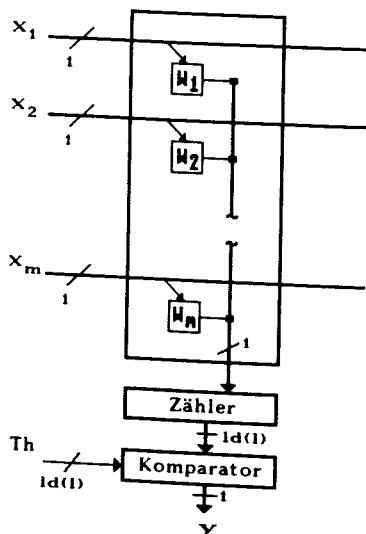

Die assoziative Matrix besteht aus  $n$  nicht miteinander gekoppelten Verarbeitungseinheiten, die alle dieselbe Eingabe erhalten. Es gibt keine versteckten Verarbeitungseinheiten, alle sind sowohl Eingabe- als auch Ausgabeeinheit. Bei Eingabe eines bestimmten Musters berechnen alle Verbindungseinheiten parallel und unabhängig voneinander den Aktivierungswert  $a_j$ . Der nachfolgende Schwellenwertvergleich liefert für jede Verarbeitungseinheit eine binäre Ausgabe, wobei in diesem Modell für alle Verarbeitungseinheiten ein einheitlicher Schwellenwert  $T_h$  angenommen wird. Der Schwellenwert wird von außen vorgegeben und ist kleiner oder gleich der Anzahl der aktivierte Eingangsleitungen ( $x_i=1$ ).

Die Zuordnungen werden in der *Lernphase* in die Matrix, deren Spalten die Gewichte der Verarbeitungseinheiten bilden, eingespeichert. Ausgehend von einer gelöschten Matrix  $W_0$  - alle Gewichte  $w_{ij}$  haben den binären Wert Null- werden die Gewichte iterativ durch Anlegen der  $z$  Musterpaare an die Matrix bestimmt:

$$W^h = W^{h-1} \vee (x^h * (y^h)^T), h = 1, \dots, z \quad (2.3.6)$$

Die Muster  $\underline{x}^h$  und  $\underline{y}^h$  werden als Spaltenvektoren aufgefaßt, wobei das Ausgabemuster  $\underline{y}^h$  in einen Zeilenvektor transponiert wird ( $\underline{y}^T$ ). Die '\*'-Operation auf diesen beiden Vektoren definiert die Matrix  $M$  mit  $m_{kl} = x_l^h \cdot y_k^h$ , die die gleiche Dimension hat wie die Verbindungsma trix  $W$  (m Zeilen, n Spalten). Die 'v'-Operation auf diesen beiden Matrizen ist als logische 'ODER'-Verknüpfung der jeweiligen Matrixelemente definiert:

$$w_{kl}^h = w_{kl}^{h-1} \swarrow m_{kl} \quad (2.3.7)$$

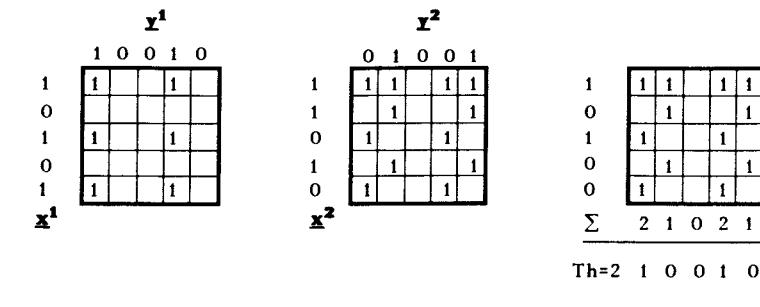

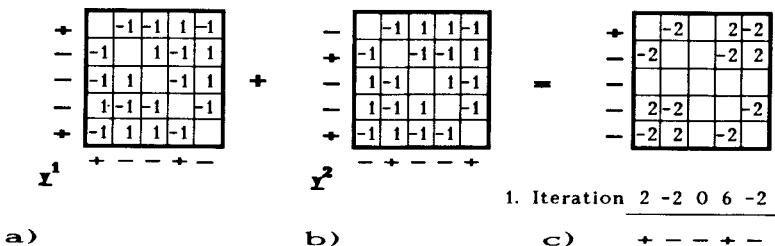

Entsprechend dieser Lernregel überlagern sich die einzelnen Musterpaare in der Gewichtsmatrix, d.h. die Matrix füllt sich mehr und mehr mit Einsen. Ein einfaches Beispiel für die Heteroassoziation zeigt Abb. 2.3.4. Die beiden eingespeicherten Ausgabemuster ( $\underline{y}^1$ ,  $\underline{y}^2$ ) lassen sich selbst beim Fortlassen einer Eins im Eingabemuster vollständig auslesen. Um eine fehlerfreie Abbildung zu gewährleisten, dürfen jedoch nicht beliebig viele Muster eingegeben werden. Eine quantitative Untersuchung erfolgt im Kapitel 3.

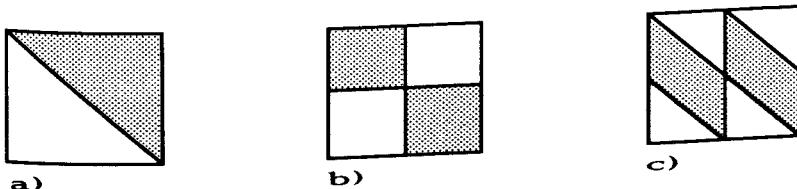

a)

b)

c)

Abb. 2.3.4: Beispiel für das Einspeichern von binären Mustern in eine assoziative Matrix (a,b) und für eine Assoziation mit einem unvollständigen Eingabemuster (c).

### 2.3.4 Das Hopfield-Netz

Ein sehr bekanntes und intensiv untersuchtes rückgekoppeltes Netzwerk ist das Hopfield-Netz [23]:

**Definition 6:** Ein **Hopfield-Netz** ist ein Netzwerk  $HN = (\mathfrak{B}, \mathfrak{C}, v, e, \delta)$  mit  $n$  Verarbeitungseinheiten  $HOP = (n, X, Y, A, W, \delta, \alpha, \lambda)$ :

$$X = Y = \{-1, +1\}; \quad W = A = Z$$

$$\underline{y}(t=0) = \underline{x} \quad \text{mit set=1};$$

$$\underline{y}(t>0) = \alpha(a(t-1)) \quad \text{mit set=0};$$

$$\delta(\underline{y}(t), \underline{w}) = \underline{y}(t)^T \cdot \underline{w} =: a(t);$$

$$\alpha(a(t)) = \begin{cases} +1, & \text{wenn } a > 0 \text{ und select=1} \\ -1, & \text{wenn } a < 0 \text{ und select=1} \\ y(t-1) \text{ sonst.} \end{cases}$$

select  $\in \{0,1\}$ , eine diskrete Zufallsvariable;

$$\lambda(\underline{x}^h, \underline{w}^{h-1}, y^h) = \underline{w}^{h-1} + y^h \cdot \underline{x}^h; \quad \forall h \in \{1, \dots, z\};$$

$$\underline{x}^0 = \text{Nullvektor}; \quad \underline{w} = \underline{w}^z;$$

$$\mathfrak{B} = \{ HOP_j : j = 1, \dots, n \}; \quad \mathfrak{C} = \{ e_i : i = 1, \dots, n \};$$

$$v(HOP_k, HOP_j) = \begin{cases} 1, & \forall k, j \in \{1, \dots, n\} \text{ und } k \neq j \\ 0, & \text{für } k=j \end{cases}$$

$$\delta(HOP_j) = 1, \quad \forall j \in \{1, \dots, n\}$$

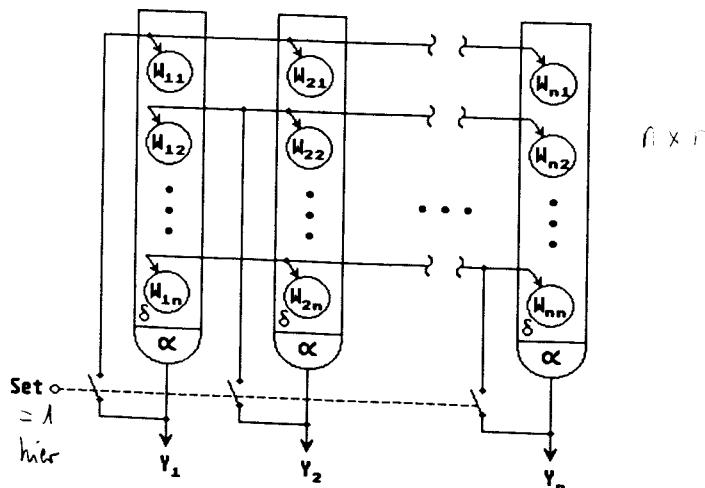

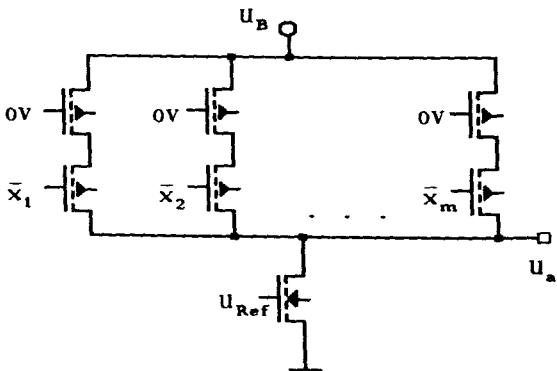

Abb. 2.3.5: Das Hopfield-Netz.

Das Hopfield-Modell basiert ebenfalls auf dem Schwellenneuron (vgl. 2.1), wobei hier der Schwellenwert  $\text{Th}=0$  festgelegt ist und die Ein- und Ausgabewerte  $+1/-1$  anstatt  $1/0$  sind. Beide Fälle lassen sich aber ineinander überführen, so daß diese Auswahl der Ein-/Ausgabesignale und der Schwelle für die Berechnungsmächtigkeit einer Verarbeitungseinheit unbedeutend ist [36].

Alle Verarbeitungseinheiten sind vollständig untereinander vernetzt, nur die Rückkopplung auf sich selbst ist nicht erlaubt. Die Verarbeitungseinheiten arbeiten asynchron, modelliert durch die Zufallsvariable *select*. Zu jedem Zeitpunkt  $t$  wird zufällig eine Teilmenge von Elementen ausgewählt, diese dürfen ihren Ausgabewert gemäß der Ausgabefunktion ändern. Die Ausgaben aller anderen Elemente bleiben konstant. In der Regel werden die Verarbeitungseinheiten mit der gleichen Wahrscheinlichkeit und im Mittel nur eine zu jedem diskreten Zeitpunkt ausgewählt.

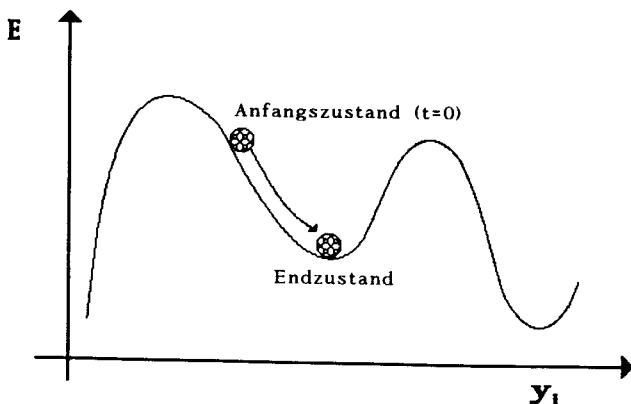

Für einen Assoziationsvorgang werden die Ausgänge der  $n$  Verarbeitungseinheiten mit einem Teilmuster eines gespeicherten Musters belegt. Die Rückkopplung wird während dieser Initialisierung aufgetrennt ( $\text{Set}=1$ , Abb. 2.3.S) und zur Assoziation wieder geschlossen ( $\text{Set}=0$ ). Jeder Anfangszustand *relaxiert* in einen stabilen Endzustand, der dem Ausgabemuster entspricht. Dieses Modell arbeitet somit autoassoziativ.

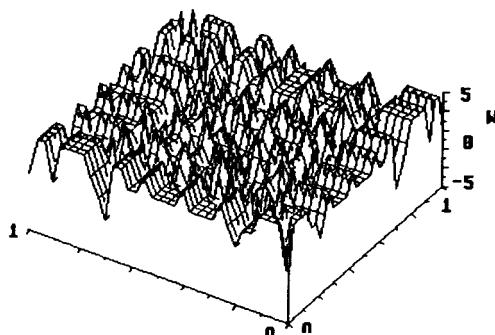

Ein wesentlicher Gesichtspunkt der Arbeiten von Hopfield ist die Einführung einer Energiebetrachtung zur Beschreibung der Netzwerkdynamik. Demnach wird jedem Netzwerkzustand eine bestimmte (potentielle) Energie zugeordnet [23]:

$$E = - \frac{1}{2} \sum_{i=1}^n \sum_{j=1}^n y_i \cdot y_j \cdot w_{ij} \quad (2.3.8)$$

Für ein symmetrisches Netzwerk, d.h.  $w_{ij} = w_{ji}$ , mit  $w_{ii} = 0$  ergibt sich bei einer Änderung eines Ausganges  $y_i$  einer Verarbeitungseinheit eine Energieänderung:

$$\Delta E = - \Delta y_i \sum_{j=1}^n y_j \cdot w_{ji} \quad (2.3.9)$$

Jede Änderung von  $E$  ist somit negativ, die Energie nimmt also stetig ab. Sie ist jedoch daran gebunden, einen endlichen Wert anzunehmen. Daraus folgt, daß das System mit der Zeit in einen stabilen Zustand laufen muß, in dem sich die Energie nicht mehr ändert. Das System befindet sich dann in einem Energieminimum. Allerdings ist nicht gewährleistet, daß der Endzustand des Systems in einem Energieminimum auch die beste Lösung bezüglich des Eingabemusters ist. Die beste Lösung ist zum Beispiel die, die den kleinsten euklidischen Abstand zu den geforderten

Lösung hat. Die dem Gradienten folgende Energieabnahme des Systemzustandes kann in einem lokalen Minimum enden und so nur zu einer suboptimalen Lösung gelangen (Abb. 2.3.6).

Abb. 2.3.6: Schematisches Bild der Systemenergie  $E$  als Funktion einer Koordinate im mehrdimensionalen Zustandsraum.

Voraussetzung für die Konvergenz dieses nichtlinearen Rückkopplungsmechanismus ist eine symmetrische Verbindungsmatrix mit einer Null-diagonalen ( $w_{ii}=0$ ). Die Verbindungsma trix wird in der Lernphase durch die angegebene Lernregel berechnet:

$$\mathbf{w}^h = \mathbf{w}^{h-1} + \frac{\lambda}{z} \mathbf{x}^h \cdot (\mathbf{x}^h)^T, \quad h = 1, \dots, z \quad (2.3.10)$$

Im Gegensatz zur assoziativen Matrix können hier die Matrixgewichte ganzzahlige Werte ( $-z \leq w_{ij} \leq +z$ ) annehmen. In Abb. 2.3.7 ist ein einfaches Beispiel für das Einspeichern von 2 Mustern und der Assoziation eines gestörten Eingabemusters aufgeführt. Das Einschwingen auf den stabilen Endzustand beschränkt sich hier auf einen Schritt.

In der Literatur gibt es eine Vielzahl von Variationen zu der hier gewählten Definition eines Hopfield-Netzes. Die Zustandsänderung der Verarbeitungseinheiten kann z.B. auch synchron erfolgen, indem entweder alle Verarbeitungseinheiten im Netz gleichzeitig (parallel) oder einzeln nach einer festgelegten Reihenfolge (seriell) einen neuen Ausgabewert erzeugen. Häufig werden die Verbindungs gewichte nach der Lernphase auf

die Werte  $\{+1, 0, -1\}$  beschränkt, das z.B. hinsichtlich einer schaltungstechnischen Realisierung vorteilhaft ist. Die Auswirkungen dieser Variationen auf die Systemeigenschaften sind Gegenstand theoretischer Untersuchungen [37].

Abb. 2.3.7: Beispiel für das Einspeichern von zwei binären Mustern in ein Hopfield-Netz (a,b) und für eine Assoziation mit einem unvollständigen Eingabemuster (c).

Die drei vorgestellten assoziativen Modelle verfügen über eine einfache und reguläre Matrixstruktur. Die Matrixkomponenten entsprechen den Verbindungsgewichten von linear angeordneten Verarbeitungseinheiten eines assoziativen Netzwerkes. Die Aktivierungsfunktion der Verarbeitungseinheiten ist die gewichtete Summe der Eingabewerte.(2.2.1). Unterschiede bei den Verarbeitungseinheiten ergeben sich hinsichtlich der berechneten Ausgabe- und Adaptationsfunktion sowie bezüglich des Wertebereiches der Verbindungsgewichte. Alle drei Modelle bedienen sich einer verteilten Speicherung und lassen sich für eine fehlertolerante Zuordnung bzw. Vervollständigung von binären Mustern verwenden.

## 2.4 Anwendungsbspiele

Ein anschauliches Beispiel für die Mustervervollständigung ist die bereits erwähnte autoassoziative Speicherung von Grauwertbildern. Verwendet man binäre Bildpunkte, dann können derartige Bilder auch in eine assoziative Matrix und ein Hopfield-Netz eingespeichert werden [38]. Die Simulation derart großer Matrizen ist auf einem Rechner mit Mehrprogrammbetrieb sehr zeitaufwendig und benötigt viel Speicherplatz. Zur Speicherung der  $3024 \times 3024 \approx 9$  Millionen Matrixkomponenten benötigt man immerhin 36 MegaByte Speicherplatz, bei einer Wortbreite von 32 Bit pro Komponente. Für eine Mustervervollständigung müssen ca. 9 Millionen

Multiplikationen und Additionen ausgeführt werden. Zur Untersuchung der Eigenschaften von verschiedenen Modellen sind derart komplexe Muster sehr unhandlich.

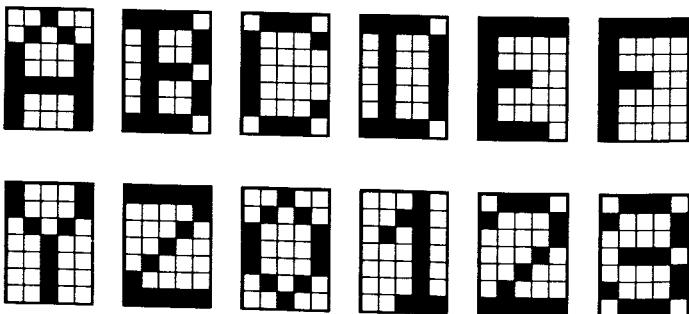

Häufig verwendet man daher einfachere Muster, wenngleich diese für eine Anwendung unattraktiv sind. Ein ganz einfaches Beispiel sind 7x5-Rasterbilder von ASCII-Zeichen (Abb. 2.4.1). In eine assoziative Matrix mit  $m=n=35$  lassen sich z.B. bis zu 6 Musterpaare fehlerfrei heteroassoziativ einspeichern [32]. Ein Hopfield-Netz kann max. 5 Muster autoassoziativ [39] und mit der Pseudoinversen-Technik lassen sich bis zu 35 Musterpaare heteroassoziativ speichern [32]. Auf den ersten Blick erscheint die Pseudoinversen-Technik als die günstigere Lösung. Es bleibt aber zu beachten, daß die Matrixkomponenten reelle Zahlen sind, während die assoziative Matrix nur binäre Verbindungsgewichte hat (vgl. 3.3).

Abb. 2.4.1: Beispiele der verwendeten 7x5-Rasterbilder von ASCII-Zeichen zur assoziativen Speicherung.

Ein attraktiveres Anwendungsbeispiel für heteroassoziative Zuordnungen ist ein Telefonregister. In einer assoziativen Matrix mit  $m=1800$  und  $n=400$  sind z.B. 500 Musterpaare [Name,Telefonnummer] eingespeichert worden, von denen 85% fehlerfrei und der Rest mit einem Bitfehler wieder ausgelesen werden konnte [40]. Aufgrund der verwendeten Kodierung konnten diese Bitfehler eindeutig und mit geringem Aufwand korrigiert werden. Beispiele für die Fehlertoleranz gegenüber Eingabefehlern zeigt Tabelle 2.4.1. Die Ergebnisse können selbstverständlich nicht auf alle Musterpaare verallgemeinert werden. Die Fehlertoleranz hängt von den Musterpaaren selbst, dem Füllungsgrad der Matrix und von der verwendeten Kodierung ab (siehe Kapitel 3).

|                                  |                           |             |

|----------------------------------|---------------------------|-------------|

| <b>gespeicherte Musterpaare:</b> | <b>Stelzner, Peter</b>    | <b>3592</b> |

|                                  | <b>Schwarz, Christoph</b> | <b>2323</b> |

|                                  | <b>Schwarz, Dittrich</b>  | <b>2365</b> |

| <b>Eingabe:</b> | <b>Stelzner</b>    | <b>Ausgabe:</b> | <b>3592</b>   |

|-----------------|--------------------|-----------------|---------------|

|                 | <b>Stelzn, P</b>   |                 | <b>3592</b>   |

|                 | <b>Selzner, P</b>  |                 | <b>3592</b>   |

|                 | <b>Schwarz</b>     |                 | <b>232365</b> |

|                 | <b>Schwarz, Di</b> |                 | <b>2365</b>   |

*Tabelle 2.4.1: Beispiele für Musterzuordnungen einer assoziativen Matrix bei fehlerhafter Eingabe.*

Eine interessante Anwendung für das Hopfield-Netz ist das Finden eines günstigen, nach Möglichkeit optimalen Reiseweges für einen Handlungsreisenden (travelling salesman problem) [41]. Für dieses Optimierungsproblem wächst der Rechenaufwand auf seriellen Rechnern exponentiell mit der Problemgröße (np-vollständiges Problem [42]).

Es gibt eine Vielzahl von weiteren Anwendungsbeispielen für assoziative Netzwerke [25,43-45]. Alle Beispiele verdeutlichen die grundlegenden qualitativen Eigenschaften von assoziativen Modellen. Für eine Bewertung der Leistungsfähigkeit der verschiedenen Modelle und insbesondere auch für einen Vergleich mit konventionellen Lösungsmethoden sind quantitative Aussagen notwendig. Die wesentlichen Fragen beziehen sich auf die Anzahl der maximal speicherbaren Muster im Verhältnis zum Aufwand, auf die Fehlertoleranz und auf die Zugriffsgeschwindigkeit bzw. die Anzahl der notwendigen Rechenoperationen für eine Musterzuordnung. Im folgenden Kapitel werden Abschätzungen zur Speichereffektivität und Fehlertoleranz der drei hier vorgestellten Modelle angegeben.

### 3. Speichereigenschaften assoziativer Netzwerke

#### 3.1 Speichereffektivität

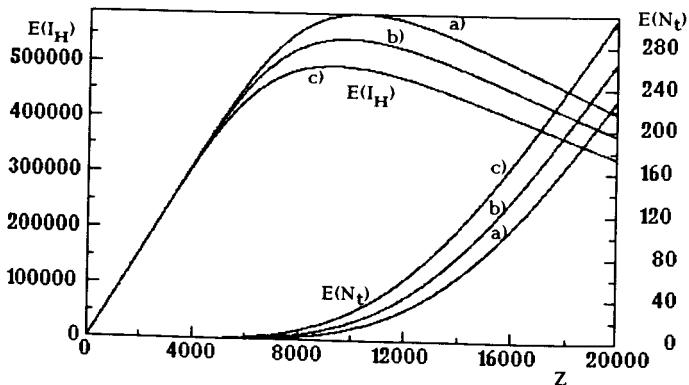

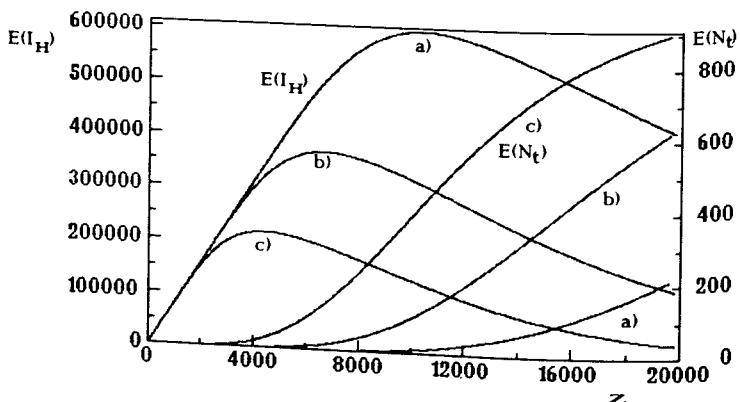

Es stellt sich die Frage, wieviele und wie effektiv binäre Musterpaare in die oben beschriebenen assoziativen Netzwerkmodelle eingespeichert werden können. Für binäre Muster läßt sich nach Shannon [46] der Informationsgehalt für ein binäres Muster der Länge  $n$  mit  $I_d(2^n) = n$ -Bit angeben, wenn alle  $2^n$  möglichen Muster zugelassen werden und alle Muster mit der gleichen Wahrscheinlichkeit auftreten. Kann ein Netzwerk nun  $z$  Muster fehlerfrei zuordnen, so entspricht das einem Informationsgehalt von  $z \cdot n$ -Bits. Aufgrund der verteilten Speichertechnik der vorgestellten assoziativen Modelle sind die Musterzuordnungen nicht grundsätzlich fehlerfrei. Für diese Fälle muß man die Information, die zur Korrektur dieser Fehler notwendig ist, wieder abziehen. Bezeichnen wir mit  $I^1$  den Informationsgehalt des fehlerfreien Ausgabemusters  $\underline{x}^1$  und mit  $I_{\text{Fehler}}^1$  die Information, die benötigt wird, um den Fehler in der Ausgabe zu korrigieren. Der *Informationsgehalt* eines assoziativen Netzwerkes mit  $z$  gespeicherten Musterpaaren ( $\underline{x}^1, \underline{x}^2$ ) ergibt sich zu:

$$I_H = \sum_{i=1}^z (I^1 - I_{\text{Fehler}}^1) \quad (3.1.1)$$

Die *Speichereffektivität*  $S_{\text{eff}}$  eines assoziativen Netzwerkes ergibt sich aus dem Quotienten des Informationsgehaltes und der aufgewendeten Speicherressourcen. Sei  $b$  die Anzahl der Bits, die zur Speicherung eines Gewichtswertes in einer  $m \times n$  Matrix aufgewendet werden muß. Für die Speichereffektivität folgt:

$$S_{\text{eff}} = \frac{I_H}{n \cdot m \cdot b} \quad (3.1.2)$$

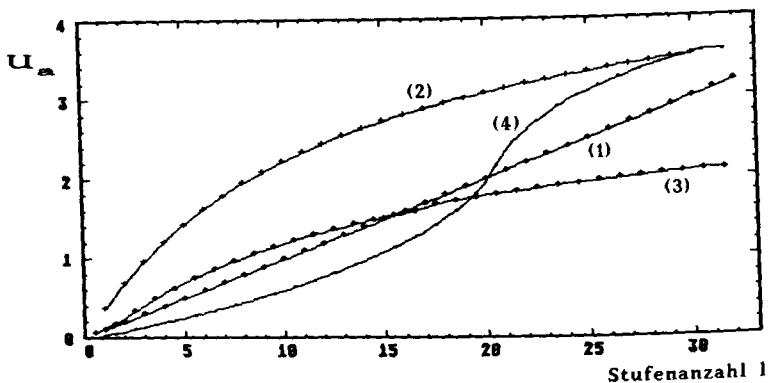

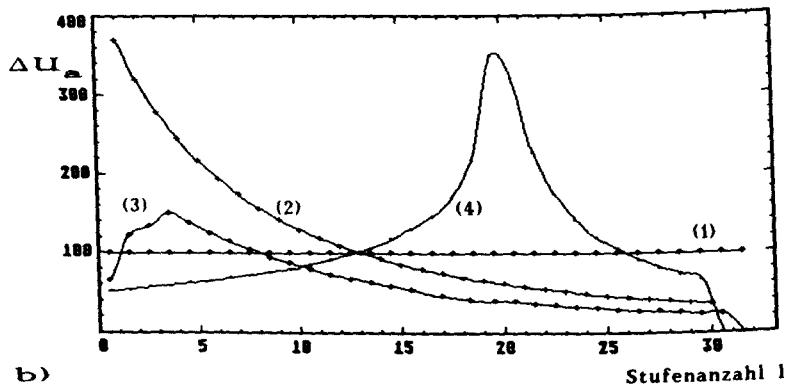

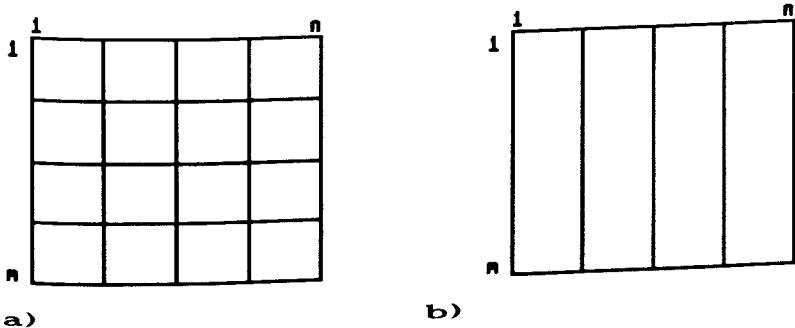

##### 3.1.1 Speichereffektivität einer assoziativen Matrix

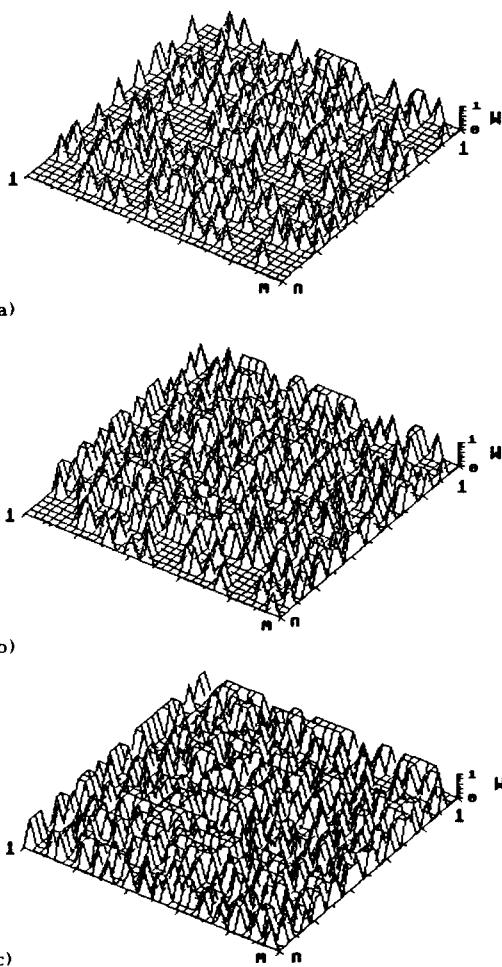

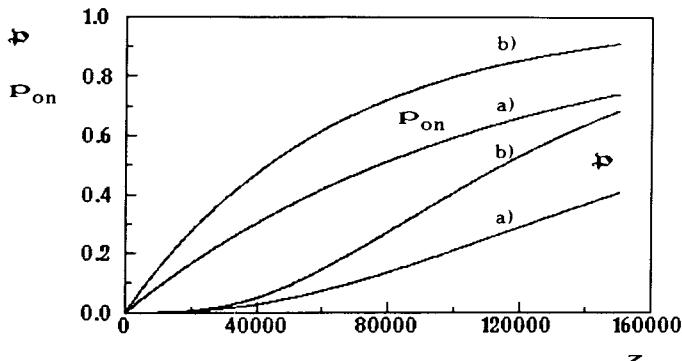

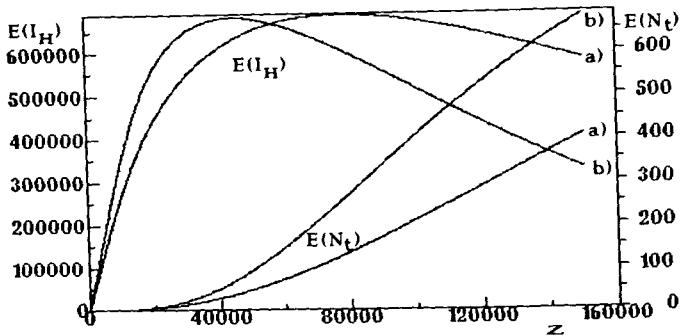

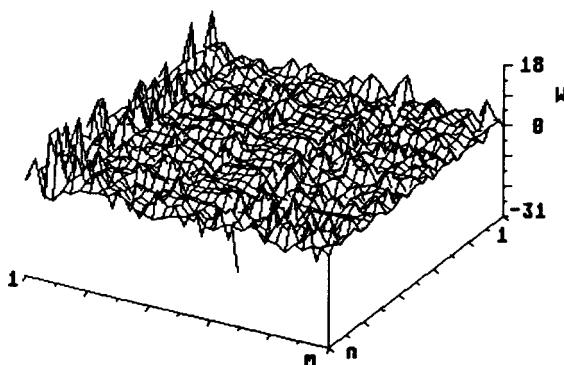

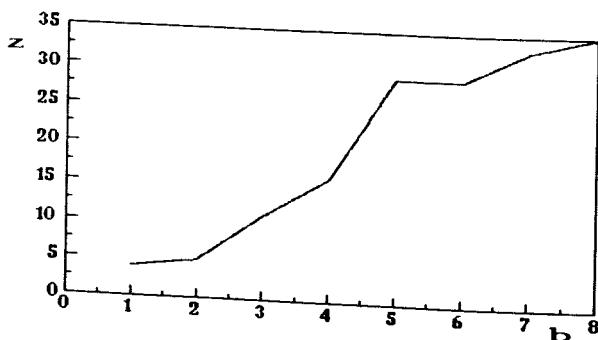

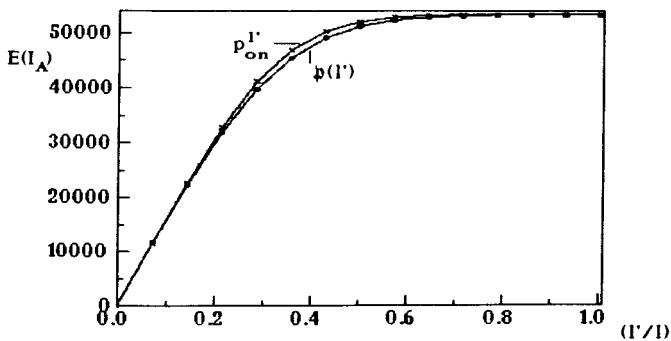

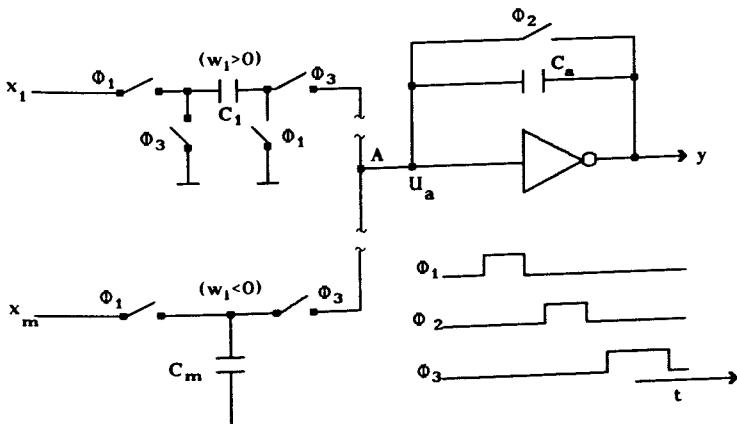

In eine assoziative Matrix sollen  $z$  Musterpaare ( $\underline{x}^1, \underline{x}^m$ ,  $\underline{x}^1, \underline{y}^n$ ) hetero-assoziativ eingespeichert werden. Die Eingabemuster  $\underline{x}^i$  haben genau 1 und die Ausgabemuster  $\underline{x}^i$  genau  $k$  Einsen. Ausgehend von einer leeren Gewichtsmatrix  $\underline{W}_0$  werden für jedes Musterpaar gemäß der Adaptionsregel Glg. (2.3.7) neue Verbindungsgewichte in der Matrix gesetzt (Abb. 3.1.1). Die Anzahl der neuen Verbindungen ist für das erste Musterpaar  $1 \cdot k$ . Sie nimmt aber für jedes weitere Musterpaar in dem Maße ab, wie die Wahrscheinlichkeit  $p_{on}$  ansteigt, mit der eine Verbindung bereits vorhanden ist.

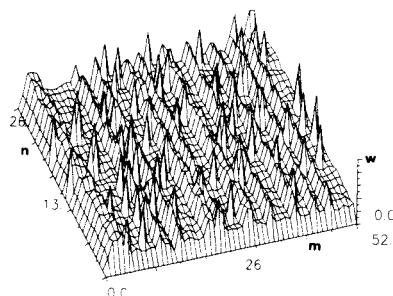

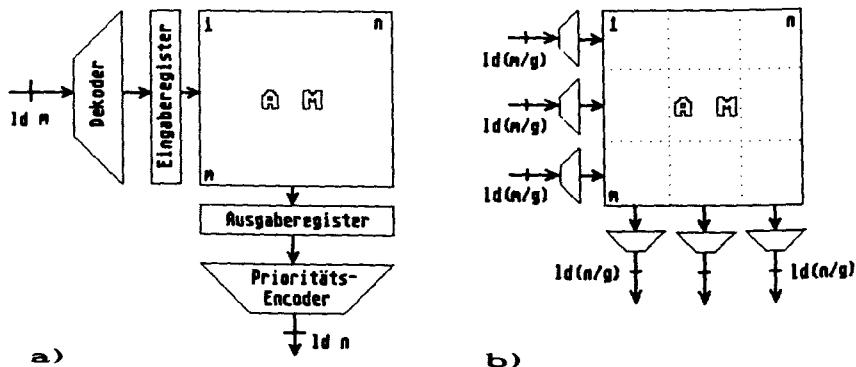

*Abb. 3.1.1: Belegungsgrad einer heteroassoziativen Matrix ( $n=m=35$ ) nach dem Einspeichern von  $z$  Musterpaaren mit ( $k=l=5$ ):

a)  $z=10$ ,  $p_{on}=0.19$ ;      b)  $z=20$ ,  $p_{on}=0.34$ ;      c)  $z=30$ ,  $p_{on}=0.45$ ;*

Sind die Muster zufällig und unabhängig voneinander ausgewählt worden, so gilt nach dem Anlernen von  $z$  Musterpaaren:

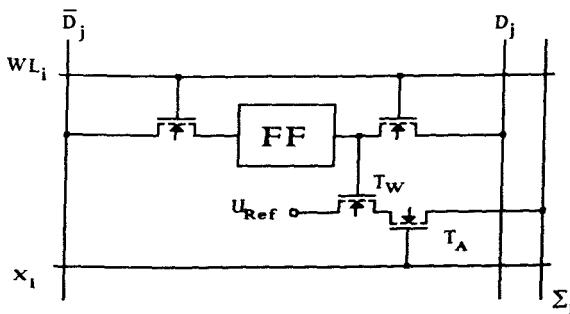

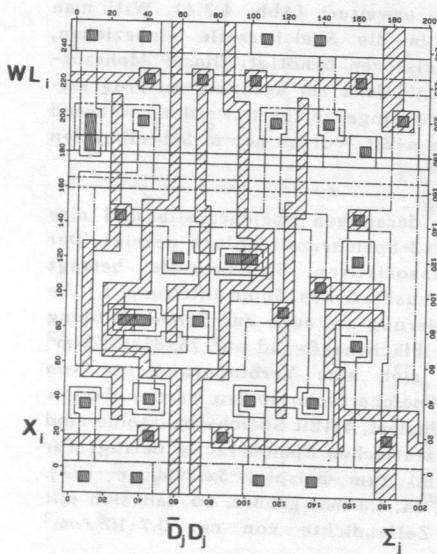

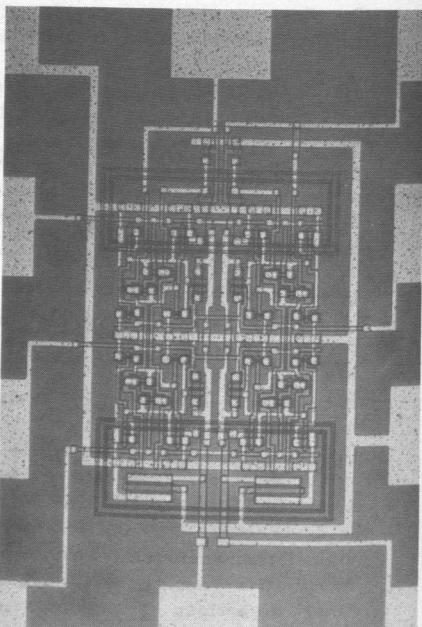

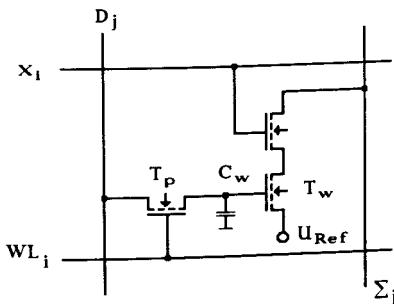

$$p_{on} = \left( 1 - \left( 1 - \frac{k \cdot l}{n \cdot m} \right)^z \right) \quad (3.1.3)$$