# **Immunorepairing of Hardware Systems**

## Dissertation

A thesis submitted to the

Faculty of Computer Science, Electrical Engineering and Mathematics

of the

University of Paderborn

in partial fulfillment of the requirements for the

degree of *Dr. rer. nat*

by

**Norma Alicia Montealegre Agramont**

Paderborn, Germany

July 2013

*Supervisor:*

Prof. Dr. Franz Josef Rammig

*Reviewers:*

Prof. Dr. Franz Josef Rammig

Prof. Dr. Sybille Hellebrand

*Additional members of the oral examination committee:*

Prof. Dr. Marco Platzner

Prof. Dr. Hans Kleine Büning

Dr. Matthias Fischer

*Date of submission:*

31.01.2013

*Date of the oral examination:*

22.03.2013

---

# Summary

Repairing a hardware system that operates in an extreme and inaccessible environment, such as a hardware module of a spaceborne or underwater device on-site, is very costly or even sometimes impossible. That is the reason why, techniques for the design of a hardware system which is able to recover from a failure autonomously are necessary. Such hardware system able to recover from a failure autonomously is named a self-repairing hardware system and is composed basically of a fault recognition module, a recovery procedure module, and the circuit to be repaired. For the design of the fault recognition module, a low fault recognition latency is a requirement, so that it can operate online and concurrently to the operation of the circuit to be repaired. In the literature there are many approaches of self-repairing systems, however, most of them do not deliver details of the design of a fault recognition module which is able to work concurrently to the operation of the circuit to be repaired. Moreover, it has been noticed that many of the existing approaches propose new non-commercial hardware platforms or self-repairing procedures which are hard to reproduce. Hence, this thesis evaluates a set of fault recognition techniques that focus on reducing the fault recognition latency and hardware overhead and delivers a modular framework for the implementation of a self-repairing hardware system.

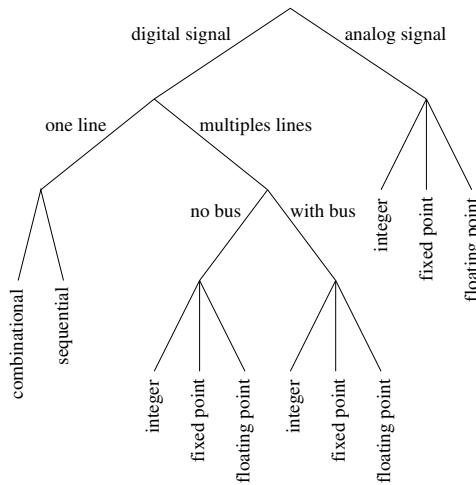

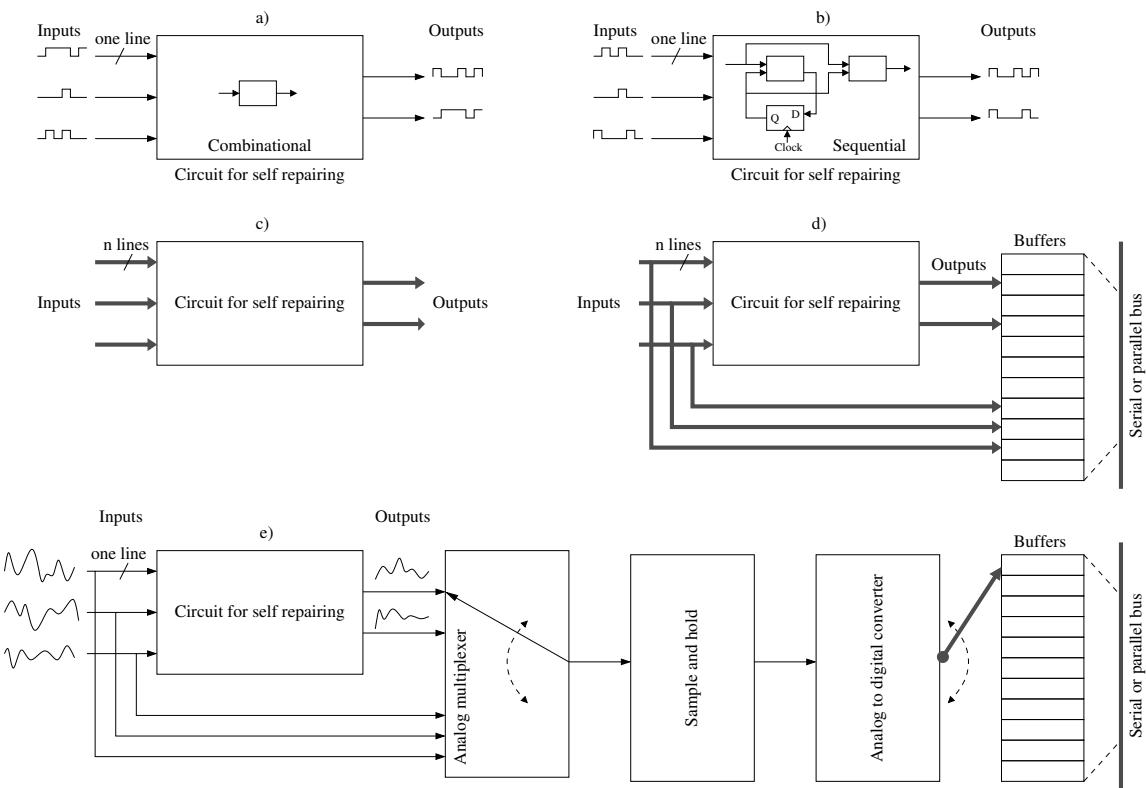

The human body recovers from illnesses and injury autonomously thanks to the immune system. The field of artificial immune systems transfers the biological principles of the immune system into models and algorithms for solving technical problems. This thesis makes use of some of those algorithms for the design of the fault recognition module, reason why in the title of this thesis immunorepairing is written instead of self-repairing. For the design of the fault recognition module, it is assumed initially the existence of a set of fault pattern vectors that address specific faults in the circuit. Each of those vectors has a recovery mechanism associated. A comparison of the vector containing the current state of the circuit with each of the fault pattern vectors in the available set is executed concurrently to the operation of the circuit using different vector distance metrics. Thereafter, the vector containing the current state of the circuit is classified based on the closest fault pattern vectors and a recovery mechanism is assigned to it if a fault is determined. Two kinds of hardware systems were recognized and taken into consideration: a hardware system with multiple line inputs and outputs and a hardware system with single line inputs and outputs. The inputs and outputs of the first one can be concatenated as vectors with real value elements expressed in fixed or floating point format. In the same way, the inputs and outputs of the second one can be concatenated as vectors with one-bit binary value elements. Hardware systems with multiple line inputs and outputs can be hardware cores that have n-bit floating point format input and output signals, or hardware systems that have input and output signals working with continuous values, such is the case of some sensor or actuator signals. Hardware systems with

single line inputs and outputs can be combinational or sequential digital systems.

In case of vectors with real value elements expressed in fixed or floating point format, the comparison of the vector containing the current state of the circuit with the stored set of fault pattern vectors is done using the Mahalanobis or the set of Minkowski distances. Thereafter, the assignment of a recovery mechanism is done using the k-nearest neighbor or the minimal distance classification methods. The performances of those methods depend on the size of the set of fault pattern vectors. That is, the number of fault pattern vectors and the number of elements in each vector, also called dimension. Therefore, in this thesis, methods for the reduction of the dimension of the fault pattern vectors are evaluated such us “Principal Component Analysis”, “Singular Value Decomposition” and “Formal Immune Networks”. Moreover, methods for the reduction of the number of fault pattern vectors are also evaluated such us “Death of immune cells with insufficient stimulation”, “Elimination of auto-reactive immune cells” and “Apoptosis and auto-immunization”. The methods that give the minimal number of incorrectly recognized faults, minimal dimension, and minimal number of fault pattern vectors, are the ones that are recommended to be employed in the design of the fault recognition module. Their use assures a low fault recognition latency and a low consumption of memory resources for storing the fault pattern vector set.

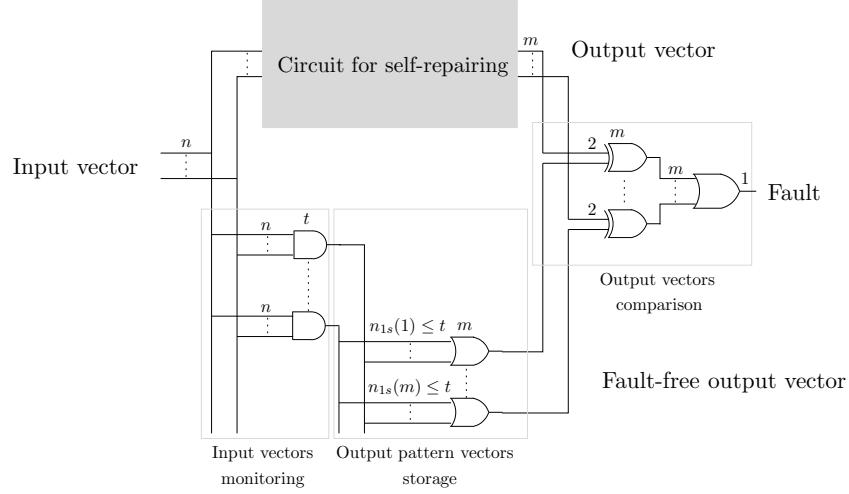

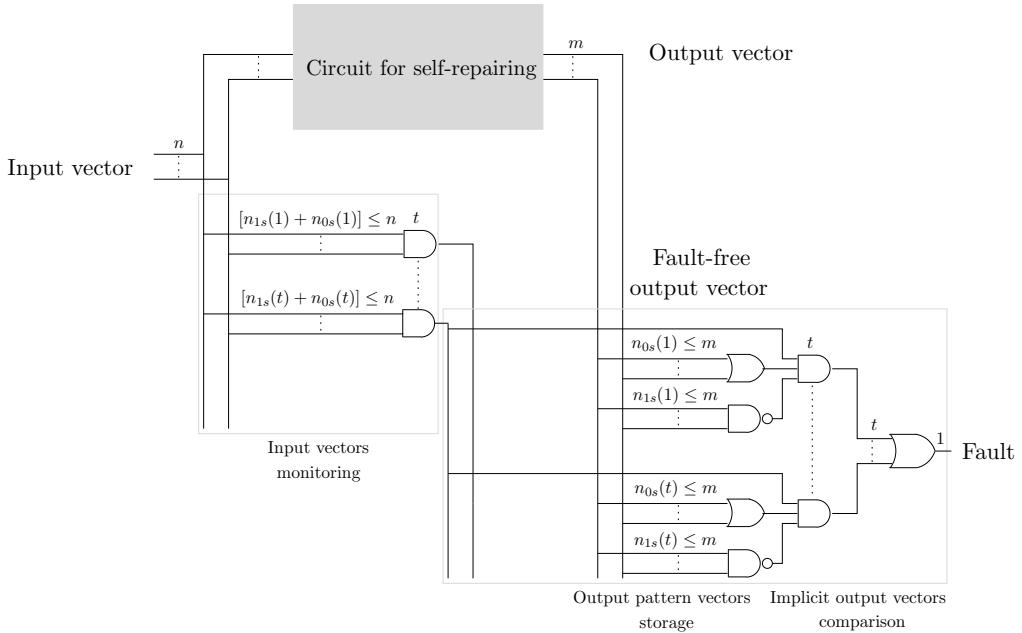

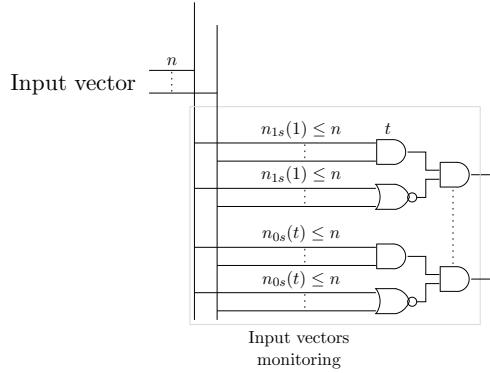

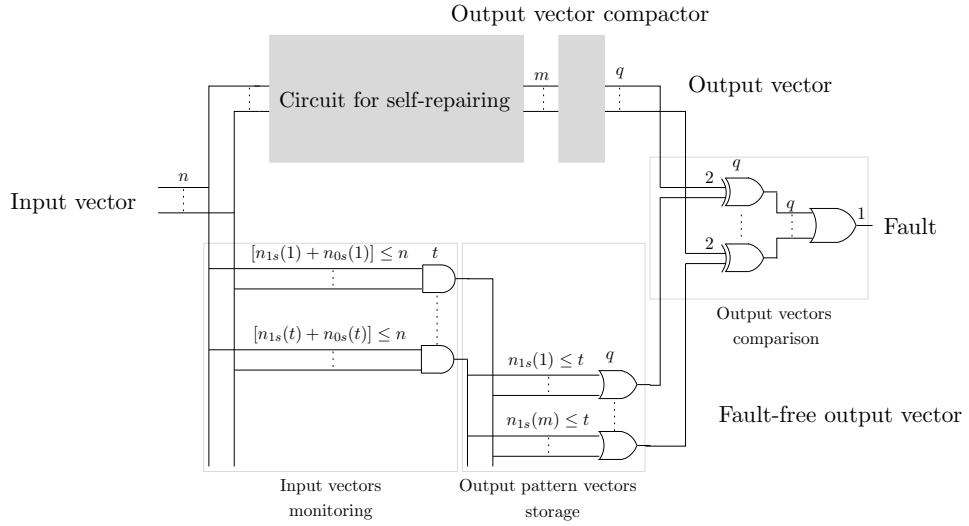

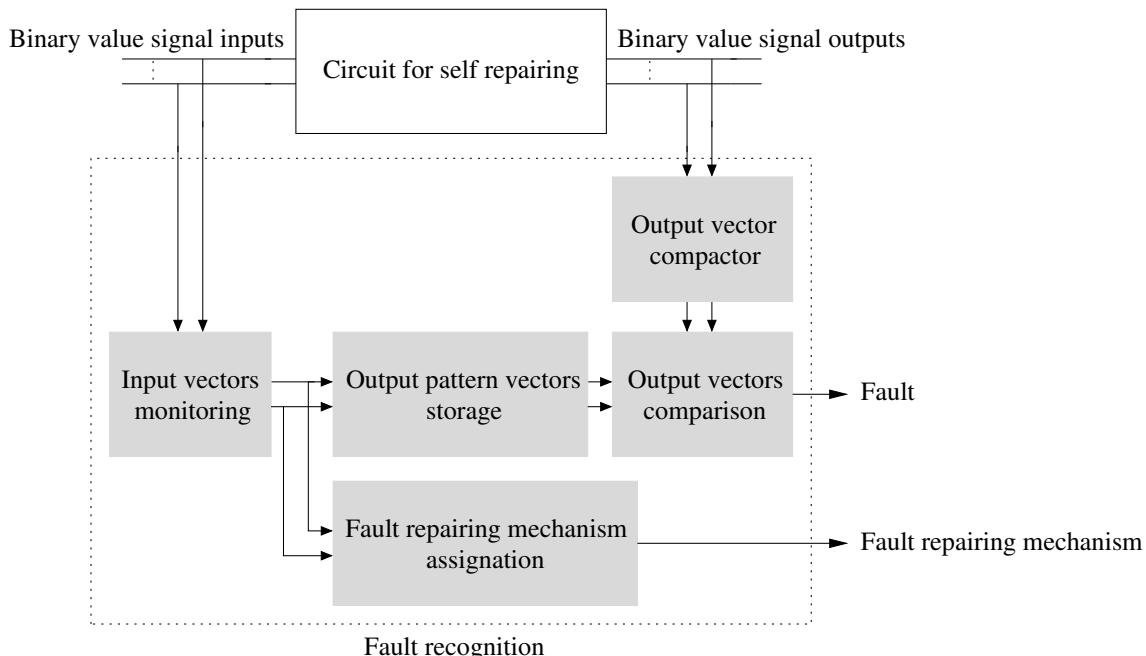

In case of vectors with one-bit binary value elements, the comparison of the vector containing the current state of the circuit with the stored set of fault pattern vectors can be done using the Hamming distance. Using that distance, the result is either zero or one, that is to say, either equal or unequal. When equal, the recovery mechanism associated to the fault pattern vector can be assigned to the vector containing the current state of the circuit in an straightforward manner, without using any classification method. The comparison of the vector containing the current state of the circuit with the stored set of fault pattern vectors is possible to be executed concurrently to the operation of the circuit, by monitoring firstly the current vector of inputs to the circuit. When the vector containing the current inputs matches one of the input vectors from the given fault pattern vectors, then, the vector of current outputs can be compared with the corresponding stored output pattern vector. Such a fault recognition module is comprised of an input vectors monitoring block, an output pattern vectors storage block, and an output vectors comparison block. The design of all those blocks can exploit the unspecified values in the elements of the fault pattern vectors in order to get a reduced hardware overhead. Furthermore, an output vector compactor block, at the output of the circuit, can be used for reducing the number of outputs to be compared, thereby reducing the hardware overhead produced by the output pattern vectors storage block.

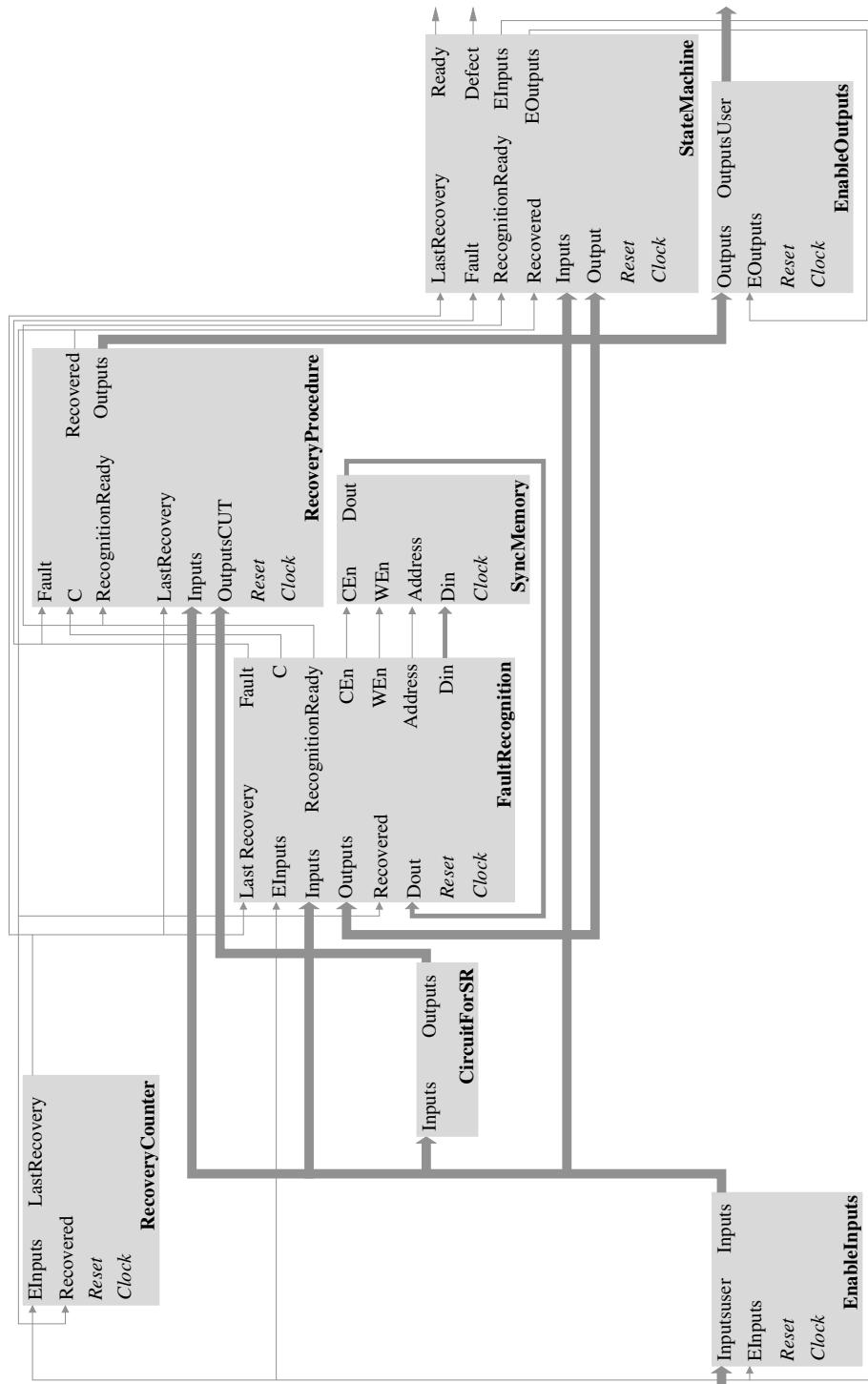

Besides the fault recognition module, the self-repairing hardware system requires a recovery procedure module and other supporting modules such as: a controller, enablers of inputs and outputs, a reconfiguration controller for recovery, etc. A modular architecture of a self-repairing hardware system with all those modules is outlined and described in this thesis at the register transfer level using the hardware description language VHDL. The delivered description intends to provide ready to use modules for designing self-repairing hardware systems, and it is a further step towards the automatic design of self-repairing circuits described at the RTL level. The controller and enablers of inputs and outputs help on driving the outputs of the circuit to a safe value, while executing fault recognition and recovery and in case of determining an unrecoverable defect after unsuccessful recoveries. The description also includes a fault injector for debugging or testing the whole system injecting stuck-at faults. That architecture has been implemented and tested for the design of a self-repairing combinational circuit that uses as recovery mechanisms the switching to redundant modules

and the partial reconfiguration of the circuit. The self-repairing combinational circuit has been successfully synthesized and implemented into an FPGA hardware platform.

---

# Acknowledgments

I would like to thank my supervisor Prof. Franz J. Rammig for the opportunity that he gave me to work in his workgroup “Design of Distributed Embedded Systems” at the Heinz Nixdorf Institute in Paderborn with the objective of writing this dissertation, specially in the writing phase for the proofreading and his patience. I would also like to thank Prof. Sybille Hellebrand for her precise advice during the realization of this dissertation, I really appreciate the bibliographical sources and tools that she suggested me to use and refer to, and her patience with me. I want to thank also my colleague Sebastian Hagenkötter for providing data to test experimentally the algorithms and the work we did together. Finally, I want to acknowledge the members of the examination board Prof. Marco Platzner, Prof. Hans Kleine Büning and Dr. Matthias Fischer for evaluating my work.

---

# Contents

|                                                                                 |             |

|---------------------------------------------------------------------------------|-------------|

| <b>List of figures</b>                                                          | <b>xi</b>   |

| <b>List of tables</b>                                                           | <b>xv</b>   |

| <b>List of algorithms</b>                                                       | <b>xvii</b> |

| <b>List of program codes</b>                                                    | <b>xix</b>  |

| <b>1 Introduction</b>                                                           | <b>1</b>    |

| 1.1 Objectives of this work . . . . .                                           | 1           |

| 1.2 Strategy . . . . .                                                          | 2           |

| 1.3 Organization of this work . . . . .                                         | 4           |

| 1.4 Bibliography . . . . .                                                      | 6           |

| <b>2 Related work</b>                                                           | <b>7</b>    |

| 2.1 Self-repairing hardware . . . . .                                           | 7           |

| 2.1.1 Multifunctional units . . . . .                                           | 8           |

| 2.1.2 Dynamic partial reconfiguration for testing and repair . . . . .          | 8           |

| 2.1.3 Distributed self-repairing of a network of FPGA nodes . . . . .           | 9           |

| 2.1.4 Small-scale reconfigurability for fault detection, diagnosis and recovery | 10          |

| 2.1.5 Logic self-repair . . . . .                                               | 11          |

| 2.1.6 Dual-FPGA architecture for autonomous self-repair . . . . .               | 12          |

| 2.2 Self-repairing approaches inspired by biological systems . . . . .          | 13          |

| 2.2.1 Immune system paradigm . . . . .                                          | 13          |

| 2.2.2 POEtic tissue . . . . .                                                   | 14          |

| 2.2.3 Evolvable hardware . . . . .                                              | 14          |

| 2.2.4 Embryonics . . . . .                                                      | 16          |

| 2.2.5 Immunotronics . . . . .                                                   | 16          |

| 2.2.6 e-DNA . . . . .                                                           | 17          |

| 2.2.7 Autonomic System on Chip . . . . .                                        | 18          |

| 2.2.8 Immunocomputing . . . . .                                                 | 19          |

| 2.3 Self-repairing in FPGAs . . . . .                                           | 20          |

| 2.3.1 Roving STAR . . . . .                                                     | 20          |

| 2.3.2 TMR + RoRA . . . . .                                                      | 20          |

| 2.4 Self-repairing introduced at the hardware description . . . . .             | 21          |

| 2.4.1 Automatic insertion of fault tolerant structures in the RTL description   | 21          |

|          |                                                                    |            |

|----------|--------------------------------------------------------------------|------------|

| 2.5      | Comments . . . . .                                                 | 21         |

| 2.5.1    | Hardware level of abstraction . . . . .                            | 21         |

| 2.5.2    | Hardware platform for the implementation . . . . .                 | 22         |

| 2.5.3    | Type of addressed fault . . . . .                                  | 23         |

| 2.5.4    | Error detection technique . . . . .                                | 23         |

| 2.5.5    | Recovery mechanism . . . . .                                       | 24         |

| 2.6      | Bibliography . . . . .                                             | 25         |

| <b>3</b> | <b>Artificial immune systems</b>                                   | <b>33</b>  |

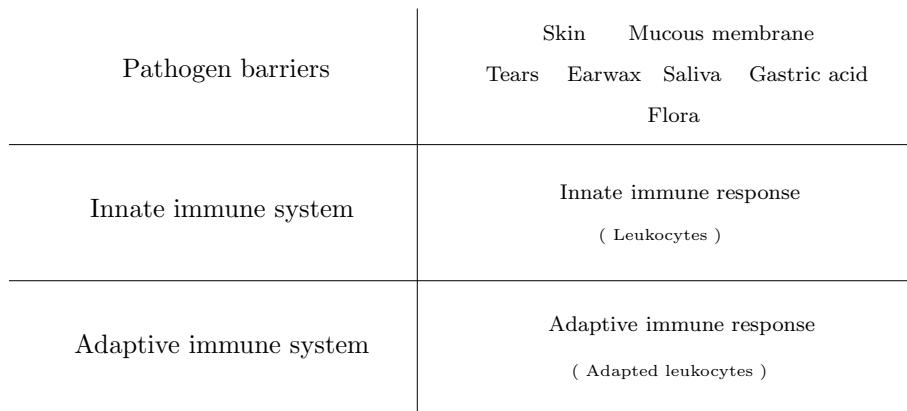

| 3.1      | Biological immune system . . . . .                                 | 34         |

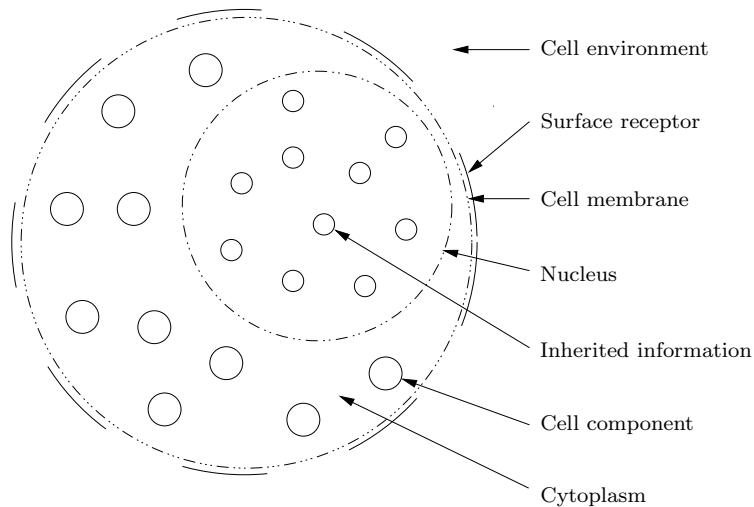

| 3.1.1    | Internal agents . . . . .                                          | 35         |

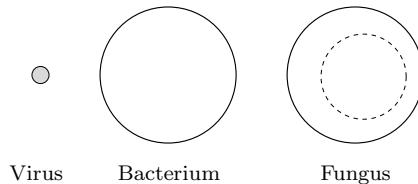

| 3.1.2    | External agents . . . . .                                          | 36         |

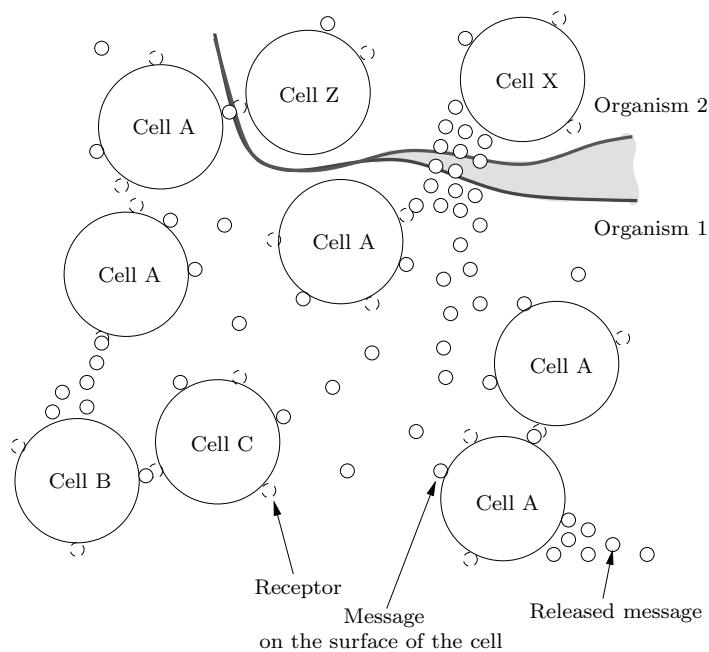

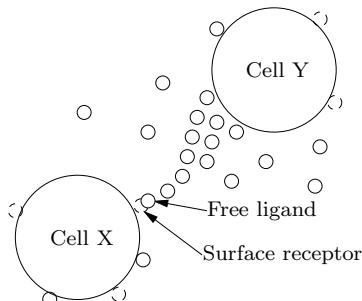

| 3.1.3    | Communication among agents . . . . .                               | 38         |

| 3.1.4    | Immune system infrastructure . . . . .                             | 54         |

| 3.1.5    | Immune system agents . . . . .                                     | 56         |

| 3.2      | Artificial immune system models and algorithms . . . . .           | 67         |

| 3.2.1    | Positive and negative selection . . . . .                          | 67         |

| 3.2.2    | Clonal selection . . . . .                                         | 68         |

| 3.2.3    | Immune network . . . . .                                           | 72         |

| 3.2.4    | Dendritic cells . . . . .                                          | 79         |

| 3.2.5    | Formal immune network . . . . .                                    | 83         |

| 3.3      | Comparison of artificial immune algorithms . . . . .               | 85         |

| 3.4      | Bibliography . . . . .                                             | 85         |

| <b>4</b> | <b>Fault recognition</b>                                           | <b>87</b>  |

| 4.1      | Fault representation . . . . .                                     | 88         |

| 4.2      | Fault recognition . . . . .                                        | 91         |

| 4.3      | Fault repairing mechanisms assignation . . . . .                   | 93         |

| 4.4      | Fault space partitioning . . . . .                                 | 95         |

| 4.5      | Fault recognition time . . . . .                                   | 96         |

| 4.6      | Fault vector dimension reduction . . . . .                         | 97         |

| 4.6.1    | Principal component analysis . . . . .                             | 98         |

| 4.6.2    | Singular value decomposition . . . . .                             | 103        |

| 4.7      | Fault pattern vectors number reduction . . . . .                   | 107        |

| 4.7.1    | Death of immune cells with insufficient stimulation . . . . .      | 108        |

| 4.7.2    | Elimination of auto-reactive immune cells . . . . .                | 108        |

| 4.8      | Cytokine formal immune network . . . . .                           | 110        |

| 4.8.1    | Protein-protein interaction formal model . . . . .                 | 111        |

| 4.8.2    | Formal immune network . . . . .                                    | 113        |

| 4.8.3    | Molecular recognition . . . . .                                    | 116        |

| 4.8.4    | Cytokine formal immune network . . . . .                           | 117        |

| 4.8.5    | Apoptosis and auto-immunization . . . . .                          | 119        |

| 4.9      | Conclusions . . . . .                                              | 121        |

| 4.10     | Bibliography . . . . .                                             | 122        |

| <b>5</b> | <b>Evaluation of fault recognition methods</b>                     | <b>123</b> |

| 5.1      | Fault recognition module with real fault vector elements . . . . . | 124        |

*Contents*

|                             |                                                                      |            |

|-----------------------------|----------------------------------------------------------------------|------------|

| 5.1.1                       | Fault recognition . . . . .                                          | 126        |

| 5.1.2                       | Fault vector dimension reduction . . . . .                           | 131        |

| 5.1.3                       | Fault pattern vectors number reduction . . . . .                     | 147        |

| 5.2                         | Fault recognition module with binary fault vector elements . . . . . | 169        |

| 5.2.1                       | Fault recognition . . . . .                                          | 171        |

| 5.2.2                       | Fault pattern vectors number reduction . . . . .                     | 174        |

| 5.2.3                       | Fault vector dimension reduction . . . . .                           | 178        |

| 5.3                         | Conclusions . . . . .                                                | 190        |

| 5.4                         | Bibliography . . . . .                                               | 191        |

| <b>6</b>                    | <b>Implementation of a self-repairing unit</b>                       | <b>195</b> |

| 6.1                         | Design of the self-repairing unit . . . . .                          | 196        |

| 6.1.1                       | Initial architecture of the self-repairing unit . . . . .            | 196        |

| 6.1.2                       | Partial reconfiguration for recovering the unit . . . . .            | 219        |

| 6.1.3                       | Fault injection for testing the self-repairing unit . . . . .        | 228        |

| 6.2                         | Simulation of the self-repairing unit . . . . .                      | 245        |

| 6.3                         | Implementation of the self-repairing unit . . . . .                  | 252        |

| 6.4                         | Performance of the self-repairing unit . . . . .                     | 257        |

| 6.5                         | Conclusions . . . . .                                                | 258        |

| 6.6                         | Bibliography . . . . .                                               | 259        |

| <b>7</b>                    | <b>Major contributions and further work</b>                          | <b>263</b> |

| 7.1                         | Major contributions . . . . .                                        | 263        |

| 7.2                         | Further work . . . . .                                               | 265        |

| 7.3                         | Bibliography . . . . .                                               | 266        |

| <b>List of publications</b> |                                                                      | <b>267</b> |

| <b>Bibliography</b>         |                                                                      | <b>269</b> |

*Contents*

---

# List of Figures

|      |                                                                           |    |

|------|---------------------------------------------------------------------------|----|

| 1.1  | Self-repairing circuit                                                    | 3  |

| 1.2  | Built-In Concurrent Self-Test [Sharma and Saluja, 1988]                   | 3  |

| 1.3  | Self-repairing architecture                                               | 5  |

| 1.4  | LOC and peripheral elements [Marinos, 1969]                               | 5  |

| 2.1  | LOC and peripheral elements [Marinos, 1969]                               | 8  |

| 2.2  | Partial reconfigurable regions as slots [Paulsson et al., 2006a]          | 9  |

| 2.3  | Subcomponent self-repairing [Akoglu et al., 2009]                         | 10 |

| 2.4  | Cone-level fault detection, diagnosis and recovery [Kumar and Lach, 2003] | 11 |

| 2.5  | POEtic layers [Tyrell et al., 2003]                                       | 15 |

| 2.6  | Self-repairing in an array with spare components [Tempesti et al., 1997]  | 16 |

| 2.7  | Immunotronics plus Embryonics concept [Bradley et al., 2000]              | 18 |

| 2.8  | Layers of the Autonomic System on Chip [Bouajila et al., 2006]            | 19 |

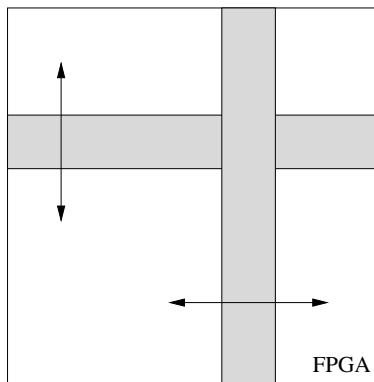

| 2.9  | FPGA with roving STAR [Abramovici et al., 2001]                           | 20 |

| 2.10 | New design flow using TMR and RoRA [Serpone and Violante, 2005]           | 21 |

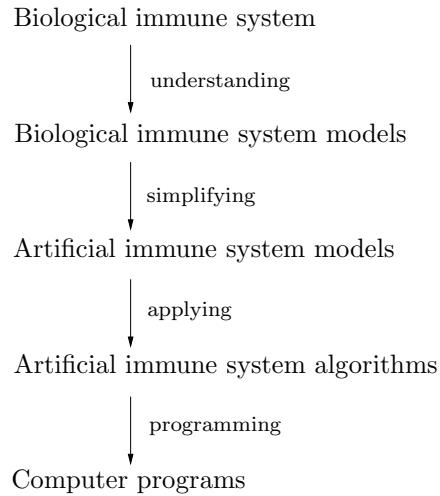

| 3.1  | Artificial immune systems flow                                            | 34 |

| 3.2  | Cell parts                                                                | 35 |

| 3.3  | Types of pathogens                                                        | 37 |

| 3.4  | Layers of protection in the human immune system                           | 37 |

| 3.5  | Cell communication                                                        | 39 |

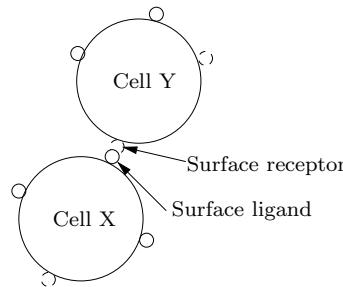

| 3.6  | Cell surface receptor and free ligand interaction                         | 39 |

| 3.7  | Cell surface receptor and cell surface ligand interaction                 | 40 |

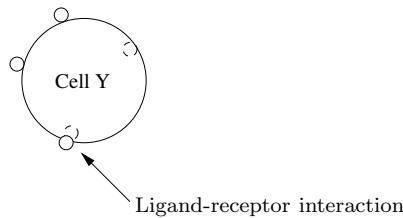

| 3.8  | Ligand-receptor interaction                                               | 40 |

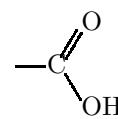

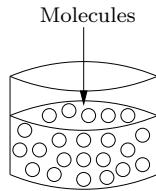

| 3.9  | Molecules in a chemical substance                                         | 41 |

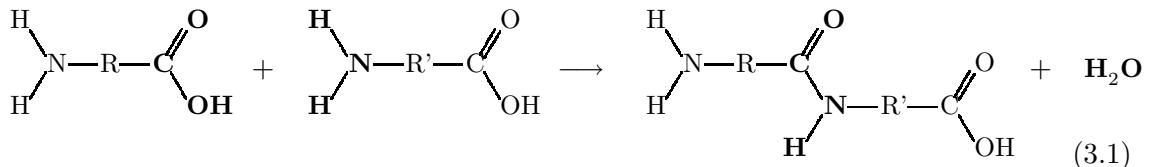

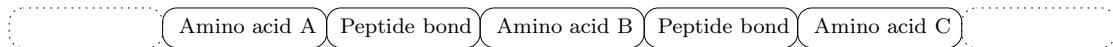

| 3.10 | Primary structure of a protein                                            | 41 |

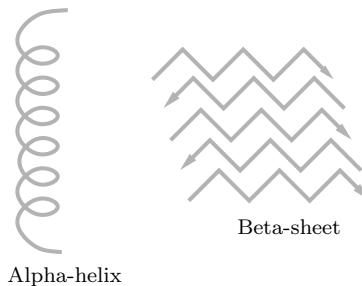

| 3.11 | Secondary structure of a protein                                          | 41 |

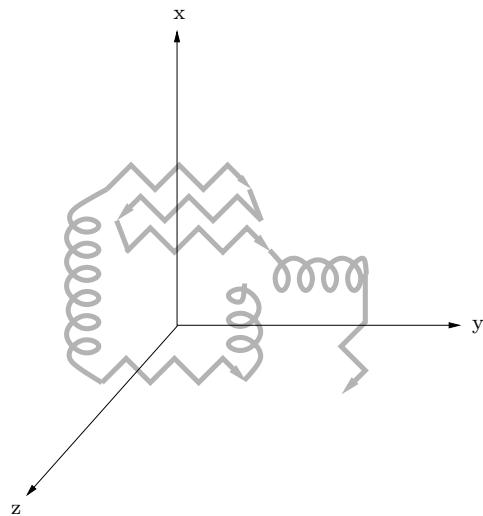

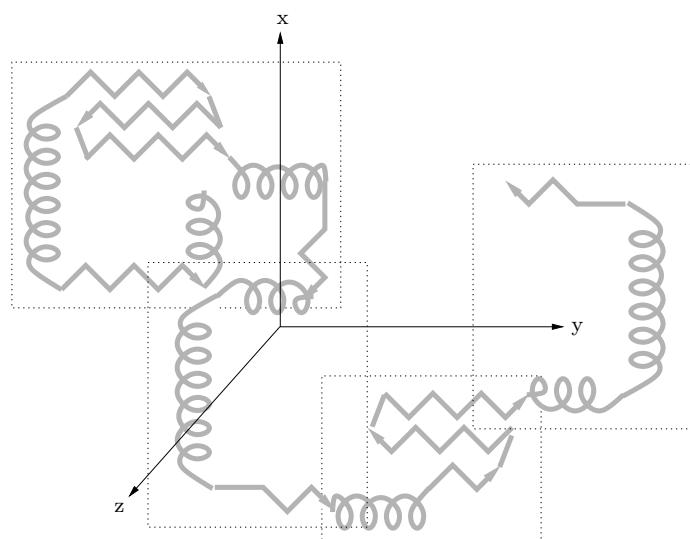

| 3.12 | Tertiary structure of a protein                                           | 42 |

| 3.13 | Quaternary structure of a protein                                         | 42 |

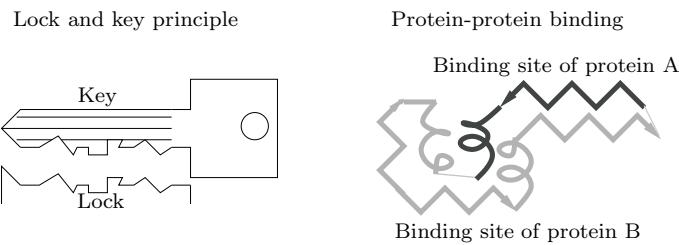

| 3.14 | Lock and key principle and protein-protein binding analogy                | 43 |

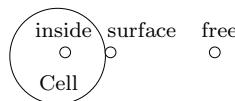

| 3.15 | Name conventions for binding sites                                        | 44 |

| 3.16 | Ligand placement                                                          | 44 |

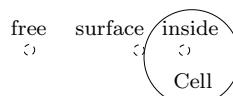

| 3.17 | Receptor placement                                                        | 47 |

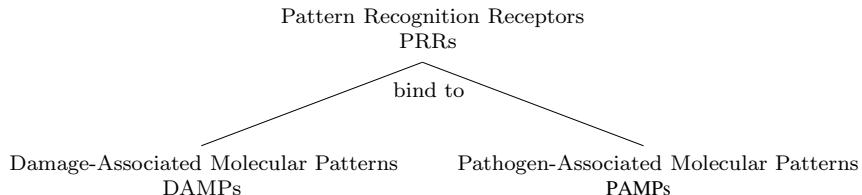

| 3.18 | PRRs, DAMPs and PAMPs                                                     | 48 |

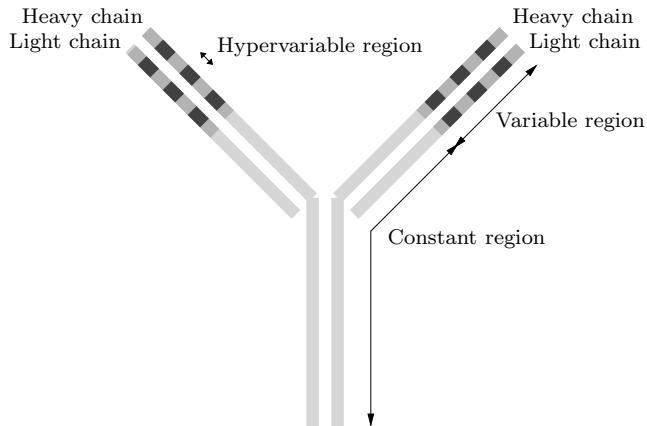

| 3.19 | B-cell receptor                                                           | 50 |

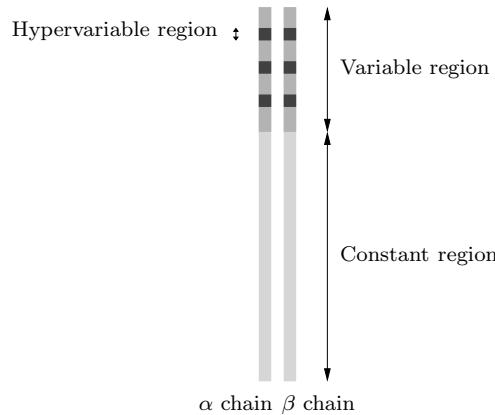

| 3.20 | T-cell receptor                                                           | 51 |

|      |                                                                                     |     |

|------|-------------------------------------------------------------------------------------|-----|

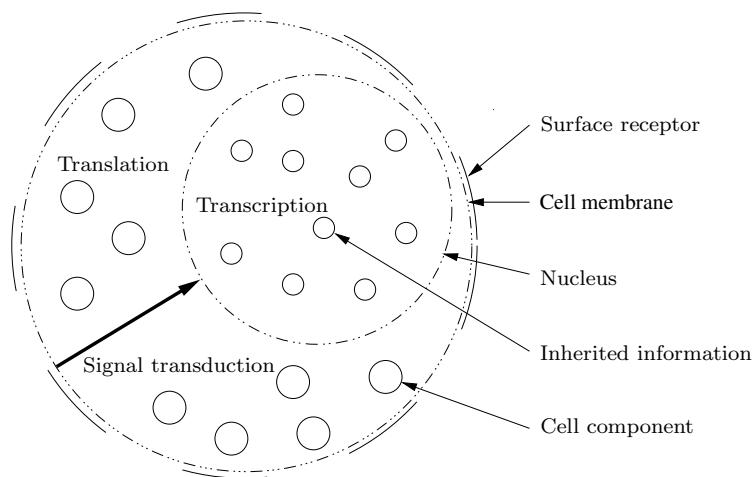

| 3.21 | Signal transduction, transcription and translation . . . . .                        | 52  |

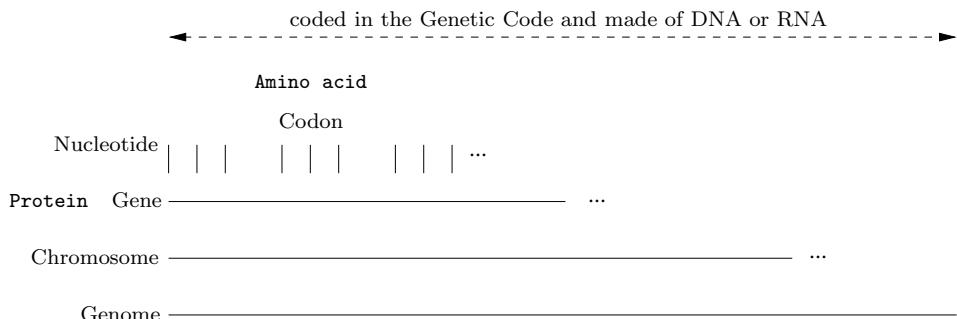

| 3.22 | Genetic material . . . . .                                                          | 53  |

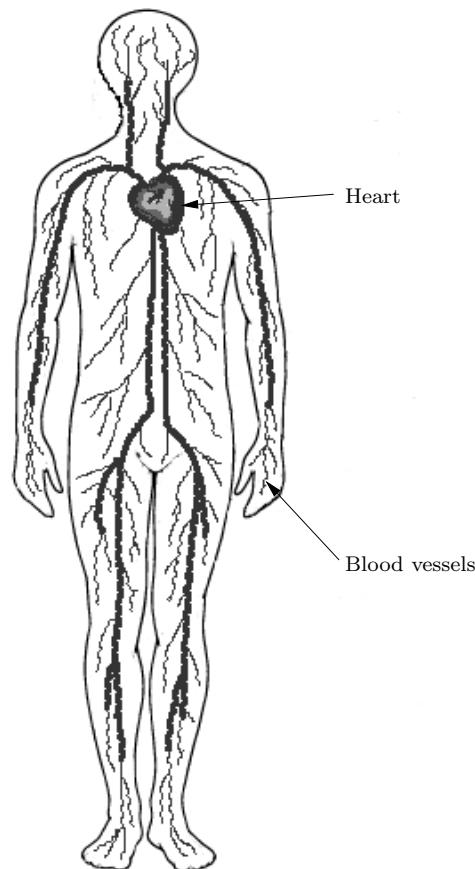

| 3.23 | Cardiovascular system . . . . .                                                     | 54  |

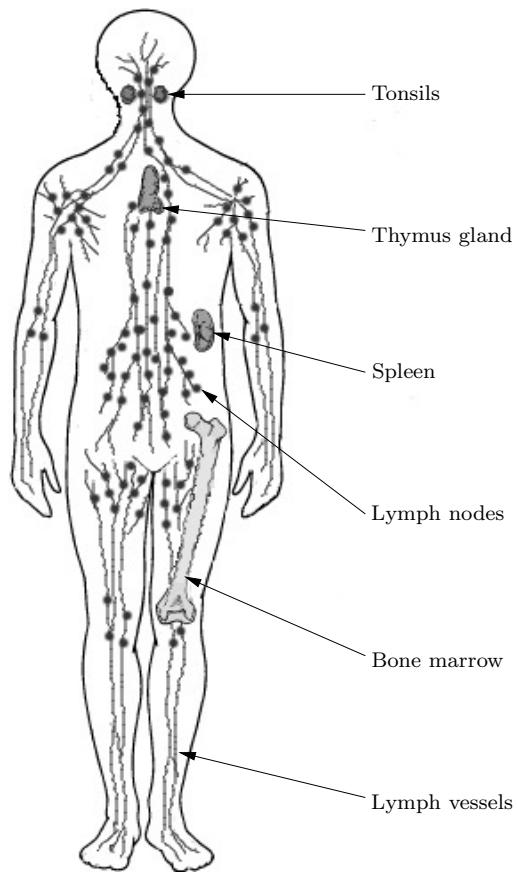

| 3.24 | Lymphatic system . . . . .                                                          | 55  |

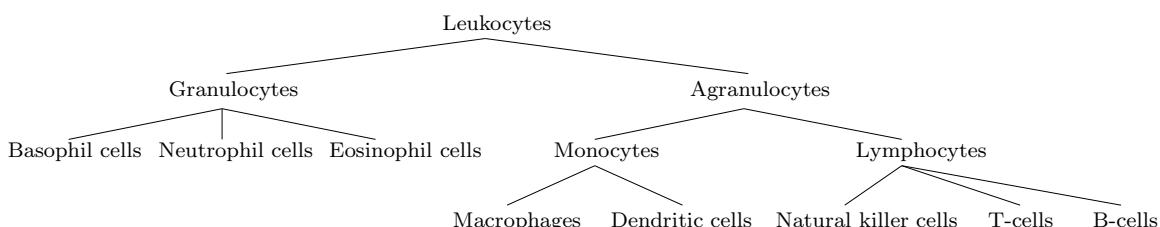

| 3.25 | Leukocyte classification . . . . .                                                  | 56  |

| 3.26 | Leukocytes in the innate and adaptive immune response . . . . .                     | 57  |

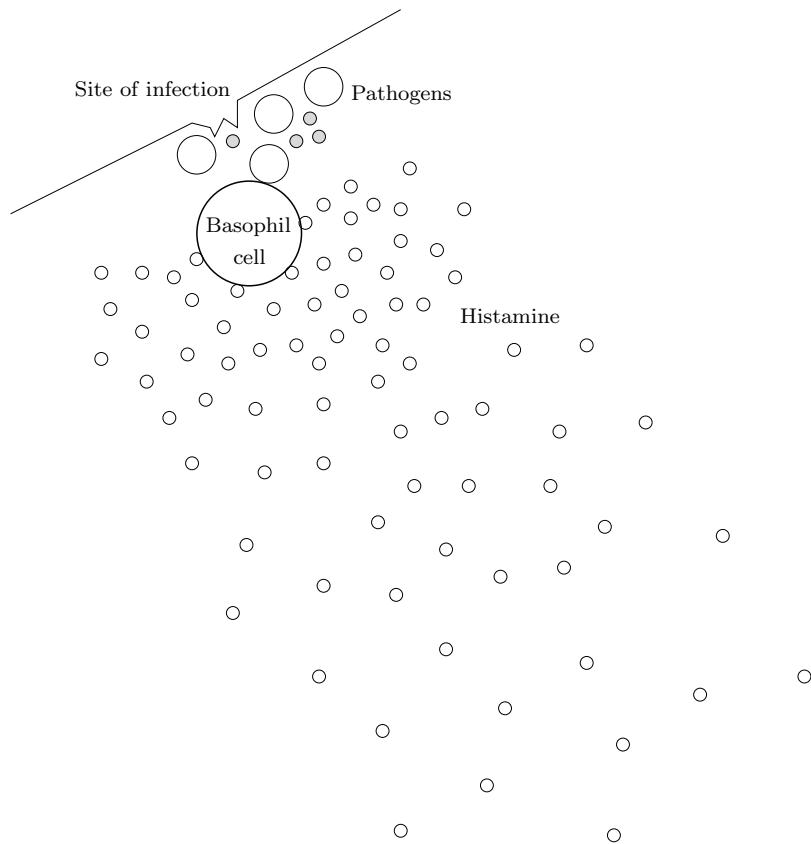

| 3.27 | Basophil cell releases histamine for attracting other leukocytes . . . . .          | 57  |

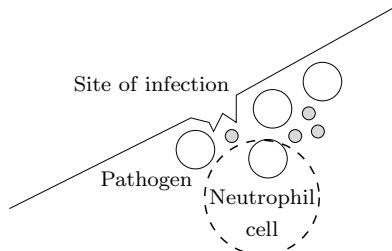

| 3.28 | Neutrophil cell engulfs pathogen and dies . . . . .                                 | 58  |

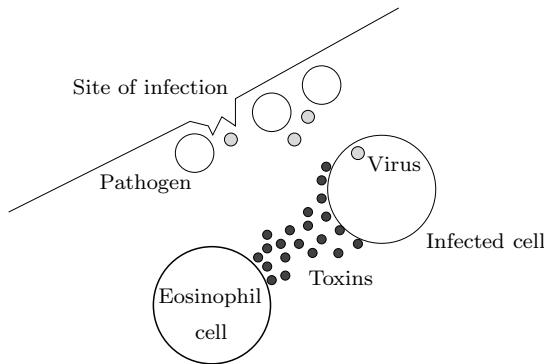

| 3.29 | Eosinophil cell releases toxins for killing infected cell . . . . .                 | 58  |

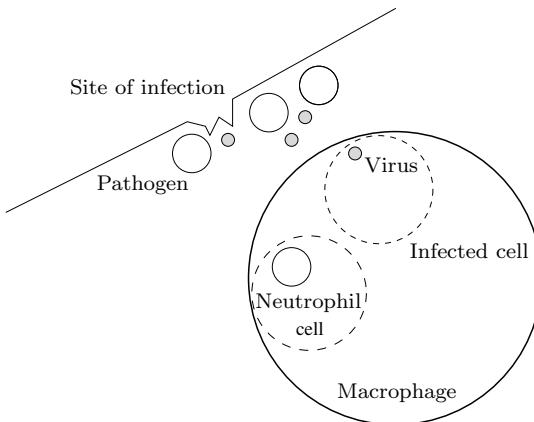

| 3.30 | Macrophage cell removes dead cells . . . . .                                        | 59  |

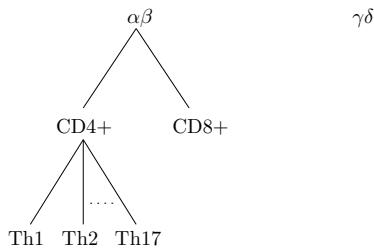

| 3.31 | T-cell classification . . . . .                                                     | 62  |

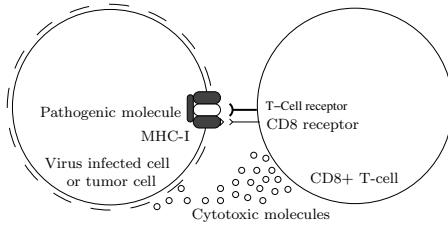

| 3.32 | Pathogen - cell - CD8+ T-cell . . . . .                                             | 62  |

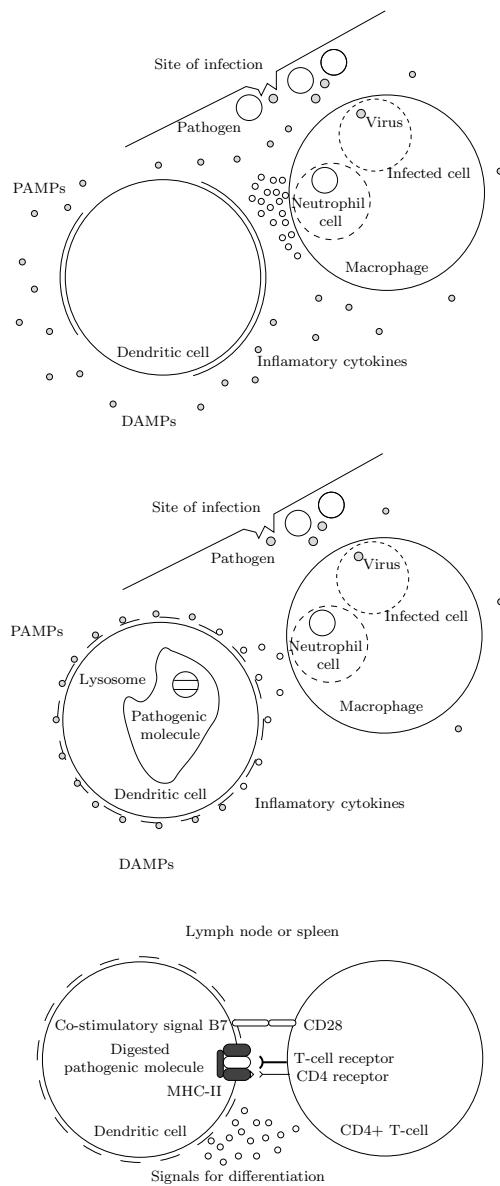

| 3.33 | Pathogen - dendritic cell - CD4+ T-cell . . . . .                                   | 63  |

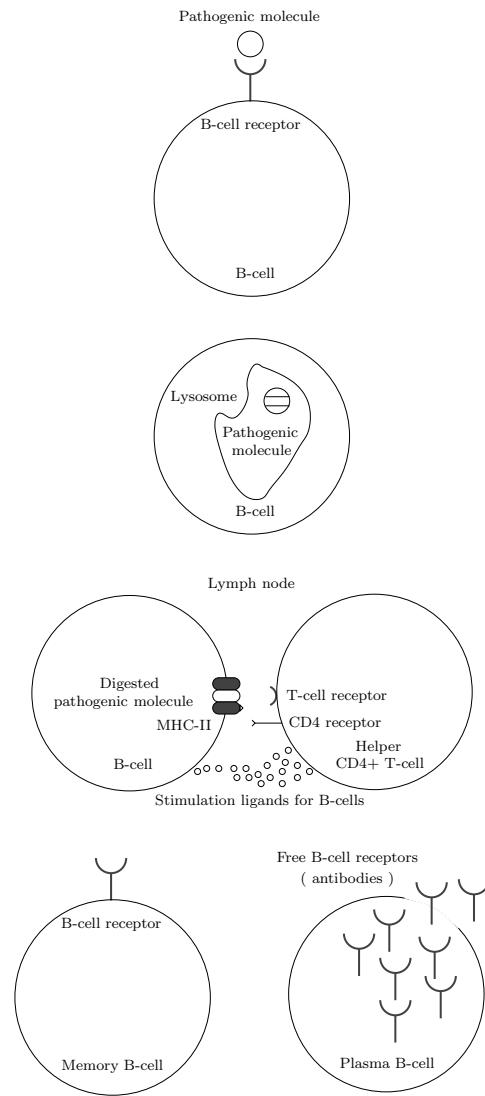

| 3.34 | Pathogen - B-cell - helper CD4+ T-cell . . . . .                                    | 66  |

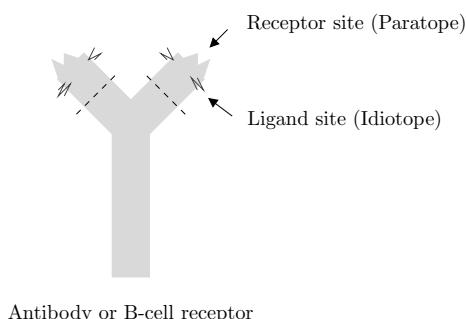

| 3.35 | Idiotope . . . . .                                                                  | 73  |

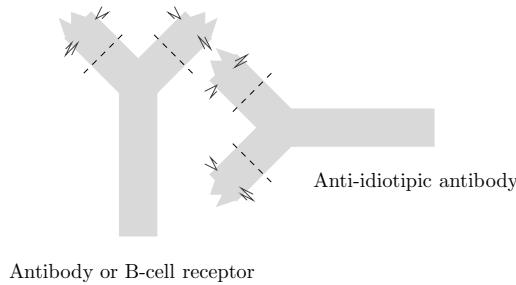

| 3.36 | Anti-idiotopic antibody . . . . .                                                   | 74  |

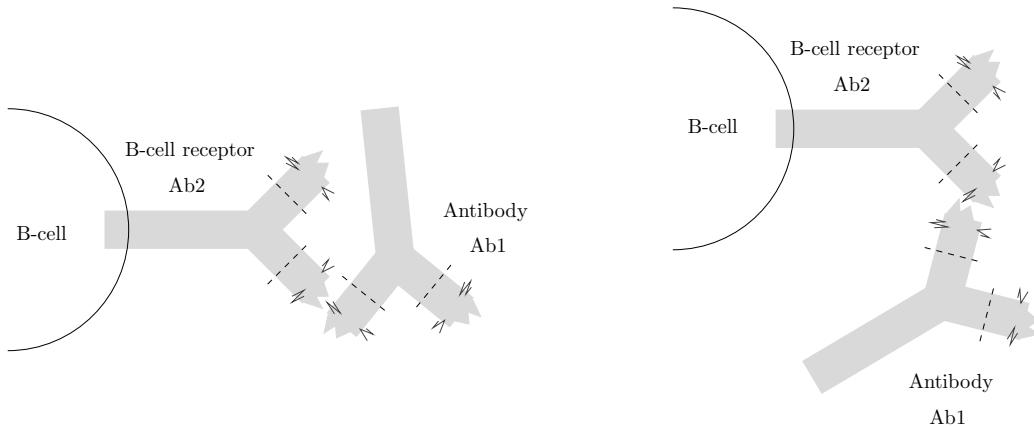

| 3.37 | Idiotope-paratope interaction . . . . .                                             | 74  |

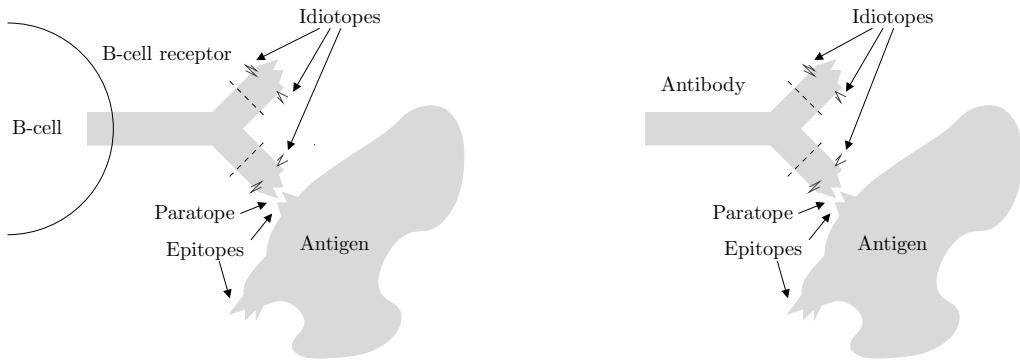

| 3.38 | Epitope-paratope interaction . . . . .                                              | 76  |

| 4.1  | Inputs and outputs of the fault recognition module . . . . .                        | 88  |

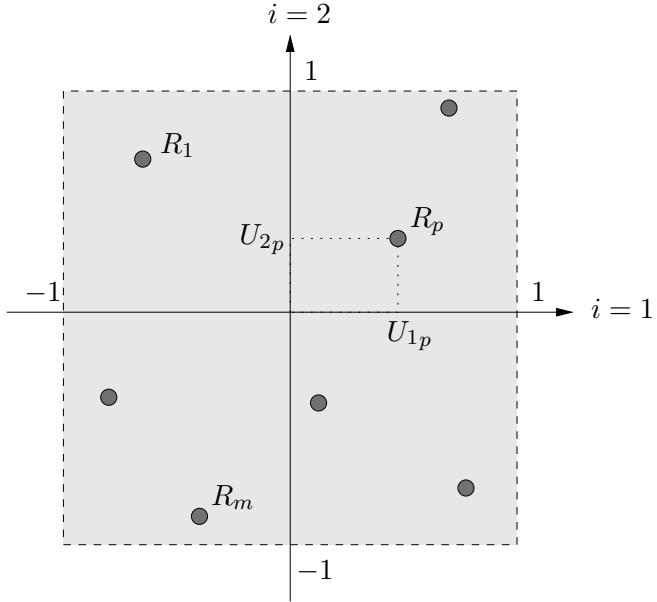

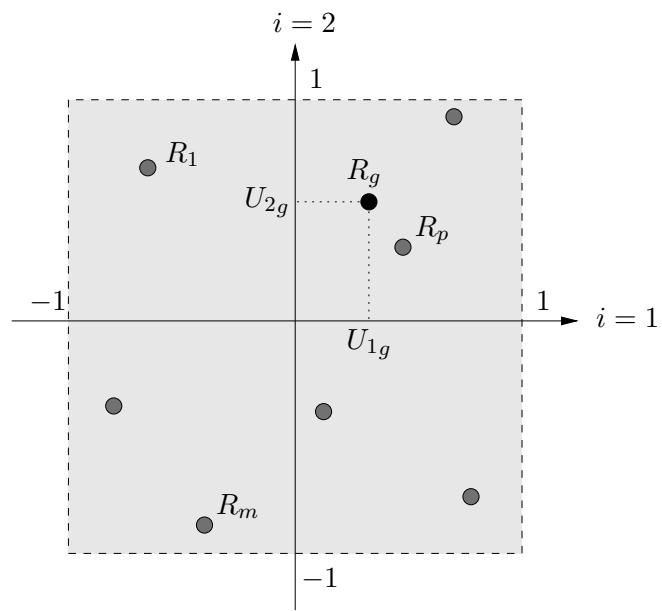

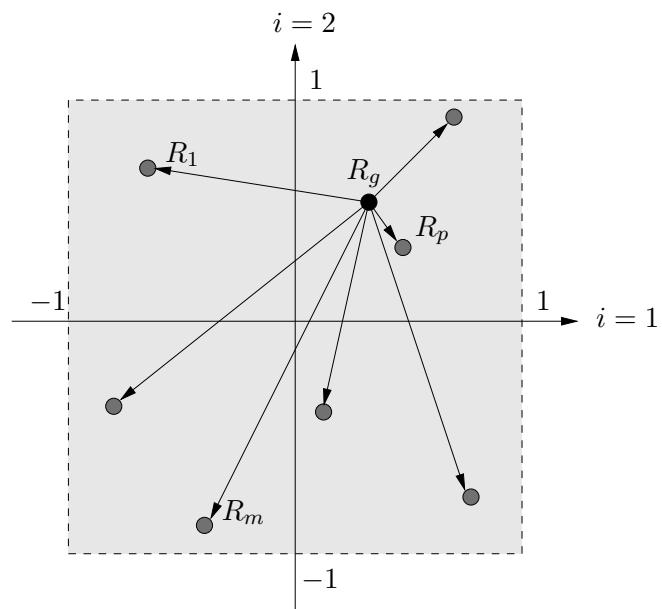

| 4.2  | Fault vector in a two dimensional space . . . . .                                   | 88  |

| 4.3  | Possibilities of inputs and outputs of the circuit for self repairing - 1 . . . . . | 90  |

| 4.4  | Possibilities of inputs and outputs of the circuit for self repairing - 2 . . . . . | 90  |

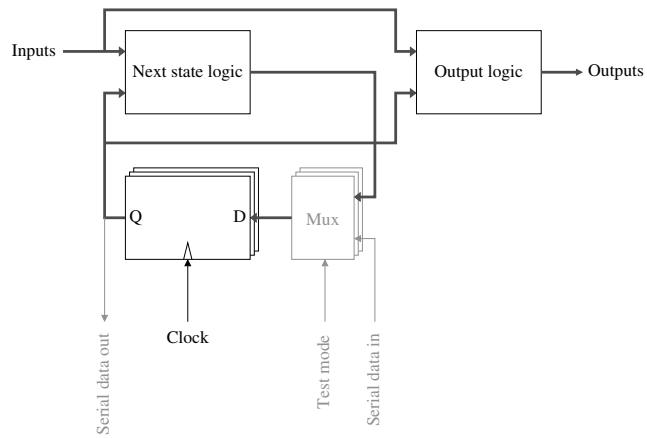

| 4.5  | Scan design of a sequential circuit . . . . .                                       | 91  |

| 4.6  | Similarity of a given fault vector and a fault pattern vector . . . . .             | 92  |

| 4.7  | k-nearest neighbor procedure . . . . .                                              | 94  |

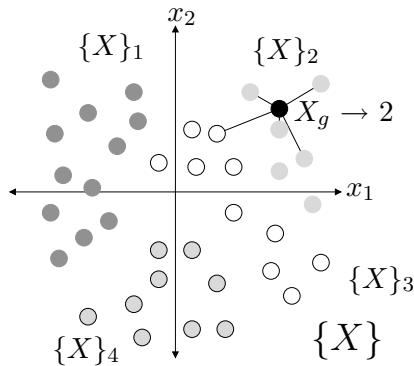

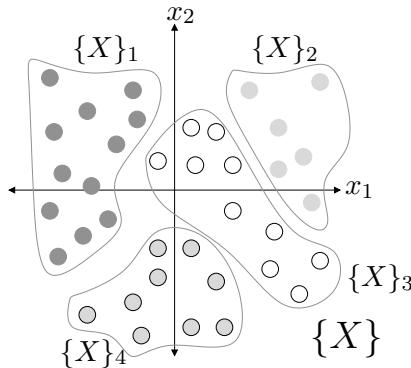

| 4.8  | Partitioning of a two dimensional space in subspaces . . . . .                      | 95  |

| 4.9  | Total time required before a repairing mechanism can be executed . . . . .          | 96  |

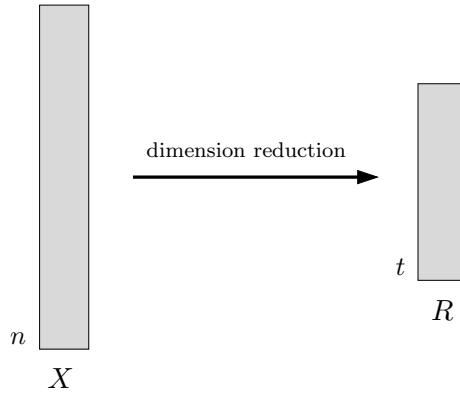

| 4.10 | Dimension reduction of a vector . . . . .                                           | 97  |

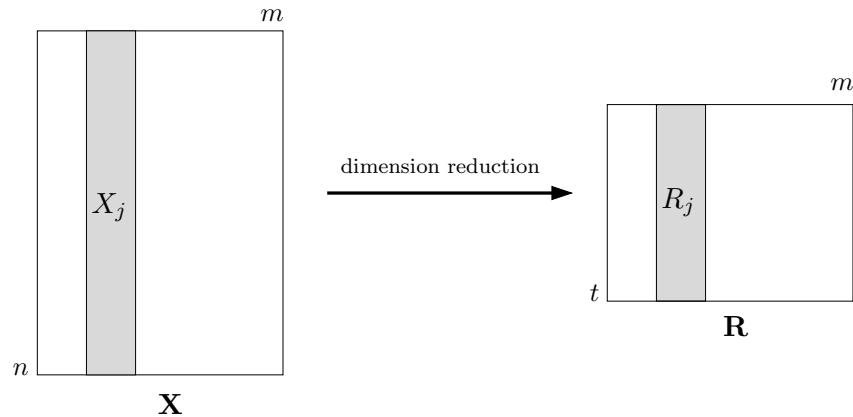

| 4.11 | Dimension reduction of a matrix . . . . .                                           | 97  |

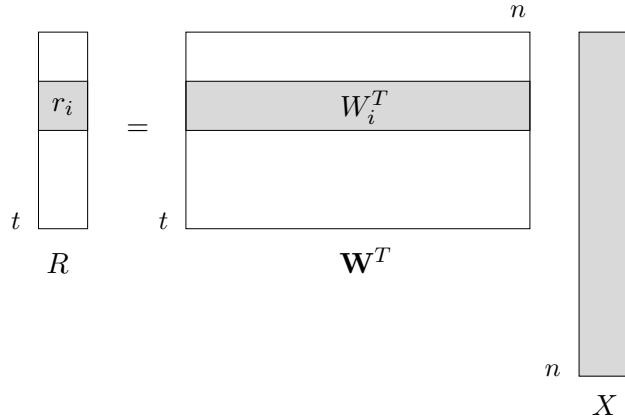

| 4.12 | Linear transformation of a vector . . . . .                                         | 98  |

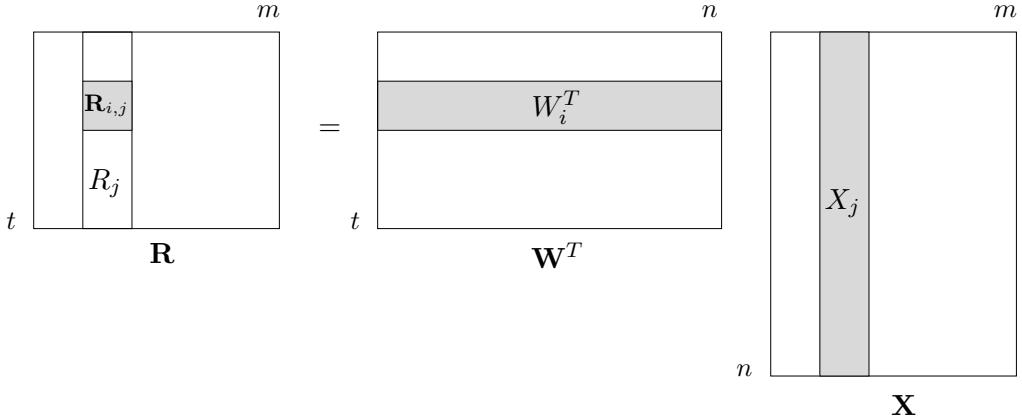

| 4.13 | Linear transformation of a matrix . . . . .                                         | 99  |

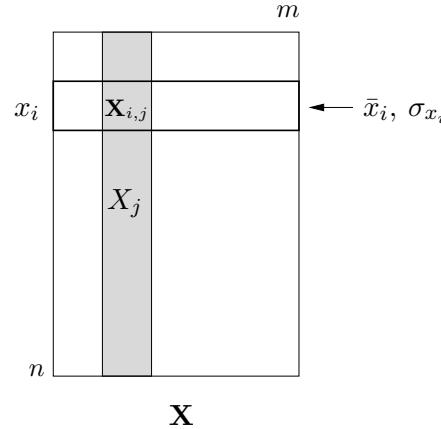

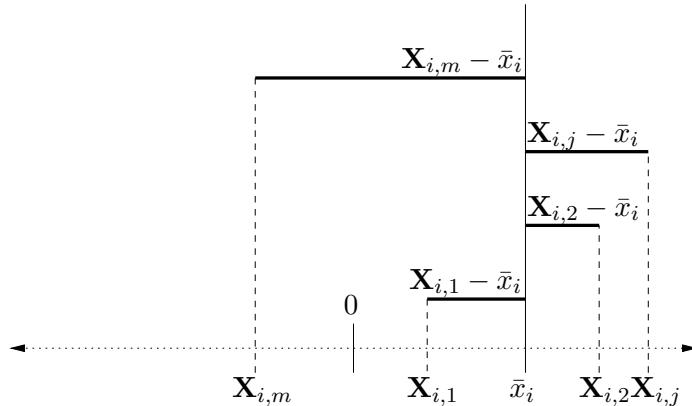

| 4.14 | Mean and standard deviation of fault pattern vector components in a matrix          | 100 |

| 4.15 | Deviation of fault pattern vector components from the mean . . . . .                | 100 |

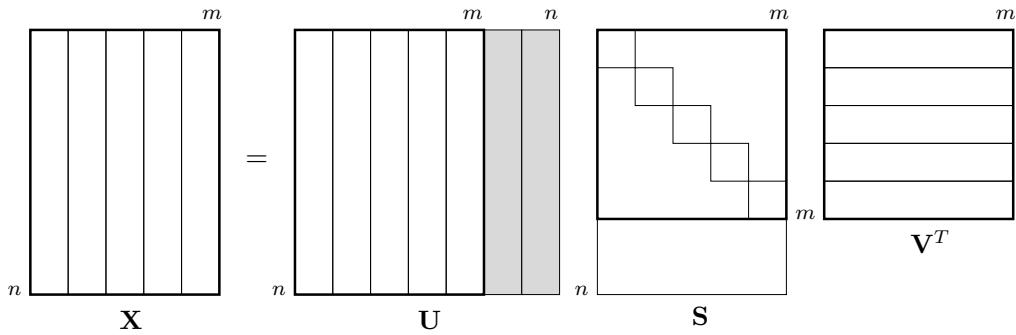

| 4.16 | Singular value decomposition of a matrix with $n > m$ . . . . .                     | 105 |

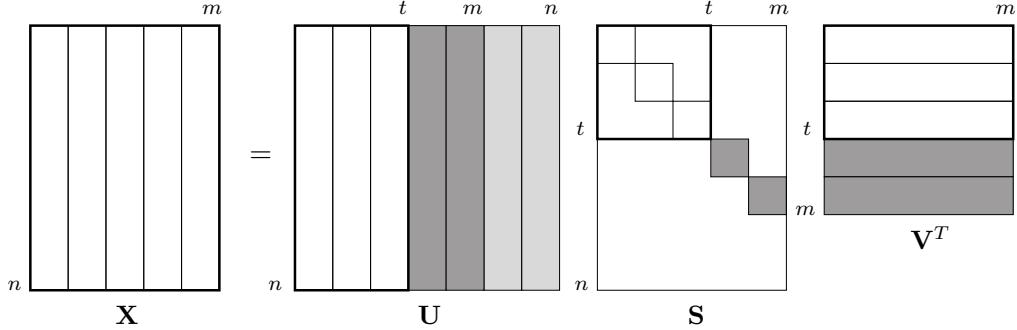

| 4.17 | Singular value decomposition of a matrix with $n < m$ . . . . .                     | 106 |

| 4.18 | Truncated singular value decomposition of a matrix with $n < m$ . . . . .           | 107 |

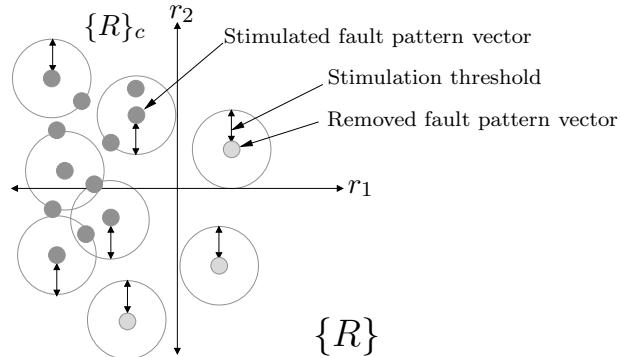

| 4.19 | Reduction of fault pattern vectors through insufficient stimulation . . . . .       | 109 |

| 4.20 | Reduction of fault pattern vectors through auto-reactive immune cells . . . . .     | 109 |

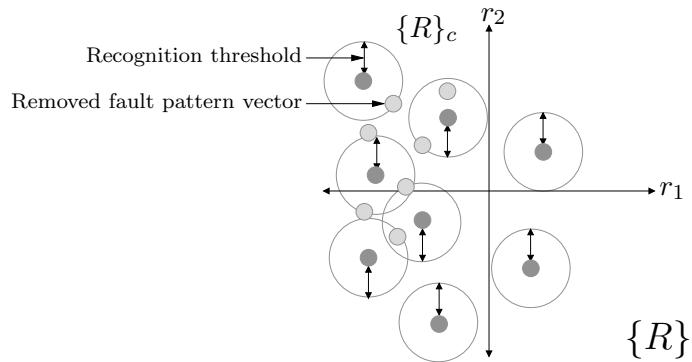

| 4.21 | Pairs of formal proteins with minimal binding energy given a binding matrix         | 113 |

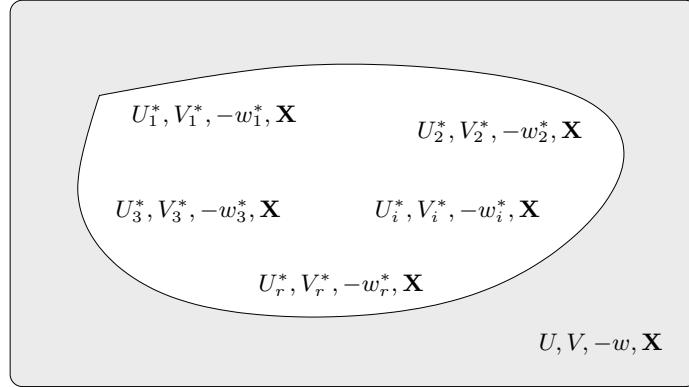

| 4.22 | Formal immune network space of dimension $t = 2$ . . . . .                          | 116 |

| 4.23 | Antigen in a formal immune network space of dimension $t = 2$ . . . . .             | 118 |

| 4.24 | Recognition in a formal immune network space of dimension $t = 2$ . . . . .         | 118 |

| 5.1  | Binary value inputs and outputs to the fault recognition module . . . . .           | 123 |

| 5.2  | Real value inputs and outputs to the fault recognition module . . . . .             | 124 |

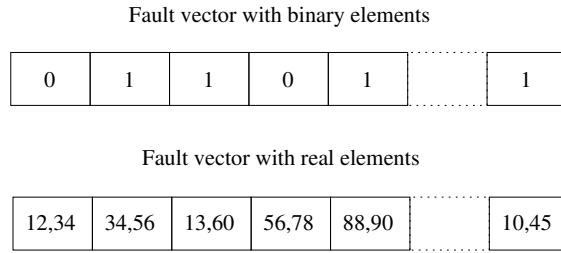

| 5.3  | Fault vector types . . . . .                                                        | 124 |

## *List of Figures*

|      |                                                                                                     |     |

|------|-----------------------------------------------------------------------------------------------------|-----|

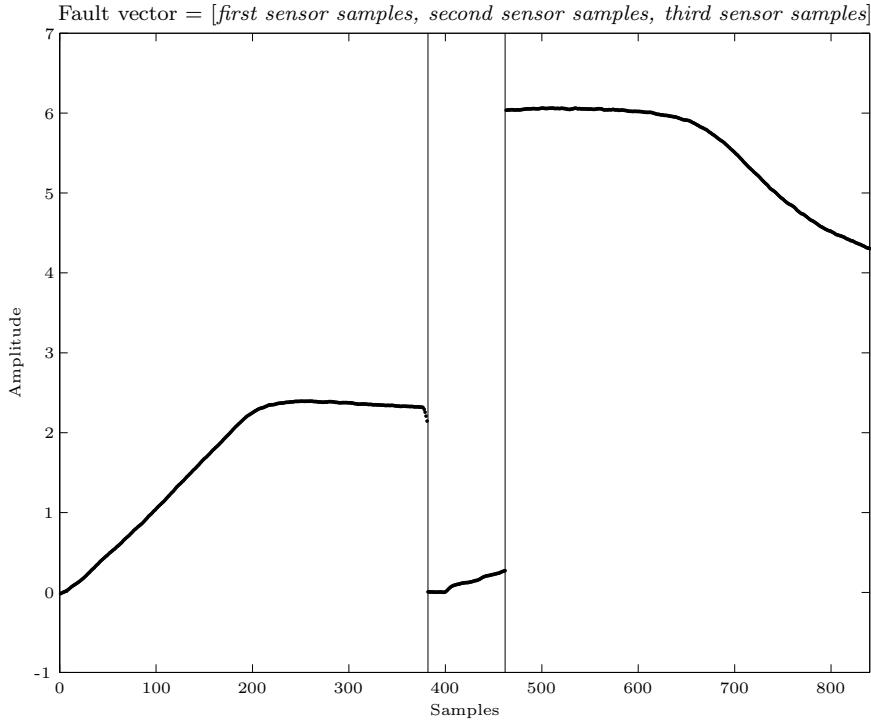

| 5.4  | Fault vector arrangement for a wire-bonding machine application . . . . .                           | 125 |

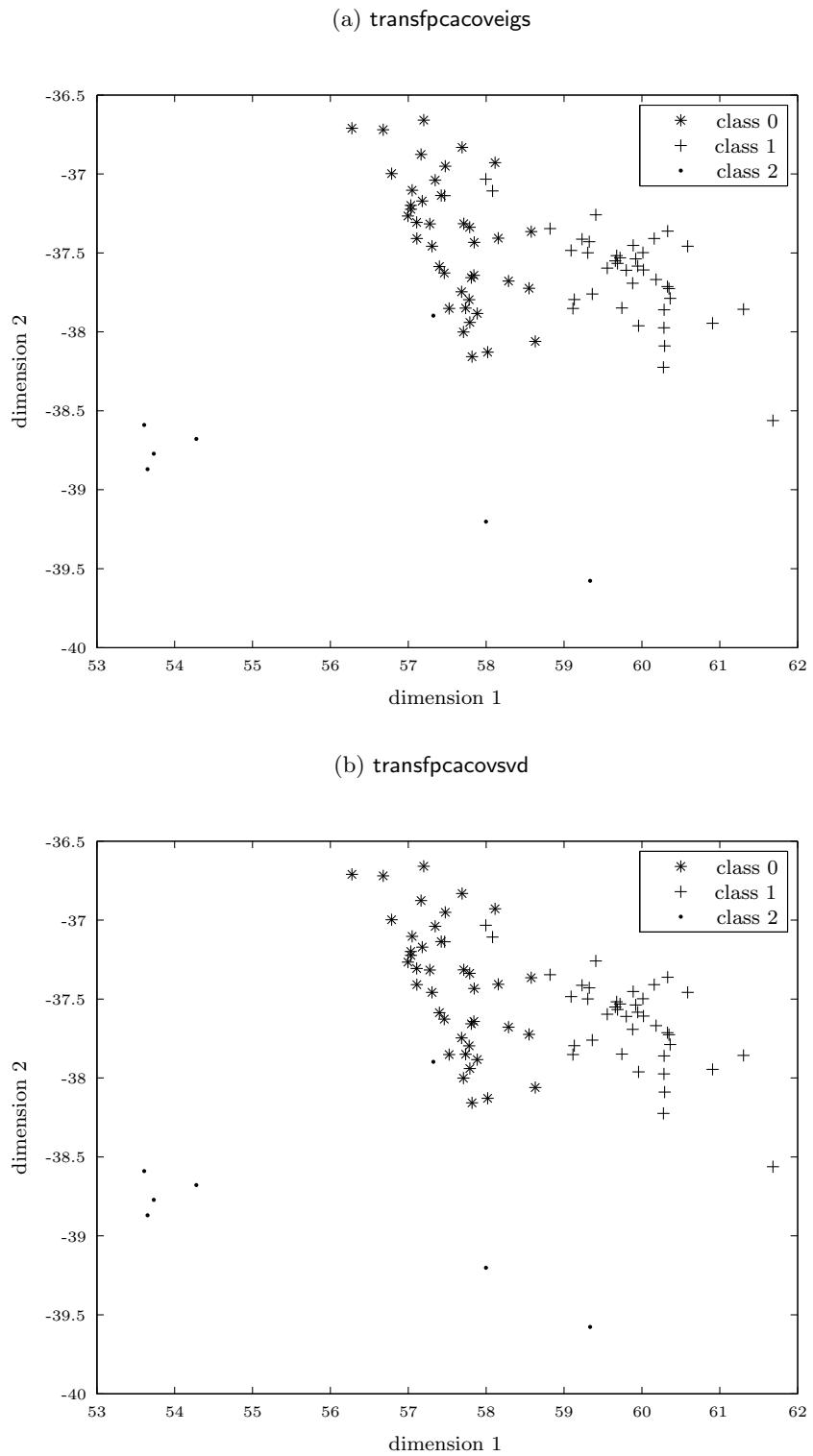

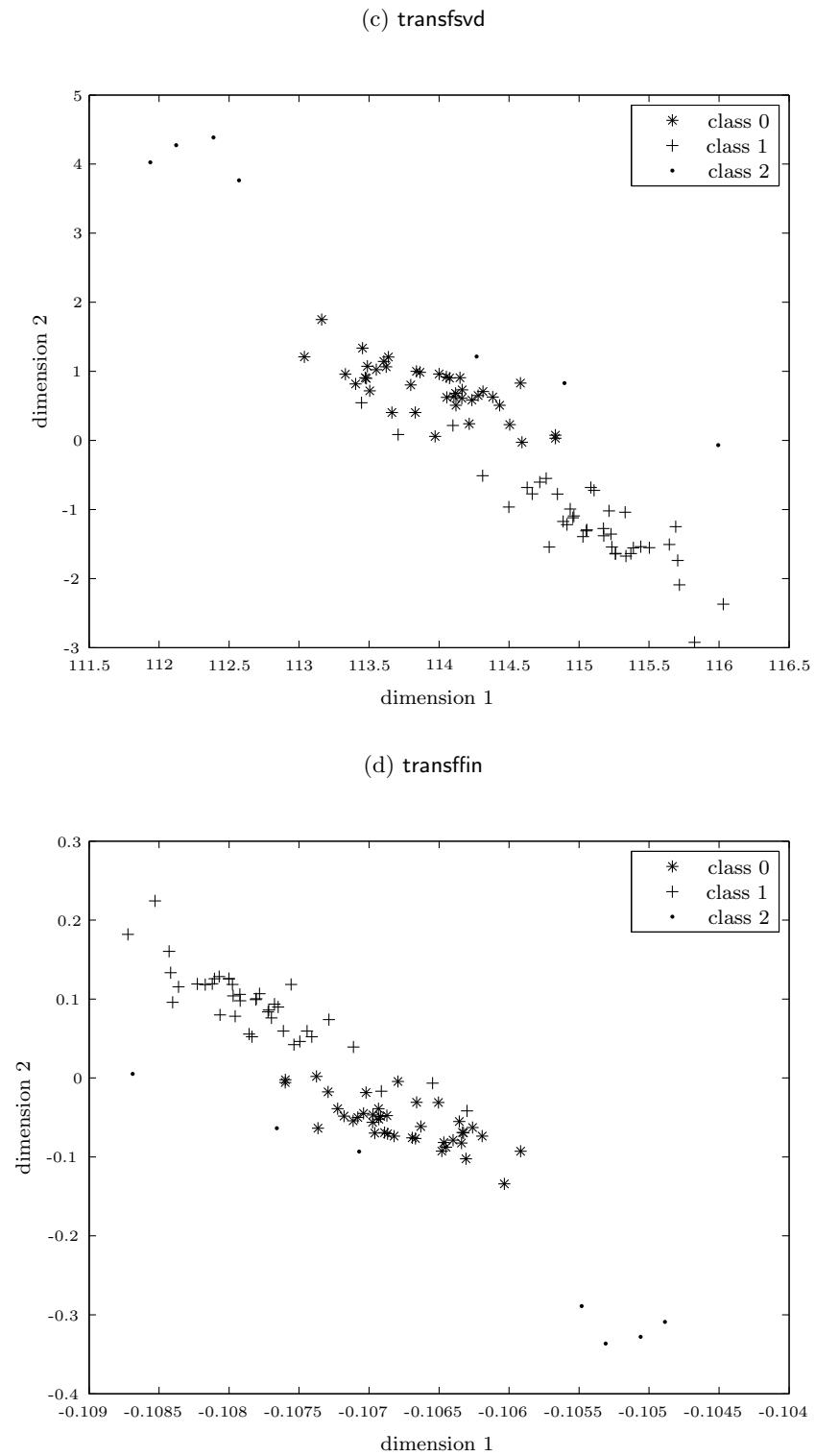

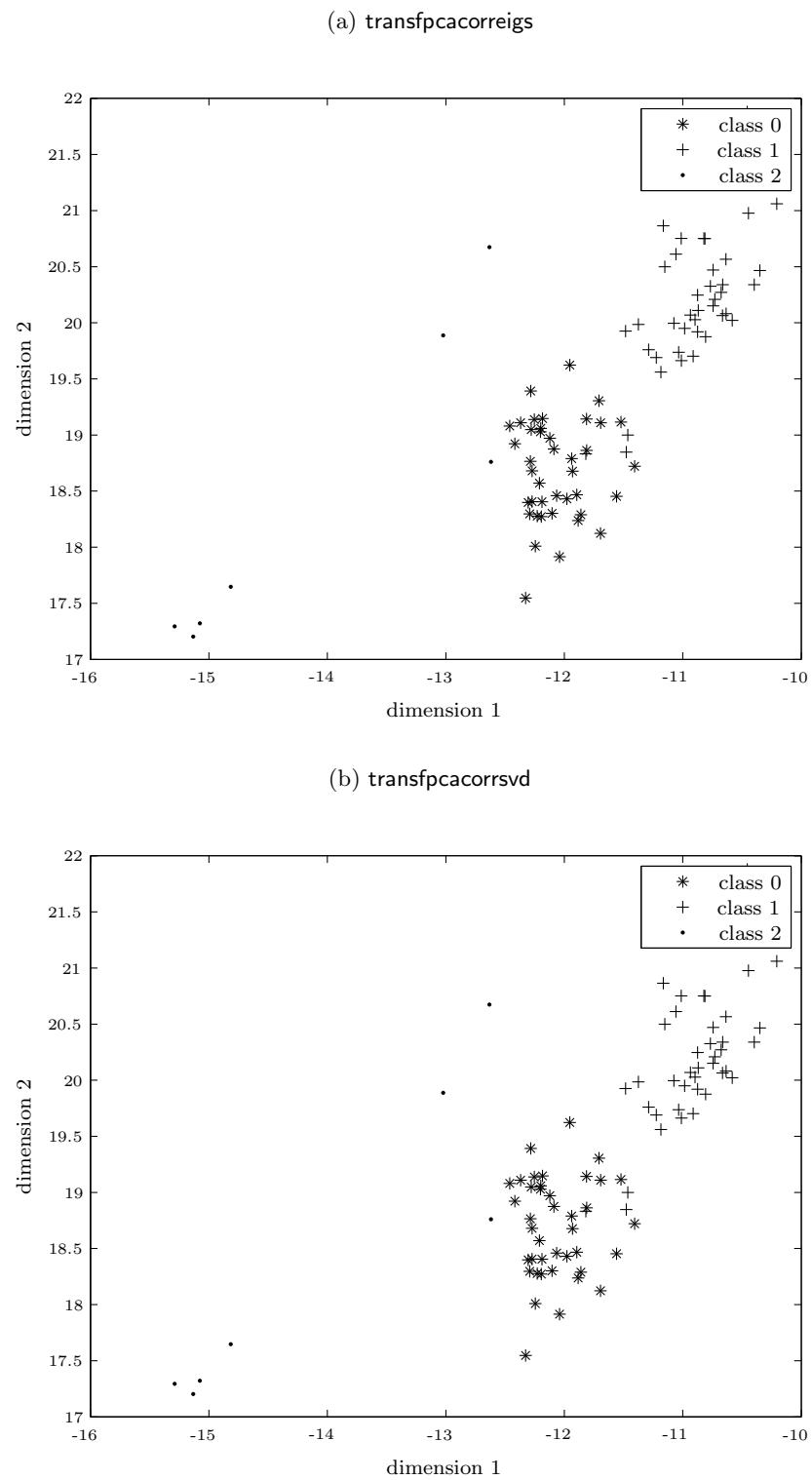

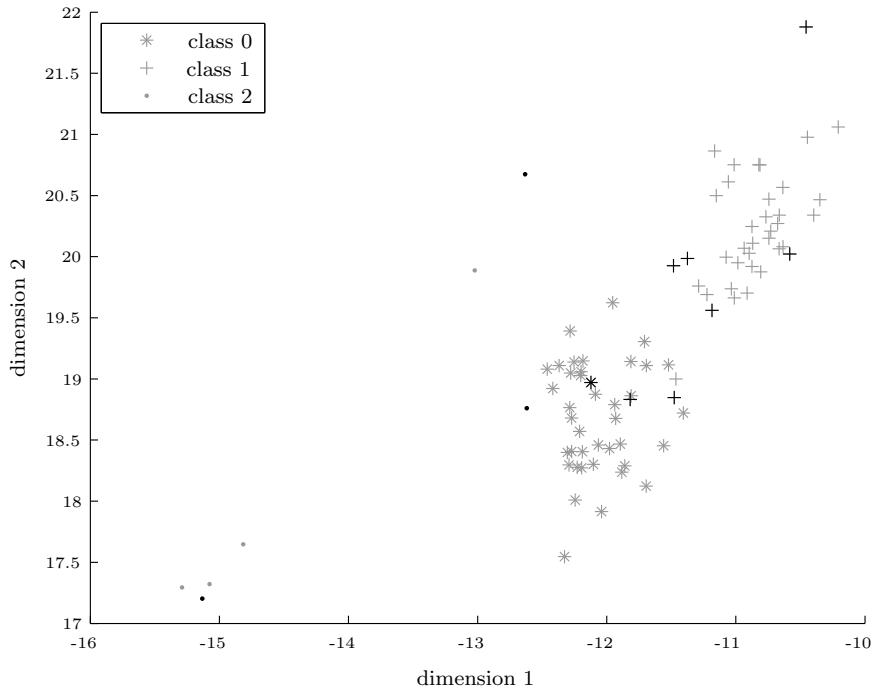

| 5.5  | Fault pattern vectors with reduced dimensions . . . . .                                             | 137 |

| 5.6  | Fault pattern vectors with reduced dimensions using normalization . . . . .                         | 142 |

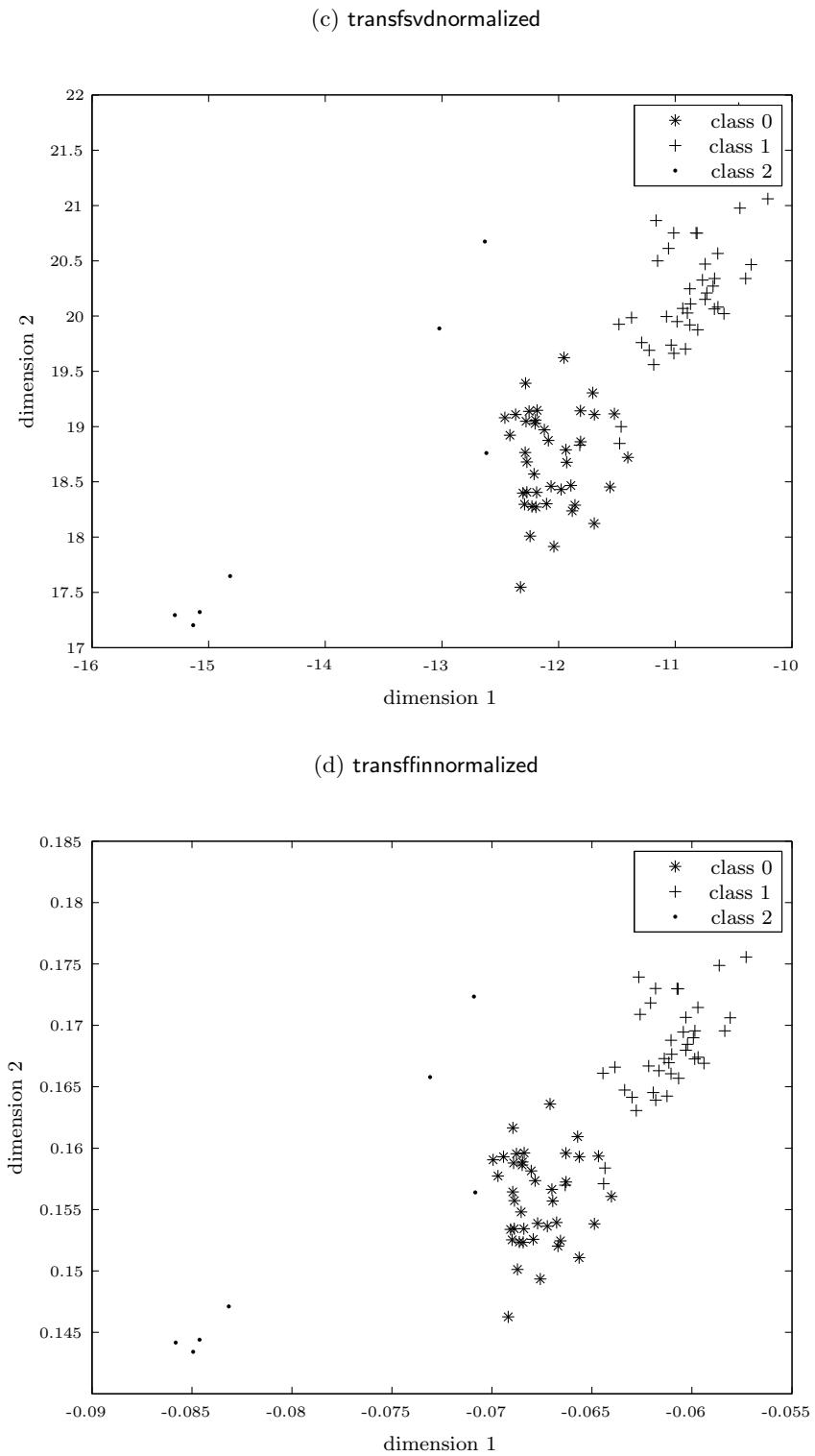

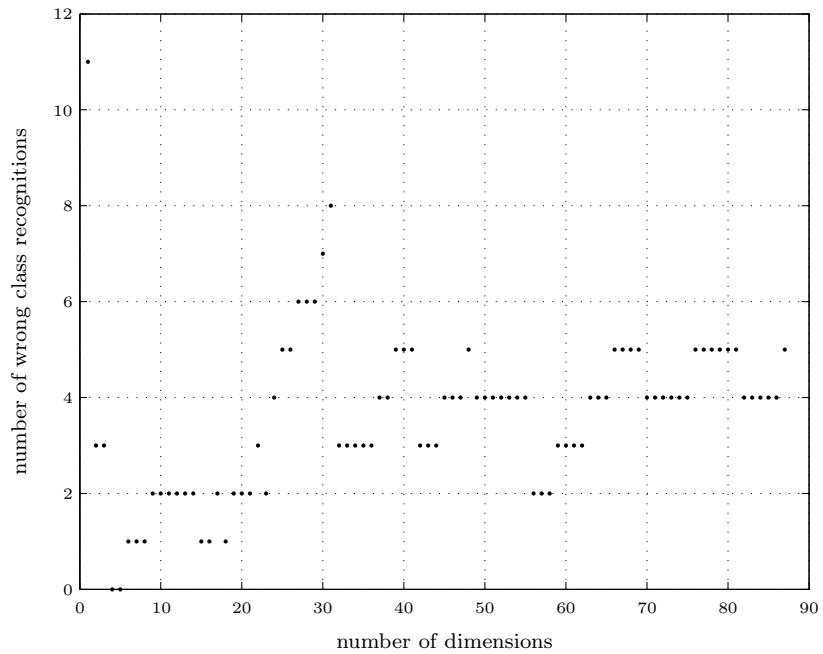

| 5.7  | Wrong class recognitions vs dimensions . . . . .                                                    | 146 |

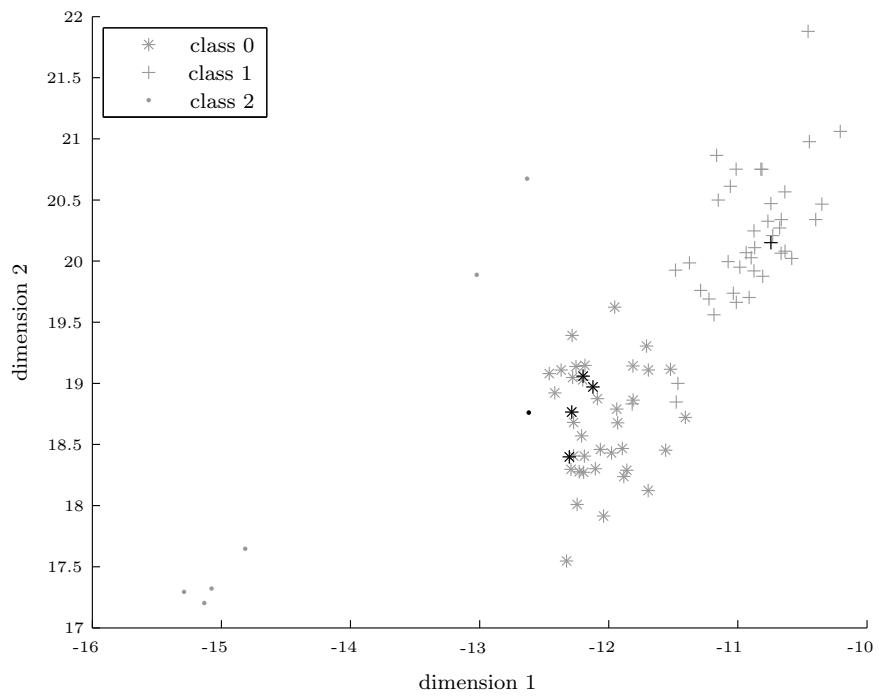

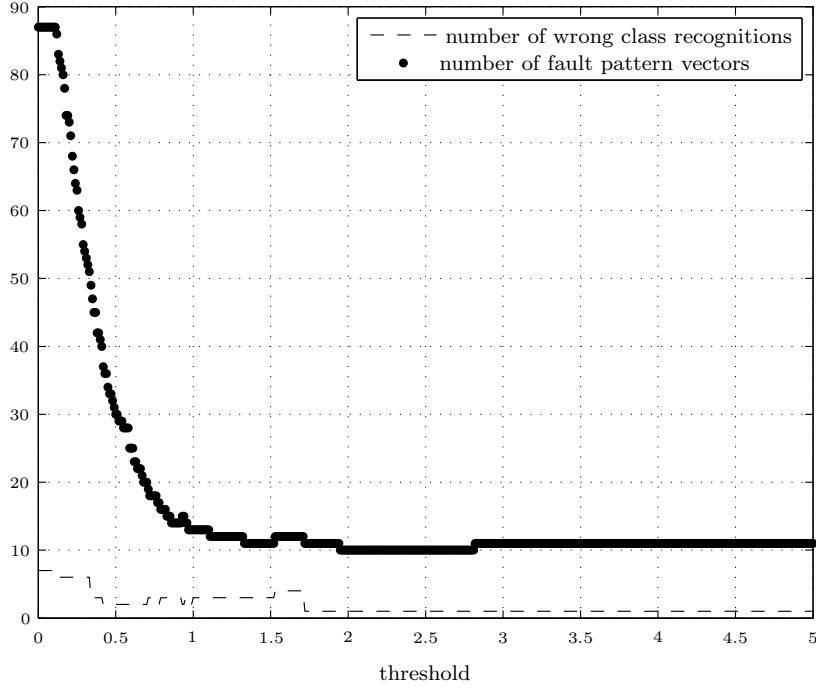

| 5.8  | Fault pattern vectors reduced by function <code>removalbylackofstimulation</code> . . . . .         | 165 |

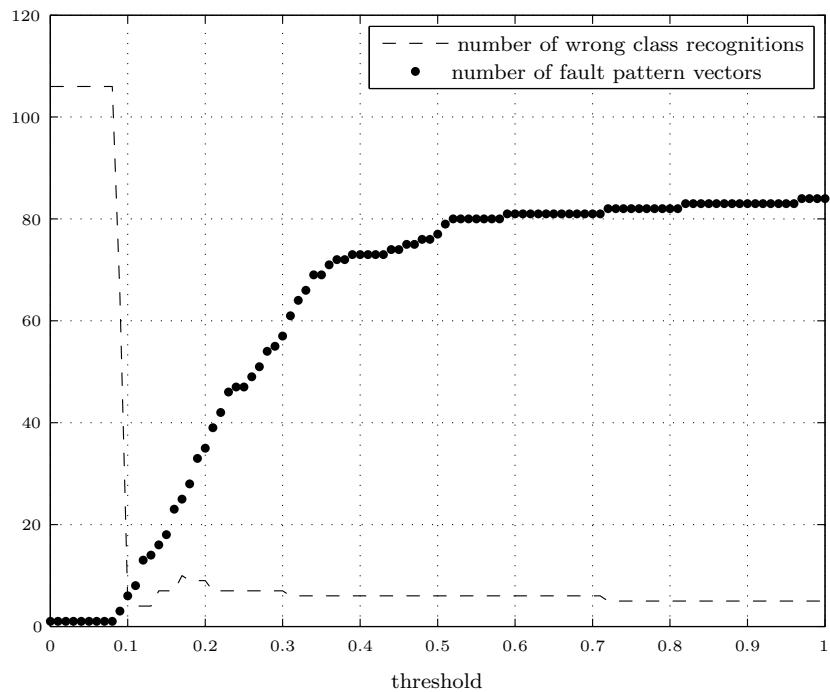

| 5.9  | Threshold variation by function <code>removalbylackofstimulation</code> . . . . .                   | 165 |

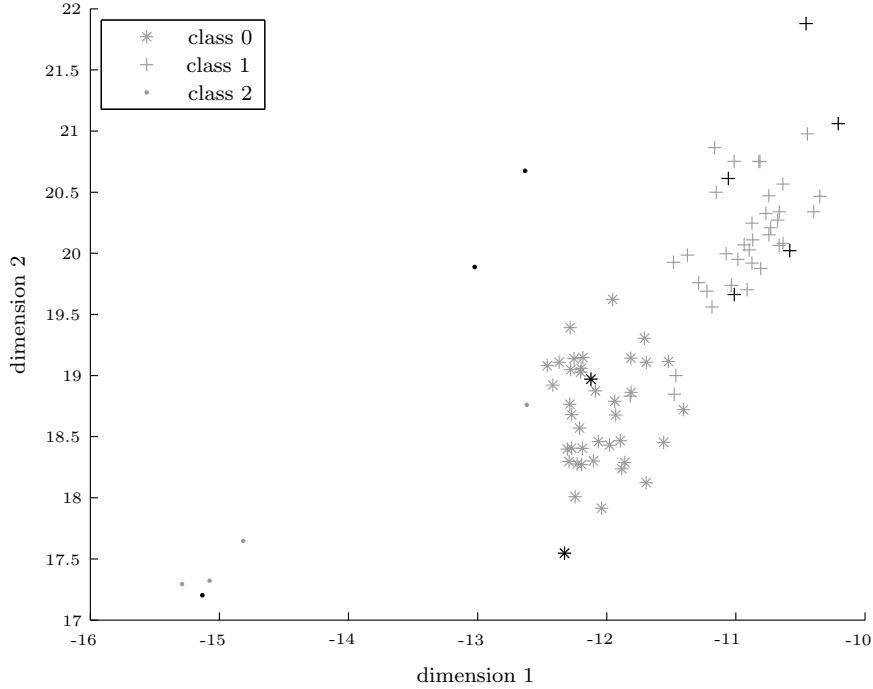

| 5.10 | Fault pattern vectors reduced by function <code>removalbyautoreactivity</code> . . . . .            | 166 |

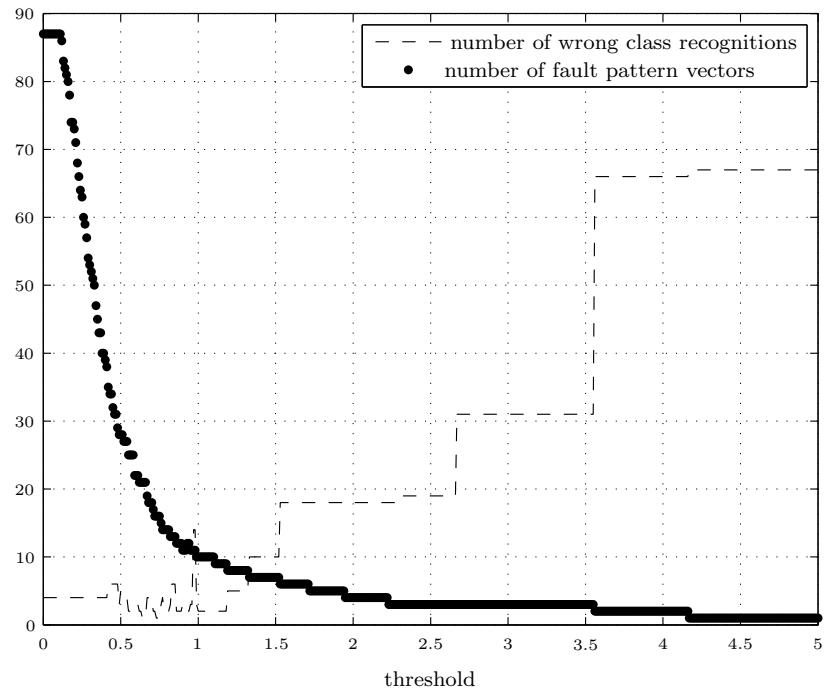

| 5.11 | Threshold variation by function <code>removalbyautoreactivity</code> . . . . .                      | 167 |

| 5.12 | Fault pattern vectors reduced by function <code>removalbyapoptosisautoimmunization</code> . . . . . | 167 |

| 5.13 | Threshold variation by function <code>removalbyapoptosisautoimmunization</code> . . . . .           | 168 |

| 5.14 | Fault recognition module design using duplication . . . . .                                         | 172 |

| 5.15 | Fault recognition module design using only specified values . . . . .                               | 173 |

| 5.16 | Fault recognition module design using a memory . . . . .                                            | 174 |

| 5.17 | Fault recognition module design using unspecified values in the input patterns                      | 179 |

| 5.18 | Fault recognition module design using an unspecified values monitor . . . . .                       | 180 |

| 5.19 | Fault recognition module design using multiplexers . . . . .                                        | 181 |

| 5.20 | Fault recognition module design using implicit output vectors comparison . .                        | 182 |

| 5.21 | Input vector monitoring block . . . . .                                                             | 186 |

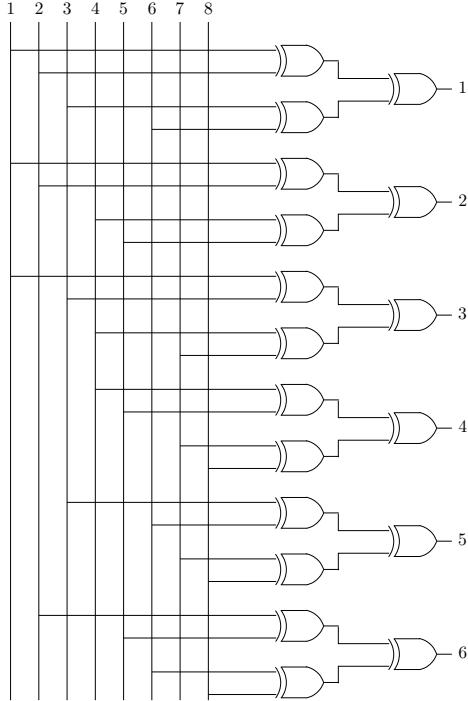

| 5.22 | Fault recognition module design using an output vector compactor . . . . .                          | 188 |

| 5.23 | X-Compactor circuit for $m = 8$ and $q = 6$ . . . . .                                               | 190 |

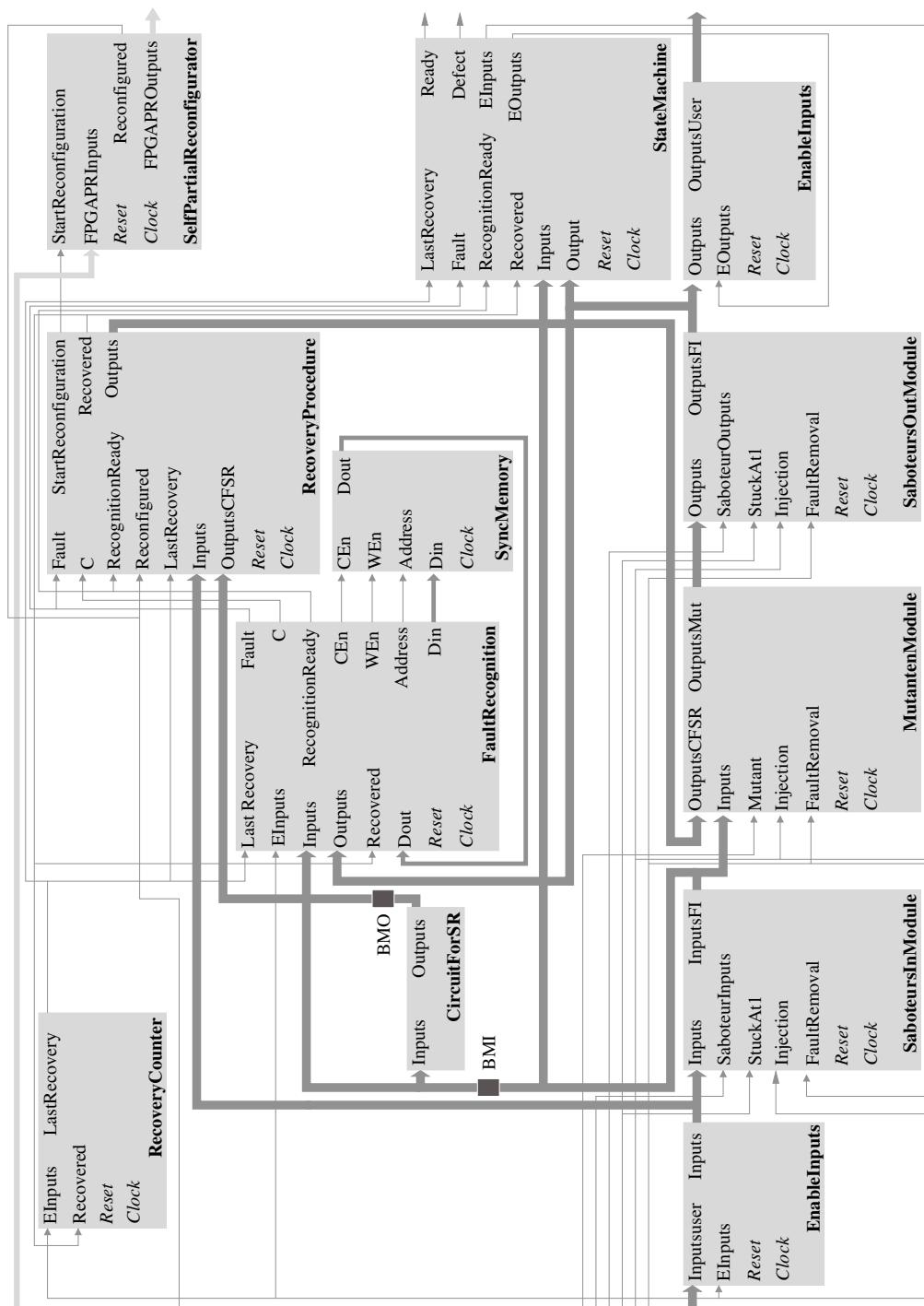

| 6.1  | Initial architecture of the self-repairing unit . . . . .                                           | 197 |

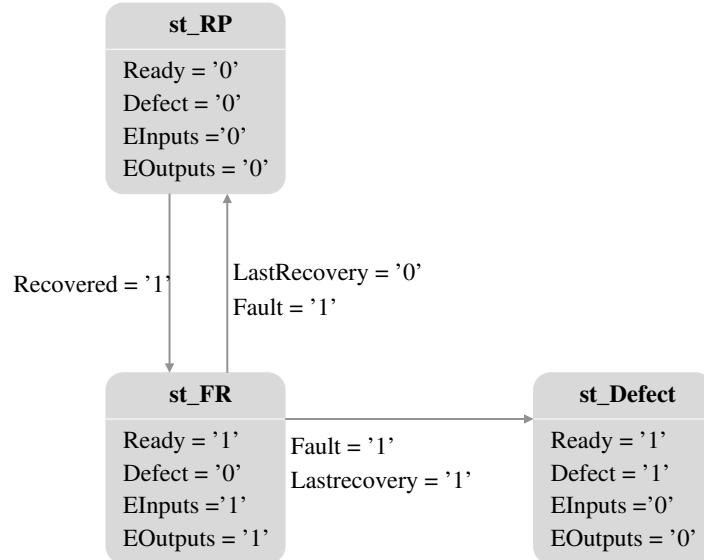

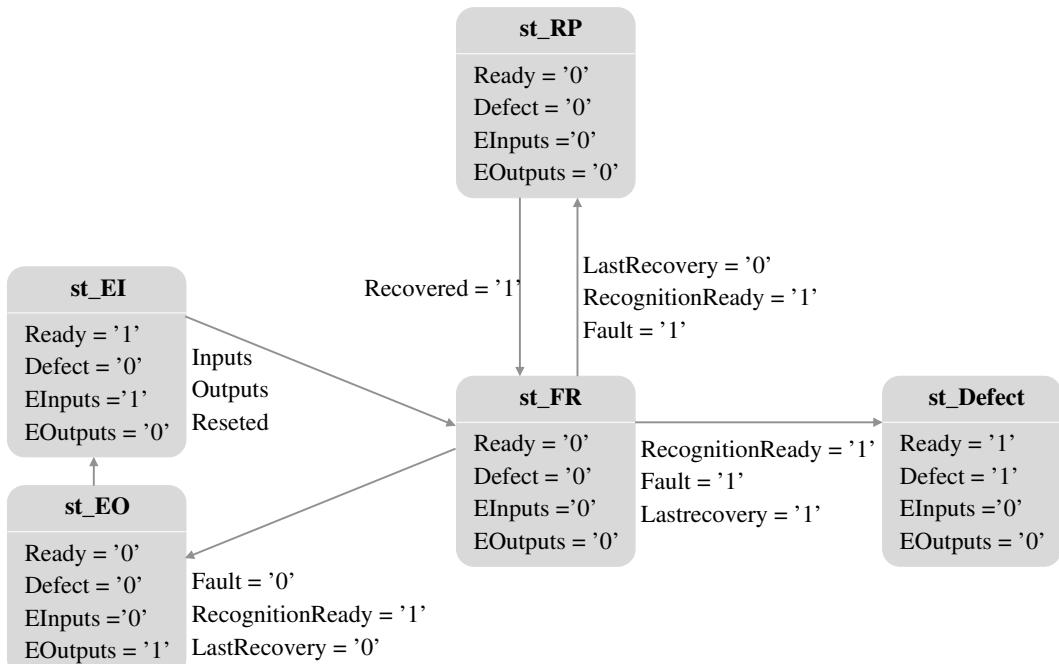

| 6.2  | State machine for concurrent fault recognition . . . . .                                            | 202 |

| 6.3  | State machine for an almost-concurrent fault recognition . . . . .                                  | 202 |

| 6.4  | A fault recognition module for a unit with binary inputs and outputs . . . . .                      | 206 |

| 6.5  | A fault recognition module for a unit with real inputs and outputs . . . . .                        | 207 |

| 6.6  | Recovery with redundant circuits . . . . .                                                          | 215 |

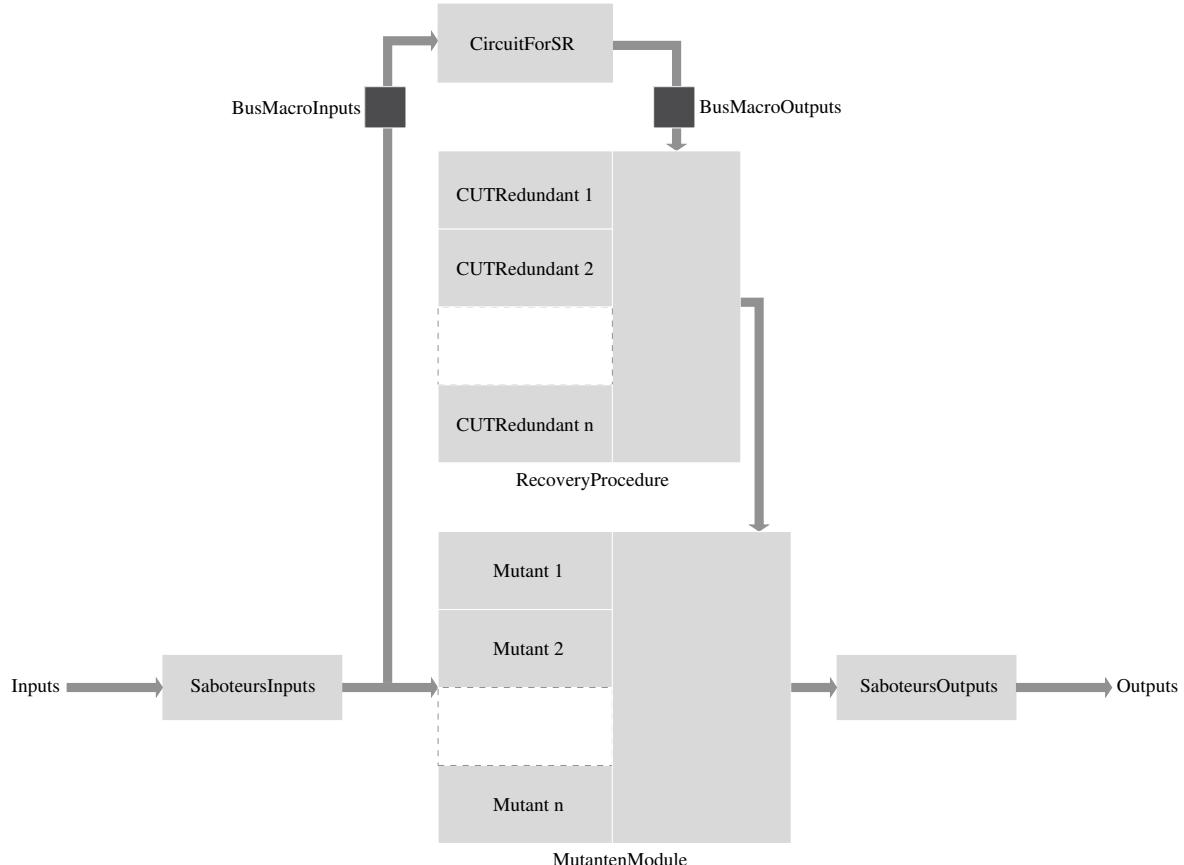

| 6.7  | Architecture of the self-repairing system . . . . .                                                 | 220 |

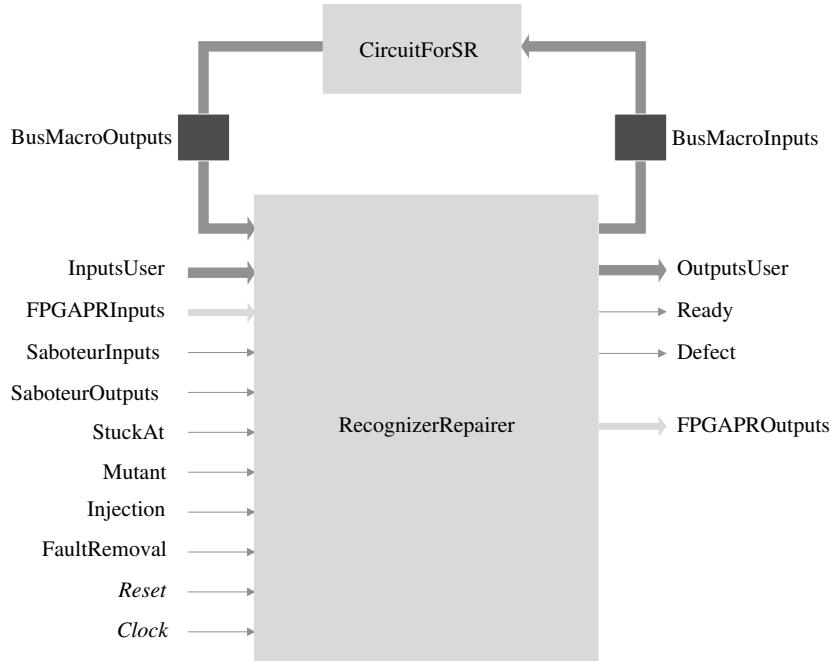

| 6.8  | Fault recognizer and repairer module for the circuit for self-repairing . . . . .                   | 221 |

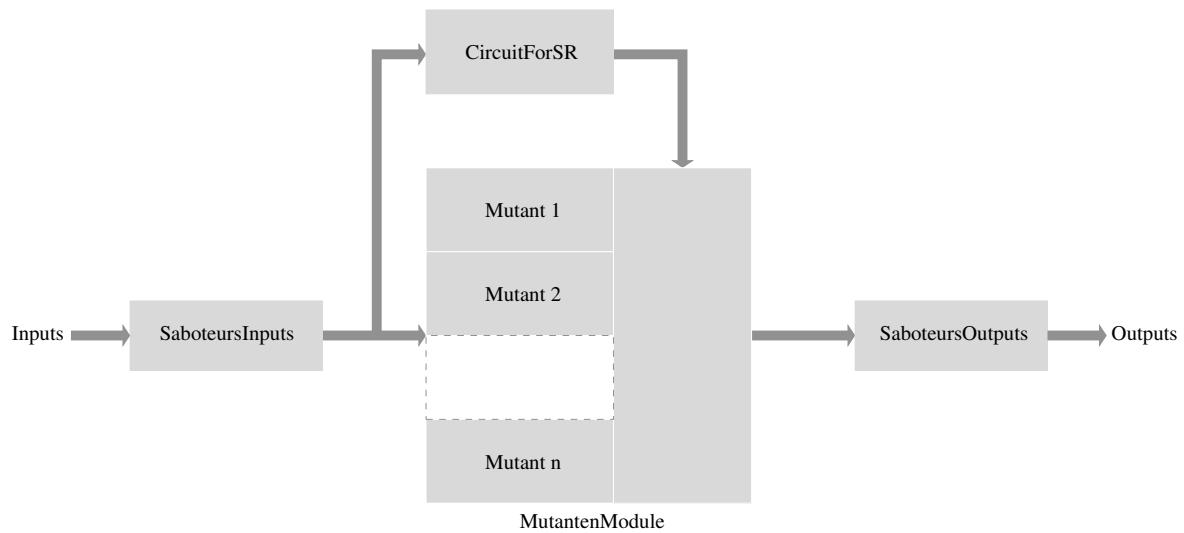

| 6.9  | Architecture for testing the self-repairing system . . . . .                                        | 230 |

| 6.10 | Fault injector . . . . .                                                                            | 231 |

| 6.11 | Fault injector and fault repairer connection . . . . .                                              | 231 |

| 6.12 | Fault recognizer and repairer module with an embedded fault injector . . . . .                      | 232 |

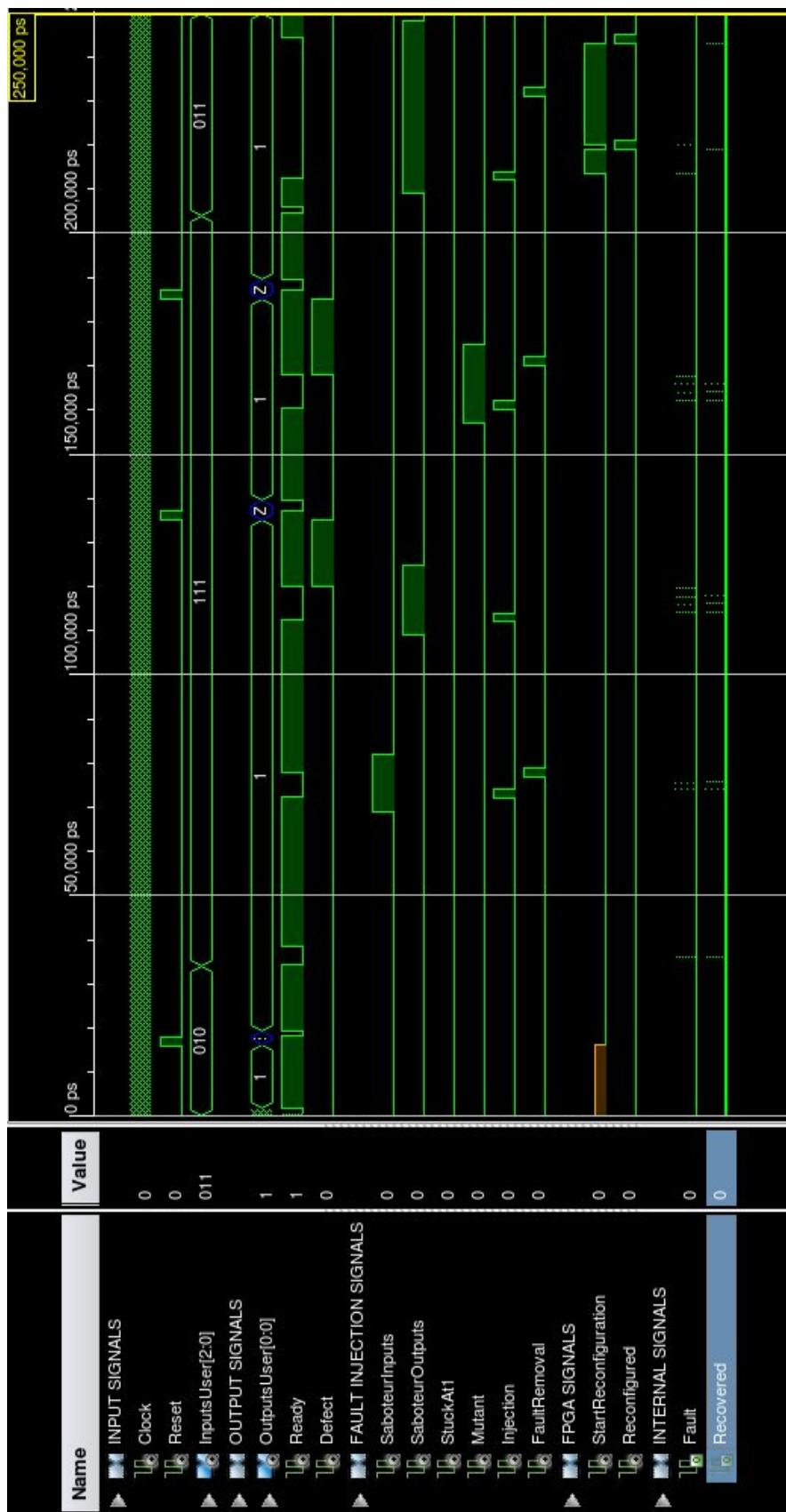

| 6.13 | Simulation of the self-repairing circuit . . . . .                                                  | 250 |

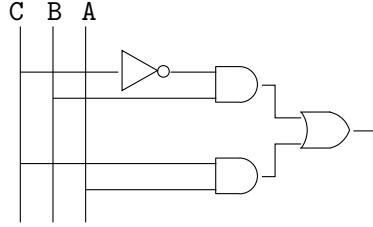

| 6.14 | Circuit for self-repairing . . . . .                                                                | 251 |

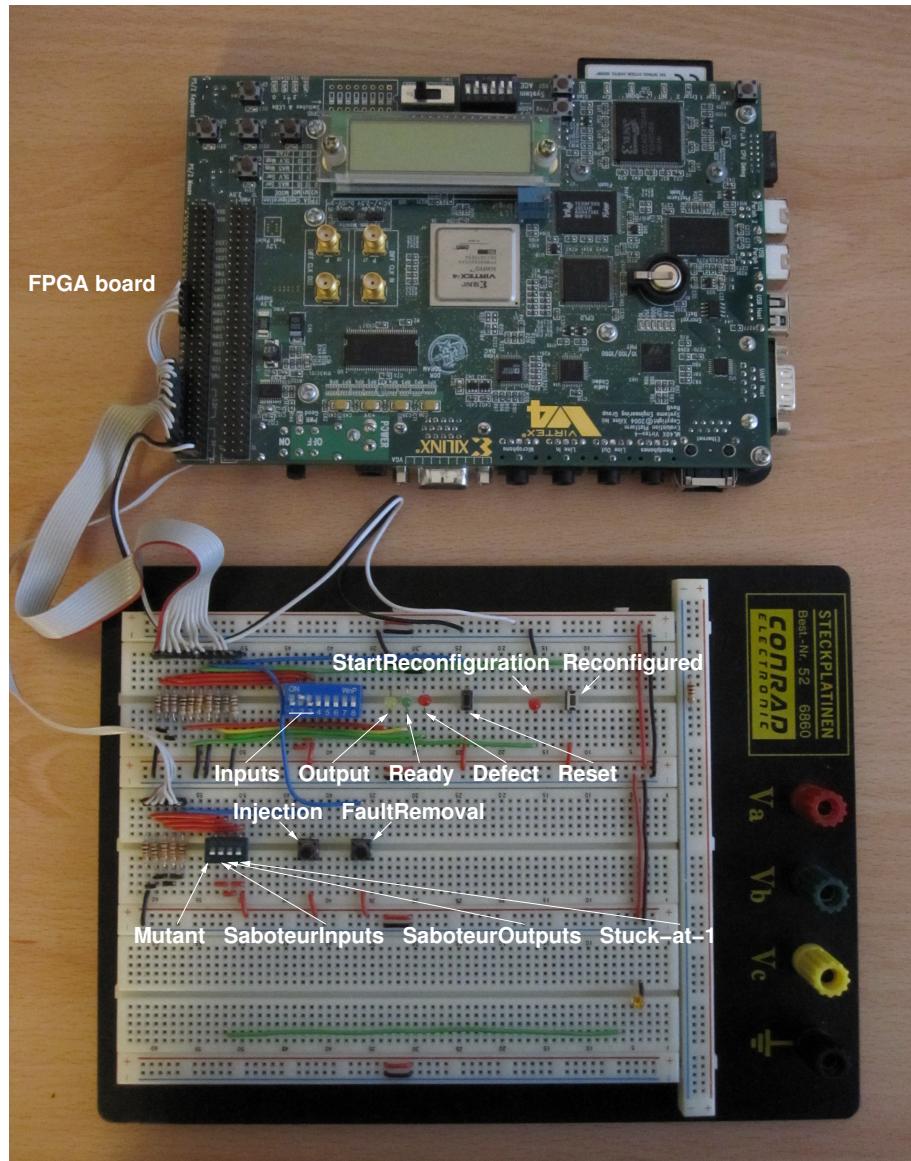

| 6.15 | FPGA board and breadboard for the hardware implementation . . . . .                                 | 254 |

| 6.16 | Performance measurement . . . . .                                                                   | 258 |

*List of Figures*

---

# List of Tables

|      |                                                                                 |     |

|------|---------------------------------------------------------------------------------|-----|

| 3.1  | Dendritic cells algorithm relative weights . . . . .                            | 81  |

| 3.2  | Comparison of artificial immune algorithms . . . . .                            | 85  |

| 5.1  | Available fault vectors with real elements . . . . .                            | 126 |

| 5.2  | Wrong class recognitions . . . . .                                              | 129 |

| 5.3  | Wrong class recognitions using variants of the Mahalanobis distance . . . . .   | 130 |

| 5.4  | Wrong class recognitions using normalization through the p-norm . . . . .       | 130 |

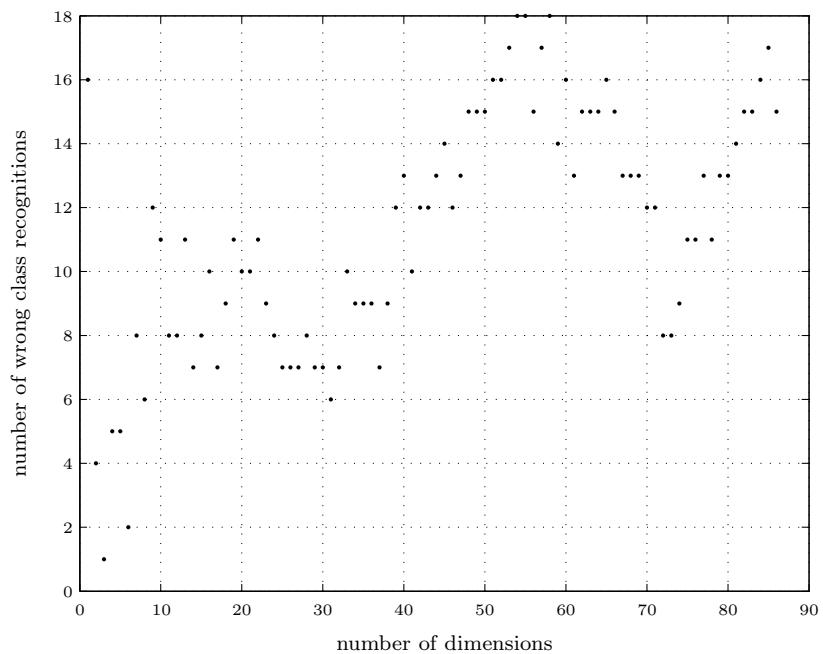

| 5.5  | Wrong class recognitions using vector dimension reduction . . . . .             | 140 |

| 5.6  | Wrong class recognitions using normalized vector dimension reduction (a) . .    | 144 |

| 5.7  | Wrong class recognitions using normalized vector dimension reduction (b) . .    | 145 |

| 5.8  | Results of “Death of immune cells with insufficient stimulation” (a) . . . . .  | 152 |

| 5.9  | Results of “Death of immune cells with insufficient stimulation” (b) . . . . .  | 153 |

| 5.10 | Results of “Death of immune cells with insufficient stimulation” (c) . . . . .  | 154 |

| 5.11 | Results of “Elimination of auto-reactive immune cells” (a) . . . . .            | 155 |

| 5.12 | Results of “Elimination of auto-reactive immune cells” (b) . . . . .            | 156 |

| 5.13 | Results of “Elimination of auto-reactive immune cells” (c) . . . . .            | 157 |

| 5.14 | Results of “Apoptosis and auto-immunization” (a) . . . . .                      | 158 |

| 5.15 | Results of “Apoptosis and auto-immunization” (b) . . . . .                      | 159 |

| 5.16 | Results of “Apoptosis and auto-immunization” (c) . . . . .                      | 160 |

| 5.17 | Best case by “Death of immune cells with insufficient stimulation” . . . . .    | 162 |

| 5.18 | Best case by “Elimination of auto-reactive immune cells” . . . . .              | 163 |

| 5.19 | Best case by “Apoptosis and auto-immunization” . . . . .                        | 164 |

| 5.20 | Summary of results from existing methods of test set compaction . . . . .       | 178 |

| 5.21 | Truth table for the output vectors comparison using multiplexers . . . . .      | 182 |

| 5.22 | Truth table for the implicit output vectors comparison when pattern bit = 0     | 183 |

| 5.23 | Truth table for the implicit output vectors comparison when pattern bit = 1     | 183 |

| 5.24 | Fault pattern vectors with all specified bits for the c17 benchmark circuit . . | 184 |

| 5.25 | Fault pattern vectors with unspecified bits for the c17 benchmark circuit . .   | 184 |

| 5.26 | Hardware overhead of the fault recognition module . . . . .                     | 185 |

| 5.27 | Possible compaction using the X-Compact technique . . . . .                     | 189 |

| 5.28 | Compaction using the X-Compact technique for the circuits of ISCAS 85 . .       | 189 |

| 6.1  | Circuit for self-repairing truth table . . . . .                                | 249 |

| 6.2  | Fault vectors with recovery mechanisms . . . . .                                | 251 |

*List of Tables*

---

# List of Algorithms

|     |                                                                                    |     |

|-----|------------------------------------------------------------------------------------|-----|

| 3.1 | Positive and negative selection . . . . .                                          | 69  |

| 3.2 | Clonal selection . . . . .                                                         | 71  |

| 3.3 | Immune network . . . . .                                                           | 78  |

| 3.4 | Dendritic cells . . . . .                                                          | 80  |

| 4.1 | Fault pattern vector dimension reduction using PCA and the covariance . . . . .    | 103 |

| 4.2 | Fault pattern vector dimension reduction using PCA and SVD . . . . .               | 104 |

| 4.3 | Fault pattern vector dimension reduction using SVD . . . . .                       | 107 |

| 4.4 | Fault pattern vectors number reduction through insufficient stimulation . . . . .  | 109 |

| 4.5 | Fault pattern vectors number reduction through auto-reactive immune cells . .      | 110 |

| 4.6 | Fault pattern vector dimension reduction in a FIN . . . . .                        | 117 |

| 4.7 | Fault recognition by means of molecular recognition . . . . .                      | 119 |

| 4.8 | Fault repairing mechanism assignation by means of a cFIN . . . . .                 | 119 |

| 4.9 | Fault pattern vectors number reduction in a cFIN . . . . .                         | 120 |

| 5.1 | Fault pattern vector set compaction using the clonal selection algorithm . . . . . | 176 |

---

# List of Program Codes

|      |                                                                                 |     |

|------|---------------------------------------------------------------------------------|-----|

| 5.1  | Minkowski, Euclidean, Manhattan and Chebyshev distance functions . . . . .      | 126 |

| 5.2  | Mahalanobis distance function . . . . .                                         | 127 |

| 5.3  | Covariance matrix function . . . . .                                            | 127 |

| 5.4  | Nearest neighbor class function . . . . .                                       | 127 |

| 5.5  | k-nearest neighbors function . . . . .                                          | 128 |

| 5.6  | PCA transformation using eigenvalue decomposition function . . . . .            | 131 |

| 5.7  | PCA transformation using singular value decomposition function . . . . .        | 132 |

| 5.8  | Singular value decomposition transformation function . . . . .                  | 134 |

| 5.9  | Formal immune network transformation function (a) . . . . .                     | 135 |

| 5.10 | Formal immune network transformation function (b) . . . . .                     | 135 |

| 5.11 | Transformation function for the fault vectors of the test set . . . . .         | 136 |

| 5.12 | Transformation function for the fault vectors of the test set for FIN . . . . . | 136 |

| 5.13 | Correlation matrix function . . . . .                                           | 139 |

| 5.14 | Death of immune cells with insufficient stimulation function . . . . .          | 147 |

| 5.15 | Elimination of auto-reactive immune cells function . . . . .                    | 148 |

| 5.16 | Apoptosis and auto-immunization function . . . . .                              | 150 |

| 6.1  | Circuit for self-repairing module . . . . .                                     | 198 |

| 6.2  | Enable inputs module . . . . .                                                  | 199 |

| 6.3  | Enable outputs module . . . . .                                                 | 200 |

| 6.4  | State machine module . . . . .                                                  | 203 |

| 6.5  | Fault recognition module . . . . .                                              | 210 |

| 6.6  | Memory module . . . . .                                                         | 213 |

| 6.7  | Recovery procedure module . . . . .                                             | 214 |

| 6.8  | Recovery counter module . . . . .                                               | 216 |

| 6.9  | Constants package . . . . .                                                     | 218 |

| 6.10 | Self-partial reconfigurator module . . . . .                                    | 223 |

| 6.11 | Saboteurs at the inputs module . . . . .                                        | 229 |

| 6.12 | Saboteurs at the outputs module . . . . .                                       | 233 |

| 6.13 | Mutants module . . . . .                                                        | 235 |

| 6.14 | Mutant module with an stuck-at-0 fault . . . . .                                | 236 |

| 6.15 | Recognizer-repairer module . . . . .                                            | 237 |

| 6.16 | Top architecture module . . . . .                                               | 242 |

| 6.17 | Top architecture test bench . . . . .                                           | 245 |

| 6.18 | Constrains file . . . . .                                                       | 255 |

*List of Program Codes*

# 1

---

## Introduction

A hardware system which is able to recover from a failure autonomously is named a self-repairing system. A self-repairing system avoids the time span from the manifestation of a failure in it to the presence of a repairing team on site. The logistics necessary for having a repairing team and replacement material on site costs time, effort and money. An extreme example is the on site repairing of the hardware module of a space telescope, which besides of having a very high cost, in some circumstances can even be impossible because of the extreme conditions. Thus, the interest in investigating how to design self-repairing hardware systems.

Biological systems show autonomous recovery mechanisms. In vertebrates the entity responsible of detecting injuries or illnesses and of triggering recovery mechanisms is the immune system. Taking the human immune system as inspiration, the field of artificial immune systems transfers those biological principles into models and algorithms which can serve to solve technical problems. This thesis searches in the field of artificial immune systems for useful methods in the design of self-repairing hardware systems. That is the reason why this thesis has the name of Immunorepairing of Hardware Systems.

This chapter is organized as follows. The first section presents the aim and main objectives of this thesis. The second section outlines the strategy for reaching those objectives, such as the preliminary architecture of a self-repairing system and the fault recognition and recovery mechanisms to be studied. Finally, the last section explains how this thesis is organized.

### 1.1 Objectives of this work

Regarding the duration of a fault in a hardware system, any fault can be classified into permanent, transient or intermittent, [Koren and Krishna, 2007]. A self-repairing hardware system which is implemented by using programmable logic, such as FPGAs, can use reconfiguration for repairing the hardware system from only transient faults. However different types of redundancy can be used for repairing a system, please refer to [Koren and Krishna,

[\[2007\]](#). Firstly, static redundancy is mostly implemented by triplicating the hardware module and determining its output using a voter. That kind of redundancy masks faults and can be used for repairing the hardware module from both transient and permanent faults. Secondly, dynamic redundancy activates an available spare hardware module under a detected fault. Such kind of redundancy can repair a hardware module from both transient and permanent faults. However its use makes more sense when a permanent fault is present. So, in [\[Bolchini et al., 2011\]](#) the type of fault, transient or permanent, is first determined for applying either reconfiguration or active redundancy in a hardware system implemented using FPGAs.

The presence of an error caused by a permanent or transient fault in a hardware system can be detected by using self-checking design techniques, such as the ones explained extensively in [\[Lala, 2000\]](#) and [\[Gössel et al., 2008\]](#). Those methods serve for first detecting a fault, but the determination of which repairing mechanism should be applied is open.

Looking at concrete efforts of developing complete self-repairing hardware systems in the literature, which are briefly presented in chapter 2, it could be noticed that most of those approaches do not deliver details of the design of a fault recognition module which is able to work concurrently to the operation of the circuit to be repaired. Moreover, it has been noticed that many of the existing approaches propose new hardware platforms or self-repairing procedures which are hard to reproduce.

Hence, this thesis has the aim of providing a general architecture for the design of a self-repairing system. Thereby stressing on the design of a fault recognition module where the faults should not only be classified into transient and permanent, but permanent faults should be classified or distinguished according to the type of required repairing mechanism given at the design time. The objectives that support that aim are:

- The design of a versatile self-repairing architecture using a hardware description language

- The design of a multiclass fault recognition module with a low fault recognition latency

The design of the self-repairing architecture using a hardware description language would make that architecture independent of the implementation hardware platform to be used. A low fault recognition latency, in the second objective, would allow the fault recognition module to operate online and concurrently to the operation of the system.

## 1.2 Strategy

To achieve the proposed objectives, this section provides the methods and tools used in this thesis.

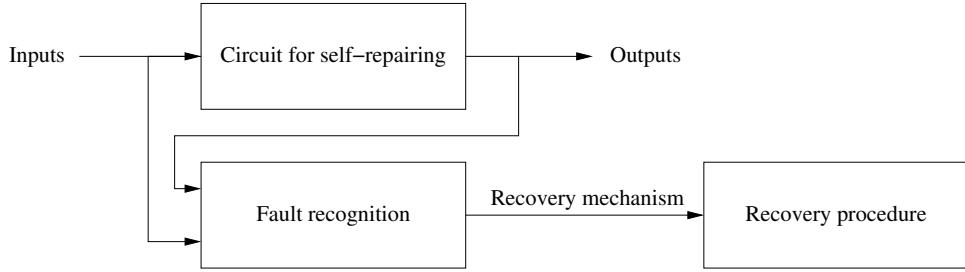

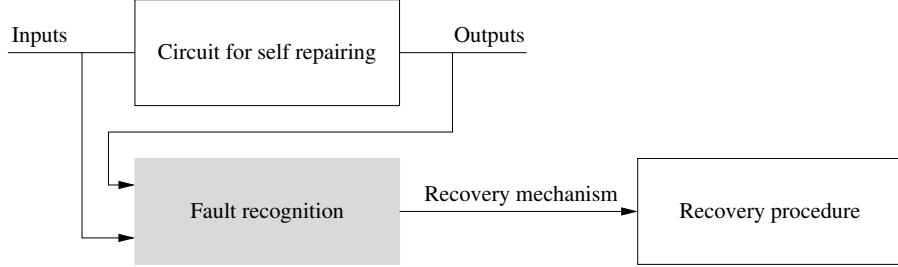

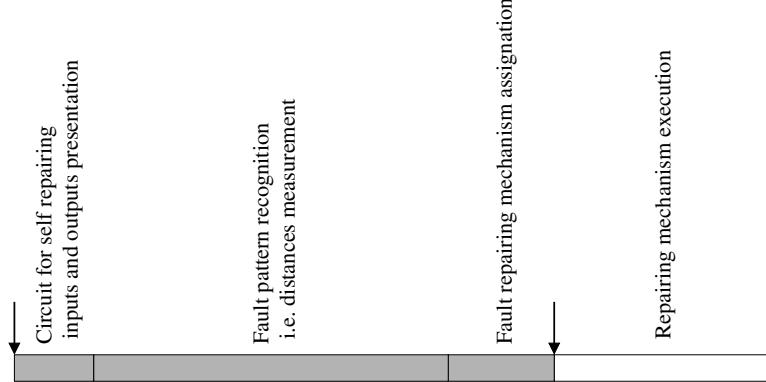

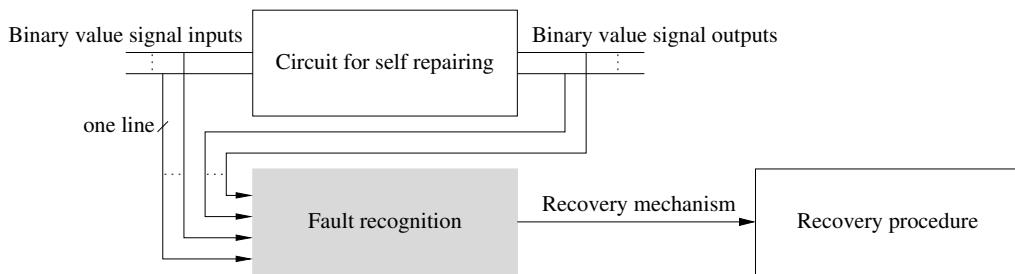

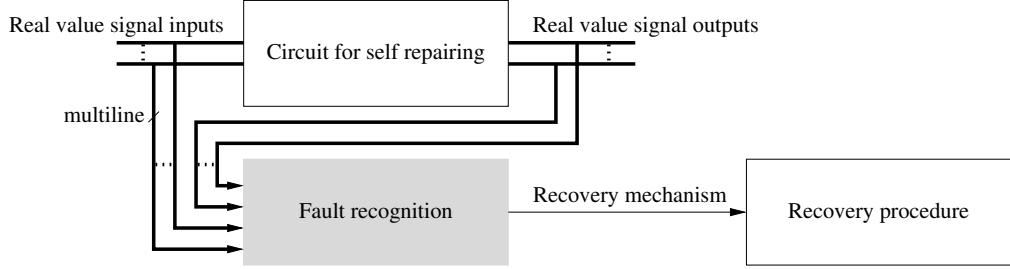

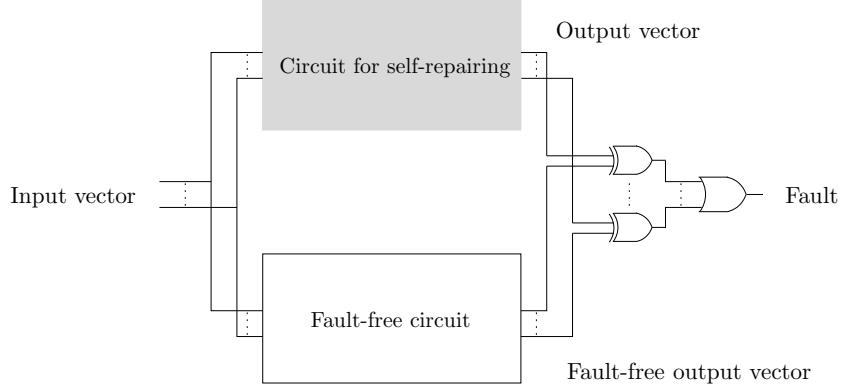

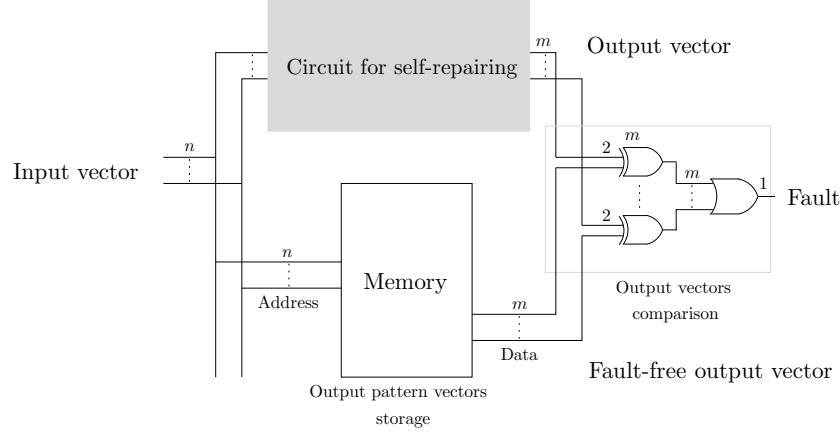

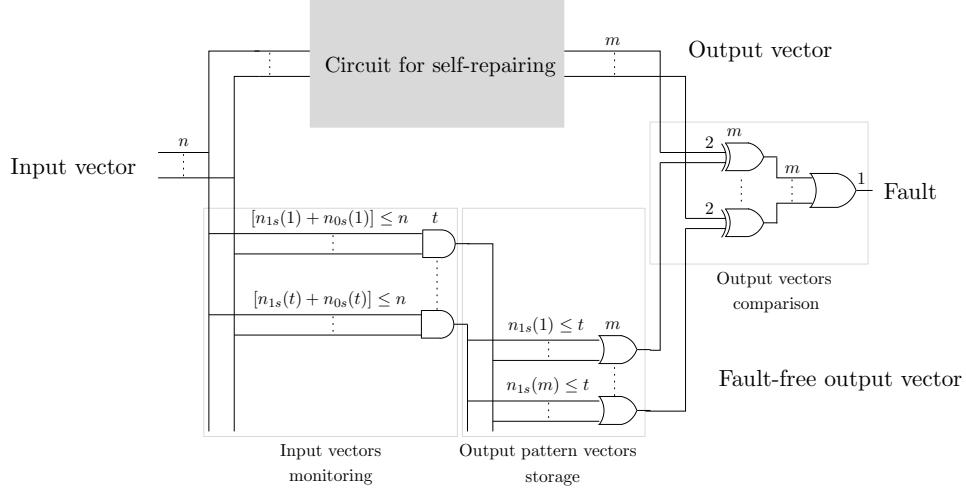

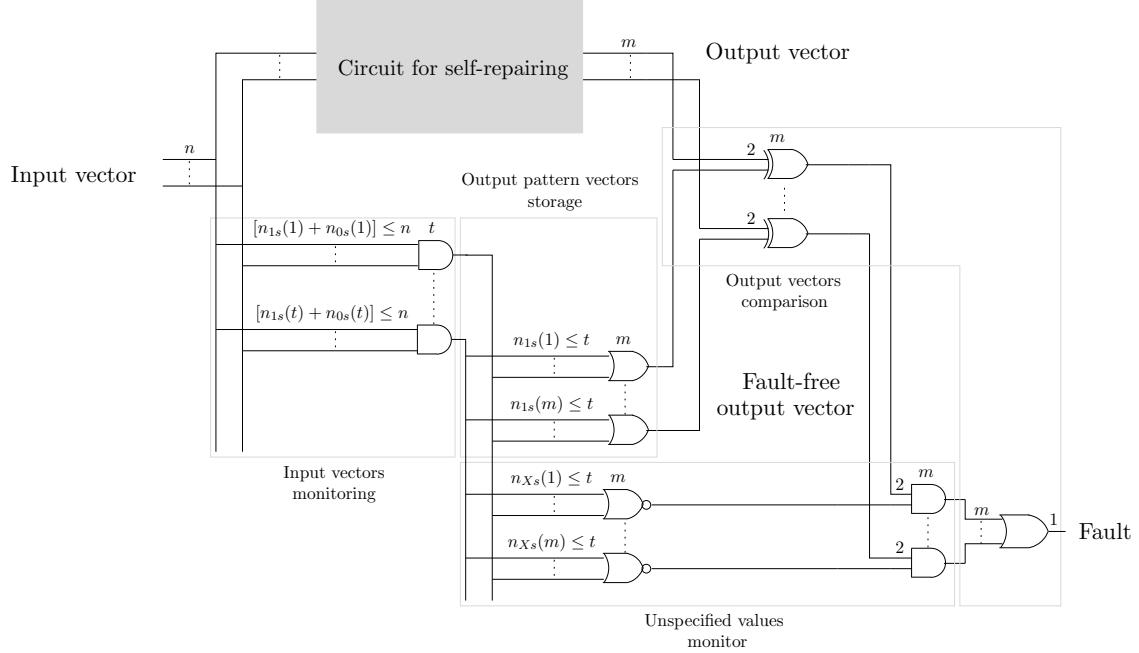

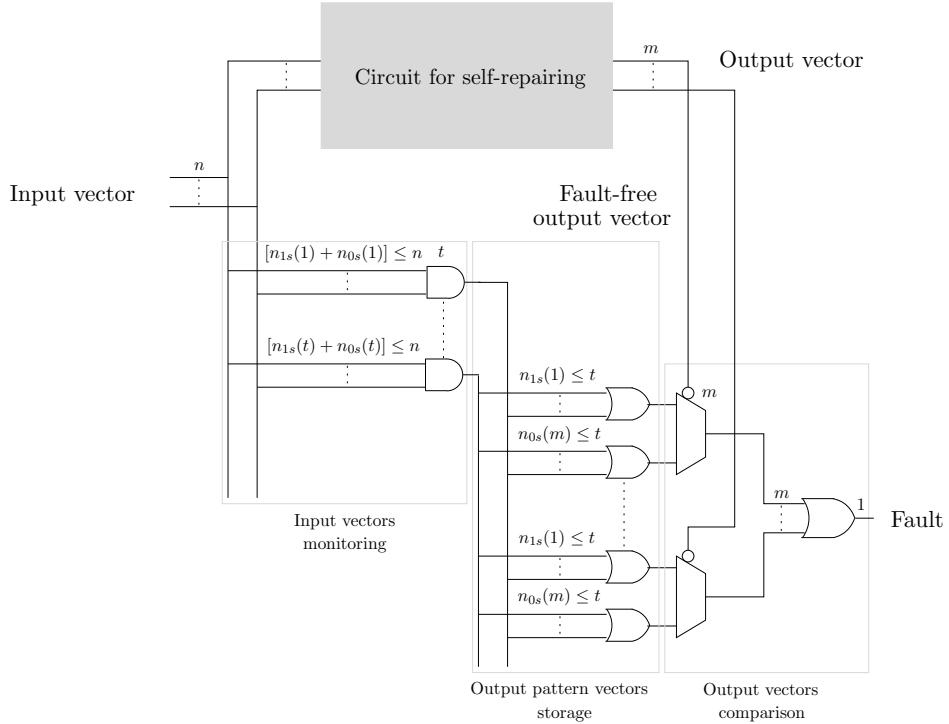

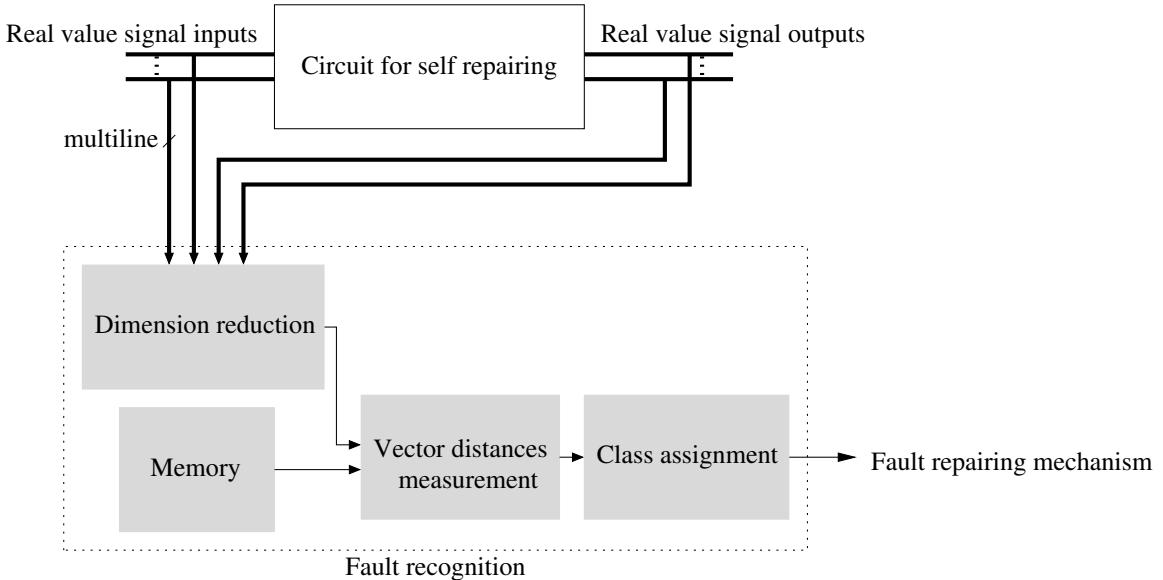

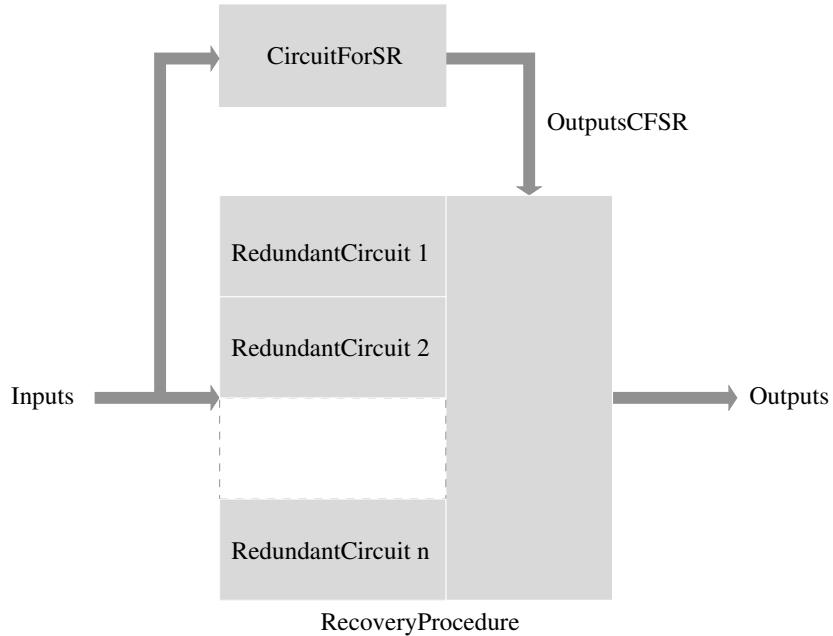

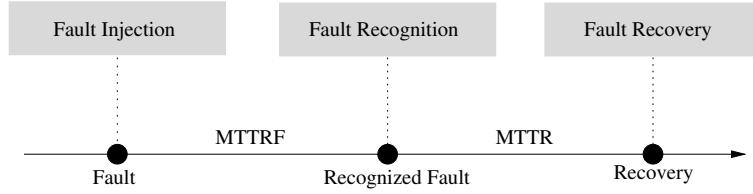

A self-repairing system is composed of the three modules drawn on figure 1.1: the circuit for self-repairing, the fault recognition module and the recovery procedure module. The fault recognition module executes fault recognition and delivers a recovery mechanism which is determined at the time of designing the system. The recovery procedure module executes the recovery mechanism provided by the fault recognition module.

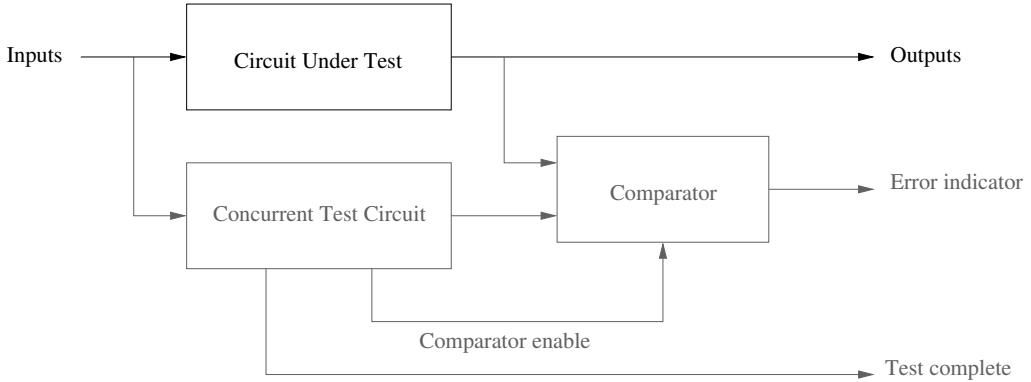

Since the fault recognition module should operate online and concurrently to the operation of the circuit for self-repairing, the technique named Built-In Concurrent Self-Test, in short BICST, is applied, please see figure 1.2 and refer to [\[Sharma and Saluja, 1988\]](#). So, the

## 1.2. Strategy

Figure 1.1: Self-repairing circuit

current inputs of the circuit for self-repairing are observed and compared with the fault pattern vectors stored in memory. When the current inputs match to the inputs of any stored fault pattern vector, it is verified if the current outputs of the circuit for self-repairing match with the desired outputs. If they do not match, the recovery mechanism associated to that fault pattern vector is delivered to the recovery procedure module.

Figure 1.2: Built-In Concurrent Self-Test (abstracted from [Sharma and Saluja, 1988] ©1988 IEEE)

For getting a low fault recognition latency, the number of fault pattern vectors should be minimal. That can be complied considering only fault pattern vectors for critical faults, or by reducing the given set of fault pattern vectors. Therefore, methods for the reduction of the number of fault pattern vectors of the given set and for the reduction of the dimensions of those fault pattern vectors are studied.

A concurrent fault recognition module for combinational circuits can be implemented using a small set of fault pattern vectors, as stated in [Kochte et al., 2009]. In that publication, they use a small set of fault pattern vectors for the so called random pattern resistant faults, which are faults that can not be covered by a random generated testing set. For a self-repairing circuit, the set of fault pattern vectors to be used can be prepared to cover only critical faults. A review of techniques for the reduction of the hardware overhead produced by such a concurrent fault recognition module for combinational circuits by using unspecified values is done.

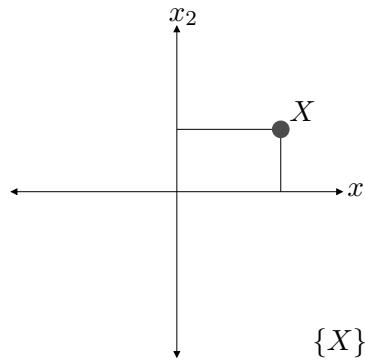

In the case of combinational or sequential circuits, the pattern vectors are vectors that contain one-bit binary value components. In case of hardware cores with, e.g., 32-bit floating point inputs and outputs, or analog hardware modules which have input and output signals

with continuous values, the fault pattern vectors are vectors that contain real value elements. In the last case, reduction of the given set of fault pattern vectors is necessary. Since fault-recognition can be inspired by methods that the biological immune system uses for finding illnesses, suitable methods were searched in the field of artificial immune systems. A special attention has been devoted to the cytokine Formal Immune Network method presented in [Tarakarov, 2008], because it performs reduction of fault pattern vectors and considers a class associated with each fault pattern vector, named cytokine, field which can be assumed to be the recovery mechanism. Besides, that method allows self-learning, which is understood as the addition of new fault pattern vectors online without requiring a recomputation of the transformation matrix used for fault pattern vector dimension reduction.

The recovery procedure is normally hardware platform dependent. However, techniques such as redundancy and partial reconfiguration can be used for many hardware platforms, reason why a hardware platform with an FPGA that supports partial reconfiguration has been used. Although, Xilinx FPGAs are SRAM-based and consequently prone to single event upsets, this thesis assumes that repairing should be executed when a permanent fault, rather than a transient fault, is detected. A permanent fault is modeled as a stuck-at fault and a fault injection module that inserts such faults for testing the self-repairing system in the simulation and in the final implementation is added to the self-repairing architecture.

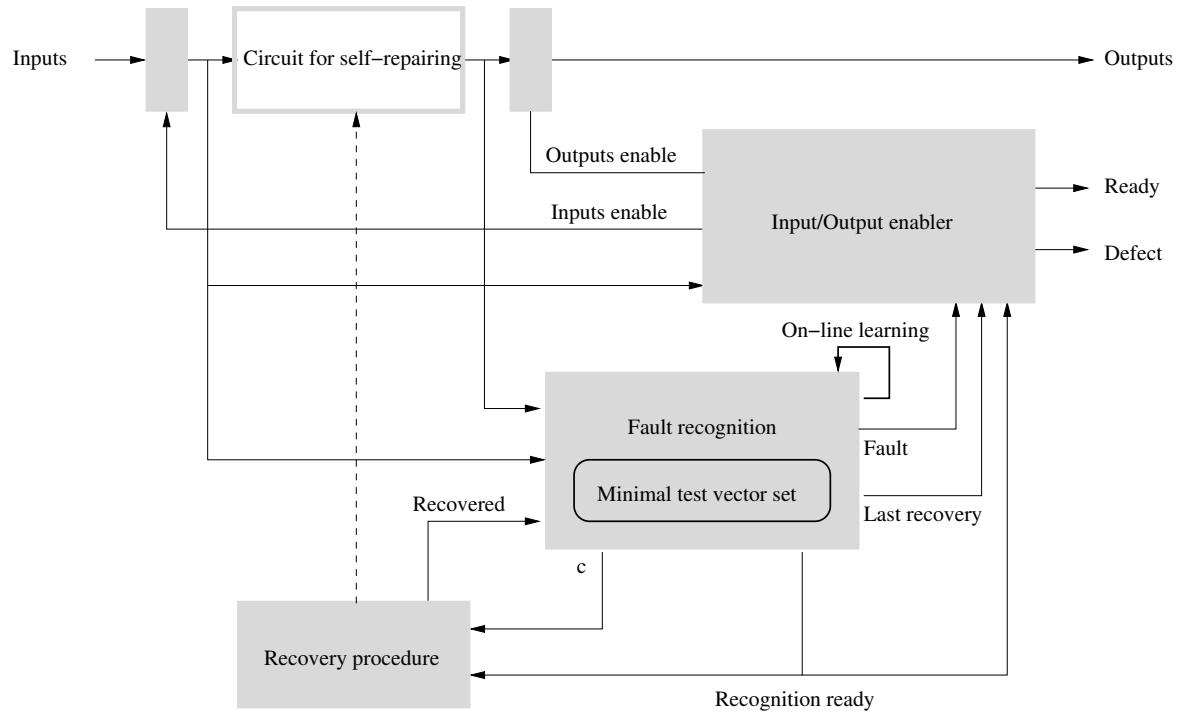

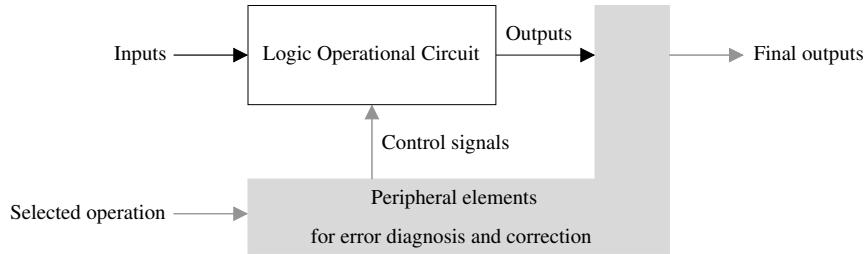

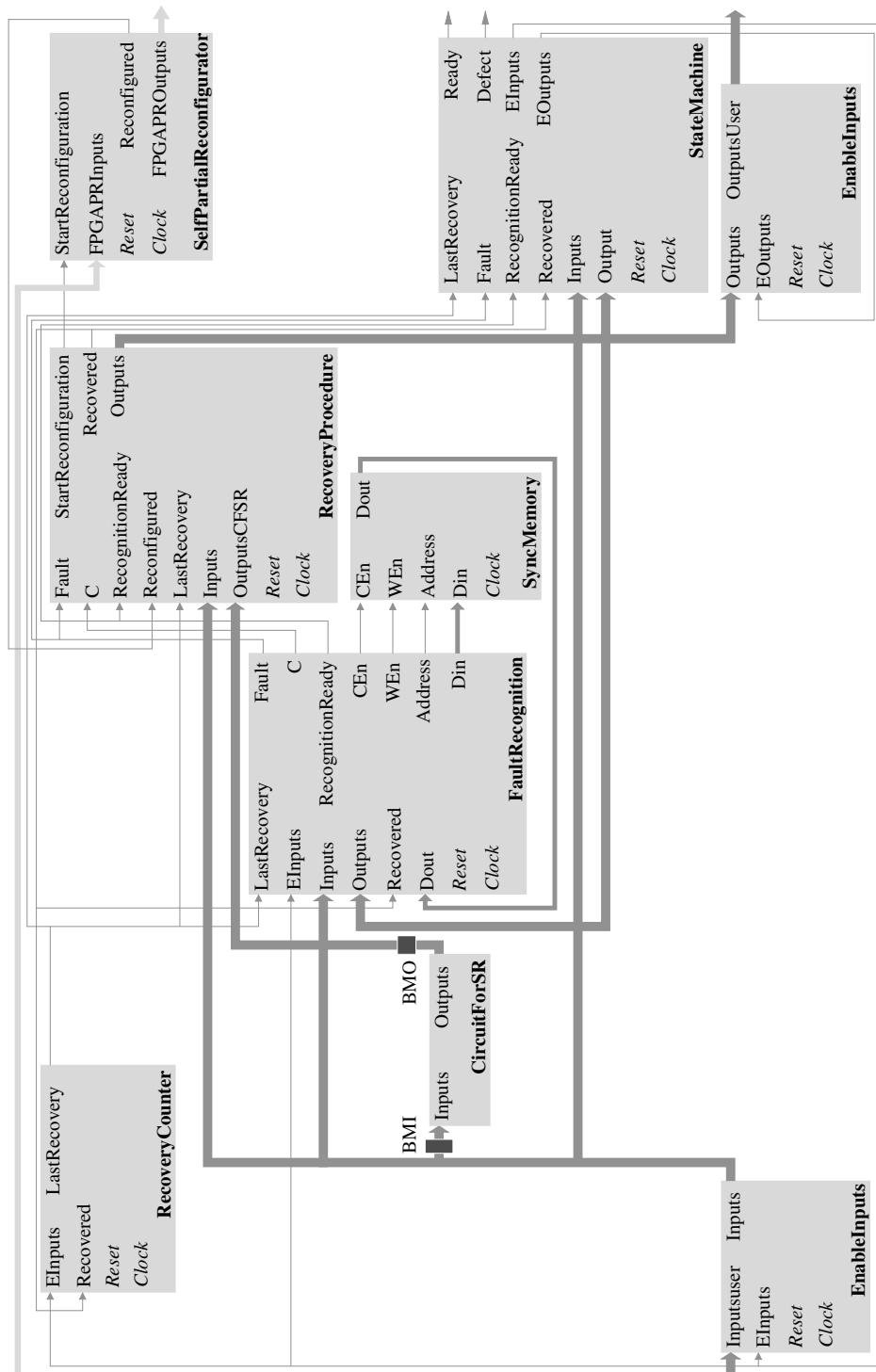

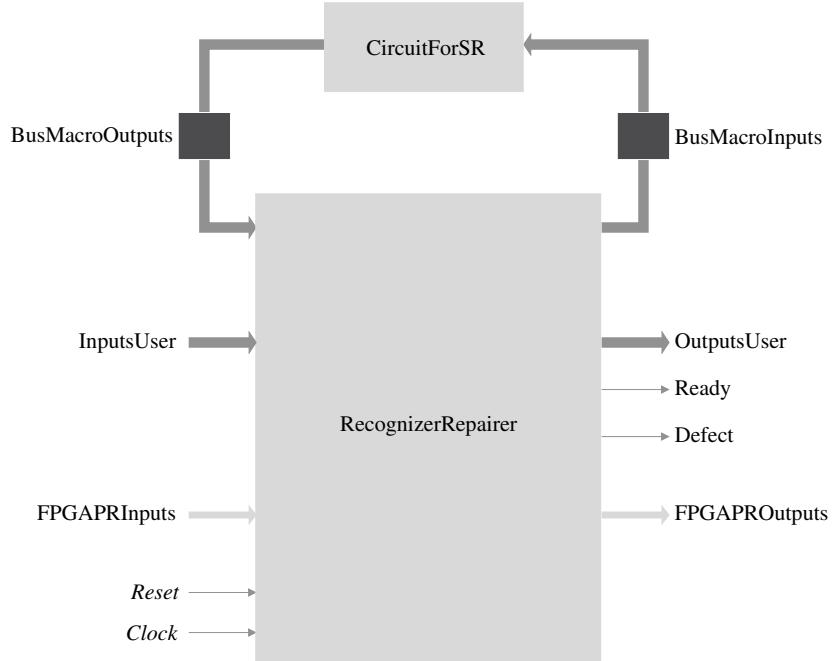

The self-repairing architecture, shown in figure 1.3, applies some ideas of the self-repairing architecture taken from [Marinos, 1969] and shown in figure 1.4. That architecture considers an Input/Output Enabler which permits that only a verified result is present at the outputs. That feature is useful in the design of safety critical systems<sup>1</sup>, which are systems that require fail-safe outputs, please refer to [Sutton, 2012]. A verified output is flagged by the output *Ready*, which can be seen in figure 1.4. After a determined number of failed recoveries, the system flags an unrecoverable defect in the system by means of the signal *Defect*, which can be seen on the same figure 1.4. In that case, the outputs maintain the verified value of the prior inputs, guaranteeing a fail-safe state of the system.

The hardware description language used for describing the self-repairing architecture is VHDL. The description proposes the delivery of modules, that is to say prepared template code for designing self-repairing hardware systems, inspired by the work in [Entrena et al., 2001] and briefly explained in section 2.4.1.

### 1.3 Organization of this work

This thesis is organized in more seven chapters with the following content. Chapter 2 presents briefly the work related to this thesis in the current literature and comments their differences and weaknesses. Chapter 3 provides a biological background, models and algorithms of artificial immune systems. That chapter explains biological concepts for non-biologists, provides the most known artificial immune algorithms with their pseudocodes, and gives a comparison mentioning the application of each algorithm. Chapter 4 deals with fault recognition concepts and thereafter concentrates on methods of fault recognition for systems whose fault pattern vectors contain real elements. That chapter explains mathematically the cytokine Formal Immune Network algorithm presented in [Tarakarov et al., 2005] and its similarities to the Principal Component Analysis algorithm for dimension reduction. Chapter 5 presents the

---

<sup>1</sup>A safety critical system is a system whose failure can produce injury to people or damage to the environment or equipment, reason why upon a failure the system should automatically become safe.

### 1.3. Organization of this work

Figure 1.3: Self-repairing architecture

Figure 1.4: LOC and peripheral elements required for error diagnosis and correction (abstracted from [Marinos, 1969] ©1969 IEEE)

implementation and evaluation of the algorithms presented in chapter 4, which are adequate for fault pattern vectors with real value elements that proceed from complex digital systems such as hardware cores or analog systems. The second part of chapter 5 presents methods for reducing the hardware overhead of a concurrent fault recognition module for combinational circuits by using the unspecified values of its fault pattern vectors that have one-bit binary value elements. Chapter 6 presents the self-repairing architecture described in VHDL, its simulation and implementation. The last chapter exposes the major contributions of this thesis and lists possible further work. This thesis is organized in nearly independent chapters. That means that each chapter is understandable without reading prior chapters unless chapter 5, which requires the understanding of the algorithms presented in chapter 4.

## 1.4 Bibliography

Bolchini, C., Sandionigi, C., Fossati, L., and Codinachs, D. M. (2011). A reliable fault classifier for dependable systems on SRAM-based FPGAs. In *17th International On-Line Testing Symposium - IOLTS 2011*. IEEE.

Entrena, L., López, C., and Olías, E. (2001). Automatic Insertion of Fault-Tolerant Structures at the RT Level. In *7th International On-Line Testing Workshop*, pages 183–200. 48-50.

Gössel, M., Ocheretny, V., Sogomonyan, E., and Marienfeld, D. (2008). *New Methods of Concurrent Checking*. Frontiers in Electronic Testing. Springer.

Kochte, M. A., Zoellin, C. G., and Wunderlich, H.-J. (2009). Concurrent Self-Test with Partially Specified Patterns For Low Test Latency and Overhead. In *14th European Test Symposium*, pages 53–58. IEEE Computer Society.

Koren, I. and Krishna, C. M. (2007). *Fault Tolerant Systems*. Morgan Kaufmann.

Lala, P. K. (2000). *Self-Checking and Fault-Tolerant Digital Design*. Morgan Kaufmann.

Marinos, P. N. (1969). The Organization of a Self-Repairing System from Multifunctional Units. *Proceedings of the IEEE*, 57(7):1320.

Sharma, R. and Saluja, K. K. (1988). An Implementation and Analysis of a Concurrent Built-In Self-Test Technique. In *18th International Symposium on Fault-Tolerant Computing - FTCS 18*, pages 164–169. IEEE.

Sutton, A. (2012). No Room for Error: Creating Highly Reliable, High-Availability FPGA Designs. Technical report, Synopsis.

Tarakanov, A., Goncharova, L., and Tarakanov, O. (2005). A Cytokine Formal Immune Network. In *8th European Conference on Advances in Artificial Life - ECAL 2005*, volume 3630 of *Lecture Notes in Computer Science*, pages 510–519. Springer.

Tarakanov, A. O. (2008). Formal Immune Networks: Self-Organization and Real-World Applications. In Prokopenko, M., editor, *Advances in Applied Self-organizing Systems*, Advanced Information and Knowledge Processing, pages 271–290. Springer.

# 2

---

## Related work

Research in the area of self-repairing hardware systems addresses: different types of faults, e.g., transient or permanent faults regarding its persistence; different types of hardware platforms, e.g., Field Programmable Gate Arrays, Programmable Systems on Chips, etc; and different levels of abstraction, e.g., system level, Register Transfer Level (RTL), gate level, transistor level, etc. Similar approaches usually differ on the employed error detection method, recovery mechanism, or system architecture, which in some cases are inspired by biological systems.

The revised work has been organized in the following sections: general work done on self-repairing hardware, approaches inspired by biological systems, work done on introducing self-repairing in the FPGA fabric, and finally work done on self-repairing introduced in the description of hardware systems. A subsection is devoted for each specific work, in which the principle is introduced with the help of a figure abstracted from the respective publication when necessary. At the end, a section is devoted to comments regarding the differences and the shortcomings of the different approaches. It is not strictly necessary to keep on reading sections 2.1, 2.2, 2.3 and 2.4.1 which introduce briefly the different approaches. It can be skipped to the section 2.5 devoted to comments and on demand or by interest look at the respective referenced subsection.

### 2.1 Self-repairing hardware

This section introduces work done in the field of self-repairing hardware systems in general, leaving approaches inspired by biological systems and work done on self-repairing of the FPGA fabric aside.

Figure 2.1: LOC and peripheral elements required for error diagnosis and correction (abstracted from [Marinos, 1969] ©1969 IEEE)

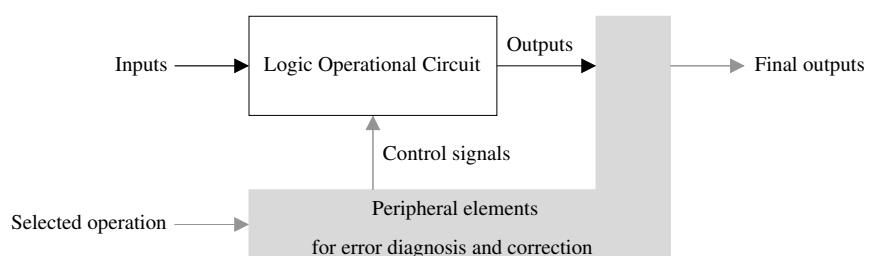

### 2.1.1 Multifunctional units

One of the most earlier publications on self-repairing systems and main reference in this thesis is the letter of Peter N. Marinos named “The Organization of a Self-Repairing System from Multifunctional Units”, please refer [Marinos, 1969]. It proposes the design of a self-organizing system using multifunctional devices, which give to the system a high flexibility in the configuration of its functioning and a capability of self-repair. A multifunctional logic device contains a so called logic operational circuit, shown in figure 2.1, which besides inputs and outputs, has control signals for selecting the operation  $f_i$  to be performed. In order that upon a failure, the logic operational circuit is able to perform the same operation but error free, each one of the operations  $f_i$  has assigned additional values for the control signals. Thus, the values of the control signals can be partitioned into classes, a class corresponding to each function  $f_i$ . The peripheral elements required for the error diagnosis and correction of a logic operation unit are shown in figure 2.1. In this work the idea of having a multifunctional logic device for a self-organizing and self-repairing system, the arrangement of peripheral elements for error detection and correction, and the partitioning of the states of a self-repairing automaton in classes are valuable.

### 2.1.2 Dynamic partial reconfiguration for testing and repair

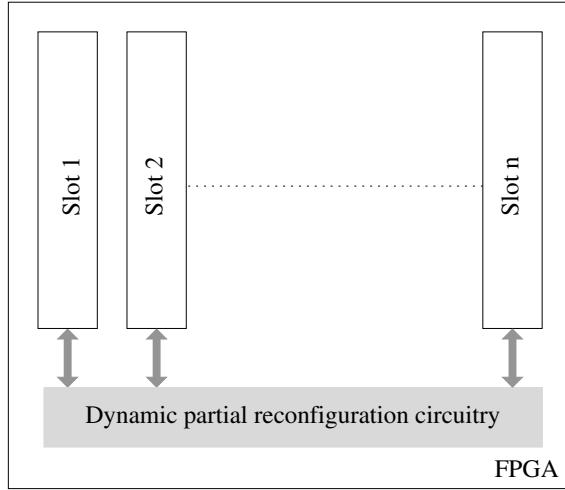

A Field Programmable Gate Array, in short FPGA, is an integrated circuit with programmable logic. The programmable logic allows to configure the functionality of the circuit after the manufacturing of the chip. Chip is a typical name given to an integrated circuit. By some FPGA chips it is possible to program only a part of its programmable logic while the remaining logic is operating, process named as dynamic partial reconfiguration. Dynamic partial reconfiguration can be used for implementing a large circuit into an FPGA that does not present enough hardware resources. The work shown in the publications [Paulsson et al., 2006b] and [Paulsson et al., 2006a] suggests using dynamic partial reconfiguration of an FPGA not only for implementing a given circuit, but also for detecting errors on it and for its recovery in the case of a detected error. For that, the FPGA is partitioned into slots which are partial reconfigurable regions able to contain a circuit partition each, as shown in figure 2.2. For error detection, a test bench module, created for testing a single slot or the circuit partition implemented in that slot, is configured into the FPGA when a slot is available. How the test bench module should be designed and executed is not mentioned, but it is recommended to restrict the testing time in order of not interfering the overall circuit operation. N-modular redundancy is a method of fault masking, where  $n$  copies of a circuit partition get the same

## 2.1. Self-repairing hardware

Figure 2.2: Partial reconfigurable regions in the FPGA as slots for dynamic partial reconfiguration (abstracted from [\[Paulsson et al., 2006a\]](#) ©2006 IEEE)

input data and deliver their outputs to a voter, which gives as final output the output of the majority. A subcase of  $N$ -modular redundancy with  $N = 3$  is the so called Triple Modular Redundancy, in short TMR. Triple Modular Redundancy, where the copies of the circuit partition and the voter module are implemented in different slots using dynamic partial reconfiguration, named as dynamic TMR, is suggested as a second method for error detection. As recovery strategies are suggested the partial reconfiguration of a failed circuit partition in the same slot, the partial reconfiguration of a failed circuit partition in a different slot, and the blocking of a slot for future use when faulty. Although the presented testing strategies can be useful for large circuit that use dynamic partial reconfiguration for its implementation, for other circuits the complexity of the required controller looks too high.

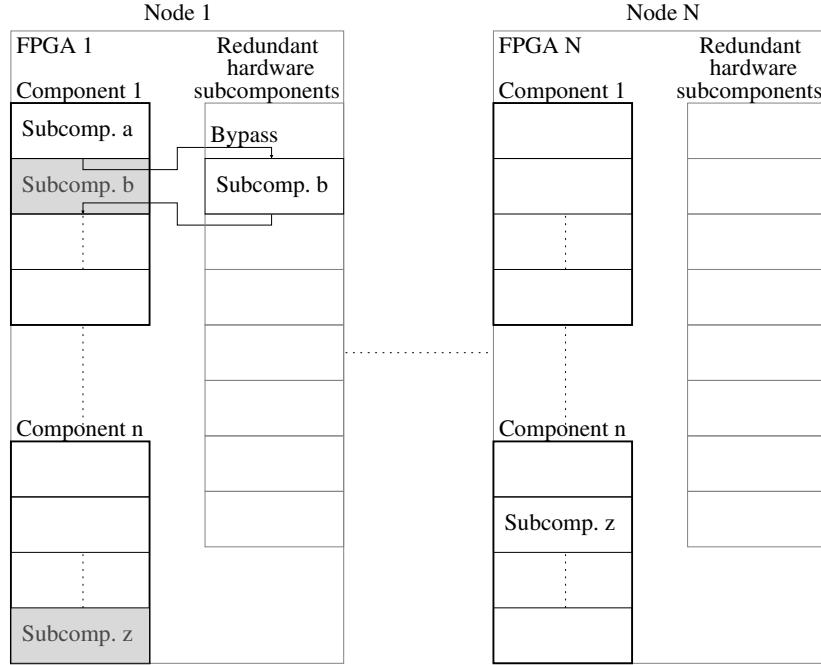

### 2.1.3 Distributed self-repairing of a network of FPGA nodes

Self-repairing for a network of nodes composed each one of an FPGA board attached to a wireless networking module is presented in [\[Venishetti et al., 2007\]](#), [\[Sreeramareddy et al., 2008\]](#), [\[Akoglu et al., 2009\]](#) and [\[Sreeramareddy et al., 2010\]](#). Thereby, self-repairing is executed at the node and at the network levels. For the determination if a node presents an error or not, the circuits implemented in the FPGA of each node are partitioned into components and subcomponents. Built-in self-testing hardware is added to each component. Thereby, a Linear Feedback Shift Register, in short LFSR, is used for generating pseudo-random input test patterns, and a Multiple Input Shift Register, in short MISR, is used for compressing the output vectors generating a signature. The generated signature is compared with the expected signature stored in extra memory. If a mismatch is detected, testing at the subcomponent level, only for that component, is triggered. Subcomponent testing is performed by applying test pattern vectors stored in memory at the inputs and by subsequently comparing the vectors at the outputs with the respective expected output vectors stored also in memory. Upon a mismatch, partial reconfiguration of the failed subcomponent is initiated. That process is able to counteract a temporary fault produced for example by a bit flip in an internal register of the FPGA. If the error remains after partial reconfiguration, it means that a permanent

Figure 2.3: Subcomponent self-repairing (abstracted from [Akoglu et al., 2009] ©2009 Springer)

hardware fault in the FPGA area occupied by the subcomponent is present. Therefore, a redundant hardware module that implements the subcomponent functionality and placed in another area on the FPGA is enabled and connected diverting the data lines to and from the subcomponent, as shown in figure 2.3. If a further error in the same subcomponent is present and if all available redundant hardware modules that implement the failed subcomponent functionality are exhausted, fault information is provided to the wireless networking module of the node. That module sends information about the failed subcomponent to the master node, which reassigns the task of the failed subcomponent to another node in the network. Reassignment of tasks is also done by the master node when it perceives, by polling, that a node fell down. One observation about this work is that it does not consider as an issue the time that self-testing of components and subcomponents take and the frequency in which self-testing is triggered. Besides, it does not mention that a component should go off-line in order to execute self-testing using LFSR and MISR. Nevertheless, in [Sreeramareddy et al., 2010] it is proposed the use of partial bitstream relocation, in short PBR. The partial bitstream relocation method, taken from [Sudarsanam et al., 2009], allows firstly the reduction of the time that partial reconfiguration of a subcomponent takes and secondly the subcomponent relocation to an empty partial reconfigurable region in the FPGA on the fly. All that, by using only the frame data part of the partial bitstream of the subcomponent, saved in Block RAM memory in the FPGA instead of in external memory, for the partial reconfiguration.

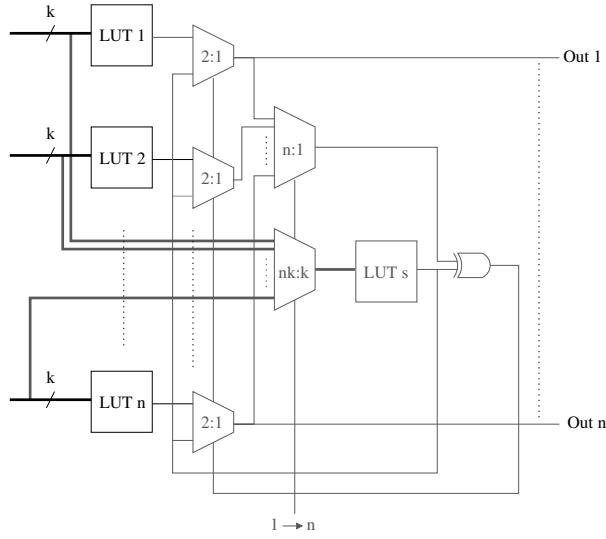

#### 2.1.4 Small-scale reconfigurability for fault detection, diagnosis and recovery

The work presented in [Kumar and Lach, 2003] considers to decompose a circuit to the cone level. Where a cone is a combinational block with many inputs, but only one output. An

## 2.1. Self-repairing hardware

Figure 2.4: Cone-level fault detection, diagnosis and recovery (abstracted from [Kumar and Lach, 2003] ©2003 IEEE)

SRAM-based  $k$ -input lookup table, in short  $k$ -LUT, can implement the functionality of any cone that has as a maximum  $k$  inputs. For fault detection, one of the  $k$ -input lookup table executes redundant computation of all  $n$  cones in a rotating manner. That is possible by using the multiplexer  $nk : k$  shown in figure 2.4. Then, the output of the rotating  $k$ -LUT is compared with the output of the selected cone through a XOR gate. When a fault at the cone is flagged by that XOR gate, the  $k$ -LUT can be permanently configured to implement the functionality of the faulty cone. That can happen when the  $nk : k$  multiplexer selects the inputs of the faulty cone and the  $2 : 1$  multiplexer at the output of the faulty cone selects the LUT output, as can be seen also in figure 2.4. What this work does not mention is how the select lines of all multiplexers are controlled.

### 2.1.5 Logic self-repair

The work in [Koal et al., 2012], [Koal et al., 2011], [Koal et al., 2009], [Koal and Vierhaus, 2008] and [Kothe and Vierhaus, 2006] intends to adapt existing self-repairing approaches for memories and regular logic, like FPGAs, to logic designs. This work relies on the idea that there exist functional units in a logic design which are implemented multiple times, or seen from another side, the design is built out of regular components, e.g., ANDs, ORs, XORs, blocks of gates, adders, ALUs, etc. Out of such identical functional units or regular components in a logic design, a reconfigurable logic block, in short RLB, is proposed. Such RLB is provided with one spare unit that can serve for replacing a faulty functional unit by controlling some MUXs in the required way, the same way as shown in subsection 2.1.4 and figure 2.4 where a functional unit is a Look Up Table. The functional units in an RLB can be tested at start-up for encountering production faults, or in idle times during operation for encountering wear-out defects. The test is proposed to be done by a built-in self-test module which executes a cyclic test of all functional units in the RLB. Thereafter, when a functional block is encountered faulty, a built-in self-repair module configures the multiplexers in the way that the spare unit replaces the faulty functional unit. Furthermore, for more flexibility,

in [Koal et al., 2009] it is proposed a regular switching scheme for the inputs and the outputs instead of multiplexers. With such a switching scheme and more spare units in the RLB, triple modular redundancy is proposed for safety critical functional units that have hard real time constraints. Regarding the granularity of a functional unit, it is recommended to apply redundancy through RLBs in functional units with more than 400 transistors due to the enormous overhead that redundancy can bring with in units with less granularity. It is important to note that this approach is dependent on the regularity of the logic and requires a method for finding such regularity.

### 2.1.6 Dual-FPGA architecture for autonomous self-repair

An architecture for autonomous self-repair with two FPGAs with a soft microcontroller each is presented in [Mitra et al., 2000] and [Mitra et al., 2004]. The function of the soft microcontroller in the first FPGA is to reconfigure the second FPGA and vice versa. For that, it must be assured that the communication between FPGAs, the bus, the memory that stores the alternative FPGA configurations, and the reconfiguration circuitry, are reliable. Three issues in autonomous self-repair are: concurrent error detection, fault location, and recovery. Since, the dual-FPGA architecture has been developed at the Stanford Center for Reliable Computing within the Reliability Obtained by Adaptive Reconfiguration project, in short ROAR, many techniques have been studied to cope with the issues of an autonomous self-repair. Those techniques are shortly listed with references below organized regarding the type of fault that they address by the detection, recovery and fault location.

Faults can be transient or permanent. Transient faults in an FPGA can be distinguished between: transient faults that affect the configuration of the FPGA; and transient faults that affect the user application data, when memory modules have been implemented using the Configurable Logic Blocks, in short CLBs, of the FPGA.

For concurrent error detection implemented in hardware, techniques for the detection of transient faults that affect the configuration of the FPGA are: the synthesis of a circuit with a parity check code towards a self-checking circuit, please see [Touba and McCluskey, 1997] and [Zeng et al., 1999]; and the use of design diversity for the design of a redundant circuit for error detection, please see [Mitra, 2000]. The last technique considers a model of a common failure mode, which is a failure present by using simple circuit duplication without considering diversity in the design.

For concurrent error detection implemented in software, in [Oh, 2000] the following techniques that address transient faults in the application memory are presented: Control Flow Checking by Software Signatures, where signatures are embedded into the program during compilation and compared with run-time signatures during execution; Error Detection by Duplicating Instructions, where instructions are duplicated at compile-time; and Error Detection by Diverse Data and Duplicated Instructions, where a program is compiled to a new program with diverse data.

A concurrent detection of permanent faults is a challenge. Some design attempts are the following: a built-in self-test circuitry in all subcircuits, using a reduced number of built-in seeds and encoded in the circuitry not in memory, please see [Al-Yamani, 2004]; the use of patterns stored in memory for testing the functionality of the circuit or subcircuits, please see an approach at [Li et al., 2008], [Mitra, 2008] and [Li et al., 2010]; the use of self-checking circuits designed using diverse duplication and organized in a pipeline fashion, where the outputs of the checkers are taken out through an scan chain towards a controller placed in

## 2.2. *Self-repairing approaches inspired by biological systems*

the second FPGA, please see [Mitra et al., 2004]; and finally, the reduction of the number of test configurations for an exhaustive test of defects on the hardware of the FPGA, please see [Chmelar, 2004b] and [Chmelar, 2004a].

For the recovery of the circuit from transient faults that affect the configuration of the FPGA, a fault free configuration can be loaded in the FPGA using partial reconfiguration. In case the transient faults affect the user application data, rollback and roll-forward techniques can be employed for recovery, see one approach at [Yu, 2001]. However, through partial reconfiguration, the content of the user application data can be altered. For that, the dirty bit memory coherence technique is presented in [Huang, 2001] and [Huang and McCluskey, 2001], which associates a bit for flagging a possible threat to a column of CLBs containing a CLB that has been configured as memory.

For the fault location and recovery of the circuit from a permanent fault, column based precompiled configurations having an intentionally unused column are used for blind reconfiguration, where all possible precompiled configuration are loaded one after another until a configuration that avoids the fault is found, please see [Mitra et al., 2004].

## 2.2 Self-repairing approaches inspired by biological systems

Some approaches for self-repairing hardware systems are inspired by biological processes. Some of the most important approaches are introduced below.

### 2.2.1 Immune system paradigm

It is an approach presented in [Avizienis, 2002], which proposes to insert a subsystem analogous to the immune system of the human body into a hardware system. That subsystem is called Fault Tolerance Infrastructure, in short FTI, and it follows a set of design principles which are based on key attributes of the human immune system. Taking those attributes, the FTI first of all must be software-independent, consist of hardware and firmware elements only, be distributed, have its own communication links, and have a fully fault-tolerant implementation. The proposed FTI in [Avizienis, 2006], which principles evolved from the Test-and-Repair processor STAR presented in [Avizienis et al., 1971], is a system composed of four types of controllers called nodes, which are implemented using read-only microcode.

The nodes in a FTI are responsible of protecting a computing node **C**. In particular, the so called monitor node **M** receives error messages from the computing node through an adapter node **A** and sends appropriate recovery commands. Those recovery commands are stored in read-only memory in the monitor node. For fault tolerance purposes there are more than one monitor nodes which are connected through an special bus. A monitor node is connected to the startup, shutdown and survival node **S3**. The functions of that node are to control the power-on, power-off, to provide a non-volatile and radiation hardened storage for system time and configuration, and to indicate the health status of the computing node. The **S3** node has been separated from the monitor node **M** to make the node that must survive catastrophic events as small as possible. The fourth type of node, the decision node **D**, provides decision services for N-version software executing on diverse computing nodes. Besides, that node serves as a communication link between the software implemented in a computing node and the monitor node.

The FTI can be placed in a hardware component, or it can be employed to protect a board with several components as shown in detail in [Avizienis, 2000]. Another option is to build a

hierarchy of FTIs, which requires dedicated communication links among them. Furthermore, considering that a self-organizing system is composed of agents, the immune system paradigm is proposed to be also employed implementing an FTI in each of the agents, please refer to [Avižienis, 2006].

### 2.2.2 POEtic tissue

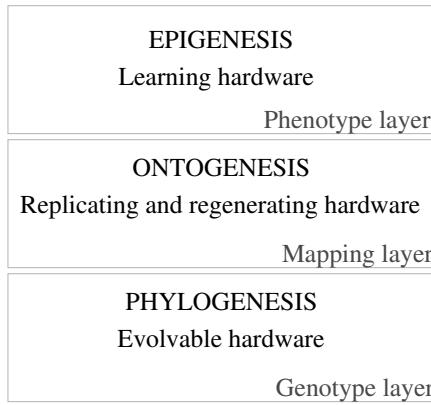

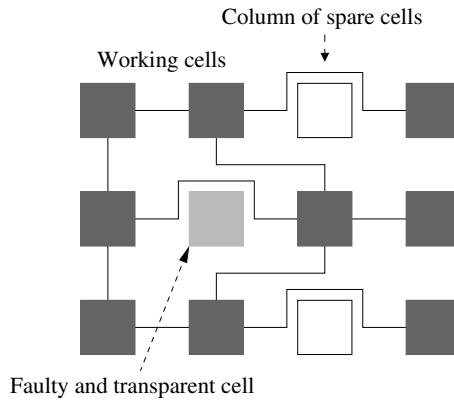

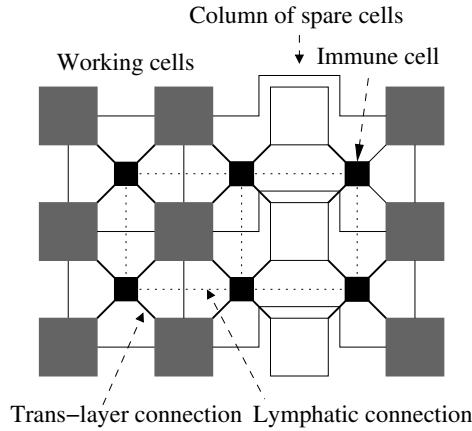

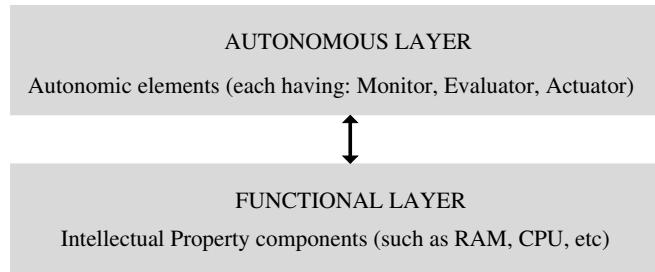

In an attempt to classify hardware systems inspired by biology, three inspiring domains of biology: Phylogenesis, Ontogenesis and Epigenesis, were identified in [Sipper et al., 1997], resulting in the three axes of the POE model. Phylogenesis is defined as the development or evolution of a particular group of organisms [Dictionary.com, 2012]. Ontogenesis is defined as the development of an individual organism from embryo to adult [Dictionary.com, 2012]. Epigenesis is defined as the development of an organism considering the action of the environment [Dictionary.com, 2012]. In those three domains, remarkable approaches are: in the domain of Phylogenesis, *Evolvable hardware* which is motivated by the concept of evolution of a group of organisms; in the domain of Ontogenesis, *Replicating and regenerating hardware* which most important example is *Embryonics* that is motivated by the concept of the development of a multicellular organism from a mother cell; and in the domain of Epigenesis, *Learning hardware* which most important example is *Immunotronics* that is motivated by the concept of the development of an organism by learning.