# **Quality Metrics Driven Functional Verification for IP based SoC Design**

Dissertation

A thesis submitted to the

Faculty of Computer Science, Mathematics and Electrical Engineering

of the University of Paderborn in partial fulfillment

of the requirements for the degree of Dr. ret. nat.

by

**Tao Xie**

Paderborn, October 2013

*Supervisors:*

1. Prof. Dr. rer. nat. Franz J. Rammig, University of Paderborn

2. Prof. Dr. rer. nat. Sybille Hellebrand, University of Paderborn

## Abstract

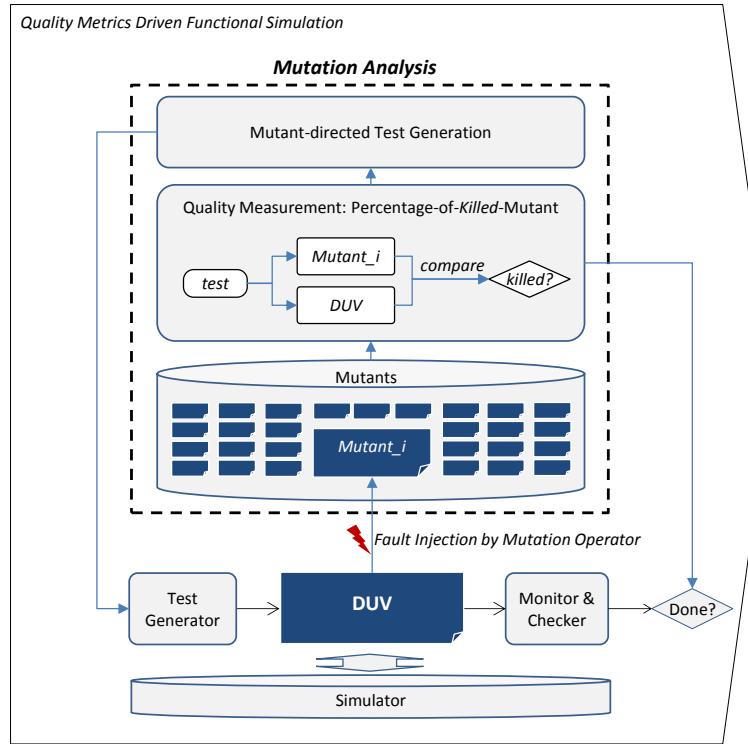

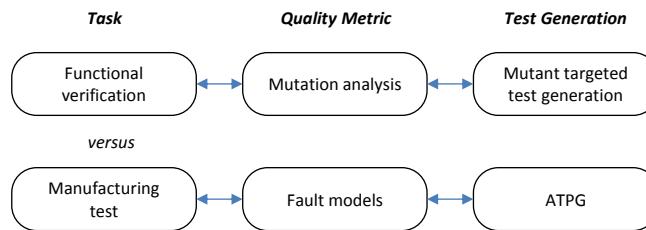

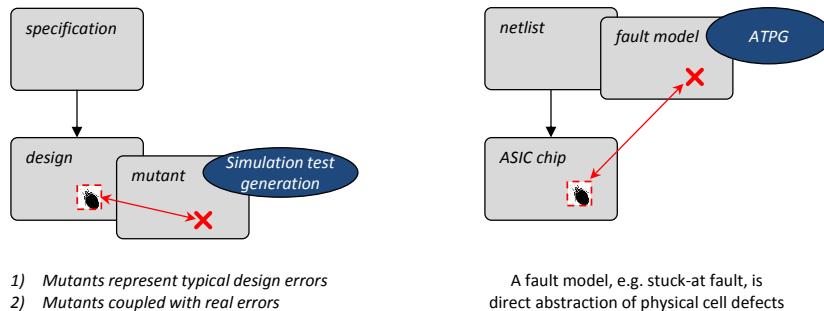

System-on-a-Chip (SoC), centered at reuse of silicon Intellectual Properties (IPs) and characterized by separation of IP development and SoC system integration, becomes a dominant paradigm for designing electronic systems. Complexity of both IP and SoC system design grows exponentially and challenges the functional verification of these designs. In this context, we consider it a necessity to have a systematic management of verification quality by applying quantitative metrics. Therefore, the dissertation has the general goal of establishing a beyond-state-of-the-art, *metrics-driven verification methodology* that i) employs automated methods to efficiently improve the verification quality measured under such metrics and ii) extends the application of these metrics to accommodate emerging SoC system-level design language. *Mutation analysis* is the focused metric in this research for developing new methods. It has a unique, complex test generation problem to detect (*kill*) an error-injected design (called a *mutant*).

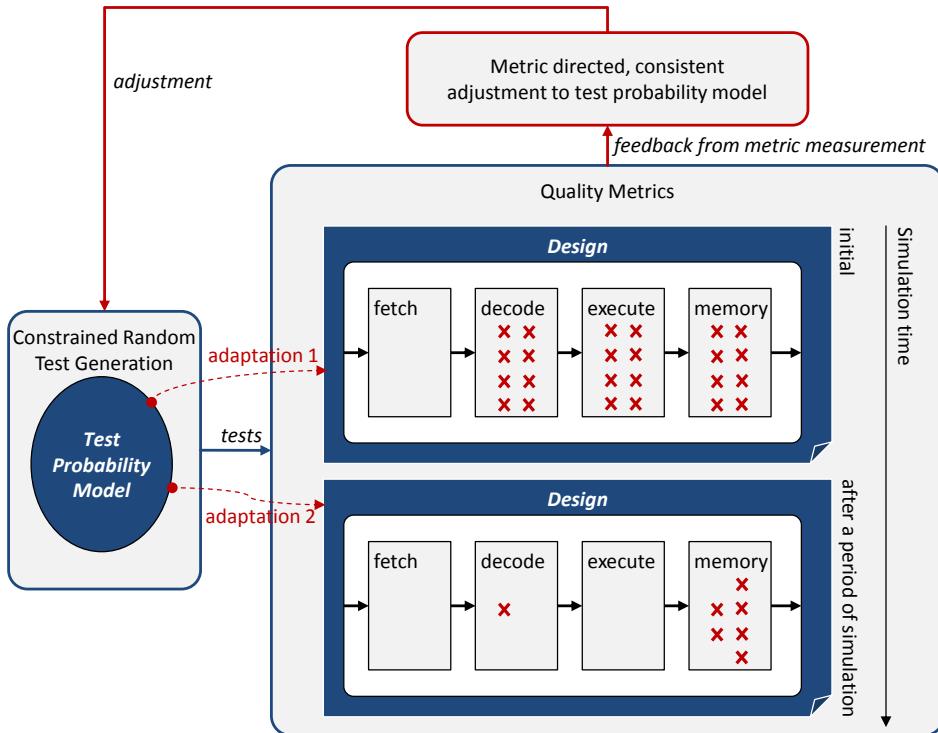

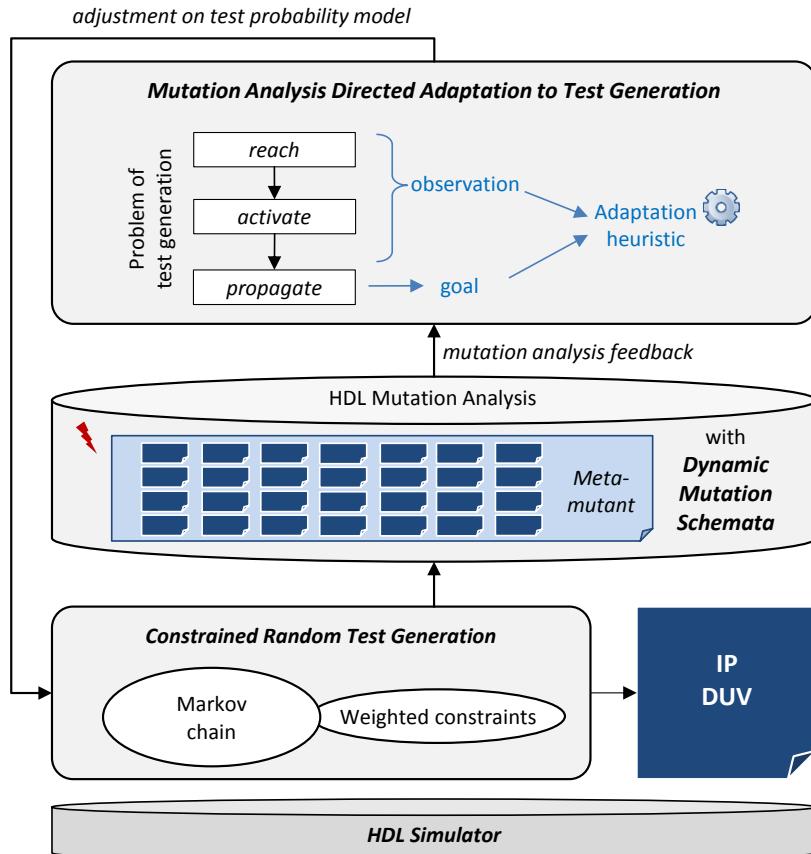

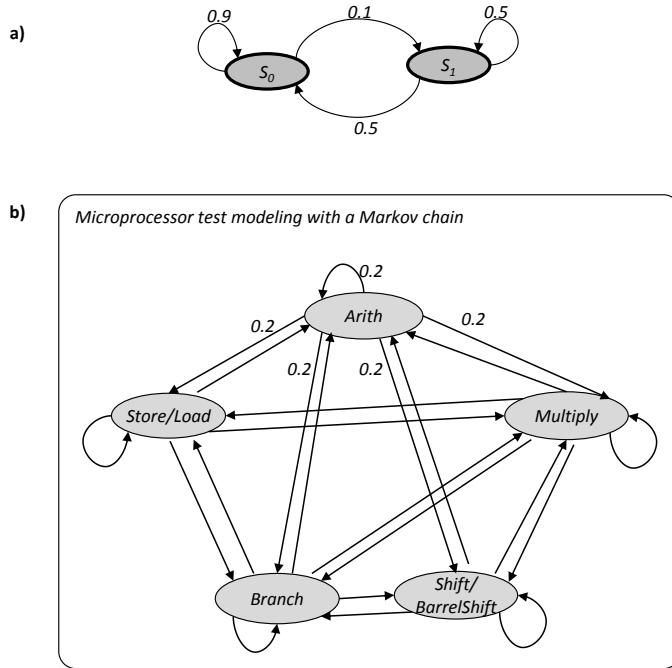

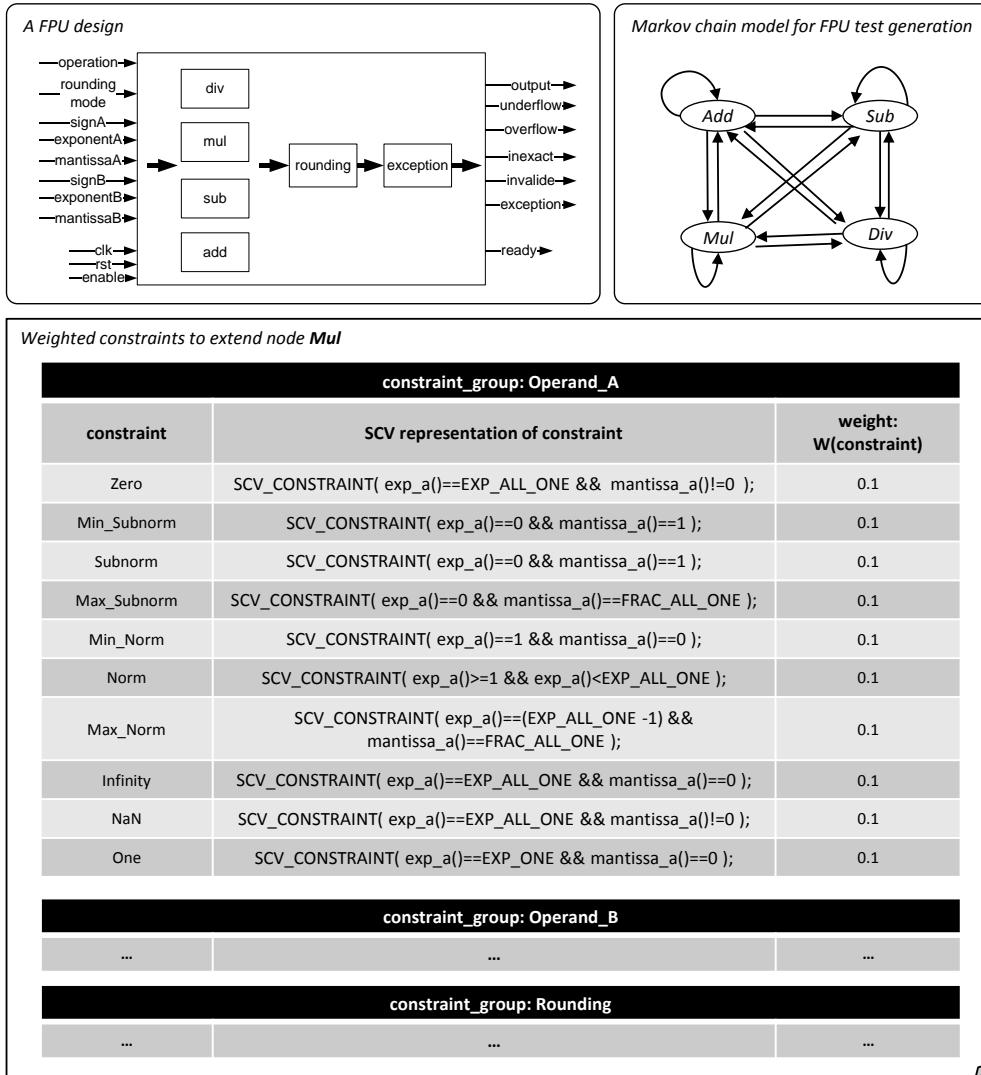

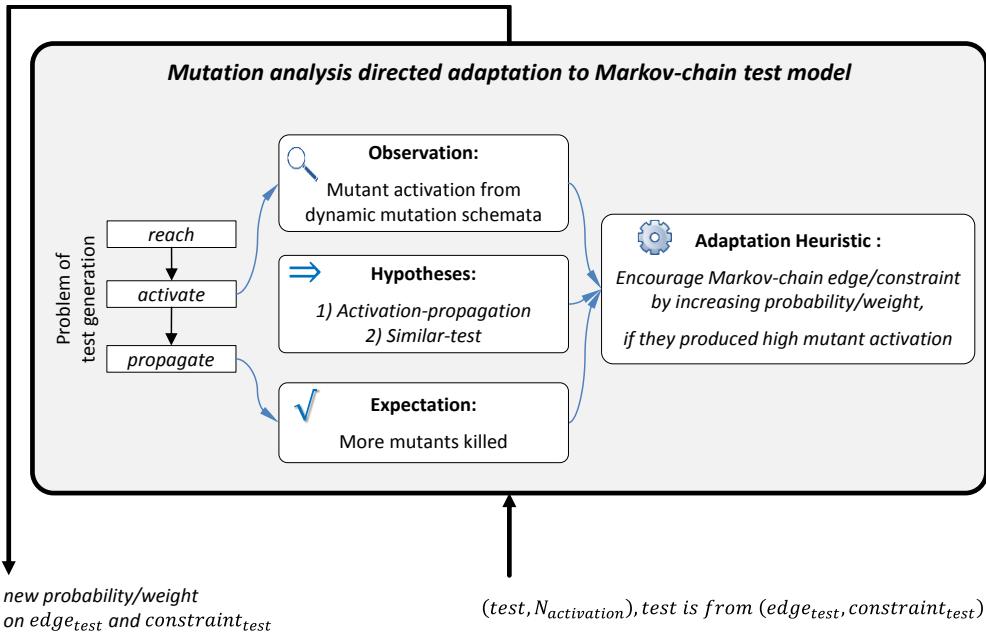

At IP level, verification handles designs in traditional hardware description languages (HDLs) and *mutant-targeted automatic test generation* is the main objective. Firstly, random simulation is considered appropriate for achieving a primary level of verification quality under mutation analysis, where we see the specific problem that random test generation becomes inefficient as being not metrics-tailored. An *adaptive random simulation* method is developed. Based on a modeling of random tests with Markov chain and constraints, the simulation process is continuously steered by a heuristic towards tests that are regarded more efficient in killing mutants. The experiments show that this adaptive simulation is effective of having more mutants killed with less simulation.

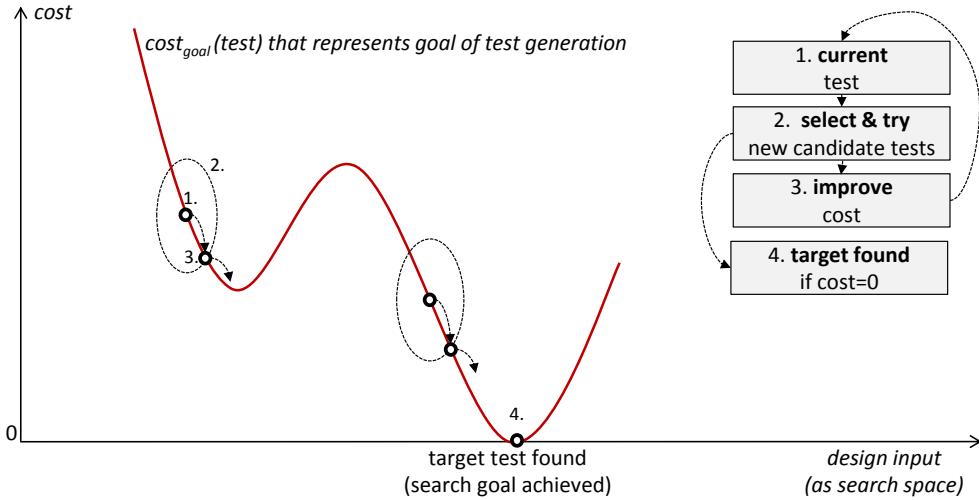

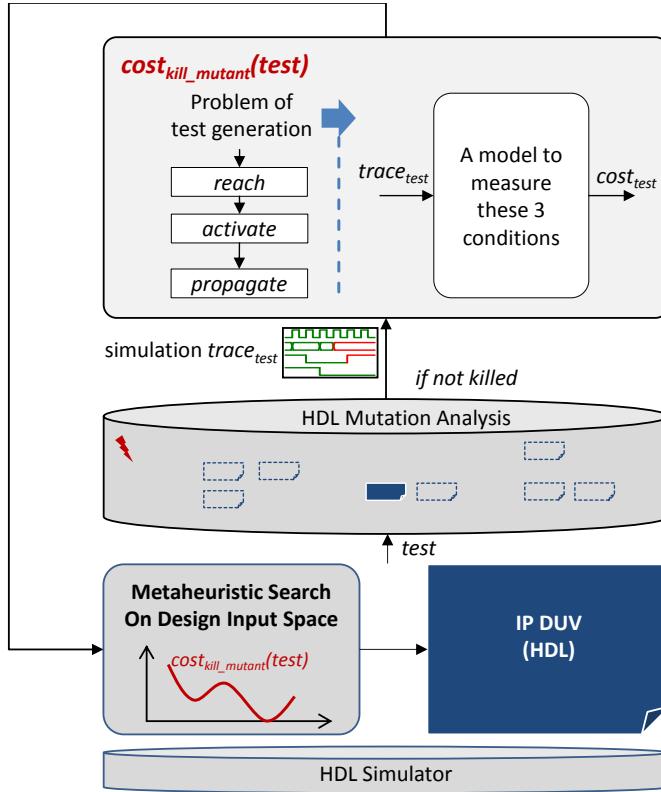

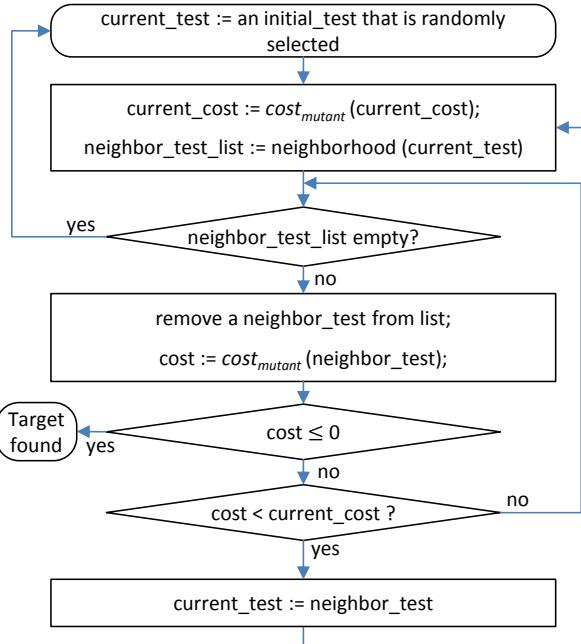

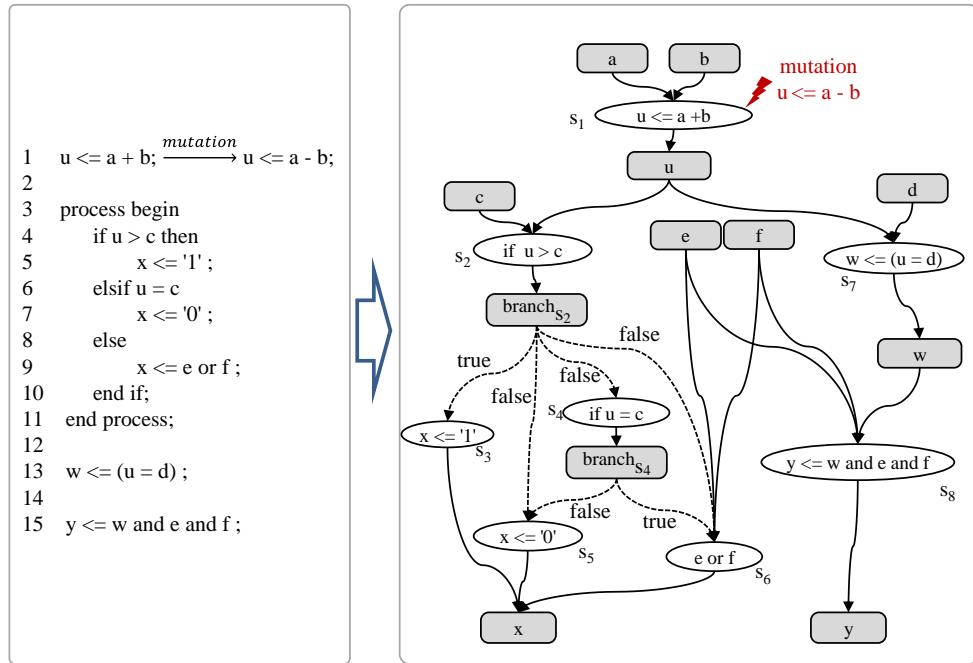

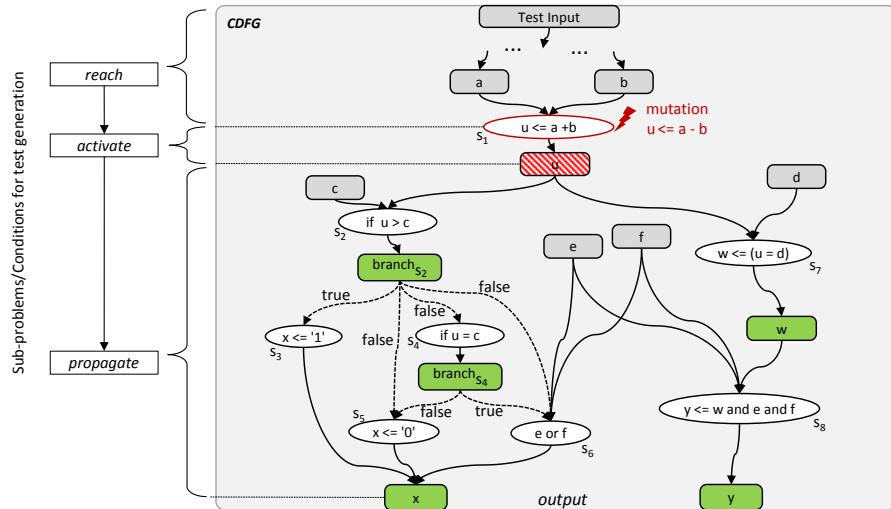

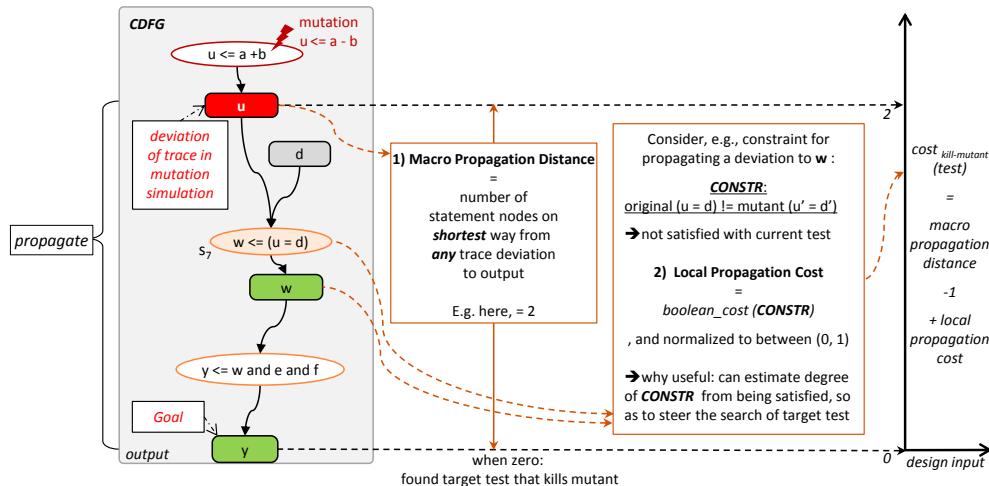

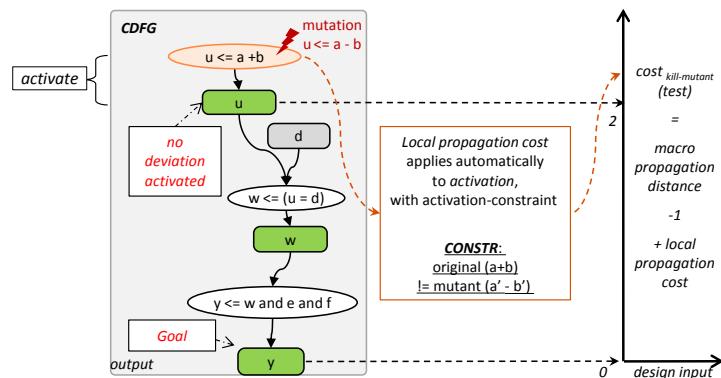

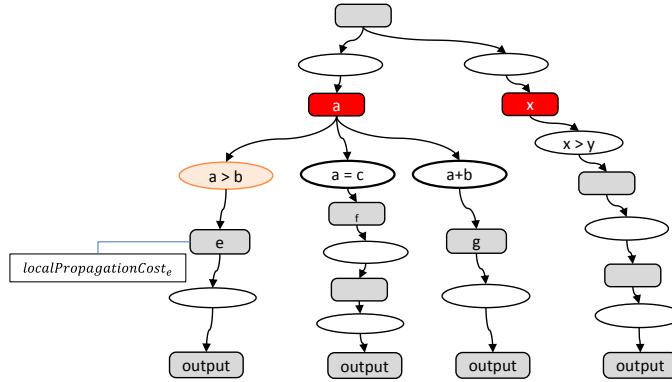

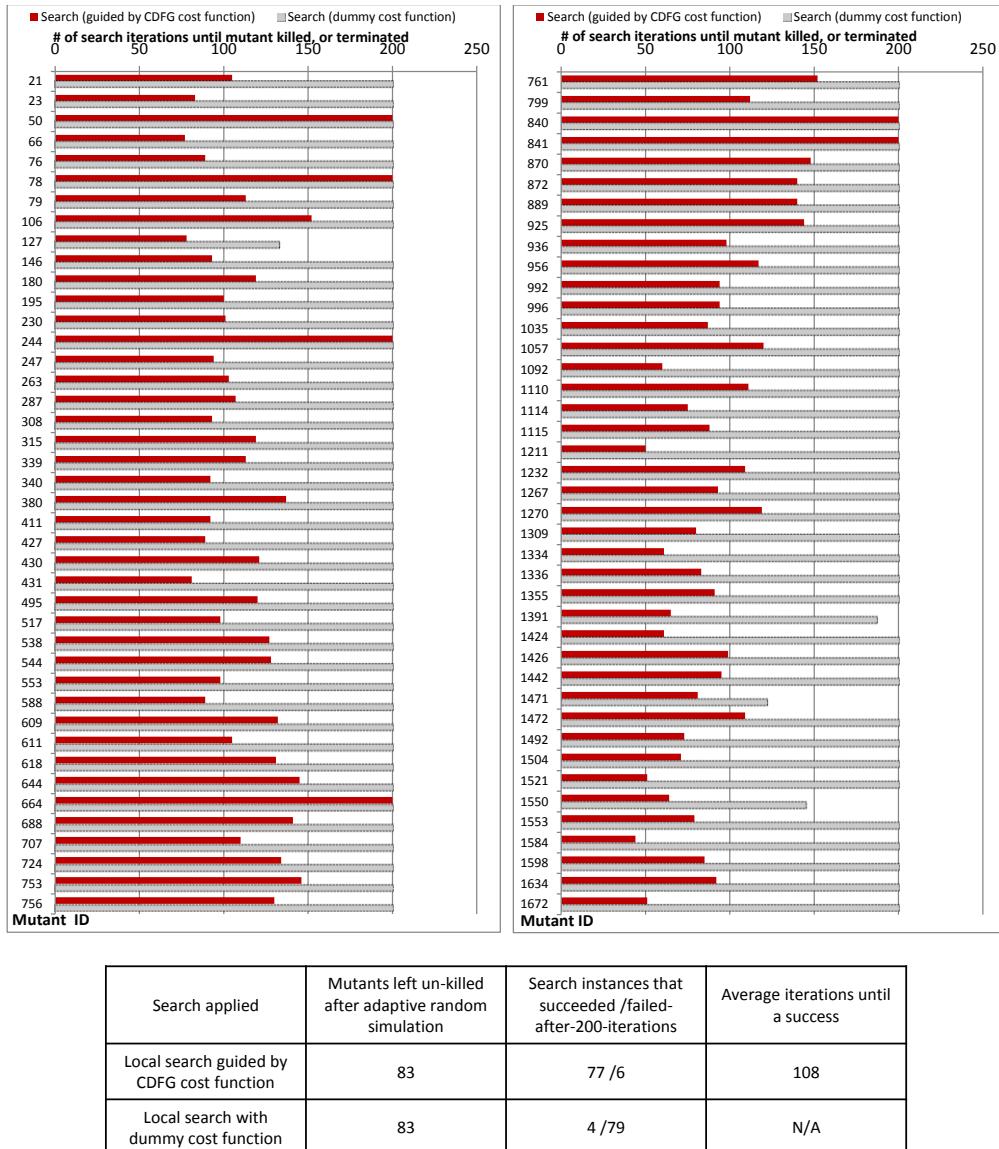

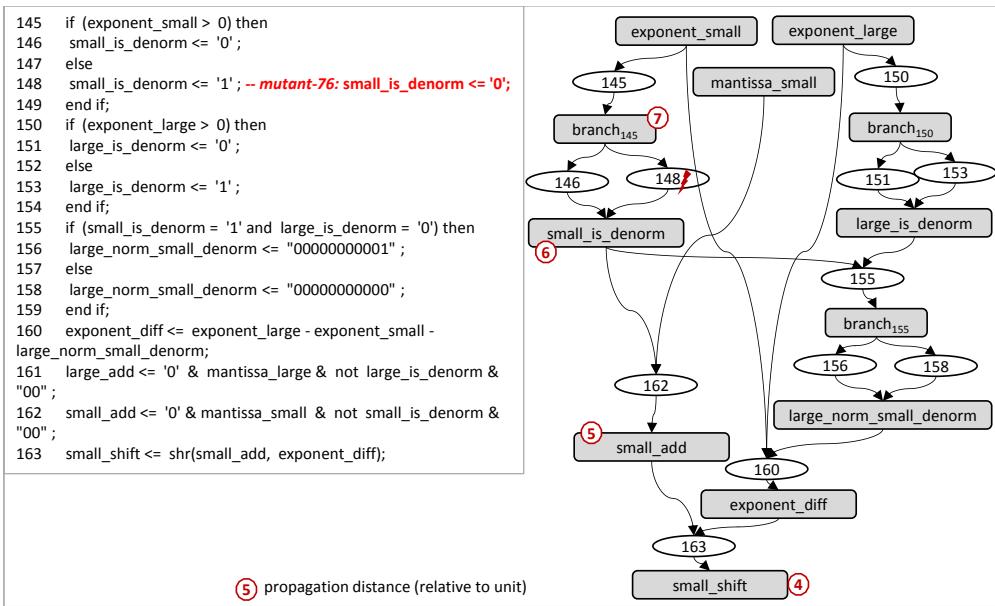

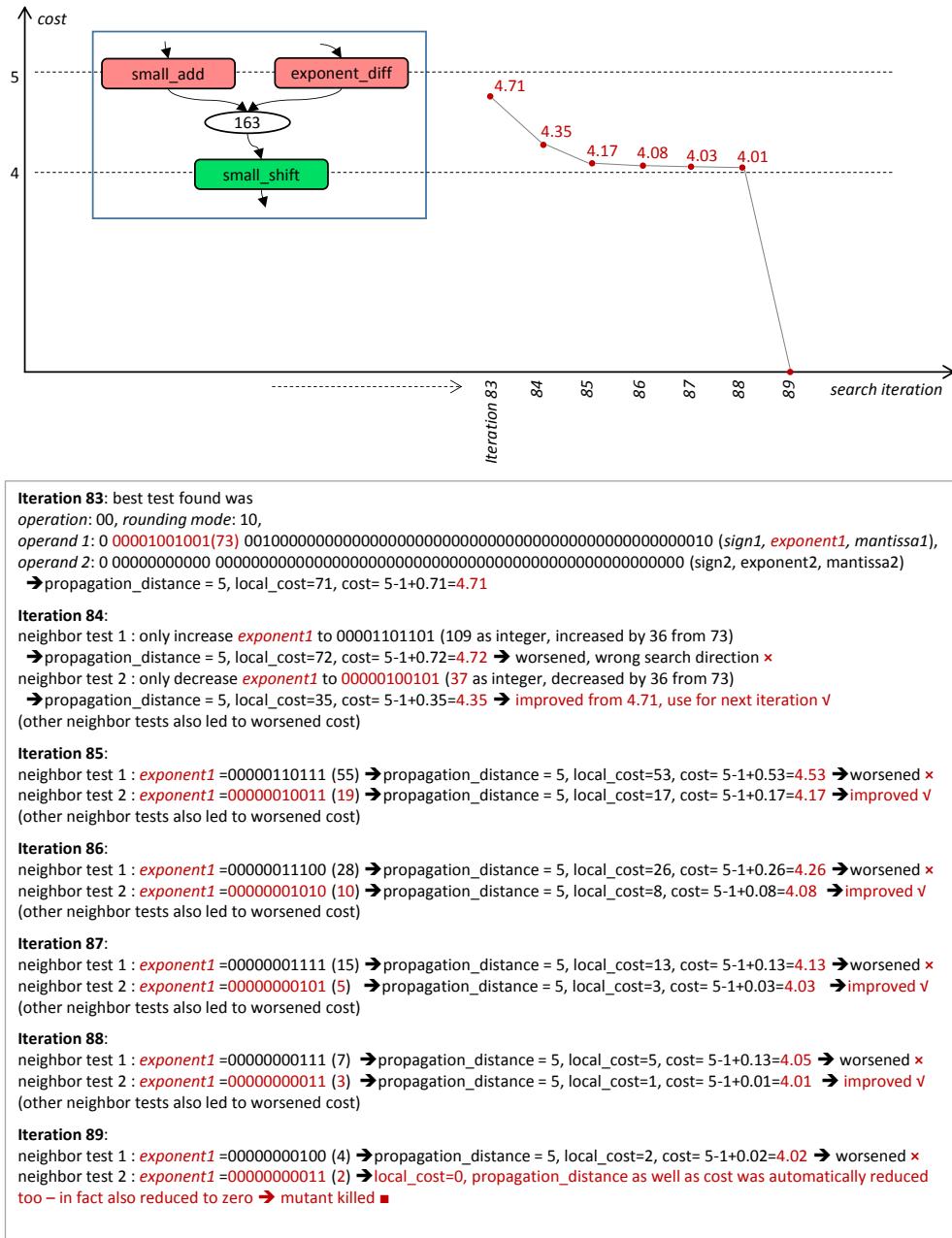

Secondly, with a portion of the mutants expected to be un-killed after random simulation, we solve the problem of further generating tests that kill each individual mutant. A *search-based test generation* method is developed, using real simulation results to guide an iterative process of finding a target test. An objective cost function is defined specifically for HDL mutation analysis, which calculates the progress of a test killing a mutant. In the experiments, the cost function, when used to equip a local search algorithm, delivers consistent performance for steering the search towards mutant-killing tests.

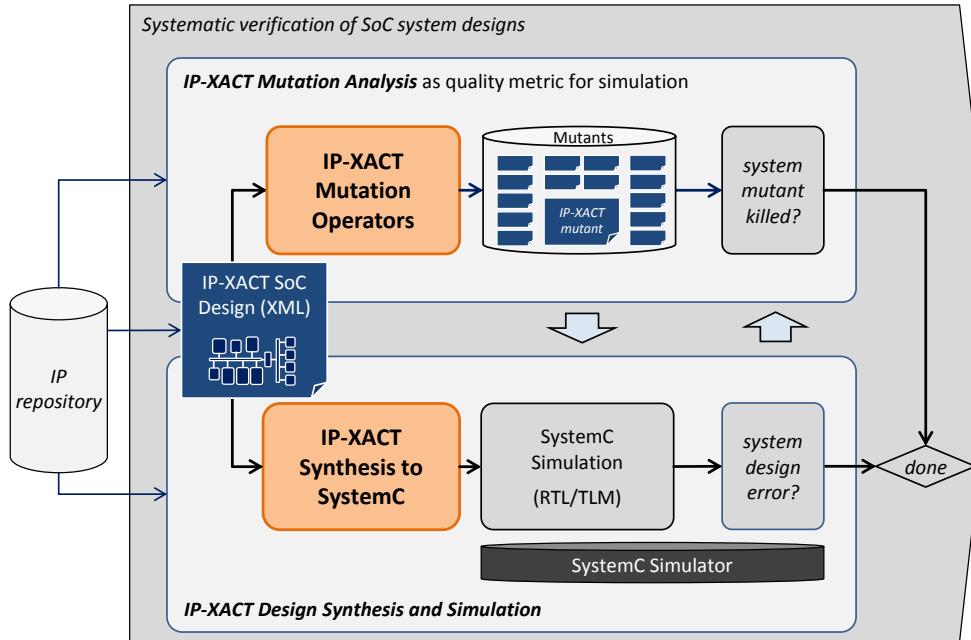

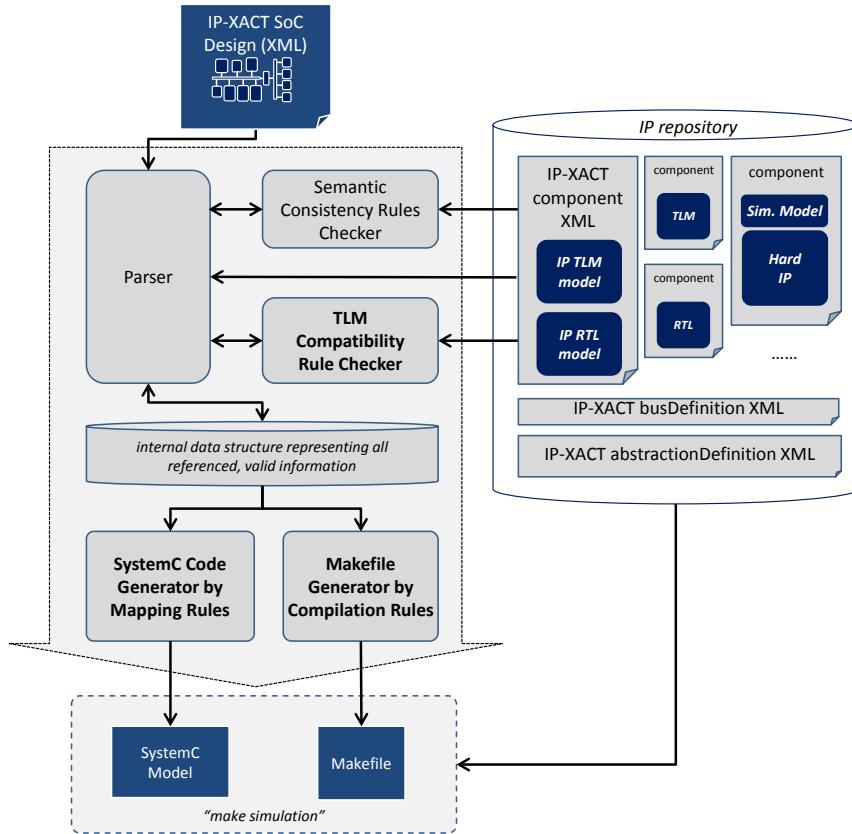

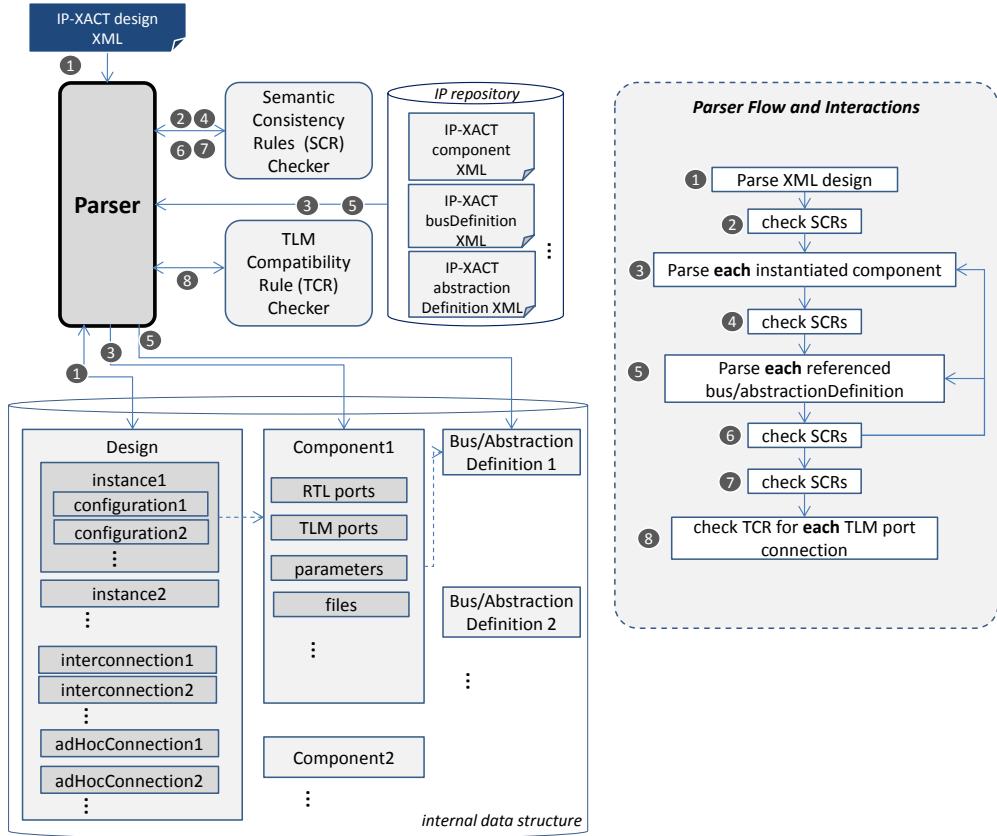

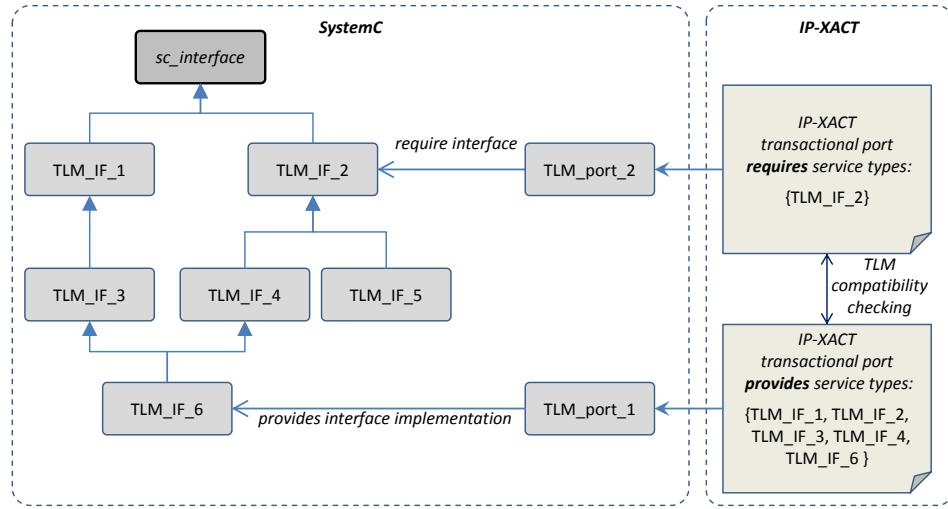

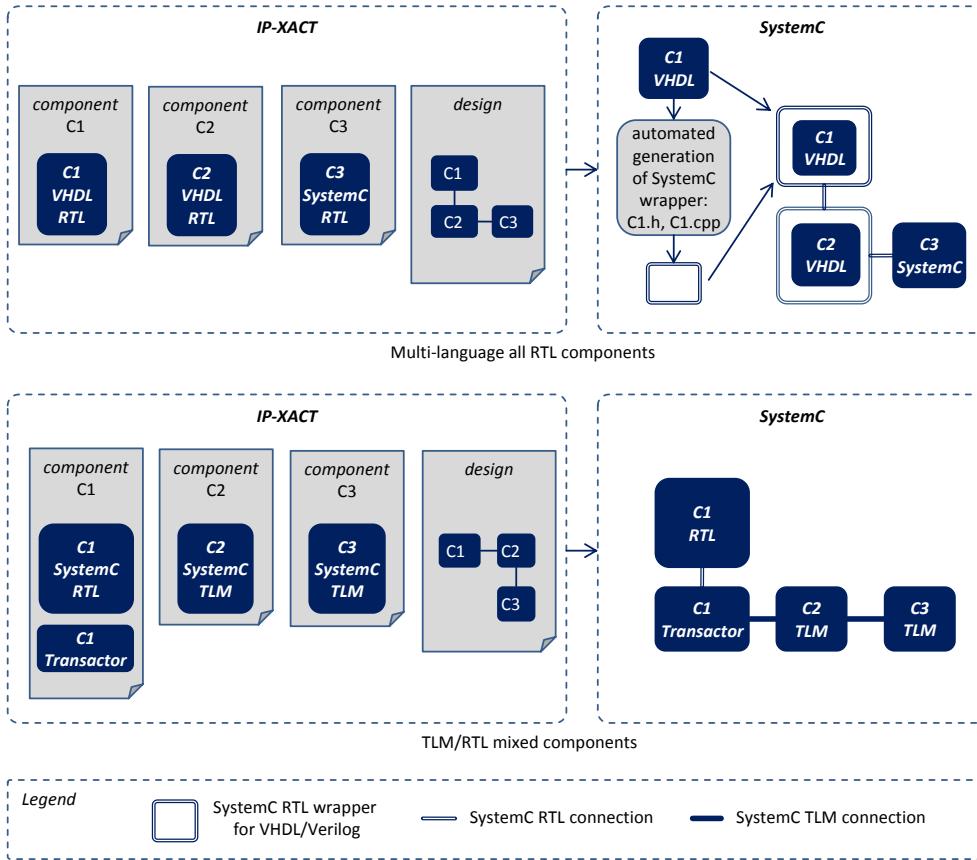

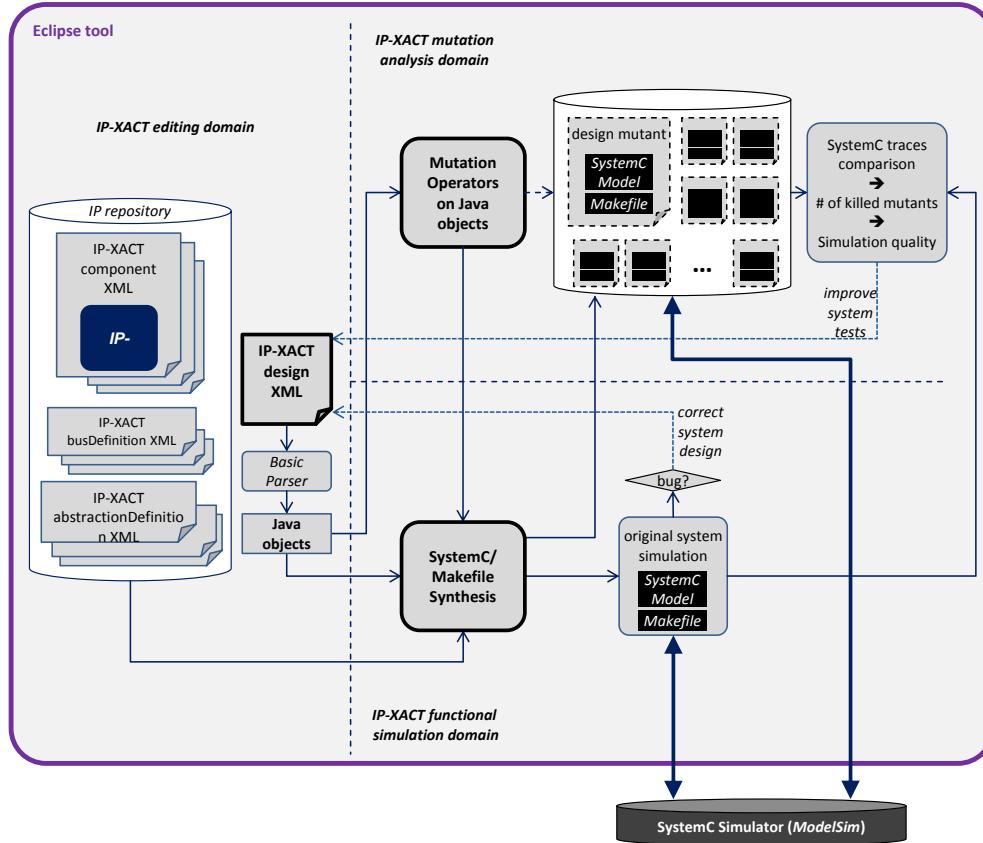

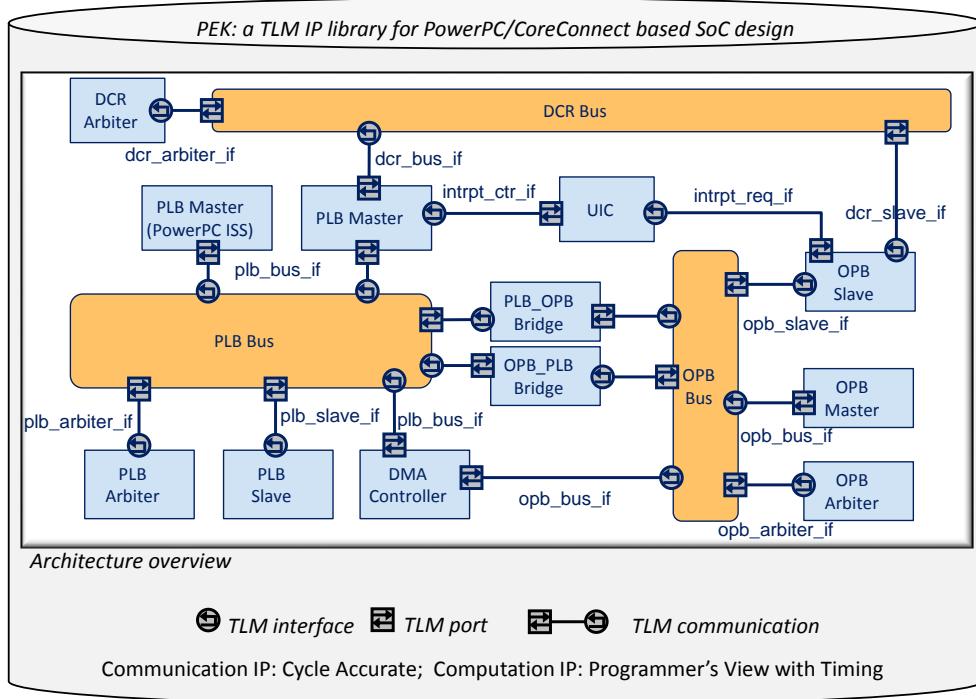

At SoC system level, an *IP-XACT mutation analysis* framework is developed, assuming IP-XACT as the default language for SoC integration. Here, first, since IP-XACT designs as XML data are not simulatable, a simulation engine for IP-XACT, in the form of an IP-XACT-to-SystemC generator that incorporates Transaction-Level Modeling, is built as the verification basis. Second, IP-XACT mutation operators are defined by compiling a table of possible error injections on the IP-XACT schema. The experiments, using an Eclipse-based tool implementation, shows that the proposal is practical and enables verification of IP-XACT SoC designs as well as quality measurement of such verification via mutation analysis.

# Contents

|                                                                |     |

|----------------------------------------------------------------|-----|

| <b>Abstract</b> .....                                          | i   |

| <b>Contents</b> .....                                          | iii |

| <b>CHAPTER 1: Introduction</b> .....                           | 1   |

| 1.1. Functional Verification Challenge .....                   | 1   |

| 1.2. System-on-a-Chip Challenge .....                          | 3   |

| 1.3. Thesis Goal and Organization .....                        | 6   |

| <b>CHAPTER 2: Background</b> .....                             | 9   |

| 2.1. IP and SoC Design .....                                   | 9   |

| 2.1.1. A Reference Flow for IP-based SoC Design .....          | 9   |

| 2.1.2. SystemC and Transaction Level Modeling .....            | 17  |

| 2.1.3. IP-XACT Standard for IP Reuse and SoC Integration ..... | 23  |

| 2.2. Simulation Based Functional Verification .....            | 31  |

| 2.2.1. Quality Metrics Driven Verification .....               | 38  |

| 2.3. Quality Metrics for Functional Simulation .....           | 39  |

| 2.3.1. Statement Coverage .....                                | 39  |

| 2.3.2. Toggle Coverage .....                                   | 40  |

| 2.3.3. Functional Coverage .....                               | 40  |

| 2.3.4. Observability Based Coverage .....                      | 41  |

| 2.3.5. Mutation Analysis .....                                 | 42  |

| 2.3.6. Comparison of Metrics .....                             | 50  |

| 2.3.7. Circuit Manufacturing Test and ATPG .....               | 52  |

|                                                                                          |            |

|------------------------------------------------------------------------------------------|------------|

| 2.4. Summary .....                                                                       | 54         |

| <b>CHAPTER 3: Methodology Overview .....</b>                                             | <b>57</b>  |

| <b>CHAPTER 4: Mutation Analysis Directed Adaptive Random Simulation .....</b>            | <b>61</b>  |

| 4.1. Introduction .....                                                                  | 61         |

| 4.2. Mutation Analysis Directed Adaptive Random Simulation .....                         | 63         |

| 4.2.1. Random Test Generation with Constrained Markov Chain .....                        | 66         |

| 4.2.2. Heuristic Closed-loop Adaptation to Test Generation .....                         | 71         |

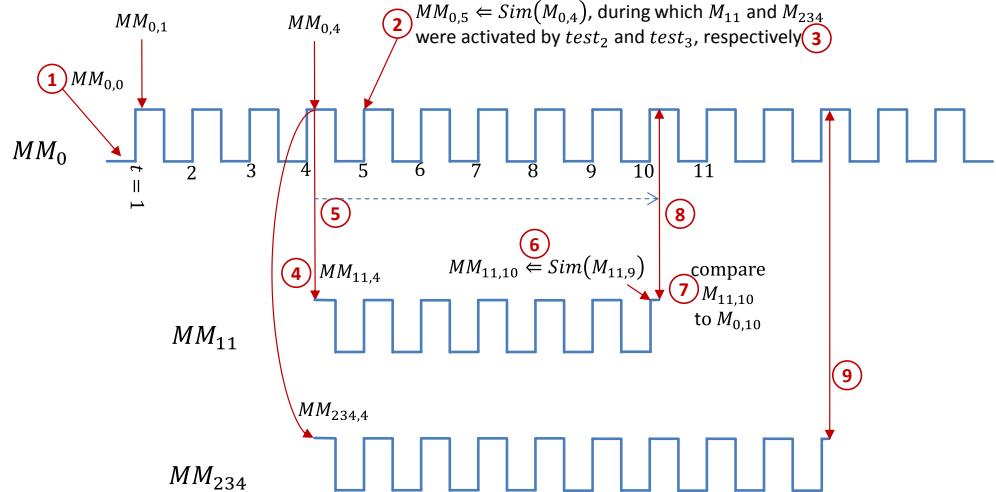

| 4.2.3. Dynamic Mutation Schemata .....                                                   | 74         |

| 4.2.4. Summarized Procedure .....                                                        | 77         |

| 4.3. Related Work .....                                                                  | 77         |

| 4.4. Summary .....                                                                       | 80         |

| <b>CHAPTER 5: Metaheuristic Search Based Test Generation for Mutation Analysis .....</b> | <b>83</b>  |

| 5.1. Introduction .....                                                                  | 83         |

| 5.2. Applying Metaheuristic Search to Mutation Analysis .....                            | 85         |

| 5.3. A Cost Function for Search Based Test Generation of HDL Mutation Analysis .....     | 88         |

| 5.3.1. A Control and Data Flow Graph (CDFG) .....                                        | 88         |

| 5.3.2. CDFG Based Cost Function Definition: Outline .....                                | 90         |

| 5.3.3. Macro Propagation Distance .....                                                  | 93         |

| 5.3.4. Local Propagation Cost .....                                                      | 95         |

| 5.3.5. Algorithmic Summary and Complexity .....                                          | 101        |

| 5.4. Related Work .....                                                                  | 103        |

| 5.5. Summary .....                                                                       | 105        |

| <b>CHAPTER 6: SoC System Design Simulation and Mutation Analysis with IP-XACT .....</b>  | <b>107</b> |

| 6.1. Introduction .....                                                                  | 107        |

| 6.2. An IP-XACT Design Simulation and Mutation Analysis Framework .....                  | 109        |

| 6.3. SystemC Based IP-XACT Design Synthesis and Simulation .....                         | 111        |

| 6.4. Mutation Operators on IP-XACT .....                                                 | 118        |

| 6.5. A Tool Implementation .....                                                         | 120        |

| 6.6. Related Work .....                                                                  | 123        |

| 6.7. Summary .....                                                                       | 125        |

|                                                                   |     |

|-------------------------------------------------------------------|-----|

| <b>CHAPTER 7: Evaluation .....</b>                                | 127 |

| 7.1. Objectives .....                                             | 127 |

| 7.2. MB-Lite Microprocessor IP Verification.....                  | 128 |

| 7.2.1. Design Under Verification and Mutants .....                | 129 |

| 7.2.2. Adaptive Random Simulation .....                           | 130 |

| 7.2.3. Metaheuristic Search based Test Generation.....            | 134 |

| 7.3. CoreConnect SoC Design Verification .....                    | 139 |

| 7.3.1. Introduction to PEK: A TLM IP Libaray for SoC Design ..... | 139 |

| 7.3.2. Two SoC Case Studies on IP-XACT Tool .....                 | 141 |

| <br>                                                              |     |

| <b>CHAPTER 8: Conclusion.....</b>                                 | 147 |

| 8.1. Outlook .....                                                | 149 |

| <br>                                                              |     |

| <b>Bibliography .....</b>                                         | 151 |

# CHAPTER 1: Introduction

The chapter presents the general research challenges that motivate this thesis.

## 1.1. Functional Verification Challenge

In the research area of *Electronic Design Automation* (EDA), *functional verification*, where the *functional correctness of a design is verified against its specification*, is widely regarded as the bottleneck of development and facing unsolved challenges [14] [15] [16]. Along the years, various automation techniques are proposed to tackle verification challenges. However, since, on the one hand, the increase of design complexity seems unstoppable and, on the other hand, new design languages and paradigms emerge alongside this complexity increase, novel verification methodology has always been needed to accommodate the changes.

For example, the functional verification of a microprocessor design should verify whether the design correctly executes sequences of instructions that are specified by its instruction set architecture (ISA). As the complexity of microprocessors increases following the *Moore's Law* – from the first commercial Intel 4004 processor containing about 2,300 transistors [17] to many over 1 billion nowadays, the design's state space that we need to verify increases *exponentially*, which is known as the *state-space explosion* problem in verification. This then suppresses the amount of design that we can verify.

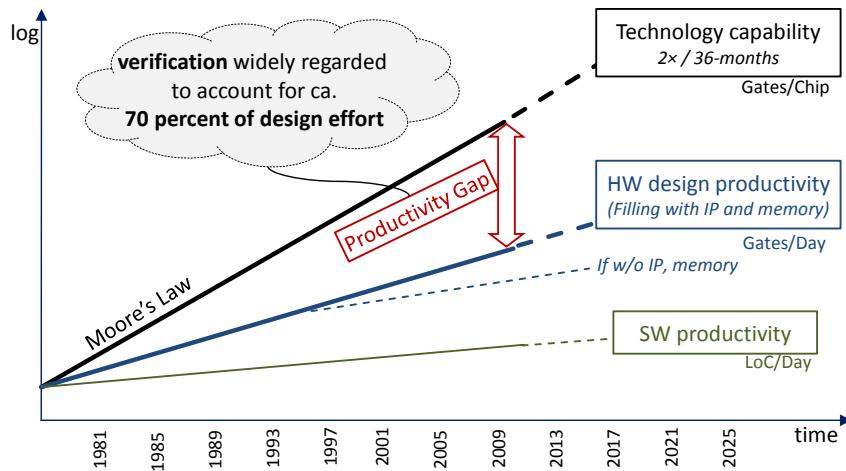

A *design productivity gap* is depicted in **Figure 1.1** [18], which refers to the ever expanding gap between the Moore's Law and design productivity, i.e. between the number of gates, or transistors that *can* be manufactured into a single chip and the number of gates that we are actually able to accomplish in a chip design project, described in gates-per-day. The *International Technology Roadmap for Semiconductors* (ITRS) updates this graph every two years in their *design chapter*, as a high-level view of electronics design challenges. The use of semiconductor *Intellectual Properties* (IP) is also mentioned in this graph as a productivity promotion, which makes the gap not worse. IP-reuse will be a topic of next section.

**Figure 1.1 International Technology Roadmap for Semiconductors (ITRS) 2011: productivity gap [18].**

In many occasions [14] [15] [19] [20], the effort spent on verification is estimated to account for 70% of the entire design activity, if not more. Considering that verification occupies a constant and large portion of design effort, we may also find a *verification gap* contained in the overall productivity gap.

In this context, a more specific question can be asked:

*When can we say that the verification is done?*

Accordingly, we may define the *verification closure* problem as finding *a point that we are certain of incompleteness and incorrectness no longer existing in the design under verification*. On the one hand, this confidence is partly a *subjective* matter. On the other hand, it is our research task to find an objective and systematic solution. For this, we may further consider two questions:

- How can we *effectively measure* the completeness, or thoroughness, or quality of our verification?

- How can we *efficiently improve* the verification quality under such measurement?

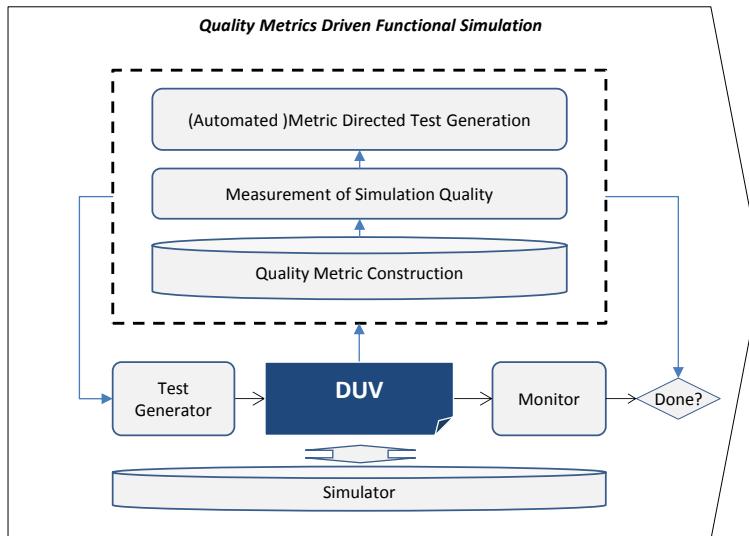

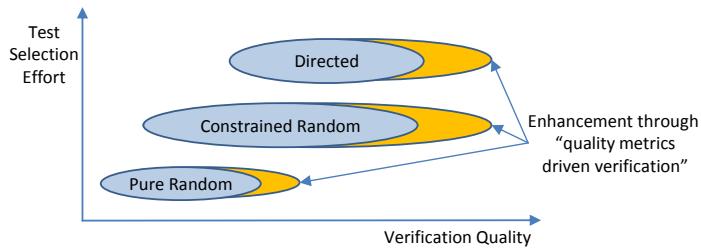

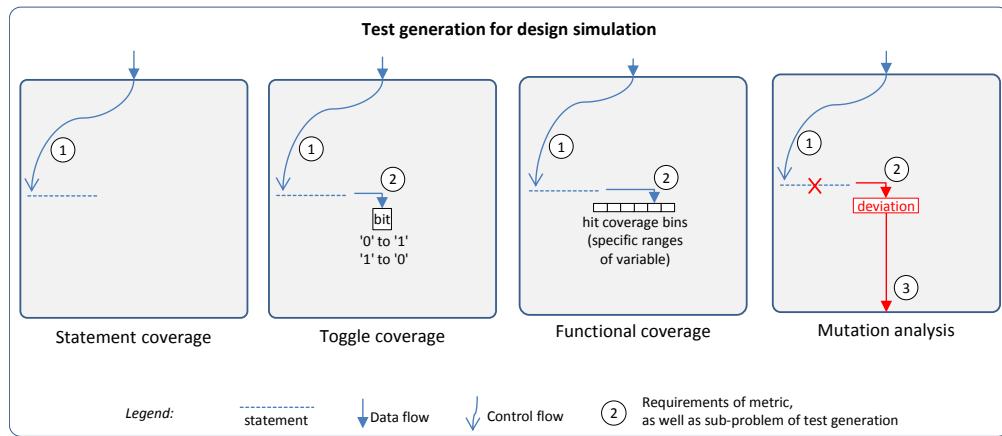

In this work, we use simulation for functional verification. We consider building a simulation-based verification methodology that i) relies on well-established coverage metrics to systematically manage the simulation quality and ii) employs novel methods for automatic simulation tests generation that targets the metrics. Therefore, we call this *quality metrics driven functional verification*.

In particular, we intend to leverage a well-researched, state-of-the-art metric for HDL (Hardware Description Language) simulation: *mutation analysis*, which has been implemented by, for example, a recent EDA tool *Certitude* [21] [22] [23] from Synopsys.

Exactly meant as an aid to answer the verification closure problem, mutation analysis gives *a quantitative, objective quality measure on simulation tests, by injecting artificial but typical errors into a design under verification, and assessing how many of these errors can be revealed by the tests*. The individual metric points are called mutants.

Further, the thesis is focused on functional verification. *No* observation on non-functional properties is considered, such as *power* or *performance*.

## 1.2. System-on-a-Chip Challenge

Nowadays, we are seeing increasingly more electronic systems in the form of *System-on-a-Chip* (SoC, or System-on-Chip), where a system is built into a single *integrated circuit* (IC) chip, instead of on a *printed circuit board* (PCB).

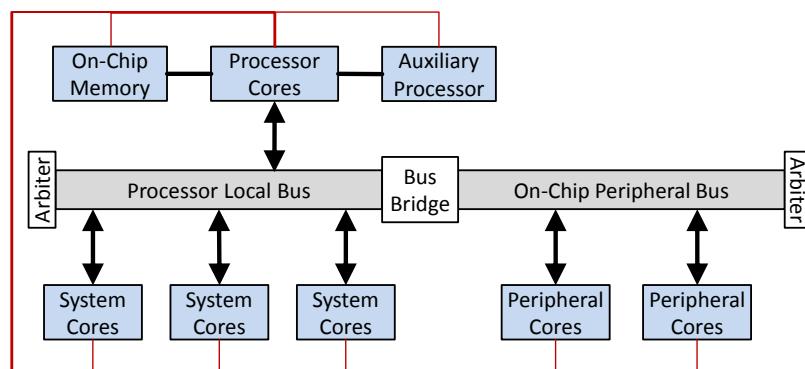

*CoreConnect*, as shown in **Figure 1.2** is an on-chip bus architecture proposed around 2000 by IBM for SoC integration [24], which is widely used ever since. The Processor Local Bus (PLB) bus provides separate 32-bit address and up to 128-bit data buses. With a fully synchronous architecture, PLB can be connected with multiple masters and slaves. High-throughput system cores, such as microprocessors, memory controllers, and Direct Memory Controller (DMA), are supported by PLB. Other peripheral cores such as a UART (Universal Asynchronous Receiver/Transmitter) controller can be connected to the low-bandwidth On-chip Peripheral Bus (OPB). Another Device Control Register (DCR) bus is intended specifically for register data move between a microprocessor and configuration registers of other components, so as to free the bandwidth of PLB.

CoreConnect will be frequently used in our examples and case studies. Here, it gives a first illustration of what defines a SoC: *higher system integration on the chip level*.

Previously, system components are implemented as separate ICs and then interconnected on a PCB. Now, both computation and communication components are

**Figure 1.2** CoreConnect on-chip bus architecture [24].

integrated on-chip. They *comprise an integrated design, to be verified, synthesized, and then manufactured as a single chip*.

Arguably, SoC is *more of a design paradigm* than a perfect reality, since in the end, most systems still need to be embedded as PCBs.

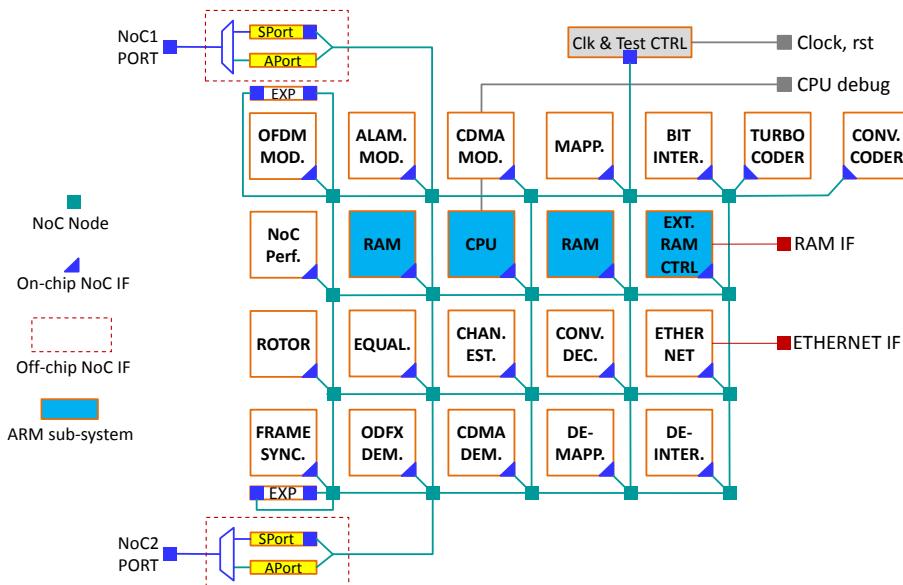

*Network-on-Chip* (NoC) is another form of SoC, where system-level integrated components communicate with each other through on-chip network and routers. **Figure 1.3** shows the *FAUST (Flexible Architecture of Unified System for Telecom)* NoC [25] [26], which we have employed in a recent European research project *COCONUT (A Correct-by-Construction Workbench for Design and Verification of Embedded Systems)* [27]. 23 IP blocks are included and connected to a network of 20 nodes, resulting in a complexity of 8 M-gates.

Using a router-based, asynchronous network for communication, higher scalability and data throughput are expected. Therefore, it is intended for dataflow-intensive, especially 4G-radio-targeted applications. The chip is categorized as a SoC, as it integrates most system components that are previously off-chip now into a single IC, including, for example, an ARM microprocessor, memory controllers, radio communications such as OFDM and CDMA, and the network routers. More details on this NoC and its applications can be found in [25].

In the COCONUT project, a high-level, *Transaction-Level Modeling (TLM)* [28] based model of this FAUST NoC has been employed as a target platform, to develop a TLM based SoC design methodology. One of the project results is a TLM-based, RTOS

**Figure 1.3 FAUST NoC [25].** A TLM model for this chip has been employed in the *COCONUT* project to create a TLM based SoC design methodology.

(real-time operating system)–aware SoC refinement flow [8]. The previously mentioned *Certitude* tool has also been involved in this project, for managing the verification quality part of the design methodology.

In this work, we do *not* particularly differentiate NoC and SoC, yet with an emphasis on traditional master-slave bus architectures.

## SoC Design is Centered at IP-reuse

A prominent characteristic of SoC design is that *it is centered at component reuse*. Here, component means *design components*, instead of fabricated devices. These components are called semiconductor *Intellectual Property* (IP) in this context. Types of IPs include encryption/decryption cores, video/audio codecs, telecommunication network controllers – wired or radio-based, memory controllers, digital signal processors, general purpose microprocessors, and so on.

Around IP reuse, two roles can be defined for SoC development. One is *IP vendor*, whose task is to design and deliver an IP component for some specific functionality. The other one is *SoC integrator* that takes a wide range of IPs as input and integrates them into a complete system capable of hosting applications. At SoC integration phase, an IP can come either from an internal design group, or from an external IP vendor.

This IP-centered SoC design paradigm has its significant impact on verification. Besides the general *verification gap* from the increasing complexity of both IPs and SoCs, we face these particular challenges:

- *Separation of IP design and SoC system design leads to more stringent requirement on the quality of IP verification.* An IP design must be verified as thoroughly as possible before its delivery to any SoC integration phase, when the in-system debugging would become more difficult because of the SoC complexity, if not entirely impossible when the IP is provided as a black-box without source code.

- *Verification at SoC system level should accommodate new paradigms and languages for SoC design.* TLM is one example that we have just mentioned with regard to project COCONUT. *IP-XACT* is another XML-based, IEEE standard format specifically for describing IP reuse and SoC integration [29], which has been seeing increasing acceptance [30]. By aligning verification to SoC-specific languages, we will be able to *focus verification on system-level integration* and cope with the complexity of SoCs.

These general motivations will be further elaborated alongside the background presentation in next chapter, before we propose our methodology to meet the challenges.

### **1.3. Thesis Goal and Organization**

Therefore, the thesis tries to provide one step towards solving the functional verification challenge, in the context of system-on-a-chip becoming a prevailing design paradigm.

We conclude this introduction chapter with the following considerations. We also present the concrete problems to be solved in the rest of the thesis.

- To meet the functional verification challenge, we consider systematic application and deployment of quality metrics to be a necessity. In particular, such application of metrics should consistently cover both IP and SoC system verification stages.

- We consider mutation analysis, as a well-researched, state-of-the-art testing technique, to be an advanced metric and the basis on which we build our verification methodology.

- We further consider that emerging system-level languages, such as IP-XACT and TLM, are used for SoC system design and, therefore, should be included in the methodology.

### **Problems**

*Test generation* is the major problem that we encounter at the stage of IP design verification with mutation analysis.

- Considering that *random simulation* is a widely recognized technique for achieving a primary level of verification quality and should also be used for mutation analysis, we have the problem that random test generation becomes inefficient in the context of metrics-oriented simulation. It is because that i) initially, the random tests are usually *not* modeled for any specific metric and ii) a target metric also changes during simulation as a consequence of its subsets being satisfied. Moreover, mutation analysis is *simulation intensive*, which makes the problem more critical. Therefore, we consider an *adaptive* simulation necessary, able to consistently *steer* a random test generation process towards the mutation metric.

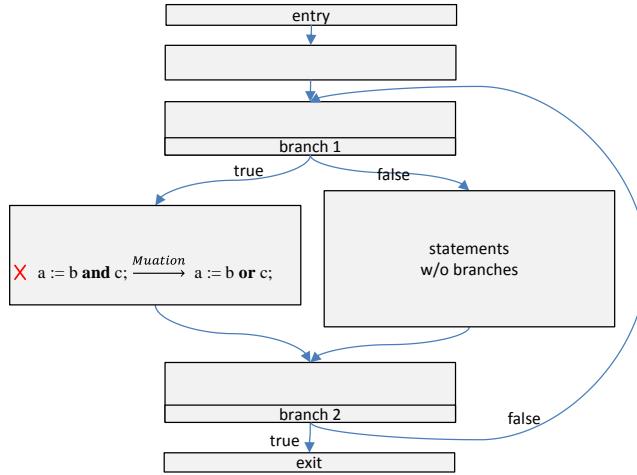

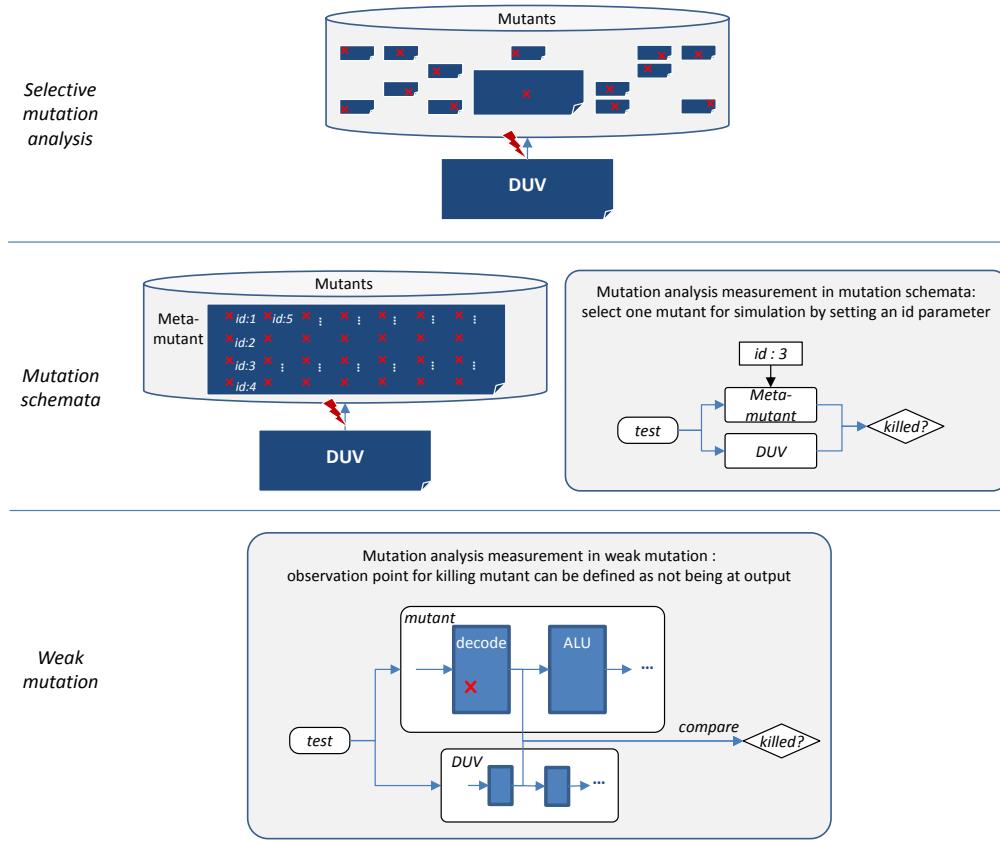

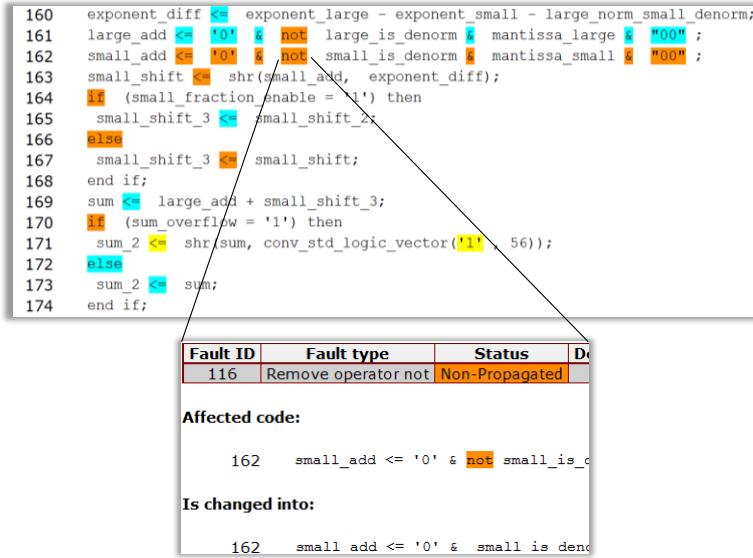

- Expecting a portion of the mutation analysis metric to be unsatisfied after random simulation, we face the problem of further generating tests to *kill* individual mutants. This test generation problem is unique to mutation analysis: tests are required to *reach a mutant, activate it, and propagate the erroneous behavior to design output*. Existing methods to the problem are based on symbolic manipulation and *not* as scalable as HDL simulation itself. We consider it necessary to develop a *non-symbolic, purely simulation-based* test generation method for HDL mutation analysis.

Moving to SoC system design, we focus on the following two sub-problems:

- IP-XACT designs as XML data are *not simulatable* and, therefore, present a barrier for us continuing the simulation-based, metrics-driven functional verification at SoC system-level. A simulation engine for IP-XACT SoC designs needs first to be built as the verification basis.

- Then, we find a general *lack of systematic metric* for SoC system verification. Specifically, if we require mutation analysis to be consistently applied also at system level, we should solve the problem of *enabling IP-XACT mutation analysis*, i.e. how IP-XACT design mutants can be created and simulated.

Solutions to these problems will *not* be limited to mutation analysis, but apply to other metrics in the general context of metrics-oriented IP and SoC verification too.

Our solution is called a *metrics-driven methodology*, as i) quantitative metrics are relied on for systematic measurement of verification thoroughness and quality, ii) automation methods are proposed to generate tests and improve such measured quality, and iii) for places where such metrics lack for IP-based SoC design, we tries to create one. The overall contribution can be stated as:

*The thesis establishes a verification methodology that systematically manages and automatically improves the quality/thoroughness of a functional design verification process. In particular, it accommodates IP-based SoC design paradigm.*

## Organization

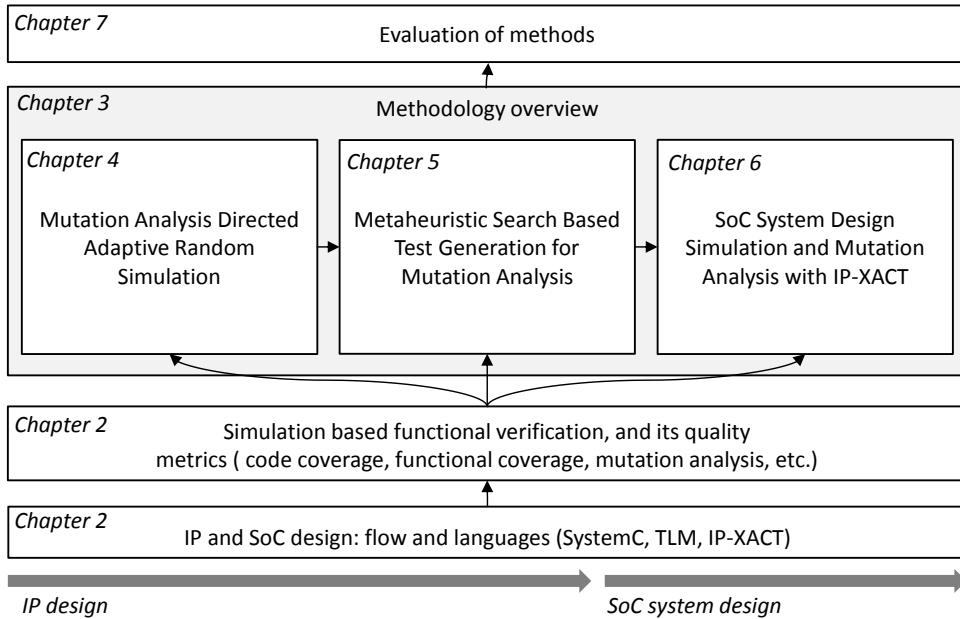

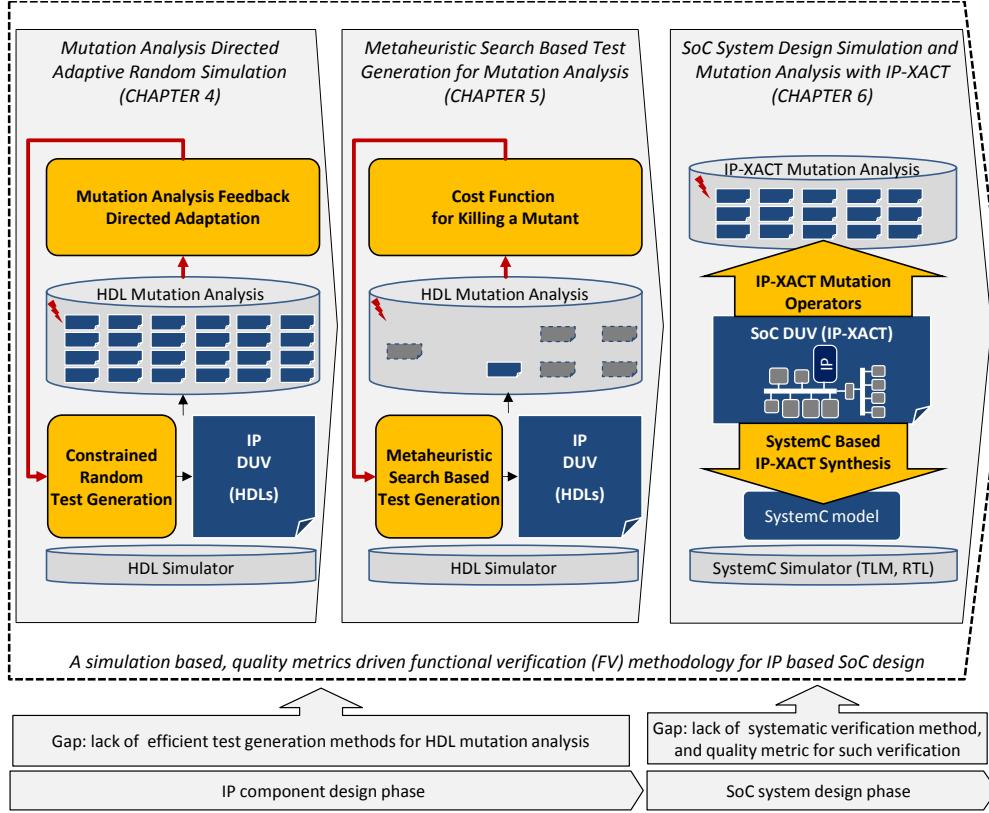

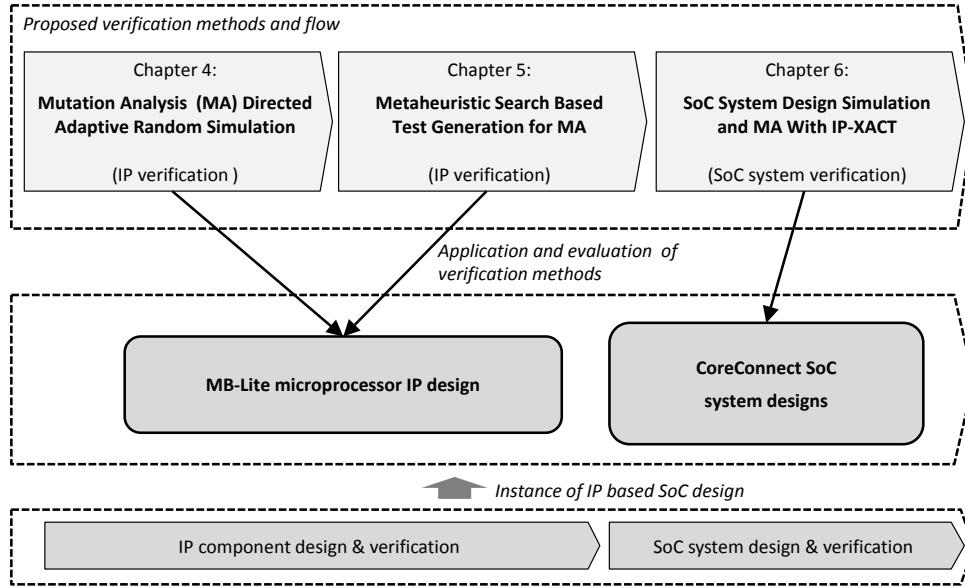

The thesis is then organized as shown in **Figure 1.4**:

- In Chapter 2, state-of-the-art techniques and methods for IP and SoC design are introduced as the background of our proposals. It follows a thread from *design*, to functional *verification* by simulation, to quality *metrics* for such simulation. In particular, *mutation analysis* as the focused metric is extensively discussed and compared to others.

- In Chapter 3, an overview of our proposals, which comprise a *quality-metrics driven functional verification methodology for IP-based SoC design*, is given.

- From Chapter 4 to Chapter 6, three components of the methodology are presented. Chapter 4 proposes an adaptive random simulation method, which uses mutation analysis results as on-line feedback to dynamically steer a random test generation process, so as to obtain an improved efficiency of mutation analysis. Chapter 5 proposes a search based test generation method for mutation analysis, where an

**Figure 1.4 Thesis organization.**

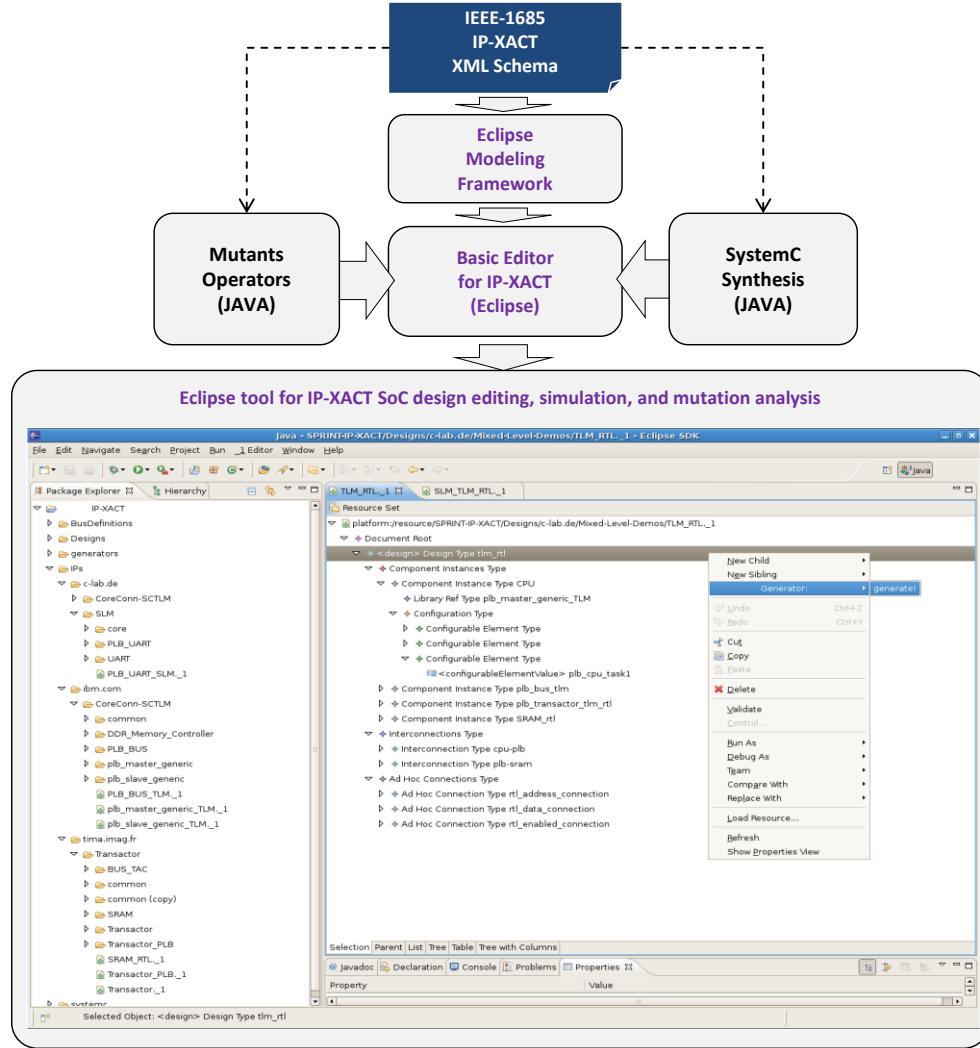

objective cost function, which is capable of guiding a metaheuristic search algorithm stepwise towards target tests that uncover a HDL mutant, is defined. These two methods are mainly for IP-level designs. In Chapter 6, an IP-XACT based SoC system design simulation and mutation analysis framework is proposed, to address the lack of systematic verification way at SoC system-level. The implementation of a prototype IP-XACT tool, based on Eclipse, is also presented.

- Literature directly related to our proposals is respectively discussed in Chapter 4 through 6.

- In Chapter 7, feasibility, effectiveness, and efficiency of the proposed verification methodology, based on simulation and mutation analysis, are investigated with real designs. IP-level test generation methods are evaluated with a microprocessor design. SoC system-level simulation methods are evaluated by exercising our IP-XACT tool with several CoreConnect/PowerPC SoC designs in TLM.

- In Chapter 8, we give conclusions on the thesis, also addressing some outlook from this research.

# CHAPTER 2: Background

In this chapter, we give the background discussion necessary for the identification of what lacks in the state-of-the-art methods and techniques for IP and SoC designs, and further as the basis for our enhancement proposal. The chapter follows the thesis organization presented at the end of last chapter and is divided into three sections: *design*, *verification*, and *metrics for verification*.

- The whole background is unfolded based on a reference flow for IP-based SoC design, which is defined in Section 2.1.1. Advanced, state-of-the-art design techniques and methods are introduced by Section 2.1.2 and 2.1.3, which are focused on SystemC, Transaction Level Modeling, and IP-XACT.

- Discussion on functional design verification is limited to simulation, with common parts and approaches in HDL simulation introduced in Section 2.2. We define *quality metrics driven verification*, an approach that we follow for our verification methods, in Section 2.2.1.

- In Section 2.3, we discuss a wide range of metrics that can be employed in such *metrics driven verification*, with an emphasis on *mutation analysis* that will play a central role in our own methods.

Literature closely related to our contributions will be left to each corresponding chapter, for a better comparison. We further assume some mature languages and methods familiar to readers and not included in this discussion, such as tradition HDLs like VHDL and Verilog, designs at Register Transfer Level (RTL), and their simulation.

## 2.1. IP and SoC Design

### 2.1.1. A Reference Flow for IP-based SoC Design

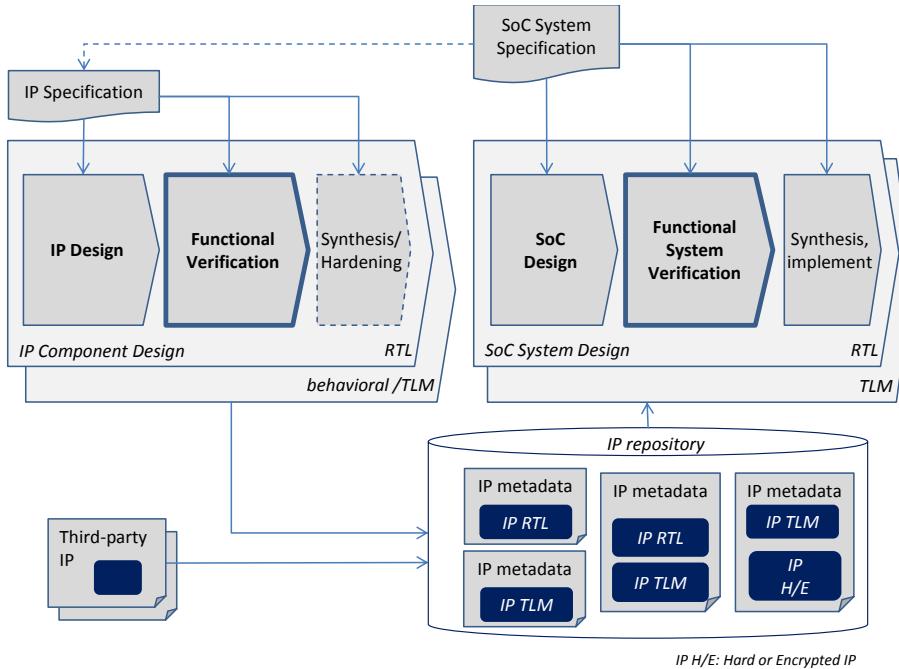

In this Section, we introduce a reference design flow for IP-based SoC design, as shown in **Figure 2.1**. The purpose of the flow is threefold. First, it serves our definition of IP-

**Figure 2.1** A reference IP-based SoC design flow.

based SoC design paradigm, in an abstract manner. Second, it constrains our discussion on design and verification, with regard to background, state-of-the-art methods, and what still lacks. Third, it is the basis flow upon which our proposal of a quality metrics driven verification methodology will be constructed, so that in the end we have an enhanced, integrated flow for IP-based SoC design.

In the figure, our key view of a typical IP-based SoC design flow is the *division and separation of IP design and SoC system integration*, which leads to two separate design phases. Main reasons for this *division and separation* are i) division between IP vendors and SoC integrators and ii) increasing complexity of SoC and larger integration.

It is often the case that for the assembly of a SoC design, the SoC integrator needs one or multiple components as IP from another specific component provider – or IP vendor. Separation of the IP design phase from the whole SoC design flow is straightforward. Even when a component is developed at the same place where the SoC should be assembled, because of the complexity of SoCs nowadays, it is reasonable that a “divide-and-conquer” paradigm is followed.

The specification for an IP does *not* necessarily come from a SoC system specification. The IP specification defines a specific functionality for a SoC component without, or only partially, considering its final integration into a larger application scenario. An Instruction Set Architecture (ISA) for the implementation of a microprocessor IP can be viewed as a good example of such IP specification, which is quite independent from its final SoC

application, although the target SoC group, for intensive digital signal processing or as leisurely microcontroller, should have some impact on the selection of instruction set. Most importantly, in most cases, we start with the specification, design, and verification of an IP, before we embark on a SoC specification.

The design of an IP component – the first phase in the design flow – consists mainly of the design activity itself, the verification, and design synthesis as well as implementation.

- One important aspect of the flow, in both IP component and SoC system design phases, is the inclusion of a state-of-the-art design technique called *Transaction-Level Modelling* (TLM) [31] [28] [32] [8]. Basically, TLM is a design level with higher abstraction than traditional RTL. It is introduced in Section 2.1.3, together with a language called SystemC, in which TLM is typically conducted. RTL is still the major entry level for many design activities, in particular for IP level designs. Nevertheless, we will spare the space and not give introduction to the quite mature RTL methods and associated HDLs, like VHDL and Verilog. Basics of VHDL and Verilog can be found in [33] [34].

- For IP verification, we consider mainly the aspect of functional design verification, for example, whether a microprocessor design can correctly execute a test program from a specified ISA. Other non-functional properties like timing and power are not considered. Existing functional verification techniques, formal or simulation based, are outlined in Section 2.2, with slightly more focus on simulation based verification.

- The logic synthesis step is optional. There are generally three forms of IPs:

- **Soft-IP**: the IP is provided as its source code.

- **Hard-IP**: the IP is synthesized with a cell library to transistor layout format, for example GDSII [35], or even to a specific fabrication process. This is called an *IP hardening* process.

- **Encrypted-IP**: the IP is provided with its source code, but encrypted. Later for the integration in a SoC, it is supposed to be decrypted by some specific accompanying tool.

The advantage of a soft-IP is its flexibility for implementation. The advantage of a hard-IP, in contrast, is its predictability, because it is nearer to the implementation. IP hardening and IP protection by encryption are topics not focused in this work. Still, we assume that a hard and encrypted IP is always accompanied with a simulatable model for its integration in system design.

- Techniques on synthesis from a TLM design to RTL and automated abstraction from a RTL design to TLM exist, which can be found in literature [36] [37], for

example. Equivalence checking between RTL and TLM is another verification topic that is *not* covered by this work.

After the exhaustive verification of IP design, the IP is supposed to be delivered to a SoC system integrator, either in-house or a third-party vendor. In both cases, the IP should be imported in an IP repository [38] at the SoC integrator with metadata that document its possible and correct usage in a system integration, such as its on-chip connection interfaces, parameters, and reference to design files. An example later shows how proprietary metadata may look like in a Xilinx IP based SoC design environment for FPGA.

An IP repository may contain IPs in various forms. These include mainly RTL and TLM IPs in our discussion. If an IP is provided as a hard core, it is usually accompanied by a simulation model, say in TLM. Therefore, in a modern flow of IP-based SoC design, the IP metadata format should be capable of both RTL and TLM.

A successful shift to SoC system level can only be secured by thorough verification of IP designs and their complete metadata. The system phase has similar steps as IP level – SoC design, verification, and synthesis/implementation.

- As a component based design paradigm, a SoC system description should mainly include the instantiation of IPs as components, their configuration, and their interconnection. The description language or format for this SoC integration further depends on the IP metadata format, since the metadata defines exactly the usage of IP in SoC. Later, we will show this dependence in the example of Xilinx SoC development environment, as well as in the introduction to IP-XACT standard.

- Inclusion of both RTL and TLM IPs implies another requirement that the SoC system design phase should also cover both RTL and TLM, and even an RTL/TLM mixed integration.

- We consider *system simulation* as a necessary step for verifying the functional correctness of a SoC system design, before any of its implementation. This step is also demonstrated in the Xilinx example. We will emphasize the provision of this system simulation as a significant gap for the IP-XACT standard. Although other system verification techniques, such as formal verification and emulation, should complement the simulation, they are *not* the target of our proposal on verification enhancement.

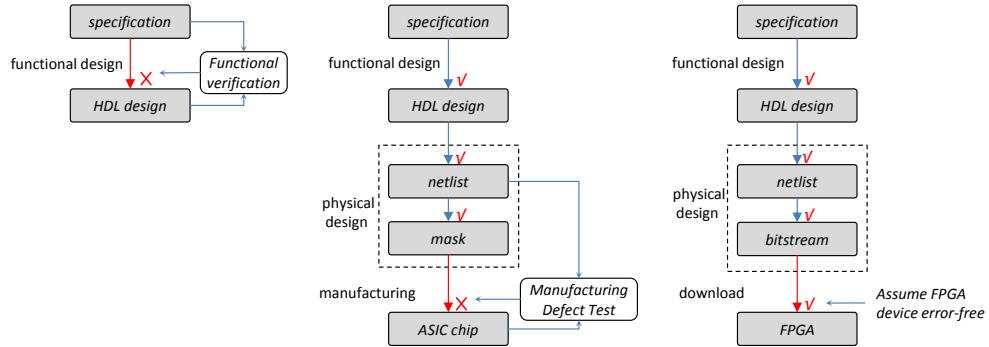

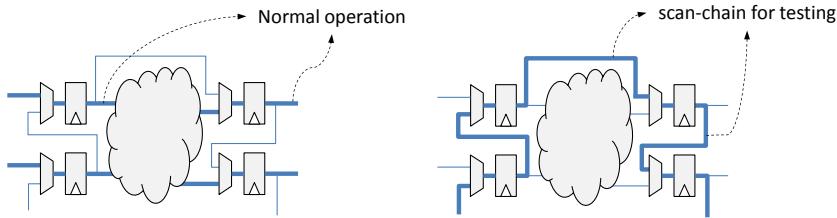

- Targeting a specific implementation technology, whether an ASIC implementation library or a FPGA device, the SoC design can be synthesized and implemented as an integrated circuit. In general, the *circuit testing* step is *not* included in our design flow. However, we will introduce briefly alike test methods that are applied in

circuit testing, such as fault-modeling and fault-aiming automated test generation, which can be compared to methods employed in our quality metric driven design verification.

- The design steps, not only here at SoC system level but also at IP level, can all be iterative. The functional verification certainly needs to be repeated, when a bug is revealed and then corrected in design.

This IP/SoC *division-and-separation* and the resulted two-phase design flow gives a significant impact on the verification aspect – the target of the thesis.

- Since that the design of an IP is separated from system integration, the IP design is required to be verified *as thoroughly as possible*. This thoroughness is only achievable through i) management of the verification process with quantitative, systematic quality metrics and ii) automated methods for improving these metrics.

- Then at the system level, the verification of the SoC design is required to be *focused on the system integration*, mainly as instantiation, configuration, and interconnection of IP *components*. Internal structure of the components may usually be not visible anymore. Any metric on verification quality should also consider a focus on integration.

- The flow implies that a design under verification is *not* always synthesizable, in both IP design and SoC system design.

We will propose our enhancement to this flow with a focus on verification and its quality, considering state-of-the-art design and verification techniques, which are to be introduced in the rest of this chapter. But before that, we present an example instance of the reference design flow.

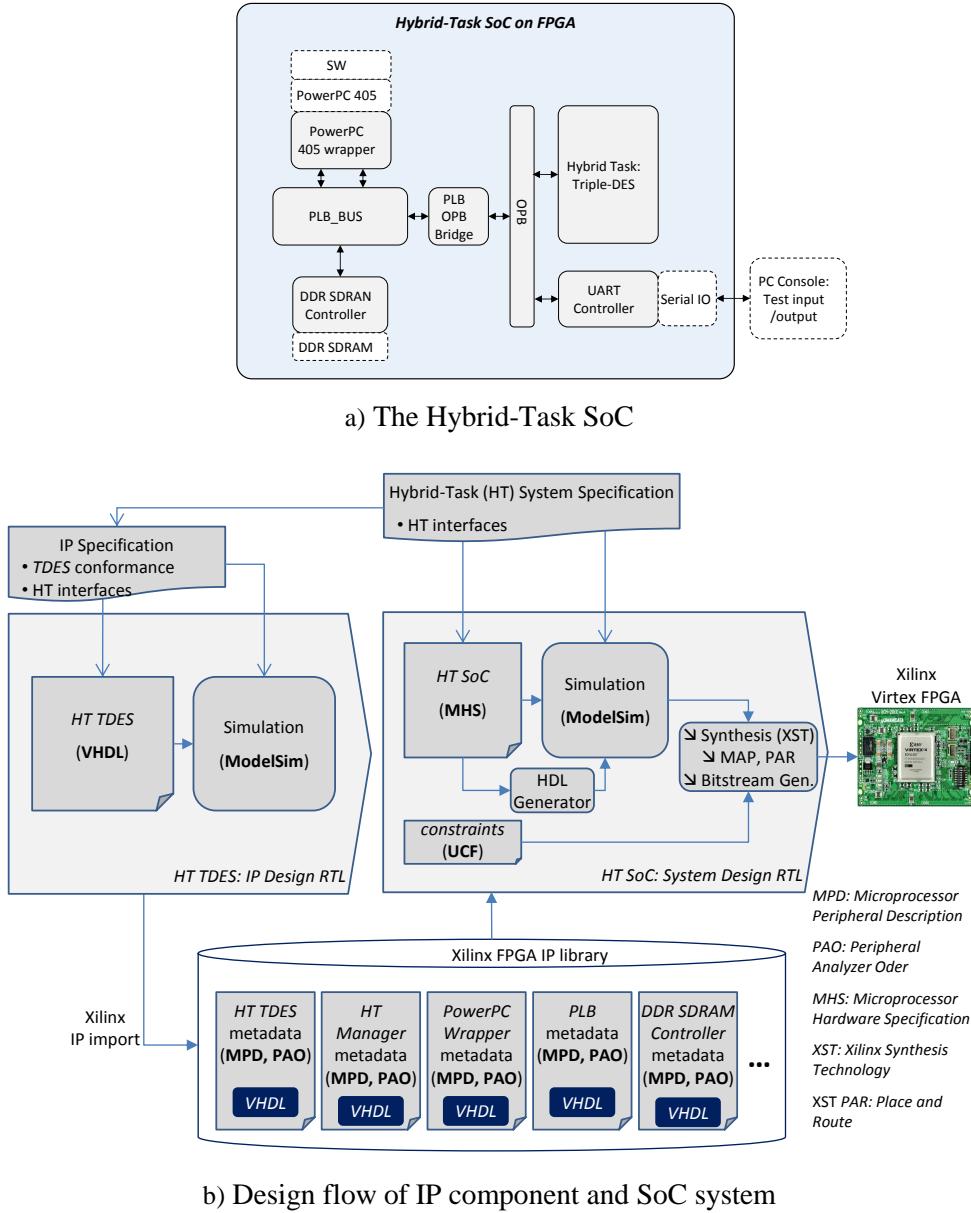

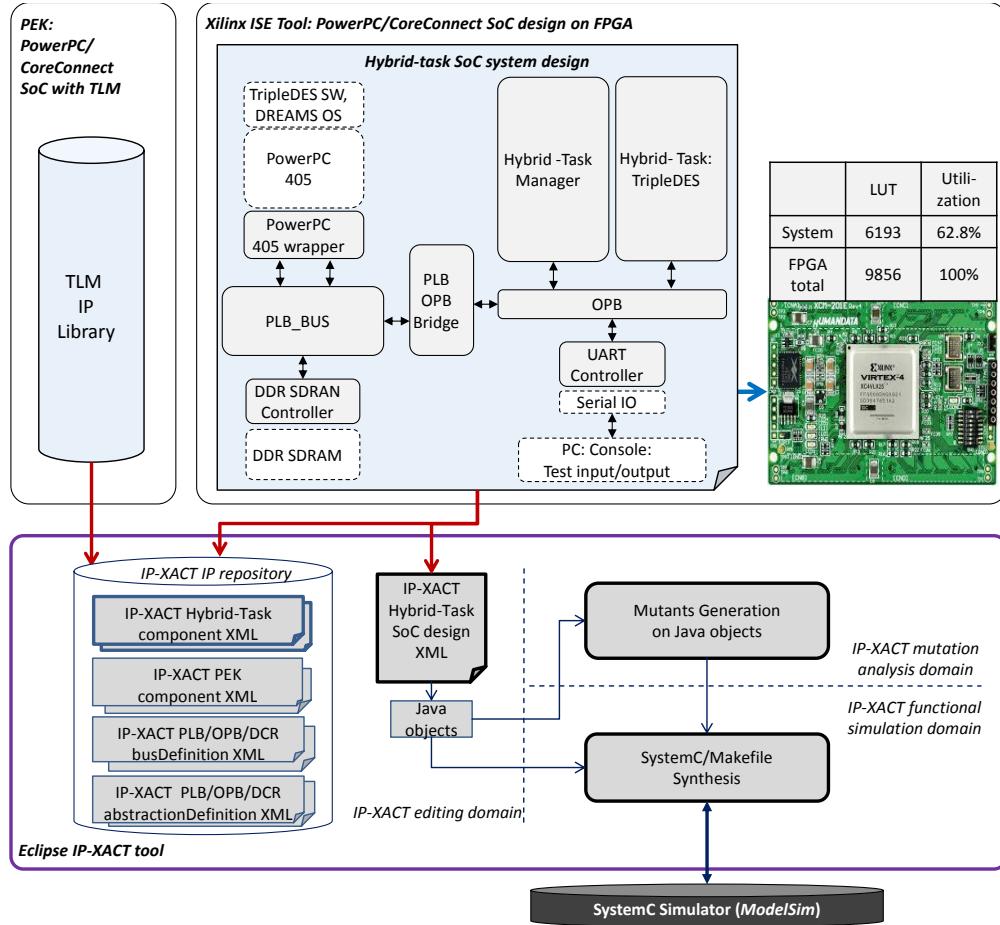

### Example: Design of Hybrid-Task SoC with Xilinx FPGA Tools

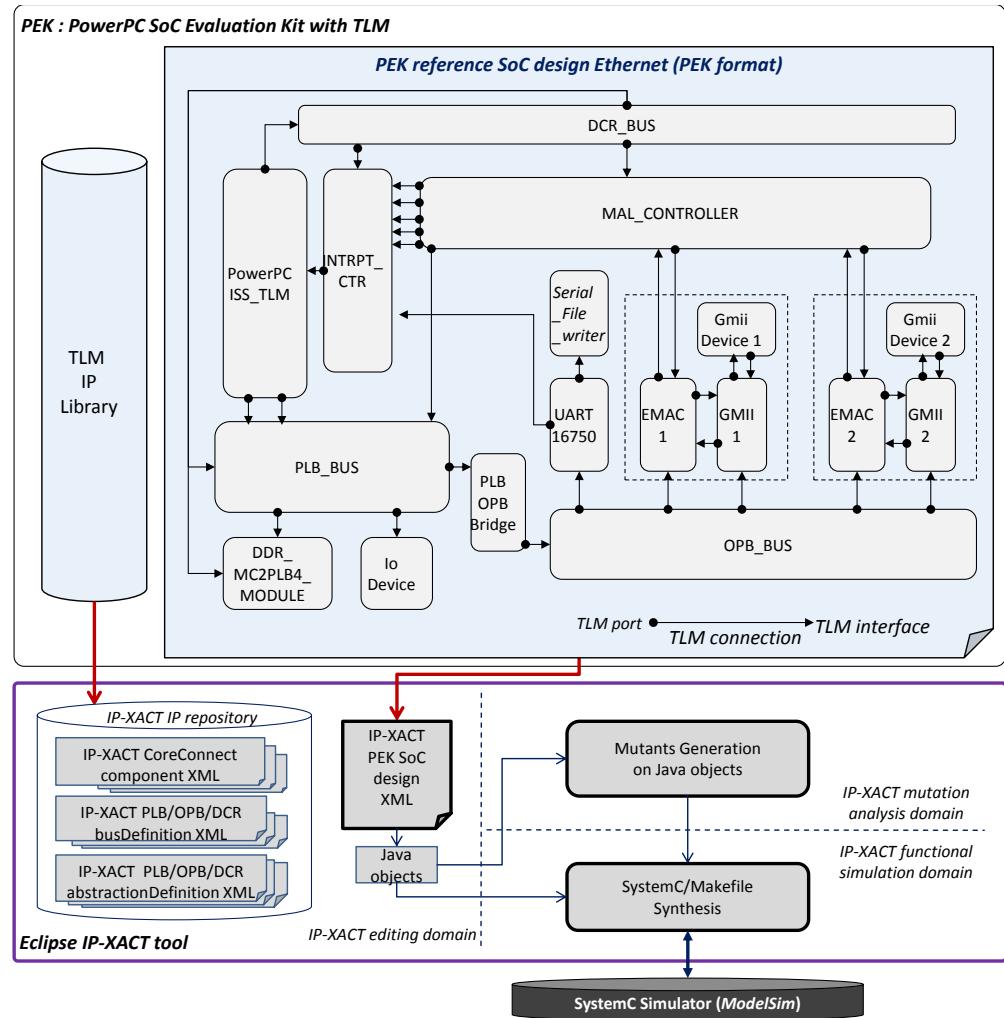

With **Figure 2.2**, we present a *hybrid-task SoC*. The purpose is, less of presenting the IPs and system themselves, to show the design steps and, in particular, the languages and tools involved. It can be viewed as an instance of the reference design flow presented above. We choose the Xilinx development environment and tools for this example, as they indeed represent a typical and state-of-the-art IP-based SoC design flow, if we do not compare the circuit implementation stage.

We have developed this *Hybrid-task SoC* as a demo system to show the concept of *unified task scheduling and task migration* on a CPU-FPGA coupled platform [13] [11]. The idea is, for example with this hybrid triple-DES task, to enable a design flow with which we are able to obtain two copies of the triple-DES encryption, one for running on

**Figure 2.2** An instance of the reference flow: design of a Hybrid-Task SoC on Xilinx

CPU and the other one for running on FPGA, whose execution can be decided then at runtime by an operating system. The two copies of a so-called *hybrid task* have corresponding states, so that each of them can have its execution suspended, execution states extracted and retrieved, and the states restored to its counterpart for a seamless execution resumption. The reason for such a *hybrid-task migration* between CPU and FPGA can be, for example, some desired *load-balancing* on these two computation hosts.

Focusing on the hardware SoC part, the main system specification is certainly the provision of functionality and interfaces for task migration, such as suspending, resuming, and restarting task execution, as just mentioned.

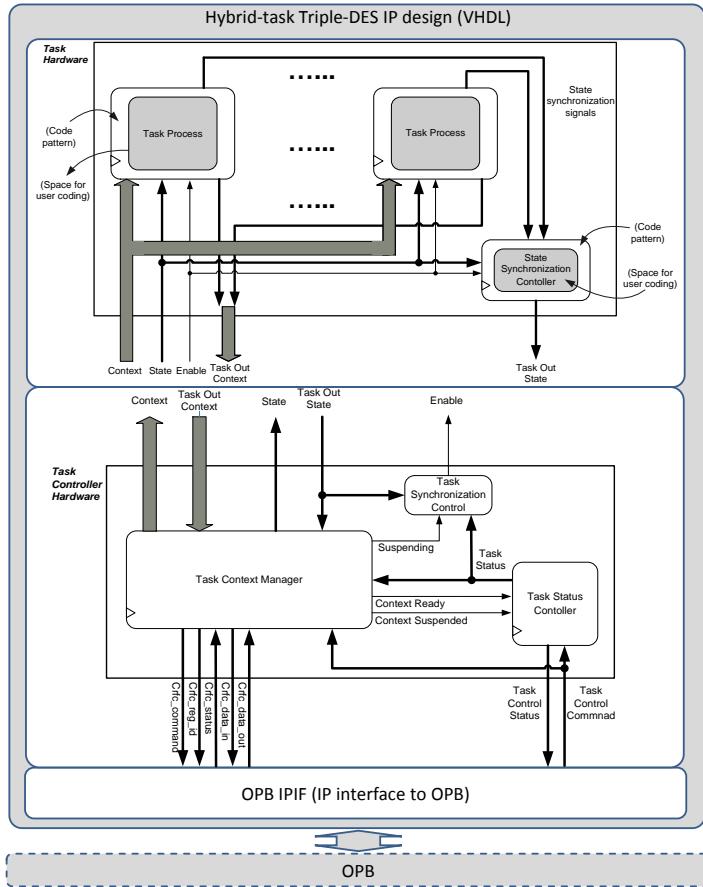

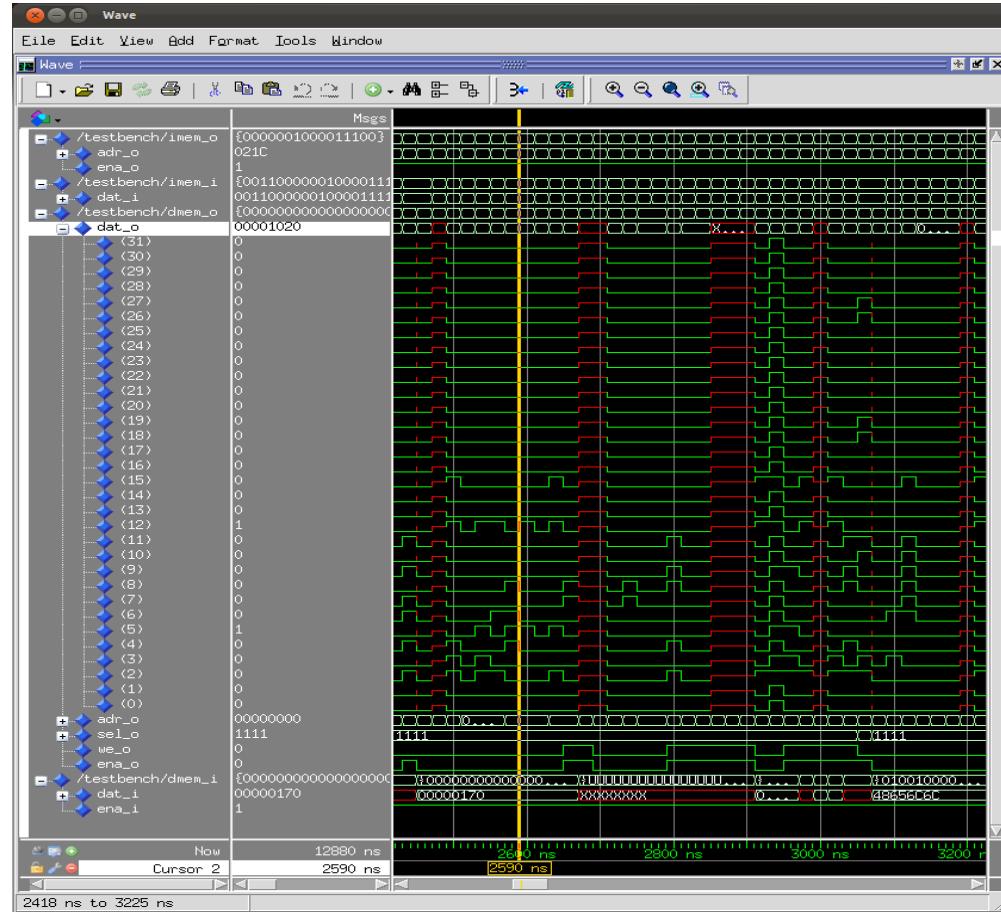

**Figure 2.3 Example IP design: Hybrid-task Triple-DES.** It is designed in VHDL, with functionality – encryption and task migration – simulated and verified with tool *ModelSim*.

Before the SoC integration, we made the design of two IP components, the *Hybrid-task Triple-DES* and the *Hybrid-Task Manager*, besides the PowerPC, memory controller, PLB/OPB buses and bridges, and UART controller directly from Xilinx IP repository.

Consider the design of *Hybrid-task Triple-DES* as the example for IP design phase. Two main expectation on the task are the conformance to the Triple-DES encryption standard and its implementation of the hybrid-task interfaces like *suspend* and *resume*.

As shown in **Figure 2.3**, the IP design is done in VHDL. With the DES encryption code taken and reused from open-source [39] and the OPB IP Interface (IPIF) generated by Xilinx tool, our design effort was mostly put on the hybrid-task controlling part. Then the IP design as a whole was simulated with tool ModelSim™. Correct production of encryption stream and response to task migration commands are thoroughly verified and debugged in ModelSim. ModelSim will be further mentioned in Section 2.2, with its capability of multi-language co-simulation.

After our best-effort verification, the IP should be packed with its metadata for later usage. In the Xilinx IP environment, this metadata consists mainly of two files – in two

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>## MPD file for triple-DES IP  BEGIN triple_des ... ## Bus Interfaces BUS_INTERFACE BUS = SOPB, BUS_TYPE = SLAVE, BUS_STD = OPB  ## Generics for VHDL or Parameters for Verilog PARAMETER C_BASEADDR = 0x00000000, DT = std_logic_vector, BUS = SOPB, ADDRESS = BASE, PAIR = C_HIGHADDR, MIN_SIZE = 0x100 PARAMETER C_HIGHADDR = 0x0000ffff, DT = std_logic_vector, BUS = SOPB, ADDRESS = HIGH, PAIR = C_BASEADDR PARAMETER C_OPB_AWIDTH = 32, DT = INTEGER, BUS = SOPB PARAMETER C_OPB_DWIDTH = 32, DT = INTEGER, BUS = SOPB PARAMETER C_FAMILY = virtex2p, DT = STRING  ## Ports PORT OPB_Clk = "", DIR = I, SIGIS = Clk, BUS = SOPB PORT OPB_Rst = OPB_Rst, DIR = I, SIGIS = Rst, BUS = SOPB PORT OPB_ABus = OPB_ABus, DIR = I, VEC = [0:(C_OPB_AWIDTH-1)], BUS = SOPB PORT OPB_DBus = OPB_DBus, DIR = I, VEC = [0:(C_OPB_DWIDTH-1)], BUS = SOPB PORT OPB_RNW = OPB_RNW, DIR = I, BUS = SOPB ... END</pre> | <pre>## PAO file for triple-DES IP  lib proc_common_v2_00_a proc_common_pkg vhdl lib proc_common_v2_00_a family vhdl lib proc_common_v2_00_a or_muxcy vhdl lib proc_common_v2_00_a or_gate vhdl lib proc_common_v2_00_a counter_bit vhdl lib proc_common_v2_00_a counter vhdl ... lib opb_ipif_v3_01_a write_buffer vhdl lib opb_ipif_v3_01_a opb_bam vhdl lib opb_ipif_v3_01_a opb_ipif vhdl lib triple_des_v1_00_a user_logic vhdl lib triple_des_v1_00_a triple_des vhdl lib triple_des_v1_00_a dual_port_reg_ctrl vhdl lib triple_des_v1_00_a fifo_channel_rd vhdl lib triple_des_v1_00_a fifo_channel_wt vhdl lib triple_des_v1_00_a reg_bank vhdl lib triple_des_v1_00_a reg_ctrl vhdl lib triple_des_v1_00_a task_section_0 vhdl lib triple_des_v1_00_a task_section_1 vhdl lib triple_des_v1_00_a task_section_2 vhdl lib triple_des_v1_00_a test_Task vhdl lib triple_des_v1_00_a test_wrapper vhdl</pre> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

**Figure 2.4 Example IP metadata: MPD and PAO descriptions for IP *Triple-DES*.**

formats called MPD and PAO – for each IP, as shown in **Figure 2.4**. For the triple-DES hybrid-task IP, the MPD (Microprocessor Peripheral Definition) file describes:

- OPB as its single bus interface.

- Its possible parameters, such as the base and high addresses when connected an OPB bus. They should be configured with new values during SoC integration, or use their default values when appropriate.

- Its ports at the component level. The ports are exposed here either with a mapping to the bus specification, for example here OPB signals, or for a later mapping to the SoC system ports.

Another complementary PAO (Peripheral Analyze Order) file further lists the paths to all files that consist the IP itself. These includes not only our VHDL design but also the dependent libraries. The *Order* in the format name PAO means that the synthesis dependences are implied by the order of the file listing. This IP metadata, as well as the IP verification, prepares our shift to the SoC system design phase.

The SoC integration is described in a Xilinx *MHS* file – Microprocessor Hardware Specification, as shown in **Figure 2.5**. The MHS format is mainly targeted at SoC integration with memory-mapped buses. In brief, it describes instantiations of IP components, their interconnections, and the corresponding configuration of their parameters.

Though in a concise form, together with the implied reference to IP metadata and the further referenced IP design files, the MHS file becomes a *complete* description of our SoC design.

To verify our hybrid-task SoC system described in MHS, the functional simulation of the whole system behavior was performed, before synthesizing and implementing the

```

## MHS for Hybrid-Task SoC

PORT fpga_0_RS232_RX_pin = fpga_0_RS232_RX,

DIR = INPUT

PORT fpga_0_RS232_TX_pin = fpga_0_RS232_TX,

DIR = OUTPUT

...

BEGIN ppc405

PARAMETER INSTANCE = ppc405_0

BUS_INTERFACE JTAGPPC = jtagppc_0_0

BUS_INTERFACE IPLB = plb

BUS_INTERFACE DPLB = plb

...

PORT CPMC405CLOCK = sys_clk_s

END

BEGIN plb_v34

PARAMETER INSTANCE = plb

...

PORT PLB_Clk = sys_clk_s

END

BEGIN opb_v20

PARAMETER INSTANCE = opb

...

PORT OPB_Clk = sys_clk_s

END

BEGIN plb2opb_bridge

PARAMETER INSTANCE = plb2opb

PARAMETER C_RNG0_BASEADDR = 0x40000000

PARAMETER C_RNG0_HIGHADDR = 0x7fffffff

PARAMETER C_RNG1_BASEADDR = 0xffffe0300

PARAMETER C_RNG1_HIGHADDR = 0xffffe03ff

...

BUS_INTERFACE SPLB = plb

BUS_INTERFACE MOPB = opb

...

PORT PLB_Clk = sys_clk_s

PORT OPB_Clk = sys_clk_s

END

BEGIN plb_ddr

PARAMETER INSTANCE = DDR_SDRAM_1

PARAMETER C_PLB_CLK_PERIOD_PS = 10000

PARAMETER C_DDR_DEPTH = 32

PARAMETER C_DDR_AWIDTH = 13

...

BUS_INTERFACE SPLB = plb

PORT PLB_Clk_n = sys_clk_n_s

PORT DDR_CLK90_in = ddr_clk_90_s

PORT DDR_CLK90_in_n = ddr_clk_90_n_s

PORT DDR_Addr = DDR_Addr

PORT DDR_BankAddr = DDR_BankAddr

PORT DDR_CASn = DDR_CASn

...

END

BEGIN opb_uartlite

PARAMETER INSTANCE = RS232

PARAMETER HW_VER = 1.00.b

PARAMETER C_BAUDRATE = 38400

PARAMETER C_DATA_BITS = 8

PARAMETER C_ODD_PARITY = 0

PARAMETER C_USE_PARITY = 0

PARAMETER C_CLK_FREQ = 100000000

PARAMETER C_BASEADDR = 0xffffe0300

PARAMETER C_HIGHADDR = 0xffffe03ff

BUS_INTERFACE SOPB = opb

PORT OPB_Clk = sys_clk_s

PORT RX = fpga_0_RS232_RX

PORT TX = fpga_0_RS232_TX

END

...

BEGIN tripple_des

PARAMETER INSTANCE = tripple_des_0

PARAMETER HW_VER = 1.00.a

PARAMETER C_BASEADDR = 0x78600000

PARAMETER C_HIGHADDR = 0x7860ffff

BUS_INTERFACE SOPB = opb

END

```

**Figure 2.5** Example SoC system design: MHS description for *Hybrid-task SoC*.

system onto FPGA. Since, on one side, the MHS description is not simulatable and, on the other side, the involved IPs are provided as VHDL models, Xilinx provides us a generation tool that transforms a MHS file into a VHDL model. With this generator, we were able to obtain a VHDL top netlist for the hybrid-task SoC and compile it together with all other IP models for a simulation, in which the system was tested and debugged.

After the simulation, with another *UCF* file – User Constraint File – that basically specifies the binding between the MHS described SoC ports and real FPGA pins, we went through the synthesis, mapping, place-and-route, and FPGA Bitstream generation steps. Software part of the system was also developed and we were finally able to run the how SoC with its software on FPGA and demonstrate the hybrid-task scheduling and migration concept. More details of the system are given in [13] [11].

### 2.1.2. SystemC and Transaction Level Modeling

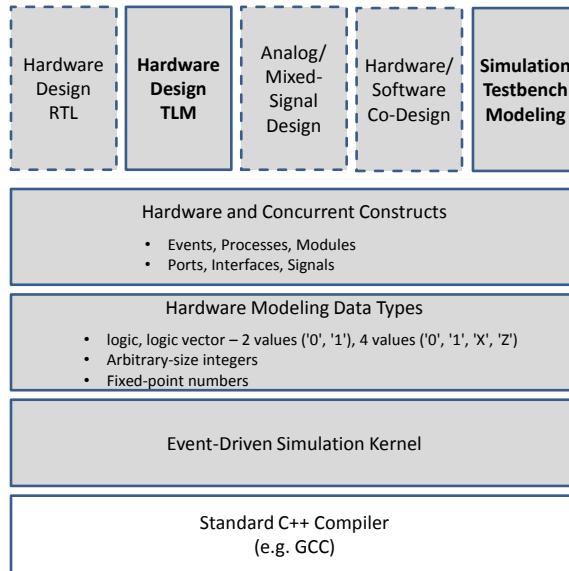

This section provides necessary background on the *SystemC* language for hardware and system design, with an emphasis on *Transaction Level Modeling* that is unique to SystemC based SoC modeling and also a focus of this work at system level.

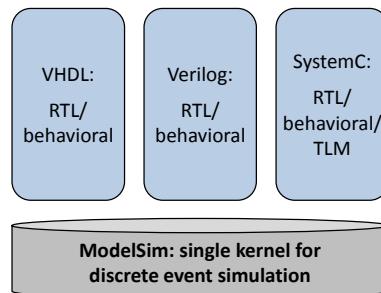

The SystemC language comes in the form of a C++ library, as shown in **Figure 2.6**, and therefore works with a standard C++ compiler such as GCC in a Linux environment. At its core, no different than most other HDLs, SystemC provides facilities for hardware description, simulation, and synthesis.

- A typical discrete-event driven simulation kernel is provided, for the modeling of concurrent hardware and system elements. Events can be timed and delta-timed,

**Figure 2.6 SystemC language: core facilities.** Its usage for traditional RTL design, hardware/software co-design, and analog/mixed-signal design is *not* a focus in this work.

with default resolution of picosecond.

- Additional data types for hardware modeling are pre-defined, besides the standard C++ types.

- Then we have the core constructs for modeling hardware and concurrency. Concurrent processes can be defined as *sc\_thread*, which should be made sensitive to some *sc\_events*. The implementation is based on the *QuickThread* C++ threading library. Threads are encapsulated in *sc\_modules*, similar to other traditional HDLs.

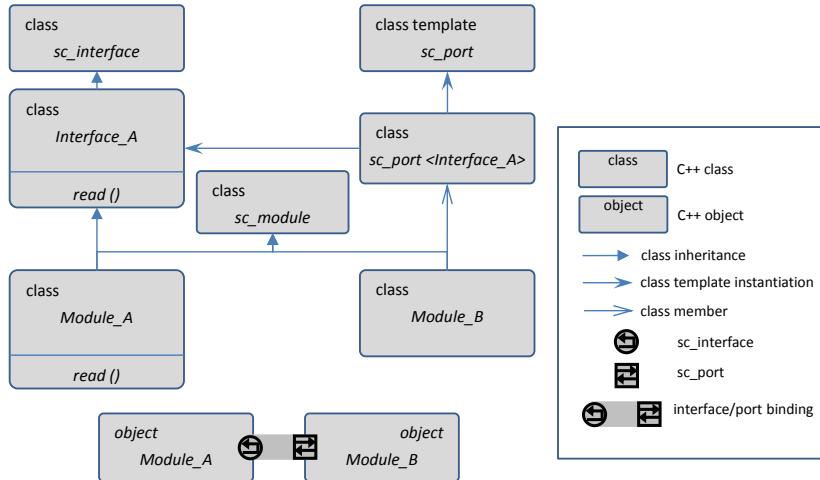

- Modules communicate with each other through ports and interfaces. **Figure 2.7** shows this mechanism. Basically, an interface class, inherited from *sc\_interface*, should first be defined, specifying the communication services to be provided at this interface, for example, reading the value from a channel. Then this signature of communication should be implemented by a module, and accessed by another module through a port that is instantiated with this interface from template class *sc\_port*. Since the first module implements the same interface as expected by the port of the second module, they are able to perform pre-defined communication during SystemC simulation, after their binding at initialization. As the fundamental mechanism for modeling communication in SystemC, this port-interface binding is used to implement not only the more abstract TLM but also RTL connections like *sc\_signal*.

There are several reasons that we skip the detailed introduction to SystemC basics.

**Figure 2.7 SystemC inter-module communication through *sc\_interface*.** It is provided by *sc\_module*, required by *sc\_port*, and bound at initialization.

Most importantly, for RTL design, SystemC provides modeling elements fundamentally no different than other HDLs. At IP level, we will consider designs at RTL or behavioral with traditional HDLs like VHDL. At system level, we will put an emphasis on TLM as a new, state-of-the-art domain.

Therefore, also assuming that our reader is *not* completely familiar with TLM, we introduce in the following not only the principle of TLM, but also an example of its application. The test-bench modeling capability of SystemC will be left to Section 2.2, in particular on *SystemC Verification Library*.

In essence, *with TLM in the context of SoC design we model on-chip communication between system components as function calls, which carries commands and data specific for that communication protocol*. Several function calls are grouped into a *TLM interface* as a class inherited from *sc\_interface*, to be provided by a *sc\_module* and accessed by another module through *sc\_port*. Use of low-level signals for communication are mostly eliminated.

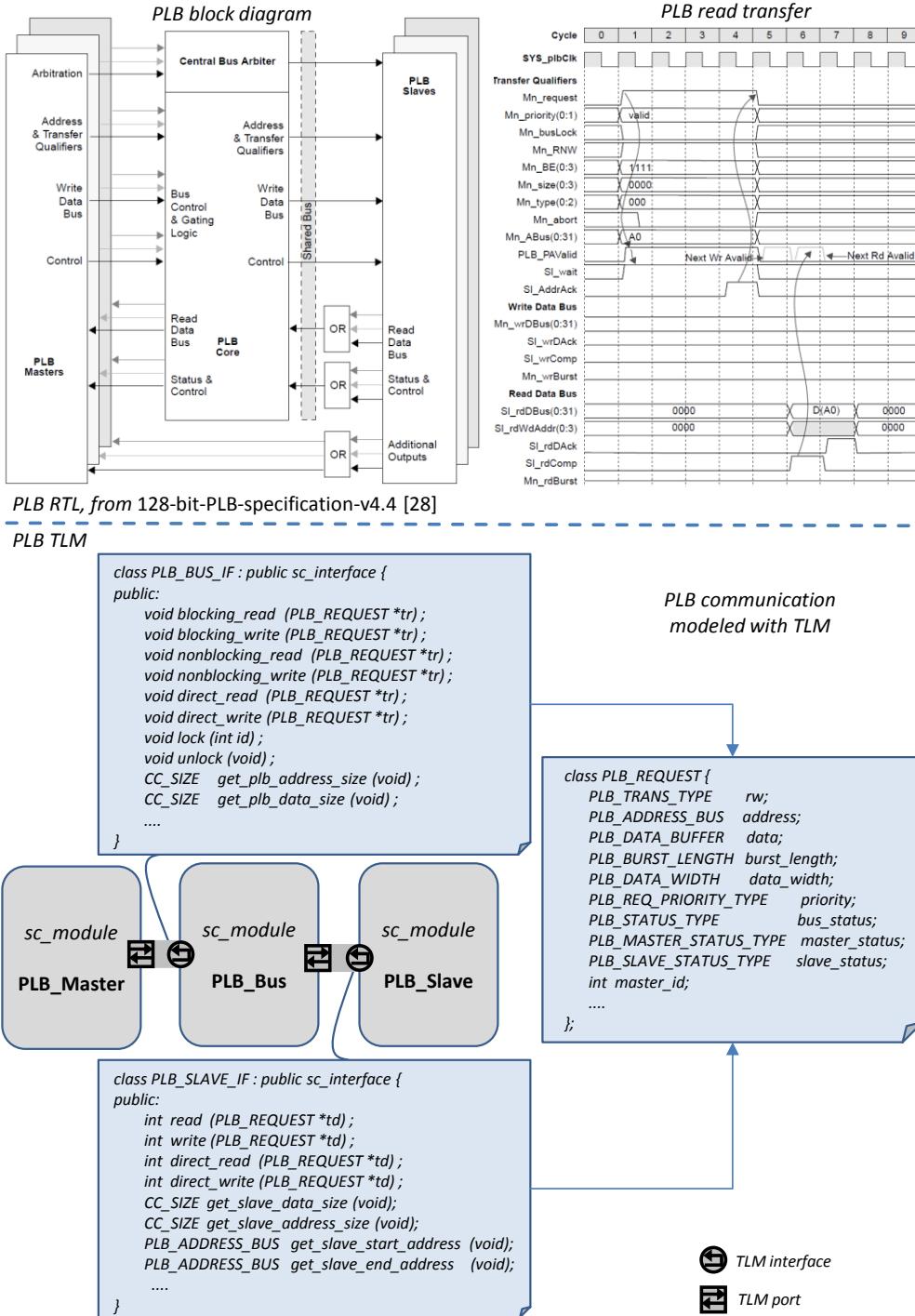

**Figure 2.8** shows this principle of TLM. Processor Local Bus (PLB), a widely used on-chip communication protocol, is used for demonstration.

The upper part of the figure shows the block diagram and a write-transfer operation from the original PLB specification [40]. Structural and timing requirements for an RTL implementation are specified. A PLB bus transaction is defined on a bunch of signals.

The lower part draws us a picture how PLB transactions are modeled at TLM, from a PowerPC/CoreConnect based SoC design library [41]. Operations, *read* and *write*, from

Figure 2.8 TLM principle: function calls to model SoC on-chip communications.

the PLB specification are abstracted as functional calls and grouped into two main TLM interfaces, *PLB\_BUS\_IF* between a PLB master and a PLB bus and *PLB\_SLAVE\_IF* between a PLB bus and a PLB slave.

*PLB\_REQUEST*, which is carried by these function calls, is a protocol specific data structure and contains fields that exactly represents signals specified by the protocol. The communication parties, i.e. *PLB\_BUS* and the corresponding ports, are responsible to maintain state-machines that match the communication protocol, according to *PLB\_REQUESTs* that they send/receive through the TLM interfaces.

The rationale behind TLM is a *separation* of on-chip communication and computation in SoC design, supposing communication generally to be modeled in a more *abstract* manner than computation. By this, SoC IPs or components at various abstraction levels, RTL or behavioral, can all be encapsulated and integrated into a TLM communication platform. This enables the TLM based SoC modeling, simulation, and evaluation, which is a focus of our verification method at SoC system level.

Timing in design and verification is *not* a focus in this work. TLM interfaces can be implemented with different timing abstractions, cycle accurate or timing approximate – for example, whether the *read* operation in the *PLB\_BUS\_IF* is implemented with clock cycles strictly conforming to the original specification, or only in a functionally correct way. TLM wrapped computation can also be of different timing accuracy, regardless of communication timing. In [8], we have also proposed a system refinement process based on TLM, taking into consideration both software and hardware.

The contribution of this thesis at SoC system level will focus on the gap between design of system integration and TLM based functional system simulation, as well as the quality of such simulation.

Further, automated TLM extraction from RTL and TLM synthesis to RTL are both *not* considered in our approach, though the equivalence checking between these two levels can also be accounted as a task of functional verification. Interested readers can refer to [36] [37] [42], for example.

### **Example: TLM based SoC Design Experiment with ARM/AMBA**

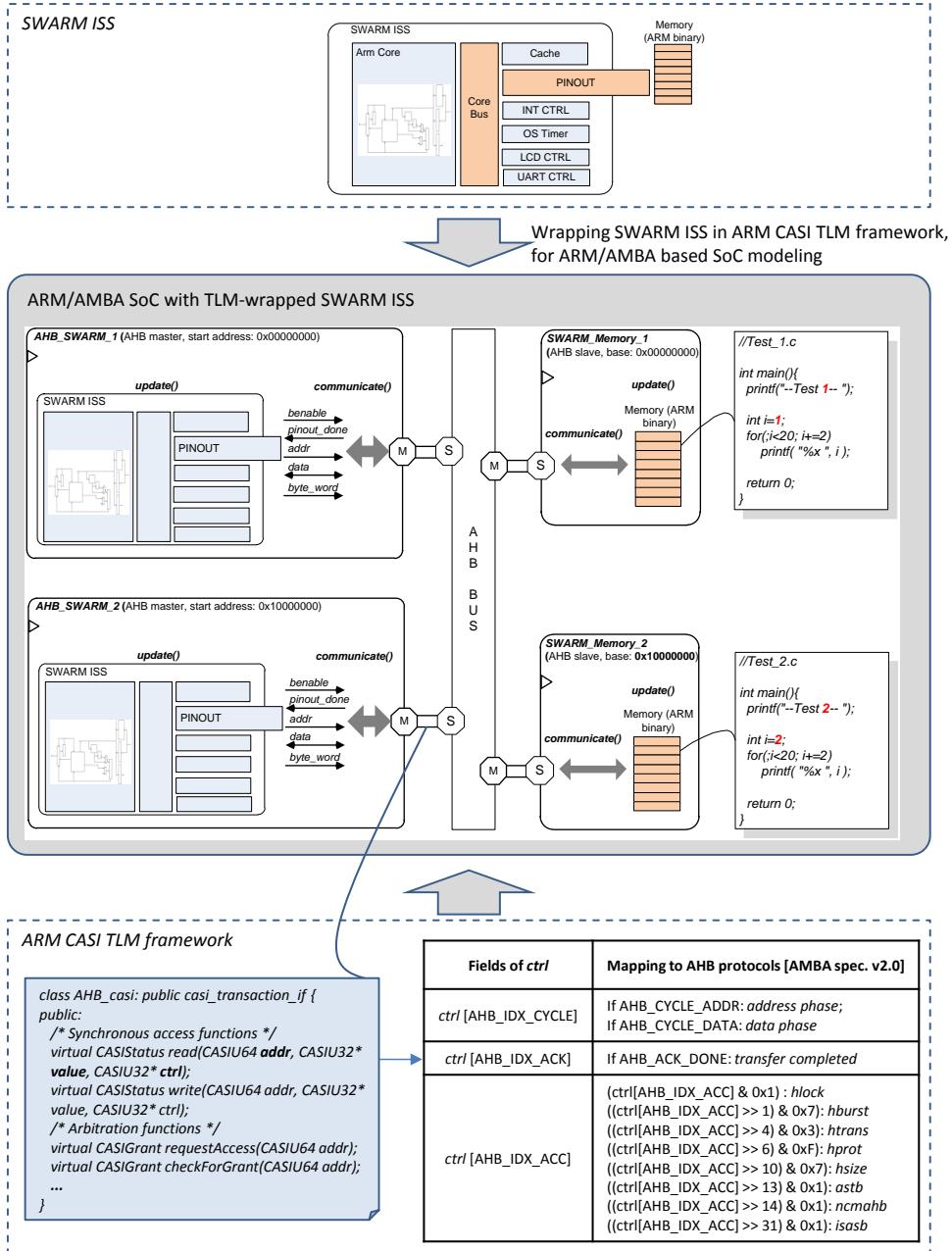

We have carried out this small design experiment shown in **Figure 2.9**, as a further demonstration of TLM design.

There are two inputs for the experiment. One is an ARM microprocessor model called *SWARM – SoftWare ARM* [43] [44]. The other one is a TLM design library for AMBA SoC architecture, called *CASI AMBA – Cycle Accurate Simulation Interface AMBA* [45].

Written in C++, *SWARM* models an ARM 7 processor that implements the ARMv4T architecture. When used as Instruction Set Simulator (ISS), it executes ARM instructions in a *cycle-accurate* manner. To be cycle accurate, it also models and simulates partially the microarchitecture of the processor, as shown in the figure. Further, it includes several basic

**Figure 2.9 TLM based SoC design experiment.** We have used ARM CASI TLM framework to wrap SWARM ISS and model a basic ARM/AMBA system.

peripheral models connected to an internal bus, such as a cache with configurable size. It is able to run a porting of Linux.

SWARM has been used in several SoC research experiments such as [44], because of its open-source nature and the popularity of ARM/AMBA SoC architecture. This also leads to our motivation of taking it as an ARM processor IP, packing it as a TLM component, and composing a TLM SoC demonstration.

For this, we find the *CASI AMBA* TLM library that is directly provided by ARM. As mentioned, the core of such TLM modeling is the abstraction of an on-chip communication protocol into TLM interfaces that consist of function calls. In the figure, we show a TLM interface from the *CASI AMBA* library, which abstracts AMBA AHB (Advanced High performance Bus) protocol. We see how the *read/write/requestAccess/checkForGrant* function calls represent the bus access and how the protocol signals are encapsulated and carried by these calls. As pointed out by the name, such CASI AMBA communication is modeled in TLM as cycle accurate to the original protocol specification, so that we can make accurate simulation, performance evaluation, and design exploration.

This CASI AMBA library does not include any concrete SoC component, except for the bus models. However, because of the advantage of TLM that provides a separation between on-chip communication and computation, we are able to wrap IP components at any level, RTL or behavioral, as TLM components and enable a TLM-based SoC system integration.

As **Figure 2.9** shows, using the CASI AMBA library we created a TLM wrapper for SWARM ISS, which converts its original memory-accessing *PINOUT* into the TLM AHB interface, and backward. We also wrapped a memory model as a TLM AHB slave, which loads ARM binary at its initialization.

The simple system was then integrated by instantiating an AHB bus from the library and at the same time attaching dual TLM SWARMS and two memory models to the bus. Two test programs were supposed to exercise this system integration in a simulation.

In the end, we were able to compile the whole TLM system with SystemC, compile the software programs with a cross-compiler *gnuarm-3.4.3*, and successfully simulate the system with dual-SWARM execution.

### 2.1.3. IP-XACT Standard for IP Reuse and SoC Integration

Verification depends on the language that is used for design. For IP-level designs, for example a microprocessor IP, we assume traditional HDLs or SystemC in use, either at RTL or behavioral. For SoC system level, we try to propose a systematic verification framework based on a standard IP reuse and SoC integration language, or format, called *IP-XACT*. In this sense, IP-XACT is our HDL at SoC system level.

The IP-XACT standard has been made IEEE 1685-2009 [29] in 2010, with the effort initiated even earlier by the *SPIRIT* consortium, formed by several major semiconductor and EDA tool vendors. It intends to provide standardization support to an IP-based SoC design flow, such as that previous example on Xilinx FPGA design environment. It is exactly the formats of IP metadata and their integration – MPD, PAO, and MHS in the

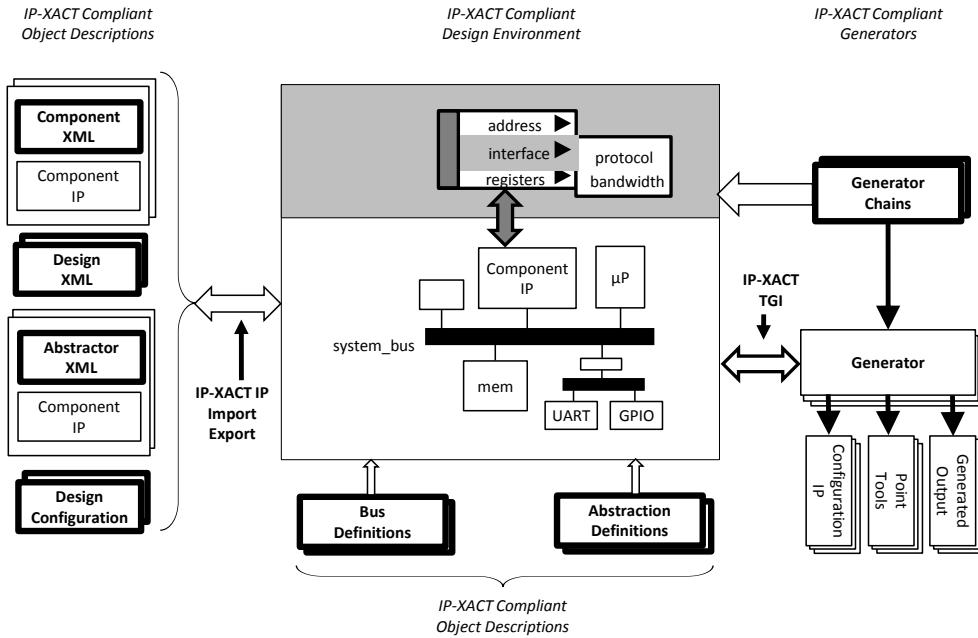

**Figure 2.10** Overview of IP-XACT standard [29].

Xilinx case – that IP-XACT tries to standardize. The idea is to have unified, vendor-neutral exchange format for both IP vendors and SoC integrators.

**Figure 2.10** from IEEE 1685-2009 [29] shows a blueprint for IP-XACT based IP reuse and SoC integration. At its core, IP-XACT *defines an XML Schema as the standard electronic format for packaging reuse information of IPs, as well as for designing SoC systems by IP integration*. Several major XML schema elements are presented here, including **component**, **design**, **abstracter**, **design configuration**, **busDefinition**, **abstractionDefinition**, **generator**, and **generator chains**. Any top IP-XACT XML document belongs to one type of them.

Based on these elements, we have two main use scenarios with IP-XACT, as an IP provider or a SoC integrator. We give an explanatory listing of IP-XACT schema for these two scenarios, instead of a comprehensive standard repetition. For this, we also prefer an example based, graphical representation of the IP-XACT schema. Basics about XML Schema can be found in [46].

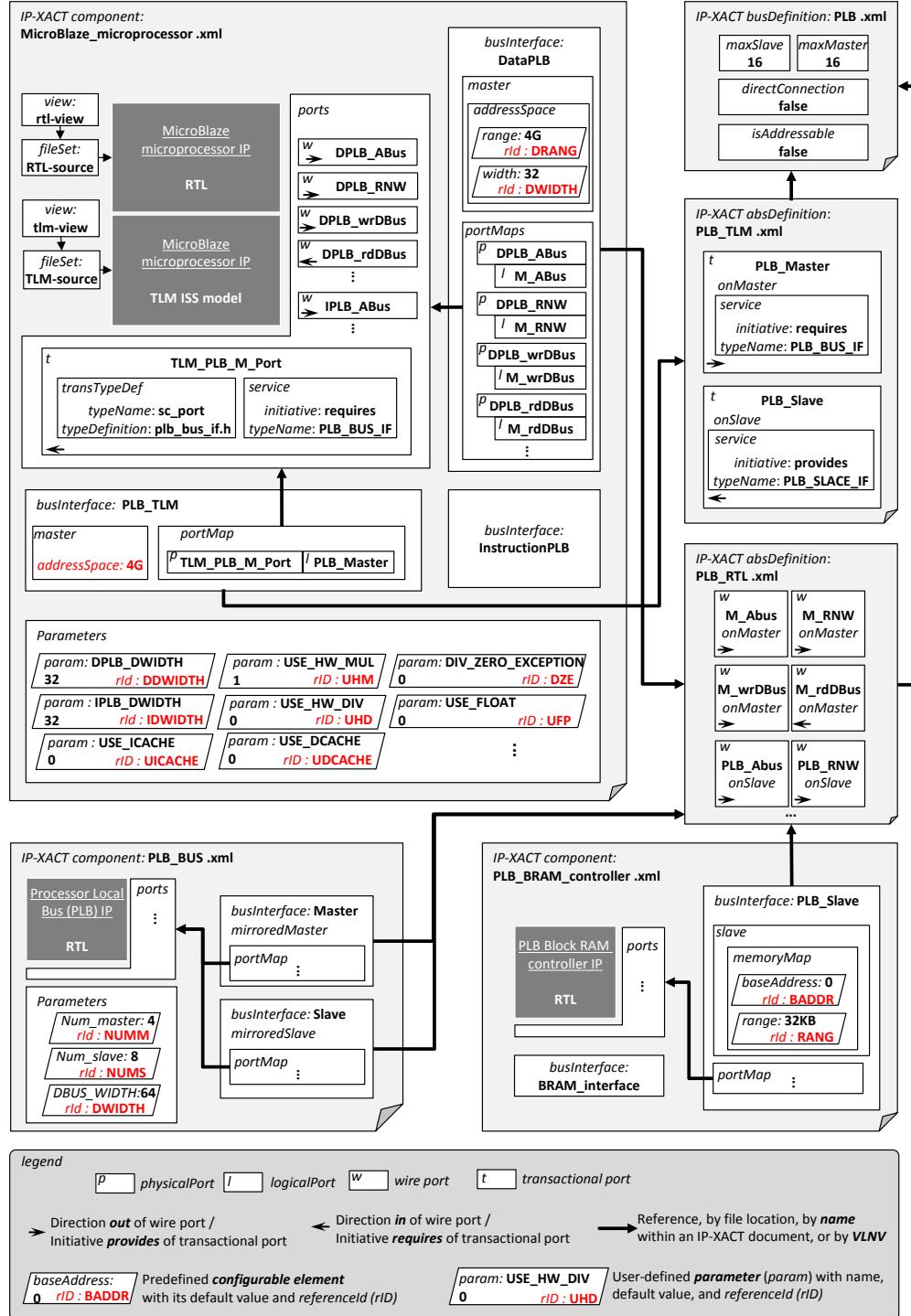

First, IP vendors use an IP-XACT **component** XML file to package all reuse-related information of an IP core, which accompanies this IP as its electronic data sheet. The information includes mainly how the IP can be configured and interconnected to other IPs via a memory-mapped bus connection, which is the main focus of IP-XACT other than more sophisticated on-chip architectures like Network-on-Chips. **Figure 2.11** shows several IP descriptions using IP-XACT **component**. Note that XML documents are depicted in graphics, as in the rest of this section.

Figure 2.11 IP-XACT component XML schema for IP description.

- Multiple **views** of the IP could be described in its **component** XML document. If the IP are provided with both VHDL source files and an abstract C simulation model, we can then include two views, say, *VHDLSourceView* and *CModelView*

in its IP-XACT description. In each *view*, the used language could be described. A *view* references a set of files that implements this *view*.

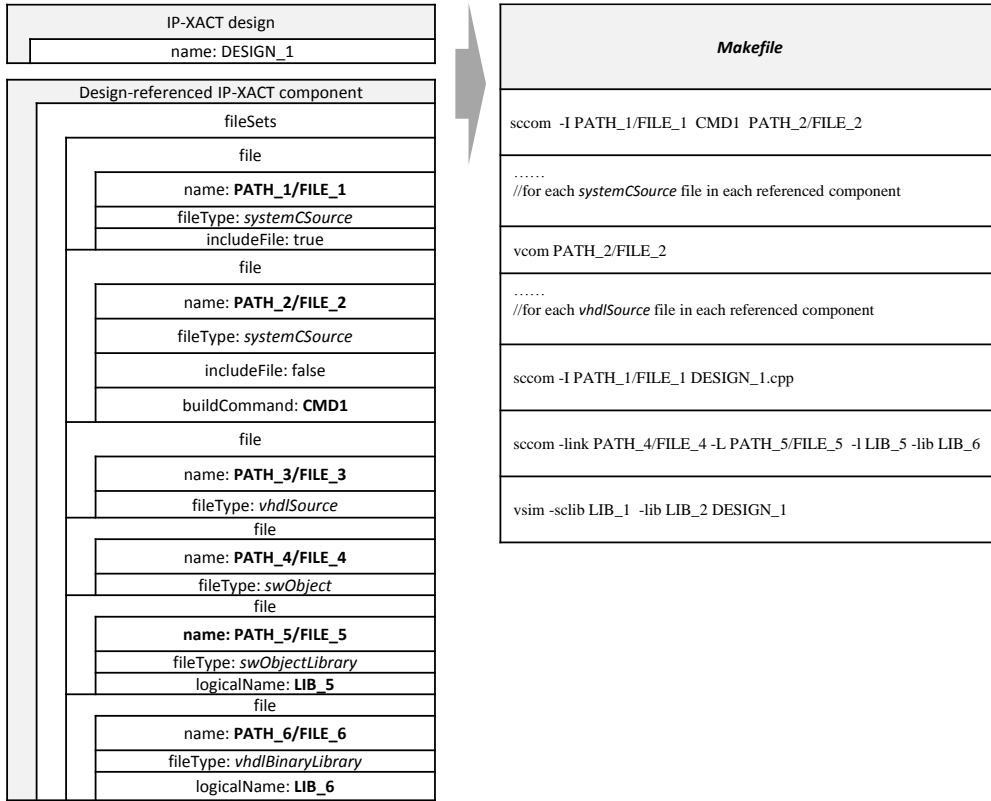

- A file set to be referenced from a *view* is first documented with *fileSet*. Each *file* in a **fileSet** describes one of the real files or directories that comprise the IP. Particularly, it contains extensive information that can be leveraged when later the IP needs to be compiled or synthesized in design flows.

This includes a *name* as the exact path to the file or directory and a *fileType* as the format of the file, which shall be selected from a pre-defined list with *systemCSource*, *vhdlSource*, *VerilogSource*, *swObject*, *swObjectLibrary*, etc. Other possible descriptions are *includeFile* as a Boolean tag to indicate whether the file is an include file, *logicalName* for the name of a library file, and *dependency* for a directory that this file depends on. Last, one can further specify with *buildCommand* explicitly commands and options that should be used in the file compilation.

- **Ports** of an IP to be exposed for connection can be declared as a collection of *port*, which should be of either a *wire* type or a *transactional* type. A *wire port* corresponds to a traditional scalar port or vectors of scalars in HDLs, such as *std\_logic* and *std\_logic\_vector* by default for VHDL. *Direction* of the port shall be specified. If the port is a vector, its *left* and *right* bit should be also be specified.

With *transactional* port, the latest Transaction Level Modeling (TLM) and TLM IPs are supported by IP-XACT. It is much tailored to SystemC transactional modeling that has become the de-facto TLM standard. First, the type of the port in SystemC can be expressed in *typeName*, such as the common *sc\_port*, *sc\_module*, *sc\_export*, *sc\_initiator*, *sc\_target*, or *sc\_socket*. Second, more importantly, the interface implemented by this port shall be detailed in a *service* structure, as TLM connection is essentially centered at SystemC interfaces. The *initiative* of a *service* is the direction of the interface implementation, having the value *requires* if it is a *sc\_port*, *provides* if a *sc\_export*, or *both* for a *sc\_socket*. Another *typeName* included in *service* describes the exact SystemC type of the interface, along with *typeDefinition* indicating the real SystemC file that declares the interface. Either a *wire port* or a *transactional port*, it should have a *name* that is exactly how the port is named in the real IP model.

- Later in IP-XACT system integration, there are two alternatives of connecting two components. One is direct port-to-port connection and the other is based on pre-specified bus interfaces. For the latter, another two top elements of IP-XACT schema need to be explained first, namely **busDefinition** and

*abstractionDefinition*, which as a pair resemble a traditional signal specification for a bus protocol.

*BusDefinition* specifies general properties of a bus, such as its *maxMasters* and *maxSlaves*. Multiple *abstractionDefinitions* may belong to one *busDefinition*, as now both RTL and TLM are supported by IP-XACT.

Each *abstractionDefinition* is a collection of *port* descriptions, which provide quite similar information as those in a *component* element, but here for a specification purpose instead of declaration of implemented IP ports. Besides, a *port* in *abstractionDefinition* also specifies whether it is *required*, *optional*, or *illegal* to be present on the bus interface and, when present, whether it should be implemented as *onMaster*, *onSlave*, or *onSystem*. Signals like system clock and reset should be grouped as *onSystem*.

- For the *bus/abstractionDefinition* based interconnection, the bus interfaces of an IP are declared by *busInterfaces* in its *component* description. Each *busInterface* possesses a unique reference to a pair of existing *busDefinition* and *abstractionDefinition*, so that a *busInterface* based interconnection between two components can be automatically verified by comparing the referenced *bus/abstractionDefinitions*.

This also enables automated port connection during SoC integration, between two IP components, via a *portMaps* structure. Such a list of *portMap* is defined for each *busInterface*, which maps a *physicalPort*, as reference to a *component port*, to a *logicalPort* that is reference to a *port* specified in *abstractionDefinition*. This defines actually how the bus protocol *abstractionDefinition* is implemented by this *busInterface*.

Common bus features like *endianness*, *bitSteering*, and *bitsInLau* may further be described for *busInterface*. *ConnectionRequired* indicates whether the interface shall be connected when integrated.

- For memory-mapped system integration, it is essential that we describe the connection purpose of *busInterface* as one from seven types defined in IP-XACT - *master*, *slave*, *system*, *mirroredMaster*, *mirroredSlave*, *mirroredSystem*, and *monitor*.

Consider three typical IP components that are shown in **Figure 2.11**: a microprocessor core, an on-chip bus, and a memory controller. The microprocessor *component* description probably includes a *busInterface* in the mode of *master*, which mainly defines an *addressSpace* as the addressable range from this master. An executable image can also be referenced.

*BusInterface* of the memory controller *component* should have a mode *slave*, where a memory-map block such as a single **addressBlock** with specification of its **baseAddress**, **range**, and **width** can be defined. Specific registers within the *addressBlock* can also be described by their **size** and **addressOffset**. The PLB bus *component* exposes two *busInterfaces*, one as *mirroredMaster* and another as *mirroredSlave*, to be connected to a matching *master* interface and a *slave*, respectively. All the components may further have *system* as well as *mirroredSystem* interfaces as in/outlets for system clock and reset signals.

We should note that in a *portMap* on *master*, *slave*, or *system busInterface*, the *physicalPort* shall implement the same direction as specified by the *logicalPort*. To the opposite, the *physicalPort* in a *portMap* on *mirroredMaster*, *mirroredSlave*, or *mirroredSystem busInterface* shall implement the inversed direction from the *logicalPort* specification. Mapping of component ports to bus specification enables their seamless interconnection later. Further, *monitor* is a special interface to be exposed by any component for verification purpose.

- In *component* and in IP-XACT generally, any element defined with an **id** attribute is configurable. For a *component* description, its configuration is done at a system *design* description that instantiates this component, by assigning the configurable elements new values under references to their *ids*, if the default values should not be effective. Slave **baseAddress** is a common use case of configurable element.

In addition to an *id*, more attributes may be defined on a configurable element, to specify and constrain its value options. Input *format* of the element can be specified as one from **bitString**, **bool**, **float**, **long**, and **string**. Attribute **resolve** defines how the element value should be configured, such as **user** indicating the value to be set by user input or **dependent** meaning that the value shall be calculated from other element values. Candidate values may also be specified in a **choice** structure as a list of enumerations. With **minimum** and **maximum** we further specify the lower and upper bound of the element value.

- Moreover, there are basically two categories of configurable elements in a *component* description. The first category is directly HDL derived, if the IP under description is in the form of a HDL model. These parameters do not have a pre-defined semantic, or meaning in IP-XACT schema, but they are immediate place holders for HDL model parameters. They describe, for example, constructor parameters of a SystemC module or generics of a VHDL entity. Such a parameter has a **name** associated that is directly taken from the model, besides all the above mentioned configuration attributes.

**Figure 2.12 IP-XACT design.** It describes a SoC integration design with *component* instantiation, configuration, and interconnection.

The second category includes those configuration elements with IP-XACT semantics. For example, IP-XACT defines a *baseAddress* for a *slave* bus interface, with this address specified as a configurable attribute. Being aware of this makes difference for us, as a configurable element with IP-XACT specified semantic means that we can take corresponding actions during the synthesis or manipulation on the element.

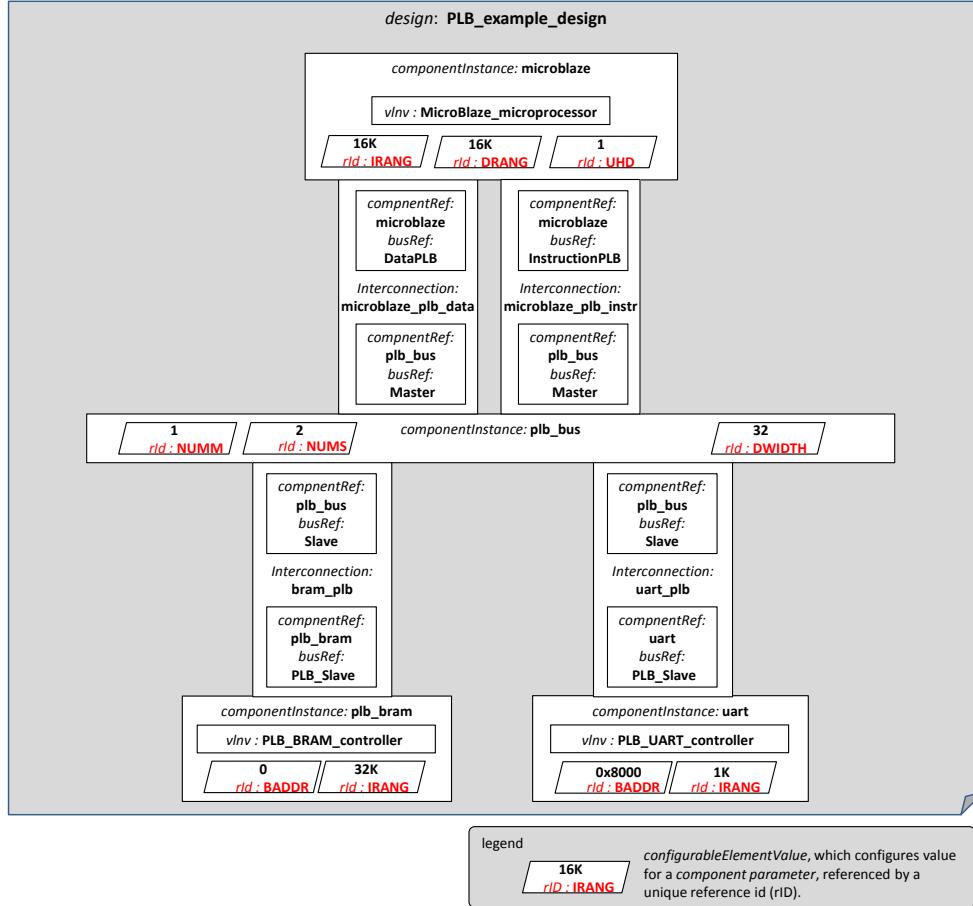

In the second scenario, SoC integrators use an IP-XACT *design* XML document to assemble an integrated system from existing *components*, as the example shows in **Figure 2.11**. This *design* mainly describes the instantiation of IP components, necessary interconnections between them, and their correspondingly derived configurations.

- A *design* instantiates all its components –processing elements and on-chip buses – by a list of *componentInstances*. A *componentInstance* is assigned a unique *instanceName* within the *design* and has a reference to the concerned IP-XACT *component* description.

The *component* is identified by the *vlnv* unified cross-document referencing mechanism of IP-XACT, as also used by *abs/busDefinition* references. In this *vlnv* system, every IP-XACT top object/document shall possess a *versionedIdentifier*, as a combination of *vendor-library-name-version*, which uniquely identifies the document in all IP-XACT mentioned context. Then this top object can be referenced within another document by a *libraryRefType* element that consists of also *vendor-library-name-version* of that object. A single *instanceName* is enough for further identification of this component within this *design*.

- IP-XACT facilitates mainly memory-mapped bus interconnection for system level integration. Each connection between two components through a bus interface is defined by an *interconnection* element. Besides a name for the connection, an *interconnection* contains merely two references of component bus interfaces. Each such reference is a pair of names, one for the component instance name assigned within this design and the other for the name of the bus interface in the original *component* description. As both interfaces not only have references to the same *abs/busDefinition* that they intend to realize but also specify with *portMaps* how the *abs/busDefinition* are implemented by the component ports, we are able to resolve correct signal connections on this bus interface.

- In *design*, we also have the possibility of creating *adHocConnections* not via any bus specification but on a port-by-port basis. Each *adHocConnection* is defined as a list of two or more port references, to bundle multiple component ports together.

- We need to assign configurable elements of the instantiated and interconnected components with appropriate values according to this integration, such as the address offset of each slave interface, if they should vary from the default. For this, we can define in *componentInstance* a list of *configurableElementValue*, each with a *referenceId* that is the **id** of the configurable element in the *component* description and its new value.

- Further, hierarchical design is also supported by IP-XACT, through the possibility of wrapping a *design* further as a *component*.

Besides these two use scenarios for IP integration, IP-XACT *generators* define standard integration interface between a main design environment and third-party tools: how the main design environment can launch a third party tool and how the latter can access the IP-XACT files in the former, through the interface called Tight Generator Interface. This tool integration is *not* a focus here and one can refer to IP-XACT standard for more information.

A general note here at the end of the section. A big challenge that we will address in this thesis is the provision of *systematic* verification for an IP-XACT SoC design. We

definitely find a gap between SoC design with IP-XACT and its functional verification, since an XML file in IP-XACT is *not* directly simulatable for verifying its behavior.

## 2.2. Simulation Based Functional Verification

*Functional verification* is the process of verifying whether a design conforms to its specification, as shown in **Figure 2.13**. Take a microprocessor design for example. The main specification to be verified regarding its functionality should be whether it can execute correctly sequences of instructions defined in the ISA that it intends to implement. Non-functional properties of a design, such as timing and power, are not the topic of our work.

**Figure 2.13** Functional verification: whether a design conforms to its specification.

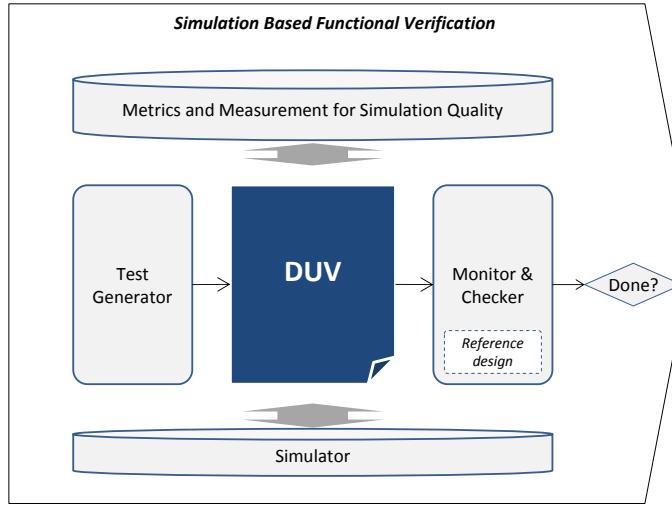

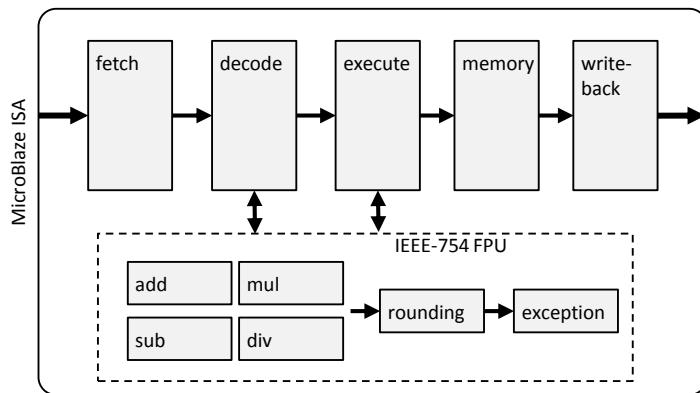

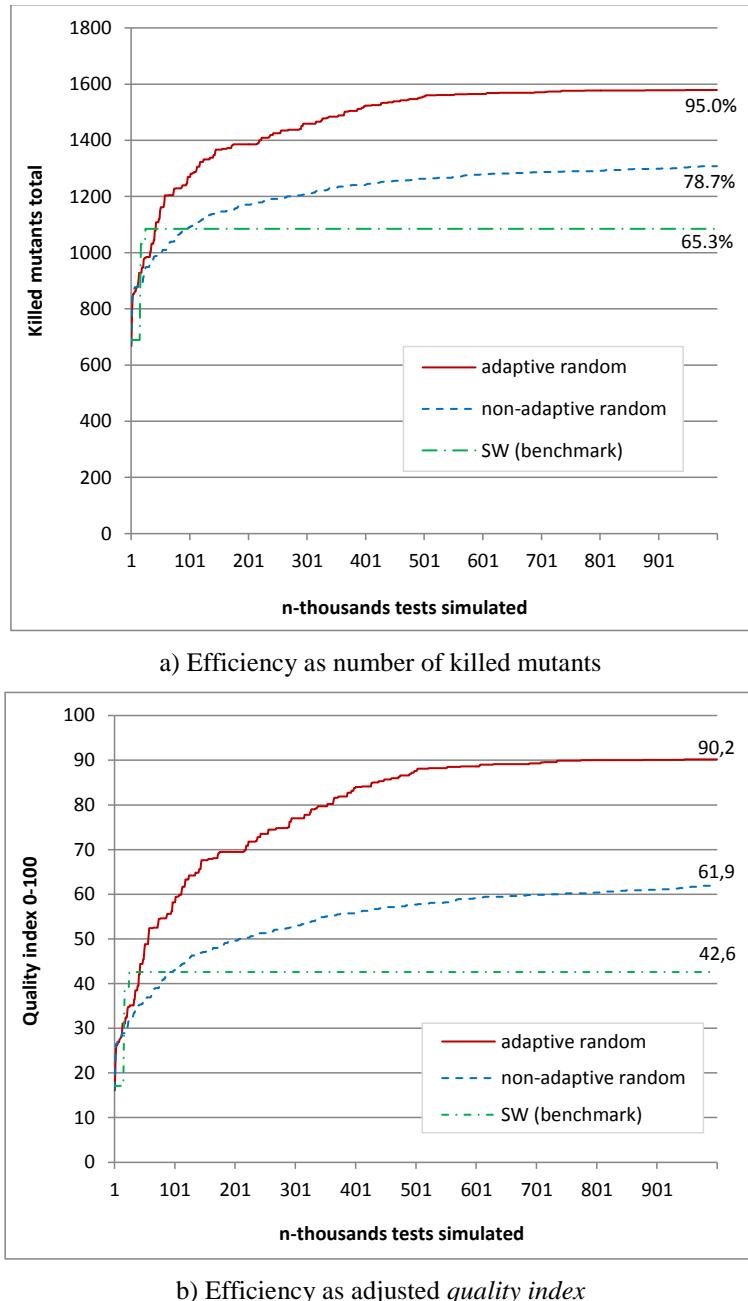

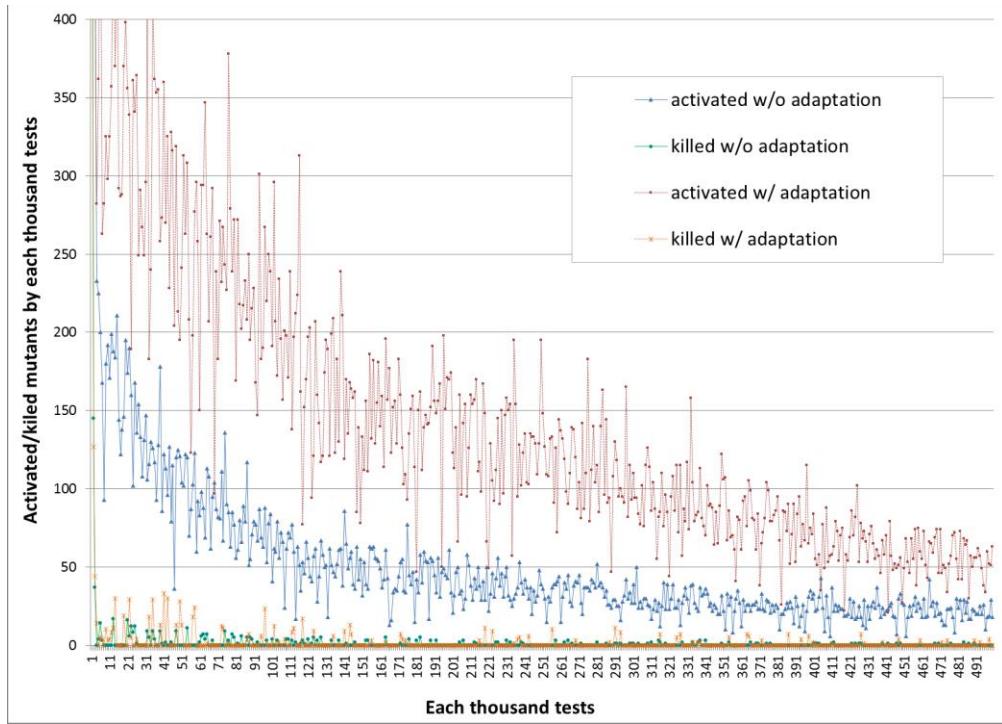

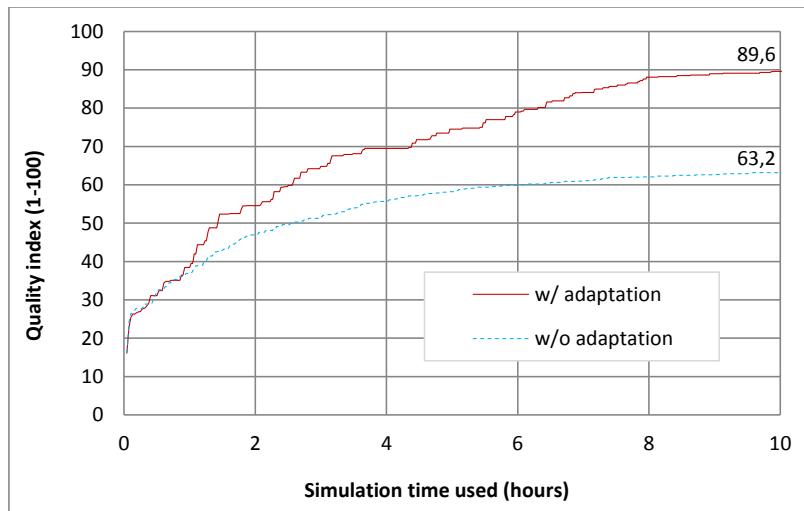

We assume *simulation based verification*, with its principle shown by **Figure 2.14**, still the overwhelming technology employed for functional verification and therefore also taken as the basis of our entire work, though other ways of design verification do exist, such as model checking [47] or FPGA based prototyping. They are not discussed, since our verification methodology to be proposed is purely based on simulation, even eliminating *symbolic execution* that is found in some literature on test generation. Therefore, this background section on verification is concentrated on simulation.